(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2017-517077

(P2017-517077A)

(43) 公表日 平成29年6月22日(2017.6.22)

(51) Int.Cl.

G06F 12/00

(2006.01)

F 1

G 06 F 12/00

5 6 4 A

テーマコード(参考)

5 B 0 6 0

審査請求 未請求 予備審査請求 有 (全 48 頁)

(21) 出願番号 特願2016-570976 (P2016-570976)

(86) (22) 出願日 平成27年5月11日 (2015.5.11)

(85) 翻訳文提出日 平成29年1月31日 (2017.1.31)

(86) 國際出願番号 PCT/US2015/030214

(87) 國際公開番号 WO2015/187308

(87) 國際公開日 平成27年12月10日 (2015.12.10)

(31) 優先権主張番号 14/298,730

(32) 優先日 平成26年6月6日 (2014.6.6)

(33) 優先権主張国 米国(US)

(71) 出願人 595020643

クアアルコム・インコーポレイテッド

Q U A L C O M M I N C O R P O R A T

E D

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100112807

弁理士 岡田 貴志

最終頁に続く

(54) 【発明の名称】メモリインターフェースのためのプログラマブル電力

## (57) 【要約】

遅延制御のためのシステム及び方法が本明細書で説明される。一実施形態では、遅延システムは、第2の遅延回路に電圧バイアスを供給し、更新レートで電圧バイアスを更新するように構成された第1の遅延回路を備え、ここにおいて、電圧バイアスは、第2の遅延回路の遅延を制御する。遅延システムはまた、第1の遅延回路の更新レートを調整するように構成された更新コントローラを備える。例えば、更新コントローラは、遅延システムを組み込んでいるメモリインターフェースのタイミング要件に基づいて更新レートを調整し得る。更新レートは、タイミング要件がより緩和されると、電力を低減するために低減され得、タイミング要件がより厳しくなると増加され得る。

【選択図】 図7

FIG. 7

**【特許請求の範囲】****【請求項 1】**

遅延システムであって、

第2の遅延回路に電圧バイアスを供給し、更新レートで前記電圧バイアスを更新するよう構成された第1の遅延回路と、ここにおいて、前記電圧バイアスは、前記第2の遅延回路の遅延を制御する、

前記第1の遅延回路の前記更新レートを調整するように構成された更新コントローラとを備える遅延システム。

**【請求項 2】**

前記更新コントローラは、前記第2の遅延回路によって遅延されている信号のデータレートに基づいて前記更新レートを調整するように構成される、

請求項1に記載の遅延システム。

**【請求項 3】**

前記更新コントローラは、前記信号の前記データレートが第1のデータレートに略等しい場合、前記更新レートを第1の更新レートに設定し、前記信号の前記データレートが第2のデータレートに略等しい場合、前記更新レートを第2の更新レートに設定するように構成され、前記第1のデータレートは、前記第2のデータレートよりも低く、前記第1の更新レートは、前記第2の更新レートよりも低い、請求項2に記載の遅延システム。

**【請求項 4】**

前記第1の遅延回路は、基準クロックに基づいて前記電圧バイアスを更新するように構成され、ここで、前記更新レートは、前記基準クロックのN個の周期あたり1回の前記電圧バイアスの更新に略等しく、Nは整数であり、前記更新コントローラは、Nを調整するように構成される、請求項1に記載の遅延システム。

**【請求項 5】**

前記更新コントローラは、前記第2の遅延回路によって遅延されている信号のデータレートが第1のデータレートに略等しい場合、Nを第1の値に設定し、前記信号の前記データレートが第2のデータレートに略等しい場合、Nを第2の値に設定するように構成され、前記第1のデータレートは、前記第2のデータレートよりも低く、Nの前記第1の値は、Nの前記第2の値よりも大きい、請求項4に記載の遅延システム。

**【請求項 6】**

前記第1の遅延回路は、

前記電圧バイアスの更新ごとに、基準クロックからパルス対を生成するように構成された更新回路と、ここにおいて、各パルス対は、第1のパルス及び第2のパルスを備え、前記第1のパルスは、前記第2のパルスに対して前記基準クロックの略1周期ぶん遅延されている、

各パルス対の前記第2のパルスを前記電圧バイアスによって制御された量ぶん遅延されるように構成された電圧制御型遅延回路と、

パルス対ごとに、それぞれの前記第1のパルスとそれぞれの遅延された前記第2のパルスとの間の位相誤差を検出するように構成された位相周波数検出器と、

それぞれの検出された前記位相誤差に基づいて、パルス対ごとに前記電圧バイアスを更新するように構成された電圧バイアスコントローラと

を備える、請求項1に記載の遅延システム。

**【請求項 7】**

前記更新回路は、前記基準クロックのN個の周期あたり1つのパルス対というレートで前記パルス対を生成するように構成され、Nは整数であり、前記更新コントローラは、Nを調整するように構成される、請求項6に記載の遅延システム。

**【請求項 8】**

前記更新コントローラは、前記第2の遅延回路によって遅延されている信号のデータレートが第1のデータレートに略等しい場合、Nを第1の値に設定し、前記信号の前記データレートが第2のデータレートに略等しい場合、Nを第2の値に設定するように構成され

10

20

30

40

50

、前記第1のデータレートは、前記第2のデータレートよりも低く、Nの前記第1の値は、Nの前記第2の値よりも大きい、請求項7に記載の遅延システム。

【請求項9】

前記電圧バイアスによって制御される前記第2の遅延回路の前記遅延は、前記第2の遅延回路のステップ遅延であり、前記第2の遅延回路は、信号を前記ステップ遅延の倍数ぶん遅延させるように構成される、請求項1に記載の遅延システム。

【請求項10】

遅延制御のための方法であつて、

遅延回路に電圧バイアスを供給することと、ここにおいて、前記電圧バイアスは、前記遅延回路の遅延を制御する、

10

更新レートで前記電圧バイアスを更新することと、

前記更新レートを調整することと

を備える方法。

【請求項11】

前記更新レートを調整することは、前記遅延回路によって遅延されている信号のデータレートに基づいて前記更新レートを調整することを備える、請求項10に記載の方法。

【請求項12】

前記更新レートを調整することは、

前記信号の前記データレートが第1のデータレートに略等しい場合、前記更新レートを第1の更新レートに設定することと、

前記信号の前記データレートが第2のデータレートに略等しい場合、前記更新レートを第2の更新レートに設定することと

20

を備え、

前記第1のデータレートは、前記第2のデータレートよりも低く、前記第1の更新レートは、前記第2の更新レートよりも低い、

請求項11に記載の方法。

【請求項13】

前記電圧バイアスを更新することは、基準クロックに基づいて前記電圧バイアスを更新することを備え、ここで、前記更新レートは、前記基準クロックのN個のあたり1回の前記電圧バイアスの更新に略等しく、Nは整数であり、前記更新レートを調整することは、Nを調整することを備える、請求項10に記載の方法。

【請求項14】

前記更新レートを調整することは、

前記遅延回路によって遅延されている信号のデータレートが第1のデータレートに略等しい場合、Nを第1の値に設定することと

前記信号の前記データレートが第2のデータレートに略等しい場合、Nを第2の値に設定することと

40

を備え、

前記第1のデータレートは、前記第2のデータレートよりも低く、Nの前記第1の値は、Nの前記第2の値よりも大きい、

請求項13に記載の方法。

【請求項15】

前記電圧バイアスを更新することは、

前記電圧バイアスの更新ごとに、基準クロックからパルス対を生成することと、ここにおいて、各パルス対は、第1のパルス及び第2のパルスを備え、前記第1のパルスは、前記第2のパルスに対して前記基準クロックの略1周期ぶん遅延されている、

各パルス対の前記第2のパルスを前記電圧バイアスによって制御された量ぶん遅延させることと、

パルス対ごとに、それぞれの前記第1のパルスとそれぞれの遅延された前記第2のパルスとの間の位相誤差を検出することと、

50

それぞれの検出された前記位相誤差に基づいて、パルス対ごとに前記電圧バイアスを更新することと

を備える、請求項 10 に記載の方法。

【請求項 16】

前記遅延回路に第 2 の電圧バイアスを供給することと、ここにおいて、前記第 2 の電圧バイアスはまた、前記遅延回路の前記遅延を制御する、

前記更新レートで前記第 2 の電圧バイアスを更新することと

を更に備える、請求項 10 に記載の方法。

【請求項 17】

遅延制御のための装置であって、

遅延回路に電圧バイアスを供給するための手段と、ここにおいて、前記電圧バイアスは前記遅延回路の遅延を制御する、

更新レートで前記電圧バイアスを更新するための手段と、

前記更新レートを調整するための手段と

を備える装置。

10

【請求項 18】

前記更新レートを調整するための前記手段は、前記遅延回路によって遅延されている信号のデータレートに基づいて前記更新レートを調整するための手段を備える、請求項 17 に記載の装置。

【請求項 19】

前記更新レートを調整するための前記手段は、

前記信号の前記データレートが第 1 のデータレートに略等しい場合、前記更新レートを第 1 の更新レートに設定するための手段と、

前記信号の前記データレートが第 2 のデータレートに略等しい場合、前記更新レートを第 2 の更新レートに設定するための手段と

を備え、

前記第 1 のデータレートは、前記第 2 のデータレートよりも低く、前記第 1 の更新レートは、前記第 2 の更新レートよりも低い、

請求項 18 に記載の装置。

20

【請求項 20】

前記電圧バイアスを更新するための前記手段は、基準クロックに基づいて前記電圧バイアスを更新するための手段を備え、ここで、前記更新レートは、前記基準クロックの N 個の周期あたり 1 回の前記電圧バイアスの更新に略等しく、N は整数であり、前記更新レートを調整するための前記手段は、N を調整するための手段を備える、請求項 17 に記載の装置。

30

【請求項 21】

前記更新レートを調整するための前記手段は、

前記遅延回路によって遅延されている信号のデータレートが第 1 のデータレートに略等しい場合、N を第 1 の値に設定するための手段と、

前記信号の前記データレートが第 2 のデータレートに略等しい場合、N を第 2 の値に設定するための手段と

を備え、

前記第 1 のデータレートは、前記第 2 のデータレートよりも低く、N の前記第 1 の値は N の前記第 2 の値よりも大きい、

請求項 20 に記載の装置。

40

【請求項 22】

前記電圧バイアスを更新するための前記手段は、

前記電圧バイアスの更新ごとに、基準クロックからパルス対を生成するための手段と、ここにおいて、各パルス対は、第 1 のパルス及び第 2 のパルスを備え、前記第 1 のパルスは、前記第 2 のパルスに対して前記基準クロックの略 1 周期ぶん遅延されている、

50

各パルス対の前記第2のパルスを前記電圧バイアスによって制御された量ぶん遅延させるための手段と、

パルス対ごとに、それぞれの前記第1のパルスとそれぞれの遅延された前記第2のパルスとの間の位相誤差を検出するための手段と、

それぞれの検出された前記位相誤差に基づいて、パルス対ごとに前記電圧バイアスを更新するための手段と

を備える、請求項17に記載の装置。

【請求項23】

前記遅延回路に第2の電圧バイアスを供給するための手段と、ここにおいて、前記第2の電圧バイアスはまた、前記遅延回路の前記遅延を制御する、

10

前記更新レートで前記第2の電圧バイアスを更新するための手段と

を更に備える、請求項17に記載の装置。

【請求項24】

メモリインターフェースであって、

信号を遅延するように構成された第1の遅延回路と、ここにおいて、前記信号は、データ信号及びデータストローブ信号のうちの1つを備える、

前記第1の遅延回路に電圧バイアスを供給し、更新レートで前記電圧バイアスを更新するように構成された第2の遅延回路と、ここにおいて、前記電圧バイアスは、前記第1の遅延回路の遅延を制御する、

20

前記第2の遅延回路の前記更新レートを調整するように構成された更新コントローラとを備えるメモリインターフェース。

【請求項25】

前記更新コントローラは、前記信号のデータレートに基づいて前記更新レートを調整するように構成される、

請求項24に記載のメモリインターフェース。

【請求項26】

前記更新コントローラは、前記信号の前記データレートが第1のデータレートに略等しい場合、前記更新レートを第1の更新レートに設定し、前記信号の前記データレートが第2のデータレートに略等しい場合、前記更新レートを第2の更新レートに設定するように構成され、前記第1のデータレートは、前記第2のデータレートよりも低く、前記第1の更新レートは、前記第2の更新レートよりも低い、請求項25に記載のメモリインターフェース。

30

【請求項27】

前記第2の遅延回路は、基準クロックに基づいて前記電圧バイアスを更新するように構成され、ここで、前記更新レートは、前記基準クロックのN個の周期あたり1回の前記電圧バイアスの更新に略等しく、Nは整数であり、前記更新コントローラは、Nを調整するように構成される、請求項24に記載のメモリインターフェース。

【請求項28】

前記更新コントローラは、前記信号のデータレートが第1のデータレートに略等しい場合、Nを第1の値に設定し、前記信号の前記データレートが第2のデータレートに略等しい場合、Nを第2の値に設定するように構成され、前記第1のデータレートは、前記第2のデータレートよりも低く、Nの前記第1の値は、Nの前記第2の値よりも大きい、請求項27に記載のメモリインターフェース。

40

【請求項29】

前記第2の遅延回路は、

前記電圧バイアスの更新ごとに、基準クロックからパルス対を生成するように構成された更新回路と、ここにおいて、各パルス対は、第1のパルス及び第2のパルスを備え、前記第1のパルスは、前記第2のパルスに対して前記基準クロックの略1周期ぶん遅延されている、

各パルス対の前記第2のパルスを前記電圧バイアスによって制御された量ぶん遅延させ

50

るよう構成された電圧制御型遅延回路と、

パルス対ごとに、それぞれの前記第1のパルスとそれぞれの遅延された前記第2のパルスとの間の位相誤差を検出するよう構成された位相周波数検出器と、

それぞれの検出された前記位相誤差に基づいて、パルス対ごとに前記電圧バイアスを更新するよう構成された電圧バイアスコントローラと

を備える、請求項24に記載のメモリインターフェース。

#### 【請求項30】

前記電圧バイアスによって制御される前記第1の遅延回路の前記遅延は、前記第1の遅延回路のステップ遅延であり、前記第1の遅延回路は、前記信号を前記ステップ遅延の倍数ぶん遅延せしるよう構成される、請求項24に記載のメモリインターフェース。

10

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

[0001]本開示の態様は一般にメモリに関し、より具体的には、メモリインターフェースのためのプログラマブル電力に関する。

##### 【背景技術】

##### 【0002】

[0002]チップは、チップ上の回路（例えば、メモリコントローラ）を、ダブルデータレートダイナミックランダムアクセスメモリ（DDR DRAM）、等の外部メモリデバイスとインターフェースするためのメモリインターフェースを含み得る。メモリインターフェースは、メモリインターフェースにおいて信号（例えば、データ信号）のタイミングを調整するための遅延回路を含み得る。例えば、メモリインターフェースは、（例えば、メモリインターフェースと外部のメモリデバイスとの間のデータ線の長さの不一致による）データ信号間のスキューを補償するために遅延回路を含み得る。別の例では、メモリインターフェースは、データサンプリングに使用されるデータストローブ信号を、データ信号の偏移間の中心に置くために遅延回路を含み得る。

20

##### 【発明の概要】

##### 【0003】

[0003]以下には、1つ又は複数の実施形態の基本的な理解を提供するために、そのような実施形態の簡略化された概要が提示される。この概要は予期される全ての実施形態の広範囲に及ぶ概観ではなく、全ての実施形態のキー又は不可欠な要素を識別することも、任意の又は全ての実施形態の範囲を描写することも意図しない。その唯一の目的は、後に提示されるより詳細な説明の前置きとして、1つ又は複数の実施形態の幾つかの概念を簡略化された形式で提示することである。

30

##### 【0004】

[0004]ある態様によれば、遅延システムが本明細書で説明される。遅延システムは、第2の遅延回路に電圧バイアスを供給することと、ここにおいて、電圧バイアスは、第2の遅延回路の遅延を制御する、更新レートで電圧バイアスを更新することとを行うように構成された第1の遅延回路を備え得る。遅延システムはまた、第1の遅延回路の更新レートを調整するように構成された更新コントローラを備える。

40

##### 【0005】

[0005]第2の態様は、遅延制御のための方法に関する。方法は、遅延回路に電圧バイアスを供給することを備え、ここにおいて、電圧バイアスは、遅延回路の遅延を制御する。方法はまた、更新レートで電圧バイアスを更新することと、更新レートを調整することを備える。

##### 【0006】

[0006]第3の態様は、遅延制御のための装置に関する。装置は、遅延回路に電圧バイアスを供給するための手段を備え、ここにおいて、電圧バイアスは、遅延回路の遅延を制御する。装置はまた、更新レートで電圧バイアスを更新するための手段と、更新レートを調整するための手段とを備える。

50

## 【0007】

[0007]第4の態様は、メモリインターフェースに関する。メモリインターフェースは、信号を遅延せるように構成された第1の遅延回路を備え、ここにおいて、信号は、データ信号及びデータストローブ信号のうちの1つを備える。メモリインターフェースはまた、第1の遅延回路に電圧バイアスを供給することと、ここにおいて、電圧バイアスは、第1の遅延回路の遅延を制御する、更新レートで電圧バイアスを更新することを行いうように構成された第2の遅延回路を備える。メモリインターフェースは更に、第2の遅延回路の更新レートを調整するように構成された更新コントローラを備える。

## 【0008】

[0008]前述した目的及び関連する目的を達成するために、1つ又は複数の実施形態は、下文で十分に説明され、特許請求の範囲において具体的に示される特徴を備える。以下の説明及び添付図面は、1つ又は複数の実施形態の特定の実例となる態様を詳細に示す。しかしながら、これらの態様は、様々な実施形態の原理が用いられ得る様々な方法のほんの一部しか示さず、説明される実施形態は、そのような態様及びそれらの等化物の全てを含むことが意図される。

10

## 【図面の簡単な説明】

## 【0009】

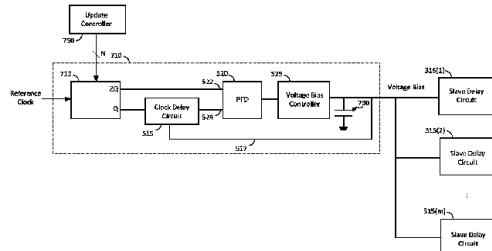

【図1】[0009]図1は、外部メモリデバイスとインターフェースするためのメモリインターフェースの例を示す。

20

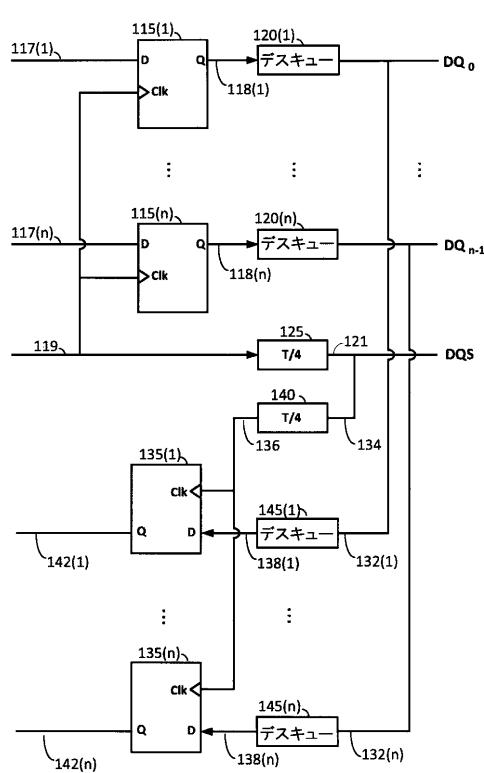

【図2】[0010]図2は、データ信号とデータストローブとの間のタイミングの例を例示するタイミング図である。

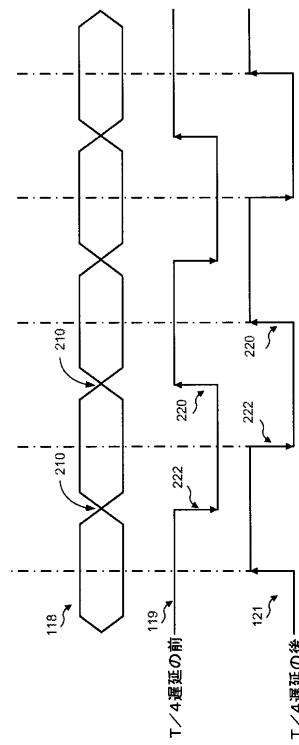

【図3】[0011]図3は、本開示の実施形態に係る、マスタ-スレーブアーキテクチャの例を示す。

20

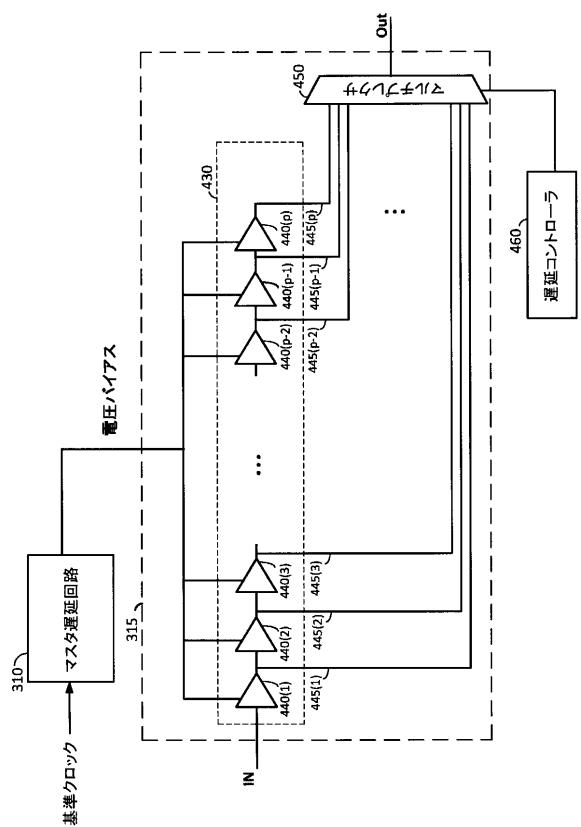

【図4】[0012]図4は、本開示の実施形態に係る、スレーブ遅延回路の例を示す。

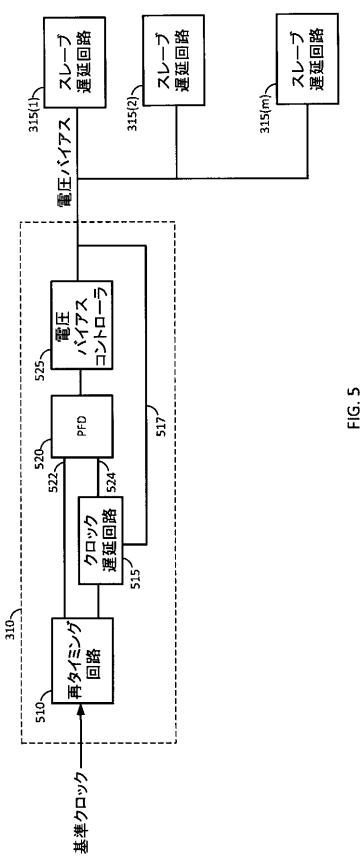

【図5】[0013]図5は、本開示の実施形態に係る、マスタ遅延回路の例を示す。

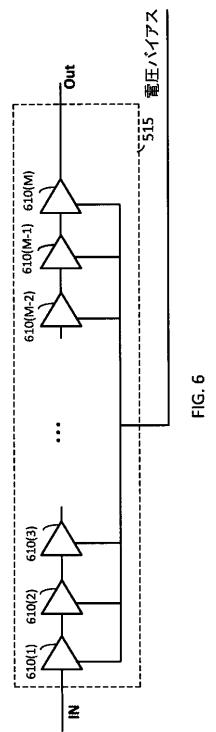

【図6】[0014]図6は、本開示の実施形態に係る、クロック遅延回路の例を示す。

30

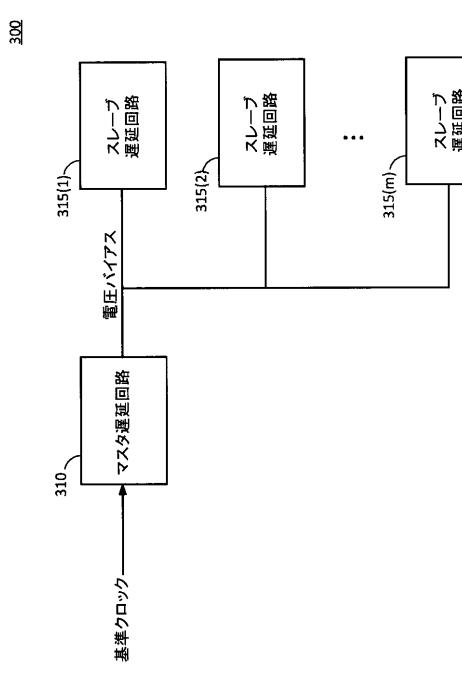

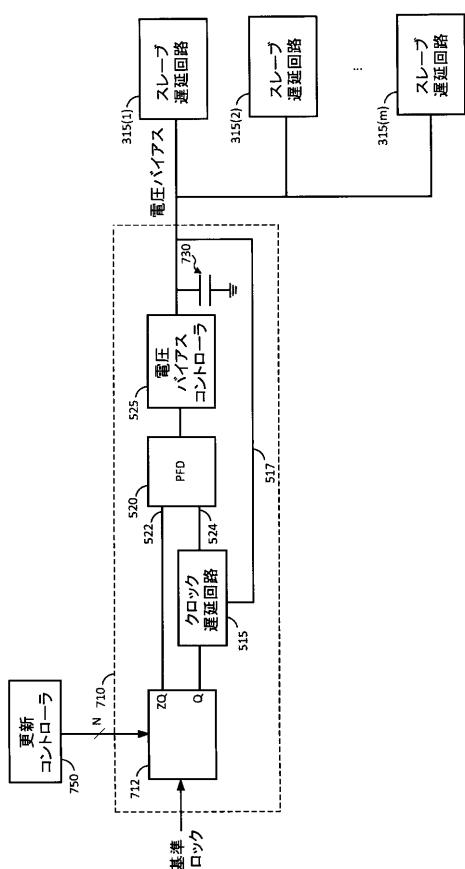

【図7】[0015]図7は、本開示の実施形態に係る、プログラマブル電力を有するマスタ遅延回路を示す。

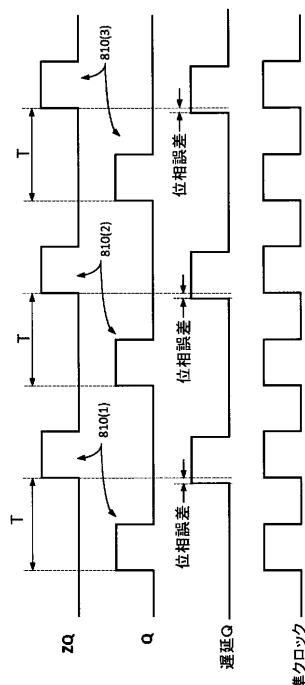

【図8】[0016]図8は、本開示の実施形態に係る、電圧バイアスが2つのクロック周期ごとに更新される例を例示するタイミング図である。

30

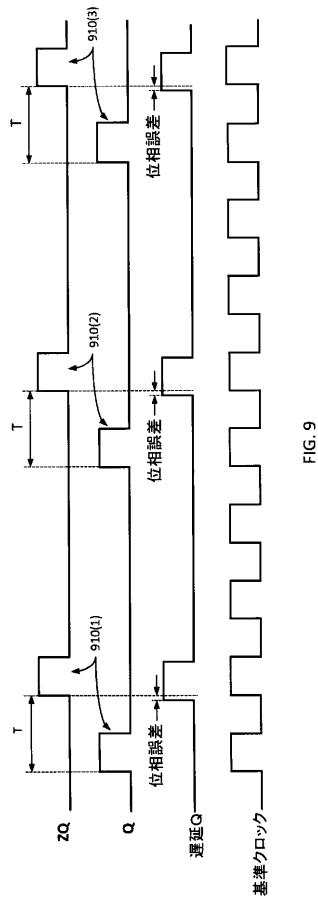

【図9】[0017]図9は、本開示の実施形態に係る、電圧バイアスが4つのクロック周期ごとに更新される例を例示するタイミング図である。

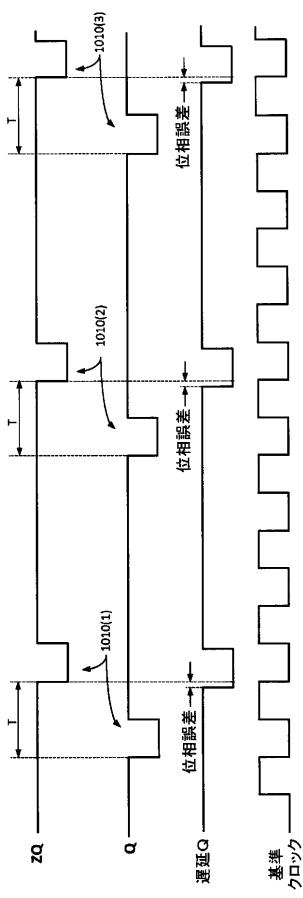

【図10】[0018]図10は、本開示の実施形態に係る、電圧バイアスが4つのクロック周期ごとに更新される別の例を例示するタイミング図である。

40

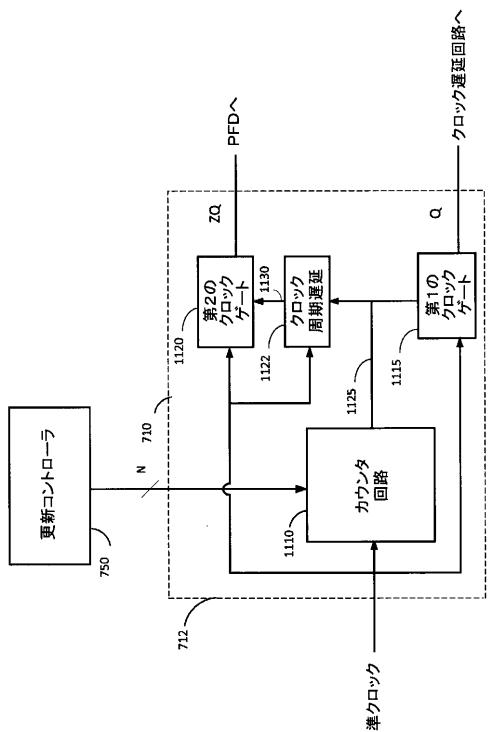

【図11】[0019]図11は、本開示の実施形態に係る、更新回路の例示的な実装形態を示す。

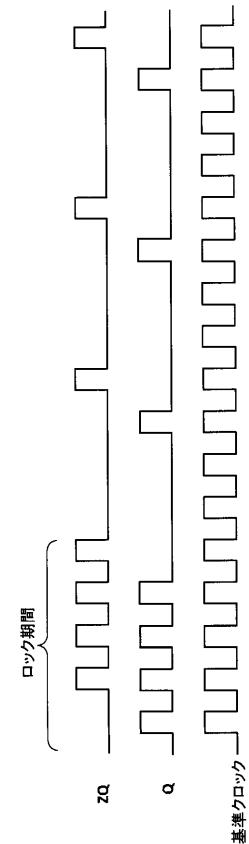

【図12】[0020]図12は、本開示の実施形態に係る、ループロッキングの例を例示するタイミング図である。

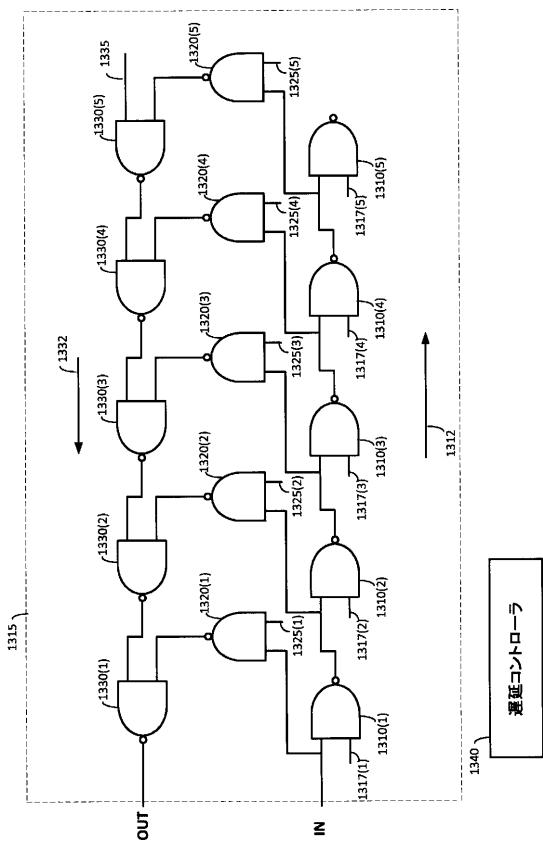

【図13】[0021]図13は、本開示の別の実施形態に係る、スレーブ遅延回路の例示的な実装形態を示す。

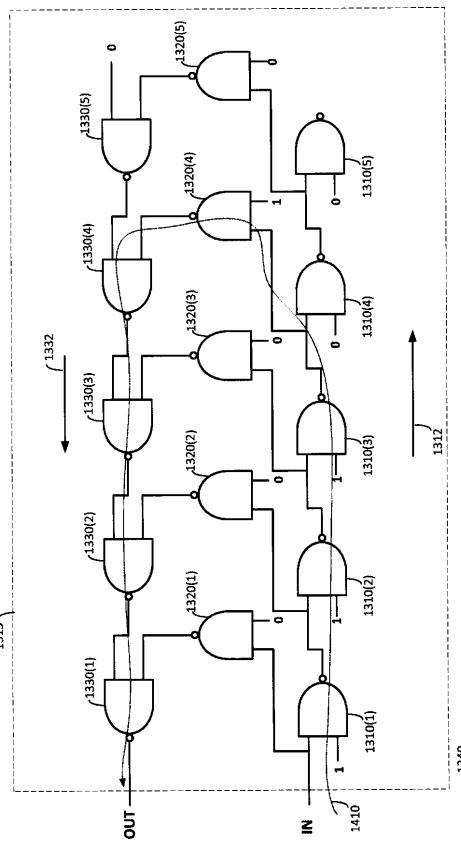

【図14A】[0022]図14Aは、図13のスレーブ遅延回路を通る異なる遅延経路の例を示す。

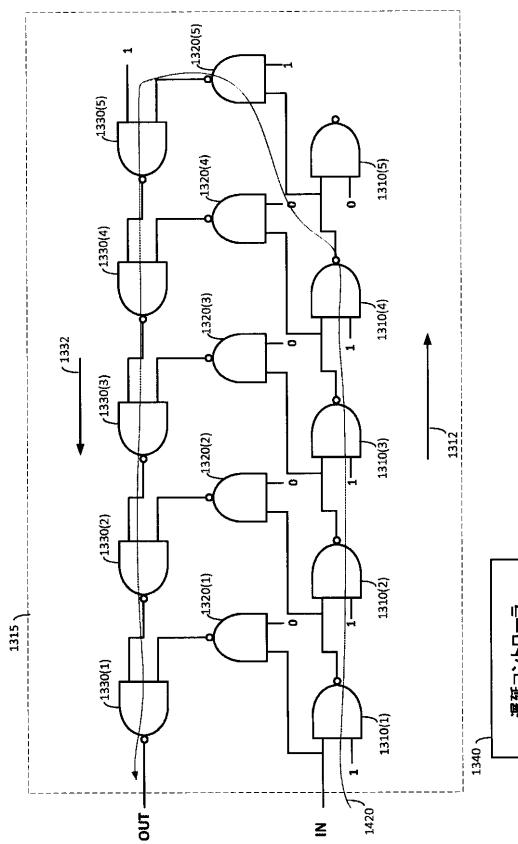

【図14B】図14Bは、図13のスレーブ遅延回路を通る異なる遅延経路の例を示す。

【図15】[0023]図15は、本開示の実施形態に係る、電圧制御型遅延を有するNANDゲートの例示的な実装形態を示す。

【図16】[0024]図16は、本開示の別の実施形態に係る、マスタ遅延回路の例示的な実装形態を示す。

【図17】[0025]図17は、本開示の別の実施形態に係る、クロック遅延回路の例示的な実装形態を示す。

【図18】[0026]図18は、本開示の実施形態に係る、クロック遅延回路の第1の遅延段

50

及び第2の遅延段の出力を例示するタイミング図である。

【図19】[0027]図19は、本開示の実施形態に係る、カウント回路の例示的な実装形態を示す。

【図20】[0028]図20は、本開示の実施形態に係る、リセット論理回路の例示的な実装形態を示す。

【図21】[0029]図21は、本開示の別の実施形態に係る、更新回路の例示的な実装形態を示す。

【図22】[0030]図22は、本開示の実施形態に係る、遅延制御のための方法を例示するフロー図である。

#### 【発明の詳細な説明】

##### 【0010】

[0031]添付の図面に関連して以下に示される詳細な説明は、様々な構成の説明を意図しており、本明細書で説明される概念が実施され得る唯一の構成を表すことを意図するものではない。詳細な説明は、様々な概念の完全な理解を提供するために特定の詳細を含む。しかしながら、これらの概念がこれらの特定の詳細なしに実施され得ることは当業者には明らかであろう。幾つかの事例では、そのような概念を曖昧にしないために、周知の構造及び構成要素がブロック図の形式で示される。

##### 【0011】

[0032]チップは、チップ上の回路（例えば、メモリコントローラ）と、DDR DRA M等の外部メモリデバイスとインターフェースするためのメモリインターフェースを含み得る。図1は、チップを外部メモリデバイス（図示されない）とインターフェースするための例示的なメモリインターフェース100を示す。メモリインターフェース100は、第1の複数のフリップフロップ115(1) - 115(n)、第1の複数のデスキュ回路120(1) - 120(n)、第2の複数のフリップフロップ135(1) - 135(n)、第2の複数のデスキュ回路145(1) - 145(n)、第1の遅延回路125及び第2の遅延回路140を含む。

##### 【0012】

[0033]書き込み動作中、第1の複数のフリップフロップ115(1) - 115(n)は、複数のデータ信号117(1) - 117(n)を同時に(in parallel)受ける。各フリップフロップ115(1) - 115(n)はまた、受信データ信号(incoming data signals)117(1) - 117(n)の半分の周波数を有する周期的な信号であり得るデータストローブ信号119を受ける。各フリップフロップ115(1) - 115(n)は、データストローブ信号119の立ち上がりエッジ及び立ち下がりエッジ上でそれぞれのデータ信号117(1) - 117(n)からデータビットを取り込み、取込まれたデータビットをそれぞれのデスキュ回路120(1) - 120(n)に出力し、これは、以下により詳細に説明される。

##### 【0013】

[0034]データストローブ信号119はまた、第1の遅延回路125に入力される。第1の遅延回路125の前に、データストローブ信号119のエッジは、フリップフロップ115(1) - 115(n)の出力データ信号118(1) - 118(n)の遷移と大まかに揃えられる。これは、各フリップフロップ115(1) - 115(n)が、データストローブ信号119の立ち上がりエッジ及び立ち下がりエッジ上で、それぞれの出力データ信号118(1) - 118(n)のデータビットを捕獲するためである。第1の遅延回路125は、遅延データストローブ信号121のエッジが、出力データ信号118(1) - 118(n)の遷移間の略中心に置かれるように、1周期の4分の1だけデータストローブ信号119を遅延させる。

##### 【0014】

[0035]図2は、出力データ信号118のうちの1つとデータストローブ信号119との間のタイミング関係性の簡略化された例を示す。この例では、データストローブ信号119の立ち上がりエッジ220及び立ち下がりエッジ222が、出力データ信号118の遷

移 2 1 0 と大まかに揃えられる。1 周期の 4 分の 1 ( T / 4 ) だけ遅延された後、データストローブ信号 1 2 1 の立ち上がりエッジ 2 2 0 及び立ち下がりエッジ 2 2 2 は、図 2 に示されるように、出力データ信号 1 1 8 の遷移 2 1 0 間の略中心に置かれる。メモリデバイスは、データストローブ信号 1 2 1 のエッジにおいてデータ信号をサンプリングする。データストローブ信号 1 2 1 のエッジをデータ信号の遷移間の中心に置くことは、メモリデバイスが、データ信号の有効データウィンドウ内でデータ信号をサンプリングすることを確実にすることを助ける。

#### 【 0 0 1 5 】

[0036] 各デスキューリング回路 1 2 0 ( 1 ) - 1 2 0 ( n ) は、メモリインターフェース 1 0 0 からメモリデバイス（例えば、DDR DRAM）に移動する際のデータ信号間のスキューを補償するために、少量の遅延をそれぞれのデータ信号 1 1 8 ( 1 ) - 1 1 8 ( n ) に追加する。スキューは、データ信号をメモリデバイスに転送するために使用される線の長さの不一致及び / 又は別の理由によるものであり得る。それぞれのデスキューリング回路 1 2 0 ( 1 ) - 1 2 0 ( n ) によって遅延された後、各出力データ信号は、それぞれの双方向データ線 D Q 0 - D Q n - 1 上でメモリデバイスに出力される。データストローブ信号 1 2 1 は、双方向ストローブ線 D Q S 上でメモリデバイスに出力される。メモリデバイスは、メモリインターフェース 1 0 0 から受けたデータ信号をサンプリングするために、データストローブ信号 1 2 1 を使用する。

#### 【 0 0 1 6 】

[0037] 読取り動作中、メモリインターフェース 1 0 0 は、双方向データ線 D Q 0 - D Q n - 1 を介してメモリデバイスから複数のデータ信号 1 3 2 ( 1 ) - 1 3 2 ( n ) を、双方向ストローブ線 D Q S を介してメモリデバイスからデータストローブ信号 1 3 4 を受ける。第 2 の複数のデスキューリング回路 1 4 5 ( 1 ) - 1 4 5 ( n ) の各々は、データ信号 1 3 2 ( 1 ) - 1 3 2 ( n ) のうちの 1 つを受け、データ信号間のスキューを補償するために少量の遅延をそれぞれのデータ信号に追加する。

#### 【 0 0 1 7 】

[0038] メモリデバイスからのデータストローブ信号 1 3 4 は、このデータストローブ信号 1 3 4 を 1 周期の 4 分の 1 ぶん遅延させる第 2 の遅延回路 1 4 0 に入力される。これは、メモリデバイスが、データストローブ信号 1 3 4 のエッジがデータ信号 1 3 2 ( 1 ) - 1 3 2 ( n ) の遷移と揃えられた状態でデータストローブ信号 1 3 4 を出力するからである。データストローブ信号 1 3 4 を 1 周期の 4 分の 1 だけ遅延させることで、第 2 の遅延回路 1 4 0 は、遅延データストローブ信号 1 3 6 のエッジを、データ信号 1 3 2 ( 1 ) - 1 3 2 ( n ) の遷移間の略中心に置く。

#### 【 0 0 1 8 】

[0039] 次に、遅延データストローブ 1 3 6 は、第 2 の複数のフリップフロップ 1 3 5 ( 1 ) - 1 3 5 ( n ) の各々のクロック入力に入力される。例えば、遅延データストローブ信号 1 3 6 は、クロックツリーを使用して、フリップフロップ 1 3 5 ( 1 ) - 1 3 5 ( n ) のクロック入力に分散され得る。各フリップフロップ 1 3 5 ( 1 ) - 1 3 5 ( n ) は、遅延データストローブ信号 1 3 6 の立ち上がりエッジ及び立ち下がりエッジ上でそれぞれのデスキューリング回路 1 4 5 ( 1 ) - 1 4 5 ( n ) の出力 1 3 8 ( 1 ) - 1 3 8 ( n ) からデータビットを取込む。結果として得られる出力データ信号 1 4 2 ( 1 ) - 1 4 2 ( n ) は、更なる処理のために、メモリインターフェース 1 0 0 内の追加の回路（図示されない）に送られ得る。

#### 【 0 0 1 9 】

[0040] メモリインターフェース 1 0 0 は、複数のデータレートをサポートし得、データがメモリデバイスに送られ、そこから受けられるレートは、動的に調整される。例えば、データレートは、高データレートを必要とするアプリケーションの場合、増やされ得、高データレートを必要としないアプリケーションの場合、減らされ得る。データレートが変化すると、遅延回路 1 2 5 及び 1 4 0 の遅延は、相応に調整される必要がある。例えば、データレートが倍にされると、データストローブ信号 1 1 9 の周期は半分に低減される。

10

20

30

40

50

この例では、データストローブ信号 119 に対して 1 周期の 4 分の 1 の遅延を維持するために、第 1 の遅延回路 125 の遅延が半分に低減される。別の例では、データレートが半分に低減されると、データストローブ信号 119 の周期は、倍にされる。この例では、データストローブ信号 119 に対して 1 周期の 4 分の 1 の遅延を維持するために、第 1 の遅延回路 125 の遅延が倍にされる。

【0020】

[0041] 図 3 は、メモリインターフェース（例えば、メモリインターフェース 100）内の、制御遅延を提供するためのマスタ・スレーブアーキテクチャ 300 の例を示す。マスタ・スレーブアーキテクチャ 300 は、1 つのマスタ遅延回路 310 と、複数のスレーブ遅延回路 315 (1) - 315 (m) とを備える。各スレーブ遅延回路 315 (1) - 315 (m) は、ステップ遅延 (step delay) の倍数である遅延を提供し、ここでは、ステップ遅延は、マスタ遅延回路 310 からの電圧バイアスによって制御される。マスタ遅延回路 310 は、以下で更に説明されるように、スレーブ遅延回路 315 (1) - 315 (m) に対して所望のステップ遅延を維持するために、（例えば、水晶発振器からの）基準クロックに基づいて電圧バイアスを調整する。スレーブ遅延回路 315 (1) - 315 (m) は、図 1 に示される遅延回路 125 及び 140 並びにデスキュー回路 120 (1) - 120 (n) 及び 145 (1) - 145 (n) を実装するために使用され得る。

10

【0021】

[0042] 図 4 は、スレーブ遅延回路 315 のうちの 1 つの例示的な実装形態を示す。スレーブ遅延回路 315 は、複数の遅延素子 440 (1) - 440 (p)（例えば、バッファ）及びマルチプレクサ 450 を備える。遅延素子 440 (1) - 440 (p) の各々は、マスタ遅延回路 310 からの電圧バイアスでバイアスが掛けられる。電圧バイアスは、各遅延素子 440 (1) - 440 (p) の遅延を制御する。

20

【0022】

[0043] 遅延素子 440 (1) - 440 (p) は、遅延チェーン 430 を形成するために直列に結合され、ここでは、各遅延素子 440 (1) - 440 (p) の出力 445 (1) - 445 (p) は、スレーブ遅延回路 315 の入力（「IN」と表される）において受ける信号に異なる量の遅延を提供する。より具体的には、各遅延素子 440 (1) - 440 (p) の出力 445 (1) - 445 (p) は、ステップ遅延の異なる倍数である遅延を提供し、ここで、ステップ遅延は、1 つの遅延素子の遅延である。例えば、出力 445 (1) は、1 つのステップ遅延に等しい遅延を提供し、出力 445 (2) は、2 つのステップ遅延に等しい遅延を提供し、出力 445 (3) は、3 つのステップ遅延に等しい遅延を提供する。

30

【0023】

[0044] 遅延素子 440 (1) - 440 (p) の出力 445 (1) - 445 (p) は、遅延コントローラ 460 の制御下で出力 445 (1) - 445 (p) のうちの 1 つを選択するマルチプレクサ 450 に結合される。マルチプレクサ 450 は、選択された出力を、スレーブ遅延回路 315 の（「OUT」と表される）出力に結合する。遅延コントローラ 460 は、所望の遅延に対応する、遅延素子 440 (1) - 440 (p) の出力 445 (1) - 445 (p) を選択するようマルチプレクサ 450 に命令することで、遅延回路 315 の遅延を制御する。

40

【0024】

[0045] 故に、遅延コントローラ 460 は、入力信号が通過する遅延素子 440 (1) - 440 (p) の数を制御することで、スレーブ遅延回路 315 の遅延を調整する。これは、遅延コントローラ 460 が、ステップ遅延の倍数で遅延を制御することを可能にし、ここで、ステップ遅延は、1 つの遅延素子の遅延である。ステップ遅延は、上述したように、マスタ遅延回路 310 からの電圧バイアスによって制御される。図 4 のスレーブ遅延回路 315 は、図 1 に示される遅延回路 125 及び 140 並びにデスキュー回路 120 (1) - 120 (n) 及び 145 (1) - 145 (n) のうちのいずれか 1 つを実装するために使用され得る。スレーブ遅延回路の他の実装形態の例が以下に説明される。

50

## 【0025】

[0046]図5は、マスタ遅延回路310の例示的な実装形態を示す。この例では、マスタ遅延回路310は、再タイミング回路510、クロック遅延回路515、位相周波数検出器(PFD)520及び電圧バイアスコントローラ525を備える遅延ロックループ(DLL)である。以下で更に説明されるように、所望のステップ遅延を達成するために、マスタ遅延回路310の電圧バイアス出力は、フィードバックループ517によってクロック遅延回路515にフィードバックされる。

## 【0026】

[0047]動作中、再タイミング回路510は、基準クロックを受け、この基準クロックを1クロック周期ぶん遅延させ、遅延基準クロックをPFD520の第1の入力522に出力する。再タイミング回路510はまた、基準クロックをクロック遅延回路515に出力する。クロック遅延回路515は、基準クロックを、フィードバックループ517によってマスタ遅延回路310の出力からクロック遅延回路515にフィードバックされる電圧バイアスによって制御された量ぶん遅延させる。クロック遅延回路515は、結果として得られた遅延基準クロックを、PFD520の第2の入力524に出力する。

10

## 【0027】

[0048]PFD520は、第1の入力522と第2の入力524との間の位相誤差を検出し、検出された位相誤差に基づいて、位相誤差信号を電圧バイアスコントローラ525に出力する。電圧バイアス回路525は、位相誤差を低減する方向に電圧バイアスを調整する。電圧バイアス回路525は、チャージポンプ及びループフィルタが実装され得る。

20

## 【0028】

[0049]位相誤差は、クロック遅延回路515の遅延が基準クロックの1周期に略等しいとき、ゼロに近づく。故に、電圧バイアスコントローラ525は、クロック遅延回路515の遅延が1クロック周期に略等しくなるように、電圧バイアスを調整する。一態様では、クロック遅延回路515は、スレーブ遅延回路315(1) - 315(m)のステップ遅延の倍数Mに略等しい遅延を有する。故に、この態様では、マスタ遅延回路310は、略T/Mのステップ遅延を維持するために、電圧バイアスを調整し、ここで、Tは、1クロック周期(サイクル)である。

## 【0029】

[0050]一態様では、基準クロックは、水晶発振器(XO)によって供給される。水晶発振器は、温度、電圧及び/又はプロセスに対して略不变な基準クロックを生成することができる。マスタ遅延回路310が、電圧バイアスを調整するための基準として基準クロックを使用するため、マスタ遅延回路310は、温度、電圧、及び/又はプロセスに対して略不变なステップ遅延を維持するために、電圧バイアスを調整することができる。

30

## 【0030】

[0051]図6は、クロック遅延回路515の例示的な実装形態を示す。この例では、クロック遅延回路515は、直列に結合されたM個の遅延素子610(1) - 610(M)を備え、ここでは、各遅延素子610(1) - 610(M)は、電圧バイアスコントローラ525からの電圧バイアスによってバイアスが掛けられる。クロック遅延回路515内の遅延素子610(1) - 610(M)は、スレーブ遅延回路315(1) - 315(m)内の遅延素子440(1) - 440(p)の複製であり得る。

40

## 【0031】

[0052]マスタ遅延回路310は、基準クロックの各周期中に電圧バイアスを更新し得る。具体的には、PFD520は、各クロック周期(サイクル)中、第1の入力522と第2の入力524との間の位相誤差を検出し得、電圧バイアスを更新するために、検出された位相誤差を電圧バイアスコントローラ525に出力する。しかしながら、各クロック周期(サイクル)中、電圧バイアスを更新することは、比較的大量の電力を消費し得、これは、メモリインターフェースがモバイルデバイスに実装されるときバッテリ寿命を低減する。

## 【0032】

50

[0053]本開示の実施形態は、マスタ遅延回路にプログラマブル電力を供給し、ここでは、マスタ遅延回路の電力消費は、マスタ遅延回路がスレーブ遅延回路への電圧バイアスを更新するレートを調整することで調整される。例えば、マスタ遅延回路は、以下で更に説明されるように、性能要件がより低い（例えば、より低いデータレートの）とき、電力消費を低減するために、より少ない頻度で電圧バイアスを更新し得る。

#### 【0033】

[0054]図7は、本開示の実施形態に係る、プログラマブル電力を有するマスタ遅延回路710を示す。マスタ遅延回路710は、クロック遅延回路515、位相周波数検出器（PFD）520及び電圧バイアスコントローラ525を備える遅延ロックドループ（DL）である。マスタ遅延回路710は、更新回路712及び出力キャパシタ730を更に備える。

10

#### 【0034】

[0055]更新回路712は、更新コントローラ750からの制御信号Nに基づいてマスタ遅延回路710が電圧バイアスを更新するレートを制御するように構成され、ここで、Nは、プログラマブルであり、整数であり得る。より具体的には、更新回路712は、マスタ遅延回路710に、基準クロックのN個の周期（サイクル）ごとに電圧バイアスを更新させる（即ち、N個の周期あたり1回の電圧バイアス更新というレート）。例えば、Nが2に等しいとき、マスタ遅延回路710は、2つのクロック周期（サイクル）ごとに電圧バイアスを更新する。

20

#### 【0035】

[0056]更新回路712は、電圧バイアスが更新されるレートを調整することによってマスタ遅延回路710の電力消費を調整するために使用され得る。例えば、更新コントローラ750は、Nを増加させること（即ち、電圧バイアスが更新されるレートを低減すること）によって、マスタ遅延回路710の電力消費を低減し得る。

#### 【0036】

[0057]動作中、更新回路712は、基準クロックのN個の周期（サイクル）ごとに一対のパルスを出力する。パルスの各対は、Qパルス及びZQパルスを備え、ここでは、ZQパルスは、Qパルスに対して略1クロック周期ぶん遅延されている。パルスの対ごとに、更新回路712は、PFD520の第1の入力522にZQパルスを出力し、クロック遅延回路515にQパルスを出力する。クロック遅延回路515は、Qパルスを、フィードバックループ517によって電圧バイアスコントローラ525の出力からクロック遅延回路515にフィードバックされる電圧バイアスによって制御された量ぶん遅延させる。クロック遅延回路515は、結果として得られた遅延Qパルスを、PFD520の第2の入力524に出力する。PFD520は、ZQパルスと遅延Qパルスとの間の位相誤差を検出する。例えば、PFD520は、ZQパルスの立ち上がりエッジと遅延Qパルスの立ち上がりエッジとの間の位相差分又はZQパルスの立ち下がりエッジと遅延Qパルスの立ち下がりエッジとの間の位相差分を検出することで、位相誤差を検出し得る。PFD520は、検出された位相誤差に基づいて、電圧バイアスコントローラ525に位相誤差信号を出力する。電圧バイアス回路525は、位相誤差を低減する方向に電圧バイアスを調整する。

30

#### 【0037】

[0058]位相誤差は、クロック遅延回路515の遅延が基準クロックの1周期に略等しいとき、ゼロに近づく。故に、電圧バイアスコントローラ525は、クロック遅延回路515の遅延が1周期クロック周期に略等しくなるように、電圧バイアスを調整する。一実施形態では、クロック遅延回路515は、スレーブ遅延回路315(1) - 315(m)のステップ遅延の倍数Mに略等しい遅延を有する。故に、この実施形態では、マスタ遅延回路710は、略T/Mのステップ遅延を維持するために、N個のクロック周期（サイクル）ごとに電圧バイアスを更新し、ここで、Tは、1クロック周期（サイクル）である。

40

#### 【0038】

[0059]出力キャパシタ730は、更新から更新までの間（between updates）、電圧バ

50

イアスコントローラ 525 の出力に電圧バイアスを保持するために使用される。出力キャパシタ 730 における電圧バイアスは、電圧バイアスの更新から更新までの間にドリフトし得、結果としてスレーブ遅延回路 315 (1) - 315 (m) にジッタを引き起す。電圧バイアスは、更新から更新までの間の時間量が増加すると、より大きな量ぶんドリフトし得る。結果として、マスタ遅延回路 710 が電圧バイアスを更新するレートを低減すること（即ち、N を増加させること）は、より低い性能（例えば、より高いジッタ）という犠牲を払って、電力消費を低減し得る。故に、マスタ遅延回路 710 の電力を低減することと、マスタ遅延回路 710 の性能との間のトレードオフが存在し得る。

#### 【0039】

[0060]この点において、更新コントローラ 750 は、特定のアプリケーションに対して依然として適切な性能を提供するレベルに、電圧バイアス更新のレートを低減する（故に、電力を低減する）ように構成され得る。例えば、メモリインターフェースが比較的低いデータレートで動作するとき、有効なデータウィンドウは比較的大きい。これは、メモリインターフェースのタイミング要件を緩和し、メモリインターフェースが、マスタ遅延回路 710 からのより低い性能（即ち、更新から更新までの間のより大きい電圧バイアスドリフト）を許容することを可能にする。このケースでは、更新コントローラ 750 は、電力消費を低減するために、電圧バイアス更新のレートを低減し（即ち、N を増加させ）得る。メモリインターフェースが、より高いデータレートで動作するとき、有効データウィンドウはより小さく、メモリインターフェースのタイミング要件はより厳しくなる（例えば、メモリインターフェース内のフリップフロップはより少ないジッタを許容する）。このケースでは、更新コントローラ 750 は、マスタ遅延回路 710 の性能を向上させるために、電圧バイアス更新のレートを増加させ（即ち、N を減少させ）得る。故に、電圧バイアスが更新されるレートは、高い性能が必要でないときは電力消費を低減するために低減され得、（例えば、より高いデータレートで）高い性能が必要とされるときには増加され得る。

#### 【0040】

[0061]2つの異なるN値についてのマスタ遅延回路 710 の例示的な動作が、ここから、図8及び9に関連して説明されるだろう。図8は、Nが2に等しい例を例示するタイミング図である。この例では、更新回路 712 は、基準クロックの2つの周期（サイクル）ごとに一対のパルス 810 (1) - 810 (3) を出力する。パルス 810 (1) - 810 (3) の各対は、クロック遅延回路 515 へのQパルス出力と、PFD520 の第1の入力 522 へのZQパルス出力とを備え、ここで、ZQパルスは、Qパルスに対して略1クロック周期ぶん遅延されている。

#### 【0041】

[0062]図8はまた、Qパルスがクロック遅延回路 515 によって遅延された後の各Qパルスを示す。パルスの対ごとに、PFD520 は、（図8に示されるように）それぞれのZQパルスとそれぞれの遅延Qパルスとの間の位相誤差を検出し、電圧バイアスコントローラ 525 は、検出された位相誤差に基づいて、電圧バイアスを更新する。この例では、マスタ遅延回路 710 は、位相誤差を検出し、基準クロックの2つの周期（サイクル）ごとに、検出された位相誤差に基づいて電圧バイアスを更新する。

#### 【0042】

[0063]図8は、各遅延QパルスがそれぞれのZQパルスに対して早い（それぞれのZQパルスに先行する）例を示すが、遅延Qパルスが、それぞれのZQパルスに対して遅い可能性があることは認識されるべきである。遅延Qパルスが早いケースでは、電圧バイアスコントローラ 525 は、位相誤差を低減するために、クロック遅延回路 515 の遅延を増加させる。遅延Qパルスが遅いケースでは、電圧バイアスコントローラ 525 は、位相誤差を低減するために、クロック遅延回路 515 の遅延を減少させる。

#### 【0043】

[0064]図9は、Nが4に等しい例を例示するタイミング図である。この例では、更新回路 712 は、基準クロックの4つの周期（サイクル）ごとに一対のパルス 910 (1) -

10

20

30

40

50

910(3)を出力する。パルス910(1)-910(3)の各対は、クロック遅延回路515へのQパルス出力と、PFD520の第1の入力522へのZQパルス出力を備え、ここで、ZQパルスは、Qパルスに対して約1クロック周期ぶん遅延されている。

#### 【0044】

[0065]図9はまた、Qパルスがクロック遅延回路515によって遅延された後の各Qパルスを示す。パルスの対ごとに、PFD520は、(図9に示されるように)それぞれのZQパルスとそれとの遅延Qパルスとの間の位相誤差を検出し、電圧バイアスコントローラ525は、検出された位相誤差に基づいて電圧バイアスを更新する。この例では、マスタ遅延回路710は、位相誤差を検出し、基準クロックの4つの周期(サイクル)ごとに、検出された位相誤差に基づいて電圧バイアスを更新する。

10

#### 【0045】

[0066]故に、図8は、電圧バイアスが2つのクロック周期ごとに更新される例を示し、図9は、電圧バイアスが4つのクロック周期ごとに更新される例を示す。図9の例は、更新から更新までの間のより多くの電圧バイアスドリフトという犠牲を払って、より少ない頻度で電圧バイアスを更新することで、図8の例と比べて電力消費を低減し得る。

#### 【0046】

[0067]図10は、Nが4に等しい別の例を例示するタイミング図である。この例では、更新回路712は、基準クロックの4つの周期(サイクル)ごとに一対のパルス1010(1)-1010(3)を出力する。パルス1010(1)-1010(3)の各対は、クロック遅延回路515へのQパルス出力と、PFD520の第1の入力522へのZQパルス出力を備え、ここで、ZQパルスは、Qパルスに対して約1クロック周期ぶん遅延されている。この例は、ZQ及びQパルスがハイではなくローであり、更新回路712の2つの出力がパルス間でローではなくハイである点で、図9の例とは異なる。

20

#### 【0047】

[0068]図10はまた、Qパルスがクロック遅延回路515によって遅延された後の各Qパルスを示す。パルスの対ごとに、PFD520は、(図10に示されるように)それぞれのZQパルスとそれとの遅延Qパルスとの間の位相誤差を検出し、電圧バイアスコントローラ525は、検出された位相誤差に基づいて、電圧バイアスを更新する。PFD520が、(図10に示されるように)これらパルスの立ち上がりエッジ間の位相差分又はこれパルスの立ち下がりエッジ間の位相差分を検出することで位相誤差を検出し得ることは認識されるべきである。この例では、マスタ遅延回路710は、基準クロックの4つの周期(サイクル)ごとに電圧バイアスを更新する。

30

#### 【0048】

[0069]図11は、本開示の実施形態に係る、更新回路712の例示的な実装形態を示す。この実施形態では、更新回路712は、プログラマブルカウンタ1110、第1のクロックゲート1115、第2のクロックゲート1120及びクロック周期遅延回路1122を備える。クロックゲート1115及び1120の各々は基準クロックを受け、以下で更に説明されるように、クロックゲートがゲートイネーブル信号を受けるときには基準クロックをパスするように、クロックゲートがゲートディセーブル信号を受けるときには基準クロックをブロックするように構成される。

40

#### 【0049】

[0070]プログラマブルカウンタ1110は、更新コントローラ750からの制御信号Nと、基準クロックとを受ける。カウンタ1110は、基準クロックのN番目ごとの周期(サイクル)の間ずっとゲートイネーブル信号1125を出力し、1より大きいNのN番目ごとの周期(サイクル)の間の周期の間ずっとゲートディセーブル信号を出力するように構成される。ゲートイネーブル信号1125は、Qパルスを生成するために、第1のクロックゲート1115に、1クロック周期の間、基準クロックをパスさせる。クロック周期遅延回路1122は、ゲートイネーブル信号を1クロック周期ぶん遅延させ、ゲートイネーブル遅延信号1130を第2のクロックゲート1120に出力する。ゲートイネーブル遅延信号1130は、ZQパルスを生成するために、第2のクロックゲート1120に、

50

1クロック周期の間基準クロックをバスさせる。第2のクロックゲート1120に入力されるゲートイネーブル信号1130が、第1のクロックゲート1115に入力されるゲートイネーブル信号1125に対して1クロック周期ぶん遅延されているため、ZQパルスは、Qパルスに対して1クロック周期ぶん遅延されている。

【0050】

[0071] 上述したように、カウンタ1110は、基準クロックのN番目ごとの周期（サイクル）の間ずっとゲートイネーブル信号1125を出力する。これを行うため、カウンタ1110は、基準クロックの周期の数をカウントし、カウンタ1110が基準クロックのN個の周期をカウントする度にゲートイネーブル信号を出力し得る。Nの値がプログラマブルであるため、パルス対を生成するために、カウンタ1010がクロックゲート1115及び1120をイネーブルにするレート（故に、マスタ遅延回路710が電圧バイアスを更新するレート）は、プログラマブルである。

10

【0051】

[0072] クロックゲート1115及び1120の各々は、1つ又は複数の論理ゲートを使用して実装され得る。例えば、各クロックゲート1115及び1120は、第1の及び第2の入力を有するANDゲートを備え得る。ANDゲートの第1の入力は、基準クロックを受け、ANDゲートの第2の入力は、ゲートイネーブル信号（論理1）又はゲートディセーブル信号（論理ゼロ）のいずれかを受ける。この例では、ANDゲートは、ANDゲートがゲートイネーブル信号（論理1）を受けるときには基準クロックをバスし、ANDゲートがゲートディセーブル信号（論理ゼロ）を受けるときには基準クロックをブロックする。基準クロックがブロックされると、ANDゲートは、論理ゼロを出力する。本実施形態に係るクロックゲート1115及び1120は、高いパルス対（この例は、図8及び9に示されている）を生成するために使用され得る。

20

【0052】

[0073] 別の例では、各クロックゲート1115及び1120は、第1の及び第2の入力を有するORゲートを備え得る。ORゲートの第1の入力は、基準クロックを受け、ORゲートの第2の入力は、ゲートイネーブル信号（論理ゼロ）又はゲートディセーブル信号（論理1）のいずれかを受ける。この例では、ORゲートは、ORゲートがゲートイネーブル信号（論理ゼロ）を受けるときには基準クロックをバスし、ORゲートがゲートディセーブル信号（論理1）を受けるときには基準クロックをブロックする。基準クロックがブロックされると、ORゲートは、論理1を出力する。本実施形態に係るクロックゲート1115及び1120は、低いパルス対（この例は、図10に示されている）を生成するために使用され得る。

30

【0053】

[0074] クロックゲート1115及び1120が、上述された例に制限されないこと、及び、各クロックゲート1115及び1120が、他のタイプの論理ゲート及び/又は論理ゲートの組み合わせを使用して実装され得ることは認識されるべきである。

【0054】

[0075] クロック周期遅延回路1122は、基準クロック及びゲートイネーブル信号を受け、ゲートイネーブル信号を、受けた基準クロックの1周期ぶん遅延させるフリップフリップ（例えば、Dフリップフロップ）が実装され得る。

40

【0055】

[0076] 上述したように、更新コントローラ750は、メモリインターフェースのタイミング要件に基づいてNの値を調整し得る。例えば、タイミング要件は、所要の時間におけるメモリインターフェースのデータレートに依存し得る。データレートが低減されると、メモリインターフェースのタイミング要件は、より緩和された状態になり、故に、マスタ遅延回路に対する性能要件が低減される。このケースでは、電圧バイアスが更新されるレートは、電力消費を低減するために低減され得る（即ち、Nが増加され得る）。データレートが増加されると、メモリインターフェースのタイミング要件はより厳しくなる（例えば、適切なデータサンプリングのためにフリップフロップによって許容され得るジッタの

50

量が低減される)。このケースでは、電圧バイアスが更新されるレートは、性能を高めるために増加され得る(即ち、Nが低減され得る)。

【0056】

[0077]一実施形態では、更新コントローラ750は、ロックアップテーブルを含み得、ここでは、ロックアップテーブルは、メモリインターフェースによってサポートされる複数の異なるデータレートを備える。ロックアップテーブルは、各データレートを、Nの対応する値にマッピングし得る。Nの値は、データレートが低くなるにつれ大きくなり得る。この実施形態では、更新コントローラ750は、(例えば、メモリコントローラから)メモリインターフェースの現在のデータレートのインジケーションを受け、ロックアップテーブルを使用して、現在のデータレートに対応するNの値を決定し得る。次に、更新コントローラ750は、決定されたNの値を用いて、マスタ遅延回路710内の更新回路712をプログラムし得る。

10

【0057】

[0078]データレートが変化すると、更新コントローラ750は、ロックアップテーブルを使用して、新しいデータレートに対応するNの値を決定し得る。新しいデータレートのためのNの値が、前のデータレートのためのNの値と異なる場合、更新コントローラ750は、新しいデータレートのためのNの値を用いてマスタ遅延回路710内の更新回路712をプログラムし得る。故に、Nの値(故に、電圧バイアス更新のレート)は、メモリインターフェースのデータレートにおける変化に従って調整され得る。

20

【0058】

[0079]例えば、DRAMメモリインターフェースの場合、Nは、データレートが第1のデータレートを下回る(例えば、400MHzを下回る)とき、最大値(例えば、32)に設定され得、Nは、データレートが第2のデータレートを上回る(例えば、1.6GHzを上回る)とき、1に設定され得る。この例では、Nは、第1のデータレートと第2のデータレートとの間(例えば、400MHzと1.6GHzとの間)のデータレートについて、1から最大値の間の値に調整され得る。

30

【0059】

[0080]マスタ遅延回路710が最初にパワーオンされるとき、位相誤差は、比較的大きいだろう。この点において、更新コントローラ750は、最初にNの値を1に設定して、位相誤差を迅速に低減し、マスタ遅延回路710のループをロックし得る。位相誤差が許容可能なレベルに低下すると、更新コントローラ750は、電力消費を低減するために、Nの値を増加させ得る。例えば、更新コントローラ750は、上述したように、メモリインターフェースの現在のデータレートに基づいてNの値を増加させ得る。

30

【0060】

[0081]図12は、ロック期間中、Nの値が初期に1に設定される例を示すタイミング図である。ロック期間中、電圧バイアスは、マスタ遅延回路710のループを迅速にロックするために、基準クロックの周期ごとに更新される。ロック期間は、位相誤差が許容可能なレベル(例えば、メモリインターフェースのタイミング要件を満たすレベル)に低下すると終了し得る。マスタ遅延回路710のループがロックされた後、Nの値は、電力を低減するために、増加され得る。図12に示される例では、Nの値は、4に増加され得る。しかしながら、本開示の実施形態がこの例に制限されないこと、及び、Nの値が、メモリインターフェースのタイミング要件を満たす任意の値に増加され得ることは認識されるべきである。ロック期間が、図12に示される例における持続時間に制限されないことも認識されるべきである。一般に、ロック期間の持続時間は、位相誤差を許容可能なレベルまで低減するのに必要な電圧バイアス更新の数に依存し得る。

40

【0061】

[0082]一実施形態では、更新コントローラ750は、ロック期間の開始から所定の数のクロック周期の後、ロック期間を終了し得る。この実施形態では、クロック周期の所定数は、マスタ遅延回路710をロックするのに必要なクロック周期の数の推定値に基づき得る。別の実施形態では、更新コントローラ750は、PFD520からの、検出された位

50

相誤差をモニタリングし得る。この実施形態では、更新コントローラ 750 は、検出された位相誤差が閾値よりも下に低下するとロック期間を終了し得る。

#### 【0062】

[0083] 図 13 は、本開示の実施形態に係る、スレーブ遅延回路 1315 の例示的な実装形態を示す。スレーブ遅延回路 1315 は、図 3 に示されるスレーブ遅延回路 315 (1) - 315 (m) のうちのいずれか 1 つを実装するために使用され得る。スレーブ遅延回路 1315 は、往路 (矢印 1312 で示される) に沿って第 1 の複数の NAND ゲート 1310 (1) - 1310 (5) を、復路 (矢印 1332 で示される) に沿って第 2 の複数の NAND ゲート 1330 (1) - 1330 (5) を備える。スレーブ遅延回路 1315 はまた、往路と復路との間に第 3 の複数の NAND ゲート 1320 (1) - 1320 (5) を備え、ここで、各 NAND ゲート 1320 (1) - 1320 (5) は、往路及び復路上の 2 つの異なる位置の間に結合される。NAND ゲート 1310 (1) - 1310 (5)、1320 (1) - 1320 (5)、及び 1330 (1) - 1330 (5) は、マスター遅延回路からの電圧バイアス (図 13 に図示せず) によってバイアスが掛けられ、ここでは、電圧バイアスは、各 NAND ゲートの遅延を制御する。10

#### 【0063】

[0084] この実施形態では、遅延コントローラ 1340 は、スレーブ遲延回路 1315 の入力と出力 (「IN」及び「OUT」と表される) との間の遅延を制御する。遅延コントローラ 1340 は、以下で更に説明されるように、スレーブ遲延回路 1315 を通る信号の経路を制御するために、スレーブ遲延回路 1315 内の NAND ゲートを選択的にイネーブル及びディセーブルにすることによってこれを行う。20

#### 【0064】

[0085] この点において、NAND ゲート 1310 (1) - 1310 (5) は、遅延コントローラ 1340 から制御入力 1317 (1) - 1317 (5) において制御信号を受け、NAND ゲート 1320 (1) - 1320 (5) は、遅延コントローラ 1340 から制御入力 1325 (1) - 1325 (5) において制御信号を受け、NAND ゲート 1330 (5) は、遅延コントローラ 1340 から制御入力 1335 において制御信号を受ける。例示を簡潔にするために、NAND ゲートの制御入力と遅延コントローラ 1340 との間の接続は、図 13 には示されない。制御信号は、スレーブ遲延回路 1315 を通る信号の経路を制御するために、NAND ゲートを選択的にイネーブル及びディセーブルにし、故に、スレーブ遲延回路 1315 を通る信号の遅延を制御する。(例えば、それぞれの制御入力に論理 1 を入力することで) NAND ゲートがイネーブルにされているとき、NAND ゲートは、インバータとして機能する。(例えば、それぞれの制御入力に論理ゼロを入力することで) NAND ゲートがディセーブルにされているとき、NAND ゲートの出力状態は、不变である。30

#### 【0065】

[0086] 図 14A は、遅延コントローラ 1340 が、スレーブ遲延回路 1315 の NAND ゲート 1310 (1) - 1310 (3)、1320 (4) 及び 1330 (1) - 1330 (4) を通る遲延経路 1410 を形成する例を示す。この例では、スレーブ遲延回路 1315 を通る遲延は、信号が 8 つの NAND ゲートを通って伝播するため、1 つの NAND ゲートの遲延の 8 倍に等しい。図 14A はまた、遲延経路 1410 を形成するために遲延コントローラ 1340 から NAND ゲート 1310 (1) - 1310 (5)、1320 (1) - 1320 (5) 及び 1330 (5) の制御入力に入力される制御信号の論理状態を示す。例示を容易にするために、制御入力の参照番号は、図 14 には示されない。40

#### 【0066】

[0087] 図 14B は、遲延コントローラ 1340 が、スレーブ遲延回路 1315 の NAND ゲート 1310 (1) - 1310 (4)、1320 (5) 及び 1330 (1) - 1330 (5) を通る遲延経路 1420 を形成する例を示す。この例では、スレーブ遲延回路 1315 を通る遲延は、信号が 10 個の NAND ゲートを通って伝播するため、1 つの NAND ゲートの遲延の 10 倍に等しい。図 14B はまた、遲延経路 1420 を形成するため50

に遅延コントローラ 1340 から NAND ゲート 1310 (1) - 1310 (5)、1320 (1) - 1320 (5) 及び 1330 (5) の制御入力に入力される制御信号の論理状態を示す。例示を容易にするために、制御入力の参照番号は、図 14B には示されない。

【0067】

[0088] この実施形態では、遅延コントローラ 1340 は、ステップ遅延の倍数によって、スレーブ遅延回路 1315 の遅延を調整するこが可能であり、ここで、ステップ遅延は、2 つの NAND ゲートの遅延である。2 つの NAND ゲートのステップ遅延は、信号が、スレーブ遅延回路 1315 の入力及び出力において同じ極性を有することを確実にする。ステップ遅延は、マスタ遅延回路から NAND ゲートに供給される電圧バイアスによって制御される。スレーブ遅延回路 1315 が図 13 に示される例における NAND ゲートの数に制限されること、及び、スレーブ遅延回路 1315 が任意の数の NAND ゲートを含み得ることは認識されるべきである。例えば、NAND ゲートの数は、選択可能な遅延の数を増加させるために、増加され得る。

10

【0068】

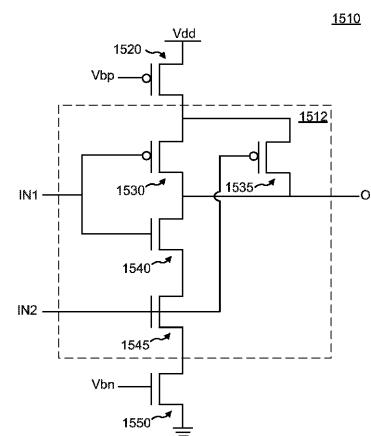

[0089] 図 15 は、本開示の実施形態に係る、電圧制御型遅延を有する NAND ゲート 1510 の例示的な実装形態を示す。NAND ゲート 1510 は、図 13 の NAND ゲートを実装するために使用され得る。NAND ゲート 1510 は、NAND 論理回路 1512、電流欠乏 (current-starving) PMOS トランジスタ 1520 及び電流欠乏 NMOS トランジスタ 1550 を備える。以下で更に説明されるように、NAND 論理回路 1512 は、NAND ゲート 1510 の論理関数を実行し、PMOS トランジスタ 1520 及び NMOS トランジスタ 1550 は、NAND ゲート 1510 の遅延を制御する。

20

【0069】

[0090] NAND 論理回路 1512 は、第 1 の PMOS トランジスタ 1530、第 2 の PMOS トランジスタ 1535、第 1 の NMOS 1540 トランジスタ及び第 2 の NMOS トランジスタ 1545 を備える。第 1 の PMOS トランジスタ 1530 及び第 2 の PMOS トランジスタ 1535 のソースは互いに結合され、第 1 の PMOS トランジスタ 1530 及び第 2 の PMOS トランジスタ 1535 のドレインは互いに結合され、第 1 の NMOS トランジスタ 1540 のドレインは、第 1 の PMOS トランジスタ 1530 及び第 2 の PMOS トランジスタ 1535 のドレインに結合され、第 1 の NMOS トランジスタ 1540 のソースは、第 2 の NMOS トランジスタ 1545 のドレインに結合される。第 1 の PMOS トランジスタ 1530 及び第 2 の PMOS トランジスタ 1535 のソースは、電流欠乏 PMOS トランジスタ 1520 を通して電源 Vdd に結合され、第 2 の NMOS トランジスタ 1545 のソースは、電流欠乏 NMOS トランジスタ 1550 を通して接地に結合される。

30

【0070】

[0091] NAND ゲート 1510 の第 1 の入力 (「IN 1」と表される) は、第 1 の PMOS トランジスタ 1530 及び第 1 の NMOS トランジスタ 1540 のゲートに結合され、NAND ゲート 1510 の第 2 の入力 (「IN 2」と表される) は、第 2 の PMOS トランジスタ 1535 及び第 2 の NMOS トランジスタ 1545 のゲートに結合される。NAND ゲート 1510 の出力 (「OUT」と表される) は、第 1 の PMOS トランジスタ 1530、第 2 の PMOS トランジスタ 1535 及び第 1 の NMOS トランジスタ 1540 のドレインに結合される。

40

【0071】

[0092] 上述したように、NAND 論理回路 1512 は、NAND ゲート 1510 の論理関数を実行する。この点において、NAND 論理回路 1512 は、第 1 及び第 2 の入力の両方 (IN 1 及び IN 2) が論理 1 である場合、論理ゼロを出力し、そうでない場合、論理 1 を出力する。故に、第 2 の入力 (IN 2) が論理ゼロである場合、NAND 論理回路 1512 は、第 1 の入力 (IN 1) における論理状態に関わらず論理 1 を出力する。第 2 の入力 (IN 2) が論理 1 である場合、NAND 論理回路 1512 は、第 1 の入力 (IN

50

1) における論理状態の逆数を出力する。

【0072】

[0093] 一例では、第1の入力(IN1)は、スレーブ遅延回路(例えば、スレーブ遅延回路1315)を通って伝播する信号を受けるために使用され得、第2の入力(IN2)は、遅延コントローラ(例えば、遅延コントローラ1340)から制御信号を受けるために使用され得る。この例では、制御信号が論理ゼロである場合、NAND論理回路1512は、第1の入力(IN1)における論理状態に関わらず論理1を出力する。このケースでは、NAND論理回路1512は、第1の入力(IN1)において信号を伝播しない。制御信号が論理1である場合、NAND論理回路1512は、第1の入力(IN1)において信号を反転させ、従って、インバータとして信号を伝播させる。

10

【0073】

[0094] 上述したように、電流欠乏PMOSトランジスタ1520及び電流欠乏NMOSトランジスタ1550は、NANDゲート1510の遅延を制御する。より具体的には、電流欠乏NMOSトランジスタ1550は、そのゲートにおいて第1の電圧バイアスV<sub>b</sub><sub>n</sub>を受け、この第1の電圧バイアスV<sub>b</sub><sub>n</sub>に基づいて、NANDゲート1510の出力において立ち下がりエッジを引き起こす信号の遅延を制御する。これは、第1の電圧バイアスV<sub>b</sub><sub>n</sub>が、電流欠乏NMOSトランジスタ1550の電導度を制御し、従って、電流欠乏NMOSトランジスタ1550を介してNANDゲート1510の出力(OUT)から接地に流すことができる電流量を制御するためである。これは、次に、NANDゲート1510の立ち下がり時間を制御し、従って、ハイからローに遷移するNANDゲート1510の出力(OUT)(即ち、立ち下がりエッジ)の時間を制御する。第1の電圧バイアスV<sub>b</sub><sub>n</sub>が高くなるほど、出力(OUT)から接地への電流は高くなり、従って、遅延は短くなる。第1の電圧バイアスV<sub>b</sub><sub>n</sub>が低くなるほど、出力(OUT)から接地への電流は低くなり、従って、遅延は長くなる。

20

【0074】

[0095] 電流欠乏PMOSトランジスタ1520は、そのゲートにおいて第2の電圧バイアスV<sub>b</sub><sub>p</sub>を受け、この第2の電圧バイアスV<sub>b</sub><sub>p</sub>に基づいて、NANDゲート1510の出力(OUT)において立ち上がりエッジを生じさせる信号の遅延を制御する。これは、第2の電圧バイアスV<sub>b</sub><sub>p</sub>が、電流欠乏PMOSトランジスタ1520の導電度を制御し、従って、電流欠乏PMOSトランジスタ1520を介してV<sub>d</sub><sub>d</sub>からNANDゲート1510の出力(OUT)に流すことができる電流量を制御するためである。これは、次に、NANDゲート1510の立ち上がり時間を制御し、従って、ローからハイに遷移するNANDゲート1510の出力(即ち、立ち上がりエッジ)の時間を制御する。第2の電圧バイアスV<sub>b</sub><sub>p</sub>が低くなるほど、V<sub>d</sub><sub>d</sub>から出力(OUT)への電流は高くなり、従って、遅延は短くなる。第2の電圧バイアスV<sub>b</sub><sub>p</sub>が高くなるほど、V<sub>d</sub><sub>d</sub>から出力(OUT)への電流は低くなり、従って、遅延は長くなる。

30

【0075】

[0096] 故に、第1の電圧バイアスV<sub>b</sub><sub>n</sub>及び第2の電圧バイアスV<sub>b</sub><sub>p</sub>は、NANDゲート1510の遅延を制御し、従って、NANDゲート1510が実装されるNANDゲートを備えるスレーブ遅延回路のステップ遅延を制御する。第1の電圧バイアスV<sub>b</sub><sub>n</sub>は、NANDゲート1510の出力(OUT)における立ち下がりエッジの遅延を制御し、第2の電圧バイアスV<sub>b</sub><sub>p</sub>は、NANDゲート1510の出力(OUT)における立ち上がりエッジを制御する。

40

【0076】

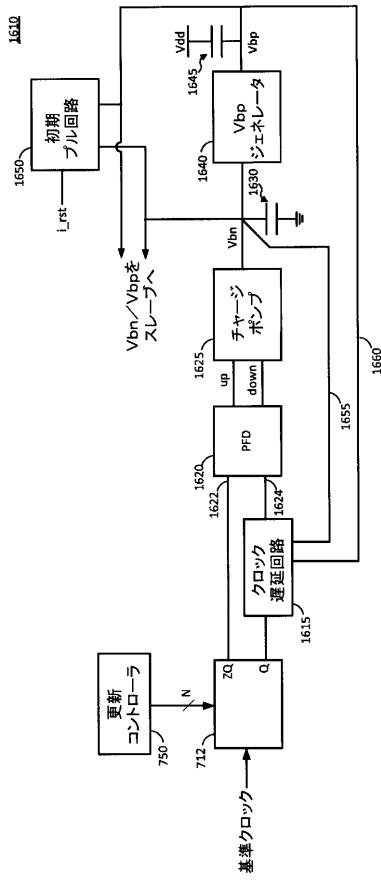

[0097] 図16は、本開示の実施形態に係る、スレーブ遅延回路について所望のステップ遅延を達成するために、第1の電圧バイアスV<sub>b</sub><sub>n</sub>及び第2の電圧バイアスV<sub>b</sub><sub>p</sub>を調整するように構成されたマスタ遅延回路1610を示す。マスタ遅延回路1610は、更新回路712、クロック遅延回路1615、位相周波数検出器(PFD)1620、チャージポンプ1625、V<sub>b</sub><sub>p</sub>ジェネレータ1640及び初期プル回路1650を備える。マスタ遅延回路1610は、チャージポンプ1625の出力と接地との間に結合された第1

50

のキャパシタ 1630 と、Vdd と Vbp ジェネレータ 1640 の出力との間に結合された第 2 のキャパシタ 1645 とを更に備える。以下で更に説明されるように、第 1 のキャパシタ 1630 は、第 1 の電圧バイアス Vbn を生成するために使用され、第 2 のキャパシタ 1645 は、第 2 の電圧バイアス Vbp を生成するために使用される。

#### 【0077】

[0098] 動作中、更新回路 712 は、基準クロックの N 個の周期（サイクル）ごとに一対のパルスを出力する。パルスの各対は、Q パルス及び ZQ パルスを備え、ここでは、ZQ パルスは、Q パルスに対して略 1 クロック周期ぶん遅延されている。パルスの対ごとに、更新回路 712 は、PFD1620 の第 1 の入力 1622 に ZQ パルスを出力し、クロック遅延回路 1615 に Q パルスを出力する。クロック遅延回路 1615 は、第 1 の電圧バイアス Vbn 及び第 2 の電圧バイアス Vbp によって制御された量だけ Q パルスを遅延させ、これは、それぞれチャージポンプ 1625 及び Vbp ジェネレータ 1640 の出力からクロック遅延回路 1615 にフィードバックされる。第 1 の電圧バイアス Vbn は、第 1 のフィードバックループ 1655 によってクロック遅延回路 1615 にフィードバックされ、第 2 の電圧バイアス Vbp は、第 2 のフィードバックループ 1660 によってクロック遅延回路 1615 にフィードバックされる。クロック遅延回路 1615 は、結果として得られた遅延 Q パルスを、PFD1620 の第 2 の入力 1624 に出力する。

10

#### 【0078】

[0099] PFD1620 は、ZQ パルスと遅延 Q パルスとの間の位相誤差を検出する。例えば、PFD1620 は、ZQ パルス及び遅延 Q パルスの立ち上がりエッジの間の位相差分又は ZQ パルス及び遅延 Q パルスの立ち下がりエッジの間の位相差分を検出することで、位相誤差を検出し得る。PFD1620 は、検出された位相誤差に基づいて、チャージポンプ 1625 に UP 信号及び / 又は DOWN 信号を出力する。UP 信号は、第 1 のキャパシタ 1630 を充電する（故に、第 1 の電圧バイアス Vbn を増加させる）ことをチャージポンプ 1625 に行わせ、DOWN 信号は、第 1 のキャパシタ 1630 を放電する（故に、第 1 の電圧バイアス Vbn を減少させる）ことをチャージポンプ 1625 に行わせる。PFD1620 は、検出された位相誤差を減少させる方向に UP 信号及び / 又は DOWN 信号（故に、第 1 の電圧バイアス Vbn）を調整する。

20

#### 【0079】

[00100] 第 1 の電圧バイアス Vbn は、この第 1 の電圧バイアス Vbn に基づいて第 2 の電圧バイアス Vbp を生成する Vbp ジェネレータ 1640 に入力される。一実施形態では、Vbp ジェネレータ 1640 は、単に、Vdd - Vbp が Vbn に略等しくなるように第 2 の電圧バイアス Vbp を調整し得る。別の実施形態では、Vbp ジェネレータ 1640 は、スレーブ遅延回路内の NAND ゲートの立ち上がり時間及び立ち下がり時間が略等しくなるように第 2 の電圧バイアス Vbp を調整し得る。例えば、Vbp ジェネレータ 1640 は、NAND ゲートのうちの 1 つを立ち上がらせ、もう一方の NAND ゲートを立ち下がらせる相補信号によって駆動される 2 つの NAND ゲートを備え得る。両方の NAND ゲートは、第 1 の電圧バイアス Vbn 及び第 2 の電圧バイアス Vbp によってバイアスが掛けられ得、スレーブ遅延回路に内の NAND ゲートの複製であり得る。この例では、Vbp ジェネレータ 1640 は、NAND ゲートの立ち上がりエッジ及び立ち下がりエッジが交差する点（例えば、電圧）を検出し、交差点が NAND ゲートの電圧振幅の略中央（例えば、略半分の Vdd）となるように第 2 の電圧バイアス Vbp を調整し得る。

30

#### 【0080】

[0101] 位相誤差は、クロック遅延回路 1615 の遅延が基準クロックの 1 周期に略等しいとき、ゼロに近づく。故に、マスタ遅延回路 1610 は、クロック遅延回路 1615 の遅延が 1 クロック周期に略等しくなるように、第 1 の電圧バイアス Vbn 及び第 2 の電圧バイアス Vbp を調整する。一実施形態では、クロック遅延回路 1615 は、スレーブ遅延回路のステップ遅延の倍数 M に略等しい遅延を有する。例えば、単純な実装形態では、クロック遅延回路 1615 は、直列に結合された  $2 \times M$  個の NAND ゲートを備え得、こ

40

50

ここで、ステップ遅延は、2つのNANDゲートの遅延である。故に、この実施形態では、マスタ遅延回路1610は、略T/Mのステップ遅延を維持するために、N個のクロック周期(サイクル)ごとに第1の電圧バイアスVbn及び第2の電圧バイアスVbpを更新し、ここで、Tは、1クロック周期(サイクル)である。

#### 【0081】

[0102]第1のキャパシタ1630は、更新から更新までの間、第1の電圧バイアスVbnを保持し、第2のキャパシタ1645は、更新から更新までの間、第2の電圧バイアスVbpを保持する。第1の電圧バイアスVbn及び第2の電圧バイアスVbpは、更新から更新までの間にドリフトする。上述したように、更新から更新までの間の時間を増加させること(即ち、Nを増加させること)は、更新から更新までの間のより多くのドリフトという犠牲を払って、電力消費を低減する(故に、性能を低下させる)。この点において、更新コントローラ750は、特定のデータレートについてタイミング要件を依然として満たしつつ、電力消費を低減するために、更新のレートを調整(即ち、Nを調整)し得る。

10

#### 【0082】

[0103]初期プル回路1650は、誤ロックを防ぐために、第1の電圧バイアスVbn及び第2の電圧バイアスVbpについての初期の値を設定するように構成される。これを行うために、リセット信号(「i\_rst」と表される)がアサートされるとき(例えば、i\_rstが論理1のとき)、初期プル回路1650は初期に、第1の電圧バイアスVbnを電源Vddに引き上げ、第2の電圧バイアスVbpを接地に引き下げる。これは初期に、クロック遅延回路1615を、1クロック周期よりも短い遅延に設定し、これは、マスタ遅延回路1610が、クロック遅延回路1615の遅延を1クロック周期にロックすることを確実にするのを助ける。

20

#### 【0083】

[0104]第1の電圧バイアスVbn及び第2の電圧バイアスVbpが初期に設定され、リセットがオフにされた(例えば、i\_rstが論理ゼロになった)後、マスタ遅延回路1610は、ロック期間中、クロック周期(サイクル)ごとに第1の電圧バイアスVbn及び第2の電圧バイアスVbpを更新し得る。一度マスタ遅延回路1610がロックされると、上述したように、電力を温存するために、更新から更新までの間の間隔は増加され得る(即ち、Nが増加され得る)。

30

#### 【0084】

[0105]図17は、本開示の実施形態に係る、クロック遅延回路1615の例示的な実装形態を示す。クロック遅延回路1615は、第1の遅延段1710及び第2の遅延段1750を備える。クロック遅延回路1615を通る総合遅延(total delay)は、大よそ、第1の遅延段1710及び第2の遅延段1750を介する遅延の合計である。

#### 【0085】

[00106]第1の遅延段1710は、発振器1720及びカウント回路1730を備える。発振器1720は、遅延回路1725及び発振イネーブル/ディセーブル回路1740を備える。

40

#### 【0086】

[0107]遅延回路1725は、図13のスレーブ遅延回路1315の構造に類似した構造で結合されたNANDゲートを備え得る。図17に示される例では、遅延回路1725を通る遅延経路1712を形成するために、遅延回路1725内のNANDゲートの一部がイネーブルにされる。一例では、経路1712の遅延は、 $16 * t_d$ に等しく、ここで、 $t_d$ は、1つのステップ遅延(例えば、2つのNANDゲートの遅延)である。ステップ遅延 $t_d$ は、第1の電圧バイアスVbn及び第2の電圧バイアスVbp(図17には示されない)によって制御される。

#### 【0087】

[0108]発振イネーブル/ディセーブル回路1740は、以下で更に説明するように、発振器1720がイネーブルにされるかディセーブルにされるかを、カウント回路1730

50

からの制御信号に基づいて制御する。図17の例では、発振イネーブル／ディセーブル回路1740は、遅延回路1725の出力1735に結合された第1の入力と、制御信号を受けるためのカウント回路1730に結合された（制御入力とも呼ばれる）第2の入力1745と、遅延回路1725の入力に結合された出力とを有するNANDゲート1740を備える。NANDゲート1740は、第1の電圧バイアスV<sub>b</sub>n及び第2の電圧バイアスV<sub>b</sub>p（図17に図示せず）によってバイアスが掛けられる。

【0088】

[0109]この例では、制御信号が論理1であるとき、NANDゲート1740は、遅延回路1725の出力と入力との間でインバータとして機能し、これは、遅延回路1725を発振させる。故に、発振器1720は、制御信号が論理1であるときイネーブルにされる。制御信号が論理ゼロであるとき、NANDゲート1740の出力状態は、遅延回路1725の出力における論理状態に関わらず、論理1に一定に保たれる。これは、遅延回路1725の入力から遅延回路1725の出力を効率的にブロックする。結果として、遅延回路1725は、発振することができない。故に、発振器1720は、制御信号が論理ゼロであるときディセーブルにされる。

10

【0089】

[0110]発振器1720がイネーブルにされると、遅延回路1725及びNANDゲート1740は、閉ループを形成し、ここでは、このループを通る1トリップは、遅延回路1725を介する経路1712の遅延と、NANDゲート1740の遅延との合計に等しい。経路1712の遅延が $16 * t_d$ に等しい例の場合、このループを通る1トリップは、 $16.5 * t_d$ （即ち、経路1712を介する $16 * t_d$ 遅延とNANDゲート1740を介する $0.5 * t_d$ 遅延）に略等しい。

20

【0090】

[0111]第1の遅延段1710の例示的な動作が、ここから、本開示の実施形態に従って説明されるだろう。この例では、第1の遅延段1710が、更新回路712（この例は、図10に示される）から低いQパルスを受けることが想定され得る。更新回路712からQパルスの立ち上がりエッジを受けるのに先立ち、発振器1720は、ディセーブルにされる（即ち、カウント回路1730は、NANDゲート1740の制御入力1745に論理ゼロを出力する）。加えて、カウント回路1730は、第2の遅延段1750に論理1を出力する。

30

【0091】

[0112]Qパルスの立ち上がりエッジ上で、カウント回路1730はトリガされる。これは、発振器1720をイネーブルにするために、NANDゲート1740の制御入力1745に論理1を出力することをカウント回路1730に行わせる。これはまた、発振器1720の発振の数のカウントを開始することと、第2の遅延段1750への出力をハイからローに遷移させることとをカウント回路1730に行わせる。

【0092】

[0113]発振器1720が発振すると、遅延回路1725の出力1735における論理状態が変化する。出力論理状態の変化から変化までの時間は、NANDゲート1740と遅延回路1725内の経路1712とを通る1トリップの遅延に略等しい。カウント回路1730は、遅延回路1725の出力1735における各立ち下がりエッジでカウント値をインクリメントし得る。代替的に、カウント回路1730は、遅延回路1725の出力1735における各立ち上がりエッジでカウント値をインクリメントし得る。どちらのケースにおいても、カウント回路1730は、信号が、NANDゲート1740と遅延回路1725内の経路1712とを通るトリップを行なう度にカウント値をインクリメントする。NANDゲート1740と遅延回路1725内の経路1712とを通る遅延が $16.5 * t_d$ に等しい例の場合、カウント回路1730は、 $2 * 16.5 * t_d$ の遅延の後にカウント値をインクリメントする。

40

【0093】

[0114]カウント値が所定の終カウント値（例えば、13カウント）に達すると、カウン

50

ト回路 1730 は、発振器 1720 をディセーブルにするために、NAND ゲート 1740 の制御入力 1745 に論理ゼロを出力する。カウント回路 1730 はまた、第 2 の遅延段 1750 に立ち上がりエッジを出力する。故に、第 1 の遅延段 1710 は、カウント値が終カウント値に達することに応答して、第 2 の遅延段 1750 に立ち上がりエッジを出力する。終カウント値が 13 であり、NAND ゲート 1740 と遅延回路 1725 とを通る遅延が  $16.5 * t_d$  である例の場合、第 1 の遅延段 1710 に入力される Q パルスの立ち上がりエッジと、第 2 の遅延段 1750 に出力される立ち上がりエッジとの間の遅延は、 $13 * 2 * 16.5 * t_d$  に略等しい。終カウントに達した後、発振器 1720 は、カウント回路 1730 が次の Q パルスの立ち上がりエッジによって再トリガされるまでディセーブルのままであるだろう。加えて、カウント回路 1730 は、再トリガされるまで、第 2 の段 1750 に論理 1 を出力し得る。

10

## 【0094】

[0115]一実施形態では、第 2 の遅延段 1750 は、第 1 の遅延段 1710 と実質的に同一の構造を有する。この実施形態では、第 2 の遅延段 1750 は、発振器 1770 及びカウント回路 1780 を備える。発振器 1770 は、発振イネーブル / ディセーブル回路 1790 及び遅延回路 1775 を備える。図 17 の例では、発振イネーブル / ディセーブル回路 1790 は、NAND ゲート 1790 を備える。第 2 の遅延段 1750 内の遅延回路 1775、カウント回路 1780 及びNAND ゲート 1790 は、第 1 の遅延段 1710 内の遅延回路 1725、カウント回路 1730、及びNAND ゲート 1740 と実質的に類似した方法で機能し得る。

20

## 【0095】

[0116]第 1 の遅延段 1710 から立ち上がりエッジを受けるのに先立ち、第 2 の遅延段 1750 内の発振器 1750 は、ディセーブルにされる（即ち、カウント回路 1780 は、NAND ゲート 1790 の制御入力 1795 に論理ゼロを出力する）。また、カウント回路 1780 は、PFD1620 に論理 1 を出力する。

## 【0096】

[0117]第 1 の遅延段 1710 からの立ち上がりエッジ上で、カウント回路 1780 はトリガされる。これは、発振器 1770 をイネーブルにするために、NAND ゲート 1790 の制御入力 1795 に論理 1 を出力することをカウント回路 1780 に行わせる。これはまた、発振器 1770 の発振の数のカウントを開始することと、PFD1620 への出力をハイからローに遷移させることとをカウント回路 1780 に行わせる。

30

## 【0097】

[0118]カウント回路 1780 におけるカウント値が所定の終カウント値（例えば、13 カウント）に達すると、カウント回路 1780 は、発振器 1770 をディセーブルするために、NAND ゲート 1790 に論理ゼロを出力する。カウント回路 1780 はまた、PFD1620 に立ち上がりエッジを出力する。終カウント値が 13 であり、NAND ゲート 1790 及び遅延回路 1775 を通る遅延が  $16.5 * t_d$  である例の場合、第 2 の遅延段 1750 に入力される立ち上がりエッジと、PFD1620 に出力される立ち上がりエッジとの間の遅延は、 $13 * 2 * 16.5 * t_d$  に略等しい。終カウントに達した後、発振器 1770 は、カウント回路 1780 が、第 1 の遅延段 1710 から次の立ち上がりエッジによって再トリガされるまでディセーブルのままであるだろう。加えて、カウント 1780 は、再トリガされるまで、PFD1620 に論理 1 を出力し得る。

40

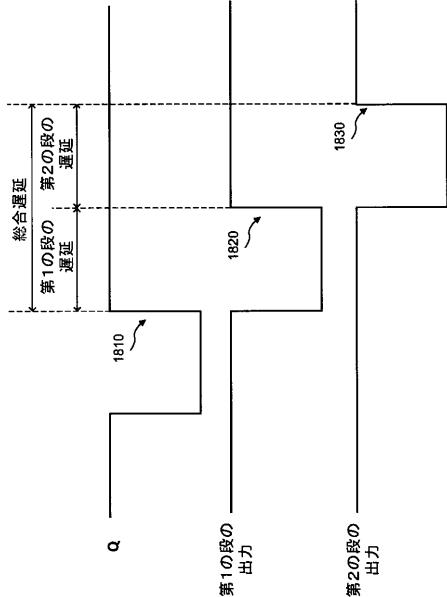

## 【0098】

[0119]図 18 は、Q パルス、第 1 の遅延段 1710 の出力及び第 2 の遅延段 1750 の出力の例を例示するタイミング図である。この例では、N は 1 よりも大きいと想定される。Q パルスの立ち上がりエッジ 1810 は、第 1 の遅延段 1710 内のカウント回路 1730 をトリガし、これは、第 1 の遅延段 1710 の出力をハイからローに遷移させる。カウント回路 1730 のカウント値が終カウントに達すると、第 1 の遅延段 1710 は、第 2 の遅延段 1750 に立ち上がりエッジ 1820 を出力する。第 1 の遅延段 1710 からの立ち上がりエッジ 1820 は、第 2 の遅延段内のかウント回路 1780 をトリガし、こ

50

れは、第2の遅延段1750の出力をハイからローに遷移させる。カウント回路1780のカウント値が終カウントに達すると、第2の遅延段1750は、PFD1620に立ち上がりエッジ1830を出力する。PFD1620に出力される立ち上がりエッジ1830は、図18に示されるように、Qパルスの立ち上がりエッジから、第1の遅延段1710及び第2の遅延段1750を介する遅延の合計ぶん遅延されている。

【0099】

[0120] 上述したように、マスタ遅延回路1610は、クロック遅延回路1615を介する遅延が1クロック周期に略等しくなるまで、第1の電圧バイアスV<sub>b</sub>n及び第2の電圧バイアスV<sub>b</sub>pを調整する。故に、マスタ遅延回路1610は、T/Mのステップ遅延を達成するように、第1の電圧バイアスV<sub>b</sub>n及び第2の電圧バイアスV<sub>b</sub>pを調整し、ここで、Tは、1クロック周期であり、Mは、第1の遅延段1710及び第2の遅延段1750におけるステップ遅延の総数である。クロック遅延回路1615の各段1710及び1750を介する遅延が $13 * 2 * 16.5 * t_d$ に等しい例の場合、クロック遅延回路1615を介する総合遅延は、 $2 * 13 * 2 * 16.5 * t_d$ である。この例では、マスタ遅延回路1610は、 $T / (2 * 13 * 2 * 16.5)$ に略等しいステップ遅延 $t_d$ を達成するように第1のバイアスV<sub>b</sub>n及び第2のバイアスV<sub>b</sub>pを調整し、ここで、Tは1クロック周期である。

10

【0100】

[0121] 図17の例示的なクロック遅延回路1615は、以下の利点のうちの1つ又は複数を提供する。第1に、クロック遅延回路1615は、単に長い遅延チェーンを使用する場合と比べてかなり少数のNANDゲートを使用して小さいステップ遅延を達成し、それによって、クロック遅延回路1615のサイズを低減することができる。これは、クロック遅延回路1615が、発振器を形成するために比較的小さい遅延チェーン（例えば、経路1712内のNANDゲート）を使用し、クロック遅延回路1615の遅延を作成するために発振器の発振数をカウントするためである。

20

【0101】

[0122] 別の利点は、電圧バイアス更新のレートが低減される（即ち、Nが増加される）とき、クロック遅延回路1615の電力消費が、大幅に低減されることである。これは、発振器1720及び1770が、更新から更新までの間、ディセーブルにされるためである。結果として、更新から更新までの間の間隔が増加される（即ち、Nが増加される）とき、発振器1720及び1770からの動的な電力消費が低減される。例えば、Nが1よりも大きいとき、発振器1720及び1770によって消費される電力は、電圧バイアスV<sub>b</sub>n及びV<sub>b</sub>pがクロック周期ごとに更新されるケースの場合の発振器1720及び1770によって消費される電力の約 $1/N$ に低減される。

30

【0102】

[0123] 別の利点は、2つの遅延段1710及び1750を使用することが、各段に、Qパルス間でリセットするための時間をより多く提供することである。例えば、第1の遅延段1710が現在のQパルスについての終カウントに達し、Nが1に等しいとき、第1の遅延段1710は、次のQパルスのためにリセットするため、第2の遅延段1750の遅延に略等しい時間量を有する。

40

【0103】

[0124] 遅延回路1725及び1775がNANDゲートに制限されないことは認識されるべきである。例えば、各遅延回路1725及び1775は、NANDゲート以外の遅延素子のチェーンを備え得、ここでは、遅延素子は、スレーブ遅延回路内の遅延素子の複製であり得る。この例では、遅延チェーンの入力及び出力は、発振器を形成するために選択的に結合され得、それぞれのカウント回路1730及び1780は、遅延を作成するために発振器の発振数をカウントし得る。

【0104】

[0125] クロック遅延回路1615が2つの遅延段に制限されないことも認識されるべきである。例えば、クロック遅延回路1615は、第1の遅延段1710の出力がPFD1

50

620に遅延Qパルスを提供する1つの遅延段1710を備え得る。1つの遅延段1710は、例えば、遅延段1710が、第2の遅延段の必要なく次のQパルスのためにリセットするのに十分な時間を有するとき(例えば、Nが2つ以上に等しいとき)、使用され得る。

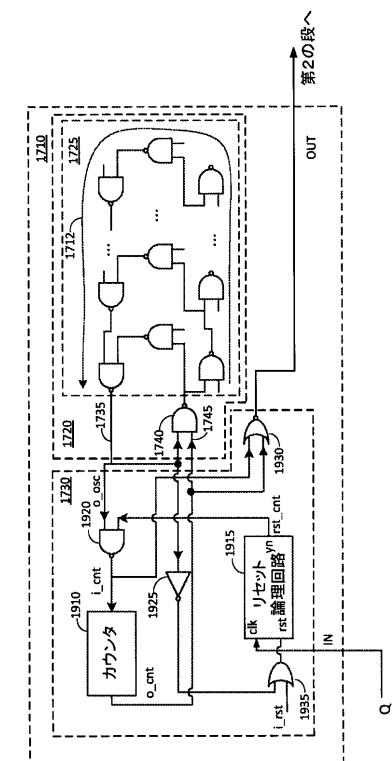

#### 【0105】

[0126]図19は、本開示の実施形態に係る、第1の遅延段1710内のカウント回路1730の例示的な実装形態を示す。第2の遅延段1750内のカウント回路1780はまた、図19に示される回路を使用して実装され得る。

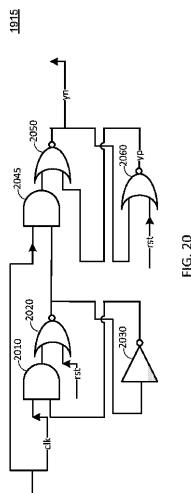

#### 【0106】

[0127]この実施形態では、カウント回路1730は、リセット論理回路1915、カウンタ1910、NANDゲート1920、NORゲート1930、インバータ1925及びORゲート1935を備える。以下の説明では、カウント回路1730内のNANDゲート1920は、第2のNANDゲート1920と呼ばれ、発振器1720をイネーブル/ディセーブルするために使用されるNANDゲート1740は、第1のNANDゲート1740と呼ばれるだろう。

#### 【0107】

[0128]第2のNANDゲート1920は、遅延回路1725の出力(「o\_osc」と表される)に結合された第1の入力と、リセット論理回路1915の出力(「rst\_cnt」と表される)に結合された第2の入力を有する。カウンタ1910は、第2のNANDゲート1920の出力に結合された入力(「i\_cnt」と表される)と、第1のNANDゲート1740の制御入力1745に結合された出力(「o\_cnt」と表される)とを有する。故に、この実施形態では、カウンタ1910の出力(o\_cnt)の論理状態は、発振器1720がイネーブルにされるかディセーブルにされるかを制御する。ORゲート1935は、初期リセット信号(「i\_rst」と表される)を受けるための第1の入力と、インバータ1925を通る遅延回路1725の出力(「o\_osc」と表される)に結合された第2の入力を有する。ORゲート1935の出力は、リセット論理回路1915のリセット入力(「rst」と表される)に結合される。NORゲート1930は、カウンタ1910の入力(i\_cnt)に結合された第1の入力と、カウンタ1910の出力(o\_cnt)に結合された第2の入力を有する。

[0129]カウント回路1730の例示的な動作が、ここから、本開示の実施形態に従って説明されるだろう。この例では、第1の遅延段が、更新回路712(この例は、図10に示される)から低いQパルスを受けることが想定され得る。更新回路712からQパルスの立ち上がりエッジを受けるのに先立ち、発振器1720は、ディセーブルにされ(即ち、カウンタ1910は、第1のNANDゲート1740の制御入力1745に論理ゼロを出力(o\_cnt)し、遅延回路1725は、第2のNANDゲート1920に論理1を出力(o\_osc)する。リセット論理回路1915は、第2のNANDゲート1920に論理1を出力(rst\_cnt)する。故に、第2のNANDゲート1920は、遅延回路1725及びリセット論理回路1915から論理1を受け、これは、カウンタ1910の入力(i\_cnt)に論理ゼロを出力することを第2のNANDゲート1920に行わせる。カウンタ1910の入力(i\_cnt)及び出力(o\_cnt)の両方が論理ゼロであるため、NORゲート1930は、論理1を出力する。

#### 【0108】

[0130]Qパルスの立ち上がりエッジ上で、リセット論理回路1915の出力(rst\_cnt)は、ハイからローに遷移する。これは、カウンタ1910の入力(i\_cnt)に論理1を出力することを第2のNANDゲート1920に行わせ、これは、カウンティングを開始するようカウンタ1910をトリガする。これに応答して、カウンタ1910は、第1のNANDゲート1740の制御入力1745に論理1を出力(o\_cnt)し、発振器1720をイネーブルにする。故に、カウンタ1910は、リセット論理回路1915の出力(rst\_cnt)がローになると応答して発振器1720をイネーブルにする。更に、カウンタ1910の出力(o\_cnt)における論理1(これは、NOR

10

20

30

40

50

ゲート1930にも供給される)は、NORゲート1930の出力を、ハイからローに遷移させる。

【0109】

[0131]遅延回路1725の出力(oosc)が最初に、発振モードにおいて論理ゼロに変化すると、インバータ1925及びORゲート1935を介してリセット論理回路1915のリセット入力(rs)に論理1が入力される。これは、リセットすることと、第2のNANDゲート1920に論理1を出力することとをリセット論理回路1915に行わせる。リセット論理回路1915からの論理1は、カウンタ1910の入力(int)に遅延回路1725の出力(oosc)の逆数をパスすることを第2のNANDゲート1920に行わせる。

10

【0110】

[0132]発振器1720が発振すると、遅延回路1725の出力(oosc)における論理状態が変化する。出力論理状態の変化から変化までの時間は、第1のNANDゲート1740と遅延回路1725内の経路1712とを通る1トリップの遅延に略等しい。

【0111】

[0133]発振中、カウンタ1910は、カウント入力(int)がローからハイに上昇する度(即ち、NANDゲート1920の出力における各立ち上がりエッジ)にカウント値をインクリメントする。これは、信号が、第1のNANDゲート1740と遅延回路1725内の経路1712とを通るトリップを2回行う度に発生する。故に、この様では、カウンタ1910は、第1のNANDゲート1740と遅延回路1725内の経路1712とを通る2回のトリップの遅延の後にカウント値をインクリメントする。第1のNANDゲート1740と遅延回路1725内の経路1712とを通る遅延が $16.5 * t_d$ に等しい例の場合、カウンタ1910は、 $2 * 16.5 * t_d$ の遅延の後にカウント値をインクリメントする。

20

【0112】

[0134]カウント値が終カウント値(例えば、13カウント)に達すると、カウンタ1910は、NORゲート1930及び第1のNANDゲート1740の制御入力1745の両方に論理ゼロを出力(o\_int)する。第1のNANDゲート1740の制御入力175における論理ゼロは、第1のNANDゲート1740出力を、論理1で一定に保たせ、これは、発振器1720をディセーブルにする。第1のNANDゲート1740の出力における論理1は、遅延回路1725を通って伝播し、これは、第2のNANDゲート1920に論理1を出力(oosc)することを遅延回路1725に行わせる。これは、次に、NORゲート1930及びカウンタ1910の入力(int)の両方に論理ゼロを出力することを第2のNANDゲート1920に行わせる。結果として、NORゲート1930の両方の入力が論理ゼロとなり、これは、NORゲート1930の出力をローからハイに遷移させ、故に、第2の遅延段1750に立ち上がりエッジを出力することをNORゲート1930に行わせる。故に、第1の遅延段1710は、カウンタ1910が終カウント値に達した後、第2の遅延段1750に立ち上がりエッジを出力する。終カウント値が13であり、NANDゲート1740及び遅延回路1725を介する遅延が $16.5 * t_d$ である例の場合、Qパルスの立ち上がりエッジと、第2の遅延段1750に出力される立ち上がりエッジとの間の遅延は、 $13 * 2 * 16.5 * t_d$ に略等しい。

30

【0113】

[0135]上述したように、カウンタ入力(int)における各立ち上がりエッジでカウント値をインクリメントする代わりに、カウンタ1910が、各立ち上がりエッジでカウンタ値をデクリメントし得ることは認識されるべきである。このケースでは、カウンタ1910は、所定のカウント値からカウントを開始し、各立ち上がりエッジにおいてカウント値をデクリメントし、カウント値が終カウント値ゼロに達したとき第2のクロック遅延回路1710をトリガし得る。

40

【0114】

[0136]図20は、本開示の実施形態に係る、リセット論理回路1915の例示的な実装

50

形態を示す。リセット論理回路1915は、第1のANDゲート2010、第1のNORゲート2020、インバータ2030、第2のANDゲート2040、第2のNORゲート2050及び第3のNORゲート2060を備える。リセット論理回路1915のクロック入力（「c1k」と表される）は、第1のANDゲート2010の第1の入力と、第2のANDゲート2040の第1の入力とに結合される。第1のANDゲート2010の出力は、第1のNORゲート2020の第1の入力に結合され、リセット入力は、第1のNORゲート2020の第2の入力に結合される。第1のNORゲート2020の出力は、インバータ2030を通して第1のANDゲート2010の第2の入力にフィードバックされる。第1のNORゲート2020の出力はまた、第2のANDゲート2040の第2の入力に結合される。第2のANDゲート2040の出力は、第2のNORゲート2050の第1の入力に結合される。第2のNORゲート2050の出力は、第3のNORゲート2060の第1の入力に結合され、リセット入力は、第3のNORゲート2060の第2の入力に結合される。第3のNORゲート2060の出力は、第2のNORゲート2050の第2の入力に結合される。第2のNORゲート2050の出力は、リセット論理回路1915の出力（「yn」と表される）に結合される。

10

## 【0115】

[0137]リセット論理回路1915は、リセット入力(rst)に論理1を入力することでリセットされ得る。一度リセットされると、リセット論理回路1915は、立ち上がりエッジをクロック入力(c1k)において受けるまで、論理1を出力(yn)し得る。リセット論理回路1915が、第1の遅延段1710において使用されるとき、クロック入力(c1k)は、更新回路712のQ出力に結合され得、リセット論理回路1915が第2の遅延段1750において使用されると、クロック入力(c1k)は、第1の遅延段1710の出力に結合され得る。

20

## 【0116】

[0138]立ち上がりエッジがクロック入力(c1k)において受けられると、リセット論理回路1915の出力はローになる（即ち、リセット論理回路1915は、論理ゼロを出力する）。上述したように、これは、カウンティングを開始するように、カウント回路1730内のカウンタ1910をトリガし得る。リセット論理回路1915は、遅延回路1725の出力(oosc)がローになると、リセットされ得る。これは、第1の遅延回路1725の出力(oosc)が、インバータ1925を通してリセット論理回路1915のリセット入力(rst)に供給されるためである。リセット論理回路1915が第1の遅延段1710で使用されるとき、これは、次のQパルスの立ち上がりエッジのためにリセット論理回路1915をリセットする。

30

## 【0117】

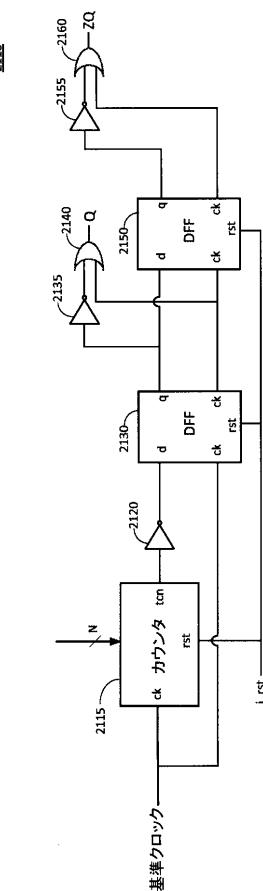

[0139]図21は、本開示の実施形態に係る、更新回路2110の例示的な実装形態を示す。更新回路2110は、図7及び16に示される更新回路712を実装するために使用され得る。更新回路2110は、入力基準クロックのN個の周期（サイクル）ごとに一対のパルスを出力するように構成される。パルスの各対は、低いQパルス及び低いZQパルス（これらの例は、図10に示される）を備え、ここでは、ZQパルスは、Qパルスに対して略1クロック周期ぶん遅延されている。

40

## 【0118】

[0140]更新コントローラ2110は、プログラマブルカウンタ2115、第1のインバータ2120、第1のDフリップフロップ2130、第2のDフリップフロップ2150、第2のインバータ2135、第1のORゲート2140、第3のインバータ2155、及び第2のORゲート2160を備える。カウンタ2115、第1のフリップフロップ2130及び第2のフリップフロップ2150は、図21に示されるように、初期リセット信号(irst)によってリセットされ得る。

## 【0119】

[0141]カウンタ2115は、更新コントローラ750からの制御信号Nと、基準クロックとを受ける。カウンタ2115は、基準クロックのN番目ごとの周期（サイクル）の間

50

ずっとその出力（「t c n」と表される）において論理ゼロを出力し、1より大きいNのN番目ごとの周期（サイクル）の間でその出力（t c n）において論理1を出力するよう構成される。

#### 【0120】

[0142]第1のフリップフロップ2130は、基準クロックに結合された（「c1k」と表される）クロック入力と、第1のインバータ2120を通してカウンタ2115の出力（t c n）に結合されたd入力と、q出力とを有する。第2のフリップフロップ2150は、基準クロックに結合された（「c1k」と表される）クロック入力と、第1のフリップフロップ2130のq出力に結合されたd入力と、q出力とを有する。フリップフロップ2130及び2150の両方が、正エッジトリガされたフリップフロップであり得、ここでは、各フリップフロップは、基準クロックの立ち上がりエッジ上でそれぞれのd入力において論理値をラッチし、そのラッチされた論理値を、略1クロック周期の間それぞれのq出力において出力する。10

#### 【0121】

[0143]第1のORゲート2140は、第2のインバータ2135を介して第1のフリップフロップ2130のq出力に結合された第1の入力と、基準クロックに結合された第2の入力とを有する。第1のORゲート2140の出力は、更新回路2110のQ出力を形成し得る。第2のORゲート2160は、第3のインバータ2155を通して第2のフリップフロップ2150のq出力に結合された第1の入力と、基準クロックに結合された第2の入力とを有する。第2のORゲート2160の出力は、更新回路2110のZ Q出力を形成し得る。20

#### 【0122】

[0144]更新回路2110の動作が、ここから、本開示の実施形態に従って説明されるだろう。

#### 【0123】

[0145]上述したように、カウンタ2115は、基準クロックのN番目ごとの周期（サイクル）の間ずっと論理ゼロを出力する。1クロック周期（サイクル）の間カウンタ2115が論理ゼロを出力する度に、第1のORゲート2140及び第2のORゲート2160は、それぞれ、低いQパルス及び低いZ Qパルスを出力し、ここでは、Z Qパルスは、Qパルスに対して略1クロック周期ぶん遅延されている。より具体的には、第1のインバータ2120は、カウンタ2115の出力（t c n）において論理ゼロを反転させ、第1のフリップフロップ2130のd入力に論理1を出力する。第1のフリップフロップ2130は、基準クロックの立ち上がりエッジ上で論理1をラッチし、そのラッチされた論理1を、1クロック周期の間にそのq出力において出力する。第2のインバータ2135は、第1のフリップフロップ2130のq出力において論理1を反転させ、第1のORゲート2140の第1の入力に論理ゼロを出力する。これは、低いQパルスを生成するために、1クロック周期の間基準クロックをQ出力にパスすることを第1のORゲート2140に行わせる。30

#### 【0124】

[0146]第2のフリップフロップ2150は、1クロック周期の遅延の後、第1のフロップ2130のq出力において論理1をラッチし、このラッチされた論理1を1クロック周期の間出力する。第3のインバータ2155は、第2のフリップフロップ2150のq出力において論理1を反転させ、第2のORゲート2160の第1の入力に論理ゼロを出力する。これは、低いZ Qパルスを生成するために、1クロック周期の間Z Q出力に基準クロックをパスすることを第2のORゲート2160に行わせる。第2のフリップフロップ2150のq出力が、第1のフリップフロップ2130のq出力に対して1クロック周期ぶん遅延されているため、Z Qパルスは、Qパルスに対して1クロック周期ぶん遅延されている。

#### 【0125】

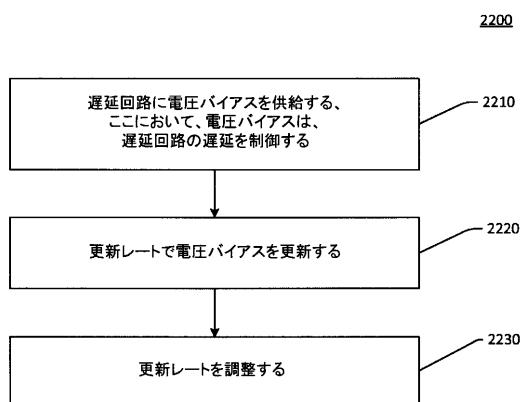

[0147]図22は、本開示の実施形態に係る、遅延制御のための方法2200を例示する

10

20

30

40

50

フロー図2200である。方法2200は、マスタ遅延回路1610及び更新コントローラ750によって実行され得る。

【0126】

[0148]ステップ2210において、電圧バイアスは、遅延回路に供給され、ここにおいて、電圧バイアスは、遅延回路の遅延を制御する。例えば、マスタ遅延回路（例えば、マスタ遅延回路1610）は、スレーブ遅延回路（例えば、スレーブ遅延回路1315）のステップ遅延を制御するために、このスレーブ遅延回路に電圧バイアスを供給し得る。

【0127】

[0149]ステップ2220において、電圧バイアスは、更新レートで更新される。例えば、電圧バイアスは、基準クロックのN個の周期（サイクル）あたり1回という更新のレートで調整され得る。

10

【0128】

[0150]ステップ2230において、更新レートが調整される。例えば、更新レートは、遅延回路を組み込んでいるメモリインターフェースのタイミング要件に基づいて調整され得る。この例では、更新レートは、タイミング要件がより緩和される（例えば、より低いデータレートである）とき、低減され得、タイミング要件がより厳しい（例えば、より高いデータレートである）とき、増加され得る。

【0129】

[0151]方法は、オプション的に、遅延回路によって遅延されている信号のデータレートに基づいて更新レートを調整すること含み得る。例えば、更新レートは、信号のデータレートが第1のデータレートに略等しい場合、第1の更新レートに設定され、更新レートは、信号のデータレートが第2のデータレートに略等しい場合、第2の更新レートに設定され得、ここにおいて、第1のデータレートは、第2のデータレートよりも低く、第1の更新レートは、第2の更新レートよりも低い。

20

【0130】

[0152]方法は、オプション的に、遅延回路に第2の電圧バイアス（例えば、電圧バイアスV<sub>b</sub>p）を供給することと、更新レートで第2の電圧バイアスを更新することとを含み得る。第2の電圧バイアスはまた、遅延回路の遅延を制御し得る。

【0131】

[0153]更新コントローラ750が、汎用プロセッサ、デジタルシグナルプロセッサ（DSP）、特定用途向け集積回路（ASIC）、フィールドプログラマブルゲートアレイ（FPGA）又は他のプログラマブル論理デバイス、ディスクリートゲート又はトランジスタ論理、ディスクリートハードウェア構成要素若しくは本明細書で説明された機能を実行するよう設計されたそれらの任意の組み合わせで実装され得ることは認識されるべきである。汎用プロセッサは、マイクロプロセッサであり得るが、代替的に、プロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ又はステートマシンであり得る。プロセッサは、本明細書で説明された更新コントローラ750の機能を実行するためのコードを備えるソフトウェアを実行することで、これらの機能を実行し得る。ソフトウェアは、RAM、ROM、EEPROM（登録商標），光ディスク及び/又は磁気ディスクのようなコンピュータ可読記憶媒体上に記憶され得る。

30

【0132】

[0154]本開示の以上の説明は、当業者が本開示を実施又は使用することを可能にするために提供される。本開示に対する様々な修正は当業者には容易に明らかであり、本明細書で定義された包括的な原理は、本開示の精神又は範囲から逸脱することなく、他の変形に適用され得る。例えば、本開示の実施形態はDRAMの例を使用して上述されているが、本開示の実施形態が、この例に制限されず、他のタイプのメモリデバイスで使用され得ることは認識されるべきである。故に、本開示は、本明細書で説明された例及び設計に制限されることを意図せず、本明細書に開示された原理及び新規な特徴に合致する最も広い範囲が与えられるべきである。

40

【 図 1 】

【 図 2 】

图 1

FIG. 1

図 2

FIG. 2

【図3】

【 図 4 】

图 3

FIG. 3

FIG. 4

【 义 5 】

图 5

【 図 6 】

図 6

【 図 7 】

図 7

【 図 8 】

8

FIG. 8

FIG. 8

FIG. 6

【図 9】

図 9

FIG. 9

【図 10】

図 10

FIG. 10

【図 11】

図 11

FIG. 11

【図 12】

図 12

FIG. 12

【図 1 3】

図 13

FIG. 13

【図 1 4 A】

図 14A

FIG. 14A

【図 1 4 B】

図 14B

【図 1 5】

FIG. 14B

FIG. 15

【 図 1 6 】

図 16

FIG. 16

【 図 1 8 】

18

EIG 18

【図19】

図 19

FIG. 19

FIG. 17

【 図 2 0 】

FIG. 20

【 図 2 1 】

图 21

FIG. 21

## 【図22】

図 22

FIG. 22

**【手続補正書】**

【提出日】平成29年2月14日(2017.2.14)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】**

【特許請求の範囲】

**【請求項1】**

遅延システムであって、

第2の遅延回路に電圧バイアスを供給し、更新レートで前記電圧バイアスを更新するよう構成された第1の遅延回路と、ここにおいて、前記電圧バイアスは、前記第2の遅延回路の遅延を制御する、

前記第2の遅延回路によって遅延されている信号のデータレートに基づいて、前記第1の遅延回路の前記更新レートを調整するよう構成された更新コントローラとを備える遅延システム。

**【請求項2】**

前記更新コントローラは、前記信号の前記データレートが第1のデータレートに略等しい場合、前記更新レートを第1の更新レートに設定し、前記信号の前記データレートが第2のデータレートに略等しい場合、前記更新レートを第2の更新レートに設定するよう構成され、前記第1のデータレートは、前記第2のデータレートよりも低く、前記第1の更新レートは、前記第2の更新レートよりも低い、請求項1に記載の遅延システム。

**【請求項3】**

前記第1の遅延回路は、基準クロックに基づいて前記電圧バイアスを更新するよう構成され、ここで、前記更新レートは、前記基準クロックのN個の周期あたり1回の前記電圧バイアスの更新に略等しく、Nは整数であり、前記更新コントローラは、Nを調整するよう構成される、請求項1に記載の遅延システム。

**【請求項4】**

前記更新コントローラは、前記信号の前記データレートが第1のデータレートに略等しい場合、Nを第1の値に設定し、前記信号の前記データレートが第2のデータレートに略等しい場合、Nを第2の値に設定するよう構成され、前記第1のデータレートは、前記第2のデータレートよりも低く、Nの前記第1の値は、Nの前記第2の値よりも大きい、請求項3に記載の遅延システム。

**【請求項5】**

前記第1の遅延回路は、

前記電圧バイアスの更新ごとに、基準クロックからパルス対を生成するよう構成された更新回路と、ここにおいて、各パルス対は、第1のパルス及び第2のパルスを備え、前記第1のパルスは、前記第2のパルスに対して前記基準クロックの略1周期ぶん遅延されている、

各パルス対の前記第2のパルスを前記電圧バイアスによって制御された量ぶん遅延するよう構成された電圧制御型遅延回路と、

パルス対ごとに、それぞれの前記第1のパルスとそれぞれの遅延された前記第2のパルスとの間の位相誤差を検出するよう構成された位相周波数検出器と、

それぞれの検出された前記位相誤差に基づいて、パルス対ごとに前記電圧バイアスを更新するよう構成された電圧バイアスコントローラと

を備える、請求項1に記載の遅延システム。

**【請求項6】**

前記更新回路は、前記基準クロックのN個の周期あたり1つのパルス対というレートで前記パルス対を生成するよう構成され、Nは整数であり、前記更新コントローラは、Nを調整するよう構成される、請求項5に記載の遅延システム。

**【請求項 7】**

前記更新コントローラは、前記信号の前記データレートが第1のデータレートに略等しい場合、Nを第1の値に設定し、前記信号の前記データレートが第2のデータレートに略等しい場合、Nを第2の値に設定するように構成され、前記第1のデータレートは、前記第2のデータレートよりも低く、Nの前記第1の値は、Nの前記第2の値よりも大きい、請求項6に記載の遅延システム。

**【請求項 8】**

前記電圧バイアスによって制御される前記第2の遅延回路の前記遅延は、前記第2の遅延回路のステップ遅延であり、前記第2の遅延回路は、信号を前記ステップ遅延の倍数ぶん遅延させるように構成される、請求項1に記載の遅延システム。

**【請求項 9】**

遅延制御のための方法であって、

遅延回路に電圧バイアスを供給することと、ここにおいて、前記電圧バイアスは、前記遅延回路の遅延を制御する、

更新レートで前記電圧バイアスを更新することと、

前記遅延回路によって遅延されている信号のデータレートに基づいて、前記更新レートを調整することと

を備える方法。

**【請求項 10】**

前記更新レートを調整することは、

前記信号の前記データレートが第1のデータレートに略等しい場合、前記更新レートを第1の更新レートに設定することと、

前記信号の前記データレートが第2のデータレートに略等しい場合、前記更新レートを第2の更新レートに設定することと

を備え、

前記第1のデータレートは、前記第2のデータレートよりも低く、前記第1の更新レートは、前記第2の更新レートよりも低い、

請求項9に記載の方法。

**【請求項 11】**

前記電圧バイアスを更新することは、基準クロックに基づいて前記電圧バイアスを更新することを備え、ここで、前記更新レートは、前記基準クロックのN個の周期あたり1回の前記電圧バイアスの更新に略等しく、Nは整数であり、前記更新レートを調整することは、Nを調整することを備える、請求項9に記載の方法。

**【請求項 12】**

前記更新レートを調整することは、

前記信号の前記データレートが第1のデータレートに略等しい場合、Nを第1の値に設定することと

前記信号の前記データレートが第2のデータレートに略等しい場合、Nを第2の値に設定することと

を備え、

前記第1のデータレートは、前記第2のデータレートよりも低く、Nの前記第1の値は、Nの前記第2の値よりも大きい、

請求項11に記載の方法。

**【請求項 13】**

前記電圧バイアスを更新することは、

前記電圧バイアスの更新ごとに、基準クロックからパルス対を生成することと、ここにおいて、各パルス対は、第1のパルス及び第2のパルスを備え、前記第1のパルスは、前記第2のパルスに対して前記基準クロックの略1周期ぶん遅延されている、

各パルス対の前記第2のパルスを前記電圧バイアスによって制御された量ぶん遅延させることと、

パルス対ごとに、それぞれの前記第1のパルスとそれぞれの遅延された前記第2のパルスとの間の位相誤差を検出することと、

それぞれの検出された前記位相誤差に基づいて、パルス対ごとに前記電圧バイアスを更新することと

を備える、請求項9に記載の方法。

【請求項14】

前記遅延回路に第2の電圧バイアスを供給することと、ここにおいて、前記第2の電圧バイアスはまた、前記遅延回路の前記遅延を制御する、

前記更新レートで前記第2の電圧バイアスを更新することと

を更に備える、請求項9に記載の方法。

【請求項15】

遅延制御のための装置であって、

遅延回路に電圧バイアスを供給するための手段と、ここにおいて、前記電圧バイアスは、前記遅延回路の遅延を制御する、

更新レートで前記電圧バイアスを更新するための手段と、

前記遅延回路によって遅延されている信号のデータレートに基づいて、前記更新レート

を調整するための手段と

を備える装置。

【請求項16】

前記更新レートを調整するための前記手段は、

前記信号の前記データレートが第1のデータレートに略等しい場合、前記更新レートを第1の更新レートに設定するための手段と、

前記信号の前記データレートが第2のデータレートに略等しい場合、前記更新レートを第2の更新レートに設定するための手段と

を備え、

前記第1のデータレートは、前記第2のデータレートよりも低く、前記第1の更新レートは、前記第2の更新レートよりも低い、

請求項15に記載の装置。

【請求項17】

前記電圧バイアスを更新するための前記手段は、基準クロックに基づいて前記電圧バイアスを更新するための手段を備え、ここで、前記更新レートは、前記基準クロックのN個の周期あたり1回の前記電圧バイアスの更新に略等しく、Nは整数であり、前記更新レートを調整するための前記手段は、Nを調整するための手段を備える、請求項15に記載の装置。

【請求項18】

前記更新レートを調整するための前記手段は、

前記信号の前記データレートが第1のデータレートに略等しい場合、Nを第1の値に設定するための手段と、

前記信号の前記データレートが第2のデータレートに略等しい場合、Nを第2の値に設定するための手段と

を備え、

前記第1のデータレートは、前記第2のデータレートよりも低く、Nの前記第1の値は、Nの前記第2の値よりも大きい、

請求項17に記載の装置。

【請求項19】

前記電圧バイアスを更新するための前記手段は、

前記電圧バイアスの更新ごとに、基準クロックからパルス対を生成するための手段と、ここにおいて、各パルス対は、第1のパルス及び第2のパルスを備え、前記第1のパルスは、前記第2のパルスに対して前記基準クロックの略1周期ぶん遅延されている、

各パルス対の前記第2のパルスを前記電圧バイアスによって制御された量ぶん遅延させ

るための手段と、

パルス対ごとに、それぞれの前記第1のパルスとそれぞれの遅延された前記第2のパルスとの間の位相誤差を検出するための手段と、

それぞれの検出された前記位相誤差に基づいて、パルス対ごとに前記電圧バイアスを更新するための手段と

を備える、請求項1 5に記載の装置。

#### 【請求項20】

前記遅延回路に第2の電圧バイアスを供給するための手段と、ここにおいて、前記第2の電圧バイアスはまた、前記遅延回路の前記遅延を制御する、

前記更新レートで前記第2の電圧バイアスを更新するための手段と

を更に備える、請求項1 5に記載の装置。

#### 【請求項21】

メモリインターフェースであって、

信号を遅延するように構成された第1の遅延回路と、ここにおいて、前記信号は、データ信号及びデータストローブ信号のうちの1つを備える、

前記第1の遅延回路に電圧バイアスを供給し、更新レートで前記電圧バイアスを更新するように構成された第2の遅延回路と、ここにおいて、前記電圧バイアスは、前記第1の遅延回路の遅延を制御する、

前記信号のデータレートに基づいて、前記第2の遅延回路の前記更新レートを調整するように構成された更新コントローラと

を備えるメモリインターフェース。

#### 【請求項22】

前記更新コントローラは、前記信号の前記データレートが第1のデータレートに略等しい場合、前記更新レートを第1の更新レートに設定し、前記信号の前記データレートが第2のデータレートに略等しい場合、前記更新レートを第2の更新レートに設定するように構成され、前記第1のデータレートは、前記第2のデータレートよりも低く、前記第1の更新レートは、前記第2の更新レートよりも低い、請求項2 1に記載のメモリインターフェース。

#### 【請求項23】

前記第2の遅延回路は、基準クロックに基づいて前記電圧バイアスを更新するように構成され、ここで、前記更新レートは、前記基準クロックのN個の周期あたり1回の前記電圧バイアスの更新に略等しく、Nは整数であり、前記更新コントローラは、Nを調整するように構成される、請求項2 1に記載のメモリインターフェース。

#### 【請求項24】

前記更新コントローラは、前記信号の前記データレートが第1のデータレートに略等しい場合、Nを第1の値に設定し、前記信号の前記データレートが第2のデータレートに略等しい場合、Nを第2の値に設定するように構成され、前記第1のデータレートは、前記第2のデータレートよりも低く、Nの前記第1の値は、Nの前記第2の値よりも大きい、請求項2 3に記載のメモリインターフェース。

#### 【請求項25】

前記第2の遅延回路は、

前記電圧バイアスの更新ごとに、基準クロックからパルス対を生成するように構成された更新回路と、ここにおいて、各パルス対は、第1のパルス及び第2のパルスを備え、前記第1のパルスは、前記第2のパルスに対して前記基準クロックの略1周期ぶん遅延されている、

各パルス対の前記第2のパルスを前記電圧バイアスによって制御された量ぶん遅延させるように構成された電圧制御型遅延回路と、

パルス対ごとに、それぞれの前記第1のパルスとそれぞれの遅延された前記第2のパルスとの間の位相誤差を検出するように構成された位相周波数検出器と、

それぞれの検出された前記位相誤差に基づいて、パルス対ごとに前記電圧バイアスを更

新するように構成された電圧バイアスコントローラと

を備える、請求項21に記載のメモリインターフェース。

【請求項26】

前記電圧バイアスによって制御される前記第1の遅延回路の前記遅延は、前記第1の遅延回路のステップ遅延であり、前記第1の遅延回路は、前記信号を前記ステップ遅延の倍数ぶん遅延させるように構成される、請求項21に記載のメモリインターフェース。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0132

【補正方法】変更

【補正の内容】

【0132】

[0154]本開示の以上の説明は、当業者が本開示を実施又は使用することを可能にするために提供される。本開示に対する様々な修正は当業者には容易に明らかであり、本明細書で定義された包括的な原理は、本開示の精神又は範囲から逸脱することなく、他の変形に適用され得る。例えば、本開示の実施形態はDRAMの例を使用して上述されているが、本開示の実施形態が、この例に制限されず、他のタイプのメモリデバイスで使用され得ることは認識されるべきである。故に、本開示は、本明細書で説明された例及び設計に制限されることを意図せず、本明細書に開示された原理及び新規な特徴に合致する最も広い範囲が与えられるべきである。

以下に本願発明の当初の特許請求の範囲に記載された発明を付記する。

[C1]

遅延システムであって、

第2の遅延回路に電圧バイアスを供給し、更新レートで前記電圧バイアスを更新するように構成された第1の遅延回路と、ここにおいて、前記電圧バイアスは、前記第2の遅延回路の遅延を制御する、

前記第1の遅延回路の前記更新レートを調整するように構成された更新コントローラとを備える遅延システム。

[C2]

前記更新コントローラは、前記第2の遅延回路によって遅延されている信号のデータレートに基づいて前記更新レートを調整するように構成される、

C1に記載の遅延システム。

[C3]

前記更新コントローラは、前記信号の前記データレートが第1のデータレートに略等しい場合、前記更新レートを第1の更新レートに設定し、前記信号の前記データレートが第2のデータレートに略等しい場合、前記更新レートを第2の更新レートに設定するように構成され、前記第1のデータレートは、前記第2のデータレートよりも低く、前記第1の更新レートは、前記第2の更新レートよりも低い、C2に記載の遅延システム。

[C4]

前記第1の遅延回路は、基準クロックに基づいて前記電圧バイアスを更新するように構成され、ここで、前記更新レートは、前記基準クロックのN個の周期あたり1回の前記電圧バイアスの更新に略等しく、Nは整数であり、前記更新コントローラは、Nを調整するように構成される、C1に記載の遅延システム。

[C5]

前記更新コントローラは、前記第2の遅延回路によって遅延されている信号のデータレートが第1のデータレートに略等しい場合、Nを第1の値に設定し、前記信号の前記データレートが第2のデータレートに略等しい場合、Nを第2の値に設定するように構成され、前記第1のデータレートは、前記第2のデータレートよりも低く、Nの前記第1の値は、Nの前記第2の値よりも大きい、C4に記載の遅延システム。

[C6]

前記第1の遅延回路は、

前記電圧バイアスの更新ごとに、基準クロックからパルス対を生成するように構成された更新回路と、ここにおいて、各パルス対は、第1のパルス及び第2のパルスを備え、前記第1のパルスは、前記第2のパルスに対して前記基準クロックの略1周期ぶん遅延されている、

各パルス対の前記第2のパルスを前記電圧バイアスによって制御された量ぶん遅延させるように構成された電圧制御型遅延回路と、

パルス対ごとに、それぞれの前記第1のパルスとそれぞれの遅延された前記第2のパルスとの間の位相誤差を検出するように構成された位相周波数検出器と、

それぞれの検出された前記位相誤差に基づいて、パルス対ごとに前記電圧バイアスを更新するように構成された電圧バイアスコントローラと

を備える、C1に記載の遅延システム。

[C7]

前記更新回路は、前記基準クロックのN個の周期あたり1つのパルス対というレートで前記パルス対を生成するように構成され、Nは整数であり、前記更新コントローラは、Nを調整するように構成される、C6に記載の遅延システム。

[C8]

前記更新コントローラは、前記第2の遅延回路によって遅延されている信号のデータレートが第1のデータレートに略等しい場合、Nを第1の値に設定し、前記信号の前記データレートが第2のデータレートに略等しい場合、Nを第2の値に設定するように構成され、前記第1のデータレートは、前記第2のデータレートよりも低く、Nの前記第1の値は、Nの前記第2の値よりも大きい、C7に記載の遅延システム。

[C9]

前記電圧バイアスによって制御される前記第2の遅延回路の前記遅延は、前記第2の遅延回路のステップ遅延であり、前記第2の遅延回路は、信号を前記ステップ遅延の倍数ぶん遅延させるように構成される、C1に記載の遅延システム。

[C10]

遅延制御のための方法であって、

遅延回路に電圧バイアスを供給することと、ここにおいて、前記電圧バイアスは、前記遅延回路の遅延を制御する、

更新レートで前記電圧バイアスを更新することと、

前記更新レートを調整することと

を備える方法。

[C11]

前記更新レートを調整することは、前記遅延回路によって遅延されている信号のデータレートに基づいて前記更新レートを調整することを備える、C10に記載の方法。

[C12]

前記更新レートを調整することは、

前記信号の前記データレートが第1のデータレートに略等しい場合、前記更新レートを第1の更新レートに設定することと、

前記信号の前記データレートが第2のデータレートに略等しい場合、前記更新レートを第2の更新レートに設定することと

を備え、

前記第1のデータレートは、前記第2のデータレートよりも低く、前記第1の更新レートは、前記第2の更新レートよりも低い、

C11に記載の方法。

[C13]

前記電圧バイアスを更新することは、基準クロックに基づいて前記電圧バイアスを更新することを備え、ここで、前記更新レートは、前記基準クロックのN個のあたり1回の前記電圧バイアスの更新に略等しく、Nは整数であり、前記更新レートを調整することは、

Nを調整することを備える、C 1 0に記載の方法。

[ C 1 4 ]

前記更新レートを調整することは、

前記遅延回路によって遅延されている信号のデータレートが第1のデータレートに略等しい場合、Nを第1の値に設定することと

前記信号の前記データレートが第2のデータレートに略等しい場合、Nを第2の値に設定することと

を備え、

前記第1のデータレートは、前記第2のデータレートよりも低く、Nの前記第1の値は、Nの前記第2の値よりも大きい、

C 1 3に記載の方法。

[ C 1 5 ]

前記電圧バイアスを更新することは、

前記電圧バイアスの更新ごとに、基準クロックからパルス対を生成することと、ここにおいて、各パルス対は、第1のパルス及び第2のパルスを備え、前記第1のパルスは、前記第2のパルスに対して前記基準クロックの略1周期ぶん遅延されている、

各パルス対の前記第2のパルスを前記電圧バイアスによって制御された量ぶん遅延させることと、

パルス対ごとに、それぞれの前記第1のパルスとそれぞれの遅延された前記第2のパルスとの間の位相誤差を検出することと、

それぞれの検出された前記位相誤差に基づいて、パルス対ごとに前記電圧バイアスを更新することと

を備える、C 1 0に記載の方法。

[ C 1 6 ]

前記遅延回路に第2の電圧バイアスを供給することと、ここにおいて、前記第2の電圧バイアスはまた、前記遅延回路の前記遅延を制御する、

前記更新レートで前記第2の電圧バイアスを更新することと

を更に備える、C 1 0に記載の方法。

[ C 1 7 ]

遅延制御のための装置であって、

遅延回路に電圧バイアスを供給するための手段と、ここにおいて、前記電圧バイアスは、前記遅延回路の遅延を制御する、

更新レートで前記電圧バイアスを更新するための手段と、

前記更新レートを調整するための手段と

を備える装置。

[ C 1 8 ]

前記更新レートを調整するための前記手段は、前記遅延回路によって遅延されている信号のデータレートに基づいて前記更新レートを調整するための手段を備える、C 1 7に記載の装置。

[ C 1 9 ]

前記更新レートを調整するための前記手段は、

前記信号の前記データレートが第1のデータレートに略等しい場合、前記更新レートを第1の更新レートに設定するための手段と、

前記信号の前記データレートが第2のデータレートに略等しい場合、前記更新レートを第2の更新レートに設定するための手段と

を備え、

前記第1のデータレートは、前記第2のデータレートよりも低く、前記第1の更新レートは、前記第2の更新レートよりも低い、

C 1 8に記載の装置。

[ C 2 0 ]

前記電圧バイアスを更新するための前記手段は、基準クロックに基づいて前記電圧バイアスを更新するための手段を備え、ここで、前記更新レートは、前記基準クロックのN個の周期あたり1回の前記電圧バイアスの更新に略等しく、Nは整数であり、前記更新レートを調整するための前記手段は、Nを調整するための手段を備える、C17に記載の装置。

[ C 2 1 ]

前記更新レートを調整するための前記手段は、

前記遅延回路によって遅延されている信号のデータレートが第1のデータレートに略等しい場合、Nを第1の値に設定するための手段と、

前記信号の前記データレートが第2のデータレートに略等しい場合、Nを第2の値に設定するための手段と

を備え、

前記第1のデータレートは、前記第2のデータレートよりも低く、Nの前記第1の値は、Nの前記第2の値よりも大きい、

C20に記載の装置。

[ C 2 2 ]

前記電圧バイアスを更新するための前記手段は、

前記電圧バイアスの更新ごとに、基準クロックからパルス対を生成するための手段と、

ここにおいて、各パルス対は、第1のパルス及び第2のパルスを備え、前記第1のパルスは、前記第2のパルスに対して前記基準クロックの略1周期ぶん遅延されている、

各パルス対の前記第2のパルスを前記電圧バイアスによって制御された量ぶん遅延させるための手段と、

パルス対ごとに、それぞれの前記第1のパルスとそれぞれの遅延された前記第2のパルスとの間の位相誤差を検出するための手段と、

それぞれの検出された前記位相誤差に基づいて、パルス対ごとに前記電圧バイアスを更新するための手段と

を備える、C17に記載の装置。

[ C 2 3 ]

前記遅延回路に第2の電圧バイアスを供給するための手段と、ここにおいて、前記第2の電圧バイアスはまた、前記遅延回路の前記遅延を制御する、

前記更新レートで前記第2の電圧バイアスを更新するための手段と

を更に備える、C17に記載の装置。

[ C 2 4 ]

メモリインターフェースであって、

信号を遅延するように構成された第1の遅延回路と、ここにおいて、前記信号は、データ信号及びデータストローブ信号のうちの1つを備える、

前記第1の遅延回路に電圧バイアスを供給し、更新レートで前記電圧バイアスを更新するように構成された第2の遅延回路と、ここにおいて、前記電圧バイアスは、前記第1の遅延回路の遅延を制御する、

前記第2の遅延回路の前記更新レートを調整するように構成された更新コントローラと

を備えるメモリインターフェース。

[ C 2 5 ]

前記更新コントローラは、前記信号のデータレートに基づいて前記更新レートを調整するように構成される、

C24に記載のメモリインターフェース。

[ C 2 6 ]

前記更新コントローラは、前記信号の前記データレートが第1のデータレートに略等しい場合、前記更新レートを第1の更新レートに設定し、前記信号の前記データレートが第2のデータレートに略等しい場合、前記更新レートを第2の更新レートに設定するように構成され、前記第1のデータレートは、前記第2のデータレートよりも低く、前記第1の

更新レートは、前記第2の更新レートよりも低い、C 2 5に記載のメモリインターフェース。

[ C 2 7 ]

前記第2の遅延回路は、基準クロックに基づいて前記電圧バイアスを更新するように構成され、ここで、前記更新レートは、前記基準クロックのN個の周期あたり1回の前記電圧バイアスの更新に略等しく、Nは整数であり、前記更新コントローラは、Nを調整するように構成される、C 2 4に記載のメモリインターフェース。

[ C 2 8 ]

前記更新コントローラは、前記信号のデータレートが第1のデータレートに略等しい場合、Nを第1の値に設定し、前記信号の前記データレートが第2のデータレートに略等しい場合、Nを第2の値に設定するように構成され、前記第1のデータレートは、前記第2のデータレートよりも低く、Nの前記第1の値は、Nの前記第2の値よりも大きい、C 2 7に記載のメモリインターフェース。

[ C 2 9 ]

前記第2の遅延回路は、前記電圧バイアスの更新ごとに、基準クロックからパルス対を生成するように構成された更新回路と、ここにおいて、各パルス対は、第1のパルス及び第2のパルスを備え、前記第1のパルスは、前記第2のパルスに対して前記基準クロックの略1周期ぶん遅延されている、

各パルス対の前記第2のパルスを前記電圧バイアスによって制御された量ぶん遅延させるように構成された電圧制御型遅延回路と、

パルス対ごとに、それぞれの前記第1のパルスとそれぞれの遅延された前記第2のパルスとの間の位相誤差を検出するように構成された位相周波数検出器と、

それぞれの検出された前記位相誤差に基づいて、パルス対ごとに前記電圧バイアスを更新するように構成された電圧バイアスコントローラと

を備える、C 2 4に記載のメモリインターフェース。

[ C 3 0 ]

前記電圧バイアスによって制御される前記第1の遅延回路の前記遅延は、前記第1の遅延回路のステップ遅延であり、前記第1の遅延回路は、前記信号を前記ステップ遅延の倍数ぶん遅延させるように構成される、C 2 4に記載のメモリインターフェース。

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                         | International application No<br>PCT/US2015/030214                    |           |                                                                                    |                       |   |                                                                                                                   |      |   |                                                                                                                                         |                                                           |   |                                                                                                                                       |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------|-----------------------|---|-------------------------------------------------------------------------------------------------------------------|------|---|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------|------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>INV. G11C7/10 G11C7/22 H03L7/08 H03L7/081<br>ADD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                         |                                                                      |           |                                                                                    |                       |   |                                                                                                                   |      |   |                                                                                                                                         |                                                           |   |                                                                                                                                       |      |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                         |                                                                      |           |                                                                                    |                       |   |                                                                                                                   |      |   |                                                                                                                                         |                                                           |   |                                                                                                                                       |      |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>G11C H03L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                         |                                                                      |           |                                                                                    |                       |   |                                                                                                                   |      |   |                                                                                                                                         |                                                           |   |                                                                                                                                       |      |