(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4598955号

(P4598955)

(45) 発行日 平成22年12月15日(2010.12.15)

(24) 登録日 平成22年10月1日(2010.10.1)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 21/8234 | (2006.01) | HO1L 27/08 | 102E |

| HO1L 27/088  | (2006.01) | HO1L 27/00 | 301A |

| HO1L 27/00   | (2006.01) | HO1L 29/78 | 613Z |

| HO1L 29/786  | (2006.01) | HO1L 29/44 | Z    |

| HO1L 29/41   | (2006.01) |            |      |

請求項の数 21 (全 12 頁)

(21) 出願番号 特願2000-585933 (P2000-585933)

(86) (22) 出願日 平成11年8月9日(1999.8.9)

(65) 公表番号 特表2002-531949 (P2002-531949A)

(43) 公表日 平成14年9月24日(2002.9.24)

(86) 國際出願番号 PCT/US1999/018038

(87) 國際公開番号 WO2000/033381

(87) 國際公開日 平成12年6月8日(2000.6.8)

審査請求日 平成18年6月30日(2006.6.30)

(31) 優先権主張番号 09/201,995

(32) 優先日 平成10年12月1日(1998.12.1)

(33) 優先権主張国 米国(US)

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVI

CES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンディベイル、ビイ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・プレイス、メイル・ストップ

・68 (番地なし)

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

最終頁に続く

(54) 【発明の名称】 2組の活性領域の間で共用されるゲート電極を有する半導体デバイス

## (57) 【特許請求の範囲】

## 【請求項1】

半導体デバイスであって、

第1の基板と、

第1の基板の上に配されるゲート電極と、

ゲート電極の上に配される第2の基板と、

第1の基板の部分にゲート電極に近接して配される第1の組の活性領域と、

ゲート電極の上に第2の基板に近接して配される第2の組の活性領域とを含み、第2の組の各活性領域は、その第2の組の各活性領域の下にあるスペーサの幅に等しい幅を有し、さらに

10

第2の基板の上に第2の組の活性領域の間に配される第1の絶縁層と、

第2の組の活性領域の各々に近接しあつ接触して配される第2の絶縁層とを含み、第2の絶縁層は対応する各スペーサ部材にも近接しあつ接触して配される、半導体デバイス。

## 【請求項2】

第2の基板層は、第2の基板層の底部の近くに電圧閾値領域を含む、請求項1に記載の半導体デバイス。

## 【請求項3】

第2の基板層は、電圧閾値領域の上にパンチスルーフィールドを含む、請求項2に記載の半導体デバイス。

## 【請求項4】

20

第 2 の組の活性領域の下のゲート電極の側壁に配されるスペーサをさらに含む、請求項 1 に記載の半導体デバイス。

【請求項 5】

第 1 および第 2 の組の活性領域はともにつながれる、請求項 1 に記載の半導体デバイス。

【請求項 6】

ゲート電極および第 1 の組の活性領域は第 1 の導電型のトランジスタを形成し、ゲート電極および第 2 の組の活性領域は異なる導電型のトランジスタを形成する、請求項 1 に記載の半導体。

【請求項 7】

ゲート電極および第 1 の組の活性領域は第 1 の導電型のトランジスタを形成し、ゲート電極および第 2 の組の活性領域は同じ導電型のトランジスタを形成する、請求項 1 に記載の半導体デバイス。

【請求項 8】

第 2 の組の活性領域の各々は、第 1 の絶縁層とともに、上部面の 1 つの平面を含む、請求項 1 に記載の半導体デバイス。

【請求項 9】

第 2 の絶縁層は、第 1 の絶縁層の上部面および第 2 の組の活性領域の上部面とともに、上部面の 1 つの平面を含む、請求項 8 に記載の半導体デバイス。

【請求項 10】

スペーサは、第 1 および第 2 の絶縁層に対して選択的にエッチング可能な材料から形成される、請求項 1 に記載の半導体デバイス。

【請求項 11】

第 1 の絶縁層に、第 1 および第 2 の組の活性領域の 1 つ以上と接触して配される 1 つ以上の接触をさらに含む、請求項 1 に記載の半導体デバイス。

【請求項 12】

第 2 の絶縁層および第 2 の基板を通ってゲート電極と接触して延在する接触をさらに含む、請求項 1 に記載の半導体デバイス。

【請求項 13】

接触と第 2 の基板との間に配される絶縁体をさらに含む、請求項 12 に記載の半導体デバイス。

【請求項 14】

絶縁体は窒化物から形成される、請求項 13 に記載の半導体デバイス。

【請求項 15】

ゲート電極と第 1 の基板との間に配される第 1 のゲート絶縁層、およびゲート電極と第 2 の基板との間に配される第 2 のゲート絶縁層をさらに含む、請求項 1 に記載の半導体デバイス。

【請求項 16】

第 2 の組の各々の活性領域は、下にあるスペーサの上に、第 2 のゲート絶縁層とゲート電極との間の界面に隣接した底部面を含む、請求項 15 に記載の半導体デバイス。

【請求項 17】

半導体デバイスであって、

第 1 の基板と、

第 1 の基板の上に配される積み重ねとを含み、前記積み重ねは、

第 1 の基板の上に配される第 1 のゲート絶縁層と、

第 1 のゲート絶縁層の上に配されるゲート電極と、

ゲート電極の上に配される第 2 のゲート絶縁層と、

第 2 のゲート絶縁層の上に配される第 2 の基板とを含み、前記半導体デバイスは、さらに、

積み重ねの側壁に配されるスペーサを含み、各々のスペーサはゲート電極の上に上部面

10

20

30

40

50

を有し、前記半導体デバイスは、さらに、

第1の基板の部分にゲート電極に近接して配される第1の組の活性領域と、

スペーサの上に第2の基板に近接して配される第2の組の活性領域とを含み、第2の組の各々の活性領域の幅は下にあるスペーサの1つの幅と同じであり、前記半導体デバイスは、さらに、

第2の基板の上に第2の組の活性領域の間に配される第1の絶縁層と、

第2の組の活性領域の各々に近接して、第2の組の活性領域の各々と接触して配される第2の絶縁層とを含み、第2の絶縁層は、さらに、スペーサの少なくとも1つに近接して、スペーサの少なくとも1つと接触して配される、半導体デバイス。

**【請求項18】**

10

第2の基板層は、第2の基板層の底部の近くに電圧閾値領域を含み、電圧閾値領域の上にパンチスルーレンジドメインを含む、請求項17に記載の半導体デバイス。

**【請求項19】**

ゲート電極および第1の組の活性領域は第1の導電型のトランジスタを形成し、ゲート電極および第2の組の活性領域は異なる導電型のトランジスタを形成する、請求項17に記載の半導体デバイス。

**【請求項20】**

ゲート電極および第1の組の活性領域は第1の導電型のトランジスタを形成し、ゲート電極および第2の組の活性領域は同じ導電型のトランジスタを形成する、請求項17に記載の半導体デバイス。

20

**【請求項21】**

積み重ねは、第2の基板の上に第2の組の活性領域の間に配されるキャップ層をさらに含む、請求項17に記載の半導体デバイス。

**【発明の詳細な説明】**

**【0001】**

**【発明の分野】**

この発明は一般的に半導体デバイスに関し、より特定的には、2組の活性領域の間で共用されるゲート電極を有する半導体デバイス、およびこうしたデバイスを製作する方法に関する。

**【0002】**

30

**【発明の背景】**

U S - A - 5 7 1 4 3 9 4 は、さまざまなレベルの半導体トポグラフィ上に能動および受動デバイスを生成するためのプロセスを開示する。このプロセスは第1の基板の上面に第1のトランジスタを形成するステップを含み、このトランジスタはゲート誘電体上のゲート導体と、半導体基板中の第1の活性領域とを含む。ゲート導体上にシリサイドが形成され、そのトポグラフィの上に階間誘電体が形成される。ゲート導体のシリサイドまでの開口部が形成され、その開口部が導電材料によって充填されることにより第2のゲート導体が形成される。階間誘電体の選択された領域上に、第2のゲート導体の上に中心合わせして第2の基板が形成される。次いで第2の基板に活性領域が注入されることによって第2の能動デバイスが形成される。

40

U S - A - 5 2 1 5 9 3 2 は、N M O S 能動デバイスの頂部に自己整合能動P M O S デバイスを製作するための方法を開示し、このデバイスは共通のゲート電極を有する。この方法は、能動P M O S デバイスのチャネル領域として働く上層を有するポリゲートサンドイッチ構造を有する基板に標準的なN M O S トランジスタを形成するステップを含む。インターポリ誘電体が蒸着され、埋め込まれた接触が形成されることによって、その後蒸着されるドーピングされた多結晶シリコン層がP M O S デバイスのソース／ドレイン端子となる。

U S - A - 4 6 8 6 7 5 8 、 U S - A - 4 6 5 4 1 2 1 およびU S - A - 5 3

1 0 6 9 6 もまた垂直方向に積み重ねられたC M O S F E T の製作方法を開示する。

過去数十年間にわたり、電子工業は半導体技術を用いて小さくかつ高度に一体化した電子

50

デバイスを製作することによって革命を起こした。現在用いられる最も一般的な半導体技術はシリコンベースである。多様な半導体デバイスが製造されており、それらは数多くの学問分野にさまざまな適用を有する。こうしたシリコンベースの半導体デバイスの1つに、金属酸化膜半導体(MOS)トランジスタがある。

#### 【0003】

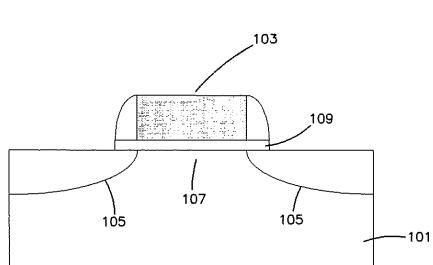

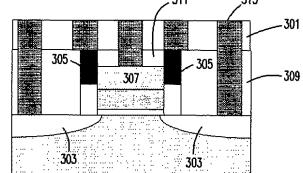

図1に、典型的なMOS半導体デバイスの主要な構成要素を示す。このデバイスは一般的に半導体基板101を含み、その上にゲート電極103が配される。ゲート電極103は導体として作用する。入力信号は典型的にはゲート端子(図示せず)を介してゲート電極103に印加される。半導体基板101中に濃くドーピングしたソース/ドレイン領域105が形成され、ソース/ドレイン端子(図示せず)に接続される。典型的なMOSトランジスタは対称であり、すなわちソースおよびドレインを互いに交換できる。ある領域がソースとして作用するか、またはドレインとして作用するかは、それぞれに印加される電圧と、作られるデバイスの型(たとえばPMOS、NMOSなど)とに依存する。10

#### 【0004】

半導体基板101中のゲート電極103の下にチャネル領域107が形成されて、ソース/ドレイン領域105を分離する。このチャネルは典型的には、ソース/ドレイン領域105のドーパントとは反対の型のドーパントによって薄くドーピングされる。ゲート電極103は一般的に、絶縁層109、典型的にはSiO<sub>2</sub>などの酸化物層によって半導体基板101から分離される。ゲート絶縁層109が設けられることによって、ゲート電極103とソース/ドレイン領域105またはチャネル領域107との間に電流が流れることができが防がれる。20

#### 【0005】

ソース/ドレイン領域105が形成された後、基板101の上に接触形成層と呼ばれる比較的厚い酸化物層(図示せず)が配される。接触形成層には一般的に開口部が切り込むことによって、ソース/ドレイン領域105およびゲート電極103の表面を露出する。次いで露出された領域をタンクステンなどの金属によって充填することにより接触を形成し、これは能動素子をチップ上のその他のデバイスに接続するために用いられる。

#### 【0006】

動作中、典型的にはソースおよびドレイン端子の間に出力電圧が生じる。ゲート電極103に入力電圧が印加されるとき、チャネル領域107中に横方向の電界がもたらされる。横方向の電界を変化させることによって、ソース領域とドレイン領域との間のチャネル領域107の導電率を調節できる。この態様で、電界はチャネル領域107を通る電流を制御する。この型のデバイスは一般的にMOS効果トランジスタ(MOSFET)と呼ばれる。30

#### 【0007】

前述のような半導体デバイスは、近年の電子デバイスのほとんどを構成するために多数用いられている。こうした電子デバイスの能力を増加させるために、単一のシリコンウェハ中により多数のこうしたデバイスを一体化する必要がある。所与の表面領域上により多数のデバイスを形成するために半導体デバイスは縮小される(すなわちより小さくされる)ため、デバイスの構造およびこうしたデバイスを作るために用いられる製作技術を変更する必要がある。40

#### 【0008】

##### 【発明の概要】

この発明は一般的に、2組の活性領域によって共用されるゲート電極を有する半導体デバイスと、その製作方法とを提供する。この発明の実施例の1つに従うと、半導体デバイスは、第1の基板の上および第2の基板の下にゲート電極を形成し、ゲート電極の下に第1の基板と結合させて第1の組の活性領域を形成し、ゲート電極の上に第2の基板と結合させて第2の組の活性領域を形成することによって形成される。2組の活性領域をたとえば別々に用いて2つのトランジスタを効果的に形成してもよい。代替的には、2組の活性領域をつないで单一のトランジスタを効果的に形成してもよい。50

**【 0 0 0 9 】**

別の実施例に従うと、半導体デバイスは第1の基板と、第1の基板の上に配されるゲート電極とを含む。ゲート電極の上に第2の基板が配される。第1の基板の部分にゲート電極に近接して第1の組の活性領域が配され、ゲート電極の上に第2の基板に近接して第2の組の活性領域が配される。前述のとおり、この2組の活性領域はたとえば別々に用いられても、互いにつながれてもよい。

**【 0 0 1 0 】**

前述のこの発明の概要は、この発明の例示される各実施例またはすべての実現例を説明することを意図するものではない。図面および以下の詳細な説明によってこれらの実施例をより特定的に例示する。

10

**【 0 0 1 1 】**

添付の図面とともに、この発明のさまざまな実施例の以下の詳細な説明を考慮することにより、この発明はより完全に理解されるであろう。

**【 0 0 1 2 】**

この発明はさまざまな変更形および代替的な形に従うが、図面においては例としてその特定のものを示し、詳細に説明する。しかし、これは説明する特定の実施例にこの発明を制限することを意図するものではないことが理解されるべきである。反対にその意図は、添付の請求項によって定められるこの発明の趣旨および範囲内にあるすべての変更形、同等のものおよび代替形を包含することにある。

**【 0 0 1 3 】**

20

**【 詳細な説明 】**

この発明は、特にMOS、CMOSおよびBiCMOS構造を含む多くの半導体デバイスの製作に適用可能であると考えられる。この発明は、チップ上のトランジスタの密度を増加させるために特に適している。この発明を制限するものではないが、以下に提供する例に関連するこうしたデバイスの製作プロセスおよび特性の考察を通じて、この発明のさまざまな局面の評価が得られる。

**【 0 0 1 4 】**

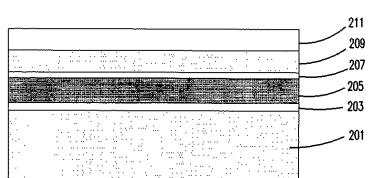

図2A-2Fに、2組の活性領域によって共用されるゲート電極を有する半導体デバイスを製作するための例示的なプロセスを例示する。この例示的なプロセスにおいて、第1の基板201の上に第1のゲート絶縁層203が形成される。第1の基板201は典型的にはシリコンなどの半導体材料から形成される。第1のゲート絶縁層203は、たとえば周知の蒸着または成長技術を用いていくつかの異なる絶縁材料から形成されてもよい。好適な材料にはたとえば二酸化シリコンなどの酸化物、または二酸化チタンなどの誘電率のより高い酸化金属が含まれる。

30

**【 0 0 1 5 】**

第1のゲート絶縁層203は、ゲート電極を第1の基板201から分離するために用いられる。第1のゲート絶縁層203の厚みは典型的に、ゲート絶縁層の誘電率を考慮して、形成されるデバイスの所望の動作特性に基づいて選択される。多くの適用に対し、この層の厚みは、10から25オングストローム( )のSiO<sub>2</sub>と同等の容量を与えるよう選択される。

40

**【 0 0 1 6 】**

第1のゲート絶縁層203を形成するのに先立ち、第1の基板201中に典型的にはドーパントが与えられて第1の基板201の上面の近くに電圧閾値領域が形成され、閾値領域の下に(典型的にはその後形成される活性領域とほぼ同じ深さに)パンチスルーフィールド領域が形成され、任意には基板201中にウェル領域が形成される。たとえば公知の注入技術を用いて背景ドーパントが与えられてもよい。背景ドーパントの導電型は、形成されるトランジスタの型と典型的には類似であり、それに依存する。NMOSまたはn-チャネルトランジスタに対しては、背景ドーパントは典型的にはp-型であり、PMOSまたはp-チャネルデバイスに対しては、典型的にはn-型の背景ドーパントが用いられる。

**【 0 0 1 7 】**

50

第1の絶縁層203の上にゲート電極層205が形成される。ゲート電極層205は、たとえば公知の蒸着技術を用いて多結晶シリコンまたは金属から形成されてもよい。多結晶シリコンで形成されるとき、ゲート電極層205は好適な拡散または注入技術を用いてインサイチュードーピングされても、または蒸着後にドーピングされてもよい。このゲート電極層205は、2組の活性領域に対するゲート電極を形成するために用いられる。ゲート電極層205の厚みは典型的にはゲート電極の所望の厚みを考慮して選択される。多くの適用に対し、好適な厚みは5000から10000の範囲である。

#### 【0018】

ゲート電極層205の上に第2のゲート絶縁層207が形成される。第2のゲート絶縁層207は、たとえば周知の蒸着または成長技術を用いて、いくつかの異なる絶縁材料から形成されてもよい。好適な材料には二酸化シリコンなどの酸化物、または二酸化チタンなどの酸化金属が含まれる。この第2のゲート絶縁層207は、ゲート電極を第2の基板から分離するために用いられ、典型的には形成されるデバイスの所望の動作特性および層の誘電率に基づいて選択される厚みを有する。多くの適用に対し、この層の厚みは10から25のSiO<sub>2</sub>と同等の容量を与えるよう選択される。

10

#### 【0019】

第2のゲート絶縁層207の上に第2の基板層209が形成される。第2の基板層209は、たとえば公知の蒸着技術を用いてたとえばシリコンから形成されてもよい。たとえば、第2の基板層209は化学気相成長(CVD)または低圧化学気相成長(LPCVD)技術を用いて多結晶シリコンから形成されてもよい。典型的には、第2の基板層209はドーピングされていない状態で形成され、その後の処理において適切にドーピングされる。第2の基板層209は、ゲート電極層205から形成されるゲート電極と結合される上側基板として用いられる。多くの適用に対し、第2の基板層209の厚みは5,000から20,000の範囲であってもよい。

20

#### 【0020】

第2の基板層209の上にキャップ層211が形成される。キャップ層211は、たとえば公知の蒸着技術を用いていくつかの異なる絶縁材料から形成されてもよい。好適な材料には二酸化シリコンなどの酸化物が含まれる。キャップ層211は、第1の基板201中に注入される活性領域ドーパントが第2の基板層209に入り込むことを防ぐために少なくとも部分的に用いられてもよい。多くの適用に対し、キャップ層211の好適な厚みは500から1,000の範囲である。その結果得られる構造を図2Aに例示する。

30

#### 【0021】

キャップ層211を形成する前または後に、第2の基板層209に背景ドーパントが与えられる。典型的には、第2の基板層209にドーパントが注入されることにより、その層に対する好適な背景ドーピング導電率および型が与えられ、第2のゲート絶縁層207に近い第2の基板層209の底部に電圧閾値(VT)領域が形成され、任意にはその電圧閾値領域の上(たとえば第2の基板底部から300-500)にパンチスルーフィールドが形成される。典型的には、背景ドーピングとVTおよびパンチスルーフィールドとは、類似の導電型のドーパントを用いて形成される。第2の基板層209において用いられるドーパントの導電型は、第1の基板201中の背景ドーパントの導電型と同じであっても異なっていてもよい。

40

#### 【0022】

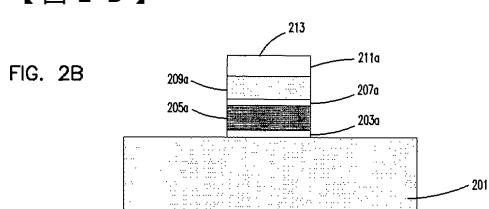

次いで、基板201上の層の積み重ねをエッチングすることにより、図2Bに例示されるように1つまたはそれ以上の積み重ね構造(その1つのみを示す)が形成される。この積み重ね層は、たとえば公知のフォトリソグラフィおよびエッチング技術を用いてエッチングされてもよい。この積み重ね構造213は一般的に、第1のゲート絶縁層203aおよび第2のゲート絶縁層207aの間に配されたゲート電極205aと、第2のゲート絶縁層207aの上に配された第2の基板209aと、基板209aの上に配されたキャップ層211aとを含む。積み重ね構造の幅は典型的にはゲート電極205aの所望の幅に基づいて選択される。多くの適用に対し、好適な幅は0.1から0.25ミクロンまたはそ

50

れ以上の範囲である。

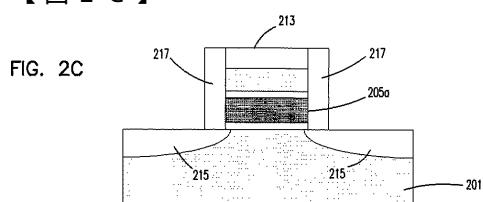

**【0023】**

基板201中に、積み重ね構造213に近接して、第1の組の活性領域215が形成される。活性領域215はソースおよびドレイン領域として用いられ、たとえば公知の注入技術を用いて形成されてもよい。活性領域215を形成する前、その間またはその後に、積み重ね構造213の側壁にスペーサ217が形成されてもよい。たとえば、LDD(薄くドーピングしたドレイン)活性領域が形成されるとき、LDD注入の後、かつソース/ドレイン注入の前にスペーサを形成することによって、ソース/ドレイン注入の積み重ね構造213からの間隔を置いてもよい。その後これらのスペーサはスペーサ217として用いられてもよく、または所望であればソース/ドレイン注入の後に広げられてもよい。

10

**【0024】**

各スペーサ217の上部が取除かれることによって、ゲート電極205aと結合される第2の、上側の組の活性領域が形成される。スペーサ217のこれらの部分は典型的には、キャップ層211aをそのまま残して選択的に取除かれ。したがってスペーサ217の材料は、キャップ層の材料を考慮して好適に選択される。キャップ層213が二酸化シリコンから形成されるとき、スペーサ217はたとえば窒化物または酸窒化物から形成されてもよい。スペーサ217の幅は典型的には第2の組の活性領域の幅を定める。多くの適用に対し、好適なスペーサの幅は300から800の範囲である。その結果得られる構造を図2Cに例示する。

**【0025】**

20

活性領域215を形成した後に、半導体構造をアニールすることによって活性領域215中のドーパントを活性化してもよい。このアニールによって、第2の基板209a中の背景ドーパント、基板201中の背景ドーパント、およびもしあればゲート電極205a中のドーパントを活性化してもよい。代替的には、背景ドーパントおよびあらゆるゲート電極ドーパントを活性化するために別のアニールを行なってもよい。

**【0026】**

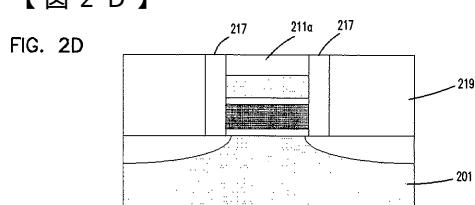

図2Dに例示するとおり、基板201の上にスペーサ217に近接して絶縁層219が形成される。絶縁層219は典型的に、スペーサ217の部分を取り除くときにもそのまま残るような材料から形成される。スペーサ217が窒化物または酸窒化物から形成されるとき、絶縁フィルム219はたとえば二酸化シリコンから形成されてもよい。絶縁フィルム219は公知の技術を用いて形成されてもよい。たとえば公知の蒸着およびポリシング技術を用いて、たとえば絶縁材料の層を基板201の上に蒸着し、ポリシングすることによってスペーサ217の上面を露出させてもよい。

30

**【0027】**

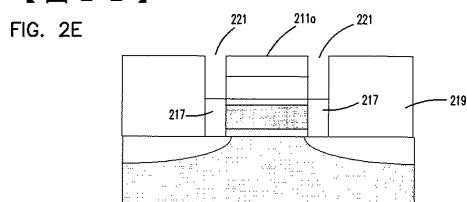

図2Eに例示されるとおり、スペーサ217の上部を取り除くことによって開口部221が形成される。後述するとおり、各開口部221中に活性領域が形成される。開口部221の深さは典型的には、第2の基板層/第2のゲート絶縁層界面まで延在する。スペーサ217の上部は、いくつかの異なるエッティング技術を用いて、キャップ層211aおよび絶縁層219を実質的にそのまま残しながら選択的にスペーサ217をエッティングすることによって取り除いてもよい。多くの適用に対し、好適なエッティング技術はプラズマエッティングを含む。典型的には、時限式のエッティングを用いてスペーサ217の上部の除去を行うことにより、開口部221の所望の深さを与える。

40

**【0028】**

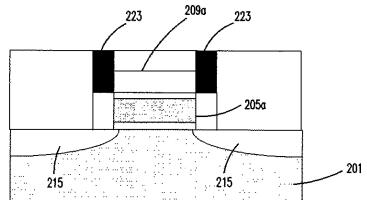

図2Fに例示されるとおり、開口部221中に活性領域223が形成される。活性領域223は、たとえば公知の蒸着およびポリシング技術を用いていくつかの異なる導電材料から形成されてもよい。多くの適用に対し、好適な材料はコバルトタングステンまたは銅などの金属、またはドーピングされた多結晶シリコンを含む。活性領域223は、ゲート電極205aおよび第2の基板209aに結合される第2の、上側の組の活性領域を形成する。活性領域223の形成に続き、典型的には能動素子への接触が形成され、公知の製作ステップによって処理が継続されて最終的なデバイス構造が完成する。能動素子への接触

50

を形成するための例示的な技術を後述する。

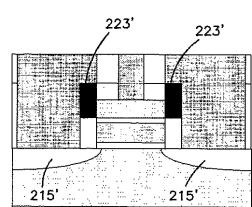

【0029】

図2Fに図示される構造は、第1の基板201およびゲート電極205aに結合される第1の組の活性領域215と、第2の基板209aおよびゲート電極205aに結合される第2の組の活性領域223とを含む。図2Fに図示される構造はいくつかの異なる態様で用いられてもよい。たとえば、活性領域223と、基板209aと、ゲート電極205aとを第1のトランジスタとして用い、下側の活性領域215と、基板201と、共用ゲート電極205aとを第2のトランジスタとして用いてもよい。評価されるとおり、各トランジスタの型（たとえばn-チャネルまたはp-チャネル）は、横方向の電界下におけるそれぞれのチャネル領域の導電型に依存する。この2つの分離したトランジスタは同じ型であっても異なる型であってもよい。たとえばいくつかの異なる論理デバイスにおいて、このさまざまな組合せは有用であり得る。図3Bに示される別の実施例において、上側の組の活性領域223は下側の組の活性領域215とつながれることによって単一のトランジスタを形成する。

10

【0030】

前述のプロセスを用いて、単一のゲート電極は上側および下側の組の活性領域に結合されてもよい。活性領域の各組および共用ゲート電極は異なるトランジスタとして用いられてもよい。このことにより、たとえば基板上のトランジスタの密度を増加させることができる。代替的には、2組の活性領域をともにつないでもよい。このことによりたとえば、その結果得られるトランジスタデバイスの駆動電流を増加させることができる。

20

【0031】

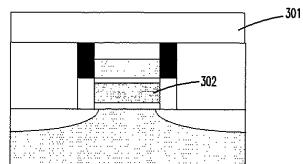

図3A-3Fに、図2Fにおいて示される構造の能動素子に接触を形成するための例示的なプロセスを例示する。これらの例示的な技術は参考のために与えられるものであって、この発明の範囲を制限することを意図するものではない。能動素子を接触させるためにいくつかの異なる技術を用いてもよい。図3Aにおいては、図2Fの構造の上に絶縁層301が形成される。絶縁層301は、たとえば公知の蒸着技術を用いていくつかの異なる材料から形成されてもよい。多くの適用に対し、好適な材料は二酸化シリコンなどの酸化物を含む。

【0032】

次いで絶縁層301を選択的にマスクすることにより、共用ゲート電極302への接触が形成されるウェハの第1の領域を覆い、他の能動素子への接触が形成されるウェハの第2の領域における層301の部分を選択的に露出させる。この第1のマスクは、公知のフォトリソグラフィ技術を用いて形成されてもよい。絶縁層301の露出された部分、および適切なときにその下にある層の部分を取り除くことにより、上側の活性領域303、下側の活性領域305、および上側の基板307への接触のための開口部が形成される。これは公知のエッチング技術を用いて行なわれてもよい。典型的にこのステップは、絶縁層301の部分およびその下にある絶縁層309の部分をエッチングすることによって活性領域303を露出する開口部を形成するステップと、絶縁層301の部分をエッチングすることによって活性領域305を露出する開口部を形成するステップと、絶縁層301の部分およびその下にあるキャップ層311の部分をエッチングすることによって第2の基板307を露出する開口部を形成するステップとを含む。

30

40

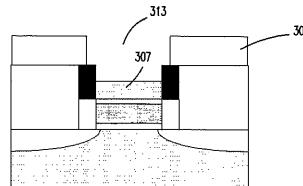

【0033】

次いでこの開口部を導電材料によって充填することにより、それぞれの能動素子への接触313が形成される。これはたとえば公知のポリシングおよび蒸着技術を用いて、導電材料の層を蒸着およびポリシングすることによって行なわれてもよい。多くの適用に対し、好適な導電材料はたとえばコバルト、タンゲステンまたは銅などの金属を含む。その結果得られる構造を図3Bに例示する。2組の活性領域がつながれているとき、図3Bに例示するとおり、つながれる各活性領域への单一の開口部を形成して導電材料によって充填してもよい。

【0034】

次いで第1のマスクが除去され、第2のパターン化されたマスクが形成されてウェハの第2の領域を覆い、第1の領域における絶縁層301の部分を選択的に露出させる。絶縁層301の露出される部分およびその下にあるキャップ層の部分を除去することによって、上側基板307の部分を露出する。その結果得られる構造を図3Cに例示する。絶縁層301およびキャップ層の選択的な除去は、たとえば公知のエッチング技術を用いて行なわれてもよい。これは典型的には上側基板307上の開口部313を残す。

#### 【0035】

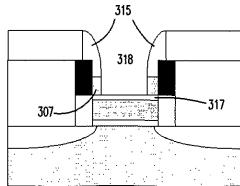

開口部313の側壁に、たとえば公知の技術を用いてスペーサ315が形成される。スペーサ315は典型的に、上側基板307をエッチングする際にもそのまま残るような材料から形成される。好適な材料の1つは窒化物である。整合のためにスペーサ315を用い、上側基板307の露出される部分を取除くことによって第2のゲート絶縁層317の部分を露出する。その結果得られる構造を図3Dに例示する。上側基板部分の選択的な除去は、公知のエッチング技術を用いて行なわれてもよい。これは一般的には第2のゲート絶縁層317上の開口部318を残す。

10

#### 【0036】

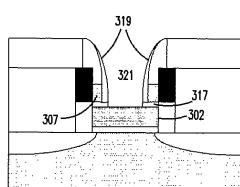

開口部318の側壁に、たとえば公知の技術を用いてスペーサ319が形成される。スペーサ319は典型的には窒化物などの材料で形成され、これは第2のゲート絶縁層317をエッチングする際にもそのまま残る。スペーサ319は、上側基板307の部分を導電接触から絶縁するために用いられる。上側基板307に近接するスペーサ319の好適な厚みは、多くの適用に対して150から300の範囲である。スペーサ319および315は別々に例示されているが、同じ材料で形成されるときには典型的にはこれらのスペーサはともに混合される。整合のためにスペーサ319を用い、第2のゲート絶縁層317の露出される部分を取除くことによってゲート電極302の上面の部分を露出する。第2のゲート絶縁層317の部分の除去は、たとえば公知のエッチング技術を用いて形成されてもよい。その結果、一般的にゲート電極302の露出される部分の上に開口部321が形成される。その結果得られる構造を図3Eに例示する。

20

#### 【0037】

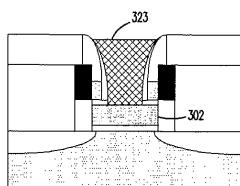

次いで図3Fに例示されるとおり、開口部321中に導電接触323が形成される。導電接触323は、タンクスチン、コバルトまたは銅などの金属を含むさまざまな材料から形成されてもよい。導電接触323の形成は、たとえば公知の蒸着およびポリシング技術を用いて行なわれてもよい。この態様で、上側の活性領域305および上側基板307から絶縁されている導電接触が共用ゲート電極に接触し得る。

30

#### 【0038】

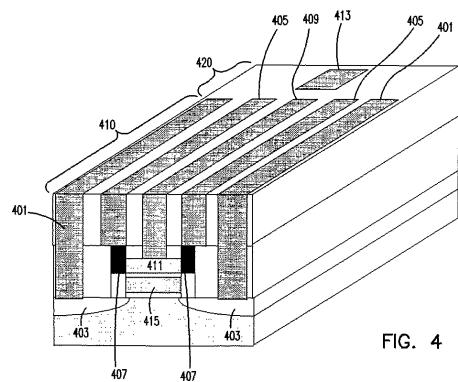

図4に、前述の技術によって形成され得るウェハの例示的な断面を例示する。このウェハ断面は、下側の対の活性領域403に接触する導電接触401と、上側の活性領域407に接触する導電接触405と、上側基板411に接触する導電接触409とを有する第1の領域410と、第1の組の活性領域403および第2の組の活性領域407に結合される共用ゲート電極415に接続される導電接触413を有する第2の領域420とを含む。

40

#### 【0039】

この発明は、共用ゲート電極の形成が望ましいことのあるいくつかの異なるデバイスの製作に適用可能である。したがってこの発明が前述の特定の例に制限されると考えることはできず、むしろ添付の請求項に公正に示されるこの発明のすべての局面を包含することが理解されるべきである。この明細書を検討することによって、この発明を適用可能なさまざまな変更形、同等のプロセスおよび多数の構造がこの発明が向けられる技術分野の当業者に容易に明らかとなる。請求項はこうした変更形およびデバイスを包含することが意図される。

#### 【図面の簡単な説明】

【図1】 従来のMOSトランジスタを例示する図である。

【図2】 図2A-2Fは、この発明の実施例に従った例示的なプロセスを例示する図で

50

ある。

【図3】 図3A - 3Fおよび3B は、この発明の別の実施例に従った例示的なプロセスを例示する図である。

【図4】 この発明のさらに別の実施例に従った例示的な構造を例示する図である。

【図1】

FIG. 1

(Prior Art)

【図2A】

FIG. 2A

【図2B】

【図2C】

【図2D】

【図2E】

【図2F】

FIG. 2F

【図3A】

FIG. 3A

【図3B】

FIG. 3B

【図3C】

FIG. 3C

【図4】

FIG. 4

【図3B-1】

FIG. 3B'

【図3D】

FIG. 3D

【図3E】

FIG. 3E

【図3F】

FIG. 3F

---

フロントページの続き

(74)代理人 100083703

弁理士 仲村 義平

(74)代理人 100091409

弁理士 伊藤 英彦

(74)代理人 100096781

弁理士 堀井 豊

(74)代理人 100096792

弁理士 森下 八郎

(72)発明者 ガードナー, マーク・アイ

アメリカ合衆国、78612 テキサス州、セダー・クリーク、ピィ・オウ・ボックス・249、ハイウェイ・535(番地なし)

(72)発明者 フルフォード, エイチ・ジム

アメリカ合衆国、78748 テキサス州、オースティン、ウッドシャー・ドライブ、9808

審査官 宇多川 勉

(56)参考文献 特開平02-117166(JP, A)

特開平11-238889(JP, A)

特開平05-090517(JP, A)

特開平07-074367(JP, A)

特開平03-104158(JP, A)

特開昭62-155556(JP, A)

特開昭59-103380(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8234

H01L 27/00

H01L 27/088

H01L 27/092

H01L 29/41

H01L 29/786