(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4822472号

(P4822472)

(45) 発行日 平成23年11月24日(2011.11.24)

(24) 登録日 平成23年9月16日(2011.9.16)

(51) Int.Cl.

F 1

|                   |                  |            |      |

|-------------------|------------------|------------|------|

| <b>G06F 13/36</b> | <b>(2006.01)</b> | G06F 13/36 | 520D |

| <b>G06F 13/38</b> | <b>(2006.01)</b> | G06F 13/38 | 320A |

| <b>G06F 15/17</b> | <b>(2006.01)</b> | G06F 15/17 | 630B |

請求項の数 1 (全 19 頁)

|              |                                     |

|--------------|-------------------------------------|

| (21) 出願番号    | 特願2011-11770 (P2011-11770)          |

| (22) 出願日     | 平成23年1月24日 (2011.1.24)              |

| (62) 分割の表示   | 特願2009-193040 (P2009-193040)<br>の分割 |

| 原出願日         | 平成13年10月24日 (2001.10.24)            |

| (65) 公開番号    | 特開2011-154685 (P2011-154685A)       |

| (43) 公開日     | 平成23年8月11日 (2011.8.11)              |

| 審査請求日        | 平成23年2月22日 (2011.2.22)              |

| (31) 優先権主張番号 | 特願2001-22587 (P2001-22587)          |

| (32) 優先日     | 平成13年1月31日 (2001.1.31)              |

| (33) 優先権主張国  | 日本国 (JP)                            |

|           |                                                        |

|-----------|--------------------------------------------------------|

| (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部 1753 番地 |

| (74) 代理人  | 100089071<br>弁理士 玉村 静世                                 |

| (72) 発明者  | 西本 順一<br>東京都小平市上水本町五丁目20番1号<br>株式会社日立製作所 半導体グループ内      |

| (72) 発明者  | 中澤 拓一郎<br>東京都小平市上水本町五丁目20番1号<br>株式会社日立製作所 半導体グループ内     |

| (72) 発明者  | 山田 孔司<br>東京都小平市上水本町五丁目20番1号<br>株式会社日立製作所 半導体グループ内      |

最終頁に続く

(54) 【発明の名称】データ処理システム

## (57) 【特許請求の範囲】

## 【請求項 1】

シングルチップで構成される第1データプロセッサと、

上記第1データプロセッサとは異なるシングルチップで構成される第2データプロセッサと、

外部デバイスと、

一方を前記第1データプロセッサに接続され、他方を前記第2データプロセッサに接続される第1外部バスと、

一方を前記第2データプロセッサに接続され、他方を前記外部デバイスに接続される第2外部バスと、を含むデータ処理システムであって、

前記第2データプロセッサは、

電源供給される動作状態と電源遮断される待機状態との間で遷移され、

前記動作状態のとき、命令をフェッチし、実行可能な中央処理装置と、

前記中央処理装置が接続される内部バスと、

前記第1外部バスと、前記内部バスとに接続可能な第1外部インターフェース回路と、

前記第2データプロセッサの待機状態のとき、一方を前記第1外部バスに接続され、他方を前記第2外部バスに接続される内部経路と、を自らのシングルチップの内部に有し、

前記動作状態のとき、前記第1データプロセッサは前記第1外部インターフェース回路を介して前記第2データプロセッサにアクセス可能であり、前記第2データプロセッサは信

10

20

号を前記第2外部バスへ供給可能であり、

前記待機状態のとき、前記第2データプロセッサ内の内部経路を経由して、前記第1データプロセッサは、異なるバスに接続された外部デバイスへアクセス可能である、データ処理システム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数のデータプロセッサと複数のシステムバスで構成されるシステムにおいて、データプロセッサ間を接続するバスのデータ転送方式及びデータ転送システムの技術分野に属する。例えば、一のデータプロセッサが他のデータプロセッサの内蔵回路を共有する技術、一のデータプロセッサが他のデータプロセッサの外部バスをアクセスする技術に適用して有効な技術に関する。更に本発明は、データプロセッサの動作プログラムをメモリに初期的に格納するブート制御の技術に関する。

【背景技術】

【0002】

システムの複雑さに伴い、そのシステム上に搭載されるデータプロセッサ及び部品の数が増えている。例えば携帯電話のシステムにおいては、従来までは通信を制御するためのベースバンドデータプロセッサがソフトウェア（アプリケーション、キー制御など）やハードウェア（RF回路、LCD、メモリなどの部品）の制御を行っていた。しかし機能の多様化に伴い、全ての処理をベースバンドデータプロセッサ行うことが困難になってきている。従来のPC系のシステムではこの問題をデータプロセッサの動作周波数を向上することで解決していたが、近年のバッテリ駆動型の携帯端末では電池寿命を長くしなくてはいけないという理由から、単純に周波数の高速化による性能向上は行えない。

【0003】

データプロセッサが行う処理により周波数を可変にする手法も存在するが、実際にシステム上で実現するのは複雑であるため実用化が難しい。また高速動作を行えるデータプロセッサはチップ面積が大きくなる傾向にあり、スタンバイ時の電流値を減らすことが困難である。

【0004】

この問題を解決するために、従来のデータプロセッサでは処理しきれないアプリケーションをコプロセッサもしくは別のデータプロセッサで処理するといった手段が採られるようになってきている。これにより特定の処理が必要になったときに、その処理に適したデータプロセッサだけを動作することが可能となるため、システム構築が容易となり最終的にはシステム全体の低消費電力化にもつながる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平7-36704号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

1つのシステム上にデータプロセッサ及びコプロセッサ等のように複数のデータプロセッサが搭載される場合、そのデータプロセッサ同士の接続には共有バスが用いられることが多い。しかしバスを共有できないデータプロセッサや、バス共有を行っていたのではメモリアクセス性能が足りず性能が出せない場合などには、片側のデータプロセッサに別のインターフェースを内蔵し、このインターフェースをもう片側のデータプロセッサのバスに接続することでデータ転送を行う必要が生じる。このインターフェースとして例えばTIのDSP(TMS320C54x)がサポートしているホストポートインターフェースなどがあり、実際にはデータプロセッサに内蔵されたRAMと割り込み機能を用いることによりデータプロセッサ間のデータ転送を行う。ただし転送したデータを使うためにはソフトウェ

10

20

30

40

50

アを実行する必要がある。

#### 【0007】

システムだけでなくデータプロセッサの機能自体も高機能化している。このためシステム上に複数のデータプロセッサを搭載した場合、お互いのデータプロセッサに搭載された機能を効率良く使うことにより、重複して同じ機能を複数のデータプロセッサがサポートする必要がなくなる。例えばS D R A M (シンクロナスD R A M) 等に対するメモリインターフェースやU S B (ユニバーサル・シリアル・バス)、メモリカード、シリアルインターフェースなどである。前記共通バスによらないインターフェースでデータプロセッサ同士が接続されている場合、それぞれのデータプロセッサがサポートしている機能を使うときは、転送されたデータをソフトウェアで処理する必要がある。例えばあるデータプロセッサが別のデータプロセッサのメモリインターフェースを用いて、そのメモリへアクセスしたい場合には、一度前記インターフェースでアクセスするデータを前記別のデータプロセッサに転送した後に、割込みで当該別のデータプロセッサのプログラム実行を起動し、そのプログラムを実行する前記別のデータプロセッサがメモリへのアクセスを行い、アクセス後に再度前記別のデータプロセッサから前記一方のデータプロセッサに対して割り込みを発生して、当該一方のデータプロセッサへ前記インターフェースを介してデータの転送を行う必要があった。

10

#### 【0008】

システムの複雑さに起因する別の問題として、実装面積の削減が挙げられる。特に携帯情報端末においては消費電力・コストの観点から実装面積を減らすためにシステムの部品点数を削減することが必要となる。しかしシステムが多機能化するにつれ、それを実現するための部品点数が増加する。特に前述のように複数のデータプロセッサを内蔵するような場合にはこの問題はさらに深刻となる。

20

#### 【0009】

従来の技術で述べたようにシステム上に複数のデータプロセッサを搭載して、そのデータプロセッサ同士が共有バスで接続できない場合には、データプロセッサを相互に接続するインターフェースを内蔵する必要が生じる。T IのD S Pのようなホストインターフェースはデータプロセッサに内蔵されたR A Mと割り込み機能を用いることによりハンドシェイクを行い、データ転送を実現する。この方法ではデータ転送の度に割り込み処理プログラムを実行する必要が生じるため、それまで走っていたプログラムの実行が中断され性能が劣化することがある。特にそのデータプロセッサがサポートする外部インターフェースだけを使いたい場合などに対処するには問題がある。

30

#### 【0010】

更に、本発明者は、データプロセッサの動作プログラムをメモリに初期的に格納する技術について検討した。例えば、C P Uの動作プログラムを格納する電気的に書換え可能なフラッシュメモリがオンチップされたマイクロプロセッサにおいて、前記フラッシュメモリに対する初期的なプログラムの書き込みは例えば、その製造段階においてE P R O Mライタのような書き込み装置を用いて行なわれるのが一般的である。しかしながら、そのような書き込み動作はペリファイ処理や再書き込みを伴うこともあり処理が複雑な上に時間もかかり、データプロセッサの製造コストを上昇させる原因にもなっている。

40

#### 【0011】

本発明の目的は、複雑・多機能化するデータ処理システムにおいて、データプロセッサがメモリインターフェースとは別にデータ転送を行うためのデータ転送インターフェースを実現することにある。更に本発明は、そのインターフェースに接続している別のデータプロセッサもしくはデバイスから、当該データプロセッサの内部機能若しくは当該データプロセッサの外付け回路を効率良く利用することを可能にすることを目的とする。そして本発明は、それによって、システム性能の向上と低コスト化を図り、最終的には低消費電力化を実現しようとするものである。

#### 【0012】

本発明の別の目的は、データプロセッサが実行すべきプログラムを不揮発性メモリに初

50

期的に書き込む処理が容易なデータ処理システム、更にはデータプロセッサを提供することにある。

【0013】

本発明の上記並びにその他の目的と新規な特徴は本明細書の以下の記述と添付図面から明らかにされるであろう。

【発明の効果】

【0014】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記の通りである。

【0015】

すなわち、第1のデータプロセッサは、第2のデータプロセッサが待機状態であっても、当該第2のデータプロセッサに接続されている外付け回路を、該第2のデータプロセッサ内部をバイパスして制御することができる。

【図面の簡単な説明】

【0016】

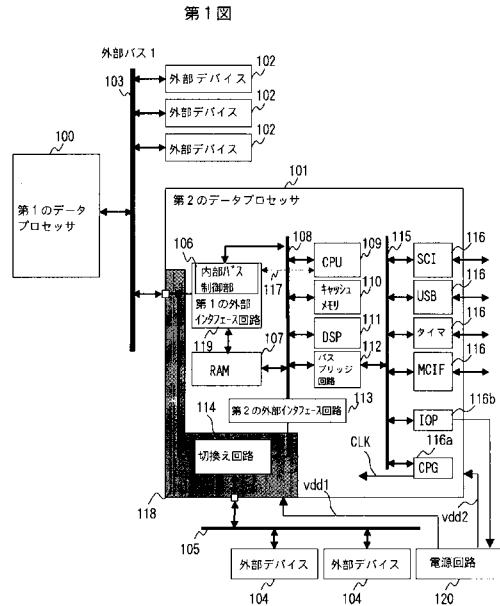

【図1】本発明に係るデータ処理システムの一例を示すブロック図である。

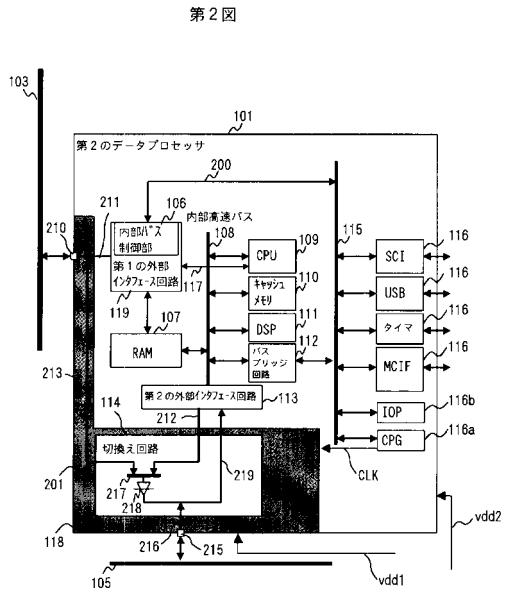

【図2】図1の第2のデータプロセッサにおけるバイパス用の領域の詳細を例示するブロック図である。

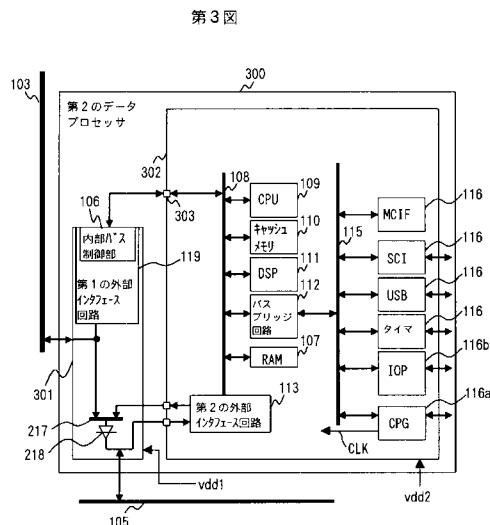

【図3】データプロセッサをマルチチップモジュールで構成した場合の例を示すブロック図である。

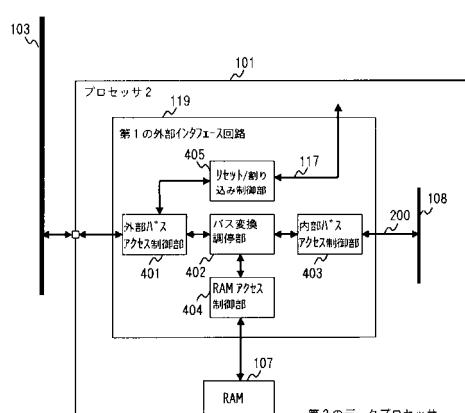

【図4】第2のデータプロセッサが備える第1の外部インターフェース回路の具体的な一例を示すブロック図である。

【図5】第2のデータプロセッサが備える第1の外部インターフェース回路の更に具体的な別の例を示すブロック図である。

【図6】本発明に係るデータ処理システムにおけるデータプロセッサのブートプログラムの初期的書き込みに関する説明図である。

【図7】図6のデータ処理システムにおけるブート動作のタイミングチャートである。

【図8】図6のデータ処理システムにおけるブート動作の別のタイミングチャートである。

【図9】プログラムメモリにブートプログラムが格納されている状態において、ブートプログラムの更新又は第2のデータプロセッサで実行されるアプリケーションを追加／更新する場合のタイミングチャートである。

【図10】図3のデータプロセッサを構成するマルチチップモジュールの断面図である。

【発明を実施するための形態】

【0017】

1. 実施の形態の概要

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。

【0018】

(1) 本発明の第1に観点は、他のデータプロセッサにデータプロセッサの内部バスアクセスを許容するものである。

【0019】

この観点による本発明は、一のデータプロセッサ(100)に他のデータプロセッサ(101)との接続を可能にするためのインターフェース手段(119)を設け、このインターフェース手段に、一のデータプロセッサ内の内部バスに他のデータプロセッサをバスマスターとして接続可能にする機能を設け、内部バスにメモリマップされた周辺機能を前記インターフェース手段を介して外部より当該他のデータプロセッサが直接操作する機能をサポートするものである。これにより、データプロセッサは、実行中のプログラムを中断することなく、別のデータプロセッサの周辺機能等を使うことが可能となる。例えば第1のデータプロセッサが第2のデータプロセッサのメモリインターフェースを使って特定のメモリへ

10

20

30

40

50

アクセスする場合、第1のデータプロセッサは、第2のデータプロセッサの前記インターフェース手段を介して、当該第2データプロセッサの周辺メモリやその他の周辺回路をアクセスして利用することが可能になる。要するに、一のデータプロセッサは別のデータプロセッサの周辺リソースを共有することが可能になる。換言すれば、第1のデータプロセッサは第2のデータプロセッサに内蔵されている別のインターフェース機能を直接使うことができるようになり、システムの高性能化を図ることが可能となる。

#### 【0020】

上記観点による発明を更に詳述する。上記第1の観点によるデータ処理システムは、第1のデータプロセッサ(100)及び第2のデータプロセッサ(101)を含む。前記第2のデータプロセッサは、前記第1のデータプロセッサが前記第2のデータプロセッサの内部バスのバス権を獲得することを可能とするインターフェース手段(119)を内蔵する。前記インターフェース手段は、前記内部バスのバス権を獲得した第1のデータプロセッサによる前記内部バスに接続された入出力回路のアクセスを可能にするものである。10

#### 【0021】

前記入出力回路は、例えば、SDRAMに接続可能なSDRAMインターフェース回路、液晶ディスプレイ装置に接続可能なLCDインターフェース回路、メモリカードに接続可能なメモリカードインターフェース回路、シリアルインターフェース回路、揮発性メモリ、電気的に書き換え可能な不揮発性メモリ、及び汎用入出力ポート回路の中から選ばれた単数若しくは複数の回路である。

#### 【0022】

前記インターフェース手段は、第2のデータプロセッサ内部からのアクセスと前記第1のデータプロセッサからのアクセスとに排他的に応答して動作可能とするバッファRAM(107)を含んでよい。20

#### 【0023】

[2]本発明の第2の観点は、他のデータプロセッサに一のデータプロセッサ固有の外部バスに対するアクセスを当該一のデータプロセッサ経由で許容するものである。

#### 【0024】

この観点による本発明は、第2のデータプロセッサの低消費電力化のために第2のデータプロセッサ(101)の待機時(電源をオフもしくはスタンバイ状態)に、第1のデータプロセッサ(100)とのインターフェースを第2のデータプロセッサ内部で当該第2のデータプロセッサの外付けデバイス(104)とインターフェース可能にする手段(114)を設ける。これにより、第2のデータプロセッサに接続していたデバイスを、当該第2のデータプロセッサの待機中には外付け回路なしに第1のデータプロセッサが制御できるようになる。要するに、第1のデータプロセッサは、第2のデータプロセッサが待機状態であっても、当該第2のデータプロセッサに接続されている外付け回路を、該第2のデータプロセッサ内部をバイパスさせて制御できる。これによりデータ処理システムを構成する部品点数の削減が行え、低コスト化が可能となる。30

#### 【0025】

上記観点による発明を更に詳述する。上記第2の観点によるデータ処理システムは、第1のデータプロセッサ(100)、前記第1のデータプロセッサに接続される第1のバス(103)、前記第1のバスに接続される第2のデータプロセッサ(101)、及び前記第2のデータプロセッサに接続される第2のバス(105)を含む。前記第2のデータプロセッサは、前記第1のバスに一方が接続され内部バスに他方が接続される第1の外部インターフェース回路(119)と、前記第2のバスに一方が接続される内部バスに他方が接続される第2の外部インターフェース回路(113)と、第2のデータプロセッサの待機状態において前記第2の外部インターフェース回路の前記一方の代わりに前記第1のインターフェース回路の前記一方を前記第2のバスに接続する切換え回路(114)と、を含む。40

#### 【0026】

前記第2のデータプロセッサの待機状態は、例えば、前記第2のデータプロセッサに含まれるクロック同期回路へのクロック信号の供給が停止される状態である。また、前記第50

2のデータプロセッサにおいて前記切換え回路の動作電源とその他の回路の動作電源とを分離可能とし、前記第2のデータプロセッサの待機状態に応答して前記その他の回路の全部又は一部への動作電源の供給を停止させる電源制御回路(116b)を更に含む。これにより、前記第2のデータプロセッサは待機状態において電力消費が低減される。

#### 【0027】

前記第2の外部インターフェース回路は、例えば、液晶ディスプレイコントローラに接続可能なLCDインターフェース回路を含む。このとき、前記第2のバスには液晶ディスプレイコントローラが接続される。これにより、前記第1のデータプロセッサは前記切換え回路を介して前記液晶ディスプレイコントローラを制御可能になる。

#### 【0028】

[3]本発明の第3の観点は、リセット動作解除後にデータプロセッサが実行すべき動作プログラムをオンチップの不揮発性メモリやローカルバス上の不揮発性メモリに初期的に書き込むための動作制御を当該データプロセッサを介して可能にするものである。

#### 【0029】

この観点の本発明によるデータ処理システムは、第1のデータプロセッサ(100)及び第2のデータプロセッサ(101)を含む。前記第2のデータプロセッサは、リセット動作解除後の第1動作モードにおいて前記第1のデータプロセッサにより書き込み可能にされる揮発性メモリ(107)と、前記第1動作モードによる書き込み後における命令フェッチの対象を前記揮発性メモリとするCPU(109)と、リセット動作解除後の第2動作モードにおいてCPUによる命令フェッチの対象とされる電気的に書換可能な不揮発性メモリ(502)とを含む。前記第1のデータプロセッサは、第2のデータプロセッサに第1動作モードを指定し、前記揮発性メモリに、前記不揮発性メモリに対する書き込み制御用プログラムを格納して、CPUに命令フェッチを許可する。これにより、第2のデータプロセッサは、揮発性メモリに書き込まれた書き込み制御プログラムを実行し、これに従って前記オンチップの不揮発性メモリに第1のデータプロセッサの動作プログラムを初期的に書き込むことができる。この動作プログラムを実行するときは、リセット動作解除後に第2動作モードが指定されればよい。

#### 【0030】

電気的に書き込み可能な不揮発性メモリは第1のデータプロセッサにオンチップされたメモリに限定されない。第1のデータプロセッサのローカルバスに接続された電気的に書換可能な不揮発性メモリ(501)であってもよい。

#### 【0031】

第3の観点による発明によれば、リセット動作解除後にデータプロセッサが実行すべき動作プログラムをオンチップの不揮発性メモリやローカルバス上の不揮発性メモリに初期的に書き込むための動作制御を当該データプロセッサを介して行うことができる。要するに、データプロセッサの製造過程においてオンチップのプログラムメモリ等にプログラムを書き込む処理を行わなくてもよい。

#### 【0032】

[4]本発明の第4の観点は、前記第1乃至3の観点によるデータ処理システムに適用されるデータプロセッサに着目する。

#### 【0033】

データプロセッサは、CPU(109)と、前記CPUに接続する内部バスと、前記内部バスに接続する周辺回路(116)と、第1の外部端子に一方が接続され前記内部バスに他方が接続される第1の外部インターフェース回路(119)と、第2の外部端子に一方が接続され前記内部バスに他方が接続される第2の外部インターフェース回路(113)とを含む。前記第1の外部インターフェース回路は外部からのアクセス要求に応答して、内部バスのバス権を獲得し、内部バスに接続された前記周辺回路のアクセスを可能にする。これにより、データプロセッサは内部バスに接続するオンチップの周辺回路などを他のデータプロセッサに利用させることが可能になる。

#### 【0034】

10

20

30

40

50

前記 C P U の待機状態において前記第 2 の外部インターフェース回路の一方の代わりに前記第 1 の外部端子を前記第 2 の外部端子に接続する切換え回路(114)を更に含んでよい。他のデータプロセッサに一のデータプロセッサ固有の外部バスに対するアクセスを当該一のデータプロセッサ経由で許容するものである。例えばデータプロセッサのローカルバスに L C D コントローラが接続されるとき、当該データプロセッサの待機状態においてシステムバス経由で他のデータプロセッサがローカルバス上の前記 L C D コントローラを介して L C D に対する時間表示制御機能を実現することが可能になる。

#### 【 0 0 3 5 】

前記第 3 の観点の如く、データプロセッサのブートプログラムを初期的に書き込むという観点では、データプロセッサは、リセット動作解除後の第 1 動作モードにおいて前記第 1 の外部インターフェース回路を介し外部から書き込み可能にされる揮発性メモリと、プログラムメモリ例えば電気的に書き込み可能な不揮発性メモリとを更に含む。前記 C P U は、前記第 1 動作モードによる書き込み後に前記揮発性メモリから命令をフェッチして実行可能であり、また、C P U は、リセット動作解除後の第 2 動作モードにおいて前記プログラムメモリから命令をフェッチして実行可能である。前記第 2 動作モードで前記プログラムメモリに対する書き込み制御プログラムを揮発性メモリに書き込み、書き込んだ書き込み制御プログラムを第 2 動作モードで実行すれば、不揮発性プログラムメモリにデータプロセッサのブートプログラムを初期的に書き込むことができる。

#### 【 0 0 3 6 】

前記 C P U 、前記内部バス、前記第 1 の外部インターフェース回路、前記第 2 の外部インターフェース回路、前記切換え回路、前記揮発性メモリ、及び前記プログラムメモリを 1 個の半導体基板上に形成して、データプロセッサをシングルチップで構成することができる。また、前記 C P U 、前記内部バス、前記第 1 の外部インターフェース回路、前記第 2 の外部インターフェース回路、前記切換え回路、及び前記揮発性メモリを第 1 の半導体基板上に形成し、前記プログラムメモリ(501)を第 2 の半導体基板上に形成し、前記第 1 の半導体基板と第 2 の半導体基板を例えば高密度実装基板に実装し 1 個のパッケージに封入し、マルチチップモジュールとして構成してよい。

#### 【 0 0 3 7 】

〔 5 〕本発明の第 5 の観点は、前記第 1 の観点によるデータ処理システムに適用されるデータプロセッサを更に別の観点から把握する。

#### 【 0 0 3 8 】

データプロセッサは、第 1 のバスに接続される第 1 の端子と、第 2 のバスに接続される第 2 の端子と、第 1 の状態又は第 2 の状態を選択的に採り得る第 1 の内部回路と、第 2 の内部回路と、前記第 1 の端子から前記第 1 の内部回路と前記第 2 の内部回路を介して前記第 2 の端子に接続される第 1 の信号経路と、前記第 1 の端子から前記第 2 の内部回路を介して前記第 2 の端子に接続される第 2 の信号経路とを含む。前記第 2 の内部回路は、前記第 1 の内部回路の状態に応じて、前記第 1 の信号経路と前記第 2 の信号経路の何れかの信号経路を選択する。

#### 【 0 0 3 9 】

前記第 1 の状態は例えば前記第 1 の内部回路が命令を実行可能な動作状態であり、前記第 2 の状態は例えば命令の実行が抑止される待機状態である。前記第 2 の内部回路は、動作状態において前記第 1 の経路を選択し、待機状態において第 2 の経路を選択する。

#### 【 0 0 4 0 】

前記第 1 の内部回路に対する第 1 の電源の供給と前記第 2 の内部回路に対する第 2 の電源の供給とを制御する電源制御回路を有する。このとき、前記電源制御回路は、前記第 2 の内部回路に前記第 2 の信号経路が選択される場合に第 1 の内部回路の全部又は一部への第 1 の電源の供給を停止する。要するに、待機状態では動作を行う必要のない回路には無駄な動作電源の供給を行わないようとする。

#### 【 0 0 4 1 】

前記第 1 の内部回路、第 2 の内部回路、及び電源制御回路は 1 個の半導体基板上に形成

10

20

30

40

50

してよい。また、前記第1の内部回路及び前記電源制御回路は第1の半導体基板上に形成し、前記第2の内部回路は第2の半導体基板上に形成し、前記第1の半導体基板と第2の半導体基板を1個のパッケージに封入して、データプロセッサをマルチチップモジュール等として構成してもよい。

【0042】

前記第1の内部回路に同期動作用のクロック信号を供給するクロック制御回路(116a)を有するとき、前記クロック制御回路は、前記第2の内部回路に前記第2の信号経路が選択される場合に前記第1の内部回路へのクロック信号の供給を停止させるとよい。待機状態では動作を行う必要のない回路には無駄な電力消費につながるようなクロック信号の供給を停止したほうが望ましいからである。

10

【0043】

望ましい形態として、前記第1の内部回路に対する第1の電源の供給と前記第2の内部回に対する第2の電源の供給とを制御する電源制御回路は、前記第1の内部回路へのクロック信号の供給が停止されるとき、前記第1の内部回路の全部又は一部への電源供給を停止するのがよい。

【0044】

前記第1の内部回路、第2の内部回路、クロック制御回路、及び電源制御回路は1個の半導体基板上に形成してよい。また、前記第1の内部回路、クロック制御回路及び電源制御回路は第1の半導体基板上に形成し、前記第2の内部回路は第2の半導体基板上に形成し、前記第1の半導体基板と第2の半導体基板を1個のパッケージに封入して、データプロセッサをマルチチップモジュール等として構成してもよい。

20

【0045】

〔6〕本発明の第6の観点は、前記第1の観点による情報処理システムを更に別の観点から把握する。

【0046】

情報処理システムは、第1のバスと、第2のバスと、前記第1のバス及び第2のバスに接続されるデータプロセッサとを有する。前記データプロセッサは、第1動作態様と第2動作態様を有し、前記第1動作態様において前記データプロセッサは、前記第1のバスから供給された情報を処理し、前記第2のバスに所定の情報を供給可能とする。前記第2動作態様において前記データプロセッサは、前記第1のバスから供給された情報をそのまま前記第2のバスに供給する。

30

【0047】

更に観点を変える。携帯電話システムは、第1乃至第3の半導体集積回路、前記第1の半導体集積回路と第2の半導体集積回路とを接続する第1のバス、及び前記第2の半導体集積回路と第3の半導体集積回路とを接続する第2のバスを有する。前記第2の半導体集積回路は、第1の動作態様と第2の動作態様を有し、前記第1の動作態様は、前記第2の半導体集積回路が前記第1の半導体集積回路から供給される情報に基づいて所定の処理を行い、前記第3の半導体集積回路に処理結果を供給する動作態様である。前記第2の動作態様は、前記第2の半導体集積回路が前記第1の半導体集積回路から供給される情報をそのまま前記第3の半導体集積回路に供給する動作態様である。

40

【0048】

前記携帯電話システムにおいて、前記第2の半導体集積回路が前記第1又は第2の動作態様の何れの動作態様に遷移すべきかを制御する制御信号を、前記第1の半導体集積回路が供給してよい。そのような制御信号はコマンドとして与えられてよい。

【0049】

前記携帯電話システムにおいて、例えば、前記第1の半導体集積回路は、ベースバンド処理用であり、前記第3の半導体集積回路は表示制御用である。前記所定の処理は、例えば、少なくとも画像を取り扱うための信号処理である。

【0050】

前記第2のバスに記憶装置を接続してよい。例えば、前記記憶装置には、前記第2の半

50

導体集積回路で行う処理を規定した処理プログラムを格納してよい。

#### 【0051】

##### 2. 実施の形態の詳細

図1に本発明に係るデータ処理システムの一例を示す。本システムは第1の外部バス103に接続された第1のデータプロセッサ100と、第2の外部バス105に接続された第2のデータプロセッサ101で構成される。第1の外部バス103にはRAM、ROM、フラッシュメモリ(FLASH)等の複数の外部デバイス102が接続される。第2の外部バス105には、RAM、ROM、FLASH、液晶ディスプレイ(LCD)コントローラ等の外部デバイス104が接続されている。第2のデータプロセッサ101は、第1の外部バス103上のデバイスの1つとして第1の外部インターフェース回路119を介して第1の外部バス103に接続されている。

10

#### 【0052】

第2のデータプロセッサ101は、内部高速バス108と内部低速バス115を有する。前記内部高速バス108には、CPU109、キャッシュメモリ110、ディジタル信号処理プロセッサ(DSP)111、内部高速バス108と内部低速バス115との間のバスブリッジ回路としてのブリッジ回路112、第1の外部インターフェース回路119、第2の外部インターフェース回路113、及びRAM107が接続されている。前記内部低速バス115にはシリアルインターフェース回路(SCI)、USB(ユニバーサル・シリアル・バス)、タイマ、メモリカードインターフェース回路(MCIF)、I/Oポートのような汎用入出力ポート(IOP)、クロックパルスジェネレータ(CPG)、フラッシュメモリ等の周辺回路116が接続されている。図1においてクロックパルスジェネレータ(CPG)には参照符号116aが付され、汎用入出力ポート(IOP)には参照符号116bが付されている。

20

#### 【0053】

データ処理システムは、特に制限されないが、携帯電話システムとされる。このとき、第1のデータプロセッサ100はベースバンド処理を行なう。第2のデータプロセッサ101は液晶ディスプレイコントローラのような外部デバイス104に対して画像表示制御の為の制御と圧縮伸張などの信号処理を行なう。液晶ディスプレイコントローラを介する時刻表示などの制御は、特に制限されないが、第1のデータプロセッサ100が第2のデータプロセッサ101を経由して行なう。

30

#### 【0054】

前記第1の外部インターフェース回路119は、前記第1のデータプロセッサ100が第2のデータプロセッサ101の内部バス例えば内部高速バス108のバス権を獲得することを可能にするものであり、内部バス108のバス権を獲得した第1のデータプロセッサ100による前記内部バス108に接続された入出力回路のアクセスを可能にする。入出力回路とは、DSP111のレジスタ等を意味する。要するに、第1のデータプロセッサ100は内部高速バス108のバスマスターとして動作することが可能にされる。そのようなバスマスターとしての動作制御は内部バス制御部106が行なう。

#### 【0055】

また、前記第1の外部インターフェース回路119は前記RAMをCPU109と第1のデータプロセッサ100との共有メモリもしくは共有バッファとして動作制御する。即ち、CPU109からのRAM107へのアクセス要求と第1のデータプロセッサ100からRAM107へのアクセス要求とに排他的に応答してRAM107を動作させる。このRAM107に対する共有バッファ機能により、第1のデータプロセッサ100と第2のデータプロセッサ101との間のデータ転送を実現できる。このデータ転送には、例えば割込み信号117を用いたハンドシェーク制御を採用してよい。具体的には、第1のデータプロセッサ100からRAM107にデータが格納されると、CPU109の割込み信号117が与えられ、この割込みに応ずる割り込み処理にてCPU109がRAM107のデータを取りこむ。逆の場合には外部インターフェース回路119は第1のデータプロセッサ100に向けて割込み要求を発行する。

40

50

**【0056】**

前記第2の外部インターフェース回路113は外部バス105に接続される外部デバイスとのインターフェースを実現する為のインターフェース仕様を有する。例えば、外部デバイス104としてF L A S H、液晶ディスプレイ(L C D)コントローラが接続することを想定している場合、第2の外部インターフェース回路113は、フラッシュメモリインターフェース回路、LCDインターフェース回路としてのインターフェース機能を有する。

**【0057】**

図1の構成において、前記領域118には、第2のデータプロセッサ101の待機状態において、前記第2の外部インターフェース回路113における外部バス105との接続端の代わりに、前記第1の外部インターフェース回路における外部バス103との接続端を、前記外部バス105に接続する切換え回路114が設けられている。即ち、前記切換え回路114は、第2のデータプロセッサ101の待機時に、第2の外部インターフェース回路113に代えて第1の外部バス103を第2の外部バス105へ接続する接続様式を選択する。これにより、第1のデータプロセッサ100は切換制御部114を介して、第2の外部バス105上のデバイスをアクセスすることが可能になる。例えば、第1のデータプロセッサ100は切換え回路114を介して外部バス105上の外部デバイス104として液晶ディスプレイコントローラを制御可能である。ここで図1の中の領域118の回路は第2のデータプロセッサ101の待機時にも動作する領域である。

10

**【0058】**

前記第2のデータプロセッサ101の待機状態は、当該第2のデータプロセッサ101に含まれるC P U 109、D S P 111、シリアルインターフェース回路、タイマ等のクロック同期回路へのクロック信号の供給が停止される状態である。例えば、C P U 109がクロックパルスジェネレータ116aの待機状態レジスタに待機状態イネーブルビットをセットすることにより、クロックパルスジェネレータ116aはクロック信号C L Kの出力動作もしくは発振動作を停止して、クロック信号の供給を抑止する。

20

**【0059】**

図1において120で示される回路は電源回路である。前記第2のデータプロセッサ101において前記切換え回路114の動作電源v d d 1とその他の回路の動作電源v d d 2とは分離可能とされる。例えば、動作電源v d d 1の外部電源端子及び電源配線と、動作電源v d d 2の外部電源端子及び電源配線とは、物理的に分離される。電源回路120は動作電源v d d 1、v d d 2を対応する電源端子に供給する。前記汎用入出力ポート116bは電源回路120に対する電源制御回路として利用される。汎用入出力ポート116bは前記第2のデータプロセッサ101の待機状態への遷移過程において前記その他の回路の全部又は一部への動作電源v d d 2の供給を停止させる。前記切換え回路114には第2のデータプロセッサ101が動作可能なときは動作電源v d d 1が常時供給される。待機状態から抜けるのに割込みを利用する場合には割込み制御回路には動作電源が供給されている。電源制御回路116bは、待機状態への遷移過程において電源回路120の電源制御レジスタを電源供給停止指示状態にセットする。これにより、動作電源v d d 2の供給が停止される。電源制御レジスタに対する電源供給指示状態へのリセット動作は、待機状態から動作状態への復帰処理過程で行われればよい。

30

**【0060】**

図2に図1の第2のデータプロセッサ101の領域118の詳細図が例示される。更にこの例では、第1の外部インターフェース回路119が内部低速バス115のバスマスターとして信号線200で接続されている。図2の信号線200が示す通り、第1の外部インターフェース回路119がバスマスターとなる内部バスは高速バス108に限定されず、低速バスであてもよい。

40

**【0061】**

データプロセッサ1において領域118に構成される回路を第2の回路、その他の領域に構成されるC P U 109などの回路を第1の回路と称する。領域118には、第1外部端子210、第1の外部端子と第1の回路を接続する第1バス211、第1の回路と第2

50

の回路を接続する第 2 バス 212、第 1 外部端子と第 2 の内部回路を接続する第 3 バス 213、第 2 外部端子 215、第 2 外部端子と第 2 の回路を接続する第 4 バス 216、前記第 2 バス 212 と第 3 バス 213 の何れを第 4 バスに接続するかを選択するセレクタ 217、バスドライバ 218、及び第 5 バス 219 を有する。セレクタ 217 は待機状態への遷移過程で第 1 バス 211 を第 4 バス 216 に接続する接続形態を選択する。CPU 109 の状態に着目すると、待機状態は第 1 の回路による命令実行が抑止される状態（第 1 の状態）であり、動作状態は第 1 の回路が命令を実行可能な状態（第 2 の状態）である。第 2 のデータプロセッサ 101 は、待機状態において、第 1 の外部バス 103 を第 2 の外部バス 105 に直接接続することが可能となる。この例では、第 2 のデータプロセッサ 101 の待機状態において第 1 の外部バス 103 のデータを第 2 の外部バス 105 に無条件に伝達するように構成されているが、第 1 の外部バス 103 と第 2 の外部バス 105 を入出力バッファ（図示せず）を介して接続することも可能である。こうすれば第 1 の外部バス 103 から第 2 の外部バス 105 の入出力を制御することが可能となる。

10

#### 【0062】

図 1 及び図 2 において第 2 のデータプロセッサ 101 は 1 個の半導体基板上に構成された、所謂シングルチップのデータプロセッサとして構成される。

#### 【0063】

図 3 にはマルチチップモジュールで第 2 のデータプロセッサ 300 を構成した場合の例が示される。第 2 のデータプロセッサ 300 は第 1 の外部インターフェース回路 119 及び切換え回路 114 の機能を内蔵したチップ 301 とそれ以外の機能を内蔵したチップ 302 で構成される。チップ 302 は内部高速バス 108 への接続部 303 を第 1 の外部インターフェース回路 119 とのインターフェース部としており、この接続部 303 に接続するチップ 301 が内部高速バス 108 のバスマスターになることが可能となる。第 2 のデータプロセッサ 300 の待機状態においてチップ 301 だけを動作させることにより、第 1 の外部バス 103 を第 2 の外部バス 105 へ接続することが可能になる。

20

#### 【0064】

図 4 には第 2 のデータプロセッサ 101 が備える第 1 の外部インターフェース 119 の具体的な一例を示す。第 1 の外部インターフェース回路 119 は外部バスアクセス制御部 401、バス変換調停部 402、内部バスアクセス制御部 403、RAM アクセス制御部 404、リセット／割り込み制御部 405 から構成される。

30

#### 【0065】

第 1 の外部バス 103 からのアクセス情報は外部バスアクセス制御部 401 に入力され、入力情報が同期化されてバス変換調停部 402 へ転送される。バス変換調停部は当該アクセスが RAM 107 へのアクセスか内部バス 108 へのアクセスかを判定し、内部バス 108 へのアクセスであった場合には内部バスアクセス制御部 403 へアクセス要求を出して内部バス 108 のバスアクセス仕様にしたがったバスアクセス動作を起動する。要するに、アドレス信号、バスアクセス制御信号、データを内部バス 108 のバスアクセス仕様に準拠してバス 108 に供給し、また、データをバス 108 から受取る。RAM 107 へのアクセス要求である場合には RAM アクセス制御部 404 にメモリアクセス要求を出して RAM 107 のアクセス仕様に準拠してアクセス動作を起動する。要するに、アドレス信号、メモリ制御信号、データをメモリアクセス仕様にしたがって RAM 107 に供給し、また、データを RAM 107 から受取る。

40

#### 【0066】

CPU 109 への割り込み／リセットの発行や、CPU 109 からの割り込みはリセット／割り込み制御部 405 で処理され、外部バスアクセス制御部 401 が第 1 の外部バス 103 上のデバイスに対して対応する要求を発行する。また、第 1 の外部バス 103 上のデバイスからの要求や RAM アクセス制御部 404 からの動作要求は外部バスアクセス制御部 401 が対応する割込み要求としてリセット／割り込み制御部 405 に与える。

#### 【0067】

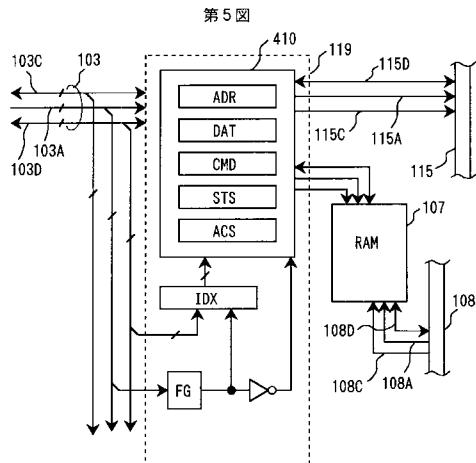

図 5 には第 2 のデータプロセッサ 101 が備える第 1 の外部インターフェース 119 の更

50

に具体的な別の例を示す。同図には、バス 103 との間のインターフェース、バス 115 との間のインターフェース、RAM 107 との間のインターフェースとを実現する為の具体例を示す。第1の外部インターフェース回路 119 は、制御回路 410、インデックスレジスタ IDX、アドレスフラグ FG を有する。制御回路 410 はアドレスレジスタ ADR、データレジスタ DAT、コマンドレジスタ CMD、アクセス制御レジスタ ACS、ステータスレジスタ STS などの制御回路内蔵レジスタを有する。アドレスフラグ FG は、論理値 “1” が設定されると、インデックスレジスタ IDX の選択を指定し、論理値 “0” が設定されると制御回路内蔵レジスタの内のどのレジスタを選択するかはインデックスレジスタ IDX の値で決まる。インデックスレジスタ IDX 及びアドレスフラグ FG は第1の外部バス 103 を介してアクセスされる。バス 103 はデータバス 103D、アドレスバス 103A 及びコントロールバス 103C から成る。インデックスレジスタ IDX の値にしたがって制御回路内蔵レジスタが選択されて、対応するレジスタにデータバス 103D 経由でアドレス情報、データ情報、バスアクセス制御情報、コマンド情報がロードされ、ロードされたコマンド情報に従って、RAM 107 に対するアクセス、バス 115 に対するアクセスが起動される。この時のアクセスには前記レジスタの設定値が用いられ、アクセスタイミングはアクセス制御情報が決定する。外部バス 103 を介して RAM 107 に書き込まれたデータは CPU 109 が内部バス 108 を経由してアクセスすることができる。バス 108 はデータバス 108D、アドレスバス 108A 及びコントロールバス 108C から成る。バス 115 はデータバス 115D、アドレスバス 115A 及びコントロールバス 115C から成る。10

#### 【0068】

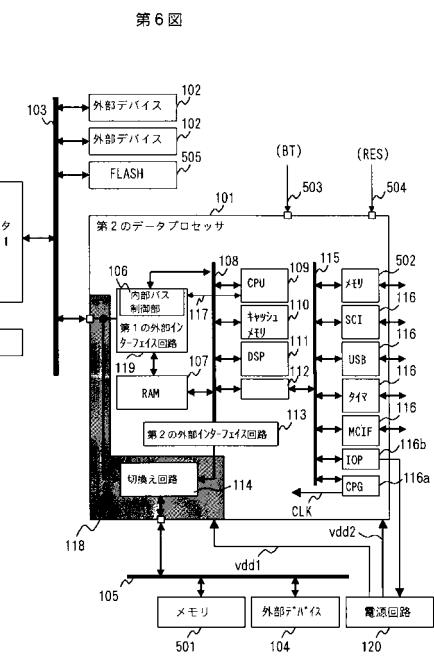

図6には本発明に係るデータ処理システムにおけるデータプロセッサのブートプログラムの初期的書き込みに関する例を示す。図6の例では、CPU 109 の内部バス 115 にメモリ 502 が配置され、また、第2の外部バス 105 にメモリ 501 が配置される。この例では、特に制限されないが、前記メモリ 501, 502 はユーザプログラム格納領域として利用されることになる。その場合には、第2のデータプロセッサ 101 がリセット直後に実行するブートプログラムは、前記メモリ 501 又は 502 に通常格納される。図6では内部メモリ 502 を内部低速バス 115 に接続しているが、内部高速バス 108 に接続してもよい。第2のデータプロセッサの内部メモリ 502 はフラッシュメモリ等のような電気的に書き換え可能な不揮発性メモリであり、CPU 109 等と同じ半導体基板上に形成してもよく、或は異なる半導体基板上にそれぞれを形成し、1のパッケージに封入するものであってもよい。異なる半導体基板上に形成して1のパッケージに封入する場合、第2のデータプロセッサ 101 の内部バス 108, 115 に接続するのではなく、パッケージ内部において第2の外部バス 105 に接続するようにしてもよい。ここでは、電気的に書き換え可能な不揮発性メモリ 501, 502 をプログラムメモリとして利用する。30

#### 【0069】

前記電気的に書き込み可能な不揮発性メモリ 501, 502 に対するプログラムの初期的な書き込みはデータプロセッサ 101 などの半導体集積回路の製造過程において EPR OM ライタのような書き込み装置を用いて行なうことが従来から行われてきた。図6の例では、データプロセッサ 101 がデータ処理システム上に実装された初期的な段階では不揮発性メモリ 501, 502 にブートプログラムが初期書き込みされていない状態を想定する。図6のデータ処理システムはそのような状態からブートプログラムを初期的に書き込み可能とするものである。要するに、第2のデータプロセッサ 101 のブートを RAM 107 から行える仕組みを第2のデータプロセッサ 101 に内蔵させる。即ち、第1のデータプロセッサ 100 から第1の外部バス 103 を経由して第2のデータプロセッサ 101 のブートプログラムを RAM 107 に書き込み、書き込み後に第2のデータプロセッサ 101 に RAM 107 のプログラムを実行させる。そのためには、第2のデータプロセッサ 101 を RAM 107 のプログラム実行により起動するかメモリ 501 又は 502 のプログラム実行により起動するかを切り替える必要がある。この切り替えは、リセット信号（4050

R E S ) 5 0 4 によるリセット動作の指示に際してブートモード信号 ( B T ) 5 0 3 のレベルを用いて行なう。例えばリセット信号 5 0 4 がローレベルの期間に、ブートモード信号 5 0 3 がハイレベルの時は R A M 1 0 7 のプログラム実行から起動し、ブートモード信号 5 0 3 がローレベルの時はメモリ 5 0 1 、 5 0 2 のプログラム実行から起動する。

#### 【 0 0 7 0 】

ブートプログラムの初期的書き込みの為の構成を詳述する。前記第 2 のデータプロセッサ 1 0 1 において、前記 R A M 1 0 7 は、リセット信号 5 0 4 によるリセット動作解除後の第 1 動作モードにおいて前記第 1 のデータプロセッサ 1 0 0 により書き込み可能にされる。前記第 1 動作モードは、例えばリセット信号 5 0 4 がローレベルされるリセット期間に、ブートモード信号 5 0 3 がハイレベルにされていて、リセット信号 5 0 4 がハイレベルにネゲートされてリセット動作が解除された動作状態である。このとき、 C P U 1 0 9 は命令フェッチが抑制される。要するに、 C P U 1 0 9 に対するスタートベクタの供給が抑制されている。このときの R A M 1 0 7 に対するアクセスは前述の通り、第 1 のデータプロセッサ 1 0 0 が第 1 の外部インターフェース回路 1 0 6 に対して行なえばよい。データプロセッサ 1 0 0 による R A M 1 0 7 への書き込みが終了すると、データプロセッサ 1 0 0 から第 1 の外部インターフェース回路 1 1 9 に与えられるコマンドにより、或はブートモード信号 5 0 3 のハイレベルからローレベルへの変化に応答して、 C P U 1 0 9 に R A M 1 0 7 の先頭アドレスを指定するスタートベクタが供給される。これによって C P U 1 0 9 は R A M 1 0 7 に格納されたプログラムを実行する。ここでは、ユーザプログラムの初期的な書き込みという操作に着目しているのであるから、 R A M 1 0 7 に格納される前記プログラムは少なくともユーザプログラムの書き込み制御プログラムであればよい。ユーザプログラム自体も前記プログラムと一緒に R A M 1 0 7 に予め転送されていてよい。或は、 R A M 1 0 7 に転送された書き込み制御プログラムの実行により、ユーザプログラムをシリアルインターフェース回路 1 1 6 等から取り込んでメモリ 5 0 2 などに初期的に書き込むようにしてもよい。

#### 【 0 0 7 1 】

リセット動作解除後の第 2 動作モードでは C P U 1 0 9 による命令フェッチの対象は、前記メモリ 5 0 1 又は 5 0 2 である。前記第 2 動作モードは、例えばリセット信号 5 0 4 がローレベルにされるリセット期間に、ブートモード信号 5 0 3 がローレベルにされて、リセット信号 5 0 4 がハイレベルにネゲートされてリセット動作が解除された動作状態である。これにより、 C P U 1 0 9 は前記第 1 動作モードを介して前記メモリ 5 0 1 又は 5 0 2 に初期的に格納されたユーザプログラムを実行する。

#### 【 0 0 7 2 】

前記第 1 のデータプロセッサ 1 0 0 から R A M 1 0 7 へブートプログラムとしての前記書き込み制御用プログラムを格納する動作を説明する。

#### 【 0 0 7 3 】

先ず、第 2 のデータプロセッサ 1 0 1 をブートする前に、第 1 のデータプロセッサ 1 0 0 に接続しているメモリ 5 0 5 もしくはメモリカード 5 0 6 などの外部記憶もしくは図示を省略するシリアルインターフェースなどから入力したブートプログラムを第 1 のデータプロセッサ 1 0 0 が第 2 のデータプロセッサ 1 0 1 の R A M 1 0 7 に書き込む。

#### 【 0 0 7 4 】

R A M 1 0 7 に転送するブートプログラムはアプリケーションまでを含んだものでも構わないが、次のような処理を含んでいれば短いブートプログラムで対応可能となる。例えば、 R A M 1 0 7 上のプログラムには、第 1 のデータプロセッサ 1 0 0 から第 1 の外部インターフェイス回路 1 1 9 を介してプログラムの転送を行なってメモリ 5 0 1 又は 5 0 2 に書き込むプログラムが格納されている。或は、第 2 のデータプロセッサの周辺デバイス 1 1 6 のシリアル、 U S B 、メモリカードを用いて、プログラムをメモリ 5 0 1 、 5 0 2 に転送して書き込むプログラムが格納される。

#### 【 0 0 7 5 】

上記より、第 2 のデータプロセッサ 1 0 1 のブート用メモリ 5 0 1 、 5 0 2 がフラッシュ

10

20

30

40

50

ユメモリであった場合に、システム組み立ての後工程において本来ならフラッシュメモリを初期化する仕組みが必要であったが、RAM107からブートするモードでフラッシュメモリの初期化を行うことができるようになるため、データプロセッサ101の量産コストを低減することが可能になる。

#### 【0076】

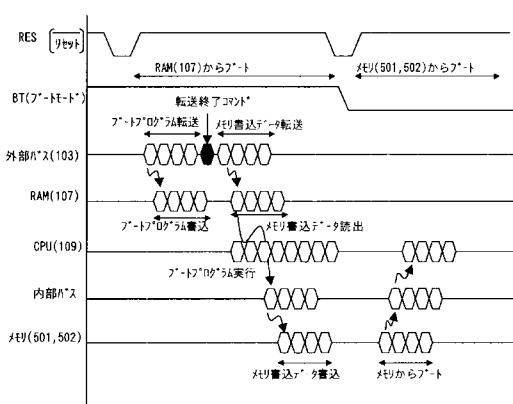

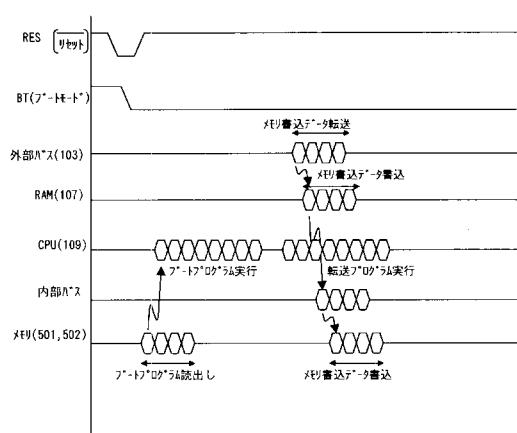

図7には図6のデータ処理システムにおけるブート動作のタイミングチャートが例示される。

#### 【0077】

第1のデータプロセッサ100はブートモード信号503とリセット信号504を供給し、第2のデータプロセッサ101の起動を制御する。

#### 【0078】

第1のデータプロセッサはブートモード信号503をハイレベルにしてリセットを解除（リセット信号をローレベルからハイレベルに遷移）することで、RAM107からブートするモードで第2のデータプロセッサを起動し、第1の外部バス103を介してRAM107にブートプログラムを転送する。第2のデータプロセッサのCPU109は、ブートモード信号がハイレベルであることを検出し、第1の外部インターフェイス回路119を介してRAM107からブートプログラムをフェッチする。CPU109は、ブートプログラムの転送中には命令フェッチが抑止されるため、ブートプログラムの供給が行われず、ウェイトした状態におかれる。ブートプログラムの転送終了にあわせて第1のデータプロセッサ100は転送終了コマンドを第1の外部インターフェイス回路119に転送し、第1の外部インターフェイス回路119はCPU109にブートプログラムのフェッチを指示することで、第2のデータプロセッサ101はRAM107のプログラムで起動する。CPU109はRAM107内のブートプログラムを実行し、内部高速バス108を経由して、メモリ501, 502にブートプログラムを書き込む処理を行なう。メモリ501, 502へのブートプログラムの書き込みが終了した段階で再度第2のデータプロセッサ101をリセットし（リセット信号（RES）504をハイレベルからローレベルに遷移）、次はブートモード信号（BT）503をローレベルにした状態でリセットを解除し、第2のデータプロセッサ101を起動する。これによりCPU109は、メモリ501, 502からブートプログラムをフェッチし、これを実行することにより、第2のデータプロセッサのデータ処理動作が起動される。

#### 【0079】

図7の例は、第1の外部バス103を介して、第1のデータプロセッサ100に接続しているメモリ505若しくはメモリカード506からメモリ501, 502にブートプログラムを供給する動作タイミングを示している。

#### 【0080】

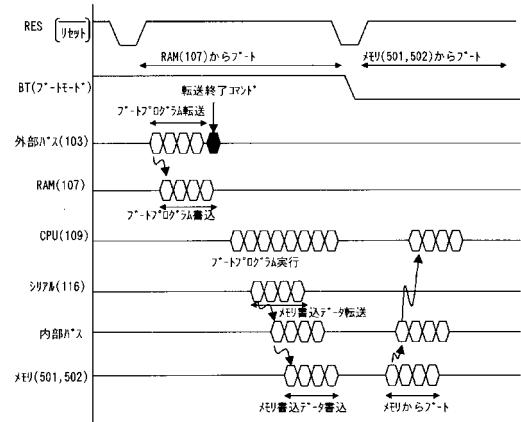

図8には図6のデータ処理システムにおけるブート動作の別のタイミングチャートが例示される。同図に示されるタイミングは、第2のデータプロセッサ101にあるシリアルやUSB116等を介してメモリ501, 502に格納するブートプログラムを供給する場合を想定している。その他の点は図7と同じである。

#### 【0081】

図9にはメモリ501又は502にブートプログラムが格納されている状態において、ブートプログラムの更新又は第2のデータプロセッサ101で実行されるアプリケーションを追加／更新する場合のタイミングチャートが例示される。

#### 【0082】

第1のデータプロセッサ100はブートモード信号503をローレベルにしてリセットを解除することで、第2のデータプロセッサ101はメモリ501, 502からブートプログラムをフェッチし起動を開始する。メモリ501, 502には予めブートプログラムの更新又はプロセッサ2で実行されるアプリケーションを追加／更新するための転送プログラムが格納されており、第1のデータプロセッサ100からの起動指示等により転送プログラムが起動される。例えば第1のデータプロセッサ100に接続されるアンテナを介

10

20

30

40

50

して、無線通信により追加のアプリケーションを受信する場合、第1のプロセッサ100は受信した追加のアプリケーションを外部バス103を介してRAM107に転送する。第2のデータプロセッサ101はRAM107に格納された追加のアプリケーションを第1の外部インターフェイス回路119を介して内部バス108に取り込み、メモリ501又は502に転送して書きを行う。

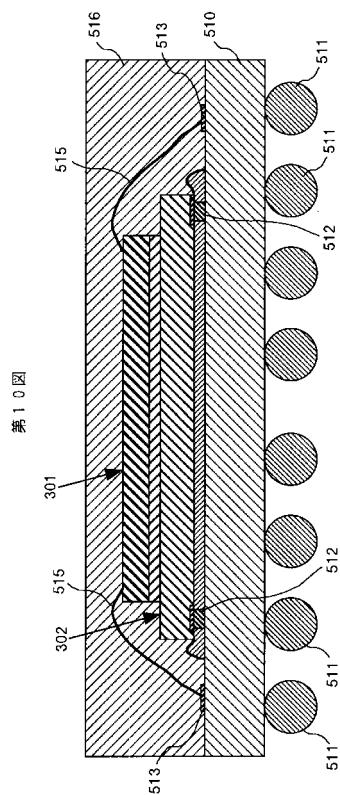

#### 【0083】

図10には図3のデータプロセッサ300を構成するマルチチップモジュールの断面図が例示される。高密度実装基板510の一面には、ガラスエポキシ基板で成るようなプリント配線基板の実装面に接続されるバンプ電極511が多数配列され、他方の面には前記バンプ電極511に接続されたマイクロバンプ電極512及びパッド電極513が多数配置される。マイクロバンプ電極512の一部には前記半導体チップ302のボンディングパッドがフェースダウンで実装される。前記半導体チップ302の上に別の半導体チップ301が積層配置され、この半導体チップ301のボンディングパッドはボンディングワイヤ515にて対応する前記パッド電極513に接続される。ボンディングワイヤ515及び半導体チップ301, 302の全体は樹脂516でモールドされる。

#### 【0084】

以上本発明者によってなされた発明を具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

#### 【0085】

例えばデータプロセッサが内蔵する周辺回路やその他の回路モジュールは図1などに基づいて説明した回路に限定されず適宜変更することが可能である。データプロセッサの内部バスは高速バスと低速バスに別れていなくてもよい。また、第1の回路部と第2の回路部に対する動作電源系統は外部電源端子から別々にしなくとも、スイッチ回路で電源供給の停止を制御できるようにしてもよい。また、データプロセッサをマルチチップモジュールとして構成するとき、登載する半導体集積回路の種類は上記の例に限定されず、フラッシュメモリ502のような半導体チップと、その他CPU109などのプロセッサコアチップ、及び半導体チップ301のようなインタフェースチップを合計3枚登載してもよい。フラッシュメモリチップはマルチチップモジュールに複数チップ登載してもよい。

#### 【0086】

本発明は、携帯電話システム、更には表示制御システム、プリンタシステム、他の携帯情報端末等、複数のデータプロセッサを用いて処理負担の分散を企図したデータ処理システム、そしてそのようなデータ処理システムに利用するデータプロセッサに広く適用することができる。

#### 【符号の説明】

#### 【0087】

- 100 第1のデータプロセッサ

- 101 第2のデータプロセッサ

- 103 第1のバス

- 105 第2のバス

- 113 第2の外部インターフェース回路

- 114 切換え回路

- 119 第1の外部インターフェース回路

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

第7図

【図8】

第8図

【図9】

第9図

【図10】

---

フロントページの続き

(72)発明者 服部 俊洋

東京都小平市上水本町五丁目20番1号 株式会社日立製作所 半導体グループ内

審査官 木村 貴俊

(56)参考文献 特開平09-128323(JP,A)

特開平08-101609(JP,A)

(58)調査した分野(Int.Cl., DB名)

G06F 1/00、 3/06 - 3/08

G06F 13/10 - 13/42、 15/78