(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2009-0045123

(43) 공개일자 2009년05월07일

(51) Int. Cl.

H01L 27/12 (2006.01)

(21) 출원번호 10-2008-0107887

(22) 출원일자 2008년10월31일

심사청구일자 없음

(30) 우선권주장

JP-P-2007-285180 2007년11월01일 일본(JP)

(71) 출원인

가부시키가이샤 한도오따이 에네루기 켄큐쇼

일본국 가나가와Ken 아쓰기시 하세 398

(72) 발명자

시모무라 아키히사

일본국 243-0036 가나가와Ken 아쓰기시 하세 398

가부시키가이샤 한도오따이 에네루기 켄큐쇼 내

모모 준페이

일본국 243-0036 가나가와Ken 아쓰기시 하세 398

가부시키가이샤 한도오따이 에네루기 켄큐쇼 내

(74) 대리인

황의만

전체 청구항 수 : 총 30 항

#### (54) S O I 기판의 제조방법 및 반도체장치의 제조방법

#### (57) 요 약

유리 기판 등 내열 온도가 낮은 기판을 사용한 경우에도, 실용에 견딜 수 있는 단결정 반도체층을 구비한 SOI 기판의 제조방법을 제공하는 것을 목적의 하나로 한다. 또한, 그와 같은 SOI 기판을 사용한 신뢰성이 높은 반도체 장치를 제조하는 것을 목적의 하나로 한다. 단결정 반도체 기판으로부터 지지 기판으로 전재(轉載)되어, 전영역에서 레이저광 조사에 의한 용융 상태를 거쳐 재단결정화된 단결정 반도체층을 가지는 SOI 기판을 사용한다. 따라서, 단결정 반도체층은 결정 결합도 저감되고 결정성이 높고, 또한, 평탄성도 높다.

#### 대 표 도 - 도1

## 특허청구의 범위

### 청구항 1

SOI 기판을 제조하는 방법으로서,

반도체 기판에 이온을 첨가하여, 상기 반도체 기판에 취약화층을 형성하는 공정;

적어도 하나의 절연층을 사이에 두고 상기 반도체 기판을 지지 기판에 접합하는 공정;

상기 반도체 기판을 상기 취약화층에서 분리하는 열처리를 행하여, 상기 지지 기판 위에 반도체층을 형성하는 공정; 및

상기 반도체층에 펠스 발진 레이저광을 조사하여, 상기 반도체층의 전체 두께에 걸쳐 조사 영역을 용융시키는 공정을 포함하는, SOI 기판 제조방법.

### 청구항 2

제 1 항에 있어서, 상기 반도체 기판이 상기 절연층을 사이에 두고 상기 지지 기판에 접합되도록 상기 반도체 기판과 상기 지지 기판의 적어도 한쪽 표면 위에 상기 절연층을 형성하는 공정을 더 포함하는, SOI 기판 제조방법.

### 청구항 3

제 1 항에 있어서, 상기 반도체 기판이 단결정 반도체 기판이고, 상기 반도체층이 상기 펠스 발진 레이저광의 조사에 의해 재결정화되는, SOI 기판 제조방법.

### 청구항 4

제 1 항에 있어서, 상기 반도체층에서의 상기 조사 영역의 단축 방향에서의 상기 펠스 발진 레이저광의 레이저 광 프로파일이 직사각형 형상과  $20 \mu\text{m}$  이하의 폭을 가지는, SOI 기판 제조방법.

### 청구항 5

제 1 항에 있어서, 상기 반도체층에서의 상기 조사 영역의 단축 방향에서의 상기 펠스 발진 레이저광의 레이저 광 프로파일이 가우시안(Gaussian) 형상과  $100 \mu\text{m}$  이하의 폭을 가지는, SOI 기판 제조방법.

### 청구항 6

제 1 항에 있어서, 상기 반도체층에서의 상기 조사 영역의 형상이 직사각형인, SOI 기판 제조방법.

### 청구항 7

제 1 항에 있어서, 용융된 반도체층의 결정 성장이, 그 용융된 반도체층에 인접하는, 단결정 반도체층의 비용융 영역을 결정핵으로 하여 일어나는, SOI 기판 제조방법.

### 청구항 8

제 1 항에 있어서, 상기 반도체층이, 상기 반도체층을 가열하면서 상기 펠스 발진 레이저광을 조사함으로써 재 결정화되는, SOI 기판 제조방법.

### 청구항 9

제 1 항에 있어서, 상기 반도체 기판에 상기 이온을 첨가하는 방법으로서 이온 도핑법이 사용되는, SOI 기판 제조방법.

### 청구항 10

제 1 항에 있어서, 상기 지지 기판이 유리 기판인, SOI 기판 제조방법.

### 청구항 11

SOI 기판을 제조하는 방법으로서,

단결정 반도체 기판에 이온을 첨가하여, 상기 단결정 반도체 기판에 쥐약화층을 형성하는 공정;

적어도 하나의 절연층을 사이에 두고 상기 단결정 반도체 기판을 지지 기판에 접합하는 공정;

상기 단결정 반도체 기판을 상기 쥐약화층에서 분리하는 열처리를 행하여, 상기 지지 기판 위에 단결정 반도체 층을 형성하는 공정; 및

상기 단결정 반도체층에 펠스 발진 레이저광을 조사하여, 상기 단결정 반도체층의 전체 두께에 걸쳐 조사 영역을 용융시키는 공정을 포함하고,

상기 단결정 반도체층의 용융 영역의 단부로부터 상기 용융 영역의 중앙을 향하여 상기 지지 기판의 표면에 평행한 방향으로 결정 성장이 일어나, 재(再)단결정화가 일어나는, SOI 기판 제조방법.

#### 청구항 12

제 11 항에 있어서, 상기 단결정 반도체 기판이 상기 절연층을 사이에 두고 상기 지지 기판에 접합되도록 상기 단결정 반도체 기판과 상기 지지 기판의 적어도 한쪽 표면 위에 상기 절연층을 형성하는 공정을 더 포함하는, SOI 기판 제조방법.

#### 청구항 13

제 11 항에 있어서, 상기 단결정 반도체층에서의 상기 조사 영역의 단축 방향에서의 상기 펠스 발진 레이저광의 레이저광 프로파일이 직사각형 형상과  $20 \mu\text{m}$  이하의 폭을 가지는, SOI 기판 제조방법.

#### 청구항 14

제 11 항에 있어서, 상기 단결정 반도체층에서의 상기 조사 영역의 단축 방향에서의 상기 펠스 발진 레이저광의 레이저광 프로파일이 가우시안(Gaussian) 형상과  $100 \mu\text{m}$  이하의 폭을 가지는, SOI 기판 제조방법.

#### 청구항 15

제 11 항에 있어서, 상기 단결정 반도체층에서의 상기 조사 영역의 형상이 직사각형인, SOI 기판 제조방법.

#### 청구항 16

제 11 항에 있어서, 용융된 단결정 반도체층의 결정 성장이, 그 용융된 단결정 반도체층에 인접하는, 단결정 반도체층의 비용융 영역을 결정핵으로 하여 일어나는, SOI 기판 제조방법.

#### 청구항 17

제 11 항에 있어서, 상기 단결정 반도체층이, 상기 단결정 반도체층을 가열하면서 상기 펠스 발진 레이저광을 조사함으로써 재결정화되는, SOI 기판 제조방법.

#### 청구항 18

제 11 항에 있어서, 상기 단결정 반도체 기판에 상기 이온을 첨가하는 방법으로서 이온 도핑법이 사용되는, SOI 기판 제조방법.

#### 청구항 19

제 11 항에 있어서, 상기 지지 기판이 유리 기판인, SOI 기판 제조방법.

#### 청구항 20

반도체장치를 제조하는 방법으로서,

반도체 기판에 이온을 첨가하여, 상기 반도체 기판에 쥐약화층을 형성하는 공정;

적어도 하나의 절연층을 사이에 두고 상기 반도체 기판을 지지 기판에 접합하는 공정;

상기 반도체 기판을 상기 쥐약화층에서 분리하는 열처리를 행하여, 상기 지지 기판 위에 반도체층을 형성하는

공정;

상기 반도체층에 펄스 발진 레이저광을 조사하여, 상기 반도체층의 전체 두께에 걸쳐 조사 영역을 용융시키는 공정; 및

상기 반도체층을 사용하여 반도체 소자를 형성하는 공정을 포함하는, 반도체장치 제조방법.

### 청구항 21

제 20 항에 있어서, 상기 반도체 기판이 상기 절연층을 사이에 두고 상기 지지 기판에 접합되도록 상기 반도체 기판과 상기 지지 기판의 적어도 한쪽 표면 위에 상기 절연층을 형성하는 공정을 더 포함하는, 반도체장치 제조방법.

### 청구항 22

제 20 항에 있어서, 상기 반도체 기판이 단결정 반도체 기판이고, 상기 반도체층이 상기 펄스 발진 레이저광의 조사에 의해 재결정화되는, 반도체장치 제조방법.

### 청구항 23

제 20 항에 있어서, 상기 반도체층에서의 상기 조사 영역의 단축 방향에서의 상기 펄스 발진 레이저광의 레이저 광 프로파일이 직사각형 형상과  $20 \mu\text{m}$  이하의 폭을 가지는, 반도체장치 제조방법.

### 청구항 24

제 20 항에 있어서, 상기 반도체층에서의 상기 조사 영역의 단축 방향에서의 상기 펄스 발진 레이저광의 레이저 광 프로파일이 가우시안(Gaussian) 형상과  $100 \mu\text{m}$  이하의 폭을 가지는, 반도체장치 제조방법.

### 청구항 25

제 20 항에 있어서, 상기 반도체층에서의 상기 조사 영역의 형상이 직사각형인, 반도체장치 제조방법.

### 청구항 26

제 20 항에 있어서, 용융된 반도체층의 결정 성장이, 그 용융된 반도체층에 인접하는, 단결정 반도체층의 비용 용 영역을 결정핵으로 하여 일어나는, 반도체장치 제조방법.

### 청구항 27

제 20 항에 있어서, 상기 반도체층이, 상기 반도체층을 가열하면서 상기 펄스 발진 레이저광을 조사함으로써 재 결정화되는, 반도체장치 제조방법.

### 청구항 28

제 20 항에 있어서, 상기 반도체 기판에 상기 이온을 첨가하는 방법으로서 이온 도핑법이 사용되는, 반도체장치 제조방법.

### 청구항 29

제 20 항에 있어서, 상기 지지 기판이 유리 기판인, 반도체장치 제조방법.

### 청구항 30

제 20 항에 있어서, 상기 반도체 소자에 전기적으로 접속되는 표시 소자를 형성하는 공정을 더 포함하는, 반도체장치 제조방법.

## 명세서

### 발명의 상세한 설명

### 기술 분야

<1> 본 발명은 절연 표면에 단결정 반도체층이 형성된 반도체 기판의 제조방법 및 반도체장치의 제조방법에 관한 것이다.

### 배경기술

<2> 단결정 반도체의 잉곳(ingot)을 얇게 슬라이스하여 제조되는 실리콘 웨이퍼를 대신하여, 절연 표면에 얇은 단결정 반도체층을 형성한 실리콘 온 인솔레이터(Silicon on Insulator, 이하, "SOI"라고도 한다)라고 불리는 반도체 기판을 사용한 집적회로가 개발되어 있다. SOI 기판을 사용한 집적회로는, 트랜지스터의 드레인과 기판 간의 기생 용량을 저감하여, 반도체 집적회로의 성능을 향상시키는 것으로서 주목을 집중시키고 있다.

<3> SOI 기판을 제조하는 방법으로서는, 수소 이온 첨가 박리법이 알려져 있다(예를 들어, 문헌 1 참조). 수소 이온 첨가 박리법은, 실리콘 웨이퍼에 수소 이온을 첨가함으로써 표면으로부터 소정의 깊이에 미소(微小) 기포층을 형성하고, 이 미소 기포층을 벽개면(劈開面)으로 함으로써, 다른 실리콘 웨이퍼에 얇은 실리콘층을 접합한다. 또한, 실리콘층을 박리하는 열처리를 행하는 것에 더하여, 산화성 분위기하에서의 열처리에 의해 실리콘층에 산화막을 형성한 후에, 이 산화막을 제거하고, 다음에 1000°C 내지 1300°C로 열처리를 행하여 접합 강도를 높일 필요가 있다고 생각되고 있다.

<4> 한편, 고내열성 유리 등의 절연 기판에 실리콘층을 형성한 반도체장치가 개시되어 있다(예를 들어, 문헌 2 참조). 이 반도체장치는, 왜곡점이 750°C 이상인 결정화 유리의 전면(全面)을 절연성 실리콘막으로 보호하고, 수소 이온 첨가 박리법에 의해 얻어지는 실리콘층을 이 절연성 실리콘막 위에 고착하는 구성을 가지고 있다.

<5> [문헌 1] 일본국 공개특허공고 2000-124092호 공보

<6> [문헌 2] 일본국 공개특허공고 평11-163363호 공보

### 발명의 내용

#### 해결 하고자하는 과제

<7> 또한, 상기 미소 기포층을 형성하기 위하여 행하는 이온 첨가 공정에서, 실리콘층은 첨가되는 이온에 의해 대미지(damage)를 받게 된다. 상기 실리콘층과 지지 기판과의 접합 강도를 높이는 열처리에서, 이온 첨가 공정에 의한 실리콘층에의 대미지의 회복도 행하고 있다.

<8> 그러나, 지지 기판에 유리 기판 등 내열 온도가 낮은 기판을 사용하는 경우, 1000°C 이상의 열처리를 행할 수 없고, 상기 이온 첨가 공정에 의한 실리콘층의 대미지에 대하여 충분히 회복을 행할 수는 없었다.

<9> 이러한 문제점을 감안하여, 유리 기판 등 내열 온도가 낮은 기판을 사용한 경우에도, 실용에 견딜 수 있는 단결정 반도체층을 구비한 SOI 기판(이하, 반도체 기판이라고도 한다)의 제조방법을 제공하는 것을 목적의 하나로 한다. 또한, 그와 같은 반도체 기판을 사용한 신뢰성이 높은 반도체장치를 제조하는 것을 목적의 하나로 한다.

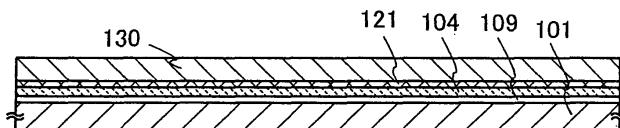

#### 과제 해결수단

<10> 반도체 기판의 제조에 있어서, 단결정 반도체 기판으로부터 분리되어, 절연 표면을 가지는 지지 기판에 접합된 단결정 반도체층의 결정성을 회복하기 위하여, 펠스 발진 레이저광을 조사하는 것을 요지로 한다. 펠스 발진 레이저광의 조사에 의해 단결정 반도체층의 조사 영역 전역을 용융시키고, 그 후의 냉각 과정에서, 이 조사 영역에 인접하는 단결정 영역을 결정 성장의 핵으로서 사용함으로써, 재단결정화를 행한다.

<11> 펠스 발진 레이저광의 조사에 의해 단결정 반도체층의 깊이 방향도 포함하는 조사 영역 전역을 용융시키고, 재단결정화시킴으로써 단결정 반도체층 중의 결정 결함을 저감시킨다. 펠스 발진 레이저광의 조사 처리를 사용하기 때문에, 지지 기판의 온도 상승이 억제되어, 유리 기판과 같은 내열성이 낮은 기판을 지지 기판에 사용하는 것이 가능하게 된다. 따라서, 단결정 반도체층에의 이온 첨가 공정에 의한 대미지를 충분히 회복시킬 수 있다.

<12> 또한, 단결정 반도체층은 용융하고 재단결정화함으로써 표면을 평탄화할 수 있다. 따라서, 펠스 발진 레이저광의 조사에 의한 단결정 반도체층의 재단결정화에 의해, 결정 결함이 저감되고, 또한, 평탄성도 높은 단결정 반도체층을 가지는 반도체 기판을 제작할 수 있다.

<13> 단결정 반도체층의 재단결정화에 사용하는 레이저광은 단결정 반도체층에 높은 에너지를 부여하는 것이면 좋고, 대표적으로는 펠스 발진 레이저광을 사용할 수 있다. 레이저광의 파장은 190 nm~600 nm로 하면 좋다.

- <14> 본 발명에서는, 단결정 반도체층의 레이저광이 조사되는 영역의 깊이 방향도 포함하여 전부를 용융한다. 따라서 본 발명에서는, 단결정 반도체층에서 레이저광 조사 영역은 전(全)영역(면 방향 및 깊이 방향)에 있어서 용융 영역이 된다. 본 명세서에서, 단결정 반도체층에서의 레이저광 조사 영역의 전영역이란, 단결정 반도체층의 레이저광이 조사되는 영역의 면 방향 및 깊이 방향도 포함하여 모든 영역을 가리킨다. 또한, 단결정 반도체층에서, 레이저광 조사 영역의 전영역을 적어도 깊이 방향으로 완전히 용융하기 때문에, 완전 용융한다고 할 수도 있다.

- <15> 따라서, 재단결정화의 결정핵(종(種)결정)은, 주위의 레이저광 비(非)조사 영역인 비용융 영역이며, 비용융 영역을 결정핵으로 하여, 용융 영역 중앙을 향하여 단결정 반도체층(지지 기판) 표면에 평행한 방향으로 결정 성장한다. 결정 성장은, 용융 영역 단부에서 용융 영역과 비용융 영역과의 계면으로부터 각각 용융 영역 내부(중앙)를 향하여 발생하고, 결정 성장에 의한 재단결정 영역끼리가 접합으로써, 레이저광 조사 영역 전역에서 단결정 반도체층을 재단결정화한다.

- <16> 본 발명에서는, 레이저광의 조사에 의해 생기는 결정 성장이, 단결정 반도체층(지지 기판) 표면에 평행한 방향으로 발생하므로, 단결정 반도체층(지지 기판) 표면에 대하여 깊이 방향(막 두께 방향)을 종방향으로 하면, 횡성장(횡방향의 성장)의 결정 성장이라고도 한다.

- <17> 이 용융 영역의 결정 성장은, 레이저광의 조사에 의해, 단결정 반도체층의 레이저광 조사 영역이 융점 이상으로 가열되어 용융하고, 조사 후의 냉각시에 융점 이하가 되어도 고화하지 않고 용융 상태인 채인 과냉각 상태일 때에 생긴다. 과냉각 상태의 시간은, 단결정 반도체층의 막 두께, 레이저광의 조사 조건(에너지 밀도, 조사 시간(펄스폭) 등) 등에 의존한다. 과냉각 상태의 시간이 길면, 결정 성장에 의해 재단결정화하는 영역도 넓어지기 때문에, 1회의 레이저광 조사 영역도 넓게 할 수 있다. 따라서 처리 효율이 향상되고, 스루풋도 높아진다. 또한, 지지 기판을 가열하면 냉각 상태의 사간의 연장에 효과적이다.

- <18> 따라서, 본 발명에서는 그 재단결정화에 의한 단결정 영역 단부(결정 성장의 단부)끼리가 접하는 영역의 넓이에 레이저광 조사 영역(용융 영역)을 설정한다. 예를 들어, 펄스 발진 레이저광의 단결정 반도체층에서의 조사 영역의 단축 방향의 레이저광 프로파일(빔 프로파일이라고도 한다)의 형상은 직사각형이고, 또한, 폭을  $20 \mu\text{m}$  이하로 한다. 또한, 펄스 발진 레이저광의 단결정 반도체층에서의 조사 영역의 단축 방향의 레이저광 프로파일의 형상은 가우시안(Gaussian)이고, 또한, 폭을  $100 \mu\text{m}$  이하로 한다. 레이저광의 펄스폭을 길게 하면, 레이저광 프로파일의 폭도 길게 할 수 있다. 상기와 같이 레이저광 프로파일을 설정하면, 과냉각 상태의 시간 내에 용융 영역 전역을 결정 성장에 의해 형성되는 재단결정 영역으로 할 수 있다. 또한, 펄스 발진 레이저광의 상기 단결정 반도체층에서의 조사 영역의 형상은 직사각형(선형 레이저에 의한 긴 직사각형 형상이어도 좋다)을 사용할 수 있고, 또한 마스크를 사용하여 다수의 직사각형을 가지는 레이저 형상을 사용하여도 좋다.

- <19> 여기서는, 단결정이란, 어느 결정축에 주목한 경우, 그 결정축의 방향이 시료의 어느 부분에서도 같은 방향을 향하고 있는 결정을 말하고, 또한, 결정과 결정과의 사이에 결정립계가 존재하지 않는 결정이다. 또한, 본 명세서에서는, 결정 결함이나 댕글링 본드(dangling bond)를 포함하고 있어도, 상기와 같이 결정축의 방향이 정렬되어 있고, 입계가 존재하지 않은 결정은 단결정이라고 한다. 또한, 단결정 반도체층의 재단결정화란, 단결정 구조의 반도체층이, 그 단결정 구조와 다른 상태(예를 들어, 액상(液相) 상태)를 거쳐, 다시 단결정 구조가 되는 것을 말한다. 또는, 단결정 반도체층의 재단결정화란, 단결정 반도체층을 재결정화하여, 단결정 반도체층을 형성하게 할 수도 있다.

- <20> 본 명세서에서, 단결정 반도체 기판으로부터 단결정 반도체층을 분리시키고, 지지 기판에 접합하여 제공하는 것을, 단결정 반도체층을 단결정 반도체 기판으로부터 지지 기판에 전재(轉載)(전치(轉置)라고도 한다)한다고 한다. 따라서, 본 발명에서, 트랜지스터는 지지 기판 위에 단결정 반도체 기판으로부터 전재된 단결정 반도체층을 포함한다.

- <21> 본 발명의 반도체 기판 제조방법의 일 형태는, 단결정 반도체 기판의 하나의 면으로부터 이온을 첨가하여, 단결정 반도체 기판의 하나의 면으로부터 일정 깊이에 쥐약화층을 형성한다. 단결정 반도체 기판의 하나의 면 위, 또는 지지 기판 위의 어느 한쪽에 절연층을 형성한다. 단결정 반도체 기판과 지지 기판을, 절연층을 끼우고 중첩시킨 상태에서 쥐약화층에 균열을 발생시켜, 단결정 반도체 기판을 쥐약화층에서 분리하는 열처리를 행하여, 단결정 반도체 기판으로부터 단결정 반도체층을 지지 기판 위에 형성한다. 단결정 반도체층에 펄스 발진 레이저광을 조사하여 단결정 반도체층의 깊이 방향도 포함하는 조사 영역 전역을 용융하여 재단결정화한다.

- <22> 본 발명의 반도체 기판 제조방법의 일 형태는, 단결정 반도체 기판의 하나의 면으로부터 이온을 첨가하여, 단결

정 반도체 기판의 하나의 면으로부터 일정 깊이에 취약화층을 형성한다. 단결정 반도체 기판의 하나의 면 위, 또는 지지 기판 위의 어느 한쪽에 절연층을 형성한다. 단결정 반도체 기판과 지지 기판을, 절연층을 끼우고 중첩시킨 상태에서 취약화층에 균열을 발생시켜, 단결정 반도체 기판을 취약화층에서 분리하는 열처리를 행하여, 단결정 반도체 기판으로부터 분리된 단결정 반도체층을 지지 기판 위에 형성한다. 단결정 반도체층에 펄스 발진 레이저광을 조사하여 단결정 반도체층의 깊이 방향도 포함하는 조사 영역 전역을 용융하고, 용융한 단결정 반도체층은 용융 영역 단부로부터 용융 영역 중앙을 향하여 지지 기판의 표면에 평행한 방향으로 결정 성장하여 재단결정화한다.

## 효과

- <23> 전영역에서 레이저광에 의해 용융되고 재단결정화된 단결정 반도체층을 사용함으로써, 유리 기판 등 내열 온도가 낮은 기판을 사용한 경우에도, 실용에 견딜 수 있는 결정 결함이 저감되고 결정성이 높고, 또한, 평탄성도 높은 단결정 반도체층을 가지는 반도체 기판을 제작할 수 있다.

- <24> 그와 같은 반도체 기판에 제공된 단결정 반도체층을 사용하여, 고성능 및 고신뢰성의 다양한 반도체소자, 기억소자, 집적회로 등을 포함하는 반도체장치를 수율 좋게 제작할 수 있다.

## 발명의 실시를 위한 구체적인 내용

- <25> 본 발명의 실시형태에 대하여 도면을 사용하여 상세하게 설명한다. 그러나, 본 발명은 이하의 설명에 한정되는 것은 아니고, 본 발명의 취지 및 그 범위로부터 벗어남이 없이 그 형태 및 상세한 사항을 다양하게 변경할 수 있다는 것은 당업자라면 용이하게 이해할 수 있다. 따라서, 본 발명은 이하에 나타내는 실시형태의 기재 내용에 한정하여 해석되는 것은 아니다. 또한, 이하에 설명하는 본 발명의 구성에서, 동일 부분 또는 동일한 기능을 가지는 부분에는 동일한 부호를 다른 도면 간에 공통으로 사용하고, 그 반복 설명은 생략한다.

- <26> [실시형태 1]

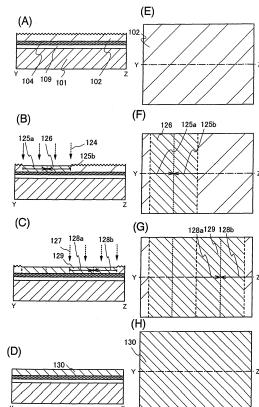

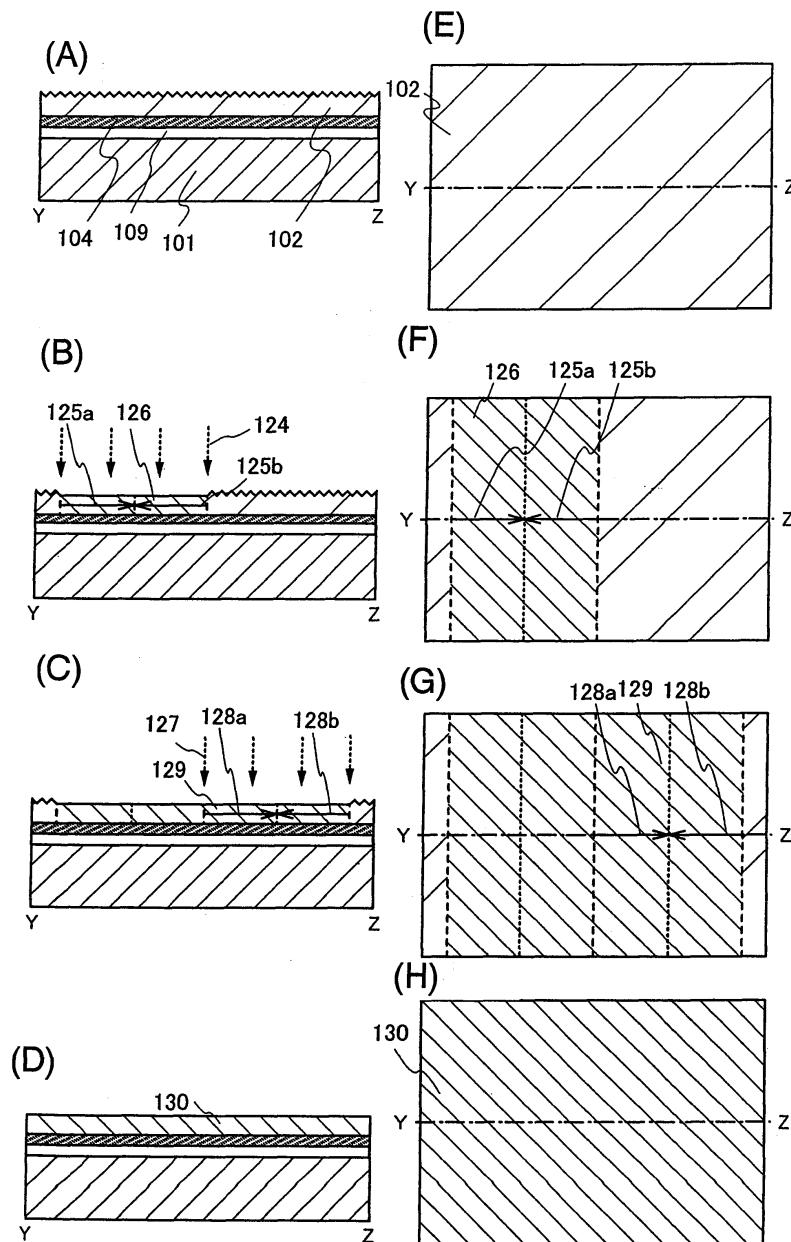

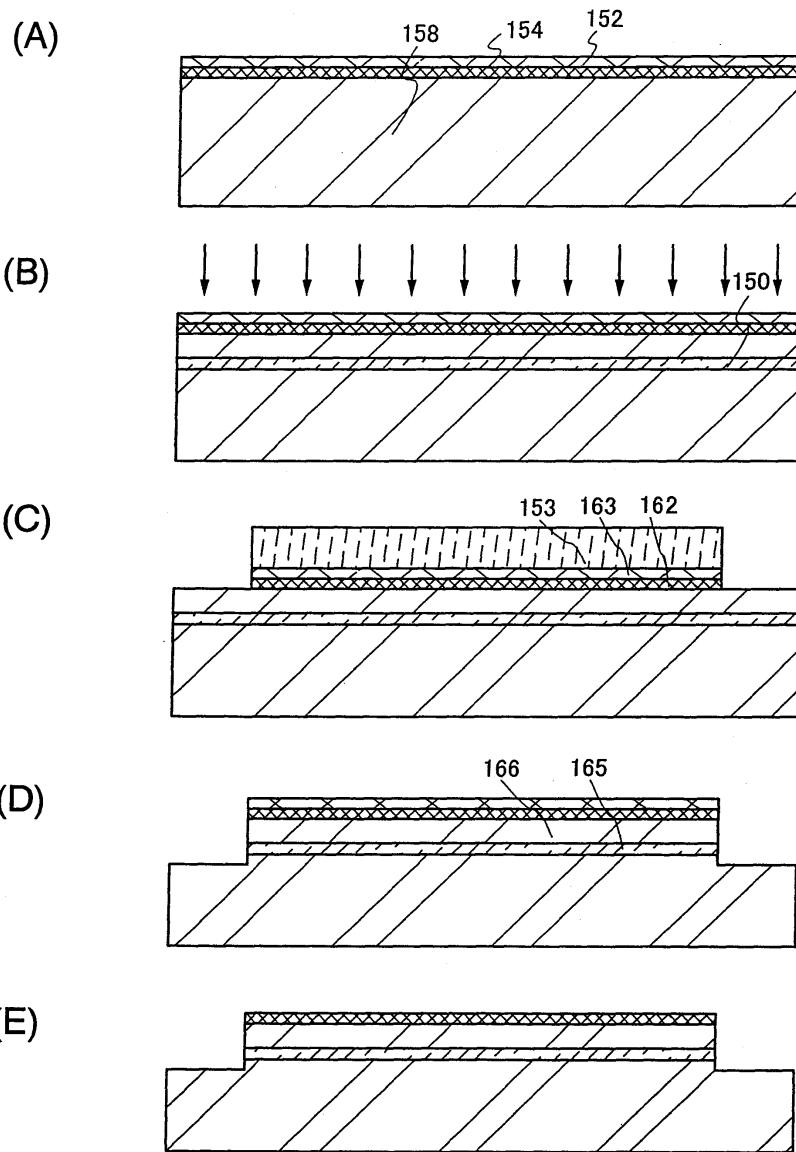

- <27> 본 발명의 반도체장치 제조방법에 대하여, 도 1 내지 도 4를 참조하여 설명한다.

- <28> 본 실시형태에서는, 반도체 기판의 제조에 있어서, 단결정 반도체 기판으로부터 분리되어, 절연 표면을 가지는 지지 기판에 접합된 단결정 반도체층을 재단결정화하기 위하여 펄스 발진 레이저광을 조사한다.

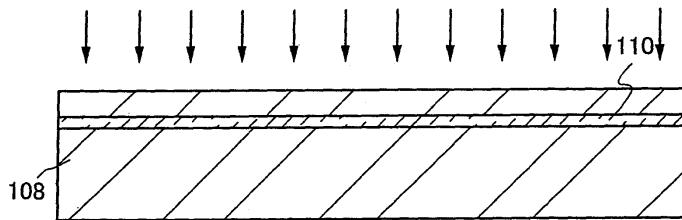

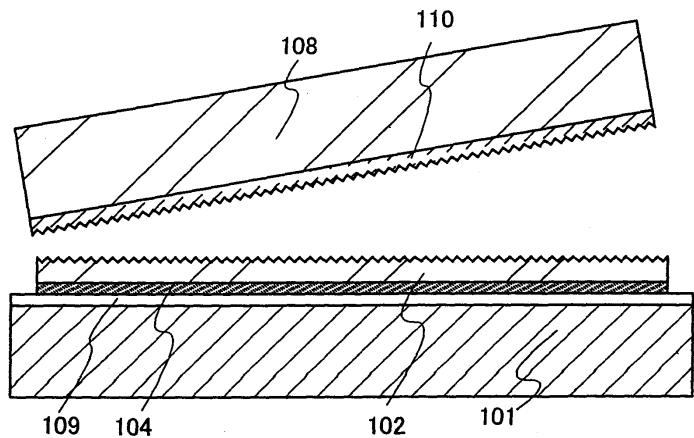

- <29> 먼저, 절연 표면을 가지는 기판인 지지 기판 위에, 단결정 반도체 기판으로부터 단결정 반도체층을 제공하는 방법을 도 3(A)~도 3(D) 및 도 4(A)~도 4(C)를 사용하여 설명한다.

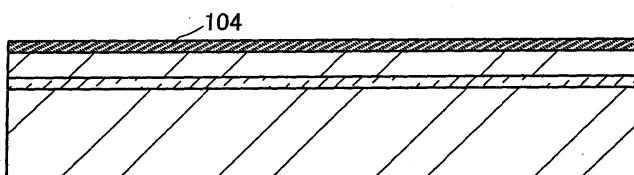

- <30> 도 3(A)에 나타내는 단결정 반도체 기판(108)은 청정화되어 있고, 그 표면으로부터 전계에 의해 가속된 이온을 소정의 깊이에 첨가하여, 취약화층(110)을 형성한다. 이온의 첨가는 지지 기판에 전재하는 단결정 반도체층의 두께를 고려하여 행해진다. 이온을 첨가할 때의 가속 전압은 이러한 두께를 고려하여, 단결정 반도체 기판(108)에 첨가되도록 한다. 본 발명에서는, 단결정 반도체 기판에 이온을 첨가하고, 이온에 의해 미소한 공동(空洞)을 가지도록 취약화된 영역을 취약화층이라고 한다.

- <31> 단결정 반도체 기판(108)에는, 시판(市販)의 단결정 반도체 기판을 사용할 수 있고, 예를 들어, 단결정 실리콘 기판, 단결정 게르마늄 기판, 단결정 실리콘 게르마늄 기판 등, 제4족 원소로 이루어지는 단결정 반도체 기판을 사용할 수 있다. 또한, 갈륨 비소나 인듐 인 등의 화합물 반도체 기판도 사용할 수 있다. 물론, 단결정 반도체 기판은, 원형의 웨이퍼에 한정되는 것은 아니고, 다양한 형상의 단결정 반도체 기판을 사용할 수 있다. 예를 들어, 장방형, 오각형, 육각형 등의 다각형의 기판을 사용할 수 있다. 물론, 시판의 원 형상의 단결정 반도체 웨이퍼를 단결정 반도체 기판에 사용하는 것도 가능하다. 원 형상의 단결정 반도체 웨이퍼에는, 실리콘이나 게르마늄 등의 반도체 웨이퍼, 갈륨 비소나 인듐 인 등의 화합물 반도체 웨이퍼 등이 있다. 단결정 반도체 웨이퍼의 대표예는 단결정 실리콘 웨이퍼이고, 직경 5 인치(125 mm), 직경 6 인치(150 mm), 직경 8 인치(200 mm), 직경 12 인치(300 mm) 사이즈, 직경 400 mm, 직경 450 mm의 원형의 웨이퍼를 사용할 수 있다. 또한, 장방형의 단결정 반도체 기판은 시판의 원 형상의 단결정 반도체 웨이퍼를 절단함으로써 형성할 수 있다. 기판의 절단에는, 다이서(dicer) 또는 와이어 소(wiresaw) 등의 절단 장치, 레이저 절단, 플라즈마 절단, 전자빔 절단, 그 외 임의의 절단 수단을 사용할 수 있다. 또한, 기판으로서 박편화하기 전의 반도체 기판 제조용의 잉곳을, 그의 단면이 장방형이 되도록 직방체 형상으로 가공하고, 이 직방체 형상의 잉곳을 박편화하는 것에 의해서도, 장방형 형상의 단결정 반도체 기판을 제작할 수 있다. 또한, 단결정 반도체 기판의 두께는 특별히 한정되지 않지만, 단결정 반도체 기판을 재이용하는 것을 고려하면, 두꺼운 것이 1장의 원료 웨이퍼로부터 보다 많은 단

결정 반도체층을 형성할 수 있기 때문에 바람직하다. 시장에 유통되고 있는 단결정 실리콘 웨이퍼의 두께는, 그 사이즈가 SEMI 규격에 준하고 있고, 예를 들어, 직경 6 인치의 웨이퍼는 막 두께  $625 \mu\text{m}$ , 직경 8 인치의 웨이퍼는 막 두께  $725 \mu\text{m}$ , 직경 12 인치의 웨이퍼는  $775 \mu\text{m}$ 로 되어 있다. 또한, SEMI 규격의 웨이퍼의 두께는 공차(公差)  $\pm 25 \mu\text{m}$ 를 포함하고 있다. 물론, 원료가 되는 단결정 반도체 기판의 두께는 SEMI 규격에 한정되는 것은 아니고, 임곳을 슬라이스할 때, 그 두께를 적절히 조절할 수 있다. 물론, 재이용된 단결정 반도체 기판(108)을 사용할 때는, 그 두께는, SEMI 규격보다 얇게 된다. 지지 기판 위에 얹어지는 단결정 반도체층은 모체가 되는 반도체 기판을 선택함으로써 결정될 수 있다.

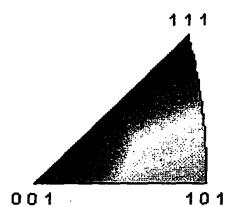

<32> 또한, 단결정 반도체 기판(108)은, 제조하는 반도체소자(본 실시형태에서는 전계효과 트랜지스터)에 따라, 결정면방위를 선택하면 좋다. 예를 들어, 결정면방위로서 {100}면, {110}면 등을 가지는 단결정 반도체 기판을 사용할 수 있다.

<33> 본 실시형태는, 단결정 반도체 기판의 소정의 깊이에 수소, 헬륨, 또는 불소를 이온 첨가하고, 그 후 열처리를 행하여 표층의 단결정 반도체층을 박리하는 이온 첨가 박리법으로 형성하지만, 다공질 실리콘(porous silicon) 위에 단결정 실리콘을 에피택셜 성장시킨 후, 다공질 실리콘층을 워터 제트로 벽개하여 박리하는 방법을 적용하여도 좋다.

<34> 예를 들어, 단결정 반도체 기판(108)으로서 단결정 실리콘 기판을 사용하고, 희불산으로 표면을 처리하고, 자연산화막의 제거와 표면에 부착하는 먼지 등의 오염물도 제거하여 단결정 반도체 기판(108) 표면을 청정화한다.

<35> 취약화층(110)은, 이온을 이온 도핑법(ID법이라고 약기한다)이나 이온 주입법(II법이라고 약기한다)에 의해 첨가(도입)하면 좋다. 취약화층(110)은 수소, 헬륨 또는 불소로 대표되는 할로겐의 이온을 첨가함으로써 형성된다. 할로겐 원소로서 불소 이온을 첨가하는 경우에는 소스 가스로서  $\text{BF}_3$ 를 사용하면 좋다. 또한, 이온 주입이란, 이온화한 가스를 질량 분리하여 반도체에 첨가하는 방식을 말한다.

<36> 예를 들어, 이온 주입법을 이용하여, 이온화한 수소 가스를 질량 분리하고,  $\text{H}^+$ 만(또는  $\text{H}_2^+$ 만)을 선택적으로 가속하여 첨가할 수 있다.

<37> 이온 도핑법은, 이온화한 가스를 질량 분리하지 않고, 플라즈마 중에서 다수종의 이온종(種)을 만들고, 그것들을 가속하여 단결정 반도체 기판에 도핑한다. 예를 들어,  $\text{H}^+$ ,  $\text{H}_2^+$ ,  $\text{H}_3^+$  이온을 포함하는 수소에서는, 도핑되는 이온은 대표적으로  $\text{H}_3^+$  이온이 50% 이상, 예를 들어,  $\text{H}_3^+$  이온이 80%, 다른 이온( $\text{H}^+$ ,  $\text{H}_2^+$  이온)이 20%가 일반적이다.  $\text{H}_3^+$  이온의 이온종만으로서 첨가하는 것도 여기서는 이온 도핑으로 한다.

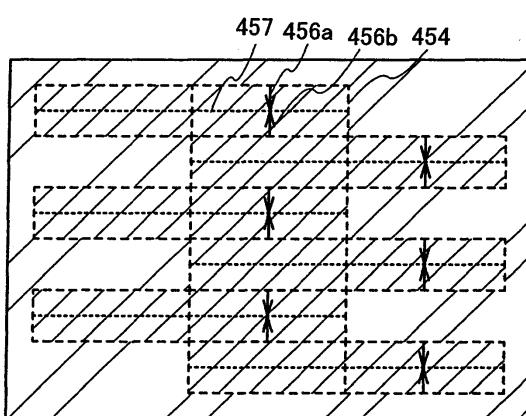

<38> 또한, 하나 또는 다수의 동일 원자로 이루어지는 질량이 다른 이온을 첨가하여도 좋다. 예를 들어, 수소 이온을 첨가하는 경우에는,  $\text{H}^+$ ,  $\text{H}_2^+$ ,  $\text{H}_3^+$  이온을 포함시킴과 동시에,  $\text{H}_3^+$  이온의 비율을 높여 두는 것이 바람직하다. 수소 이온을 첨가하는 경우에는,  $\text{H}^+$ ,  $\text{H}_2^+$ ,  $\text{H}_3^+$  이온을 포함시키는 것과 함께,  $\text{H}_3^+$  이온의 비율을 높여 두면 첨가 효율을 높일 수 있고, 첨가 시간을 단축할 수 있다. 이와 같은 구성으로 함으로써, 박리를 용이하게 행할 수 있다.

<39> 이하, 이온 도핑법과 이온 주입법에 대하여 상세하게 설명한다. 이온 도핑법에 사용하는 이온 도핑 장치(ID 장치라고도 한다)에서는, 플라즈마 공간이 크고, 대량의 이온을 단결정 반도체 기판에 첨가할 수 있다. 한편, 이온 주입법에 사용하는 이온 주입 장치(II 장치라고도 한다)는, 플라즈마로부터 취출한 이온을 질량 분석하여 특정 이온종만을 반도체 기판에 박아 넣을 수 있다는 특징이 있고, 기본적으로 점빔(point beam)을 스캔시켜 처리한다.

<40> 플라즈마 발생 방법으로서는, 어느 장치도, 예를 들어, 필라멘트를 가열하여 나오는 열전자에 의해 플라즈마 상태를 만들고 있다. 그러나, 생성되는 수소 이온( $\text{H}^+$ ,  $\text{H}_2^+$ ,  $\text{H}_3^+$ )이 반도체 기판에 첨가될(박힐) 때의 수소 이온종의 비율은, 이온 도핑법과 이온 주입법에서 크게 다르다.

<41> 이하에서, 본 발명의 특징의 하나인 이온 조사 방법에 대하여 고찰한다.

<42> 본 발명에서는, 수소(H)에 유래하는 이온(이하 "수소 이온종"이라고 부른다)을 단결정 반도체 기판에 대하여 조

사하고 있다. 보다 구체적으로는, 수소 가스 또는 수소를 조성에 포함하는 가스를 원재료로서 사용하고, 수소 플라즈마를 발생시키고, 이 수소 플라즈마 중의 수소 이온종을 단결정 반도체 기판에 대하여 조사하고 있다.

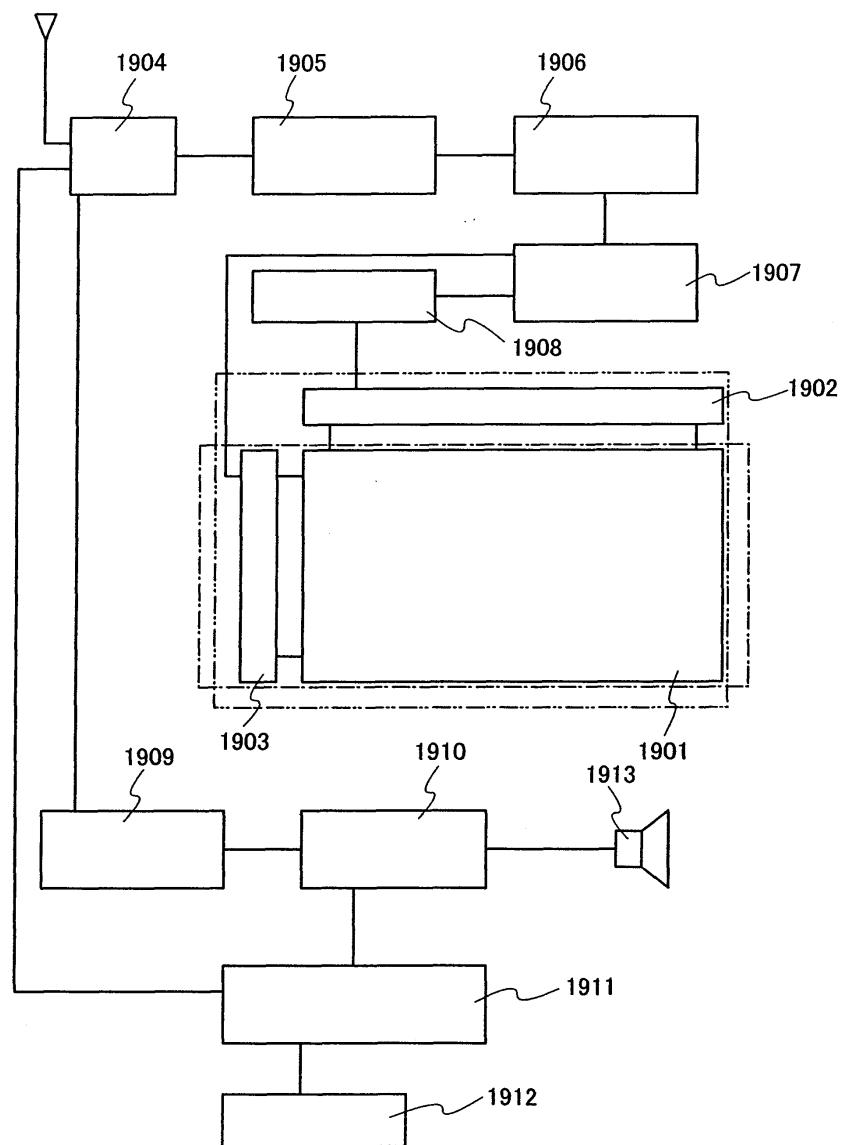

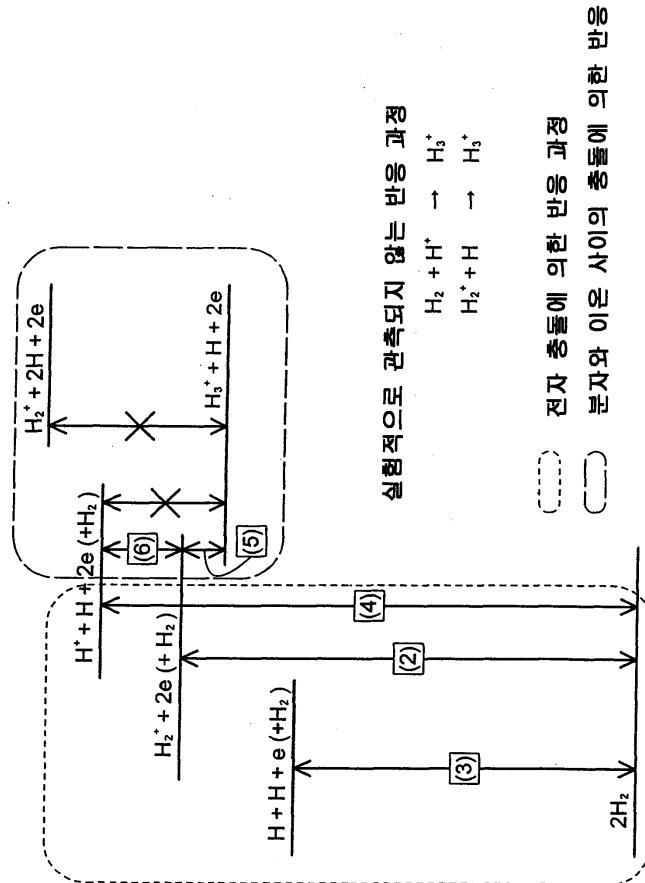

<43> (수소 플라즈마 중의 이온)

<44> 상기와 같은 수소 플라즈마 중에는,  $H^+$ ,  $H_2^+$ ,  $H_3^+$ 와 같은 수소 이온종이 존재한다. 여기서, 각 수소 이온종의 반응 과정(생성 과정, 소멸 과정)에 대하여, 이하에 반응식을 열거한다

<54> 도 25에, 상기 반응의 일부를 모식적으로 나타낸 에너지 다이어그램을 나타낸다. 또한, 도 25에 나타내는 에너지 다이어그램은 모식도에 지나지 않고, 반응에 관한 에너지의 관계를 염밀하게 규정하는 것이 아니라는 점을 유의하기 바란다.

<55> ( $H_3^+$ 의 생성 과정)

<56> 상기와 같이,  $H_3^+$ 는, 주로 반응식 (5)에 의해 나타내어지는 반응 과정에 의해 생성된다. 한편, 반응식 (5)와 경합하는 반응으로서, 반응식 (6)에 의해 나타내어지는 반응 과정이 존재한다.  $H_3^+$ 가 증가하기 위해서는, 적어도, 반응식 (5)의 반응이 반응식 (6)의 반응보다 많이 일어날 필요가 있다(또한,  $H_3^+$ 가 감소하는 반응으로서는 그 밖에도 (7), (8), (9)가 존재하기 때문에, (5)의 반응이 (6)의 반응보다 많다고 하여, 반드시  $H_3^+$ 가 증가한다고는 할 수 없다). 반대로, 반응식 (5)의 반응이 반응식 (6)의 반응보다 적은 경우에는, 플라즈마 중에서의  $H_3^+$ 의 비율은 감소한다.

<57> 상기 반응식의 우변(최우변)의 생성물의 증가량은, 반응식의 좌변(최좌변)에 나타내는 원료의 밀도나, 그 반응에 관한 속도 계수 등에 의존한다. 여기서,  $H_2^+$ 의 운동 에너지가 약 11 eV보다 작은 경우에는, (5)의 반응이 주요가 되고(즉, 반응식 (5)에 관한 속도 계수가 반응식 (6)에 관한 속도 계수와 비교하여 충분히 크게 되고),  $H_2^+$ 의 운동 에너지가 약 11 eV보다 큰 경우에는, (6)의 반응이 주요가 되는 것이 실험적으로 확인되었다.

<58> 하전 입자는 전장(電場)으로부터 힘을 받아 운동 에너지를 얻는다. 이 운동 에너지는, 전장에 의한 포텐셜 에너지의 감소량에 대응하고 있다. 예를 들어, 어떤 하전 입자가 다른 입자와 충돌할 때까지의 동안에 얻는 운동 에너지는, 그 동안에 통과한 전위차만큼의 포텐셜 에너지와 같다. 즉, 전장 중에서, 다른 입자와 충돌하지 않고 긴 거리를 이동할 수 있는 상황에서는, 그렇지 않은 상황과 비교하여, 하전 입자의 운동 에너지(의 평균)는 커지는 경향이 있다. 이와 같은 하전 입자에 관한 운동 에너지의 증대 경향은, 입자의 평균 자유 행정이 큰 상

황, 즉, 압력이 낮은 상황에서 생길 수 있다.

<59> 또한, 평균 자유 행정이 작아도, 그 동안에 큰 운동 에너지를 얻을 수 있는 상황이라면, 하전 입자의 운동 에너지는 커진다. 즉, 평균 자유 행정이 작아도, 전위차가 큰 상황이라면, 하전 입자가 가지는 운동 에너지는 커진다고 할 수 있다.

<60> 이것을  $H_2^+$ 에 적용하여 본다. 플라즈마 생성에 관련되는 체임버 내와 같이 전장의 존재를 전제로 하면, 이 체임버 내의 압력이 낮은 상황에서는  $H_2^+$ 의 운동 에너지는 커지고, 이 체임버 내의 압력이 높은 상황에서는  $H_2^+$ 의 운동 에너지는 작아진다. 즉, 체임버 내의 압력이 낮은 상황에서는, (6)의 반응이 주요가 되기 때문에,  $H_3^+$ 는 감소하는 경향이 되고, 체임버 내의 압력이 높은 상황에서는, (5)의 반응이 주요가 되기 때문에,  $H_3^+$ 는 증가하는 경향이 된다. 또한, 플라즈마 생성 영역에서의 전장(또는 전계)이 강한 상황, 즉, 어느 2점 사이의 전위차가 큰 상황에서는,  $H_2^+$ 의 운동 에너지는 커지고, 반대의 상황에서는,  $H_2^+$ 의 운동 에너지는 작아진다. 즉, 전장이 강한 상황에서는, (6)의 반응이 주요가 되기 때문에,  $H_3^+$ 는 감소하는 경향이 되고, 전장이 약한 상황에서는, (5)의 반응이 주요가 되기 때문에,  $H_3^+$ 는 증가하는 경향이 된다.

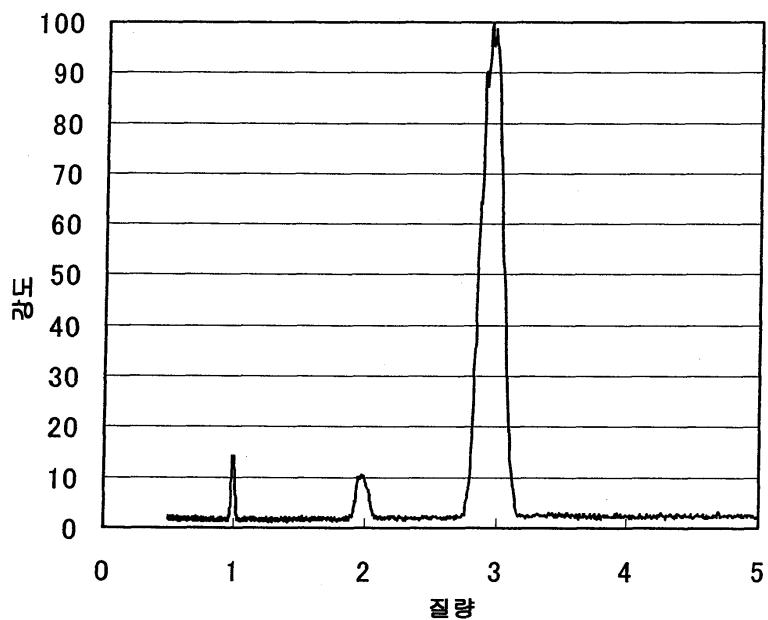

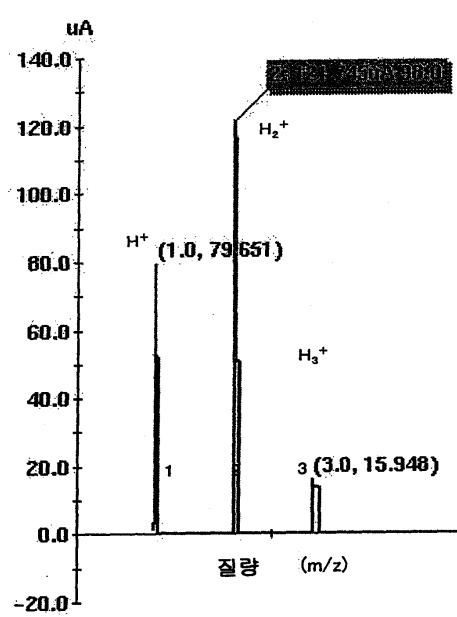

<61> (이온원(源)에 의한 차이)

<62> 여기서, 이온종의 비율(특히  $H_3^+$ 의 비율)이 다른 예를 나타낸다. 도 26은, 100% 수소 가스(이온원(源))의 압력:  $4.7 \times 10^{-2}$  Pa로부터 생성되는 이온의 질량 분석 결과를 나타내는 그래프이다. 또한, 상기 질량 분석은 이온원으로부터 인출된 이온을 측정하는 것에 의해 행해졌다. 횡축은 이온의 질량이다. 질량 1, 2, 3의 피크는 각각  $H^+$ ,  $H_2^+$ ,  $H_3^+$ 에 대응한다. 종축은 스펙트럼의 강도이고, 이온의 수에 대응한다. 도 26에서는, 질량이 다른 이온의 수량을, 질량 3의 이온의 수를 100으로 한 경우의 상대비로 나타내고 있다. 도 26으로부터, 상기 이온원에 의해 생성되는 이온의 비율은,  $H^+ : H_2^+ : H_3^+ = 1 : 1 : 8$  정도가 되는 것을 알 수 있다. 또한, 이러한 비율의 이온은, 플라즈마를 생성하는 플라즈마 소스부(이온원)와, 이 플라즈마로부터 이온 범을 인출하기 위한 인출 전극 등으로 구성되는 이온 도핑 장치에 의해서도 얻을 수 있다.

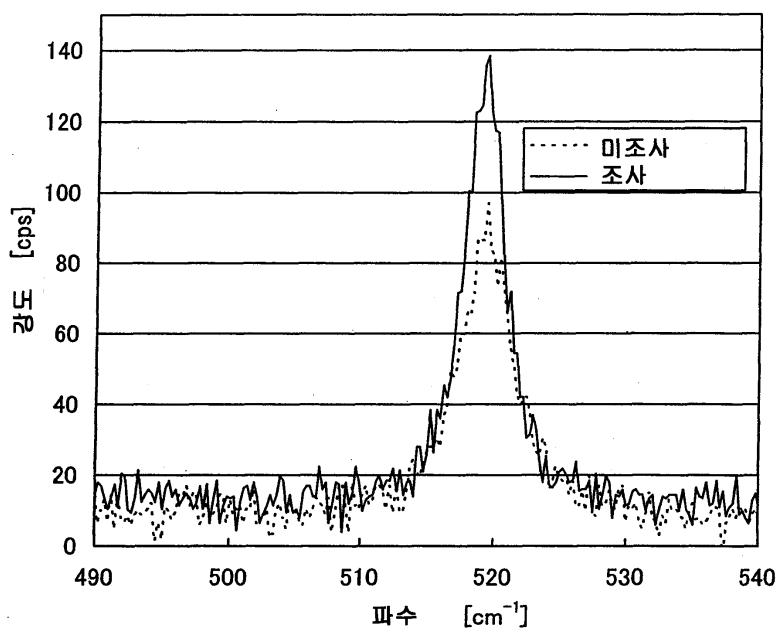

<63> 도 30은, 도 26과는 다른 이온원을 사용한 경우이며, 이온원의 압력이 대략  $3 \times 10^{-3}$  Pa일 때에,  $PH_3$ 로부터 생성한 이온의 질량 분석 결과를 나타내는 그래프이다. 상기 질량 분석 결과는 수소 이온종에 주목한 것이다. 또한, 질량 분석은, 이온원으로부터 인출된 이온을 측정하는 것에 의해 행하였다. 도 26과 마찬가지로, 횡축은 이온의 질량을 나타내고, 질량 1, 2, 3의 피크는 각각  $H^+$ ,  $H_2^+$ ,  $H_3^+$ 에 대응한다. 종축은 이온의 수량에 대응하는 스펙트럼의 강도이다. 도 30으로부터, 플라즈마 중의 이온의 비율은  $H^+ : H_2^+ : H_3^+ = 37 : 56 : 7$  정도인 것을 알 수 있다. 또한, 도 30은 소스 가스가  $PH_3$ 인 경우의 데이터이지만, 소스 가스로서 100% 수소 가스를 사용했을 때에도, 수소 이온종의 비율은 동일한 정도가 된다.

<64> 도 30의 데이터를 얻은 이온원의 경우에는,  $H^+$ ,  $H_2^+$  및  $H_3^+$  중,  $H_3^+$ 가 7% 정도밖에 생성되지 않았다. 한편, 도 26의 데이터를 얻은 이온원의 경우에는,  $H_3^+$ 의 비율을 50% 이상(상기의 조건에서는 80% 정도)으로 하는 것이 가능하다. 이것은, 상기 고찰에서 명확하게 된 체임버 내의 압력 및 전장에 기인하는 것이라고 생각된다.

<65> ( $H_3^+$ 의 조사 메카니즘)

<66> 도 26과 같은 다수의 이온종을 포함하는 플라즈마를 생성하고, 생성된 이온종을 질량 분리하지 않고 반도체 기판에 조사하는 경우, 단결정 반도체 기판의 표면에는,  $H^+$ ,  $H_2^+$ ,  $H_3^+$ 의 각 이온이 조사된다. 이온 조사로부터 이온 도입 영역 형성까지의 메카니즘을 재현하기 위해, 다음의 5 종류의 모델을 고려한다.

<67> 모델 1. 조사되는 이온종이  $H^+$ 이고, 조사 후에도  $H^+(H)$ 인 경우

<68> 모델 2. 조사되는 이온종이  $H_2^+$ 이고, 조사 후에도  $H_2^+(H_2)$ 인 채인 경우

<69> 모델 3. 조사되는 이온종이  $H_2^+$ 이고, 조사 후에 2개의  $H(H^+)$ 로 분열하는 경우

<70> 모델 4. 조사되는 이온종이  $H_3^+$ 이고, 조사 후에도  $H_3^+(H_3)$ 인 채인 경우

<71> 모델 5. 조사되는 이온종이  $H_3^+$ 이고, 조사 후에 3개의  $H(H^+)$ 로 분열하는 경우

<72> (시뮬레이션 결과와 실측값과의 비교)

<73> 상기 모델 1~5를 기초로 하여, 수소 이온종을 Si 기판에 조사하는 경우의 시뮬레이션을 행하였다. 시뮬레이션 용의 소프트웨어로서, SRIM(the Stopping and Range of Ions in Matter: 몬테 카를로(Monte Carlo)법에 의한 이온 도입 과정의 시뮬레이션 소프트웨어, TRIM(the Transport of Ions in Matter)의 개량판)을 사용하였다. 또한, 계산 관계상, 모델 2에서는  $H_2^+$ 를 질량 2배의  $H^+$ 로 치환하여 계산하였다. 또한, 모델 4에서는  $H_3^+$ 를 질량 3배의  $H^+$ 로 치환하여 계산하였다. 또한, 모델 3에서는  $H_2^+$ 를 운동 에너지 1/2의  $H^+$ 로 치환하고, 모델 5에서는  $H_3^+$ 를 운동 에너지 1/3의  $H^+$ 로 치환하여 계산을 행하였다.

<74> 또한, SRIM은 비정질 구조를 대상으로 하는 소프트웨어이지만, 고에너지, 고도즈의 조건으로 수소 이온종을 조사하는 경우에는, SRIM을 적용할 수 있다. 그것은, 수소 이온종과 Si 원자의 충돌에 의해, Si 기판의 결정 구조가 비(非)단결정 구조로 변화하기 때문이다.

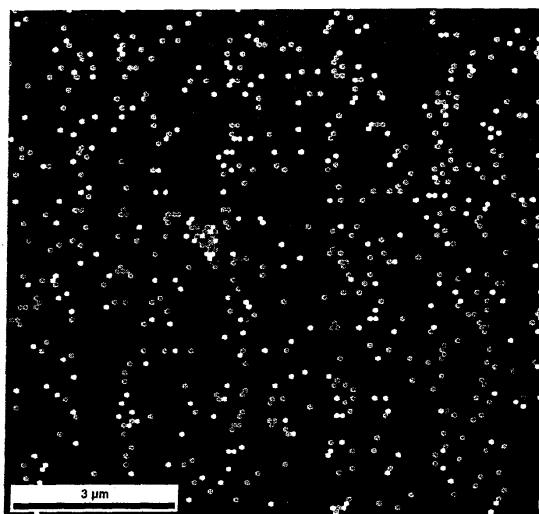

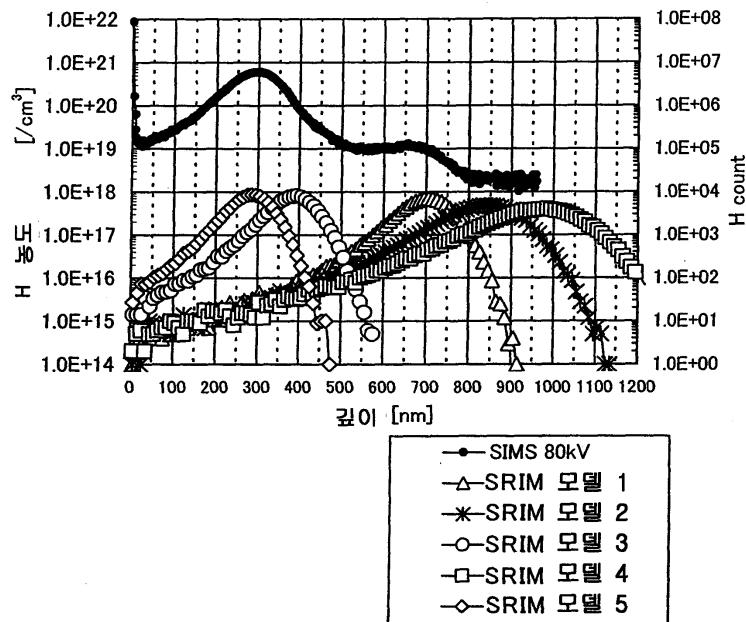

<75> 도 31에, 모델 1 내지 모델 5를 사용하여 수소 이온종을 조사한 경우(H 환산으로 10만개 조사시)의 계산 결과를 나타낸다. 또한, 도 26의 수소 이온종을 조사한 Si 기판 중의 수소 농도(SIMS(Secondary Ion Mass Spectroscopy)의 데이터)를 아울러 나타낸다. 모델 1 내지 모델 5를 사용하여 행한 계산의 결과에 대해서는, 종축을 수소 원자의 수로 나타내고 있고(오른쪽 축), SIMS 데이터에 대해서는, 종축을 수소 원자의 밀도로 나타내고 있다(왼쪽 축). 횡축은 Si 기판 표면으로부터의 깊이이다. 실측값인 SIMS 데이터와 계산 결과를 비교한 경우, 모델 2 및 모델 4는 명확히 SIMS 데이터의 피크로부터 벗어나 있고, 또한, SIMS 데이터 중에는 모델 3에 대응하는 피크도 보이지 않는다. 이것으로부터, 모델 2 내지 모델 4의 기여는 상대적으로 작다는 것을 알 수 있다. 이온의 운동 에너지가 keV의 단위인 것에 대하여, H-H의 결합 에너지는 수 eV 정도에 지나치지 않는 것을 고려하면, 모델 2 및 모델 4의 기여가 작은 것은, Si 원소와의 충돌에 의해, 대부분의  $H_2^+$ 나  $H_3^+$ 가  $H^+$ 나 H로 분리하고 있기 때문이라고 생각된다.

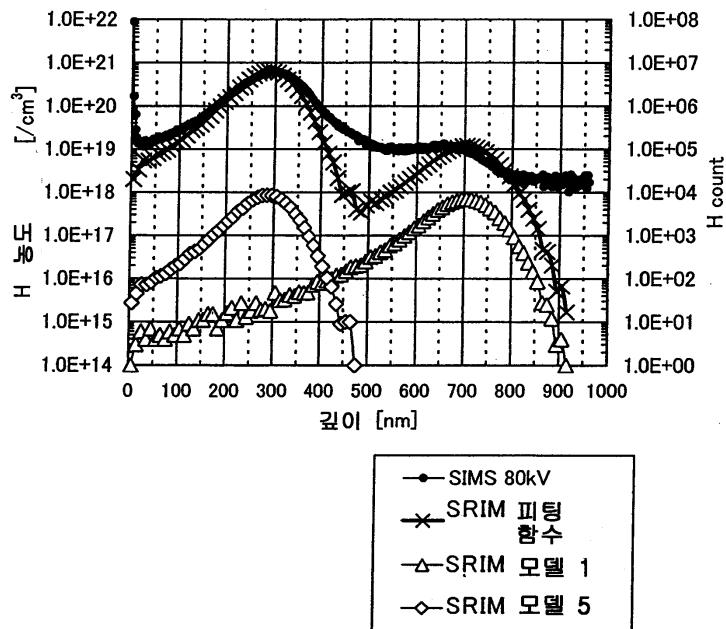

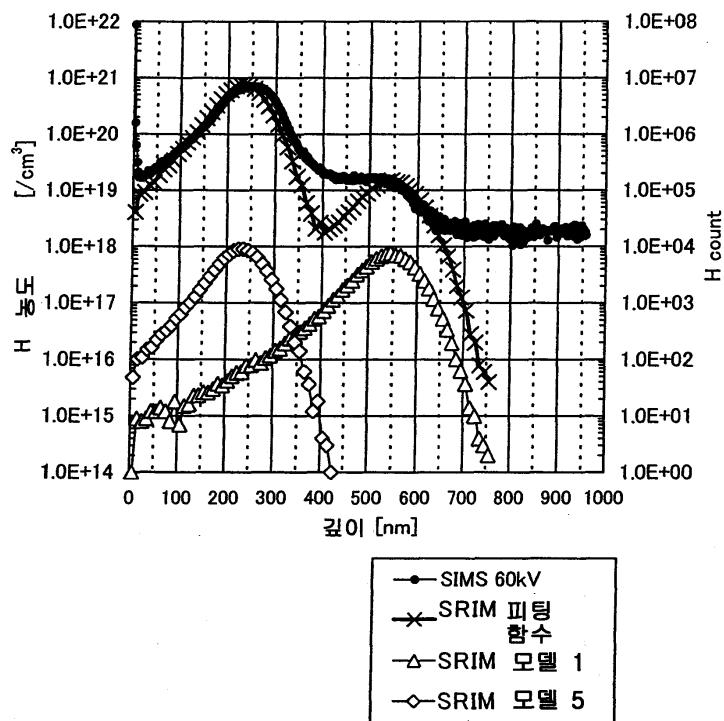

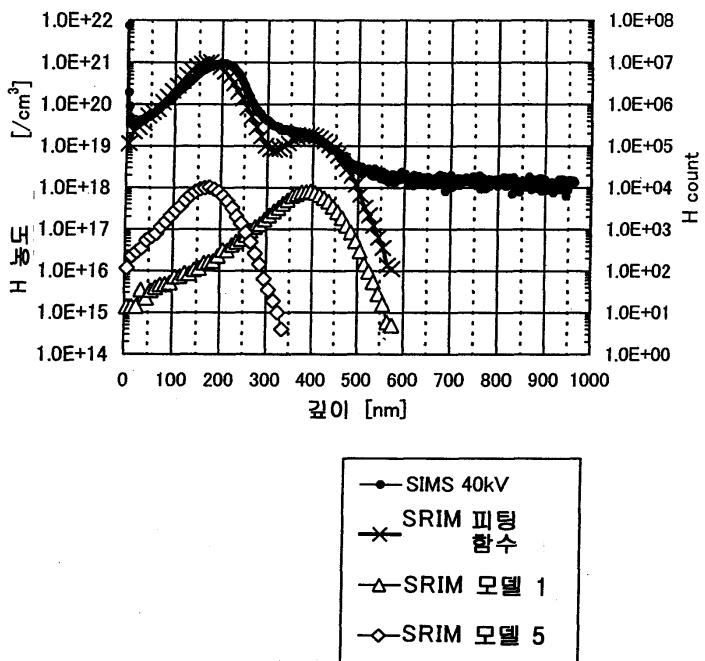

<76> 따라서, 모델 2 내지 모델 4에 대해서는 고려하지 않는다. 도 32~도 34에, 모델 1 및 모델 5를 사용하여 수소 이온종을 조사한 경우(H 환산으로 10만개 조사 시)의 계산 결과를 나타낸다. 또한, 도 26의 수소 이온종을 조사한 Si 기판 중의 수소 농도(SIMS 데이터) 및 상기 시뮬레이션 결과를 SIMS 데이터에 피팅(fitting)한 것(이하, 피팅 함수라고 부른다)을 아울러 나타낸다. 여기서, 도 32는 가속 전압을 80 kV로 한 경우를 나타내고, 도 33은 가속 전압을 60 kV로 한 경우를 나타내고, 도 34는 가속 전압을 40 kV로 한 경우를 나타내고 있다. 또한, 모델 1 및 모델 5를 사용하여 행한 계산의 결과에 대해서는, 종축을 수소 원자의 수로 나타내고 있고(오른쪽 축), SIMS 데이터 및 피팅 함수에 대해서는, 종축을 수소 원자의 밀도로 나타내고 있다(왼쪽 축). 횡축은 Si 기판 표면으로부터의 깊이이다.

<77> 피팅 함수는 모델 1 및 모델 5를 고려하여 이하의 계산식에 의해 구하기로 하였다. 또한, 계산식 중, X, Y는 피팅에 관한 파라미터이고, V는 체적이다.

<78> [피팅 함수] =  $X/V \times [\text{모델 1의 데이터}] + Y/V \times [\text{모델 5의 데이터}]$

<79> 실제로 조사되는 이온종의 비율( $H^+ : H_2^+ : H_3^+ = 1 : 1 : 8$  정도)을 고려하면,  $H_2^+$ 의 기여(즉, 모델 3)에 대해서도 고려해야 하지만, 이하에 나타내는 이유에 의해, 여기서는 제외하고 고려하였다.

<80> · 모델 3에 나타내는 조사 과정에 의해 도입되는 수소는, 모델 5의 조사 과정과 비교하여 얼마 안되기 때문에,

제외하여 고려하여도 큰 영향은 없다(SIMS 데이터에 있어서도, 피크가 나타나지 않는다).

- <81> · 모델 5와 피크 위치가 가까운 모델 3은, 모델 5에서 생기는 채널링(channeling)(결정의 격자 구조에 기인하는 원소의 이동)에 의해 숨겨질 가능성이 높다. 즉, 모델 3의 피팅 파라미터를 추측하는 것은 곤란하다. 이것은, 본 시뮬레이션이 비정질 Si를 전제로 하고 있고, 결정성에 기인하는 영향을 고려하지 않은 것에 의한 것이다.

- <82> 도 35에, 상기 피팅 파라미터를 나타낸다. 어느 가속 전압에서도, 도입되는 H의 수의 비(比)는, [모델 1] : [모델 5] = 1 : 42 내지 1 : 45 정도 (모델 1에서의 H의 수를 1로 한 경우, 모델 5에서의 H의 수는 42 이상 45 이하 정도)이고, 조사되는 이온종의 수의 비는,  $[H^+(모델 1)] : [H_3^+(모델 5)] = 1 : 14$  내지 1 : 15 정도 (모델 1에서의  $H^+$ 의 수를 1로 한 경우, 모델 5에서의  $H_3^+$ 의 수는 14 이상 15 이하 정도)이다. 모델 3을 고려하지 않고 있는 것이나, 비정질 Si라고 가정하여 계산하고 있는 것 등을 고려하면, 실제의 조사에 관한 수소 이온종의 비 ( $H^+ : H_2^+ : H_3^+ = 1 : 1 : 8$  정도)에 가까운 값이 얻어진다고 할 수 있다.

- <83> ( $H_3^+$ 를 사용하는 효과)

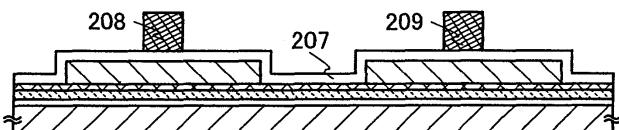

- <84> 도 26에 나타내는 바와 같은  $H_3^+$ 의 비율을 높인 수소 이온종을 기판에 조사함으로써,  $H_3^+$ 에 기인하는 다수의 이점 (利點)을 누릴 수 있다. 예를 들어,  $H_3^+$ 는  $H^+$ 나 H 등으로 분리하여 기판 내에 도입되기 때문에, 주로  $H^+$ 나  $H_2^+$ 를 조사하는 경우와 비교하여, 이온 도입 효율을 향상시킬 수 있다. 이것에 의해, 반도체 기판의 생산성 향상을 도모할 수 있다. 또한, 마찬가지로,  $H_3^+$ 가 분리한 후의  $H^+$ 나 H의 운동 에너지는 작아지는 경향에 있기 때문에, 얇은 반도체층의 제조에 적합하다.

- <85> 또한, 본 명세서에서는,  $H_3^+$ 를 효율적으로 조사하기 위해, 도 26에 나타내는 바와 같은 수소 이온종을 조사할 수 있는 이온 도핑 장치를 사용하는 방법에 대하여 설명하고 있다. 이온 도핑 장치는 저렴하고, 대면적 처리에 뛰어나기 때문에, 이와 같은 이온 도핑 장치를 사용하여  $H_3^+$ 를 조사함으로써, 반도체 특성의 향상, 기판의 대면적화, 저비용화, 생산성 향상 등의 현저한 효과를 얻을 수 있다. 한편,  $H_3^+$ 의 조사를 제일로 고려한다면, 이온 도핑 장치를 사용하는 것에 한정하여 해석할 필요는 없다.

- <86> 단결정 실리콘 기판에 불소 이온과 같은 할로겐 이온을 첨가한 경우, 첨가된 불소가 실리콘 결정 격자 내의 실리콘 원자를 농아웃(knock out)하는(축출하는) 것에 의해 공백 부분을 효과적으로 만들어내고, 취약화층에 미소한 공동(空洞)을 만든다. 이 경우, 비교적 저온의 열처리에 의해 취약화층에 형성된 미소한 공동의 체적 변화가 일어나고, 취약화층을 따라 벽개함으로써 단결정 반도체층을 형성할 수 있다. 불소 이온을 첨가한 후에, 수소 이온을 첨가하여 공동 내에 수소를 포함시켜도 좋다. 단결정 반도체 기판으로부터 얇은 반도체층을 박리하기 위해 형성하는 취약화층은, 취약화층에 형성된 미소한 공동의 체적 변화를 이용하여 벽개하므로, 이와 같이 불소 이온이나 수소 이온의 작용을 유효하게 이용하는 것이 바람직하다.

- <87> 본 명세서에서, 산화질화규소막이란, 그의 조성으로서 질소보다 산소의 함유량이 많은 것으로서, 러더포드 후방 산란법(RBS: Rutherford Backscattering Spectrometry) 및 수소 전방 산란법(HFS: Hydrogen Forward Scattering)을 이용하여 측정한 경우에, 농도 범위로서 산소가 50~70 원자%, 질소가 0.5~15 원자%, Si가 25~35 원자%, 수소가 0.1~10 원자%의 범위로 함유되는 것을 말한다. 또한, 질화산화규소막이란, 그의 조성으로서, 산소보다 질소의 함유량이 많은 것으로, RBS 및 HFS를 이용하여 측정한 경우에, 농도 범위로서 산소가 5~30 원자%, 질소가 20~55 원자%, Si가 25~35 원자%, 수소가 10~30 원자%의 범위로 함유되는 것을 말한다. 단, 산화질화규소 또는 질화산화규소를 구성하는 원자의 합계를 100 원자%로 했을 때, 질소, 산소, Si 및 수소의 함유 비율이 상기 범위 내에 포함되는 것으로 한다.

- <88> 또한, 단결정 반도체 기판과 상기 단결정 반도체층과 접합하는 절연층과의 사이에 보호층을 형성해도 좋다. 보호층은, 질화규소층, 산화규소층, 질화산화규소층, 또는 산화질화규소층으로부터 선택된 1층 또는 다수의 층에 의한 적층 구조에 의해 형성할 수 있다. 이들 층은, 단결정 반도체 기판에 취약화층이 형성되기 전에 단결정 반도체 기판 위에 형성할 수 있다. 또한, 단결정 반도체 기판에 취약화층을 형성한 후에 단결정 반도체 기판 위에 형성해도 좋다.

- <89> 취약화층의 형성에 있어서는 이온을 고도즈 조건으로 첨가할 필요가 있고, 단결정 반도체 기판(108)의 표면이 거칠게 되어 벼리는 경우가 있다. 그 때문에 이온이 첨가되는 표면에 질화규소막, 질화산화규소막, 또는 산화규소막 등에 의해 이온 첨가에 대한 보호층을 50 nm 내지 200 nm의 두께로 형성해 두어도 좋다.

- <90> 예를 들어, 단결정 반도체 기판(108) 위에 보호층으로서 플라즈마 CVD법에 의해 산화질화규소막(막 두께 5 nm~300 nm, 바람직하게는 30 nm~150 nm (예를 들어 50 nm))과 질화산화규소막(막 두께 5 nm~150 nm, 바람직하게는 10 nm~100 nm (예를 들어 50 nm))의 적층을 형성한다. 일례로서는, 단결정 반도체 기판(108) 위에 산화질화규소막을 막 두께 50 nm로 형성하고, 이 산화질화규소막 위에 질화산화규소막을 막 두께 50 nm로 형성하여 적층한다. 산화질화규소막은 유기 실란 가스를 사용하여 화학 기상 성장법에 의해 제조되는 산화규소막이어도 좋다.

- <91> 또한, 단결정 반도체 기판(108)을 탈지(脫脂) 세정하고, 표면의 산화막을 제거하여 열산화를 행하여도 좋다. 열산화로서는 통상의 건식 산화이어도 좋지만, 산화 분위기 중에 할로겐을 첨가한 산화를 행하는 것이 바람직하다. 예를 들어, 산소에 대하여 HCl을 0.5~10 체적%(바람직하게는 3 체적%)의 비율로 함유하는 분위기 중에서, 700°C 이상의 온도로 열처리를 행한다. 적합하게는 950°C~1100°C의 온도로 열산화를 행하면 좋다. 처리 시간은 0.1~6 시간, 바람직하게는 0.5~3.5 시간으로 하면 좋다. 형성되는 산화막의 막 두께로서는, 10 nm~1000 nm (바람직하게는 50 nm~200 nm), 예를 들어, 100 nm의 두께로 한다.

- <92> 할로겐을 포함하는 것으로서는, HCl 외에, HF, NF<sub>3</sub>, HBr, Cl<sub>2</sub>, ClF<sub>3</sub>, BC<sub>13</sub>, F<sub>2</sub>, Br<sub>2</sub> 등에서 선택된 1종 또는 다수 종을 적용할 수 있다.

- <93> 이와 같은 온도 범위에서 열처리를 행함으로써, 할로겐 원소에 의한 게터링 효과를 얻을 수 있다. 게터링으로서는, 특히 금속 불순물을 제거하는 효과가 있다. 즉, 염소의 작용에 의해, 금속 등의 불순물이 휘발성의 염화물이 되어 기상(氣相) 중으로 이탈하여 제거된다. 단결정 반도체 기판(108)의 표면을 화학적 기계 연마(CMP) 처리를 한 것에 대해서는 유효하다. 또한, 수소는 단결정 반도체 기판(108)과 형성되는 산화막의 계면의 결함을 보상하여 계면의 국재(局在) 준위 밀도를 저감하는 작용을 얻을 수 있고, 단결정 반도체 기판(108)과 산화막과의 계면이 불활성화되어 전기적 특성이 안정화한다.

- <94> 이 열처리에 의해 형성되는 산화막 중에 할로겐을 포함시킬 수 있다. 할로겐 원소는  $1 \times 10^{17} / \text{cm}^3 \sim 5 \times 10^{20} / \text{cm}^3$ 의 농도로 포함됨으로써 금속 등의 불순물을 포획하여 단결정 반도체 기판(108)의 오염을 방지하는 보호층으로서의 기능을 발현시킬 수 있다.

- <95> 취약화층(110)을 형성할 때, 가속 전압과 전(全)이온수는, 단결정 반도체 기판 위에 퇴적한 막의 두께와, 목적으로 하는 단결정 반도체 기판으로부터 분리되어 지지 기판 위에 전재되는 단결정 반도체층의 막 두께와, 첨가하는 이온종에 의해 조정할 수 있다.

- <96> 예를 들어, 이온 도핑법으로 원료로서 수소 가스를 사용하고, 가속 전압을 40 kV, 전이온수  $2 \times 10^{16} \text{ ions/cm}^2$ 로 이온을 첨가하여 취약화층을 형성할 수 있다. 보호층의 막 두께를 두껍게 하면, 동일 조건으로 이온을 첨가하여 취약화층을 형성한 경우, 목적으로 하는 단결정 반도체 기판으로부터 분리하여 지지 기판 위에 전치(전재)되는 단결정 반도체층으로서, 막 두께가 얇은 단결정 반도체층을 형성할 수 있다. 예를 들어, 이온종(H<sup>+</sup>, H<sub>2</sub><sup>+</sup>, H<sub>3</sub><sup>+</sup> 이온)의 비율에 따라서도 영향을 받지만, 상기 조건으로 취약화층을 형성하고, 보호층으로서 단결정 반도체 기판 위에 산화질화규소막(막 두께 50 nm)과 질화산화규소막(막 두께 50 nm)을 보호층으로서 적층하는 경우, 지지 기판에 전재되는 단결정 반도체층의 막 두께는 약 120 nm가 되고, 단결정 반도체 기판 위에 산화질화규소막(막 두께 100 nm)과 질화산화규소막(막 두께 50 nm)을 보호층으로서 적층하는 경우는, 지지 기판에 전재되는 단결정 반도체층의 막 두께는 약 70 nm가 된다.

- <97> 헬륨(He)이나 수소를 원료 가스로 하는 경우, 가속 전압을 10 kV~200 kV의 범위에서, 도즈량을  $1 \times 10^{16} \text{ ions/cm}^2 \sim 6 \times 10^{16} \text{ ions/cm}^2$ 의 범위로 첨가하여 취약화층을 형성할 수 있다. 헬륨을 원료 가스로 하면, 질량 분리를 행하지 않아도 He<sup>+</sup> 이온을 주된 이온으로서 첨가할 수 있다. 또한, 수소를 원료 가스로 하면, H<sub>3</sub><sup>+</sup> 이온이나 H<sub>2</sub><sup>+</sup> 이온을 주된 이온으로서 첨가할 수 있다. 이온종은, 플라즈마의 생성 방법, 압력, 원료 가스 공급량, 가속 전압에 따라서도 변화한다.

- <98> 취약화층 형성의 예로서는, 단결정 반도체 기판 위에 산화질화규소막(막 두께 50 nm), 질화산화규소막(막 두께 50 nm), 및 산화규소막(막 두께 50 nm)을 보호층으로서 적층하고, 수소를 가속 전압 40 kV, 도즈량  $2 \times 10^{16}$  ions/cm<sup>2</sup>로 첨가하여 단결정 반도체 기판에 취약화층을 형성한다. 그 후, 보호층의 최상층인 산화규소막 위에 접합면을 가지는 절연층으로서 산화규소막(막 두께 50 nm)을 형성한다. 취약화층 형성의 다른 예로서는, 단결정 반도체 기판 위에 산화규소막(막 두께 100 nm), 및 질화산화규소막(막 두께 50 nm)을 보호층으로서 적층하고, 수소를 가속 전압 40 kV, 도즈량  $2 \times 10^{16}$  ions/cm<sup>2</sup>로 첨가하여 단결정 반도체 기판에 취약화층을 형성한다. 그 후, 보호층의 최상층인 질화산화규소막 위에 접합면을 가지는 절연층으로서 산화규소막(막 두께 50 nm)을 형성한다. 또한, 상기 산화질화규소막 및 질화산화규소막은 플라즈마 CVD법에 의해 형성하면 좋고, 상기 산화규소막은 유기 실란 가스를 사용하여 CVD법에 의해 형성하면 좋다.

- <99> 지지 기판(101)으로서 알루미노 실리케이트 유리, 알루미노 봉규산 유리, 바륨 봉규산 유리와 같은, 전자 공업 용으로 사용되는 유리 기판을 적용하는 경우, 유리 기판 중에 나트륨 등의 알칼리 금속이 미량으로 함유되어 있고, 이 미량의 불순물에 의해 트랜지스터 등 반도체소자의 특성에 악영향을 미칠 우려가 있다. 이와 같은 불순물에 대하여, 질화산화규소막은 지지 기판(101)에 포함되는 금속 불순물이 단결정 반도체 기판측으로 확산하는 것을 방지하는 효과가 있다. 또한, 질화산화규소막 대신에, 질화규소막을 형성해도 좋다. 단결정 반도체 기판과 질화산화규소막과의 사이에 산화질화규소막이나 산화규소막 등의 응력 완화 층을 마련하면 좋다. 질화산화규소막과 산화질화규소막의 적층 구조를 형성함으로써, 단결정 반도체 기판에의 불순물 확산을 방지하면서, 응력 왜곡을 완화하는 구성으로 할 수도 있다.

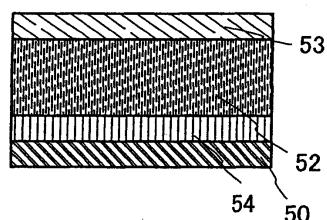

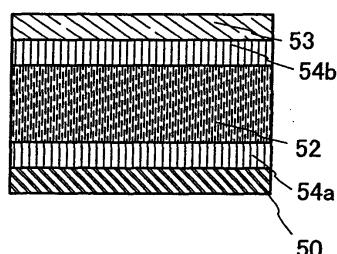

- <100> 지지 기판에는, 불순물 원소의 확산을 방지하는 질화규소막 또는 질화산화규소막을 블로킹층(배리어층이라고도 한다)으로서 제공하여도 좋다. 또한, 응력을 완화하는 작용이 있는 절연막으로서 산화질화규소막을 조합해도 좋다. 도 3(C)에서 나타내는 바와 같이, 본 실시형태에서는, 지지 기판(101) 위에 블로킹층(109)을 형성한다.

- <101> 다음에, 도 3(B)에서 나타내는 바와 같이, 지지 기판과 접합을 형성하는 면에 절연층(104)로서 산화규소막을 형성한다. 산화규소막으로서는, 유기 실란 가스를 사용하여 화학 기상 성장법에 의해 제조되는 산화규소막이 바람직하다. 그 외에, 실란 가스를 사용하여 화학 기상 성장법에 의해 제조되는 산화규소막을 적용할 수도 있다. 화학 기상 성장법에 의한 성막에서는, 단결정 반도체 기판에 형성한 취약화층(110)으로부터 탈가스가 일어나지 않는 온도로서, 예를 들어, 350°C 이하(구체적인 예로서는 300°C)의 성막 온도가 적용된다. 또한, 단결정 반도체 기판으로부터 단결정 반도체층을 박리하는 열처리는, 성막 온도보다 높은 열처리 온도가 적용된다.

- <102> 절연층(104)은 평활면을 가지고 친수성 표면을 형성한다. 이 절연층(104)으로서 산화규소막이 적합하다. 특히, 유기 실란 가스를 사용하여 화학 기상 성장법에 의해 제조되는 산화규소막이 바람직하다. 유기 실란 가스로서는, 규산에틸(TEOS: 화학식 Si(OC<sub>2</sub>H<sub>5</sub>)<sub>4</sub>), 트리메틸실란(TMS:(CH<sub>3</sub>)<sub>3</sub>SiH), 테트라메틸실란(화학식 Si(CH<sub>3</sub>)<sub>4</sub>), 테트라메틸시클로테트라실록산(TMCTS), 옥타메틸시클로테트라실록산(OMCTS), 헥사메틸디실라잔(HMDS), 트리에톡시실란(SiH(OC<sub>2</sub>H<sub>5</sub>)<sub>3</sub>), 트리스디메틸아미노실란(SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>) 등의 실리콘 함유 화합물을 사용할 수 있다. 또한, 원료 가스에 유기 실란을 사용하여 화학 기상 성장법에 의해 산화규소층을 형성하는 경우, 산소를 부여하는 가스를 혼합시키는 것이 바람직하다. 산소를 부여하는 가스로서는, 산소, 아산화질소, 이산화질소 등을 사용할 수 있다. 또한, 아르곤, 헬륨, 질소 또는 수소 등의 불활성 가스를 혼합시켜도 좋다.

- <103> 또한, 절연층(104)으로서, 모노실란, 디실란, 또는 트리실란 등의 실란을 원료 가스에 사용하여 화학 기상 성장법에 의해 형성되는 산화규소막을 적용할 수도 있다. 이 경우도, 산소를 부여하는 가스나 불활성 가스 등을 혼합시키는 것이 바람직하다. 또한, 단결정 반도체층과 접합하는 절연층이 되는 산화규소막은 염소를 포함하고 있어도 좋다. 화학 기상 성장법에 의한 성막에서는, 단결정 반도체 기판(108)에 형성한 취약화층(110)으로부터 탈가스가 일어나지 않는 온도로서, 예를 들어, 350°C 이하의 성막 온도가 적용된다. 또한, 단결정 반도체 기판으로부터 단결정 반도체층을 박리하는 열처리는 성막 온도보다도 높은 열처리 온도가 적용된다. 또한, 본 명세서에서, 화학 기상 성장(CVD: Chemical Vapor Deposition)법은 플라즈마 CVD법, 열 CVD법, 광 CVD법을 범주에 포함한다.

- <104> 또한, 절연층(104)으로서, 산화성 분위기 하에서 열처리를 함으로써 형성되는 산화규소, 산소 라디칼의 반응에 의해 성장하는 산화규소, 산화성의 약액에 의해 형성되는 케미칼 옥사이드 등을 적용할 수도 있다. 절연층(104)으로서, 실록산(Si-O-Si) 결합을 포함하는 절연층을 적용하여도 좋다. 또한, 상기 유기 실란 가스와 산소 라디칼 또는 질소 라디칼을 반응시켜 절연층(104)을 형성하여도 좋다.

- <105> 상기 평활면을 가지고 친수성 표면을 형성하는 절연층(104)은 5 nm~500 nm, 바람직하게는 10 nm~200 nm의 두께로 형성된다. 이 두께라면, 퍼싱막 표면의 거치를 평활화하는 것과 함께, 이 막의 성장 표면의 평활성을 확보하는 것이 가능하다. 또한, 절연층(104)을 형성함으로써, 지지 기판과의 접합에 의한 단결정 반도체층의 왜곡을 완화할 수 있다. 절연층(104)의 표면은, 산술 평균 조도(粗度)(Ra)가 0.8 nm 미만, 제곱 평균 평방근 조도(Rms)가 0.9 nm 미만이 바람직하고, Ra가 0.4 nm 이하, Rms가 0.5 nm 이하가 보다 바람직하고, 또한 Ra가 0.3 nm 이하, Rms가 0.4 nm 이하가 보다 바람직하다. 예를 들어, Ra가 0.27 nm, Rms가 0.34 nm이다. 본 명세서에서, Ra는 산술 평균 조도이고, Rms는 제곱 평균 평방근 조도이고, 측정 범위는  $2 \mu\text{m}^2$ , 또는  $10 \mu\text{m}^2$ 이다.

- <106> 지지 기판(101)에도 절연층(104)과 같은 산화규소막을 형성해 두어도 좋다. 즉, 지지 기판(101)에 단결정 반도체층(102)을 접합함에 있어서, 접합을 형성하는 면의 한쪽 또는 양쪽에, 바람직하게는 유기 실란을 원재료로 하여 성막한 산화규소막으로 이루어지는 절연층(104)을 형성함으로써 강고한 접합을 형성할 수 있다.

- <107> 도 3(C)는 지지 기판(101) 위에 형성된 블로킹층(109)과 단결정 반도체 기판(108)의 절연층(104)이 형성된 면을 밀접시키고, 이 양자를 접합시키는 양태를 나타낸다. 접합을 형성하는 면은 충분히 청정화해 둔다. 지지 기판(101) 위에 형성된 블로킹층(109)과 단결정 반도체 기판(108)의 절연층(104)이 형성된 면은, 메가소닉(megasonic) 세정 등에 의해 청정화하면 좋다. 또한, 메가소닉 세정 후에 오존수로 세정하여, 유기물의 제거와 표면의 친수성 향상을 행하여도 좋다.

- <108> 지지 기판(101) 위의 블로킹층(109)과 절연층(104)을 대향시켜, 일 개소를 외부로부터 누르면, 국소적으로 접합면끼리의 거리가 줄어드는 것에 의한 반 데르 발스력(van der Waals force)의 세기나 수소 결합의 기여에 의해 서로 끌어당긴다. 또한, 인접한 영역에서도 대향하는 지지 기판(101) 위의 블로킹층(109)과 절연층(104)과의 사이의 거리가 줄어들기 때문에, 반 데르 발스력이 강하게 작용하는 영역이나 수소 결합이 관여하는 영역이 넓어지는 것에 의해, 접합(본딩이라고도 한다)이 진행하여 접합면 전역으로 접합이 넓어진다. 예를 들어, 누르는 압력은 100 kPa~5000 kPa 정도로 하면 좋다. 또한, 지지 기판과 반도체 기판을 겹치도록 배치하고, 겹치는 기판의 무게로도 접합을 넓힐 수도 있다.

- <109> 양호한 접합을 형성하기 위하여, 표면을 활성화해 두어도 좋다. 예를 들어, 접합을 형성하는 면에 원자 빔 또는 이온 빔을 조사한다. 원자 빔 또는 이온 빔을 이용하는 경우에는, 아르곤 등의 불활성 가스 중성 원자 빔 또는 불활성 가스 이온 빔을 사용할 수 있다. 그 외에, 플라즈마 조사 또는 라디칼 처리를 행한다. 이와 같은 표면 처리에 의해 200°C~400°C의 온도에서도 이종(異種) 재료 간의 접합을 형성하는 것이 용이하게 된다.

- <110> 또한, 지지 기판과 절연층과의 접합계면의 접합 강도를 향상시키기 위해, 가열 처리를 행하는 것이 바람직하다. 예를 들어, 오븐이나 노(爐) 등에서 70°C~350°C(예를 들어, 200°C에서 2 시간)의 온도 조건으로 열처리를 행한다.

- <111> 도 3(D)에서, 지지 기판(101)과 단결정 반도체 기판(108)을 접합시킨 후, 가열 처리를 행하여 취약화층(110)을 벽개면으로 하여 단결정 반도체 기판(108)을 지지 기판(101)으로부터 박리한다. 예를 들어, 400°C~700°C의 열처리를 행함으로써, 취약화층(110)에 형성된 미소한 공동의 체적 변화가 일어나, 취약화층(110)을 따라 벽개하는 것이 가능하게 된다. 절연층(104)은 블로킹층(109)을 사이에 두고 지지 기판(101)과 접합하고 있으므로, 지지 기판(101) 위에는 단결정 반도체 기판(108)과 같은 결정성의 단결정 반도체층(102)이 잔존하게 된다.

- <112> 400°C~700°C의 온도역에서의 열처리는, 상술한 접합 강도를 향상시키기 위한 열처리와 같은 장치로 연속하여 행하여도 좋고, 다른 장치로 행하여도 좋다. 예를 들어, 노에서 200°C로 2시간 열처리한 후에, 600°C 근방까지 승온하여 2시간 유지하고, 400°C로부터 실온까지의 온도역으로 강온한 후, 노로부터 취출한다. 또한, 열처리는 실온으로부터 승온하여도 좋다. 또한, 노에서 200°C로 2시간 열처리한 후에, 순간 열어닐(RTA) 장치에 의해 600°C~700°C의 온도역으로 1분~30분간(예를 들어, 600°C로 7분간, 650°C로 7분간) 열처리를 행하여도 좋다.

- <113> 400°C~700°C의 온도역에서의 열처리에 의해, 절연층과 지지 기판과의 접합은 수소 결합으로부터 공유 결합으로 이행하고, 취약화층에 첨가된 원소가 석출하여 압력이 상승하고, 단결정 반도체 기판으로부터 단결정 반도체층을 박리할 수 있다. 열처리를 행한 후에는 지지 기판과 단결정 반도체 기판은, 한쪽이 다른 한쪽에 올려진 상태이고, 큰 힘을 가하지 않고 지지 기판과 단결정 반도체 기판을 떼어 놓을 수 있다. 예를 들어, 상방에 놓여 있는 기판을 진공 척(chuck)으로 들어 올리는 것에 의해 간단하게 떼어 놓을 수 있다. 이때, 하측의 기판의 진공 척이나 메카니컬 척으로 고정해 두면 수평 방향으로 어긋나지 않게 지지 기판 및 단결정 반도체 기판의 양 기판을 떼어 놓을 수 있다.

- <114> 또한, 도 3 및 도 4에서는, 단결정 반도체 기판(108)이 지지 기판(101)보다 작은 사이즈인 예를 나타내지만, 본

발명은 그것에 한정되지 않고, 단결정 반도체 기판(108)과 지지 기판(101)이 같은 사이즈이어도 좋고, 단결정 반도체 기판(108)이 지지 기판(101)보다 큰 사이즈이어도 좋다.

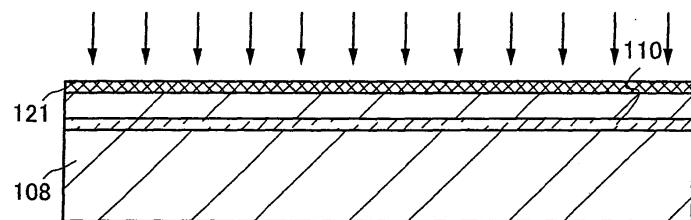

<115> 도 4는 지지 기판측에 절연층을 형성하고 단결정 반도체층을 형성하는 공정을 나타낸다. 도 4(A)는 보호층(121)으로서 산화규소막이 형성된 단결정 반도체 기판(108)에 전계에 의해 가속된 이온을 소정의 깊이로 첨가하여, 취약화층(110)을 형성하는 공정을 나타내고 있다. 이온의 첨가는 도 3(A)의 경우와 마찬가지이다. 단결정 반도체 기판(108)의 표면에 보호층(121)을 형성해 둠으로써 이온 첨가에 의해 표면이 대미지를 받아, 평탄성이 손상되는 것을 방지할 수 있다. 또한, 보호층(121)에 의해, 단결정 반도체 기판(108)으로부터 형성되는 단결정 반도체층(102)에 대한 불순물의 확산 방지 효과를 발현한다.

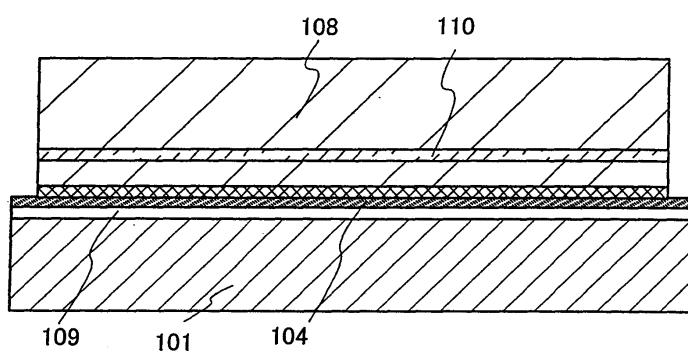

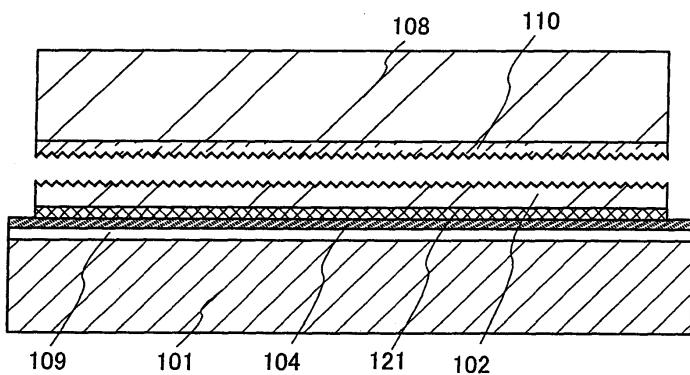

<116> 도 4(B)는, 블로킹층(109) 및 절연층(104)이 형성된 지지 기판(101)과 단결정 반도체 기판(108)의 보호층(121)이 형성된 면을 밀착시켜 접합을 형성하는 공정을 나타내고 있다. 지지 기판(101) 위의 절연층(104)과 단결정 반도체 기판(108)의 보호층(121)을 밀착시킴으로써 접합이 형성된다.

<117> 그 후, 도 4(C)에서 나타내는 바와 같이, 단결정 반도체 기판(108)을 박리한다. 단결정 반도체층을 박리하는 열처리는 도 3(D)의 경우와 마찬가지로 하여 행한다. 이와 같이 하여, 도 4(C)에서 나타내는 절연층을 사이에 두고 지지 기판 위에 단결정 반도체층을 가지는 SOI 구조의 반도체 기판을 얻을 수 있다.

<118> 지지 기판(101)으로서는, 절연성을 가지는 기판, 또는 절연 표면을 가지는 기판을 사용할 수 있고, 예를 들어, 알루미노 실리케이트 유리, 알루미노 봉규산 유리, 바륨 봉규산 유리와 같은 무(無)알칼리 유리로 불리는 전자 공업용으로 사용되는 각종 유리 기판을 적용할 수 있다. 예를 들어, 지지 기판(100)으로서, 무알칼리 유리 기판(상품명 AN100), 무알칼리 유리 기판(상품명 EAGLE2000(등록상표) 또는 무알칼리 유리 기판(상품명 EAGLEXG(등록상표)를 사용하는 것이 바람직하다. 또한, 유리 기판 외에, 세라믹 기판, 석영 기판이나 사파이어 기판 등의 절연체로 이루어지는 절연성 기판 등을 사용할 수 있다.

<119> 이상의 공정에 의해, 도 1(A) 및 도 1(E)에 나타내는 바와 같이, 절연 표면을 가지는 기판인 지지 기판(101) 위에 블로킹층(109)과 절연층(104)이 형성되고, 단결정 반도체 기판(108)으로부터 분리된 단결정 반도체층(102)이 형성된다.

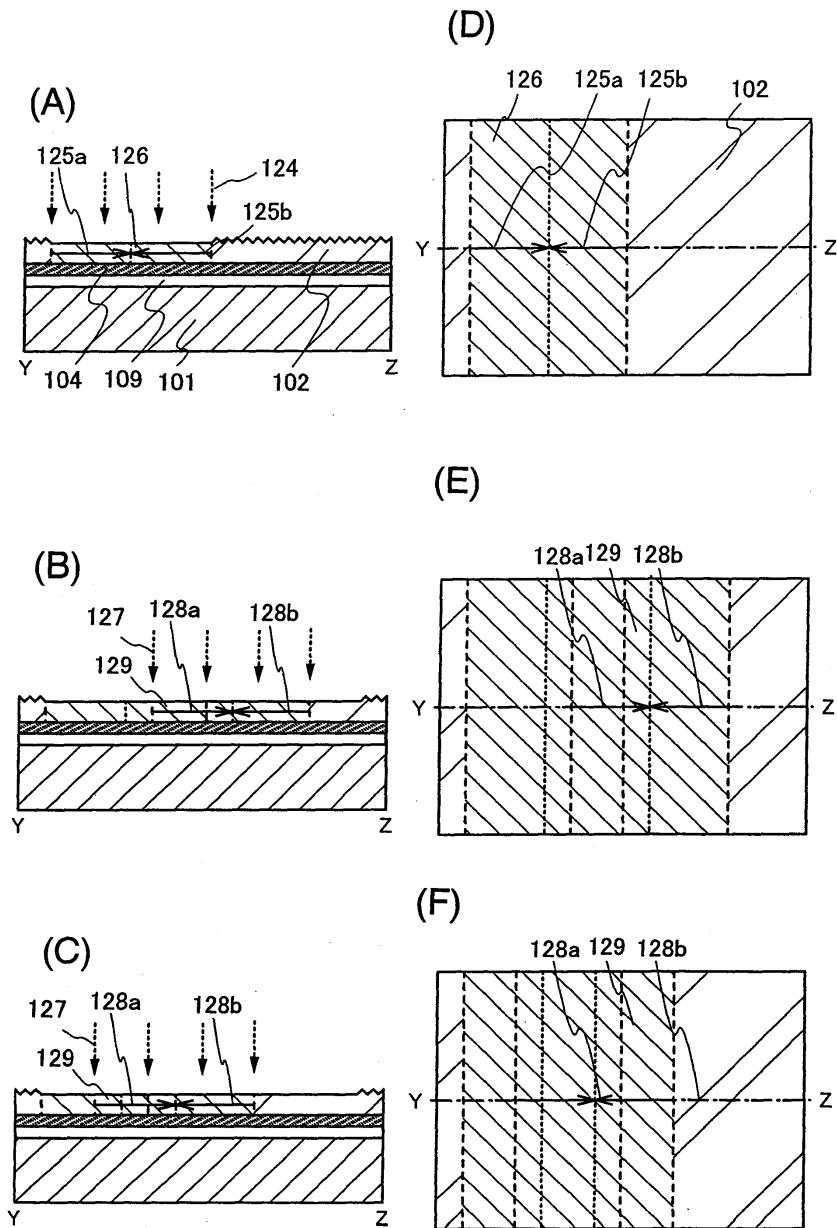

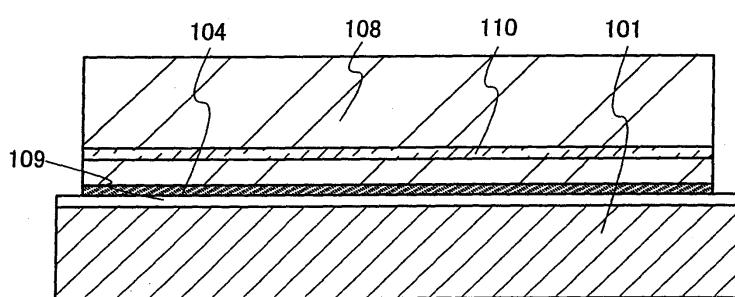

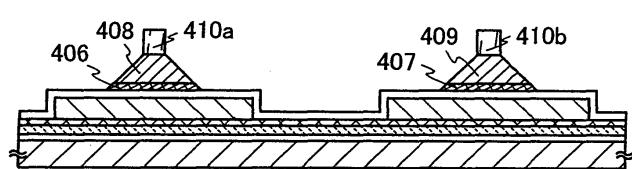

<120> 도 1(E)~도 1(H) 및 도 2(D)~도 2(F)는 평면도이고, 도 1(A)~도 1(D) 및 도 2(A)~도 2(C)는 도 1(E)~도 1(H) 및 도 2(D)~도 2(F)의 선 Y-Z에서의 단면도이다.

<121> 지지 기판(101) 위의 단결정 반도체층(102)은, 분리 공정 및 이온 첨가 공정에 의해, 결정 결함이 생기고, 또한, 그의 표면은 평탄성이 손상되어, 요철이 형성되어 있다. 단결정 반도체층(102)을 사용하여 반도체소자로서 트랜지스터를 제조하는 경우, 이와 같은 요철이 있는 단결정 반도체층(102)의 상면에 얹고 절연 내압성이 높은 게이트 절연층을 형성하는 것은 곤란하다. 또한, 단결정 반도체층(102)에 결정 결함이 있으면, 게이트 절연 층과의 국재(局在) 계면 준위 밀도가 높아지는 등, 트랜지스터의 성능 및 신뢰성에 영향을 준다.

<122> 본 발명에서는 그와 같은 단결정 반도체층(102)에 펄스 발진 레이저광(124)을 조사하여, 단결정 반도체층(102)을 깊이 방향에서도 완전히 용융시키고, 재단결정화시킨, 결정 결함을 저감시키고 결정성이 높고, 또한, 평탄성도 높은 단결정 반도체층(130)을 얻는다.

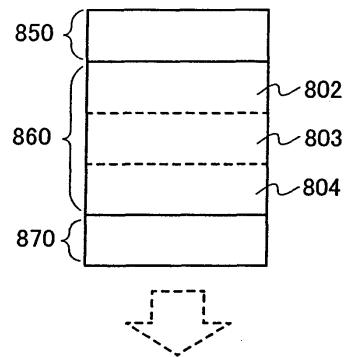

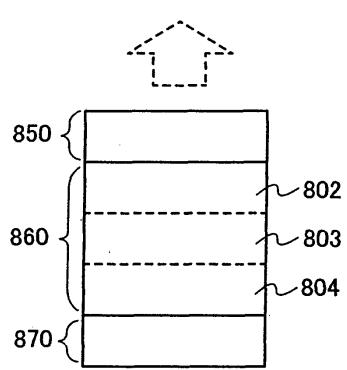

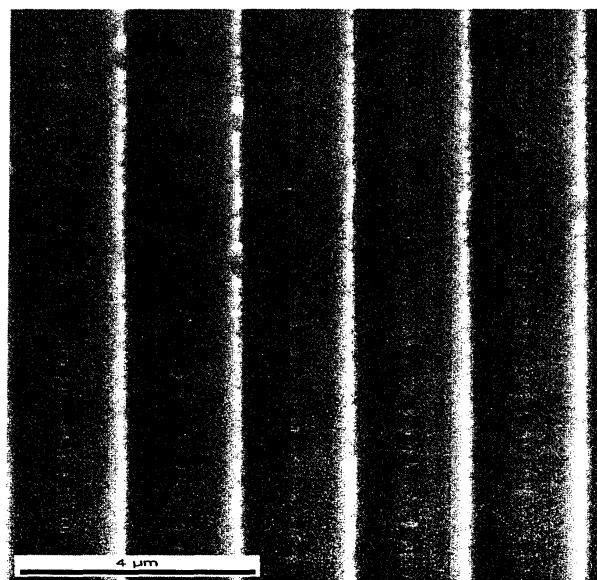

<123> 지지 기판(101) 위에 전재된 단결정 반도체층(102)에 펄스 발진 레이저광(124)을 조사하여, 단결정 반도체층(102)의 재단결정화를 행한다. 단결정 반도체층(102)에서 레이저광(124)의 조사 영역은 적어도 깊이 방향 전영역에 걸쳐 용융하고, 주위의 비조사 영역(비용융 영역)을 결정핵(종결정)으로 하여 조사 영역(용융 영역) 중앙을 향하여(도 1(B) 및 도 1(F)의 화살표(125a, 125b) 방향을 향하여) 재단결정화한다. 결정 성장은, 용융 영역 단부에서 용융 영역과 비용융 영역과의 계면으로부터 각각 용융 영역 내부(중앙)를 향하여 일어나고, 결정 성장에 의한 재단결정 영역끼리가 화살표(125a) 및 화살표(125b)로 나타내는 바와 같이 접함으로써, 레이저광(124) 조사 영역 전역에서 단결정 반도체층(102)을 재단결정화한다. 단결정 반도체층(102)의 재단결정화에 의해, 결정성 및 평탄성이 높은 단결정 반도체 영역(126)을 형성한다(도 1(B) 및 도 1(F) 참조). 또한, 도 1 및 도 2에서는, 결정 성장에 의한 재단결정 영역끼리가 접하는 영역을 점선으로 나타내고 있다.

<124> 다음에, 레이저광(124)의 조사에 의해 재단결정화된 단결정 반도체 영역(126)에 인접하는 영역을 레이저광(127)의 조사에 의해 재단결정화한다. 단결정 반도체층(102)에서 레이저광(127)의 조사 영역은 적어도 깊이 방향 전영역에 걸쳐 용융하고, 주위의 비조사 영역(비용융 영역)을 결정핵(종결정)으로 하여 조사 영역(용융 영역) 중앙을 향하여(도 1(C) 및 도 1(G) 화살표(128a, 128b) 방향을 향하여) 재단결정화한다. 결정 성장은, 용융 영역 단부에서 용융 영역과 비용융 영역과의 계면으로부터 각각 용융 영역 내부(중앙)를 향하여 일어나고, 결정

성장에 의한 재단결정 영역끼리가 화살표(128a) 및 화살표(128b)로 나타내는 바와 같이 접합으로써, 레이저광(127) 조사 영역 전역에서 단결정 반도체층(102)을 재단결정화한다. 단결정 반도체층(102)의 재단결정화에 의해, 결정성 및 평탄성이 높은 단결정 반도체 영역(129)을 형성한다(도 1(C) 및 도 1(G) 참조).

<125> 이상의 레이저광의 조사에 의한 단결정 반도체층의 재단결정화를 반복함으로써, 단결정 반도체층은 전영역에서 레이저광 조사에 의한 용융 상태를 거쳐 재단결정화되어, 결정성 및 평탄성이 높은 단결정 반도체층(130)을 형성할 수 있다(도 1(D) 및 도 1(H) 참조).

<126> 본 발명에서는, 단결정 반도체층의 레이저광이 조사되어 있는 영역의 깊이 방향도 포함하여 전부를 용융한다. 따라서, 본 발명에서는, 단결정 반도체층에서 레이저광 조사 영역은 전영역(면 방향 및 깊이 방향)에서 용융 영역이 된다. 본 명세서에서, 단결정 반도체층에서의 레이저광 조사 영역의 전영역이란, 단결정 반도체층의 레이저광이 조사되어 있는 영역의 면 방향 및 깊이 방향도 포함하여 모든 영역을 가리킨다. 또한, 단결정 반도체층에서, 레이저광 조사 영역의 전영역을 적어도 깊이 방향으로 완전히 용융하기 때문에, 완전 용융한다고도 할 수 있다.

<127> 따라서, 재단결정화의 결정핵(종결정)은, 주위의 레이저광 비조사 영역인 비용융 영역이며, 비용융 영역을 결정핵으로 하여, 용융 영역 중앙을 향하여 단결정 반도체층(지지 기판) 표면에 평행한 방향으로 결정 성장한다. 결정 성장은, 용융 영역 단부에서 용융 영역과 비용융 영역과의 계면으로부터 각각 용융 영역 내부(중앙)를 향하여 일어나고, 결정 성장에 의한 재단결정 영역끼리가 접합으로써, 레이저광 조사 영역 전역에서 단결정 반도체층을 재단결정화한다.

<128> 본 발명에서는, 레이저광의 조사에 의해 일어나는 결정 성장이, 단결정 반도체층(지지 기판) 표면에 평행한 방향에 일어나므로, 단결정 반도체층(지지 기판) 표면에 대하여 깊이 방향(막 두께 방향)을 종방향으로 하면, 횡성장(횡방향의 성장)의 결정 성장이라고도 한다.

<129> 이 용융 영역의 결정 성장은, 레이저광의 조사에 의해, 단결정 반도체층의 레이저광 조사 영역이 용접 이상으로 가열되어 용융하고, 조사 후의 냉각시에 용접 이하가 되어도 고화하지 않고 용융 상태인 채인 과냉각 상태 시에 일어난다. 과냉각 상태의 시간은, 단결정 반도체층의 막 두께, 레이저광의 조사 조건(에너지 밀도, 조사 시간(펄스폭) 등) 등에 의존한다. 과냉각 상태의 시간이 길면, 결정 성장에 의해 재단결정화하는 영역도 넓어지기 때문에, 1회의 레이저광 조사 영역도 넓게 할 수 있다. 따라서, 처리 효율이 향상되고, 스루풋도 높아진다. 또한, 레이저광 조사되는 단결정 반도체층을 가열해 두면 과냉각 상태의 시간의 연장에 효과적이다. 단결정 반도체층의 온도는 실온으로부터 500°C 이하(지지 기판의 왜곡점 이하)로 하면 좋고, 단결정 반도체층의 가열은 지지 기판을 가열 처리하거나 또는 단결정 반도체층에 가열한 기체 등을 내뿜는 것에 의해 행할 수 있다.

<130> 따라서, 본 발명에서는 그 재단결정화에 의한 단결정 영역 단부(결정 성장 단부)끼리가 접하는 영역의 넓이로 레이저광 조사 영역(용융 영역)을 설정한다. 예를 들어, 펄스 발진 레이저광의 단결정 반도체층에서의 조사 영역의 단축 방향의 레이저광 프로파일(빔 프로파일이라고도 한다)의 형상은 직사각형이며, 또한, 폭을 20 μm 이하로 한다. 또한, 펄스 발진 레이저광의 단결정 반도체층에서의 조사 영역의 단축 방향의 레이저광 프로파일의 형상은 가우시안이며, 또한, 폭을 100 μm 이하로 한다. 레이저광의 펄스폭을 길게 하면, 레이저광 프로파일의 폭도 길게 할 수 있다. 상기와 같이 레이저광 프로파일을 설정하면, 과냉각 상태의 시간 내에 용융 영역 전역을 결정 성장에 의해 형성되는 재단결정 영역으로 할 수 있다. 또한, 펄스 발진 레이저광의 상기 단결정 반도체층에서의 조사 영역의 형상은 직사각형(선 형상 레이저에 의한 긴 직사각형 형상이어도 좋다)을 사용할 수 있고, 또한, 마스크를 사용하여 다수의 직사각형을 가지는 레이저 형상을 사용하여도 좋다.

<131> 레이저광의 조사 영역이 넓으면, 단결정 반도체층의 결정 성장이 일어나는 과냉각 상태의 시간 내에는 조사 영역 전역을 재단결정화할 수 없고, 조사 영역의 중앙 부분에 미(微)결정 영역이 생기게 된다. 따라서, 레이저광 조사 영역 전역을 재단결정화할 수 있도록, 단결정 반도체층의 과냉각 상태의 시간 내에 결정 성장 단부끼리가 조사 영역(용융 영역) 내에서 접하는(만나는) 레이저광 조사 영역을 설정한다. 약간의 미결정 영역이라면, 레이저광의 조사를 조사 영역이 미결정 영역과 겹치도록 스캔하여 미결정 영역을 재단결정화할 수 있다.

<132> 단결정 반도체층의 주변 단부 부근의 레이저광의 조사에 의한 재단결정 반도체 영역을 형성하기 위한 결정핵이 된 레이저광의 비조사 영역(재단결정화되어 있지 않은 영역)은 제거하면 좋다.

<133> 펄스 발진 레이저광의 조사 처리를 사용하기 때문에, 지지 기판의 온도 상승이 억제되어, 유리 기판과 같은 내열성이 낮은 기판을 지지 기판에 사용하는 것이 가능하게 된다. 따라서, 단결정 반도체층에의 이온 첨가 공정에 의한 대미지를 충분히 회복시킬 수 있다.

- <134> 또한, 단결정 반도체층은 용융하여 재단결정화함으로써 표면을 평탄화할 수 있다. 따라서, 펠스 발진 레이저광의 조사에 의한 단결정 반도체층의 재단결정화에 의해, 결정 결합이 저감되고, 또한, 평탄성도 높은 단결정 반도체층을 가지는 반도체 기판을 제작할 수 있다.

- <135> 또한, 레이저광의 조사 전에 단결정 반도체층 표면에 형성된 산화막(자연 산화막, 또는 케미칼 산화막)을 희불산으로 제거하면 좋다.

- <136> 레이저광은 단결정 반도체층에 높은 에너지를 부여하는 것이면 좋고, 적합하게는 펠스 발진 레이저광을 사용할 수 있다.

- <137> 레이저광의 파장은, 단결정 반도체층에 흡수되는 파장으로 한다. 그 파장은, 레이저광의 표피 깊이(skin depth) 등을 고려하여 결정할 수 있다. 예를 들어, 레이저광의 파장은 190 nm~600 nm를 사용할 수 있다. 또한, 레이저광의 에너지는, 레이저광의 파장, 레이저광의 표피 깊이, 조사하는 단결정 반도체층의 막 두께 등을 고려하여 결정할 수 있다.

- <138> 레이저광을 발진하는 레이저는, 펠스 발진 레이저를 사용할 수 있다. 예를 들어, KrF 레이저 등의 엑시머 레이저, Ar 레이저, Kr 레이저 등의 기체 레이저가 있다. 그 외에, 고체 레이저로서 YAG 레이저, YVO<sub>4</sub> 레이저, YLF 레이저, YAIO<sub>3</sub> 레이저, GdVO<sub>4</sub> 레이저, KGW 레이저, KYW 레이저, 알렉산드라이트 레이저, Ti:사파이어 레이저, Y<sub>2</sub>O<sub>3</sub> 레이저 등이 있다. 또한, 고체 레이저에서는, 기본파인 제2 고조파~제5 고조파를 적용하는 것이 바람직하다. 또한, GaN, GaAs, GaAlAs, InGaAsP 등의 반도체 레이저도 사용할 수 있다.

- <139> 레이저광의 형상이나 레이저광의 진로를 조정하기 위해, 셔터, 미러 또는 하프 미러(half mirror) 등의 반사체, 실린드리컬(cylindrical) 렌즈나 볼록 렌즈 등에 의해 구성되는 광학계가 구비되어 있어도 좋다.

- <140> 또한, 레이저광의 조사 방법은, 선택적으로 레이저광을 조사하여도 좋고, 레이저광을 XY축 방향으로 주사하여 레이저광을 조사할 수 있다. 이 경우, 광학계에 폴리곤 미러(polygon mirror)나 갈바노 미러(galvanometer mirror)를 사용하는 것이 바람직하다.

- <141> 예를 들어, 레이저광으로서, 파장 308 nm, 펠스폭 25 nsec의 XeCl 엑시머 레이저를 사용하고, 조사하는 단결정 반도체층이 단결정 실리콘층인 경우, 이 실리콘층의 막 두께가 90 nm~120 nm에서는, 이 실리콘층에 부여하는 에너지 밀도는 600 J/cm<sup>2</sup>~2000 mJ/cm<sup>2</sup>의 범위에서 적절히 설정하면 좋다.

- <142> 레이저광의 조사는, 대기 분위기와 같은 산소를 포함하는 분위기, 또는 질소 분위기와 같은 불활성 분위기에서 행할 수 있다. 불활성 분위기 중에서 레이저광을 조사하기 위해서는, 기밀성이 있는 체임버 내에서 레이저광을 조사하고, 이 체임버 내의 분위기를 제어하면 좋다. 체임버를 사용하지 않는 경우는, 레이저광의 피조사면에 질소 가스 등 불활성 가스를 내뿜는 것에 의해, 질소 분위기를 형성할 수도 있다.

- <143> 산소를 10 ppm 이하, 바람직하게는 6 ppm 이하로 한 질소 분위기 중에서, 레이저광 조사 처리를 행하면, 단결정 반도체층 표면을 비교적 평탄하게 할 수 있다.

- <144> 또한, 레이저광 조사 등의 고에너지가 공급되어, 결정 결합이 저감된 단결정 반도체층 표면에 연마 처리를 행하여도 좋다. 연마 처리에 의해 단결정 반도체층 표면의 평탄성을 높일 수 있다.

- <145> 연마 처리로서는, 화학적 기계 연마(Chemical Mechanical Polishing: CMP)법이나 액체 젯(jet) 연마법을 이용할 수 있다. 또한, 연마 처리 전에 단결정 반도체층 표면을 세정하여, 청정화한다. 세정은 메가소닉 세정이나 2 유체 젯 세정 등을 사용하면 좋고, 세정에 의해 단결정 반도체층 표면의 오물 등을 제거한다. 또한, 희불산을 사용하여 단결정 반도체층 표면 위의 자연 산화막 등을 제거하여 단결정 반도체층을 노출시키면 바람직하다.

- <146> 또한, 레이저광을 조사하기 전에도 단결정 반도체층 표면에 연마 처리(또는 에칭 처리)를 행하여도 좋다. 에칭 처리는 습식 에칭법, 건식 에칭법, 또는 습식 에칭법 및 건식 에칭법을 조합하여 행할 수 있다.

- <147> 레이저광 조사 공정 전에, 단결정 반도체층에 연마 처리를 행하면 이하와 같은 효과를 얻을 수 있다. 연마 처리에 의해, 단결정 반도체층 표면의 평탄화와 단결정 반도체층의 막 두께의 제어를 할 수 있다. 단결정 반도체층 표면을 평탄화하는 것에 의해, 레이저광 조사 공정에서 단결정 반도체층의 열용량을 균일화할 수 있고, 균일한 가열 냉각 과정, 또는 용융 및 응고 과정을 거침으로써, 균일한 결정을 형성할 수 있다. 또한, 연마 처리(또는 연마 처리가 아니고, 에칭 처리에서도) 단결정 반도체층의 막 두께를, 레이저광의 에너지를 흡수하는 적절한 값으로 함으로써, 효율적으로 단결정 반도체층에 에너지를 부여할 수 있다. 또한, 단결정 반도체층 표면

은 결정 결함이 많기 때문에, 결정 결함이 많은 표면을 제거함으로써, 레이저광 조사 후의 단결정 반도체층 중의 결정 결함을 저감할 수 있다.

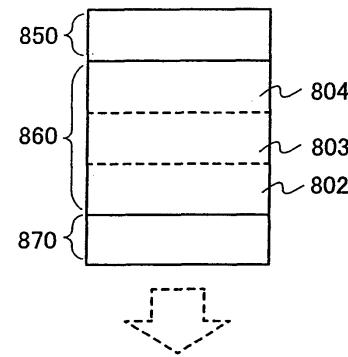

<148> 또한, 레이저광의 조사 영역(단결정 반도체층의 재단결정화 영역)은, 도 1과 같이 겹치지 않아도 좋고, 겹치도록 레이저광을 스캔하여 레이저광 조사를 행하여도 좋다. 레이저광의 조사 영역(단결정 반도체층의 재단결정화 영역)을 겹치도록(오버랩하도록)하여 반도체 기판을 제조하는 예를 도 2에 나타낸다.

<149> 도 2(A) 및 도 2(D)는 도 1(B) 및 도 1(F)에 대응하고, 레이저광(124)에 의해 단결정 반도체층(102)에서, 재단결정화된 단결정 반도체 영역(126)이 형성되어 있다.

<150> 도 2(B) 및 도 2(E), 도 2(C) 및 도 2(F)에서는, 레이저광(127)을 레이저광(124)의 조사 영역인 단결정 반도체 영역(126)에 일부 겹치도록 조사하고, 단결정 반도체 영역(126)의 일부도 재차 용융하여 재단결정화하고 있다.

<151> 레이저광(124)의 조사 영역인 단결정 반도체 영역(126)의 단부는 럭지(ridge)(볼록부)가 생기기 쉽기 때문에, 재차 레이저광(127)에 의해 재용융하여 재단결정화되면, 럭지를 경감하여, 보다 평탄성을 높이는데 효과적이다. 또한, 도 2(C) 및 도 2(F)와 같이, 단결정 반도체 영역(126)에서, 결정 성장 단부끼리가 접하는 영역(도 2에서 접선으로 나타낸다)까지 겹치도록 레이저광(127)을 조사하여, 재차 용융하여 재단결정화하여도 좋다.

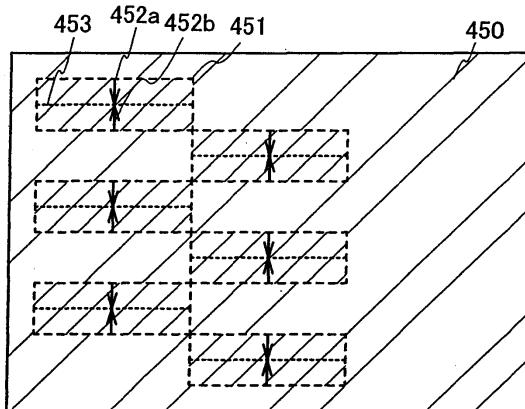

<152> 또는, 레이저광을 마스크에 의해 가공하고, 선택적으로 다수의 영역을 동시에 용융하여 재단결정화 처리를 행하여도 좋다. 단결정 반도체층에서의 레이저광의 조사 패턴의 예를 도 23에 나타낸다. 도 23에서, 지지 기판에 전재된 단결정 반도체층(450)에 대하여, 먼저 도 23(A)와 같이 레이저광은 다수의 직사각형의 조사 패턴(451)으로 조사된다. 각각의 직사각형의 레이저광 조사 영역에서, 단결정 반도체층(450)이 용융하고, 화살표(452a, 452b)와 같이 중앙부(453)에서 재단결정 영역이 접할 때까지 결정 성장하여, 재단결정화한다.

<153> 다음에, 도 23(B)에 나타내는 바와 같이, 레이저광의 마스크를 약간 옮기고, 레이저광을 다수의 직사각형의 조사 패턴(454)으로 조사한다. 마찬가지로, 각각의 직사각형의 레이저광 조사 영역에서, 단결정 반도체층(450)은 용융하고, 화살표(456a, 456b)와 같이 중앙부(457)에서 재단결정 영역이 접할 때까지 결정 성장하여, 재단결정화한다. 이와 같이 선택적으로 다수의 영역을 동시에 용융하여 재단결정화 처리를 행함으로써, 처리 속도를 향상시킬 수 있기 때문에 생산성이 향상된다.

<154> 이상과 같이, 단결정 반도체 기판으로부터 지지 기판에 전재되고, 전영역에서 레이저광 조사에 의한 용융 상태를 거쳐 재단결정화된 단결정 반도체층을 가지는 반도체 기판을 제작할 수 있고, 이 반도체 기판의 단결정 반도체층(130)은 결정 결함도 저감되고 결정성이 높고, 또한 평탄성도 높다.

<155> 반도체 기판에 형성된 단결정 반도체층(130)으로부터 트랜ジ스터 등의 반도체소자를 제조함으로써, 게이트 절연층의 박막화 및 게이트 절연층의 국제 계면 준위 밀도의 저감이 가능하게 된다. 또한, 단결정 반도체층(130)의 막 두께를 얇게 함으로써, 지지 기판 위에, 단결정 반도체층에서 완전 공핍형의 트랜지스터를 제작할 수 있다.

<156> 또한, 본 실시형태에서, 단결정 반도체 기판(108)으로서 단결정 실리콘 기판을 적용한 경우에는, 단결정 반도체층(130)으로서 단결정 실리콘층을 얻는 것이 가능하다. 또한, 본 실시형태에 관한 반도체 기판의 제조방법은, 프로세스 온도를 700°C 이하로 할 수 있기 때문에, 지지 기판(101)으로서 유리 기판을 적용할 수 있다. 즉, 종래의 박막트랜지스터와 마찬가지로 유리 기판 위에 형성할 수 있고, 또한, 단결정 실리콘층을 단결정 반도체층에 적용하는 것이 가능하게 된다. 이에 따라, 고속 동작이 가능하고, 서브스레시홀드(subthreshold)값이 낮고, 전계효과 이동도가 높고, 저소비 전압으로 구동 가능 등의 고성능, 고신뢰성의 트랜지스터를 유리 기판 등의 지지 기판 위에 제작할 수 있다.

<157> 또한, 본 발명에서, 반도체장치란, 반도체 특성을 이용함으로써 기능할 수 있는 장치를 가리킨다. 본 발명을 사용하여 반도체소자(트랜지스터, 메모리 소자나 다이오드 등)를 포함하는 회로를 가지는 장치나, 프로세서 회로를 가지는 칩 등의 반도체장치를 제작할 수 있다.

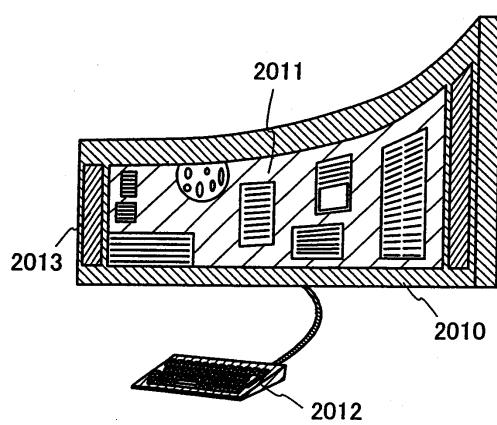

<158> 본 발명은 표시 기능을 가지는 장치인 반도체장치(표시장치라고도 한다)에도 사용할 수 있고, 본 발명을 사용하는 반도체장치에는, 일렉트로루미네스نس(이하 "EL"이라고도 한다)라고 불리는 발광을 발현하는 유기물, 무기물, 또는 유기물과 무기물의 혼합물을 포함하는 층을 전극들 사이에 개재시킨 발광소자와 트랜지스터가 접속된 반도체장치(발광 표시장치)나, 액정 재료를 가지는 액정 소자(액정 표시 소자)를 표시 소자로서 사용하는 반도체장치(액정 표시장치) 등이 있다. 본 명세서에서, 표시장치란 표시 소자를 가지는 장치를 가리키고, 표시장치는, 기판 위에 표시 소자를 포함하는 다수의 화소나 그들의 화소를 구동시키는 주변 구동회로가 형성된 표시 패널 본체도 포함한다. 또한, 가요성 프린트 회로(FPC)나 프린트 배선 기반(PWB)이 부착된 것(IC나 저항 소자나 용

량 소자나 인더터나 트랜지스터 등)을 포함하여도 좋다. 또한, 편광판이나 위상차 판 등의 광학 시트를 포함하고 있어도 좋다. 또한, 백라이트(도광판이나 프리즘 시트나 확산 시트나 반사 시트나 광원(LED나 냉음극관 등)을 포함하고 있어도 좋다)을 포함하고 있어도 좋다.

<159> 또한, 표시 소자나 반도체장치는, 다양한 형태 및 다양한 소자를 사용할 수 있다. 예를 들어, EL 소자(유기 EL 소자, 무기 EL 소자 또는 유기물 및 무기물을 포함하는 EL 소자), 전자 방출 소자, 액정 소자, 전자 잉크, 그레이팅 라이트 밸브(GLV), 플라즈마 디스플레이(PDP), 디지털 마이크로미러 디바이스(DMD), 압전 세라믹 디스플레이, 카본 나노튜브 등, 전기 자기적 작용에 의해 콘트라스트가 변화하는 표시 매체를 적용할 수 있다. 또한, EL 소자를 사용한 반도체장치로서는 EL 디스플레이, 전자 방출 소자를 사용한 반도체장치로서는 필드 에미션 디스플레이(FED)나 SED 방식 평면형 디스플레이(SED: Surface-conduction Electron-emitter Display) 등 액정 소자를 사용한 반도체장치로서는 액정 디스플레이, 투과형 액정 디스플레이, 반투과형 액정 디스플레이, 반사형 액정 디스플레이, 전자 잉크를 사용한 반도체장치로서는 전자 페인팅 있다.

<160> 이와 같이, 고성능 및 고신뢰성의 반도체 기판 및 반도체장치를 수율 좋게 제작할 수 있다.

<161> [실시형태 2]

<162> 본 실시형태에서는, 실시형태 1에서 단결정 반도체 기판으로부터 지지 기판에 단결정 반도체층을 접합하는 공정이 다른 예를 나타낸다. 따라서, 실시형태 1과 동일 부분 또는 동일한 기능을 가지는 부분의 반복 설명은 생략한다.

<163> 본 실시형태는, 단결정 반도체 기판으로부터 단결정 반도체층을 전재할 때, 단결정 반도체 기판을 선택적으로 에칭(홈 가공이라고도 한다)하고, 형상이 가공된 다수의 단결정 반도체층을 지지 기판에 전재한다. 따라서, 지지 기판에는, 다수의 섬 형상의 단결정 반도체층을 형성할 수 있다. 단결정 반도체 기판에 미리 형상을 가공하여 전재하기 때문에, 단결정 반도체 기판의 크기나 형상에 제한을 받지 않는다. 따라서, 대형의 지지 기판에의 단결정 반도체층의 전재를 보다 효율 좋게 행할 수 있다.

<164> 또한, 지지 기판 위에 형성된 반도체층에 대하여 에칭을 행하고, 반도체층의 형상을 가공, 수정하여 정밀하게 제어한다. 이것에 의해, 반도체소자의 단결정 반도체층의 형상으로 가공할 수 있고, 또한, 레지스트 마스크 형성시의 노광에서의 광 등에 의한 패턴 어긋남이나, 전재시의 부착 공정에 의한 위치 어긋남 등에 의한 단결정 반도체층의 형성 위치의 오차나 형상 불량을 수정할 수 있다.

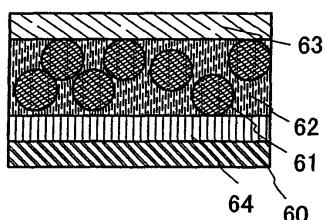

<165> 따라서, 지지 기판에 소망의 형상의 다수의 단결정 반도체층을 수율 좋게 형성할 수 있다. 따라서, 대면적 기판에 의해 정밀한 고성능의 반도체소자 및 접적회로를 가지는 반도체장치를 높은 스루풋으로 생산성 좋게 제작할 수 있다.

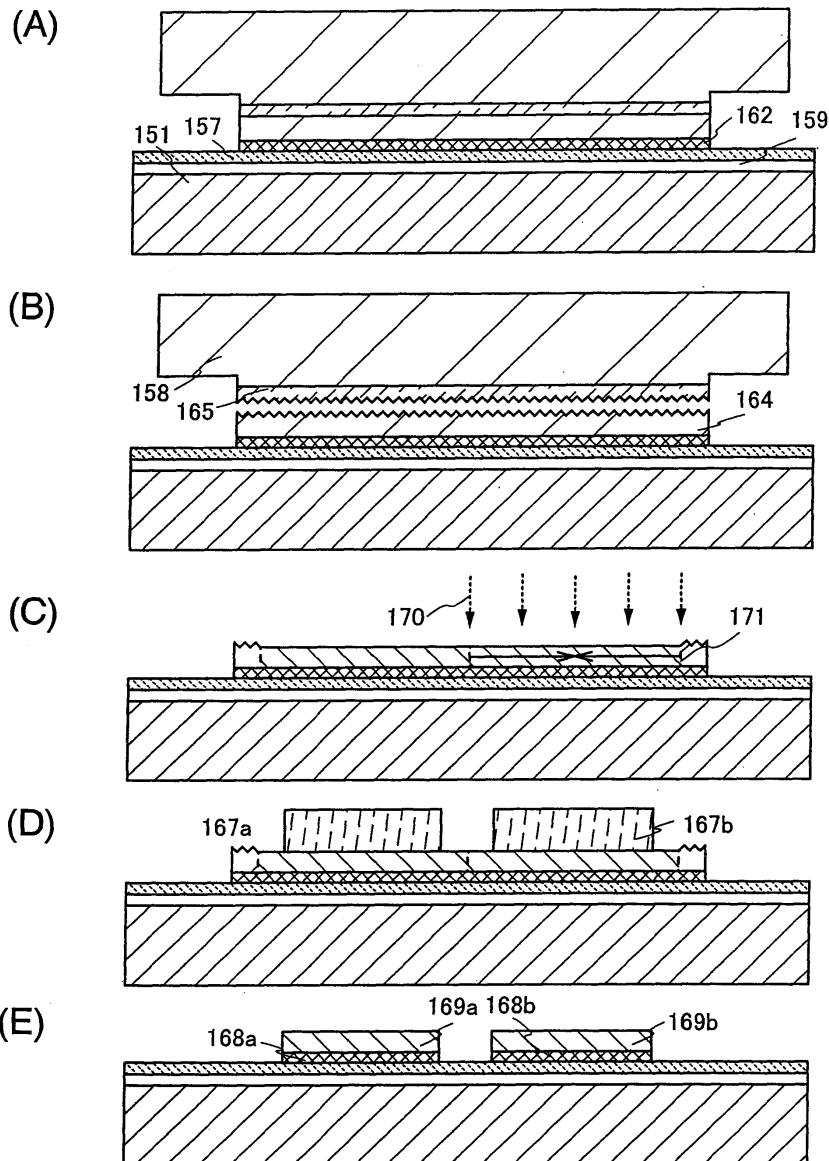

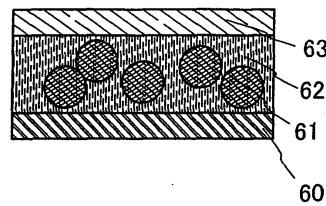

<166> 도 5(A)에서, 단결정 반도체 기판(158) 위에 보호층(154)과 질화규소막(152)이 형성된 상태를 나타내고 있다. 질화규소막(152)은, 단결정 반도체 기판(158)을 홈 가공할 때의 하드 마스크로서 사용한다. 질화규소막(152)은, 실란과 암모니아를 사용하여 기상 성장법에 의해 퇴적시킴으로써 형성하면 좋다.

<167> 다음에, 이온을 첨가하여, 단결정 반도체 기판(158)에 취약화층(150)을 형성한다(도 5(B) 참조). 이온의 첨가는 지지 기판에 전재하는 단결정 반도체층의 두께를 고려하여 행해진다. 이온을 첨가할 때의 가속 전압은 이와 같은 두께를 고려하여, 단결정 반도체 기판(158)의 심부(深部)에 첨가되도록 한다. 이 처리에 의해 단결정 반도체 기판(158)의 표면으로부터 일정 깊이의 영역에 취약화층(150)이 형성된다.

<168> 홈 가공은, 반도체소자의 단결정 반도체층의 형상을 고려하여 행해진다. 즉, 반도체소자의 단결정 반도체층이 지지 기판에 전재될 수 있도록, 그 부위가 볼록 형상부로서 잔존하도록 단결정 반도체 기판(158)에 대하여 홈 가공을 행한다.

<169> 포토레지스트로 마스크(153)를 형성한다. 마스크(153)를 사용하여, 질화규소막(152) 및 보호층(154)을 에칭하여, 보호층(162) 및 질화규소층(163)을 형성한다(도 5(C) 참조).

<170> 다음에, 질화규소층(163)을 하드 마스크로 하여 단결정 반도체 기판(158)의 에칭을 행하여, 취약화층(165)과 단결정 반도체층(166)을 가지는 단결정 반도체 기판(158)을 형성한다(도 5(D) 참조). 본 발명에서는, 취약화층 및 홈 가공에 의해 볼록 형상으로 가공된 단결정 반도체 기판의 일부인 반도체 영역을 도 5(D)와 같이 단결정 반도체층(166)이라고 한다.

<171> 단결정 반도체 기판(158)을 에칭하는 깊이는, 지지 기판에 전재하는 단결정 반도체층의 두께를 고려하여 적절히

설정된다. 이 단결정 반도체층의 두께는 수소 이온을 첨가하는 깊이로 설정하는 것이 가능하다. 단결정 반도체 기판(158)에 형성하는 흄의 깊이는, 취약화층보다 깊게 되도록 형성하는 것이 바람직하다. 이 흄 가공에서, 흄의 깊이를 취약화층보다 깊게 가공함으로써, 취약화층을 박리해야 하는 단결정 반도체층의 영역에만 남길 수 있다.

<172> 표면의 질화규소층(163)을 제거한다(도 5(E) 참조). 그리고, 단결정 반도체 기판(158)에서의 보호층(162)의 표면과 지지 기판(151)을 접합시킨다(도 6(A) 참조).

<173> 지지 기판(151)의 표면에는, 블로킹층(159) 및 절연층(157)이 형성되어 있다. 블로킹층(159)은 지지 기판(151)으로부터 나트륨 이온 등의 불순물이 확산하여 단결정 반도체층을 오염시키지 않게 하기 위해 형성되어 있다. 단, 지지 기판(151)으로부터 단결정 반도체층에 악영향을 주는 불순물의 확산을 걱정할 필요가 없는 경우에는, 블로킹층(159)을 생략하는 것도 가능하다. 한편, 절연층(157)은 보호층(162)과 접합을 형성하기 위하여 형성되어 있다.

<174> 접합은, 표면이 청정화된 단결정 반도체 기판(158)측의 보호층(162)과, 지지 기판측의 절연층(157)이 밀접함으로써 형성된다. 접합의 형성은 실온에서 행하는 것이 가능하다. 이 접합은 원자 레벨에서 행해지고, 반 데르발스력이 작용하여 실온에서 강고한 접합이 형성된다. 단결정 반도체 기판(158)에는 흄 가공이 되어 있으므로, 단결정 반도체층을 형성하는 볼록 형상부가 지지 기판(151)과 접하게 된다.

<175> 단결정 반도체 기판(158)과 지지 기판(151) 사이에서 접합을 형성한 후, 열처리를 행함으로써, 도 6(B)에서 나타내는 바와 같이 단결정 반도체 기판(158)으로부터 단결정 반도체층(164)을 박리하여 지지 기판(151)에 고정시킬 수 있다. 단결정 반도체층의 박리는, 취약화층(150)에 형성된 미소한 공동의 체적 변화가 일어나, 취약화층(150)을 따라 파단면을 발생시킴으로써 행해진다. 그 후, 접합을 더욱 강고한 것으로 하기 위해, 열처리를 행하는 것이 바람직하다. 이와 같이 하여, 절연 표면 위에 단결정 반도체층이 형성된다. 도 6(B)에서는, 단결정 반도체층(164)이 지지 기판(151) 위에 접합된 상태를 나타내고 있다.

<176> 본 실시형태는, 단결정 반도체층의 형상을 미리 가공하여 전재하기 때문에, 단결정 반도체 기판 그 자체의 크기나 형상에 제한을 받지 않는다. 따라서, 기판 위에서 다양한 형상의 단결정 반도체층을 형성할 수 있다. 예를 들어, 에칭 시에 사용하는 노광 장치의 마스크마다, 이 마스크 패턴을 형성하기 위한 노광 장치가 가지는 스텝 퍼마다, 대형 기판으로부터 잘라내는 반도체장치의 패널 또는 칩 사이즈마다, 자유롭게 단결정 반도체층을 형성할 수 있다.

<177> 지지 기판(151) 위에 전재된 단결정 반도체층(164)에 레이저광을 조사하여, 단결정 반도체층의 재단결정화를 행한다. 단결정 반도체층(164)에서 레이저광(170)의 조사 영역은 적어도 깊이 방향 전영역에 걸쳐 용융하고, 주위의 비조사 영역(비용융 영역)을 결정핵(종결정)으로 하여 조사 영역(용융 영역) 중앙을 향하여(도 6(C)의 화살표 방향을 향하여) 재단결정화한다. 단결정 반도체층(164)의 재단결정화에 의해, 결정성 및 평탄성이 높은 단결정 반도체층(171)을 형성한다(도 6(C) 참조).

<178> 제작하는 반도체소자에 대응시켜, 단결정 반도체층(171) 위에 마스크(167a, 167b)를 선택적으로 형성한다.

<179> 마스크(167a, 167b)를 사용하여, 단결정 반도체층(171)을 에칭하여, 단결정 반도체층(169a, 169b)을 각각 형성한다. 본 실시형태에서는, 단결정 반도체층 아래의 보호층(162)도 단결정 반도체층과 함께 에칭하여, 보호층(168a, 168b)으로 한다(도 6(D), 도 6(E) 참조). 이와 같이, 지지 기판에 전재한 후, 더욱 형상을 가공함으로써, 재단결정화된 결정성 및 평탄성이 높은 단결정 반도체층만을 사용하여, 반도체소자의 단결정 반도체층을 제작할 수 있고, 또한, 제조 공정에서 생긴 형성 영역의 어긋남이나, 형상 불량 등도 수정할 수 있다.

<180> 이상과 같이, 단결정 반도체 기판으로부터 지지 기판에 전재되고, 전영역에서 레이저광 조사에 의한 용융 상태를 거쳐 재단결정화된 단결정 반도체층을 가지는 반도체 기판을 제작할 수 있고, 이 반도체 기판의 단결정 반도체층(169a, 169b)은 결정 결함도 저감되고 결정성이 높고, 또한, 평탄성도 높다.

<181> 반도체 기판에 제공된 단결정 반도체층(169a, 169b)으로부터 트랜지스터 등의 반도체소자를 제작함으로써, 고성능 및 고신뢰성의 반도체 기판 및 반도체장치를 수율 좋게 제작할 수 있다.

<182> 본 실시형태는 실시형태 1과 적절히 조합할 수 있다.

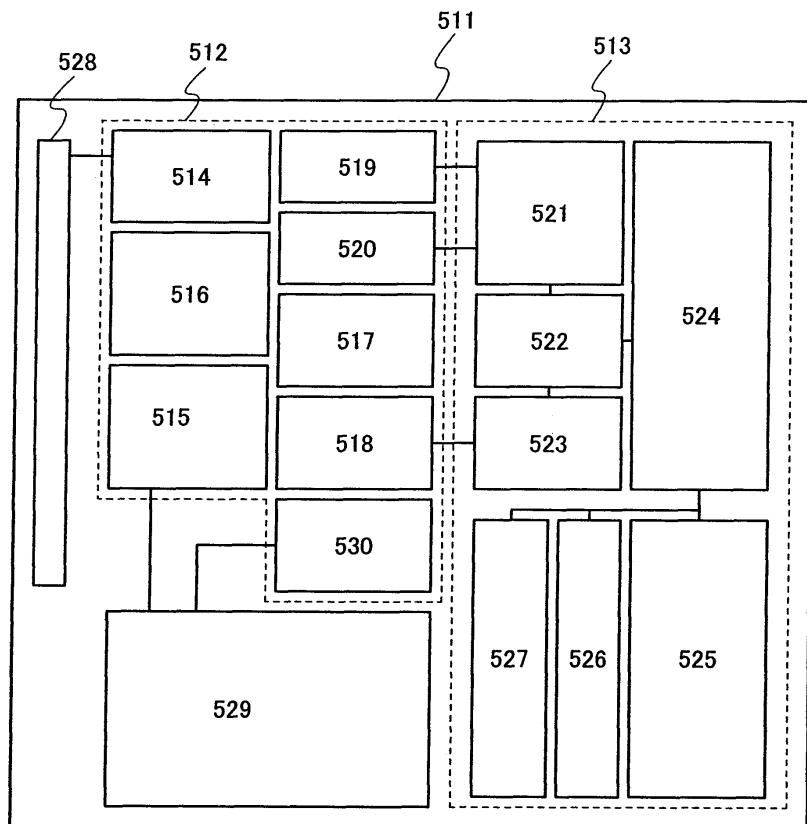

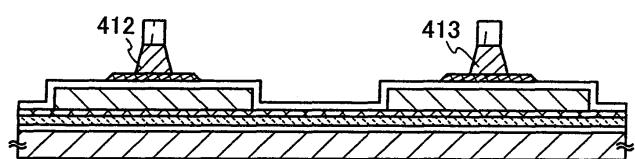

<183> [실시형태 3]

<184> 본 실시형태에서는, 고성능 및 고신뢰성의 반도체소자를 가지는 반도체장치를 수율 좋게 제작하는 것을 목적으

로 한 반도체장치 제조방법의 일례로서 CMOS(상보형 금속 산화물 반도체: Complementary Metal Oxide Semiconductor) 장치에 관하여 도 7 및 도 8을 사용하여 설명한다. 또한, 실시형태 1과 동일 부분 또는 동일한 기능을 가지는 부분의 반복 설명은 생략한다.

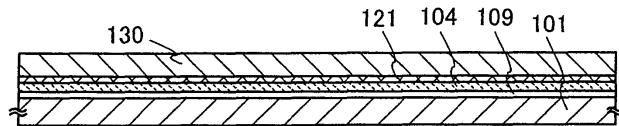

<185> 도 7(A)에서는, 지지 기판(101) 위에 블로킹층(109), 절연층(104), 보호층(121), 단결정 반도체층(130)이 형성되어 있다. 단결정 반도체층(130)은 도 1(D)과 대응하고, 블로킹층(109), 절연층(104), 보호층(121)은 도 4(C)와 대응하고 있다. 또한, 여기서는 도 7(A)에 나타내는 구성의 반도체 기판을 적용하는 예를 나타내지만, 본 명세서에서 나타내는 그 외의 구성의 반도체 기판도 적용할 수 있다. 또한, 블로킹층(109), 절연층(104), 보호층(121)을 지지 기판(101)과 단결정 반도체층(130)과의 사이에 제공된 버퍼층이라고 할 수도 있고, 버퍼층은 상기 구성에 한정되지 않는다.

<186> 단결정 반도체층(130)은, 단결정 반도체 기판(108)으로부터 지지 기판(101)에 전재되고, 전영역에서 레이저광 조사에 의한 용융 상태를 거쳐 재단결정화된 단결정 반도체층이기 때문에, 결정 결함도 저감되고 결정성이 높고, 또한, 평탄성도 높은 단결정 반도체층(130)이다.

<187> 단결정 반도체층(130)에는, 분리된 단결정 반도체 기판의 도전형(포함되는 일 도전형을 부여하는 불순물 원소)에 따라, 스레시홀드 전압을 제어하기 위해 n채널형 전계효과 트랜지스터 및 p채널형 전계효과 트랜지스터의 형성 영역에 맞추어, 봉소, 알루미늄, 갈륨 등의 p형을 부여하는 불순물 원소, 또는 인, 비소 등의 n형을 부여하는 불순물 원소를 첨가하여도 좋다. 불순물 원소의 도즈량은  $1 \times 10^{12} / \text{cm}^2 \sim 1 \times 10^{14} / \text{cm}^2$  정도로 행하면 좋다.

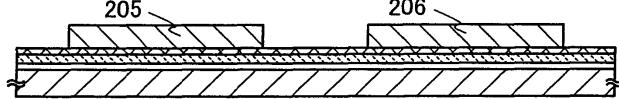

<188> 단결정 반도체층(130)을 예칭하여, 반도체소자의 배치에 맞추어 섬 형상으로 분리된 단결정 반도체층(205, 206)을 형성한다(도 7(B) 참조).

<189> 단결정 반도체층 위의 산화막을 제거하고, 단결정 반도체층(205, 206)을 덮는 게이트 절연층(207)을 형성한다. 본 실시형태에서의 단결정 반도체층(205, 206)은 평탄성이 높기 때문에, 단결정 반도체층(205, 206) 위에 형성되는 게이트 절연층이 박막의 게이트 절연층이어도 피복성 좋게 덮을 수 있다. 따라서, 게이트 절연층의 피복 불량에 의한 특성 불량을 방지할 수 있고, 고신뢰성의 반도체장치를 수율 좋게 제작할 수 있다. 게이트 절연층(207)의 박막화는 박막트랜지스터를 저전압, 고속으로 동작시키는 효과가 있다.

<190> 게이트 절연층(207)은 산화규소, 또는 산화규소와 질화규소의 적층 구조로 형성하면 좋다. 게이트 절연층(207)은, 플라즈마 CVD법이나 감압 CVD법에 의해 절연막을 퇴적함으로써 형성해도 좋고, 플라즈마 처리에 의한 고상 산화 또는 고상 질화로 형성하면 좋다. 단결정 반도체층을 플라즈마 처리에 의해 산화 또는 질화함으로써 형성하는 게이트 절연층은, 치밀하고 절연 내압이 높고 신뢰성이 뛰어나기 때문이다. 예를 들어, 아산화질소( $\text{N}_2\text{O}$ )를 Ar으로 1~3배(유량비)로 희석하여, 10~30 Pa의 압력에서 3~5 kW의 마이크로파(2.45 GHz) 전력을 인가하여 단결정 반도체층(205, 206)의 표면을 산화 또는 질화시킨다. 이 처리에 의해 1 nm~10 nm(바람직하게는 2 nm~6 nm)의 절연막을 형성한다. 또한, 아산화질소( $\text{N}_2\text{O}$ )와 실란( $\text{SiH}_4$ )을 도입하고, 10~30 Pa의 압력에서 3~5 kW의 마이크로파(2.45 GHz) 전력을 인가하여 기상 성장법에 의해 산화질화규소막을 형성하여 게이트 절연층을 형성한다. 고상 반응과 기상 성장법에 의한 반응을 조합함으로써, 계면 준위 밀도가 낮고 절연 내압이 뛰어난 게이트 절연층을 형성할 수 있다.

<191> 또한, 게이트 절연층(207)으로서, 이산화지르코늄, 산화하프늄, 이산화티탄, 오산화탄탈 등의 고유전율 재료를 사용해도 좋다. 게이트 절연층(207)에 고유전율 재료를 사용함으로써, 게이트 리크 전류를 저감할 수 있다.

<192> 게이트 절연층(207) 위에 게이트 전극층(208) 및 게이트 전극층(209)을 형성한다(도 7(C) 참조). 게이트 전극층(208, 209)은, 스퍼터링법, 증착법, CVD법 등의 방법에 의해 형성할 수 있다. 게이트 전극층(208, 209)은 탄탈(Ta), 텅스텐(W), 티탄(Ti), 몰리브덴(Mo), 알루미늄(Al), 구리(Cu), 크롬(Cr), 네오디뮴(Nd)으로부터 선택된 원소, 또는 상기 원소를 주성분으로 하는 합금 재료 또는 화합물 재료로 형성하면 좋다. 또한, 게이트 전극층(208, 209)으로서, 인 등의 불순물 원소를 도핑한 다결정 실리콘막으로 대표되는 반도체막이나, AgPdCu 합금을 사용해도 좋다.

<193> 단결정 반도체층(206)을 덮는 마스크(211)를 형성한다. 마스크(211) 및 게이트 전극층(208)을 마스크로 하여, n형을 부여하는 불순물 원소(210)를 첨가하여, 제1 n형 불순물 영역(212a, 212b)을 형성한다(도 7(D) 참조). 본 실시형태에서는, 불순물 원소를 포함하는 도핑 가스로서 포스핀( $\text{PH}_3$ )을 사용한다. 여기서는, 제1 n형 불순물 영역(212a, 212b)에, n형을 부여하는 불순물 원소가  $1 \times 10^{17} \sim 5 \times 10^{18} \text{ atoms/cm}^3$  정도의 농도로 함유되도록

첨가한다. 본 실시형태에서는, n형을 부여하는 불순물 원소로서 인(P)을 사용한다.

<194> 다음에, 단결정 반도체층(205)을 덮는 마스크(214)를 형성한다. 마스크(214) 및 게이트 전극층(209)을 마스크로 하여, p형을 부여하는 불순물 원소(213)를 첨가하여, 제1 p형 불순물 영역(215a) 및 제1 p형 불순물 영역(215b)을 형성한다(도 7(E) 참조). 본 실시형태에서는, 불순물 원소로서 봉소(B)를 사용하기 때문에, 불순물 원소를 포함하는 도핑 가스로서는 디보란( $B_2H_6$ ) 등을 사용한다.

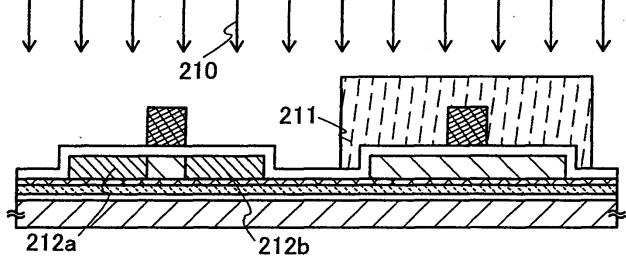

<195> 마스크(214)를 제거하고, 게이트 전극층(208, 209)의 측면에 사이드월(sidewall) 구조의 측벽 절연층(216a~216d), 및 게이트 절연층(233a, 233b)을 형성한다(도 8(A) 참조). 측벽 절연층(216a~216d)은, 게이트 전극층(208, 209)을 덮는 절연층을 형성한 후, 이것을 RIE(Reactive ion etching: 반응성 이온 에칭)법에 의한 이방성 에칭에 의해 가공하고, 게이트 전극층(208, 209)의 측벽에 자기정합적으로 사이드월 구조의 측벽 절연층(216a~216d)을 형성하면 좋다. 여기서, 절연층의 재료에 대하여 특별히 한정은 없고, TEOS(Tetra-Ethyl-Ortho-Silicate) 또는 실란 등과, 산소 또는 아산화질소 등을 반응시켜 형성한 단차 피복성이 좋은 산화규소인 것이 바람직하다. 절연층은 열 CVD, 플라즈마 CVD, 상압 CVD, 바이어스 ECRCVD, 스퍼터링 등의 방법에 의해 형성할 수 있다. 게이트 절연층(233a, 233b)은 게이트 전극층(208, 209) 및 측벽 절연층(216a~216d)을 마스크로 하여 게이트 절연층(207)을 에칭하여 형성할 수 있다.

<196> 또한, 본 실시형태에서는, 절연층을 에칭할 때, 게이트 전극층 위의 절연층을 제거하여, 게이트 전극층을 노출시키지만, 절연층을 게이트 전극층 위에 남기는 형상으로 측벽 절연층(216a~216d)을 형성하여도 좋다. 또한, 후의 공정에서 게이트 전극층 위에 보호막을 형성해도 좋다. 이와 같이 게이트 전극층을 보호함으로써, 에칭 가공할 때, 게이트 전극층의 막 감소를 막을 수 있다. 또한, 소스 영역 및 드레인 영역에 실리사이드를 형성하는 경우, 실리사이드 형성시에 성막하는 금속막과 게이트 전극층이 접하지 않기 때문에, 금속막의 재료와 게이트 전극층의 재료가 반응하기 쉬운 재료이어도, 화학 반응이나 확산 등의 불량을 방지할 수 있다. 에칭 방법은, 건식 에칭법이어도 습식 에칭법이어도 좋고, 다양한 에칭 방법을 이용할 수 있다. 본 실시형태에서는, 건식 에칭법을 사용한다. 에칭용 가스로서는,  $Cl_2$ ,  $BCl_3$ ,  $SiCl_4$  또는  $CCl_4$  등을 대표로 하는 염소계 가스,  $CF_4$ ,  $SF_6$  또는  $NF_3$  등을 대표로 하는 불소계 가스 또는  $O_2$ 를 적절히 사용할 수 있다.

<197> 다음에, 단결정 반도체층(206)을 덮는 마스크(218)를 형성한다. 마스크(218), 게이트 전극층(208), 측벽 절연층(216a, 216b)을 마스크로 하여 n형을 부여하는 불순물 원소(217)를 첨가하여, 제2 n형 불순물 영역(219a, 219b) 및 제3 n형 불순물 영역(220a, 220b)이 형성된다. 본 실시형태에서는, 불순물 원소를 포함하는 도핑 가스로서  $PH_3$ 를 사용한다. 여기서는, 제2 n형 불순물 영역(219a, 219b)에 n형을 부여하는 불순물 원소가  $5 \times 10^{19}$  ~ $5 \times 10^{20}$  atoms/cm<sup>3</sup> 정도의 농도로 함유되도록 첨가한다. 또한, 단결정 반도체층(205)에 채널 형성 영역(221)이 형성된다(도 8(B) 참조).

<198> 제2 n형 불순물 영역(219a) 및 제2 n형 불순물 영역(219b)은 고농도 n형 불순물 영역이고, 소스, 드레인으로서 기능한다. 한편, 제3 n형 불순물 영역(220a, 220b)은 저농도 불순물 영역이고, LDD(Lightly Doped Drain) 영역이 된다. 제3 n형 불순물 영역(220a, 220b)은 게이트 전극층(208)으로 덮이지 않은 Loff 영역에 형성되기 때문에, 오프 전류를 저감하는 효과가 있다. 이 결과, 더욱 신뢰성이 높고, 저소비전력의 반도체장치를 제작하는 것이 가능하다.

<199> 마스크(218)를 제거하고, 단결정 반도체층(205)을 덮는 마스크(223)를 형성한다. 마스크(223), 게이트 전극층(209), 측벽 절연층(216c, 216d)을 마스크로 하여, p형을 부여하는 불순물 원소(222)를 첨가하여, 제2 p형 불순물 영역(224a, 224b) 및 제3 p형 불순물 영역(225a, 225b)을 형성한다.

<200> 제2 p형 불순물 영역(224a, 224b)에 p형을 부여하는 불순물 원소가  $1 \times 10^{20}$  ~ $5 \times 10^{21}$  atoms/cm<sup>3</sup> 정도의 농도로 함유되도록 첨가한다. 본 실시형태에서는, 제3 p형 불순물 영역(225a, 225b)은, 측벽 절연층(216c, 216d)에 의해, 자기정합적으로 제2 p형 불순물 영역(224a, 224b)보다 저농도가 되도록 형성한다. 또한, 단결정 반도체층(206)에 채널 형성 영역(226)이 형성된다(도 8(C) 참조).

<201> 제2 p형 불순물 영역(224a, 224b)은 고농도 p형 불순물 영역이고, 소스, 드레인으로서 기능한다. 한편, 제3 p형 불순물 영역(225a, 225b)은 저농도 불순물 영역이고, LDD(Lightly Doped Drain) 영역이 된다. 제3 p형 불순물 영역(225a, 225b)은 게이트 전극층(209)으로 덮이지 않은 Loff 영역에 형성되기 때문에, 오프 전류를 저감하는 효과가 있다. 이 결과, 더욱 신뢰성이 높고, 저소비전력의 반도체장치를 제작하는 것이 가능하다.

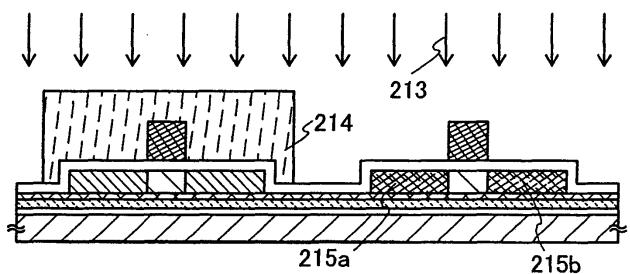

- <202> 마스크(223)를 제거하고, 불순물 원소를 활성화하기 위해 가열 처리, 강광의 조사, 또는 레이저광의 조사를 행하여도 좋다. 활성화와 동시에 게이트 절연층에의 플라즈마 대미지나 게이트 절연층과 단결정 반도체층과의 계면에의 플라즈마 대미지를 회복할 수 있다.

- <203> 다음에, 게이트 전극층 및 게이트 절연층을 덮는 층간절연층을 형성한다. 본 실시형태에서는, 보호막이 되는 수소를 포함하는 절연막(227)과 절연층(228)과의 적층 구조로 한다. 절연막(227)과 절연층(228)은, 스퍼터링법 또는 플라즈마 CVD를 이용한 질화규소막, 질화산화규소막, 산화질화규소막, 산화규소막이어도 좋고, 다른 규소를 포함하는 절연막을 단층 또는 3층 이상의 적층 구조로서 사용하여도 좋다.

- <204> 또한, 질소 분위기 중에서, 300°C~550°C로 1~12 시간의 열처리를 행하여, 단결정 반도체층을 수소화하는 공정을 행한다. 바람직하게는, 400°C~500°C로 행한다. 이 공정은 층간절연층인 절연막(227)에 포함되는 수소에 의해 단결정 반도체층의 맹글링 본드를 종단하는 공정이다. 본 실시형태에서는, 410°C, 1 시간의 가열 처리를 행한다.

- <205> 절연막(227) 및 절연층(228)으로서는 그 외에 질화알루미늄(AlN), 산화질화알루미늄(AlON), 질소 함유량이 산소 함유량보다 많은 질화산화알루미늄(AlNO) 또는 산화알루미늄, 다이아몬드 라이크 카본(diamond-like carbon: DLC), 질소 함유 탄소(CN) 그 외의 무기 절연성 재료를 포함하는 물질로부터 선택된 재료로 형성할 수 있다. 또한, 실록산 수지를 사용해도 좋다. 또한, 실록산 수지란, Si-O-Si 결합을 포함하는 수지에 상당한다. 실록산은, 실리콘(Si)과 산소(O)와의 결합으로 골격 구조가 구성된다. 치환기로서 적어도 수소를 함유하는 유기기(예를 들어, 알킬기, 아릴기)가 사용된다. 유기기는 플루오로기를 포함하여도 좋다. 또한, 유기 절연성 재료를 사용해도 좋고, 유기 재료로서는, 폴리이미드, 아크릴, 폴리아미드, 폴리이미드 아미드, 레지스트 또는 벤조시클로부텐, 폴리실라잔을 사용할 수 있다. 평탄성이 좋은 도포법에 의해 형성되는 도포막을 사용해도 좋다.

- <206> 절연막(227) 및 절연층(228)의 형성 방법으로는, 딥, 스프레이 도포, 닉터 나이프, 롤 코터, 커튼 코터, 나이프 코터, CVD법, 증착법 등을 채용할 수 있다. 액적 토출법에 의해 절연막(227) 및 절연층(228)을 형성해도 좋다. 액적 토출법을 이용한 경우에는 재료액을 절약할 수 있다. 또한, 액적 토출법과 같이 패턴을 전사 또는 묘사할 수 있는 방법, 예를 들어, 인쇄법(스크린 인쇄나 오프셋 인쇄 등 패턴이 형성되는 방법) 등도 이용할 수 있다.

- <207> 다음에, 레지스트로 이루어지는 마스크를 사용하여 절연막(227) 및 절연층(228)에 단결정 반도체층에 도달하는 콘택트 홀(개구)을 형성한다. 예칭은, 사용하는 재료의 선택비에 따라, 1회 행하여도 좋고 다수회 행하여도 좋다. 예칭에 의해, 절연막(227) 및 절연층(228)을 제거하고, 소스 영역 또는 드레인 영역인 제2 n형 불순물 영역(219a, 219b) 및 제2 p형 불순물 영역(224a, 224b)에 도달하는 개구를 형성한다. 예칭은, 습식 예칭이어도 좋고 전식 예칭이어도 좋고, 양쪽 모두를 사용해도 좋다. 습식 예칭의 예천트는, 불소 수소 암모늄 및 불화암모늄을 포함하는 혼합 용액과 같은 불산계 용액을 사용하면 좋다. 예칭용 가스로서는, Cl<sub>2</sub>, BC1<sub>3</sub>, SiCl<sub>4</sub> 또는 CCl<sub>4</sub> 등을 대표로 하는 염소계 가스, CF<sub>4</sub>, SF<sub>6</sub> 또는 NF<sub>3</sub> 등을 대표로 하는 불소계 가스 또는 O<sub>2</sub>를 적절히 사용할 수 있다. 또한 사용하는 예칭용 가스에 불활성 기체를 첨가하여도 좋다. 첨가하는 불활성 원소로서는, He, Ne, Ar, Kr, Xe으로부터 선택된 1종 또는 다수종의 원소를 사용할 수 있다.

- <208> 개구를 덮도록 도전막을 형성하고, 도전막을 예칭하여 각 소스 영역 또는 드레인 영역의 일부에 각각 전기적으로 접속하는 소스 전극층 또는 드레인 전극층으로서 기능하는 배선층(229a, 229b, 230a, 230b)을 형성한다. 배선층은, PVD법, CVD법, 증착법 등에 의해 도전막을 성막한 후, 소망의 형상으로 예칭하여 형성할 수 있다. 또한, 액적 토출법, 인쇄법, 전해 도금법 등에 의해, 소정의 장소에 선택적으로 도전층을 형성할 수도 있다. 또한, 리플로우(reflow)법, 다마신(damascene)법을 이용해도 좋다. 배선층의 재료는, Ag, Au, Cu, Ni, Pt, Pd, Ir, Rh, W, Al, Ta, Mo, Cd, Zn, Fe, Ti, Zr, Ba 등의 금속, 및 Si, Ge, 또는 그의 합금 또는 그의 질화물을 사용하여 형성한다. 또한, 이들의 적층 구조로 하여도 좋다.

- <209> 이상의 공정에 의해 CMOS 구조의 n채널형 박막트랜지스터인 박막트랜지스터(231) 및 p채널형 박막트랜지스터인 박막트랜지스터(232)를 포함하는 반도체장치를 제작할 수 있다(도 8(D) 참조). 도시하지 않았지만, 본 실시형태는 CMOS 구조이기 때문에, 박막트랜지스터(231)와 박막트랜지스터(232)는 전기적으로 접속하고 있다.

- <210> 본 실시형태에 한정되지 않고, 박막트랜지스터는 채널 형성 영역이 1개 형성되는 싱글 게이트 구조이어도 좋고, 2개 형성되는 더블 게이트 구조, 또는 3개 형성되는 트리플 게이트 구조이어도 좋다.

- <211> 이상과 같이, 단결정 반도체 기판으로부터 지지 기판으로 전재되고, 전영역에서 레이저광 조사에 의한 용융 상태를 거쳐 재단결정화된 단결정 반도체층을 가지는 반도체 기판을 사용하기 때문에, 단결정 반도체층은 결정 결

함도 저감되고 결정성이 높고, 또한, 평탄성도 높다.

<212> 따라서, 고성능 및 고신뢰성의 반도체장치를 수율 좋게 제작할 수 있다.

<213> 본 실시형태는 실시형태 1 및 실시형태 2와 적절히 조합할 수 있다.

<214> [실시형태 4]

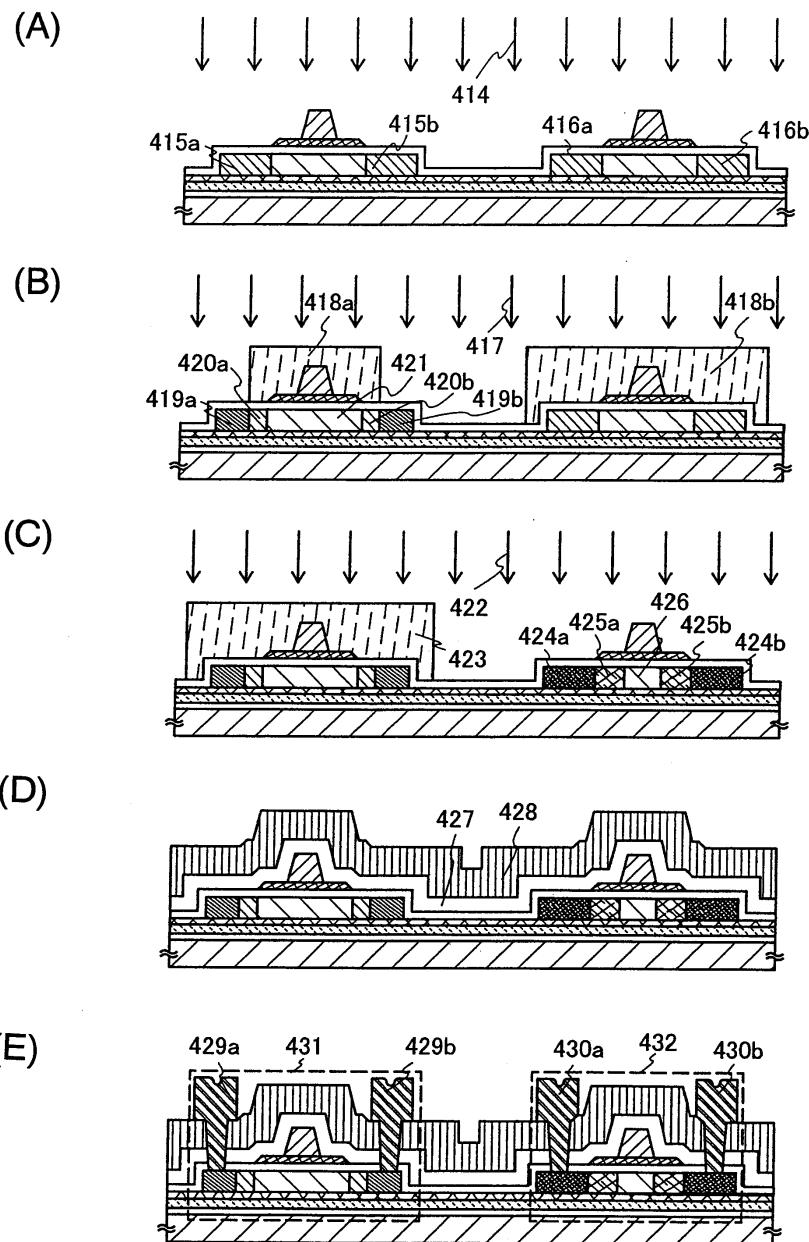

<215> 본 실시형태에서는, 고성능 및 고신뢰성의 반도체소자를 가지는 반도체장치를 수율 좋게 제작하는 것을 목적으로 한 반도체장치 제조방법의 일례로서, 실시형태 3과는 다른 구조의 CMOS에 관하여 도 21 및 도 22를 사용하여 설명한다. 또한, 실시형태 1 및 실시형태 3과 동일 부분 또는 동일한 기능을 가지는 부분의 반복 설명은 생략한다.

<216> 도 21(A)에 나타내는 바와 같이, 반도체 기판을 준비한다. 본 실시형태에서는, 도 7(A)의 반도체 기판을 사용한다. 절연 표면을 가지는 지지 기판(101) 위에, 블로킹층(109), 절연층(104), 및 보호층(121)을 사이에 두고 단결정 반도체층(130)이 고정된 반도체 기판을 사용한다. 단결정 반도체층(130)은 도 1(D)와 대응하고, 블로킹 층(109), 절연층(104), 보호층(121)은 도 4(C)와 대응한다. 또한, 여기서는 도 7(A)에 나타내는 구성의 반도체 기판을 적용하는 예를 나타내지만, 본 명세서에서 나타내는 그 외의 구성의 반도체 기판도 적용할 수 있다. 또한, 블로킹층(109), 절연층(104), 및 보호층(121)을 총괄하여, 지지 기판(101)과 단결정 반도체층(130)과의 사이에 제공된 벼퍼층이라고 할 수도 있고, 벼퍼층은 상기 구성에 한정되지 않는다.

<217> 단결정 반도체층(130)은, 단결정 반도체 기판(108)으로부터 지지 기판(101)에 전재되고, 전영역에서 레이저광 조사에 의한 용융 상태를 거쳐 재단결정화된 단결정 반도체층이기 때문에, 결정 결함도 저감되고 결정성이 높고, 또한, 평탄성도 높은 단결정 반도체층(130)이다.

<218> 단결정 반도체층(130)에는, 분리한 단결정 반도체 기판의 도전형(포함되는일 도전형을 부여하는 불순물 원소)에 따라, 스레시홀드 전압을 제어하기 위하여 n채널형 전계효과 트랜지스터 및 p채널형 전계효과 트랜지스터의 형성 영역에 맞추어, 봉소, 알루미늄, 갈륨 등의 p형을 부여하는 불순물 원소, 또는 인, 비소 등의 n형을 부여하는 불순물 원소를 첨가하여도 좋다. 불순물 원소의 도즈량은  $1 \times 10^{12} / \text{cm}^2$  내지  $1 \times 10^{14} / \text{cm}^2$  정도로 행하면 좋다.

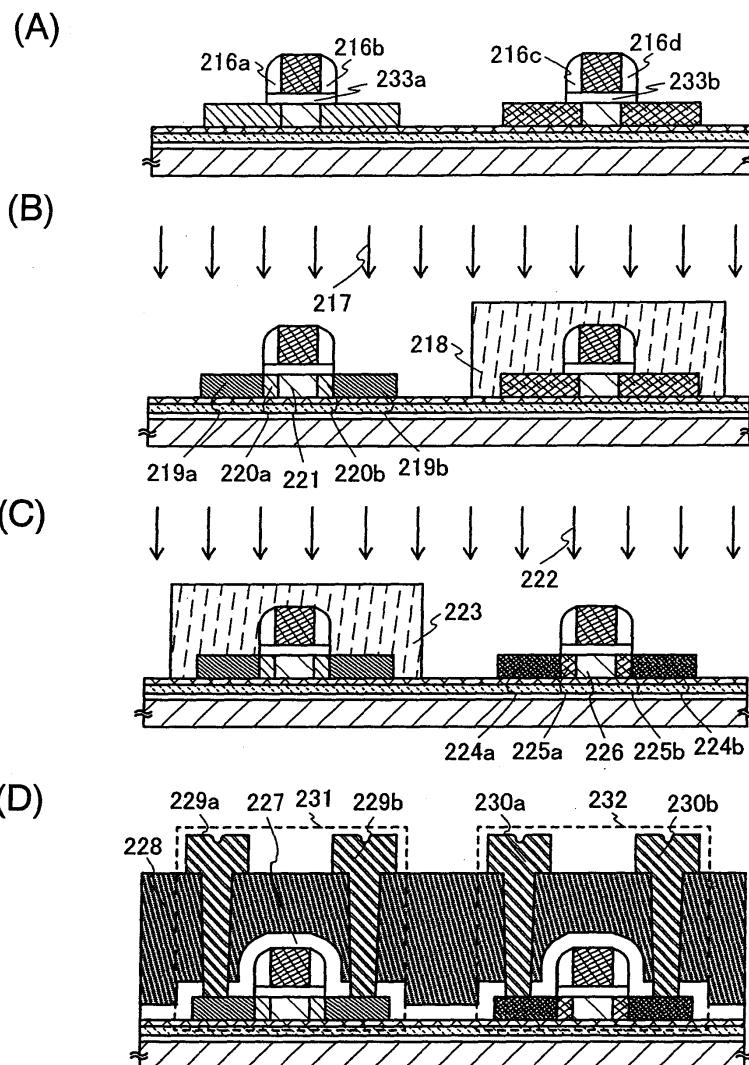

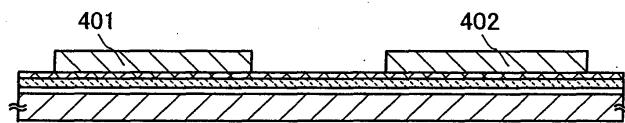

<219> 단결정 반도체층(130)을 예칭하여, 반도체소자의 배치에 맞추어 섬 형상으로 분리한 단결정 반도체층(401, 402)을 형성한다(도 21(B) 참조).

<220> 단결정 반도체층 위의 산화막을 제거하고, 단결정 반도체층(401, 402)을 덮는 게이트 절연층(403)을 형성한다. 본 실시형태에서의 단결정 반도체층(401, 402)은 평탄성이 높기 때문에, 단결정 반도체층(401, 402) 위에 형성되는 게이트 절연층이 박막의 게이트 절연층이어도 괴복성 좋게 덮을 수 있다. 따라서, 게이트 절연층의 괴복 불량에 의한 특성 불량을 방지할 수 있고, 고신뢰성의 반도체장치를 수율 좋게 제작할 수 있다. 게이트 절연층(403)의 박막화는, 트랜지스터를 저전압, 고속으로 동작시키는 효과가 있다.

<221> 게이트 절연층(403)은 산화규소, 또는 산화규소와 질화규소의 적층 구조로 형성하면 좋다. 게이트 절연층(403)은, 플라즈마 CVD법이나 감압 CVD법에 의해 절연막을 퇴적함으로써 형성해도 좋고, 플라즈마 처리에 의한 고상 산화 또는 고상 질화로 형성하면 좋다. 단결정 반도체층을 플라즈마 처리에 의해 산화 또는 질화함으로써 형성하는 게이트 절연층은 치밀하고 절연 내압이 높고 신뢰성이 뛰어나기 때문이다. 예를 들어, 아산화질소( $\text{N}_2\text{O}$ )를 Ar으로 1~3배(유량비)로 희석하여, 10~30 Pa의 압력에서 3~5 kW의 마이크로파(2.45 GHz) 전력을 인가하여 단결정 반도체층(401, 402)의 표면을 산화 또는 질화시킨다. 이 처리에 의해 1 nm~10 nm(바람직하게는 2 nm~6 nm)의 절연막을 형성한다. 또한, 아산화질소( $\text{N}_2\text{O}$ )와 실란( $\text{SiH}_4$ )을 도입하고, 10~30 Pa의 압력에서 3~5 kW의 마이크로파(2.45 GHz) 전력을 인가하여 기상 성장법에 의해 산화질화규소막을 형성하여 게이트 절연층을 형성한다. 고상 반응과 기상 성장법에 의한 반응을 조합함으로써, 계면 준위 밀도가 낮고 절연 내압이 뛰어난 게이트 절연층을 형성할 수 있다.

<222> 또한, 게이트 절연층(403)으로서, 이산화지르코늄, 산화하프늄, 이산화티탄, 오산화탄탈 등의 고유전율 재료를 사용하여도 좋다. 게이트 절연층(403)에 고유전율 재료를 사용함으로써, 게이트 리크 전류를 저감할 수 있다.

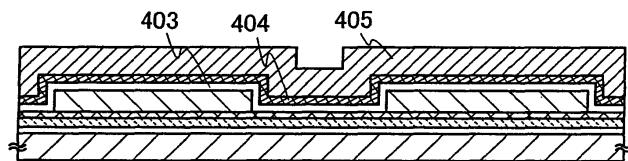

<223> 또한, 게이트 절연층(403) 위에, 게이트 전극층을 형성하는 도전막(404) 및 도전막(405)을 순차로 형성한다(도 21(C) 참조).

- <224> 게이트 전극층을 형성하는 도전막(404, 405)은, 탄탈, 질화탄탈, 텉스텐, 티탄, 몰리브덴, 알루미늄, 구리, 크롬, 또는 니오브 등으로부터 선택된 원소, 또는 이들 원소를 주성분으로 하는 합금 재료 또는 화합물 재료, 인 등의 불순물 원소를 도핑한 다결정 실리콘으로 대표되는 반도체 재료를 사용하여, CVD법이나 스팍터링법에 의해, 단층막 또는 적층막으로 형성한다. 적층막으로 하는 경우는, 상이한 도전 재료를 사용하여 형성할 수도 있고, 동일한 도전 재료를 사용하여 형성할 수도 있다. 본 실시형태에서는, 게이트 전극을 형성하는 도전막을, 도전막(404) 및 도전막(405)의 2층 구조로 형성하는 예를 나타낸다.

- <225> 게이트 전극층을 형성하는 도전막을, 도전막(404) 및 도전막(405)의 2층의 적층 구조로 하는 경우는, 예를 들어, 질화탄탈막과 텉스텐막, 질화텅스텐막과 텉스텐막, 질화몰리브덴막과 몰리브덴막의 적층막을 형성할 수 있다. 또한, 질화탄탈막과 텉스텐막과의 적층막으로 하면, 양자의 에칭 선택비를 취하기 쉬워 바람직하다. 또한, 예시한 2층의 적층막에서, 먼저 기재한 막이 게이트 절연층(403) 위에 형성되는 막으로 하는 것이 바람직하다. 본 실시형태에서는, 도전막(404)은 20 nm 내지 100 nm의 두께로 형성하고, 도전막(405)은 100 nm 내지 400 nm의 두께로 형성한다. 또한, 게이트 전극층은 3층 이상의 적층 구조로 할 수도 있고, 그 경우는, 몰리브덴막과 알루미늄막과 몰리브덴막의 적층 구조를 채용하면 좋다.

- <226> 다음에, 도전막(405) 위에 레지스트 마스크(410a, 410b)를 선택적으로 형성한다. 그리고, 레지스트 마스크(410a, 410b)를 사용하여 제1 에칭 처리 및 제2 에칭 처리를 행한다.

- <227> 먼저, 레지스트 마스크(410a, 410b)를 사용한 제1 에칭 처리에 의해 도전막(404, 405)을 선택적으로 에칭하여, 단결정 반도체층(401) 위에 제1 게이트 전극층(406) 및 도전층(408)을 형성하고, 단결정 반도체층(402) 위에 제1 게이트 전극층(407) 및 도전층(409)을 형성한다(도 21(D) 참조).

- <228> 다음에, 레지스트 마스크(410a, 410b)를 사용한 제2 에칭 처리에 의해 도전층(408) 및 도전층(409)의 일부를 에칭하여, 제2 게이트 전극층(412) 및 제2 게이트 전극층(413)을 형성한다(도 21(E) 참조). 또한, 제2 게이트 전극층(412) 및 제2 게이트 전극층(413)은 제1 게이트 전극층(406) 및 제1 게이트 전극층(407)보다 폭(캐리어가 채널 형성 영역을 흐르는 방향(소스 영역과 드레인 영역을 연결하는 방향)에 평행한 방향의 길이)이 작게 되도록 형성한다. 이와 같이 하여, 제1 게이트 전극층(406) 및 제2 게이트 전극층(412)으로 이루어지는 2층 구조의 게이트 전극층, 및 제1 게이트 전극층(407) 및 제2 게이트 전극층(413)으로 이루어지는 2층 구조의 게이트 전극층을 형성한다.

- <229> 제1 에칭 처리 및 제2 에칭 처리에 적용하는 에칭법은 적절히 선택하면 좋지만, 에칭 속도를 향상시키기 위해서는 ECR(Electron Cyclotron Resonance) 방식이나 ICP(Inductively Coupled Plasma: 유도 결합 플라즈마) 방식 등의 고밀도 플라즈마원을 이용한 건식 에칭 장치를 사용한다. 제1 에칭 처리 및 제2 에칭 처리의 에칭 조건을 적절히 조절함으로써, 제1 게이트 전극층(406, 407) 및 제2 게이트 전극층(412, 413)의 측면을 소망의 테이퍼 형상으로 할 수 있다. 소망의 형상의 제1 게이트 전극층(406, 407) 및 제2 게이트 전극층(412, 413)을 형성한 후, 레지스트 마스크(410a, 410b)를 제거한다.

- <230> 다음에, 제1 게이트 전극층(406) 및 제2 게이트 전극층(412), 제1 게이트 전극층(407) 및 제2 게이트 전극층(413)을 마스크로 하여, 단결정 반도체층(401) 및 단결정 반도체층(402)에 불순물 원소(414)를 첨가한다. 단결정 반도체층(401)에는, 제1 게이트 전극층(406) 및 제2 게이트 전극층(412)을 마스크로 하여 자기정합적으로 불순물 영역(415a, 415b)이 형성된다. 또한, 단결정 반도체층(402)에는, 제1 게이트 전극층(407) 및 제2 게이트 전극층(413)을 마스크로 하여 자기정합적으로 불순물 영역(416a, 416b)이 형성된다(도 22(A) 참조).

- <231> 불순물 원소(414)로서는, 봉소, 알루미늄, 갈륨 등의 p형 불순물 원소, 또는 인, 비소 등의 n형 불순물 원소를 첨가한다. 여기서는, n채널형 트랜지스터의 저농도 불순물 영역을 형성하기 위하여, 불순물 원소(414)로서 n형 불순물 원소인 인을 첨가한다. 또한, 불순물 영역(415a, 415b, 416a, 416b)에,  $1 \times 10^{17} \text{ atoms/cm}^3$  내지  $5 \times 10^{18} \text{ atoms/cm}^3$  정도의 농도로 인이 함유되도록, 인을 첨가하는 것으로 한다.

- <232> 다음에, n채널형 트랜지스터의 소스 영역 및 드레인 영역이 되는 불순물 영역(고농도 불순물 영역)을 형성하기 위해, 단결정 반도체층(401)을 부분적으로 덮도록 레지스트 마스크(418a)를 형성하고, 단결정 반도체층(402)을 덮도록 레지스트 마스크(418b)를 선택적으로 형성한다. 그리고, 레지스트 마스크(418a)를 마스크로 하여, 단결정 반도체층(401)에 불순물 원소(417)를 첨가하여, 단결정 반도체층(401)에 불순물 영역(419a, 419b)을 형성한다(도 22(B) 참조).

- <233> 불순물 원소(417)로서는, n형 불순물 원소인 인을 단결정 반도체층(401)에 첨가하고, 첨가되는 농도를  $5 \times 10^{19}$

atoms/cm<sup>3</sup> 내지  $5 \times 10^{20}$  atoms/cm<sup>3</sup>가 되도록 하는 것으로 한다. 불순물 영역(419a, 419b)은 고농도 n형 불순물 영역이고, 소스 영역 또는 드레인 영역으로서 기능한다. 불순물 영역(419a, 419b)은 제1 게이트 전극층(406) 및 제2 게이트 전극층(412)과 겹치지 않는 영역에 형성된다.

<234> 또한, 단결정 반도체층(401)에서, 불순물 영역(420a, 420b)은 불순물 원소(417)가 첨가되지 않았던 저농도 불순물 영역이다. 불순물 영역(420a, 420b)은, 불순물 영역(419a, 419b)보다 n형을 부여하는 불순물 원소의 농도가 낮고, 저농도 불순물 영역이므로, 고저항 영역 또는 LDD 영역으로서 기능한다. 단결정 반도체층(401)에서, 제1 게이트 전극층(406) 및 제2 게이트 전극층(412)과 겹치는 영역에 채널 형성 영역(421)이 형성된다.

<235> 또한, LDD 영역이란, 채널 형성 영역과, 고농도로 불순물 원소를 첨가하여 형성하는 소스 영역 또는 드레인 영역과의 사이에 형성하는 저농도로 불순물 원소를 첨가한 영역이다. LDD 영역을 형성하면, 드레인 영역 근방의 전계를 완화하여 핫 캐리어 주입에 의한 열화(劣化)를 방지하는 효과가 있다. 또한, 핫 캐리어에 의한 온(ON) 전류값의 열화를 방지하기 위해, 게이트 절연층을 사이에 두고 LDD 영역을 게이트 전극과 겹쳐 배치시킨 구조 ("GOLD(Gate-drain Overlapped LDD) 구조"라고도 부른다)로 하여도 좋다.

<236> 다음에, 레지스트 마스크(418a, 418b)를 제거한 후, p채널형 트랜지스터의 소스 영역 및 드레인 영역을 형성하기 위해, 단결정 반도체층(401)을 덮도록 레지스트 마스크(423)를 형성한다. 그리고, 레지스트 마스크(423), 제1 게이트 전극층(407) 및 제2 게이트 전극층(413)을 마스크로 하여 불순물 원소(422)를 첨가하여, 단결정 반도체층(402)에 불순물 영역(424a, 424b)과, 불순물 영역(425a, 425b)과, 채널 형성 영역(426)을 형성한다(도 22(C) 참조).

<237> 불순물 원소(422)는, 붕소, 알루미늄, 갈륨 등의 p형 불순물 원소가 사용된다. 여기서는 p형 불순물 원소인 붕소를  $1 \times 10^{20}$  atoms/cm<sup>3</sup> 내지  $5 \times 10^{21}$  atoms/cm<sup>3</sup> 정도 함유되도록 첨가하는 것으로 한다.

<238> 단결정 반도체층(402)에서, 고농도 불순물 영역인 불순물 영역(424a, 424b)은 제1 게이트 전극층(407) 및 제2 게이트 전극층(413)과 겹치지 않는 영역에 형성되고, 소스 영역 또는 드레인 영역으로서 기능한다. 불순물 영역(424a, 424b)에, 여기서는 p형 불순물 원소인 붕소를  $1 \times 10^{20}$  atoms/cm<sup>3</sup> 내지  $5 \times 10^{21}$  atoms/cm<sup>3</sup> 정도 함유되도록 한다. 불순물 영역(424a, 424b)은 불순물 영역(416a, 416b)에 불순물 원소(422)가 첨가된 영역이다. 불순물 영역(416a, 416b)은 n형의 도전성을 나타내기 때문에, 불순물 영역(424a, 424b)이 p형의 도전성을 가지도록, 불순물 원소(422)를 첨가한다. 불순물 영역(424a, 424b)에 함유되는 불순물 원소(422)의 농도를 조절함으로써, 불순물 영역(424a, 424b)을 소스 영역 또는 드레인 영역으로서 기능시킬 수 있다.

<239> 불순물 영역(425a, 425b)은, 제1 게이트 전극층(407)과 겹치고 제2 게이트 전극층(413)과 겹치지 않는 영역에 형성되어 있고, 불순물 원소(422)가 제1 게이트 전극층(407)을 관통하여 단결정 반도체층(402)에 첨가된 영역이다. 또는, 불순물 영역(425a, 425b)은 LDD 영역으로서 기능시킬 수 있다.

<240> 단결정 반도체층(402)에서, 제1 게이트 전극층(407) 및 제2 게이트 전극층(413)과 겹치는 영역에 채널 형성 영역(426)이 형성된다.

<241> 다음에, 충간절연층을 형성한다. 충간절연층은 단층 구조 또는 적층 구조로 형성할 수 있지만, 여기서는 절연층(427) 및 절연층(428)의 2층의 적층 구조로 형성한다(도 22(D) 참조).

<242> 충간절연층으로서는, CVD법이나 스팍터링법에 의해, 산화규소층, 산화질화규소층, 질화규소층, 또는 질화산화규소층 등을 형성할 수 있다. 또한, 폴리이미드, 폴리아미드, 폴리비닐페놀, 벤조시클로부텐, 아크릴 또는 에폭시 등의 유기 재료, 실록산 수지 등의 실록산 재료, 또는 옥사졸 수지 등을 사용하여, 스픬 코팅법 등의 도포법에 의해 형성할 수 있다. 또한, 실록산 재료란, Si-O-Si 결합을 포함하는 재료에 상당한다. 실록산은, 실리콘(Si)과 산소(O)와의 결합으로 골격 구조가 구성된다. 치환기로서, 적어도 수소를 함유하는 유기기(예를 들어, 알킬기, 방향족 탄화수소)가 사용된다. 유기기는 플루오로기를 포함하여도 좋다.

<243> 예를 들어, 절연층(427)으로서 질화산화규소층을 막 두께 100 nm로 형성하고, 절연층(428)으로서 산화질화규소층을 막 두께 900 nm로 형성한다. 또한, 절연층(427) 및 절연층(428)을 플라즈마 CVD법을 적용하여 연속 성막 한다. 또한, 충간절연층은 3층 이상의 적층 구조로 할 수도 있다. 또한, 산화규소층, 산화질화규소층 또는 질화규소층과, 폴리이미드, 폴리아미드, 폴리비닐페놀, 벤조시클로부텐, 아크릴, 에폭시 등의 유기 재료, 실록산 수지 등의 실록산 재료, 또는 옥사졸 수지를 사용하여 형성한 절연층과의 적층 구조로 할 수도 있다.

<244> 다음에, 충간절연층(본 실시형태에서는 절연층(427) 및 절연층(428))에 콘택트 홀을 형성하고, 이 콘택트 홀에

소스 전극층 또는 드레인 전극층으로서 기능하는 배선층(429a, 429b, 430a, 430b)을 형성한다.

<245> 콘택트 홀은, 단결정 반도체층(401)에 형성된 불순물 영역(419a, 419b)과, 단결정 반도체층(402)에 형성된 불순물 영역(424a, 424b)에 도달하도록 절연층(427) 및 절연층(428)에 선택적으로 형성한다.

<246> 배선층(429a, 429b, 430a, 430b)은, 알루미늄, 텅스텐, 티탄, 탄탈, 몰리브덴, 니켈, 네오디뮴으로부터 선택된 1종의 원소 또는 이 원소를 다수 함유하는 합금으로 이루어지는 단층막 또는 적층막을 사용할 수 있다. 예를 들어, 이 원소를 다수 함유하는 합금으로 이루어지는 도전층으로서, 티탄을 함유한 알루미늄 합금, 네오디뮴을 함유한 알루미늄 합금 등을 형성할 수 있다. 또한, 적층막으로 하는 경우, 예를 들어, 알루미늄층 또는 상술한 바와 같은 알루미늄 합금층을 티탄층 사이에 끼운 구조으로 할 수 있다.

<247> 이상의 공정으로, 단결정 반도체층을 가지는 반도체 기판을 사용하여, n채널형 트랜지스터(431) 및 p채널형 트랜지스터(432)를 제작할 수 있다.

<248> 본 실시형태는, 단결정 반도체 기판으로부터 지지 기판에 전재되고, 전영역에서 레이저광 조사에 의한 용융 상태를 거쳐 재단결정화된 단결정 반도체층을 가지는 반도체 기판을 사용하기 때문에, 단결정 반도체층은 결정 결합도 저감되고 결정성이 높고, 또한, 평탄성도 높다.

<249> 따라서, 고성능 및 고신뢰성의 반도체장치를 수율 좋게 제작할 수 있다.

<250> 본 실시형태는 실시형태 1 내지 3과 적절히 조합할 수 있다.

#### [실시형태 5]

<252> 본 실시형태에서는, 고성능 및 고신뢰성이 부여된 반도체장치로서 표시 기능을 가지는 반도체장치(액정 표시장 치라고도 한다)를 수율 좋게 생산하는 것을 목적으로 한 반도체장치 제조방법의 예를 도 9를 사용하여 설명한다. 상세하게는, 표시 소자에 액정 표시 소자를 사용하는 액정 표시장치에 대하여 설명한다.

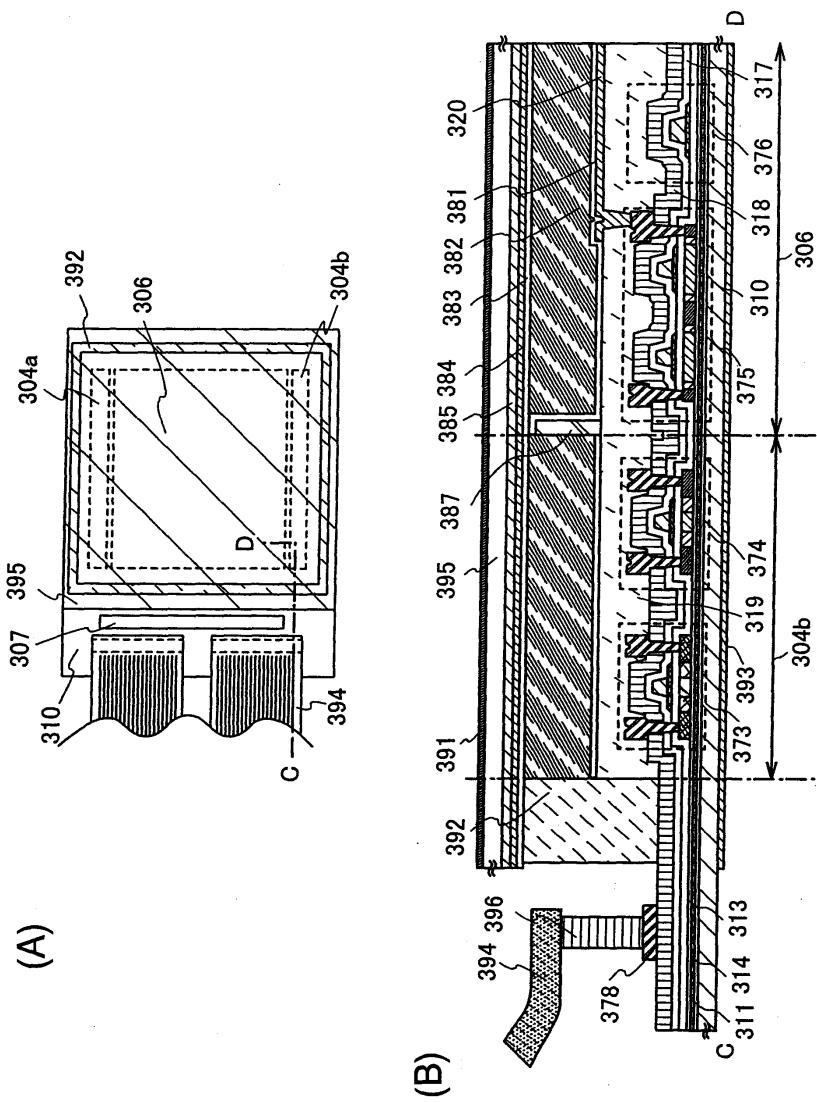

<253> 도 9(A)는, 본 발명의 일 형태인 반도체장치의 상면도이고, 도 9(B)는 도 9(A)의 선 C-D에서의 단면도이다.

<254> 도 9(A)에서 나타내는 바와 같이, 화소 영역(306), 주사선 구동회로인 구동회로 영역(304a) 및 구동회로 영역(304b)이 시일(seal)재(392)에 의해 지지 기판(310)과 대향 기판(395)과의 사이에 봉지(封止)되고, 지지 기판(310) 위에 드라이버 IC에 의해 형성된 신호선 구동회로인 구동회로 영역(307)이 제공되어 있다. 화소 영역(306)에는 트랜지스터(375) 및 용량 소자(376)가 제공되고, 구동회로 영역(304b)에는 트랜지스터(373) 및 트랜지스터(374)를 가지는 구동회로가 제공되어 있다. 본 실시형태의 반도체장치에서도 실시형태 1에서 나타내는 본 발명을 사용한 고성능 및 고신뢰성의 반도체 기판을 적용한다.

<255> 화소 영역(306)에는, 블로킹층(311), 접합면을 가지는 절연층(314), 보호층(313) 위에 스위칭 소자가 되는 트랜지스터(375)가 제공되어 있다. 본 실시형태에서는, 트랜지스터(375)에 멀티케이트형 박막트랜지스터(TFT)를 사용하고, 소스 영역 및 드레인 영역으로서 기능하는 불순물 영역을 가지는 단결정 반도체층, 게이트 절연층, 2층의 적층 구조인 게이트 전극층, 소스 전극층 및 드레인 전극층을 가지고, 소스 전극층 또는 드레인 전극층은, 단결정 반도체층의 불순물 영역과 화소 전극층이라고도 불리는 표시 소자에 사용하는 전극층(320)에 접하여 전기적으로 접속하여 있다.

<256> 단결정 반도체층 종의 불순물 영역은 그의 농도를 제어함으로써 고농도 불순물 영역 및 저농도 불순물 영역으로 할 수 있다. 이와 같이 저농도 불순물 영역을 가지는 박막트랜지스터를 LDD(Light doped drain) 구조라고 부른다. 또한, 저농도 불순물 영역은 게이트 전극과 접치도록 형성할 수 있고, 이와 같은 박막트랜지스터를 GOLD(Gate Overlaped LDD) 구조라고 부른다. 또한, 박막트랜지스터의 극성은, 불순물 영역에 인(P) 등을 사용함으로써 n형으로 한다. p형으로 하는 경우는, 붕소(B) 등을 첨가하면 좋다. 그 후, 게이트 전극 등을 덮는 절연막(317) 및 절연막(318)을 형성한다.

<257> 또한, 평탄성을 높이기 위하여, 충간절연막으로서 절연막(319)을 형성한다. 절연막(319)에는, 유기 재료 또는 무기 재료, 또는 그들의 적층 구조를 사용할 수 있다. 예를 들어, 산화규소, 질화규소, 산화질화규소, 질화산화규소, 질화알루미늄, 산화질화알루미늄, 질소 함유량이 산소 함유량보다 많은 질화산화알루미늄 또는 산화알루미늄, 다이아몬드 라이크 카본(DLC), 폴리실라잔, 질소 함유 탄소(CN), PSG(인 유리), BPSG(인 붕소 유리), 알루미나, 그 외의 무기 절연성 재료를 포함하는 물질로부터 선택된 재료로 형성할 수 있다. 또한, 유기 절연성 재료를 사용해도 좋고, 유기 재료로서는, 감광성과 비감광성 중 어느 것이어도 좋고, 폴리이미드, 아크릴, 폴리아미드, 폴리이미드아미드, 레지스트 또는 벤조시클로부텐, 실록산 수지 등을 사용할 수 있다.

- <258> 반도체소자에 사용하는 단결정 반도체층을, 본 발명을 사용한 실시형태 1과 마찬가지로 형성하므로, 단결정 반도체 기판으로부터 전재한 단결정 반도체층으로 할 수 있고, 화소 영역과 구동회로 영역을 동일 기판 위에 일체로 형성할 수 있다. 그 경우, 화소 영역(306)의 트랜ジ스터와 구동회로 영역(304b)의 트랜ジ스터는 동시에 형성된다. 물론, 구동회로 영역(307)도 마찬가지로 동일 기판 위에 일체로 형성해도 좋다. 구동회로 영역(304b)에 사용하는 트랜ジ스터는 CMOS 회로를 구성한다. CMOS 회로를 구성하는 박막트랜ジ스터는 GOLD 구조이지만, 트랜ジ스터(375)와 같은 LDD 구조를 사용할 수도 있다.

- <259> 다음에, 표시 소자에 사용하는 전극층(320) 및 절연막(319)을 덮도록, 인쇄법이나 액적 토출법에 의해, 배향막으로서 기능하는 절연층(381)을 형성한다. 또한, 절연층(381)은, 스크린 인쇄법이나 오프셋 인쇄법을 이용하면 선택적으로 형성할 수도 있다. 그 후, 러빙 처리를 행한다. 이 러빙 처리는 액정의 모드, 예를 들어, VA 모드 일 때에는 처리를 행하지 않을 때가 있다. 배향막으로서 기능하는 절연층(383)도 절연층(381)과 마찬가지이다. 계속하여, 시일재(392)를 액적 토출법에 의해 화소를 형성한 주변의 영역에 형성한다.

- <260> 그 후, 배향막으로서 기능하는 절연층(383), 대향 전극층이라고도 하는 표시 소자에 사용하는 전극층(384), 컬러 필터로서 기능하는 착색층(385), 및 편광자(391)(편광판이라고도 한다)가 제공된 대향 기판(395)과, TFT 기판인 지지 기판(310)을 스페이서(387)를 사이에 두고 부착시키고, 그 공극(空隙)에 액정층(382)을 제공한다. 본 실시형태의 반도체장치는 투과형이기 때문에, 지지 기판(310)의 소자를 가지는 면과 반대측에도 편광자(편광판)(393)를 제공한다. 편광자와 착색층의 적층 구조도 도 9에 한정되지 않고, 편광자 및 착색층의 재료나 제조 공정 조건에 따라 적절히 설정하면 좋다. 편광자는 접착층에 의해 기판에 설치될 수 있다. 시일재에는 필러(filler)가 혼입되어 있어도 좋고, 또한, 대향 기판(395)에는, 차폐막(블랙 매트릭스) 등이 형성되어 있어도 좋다. 또한, 컬러 필터 등은, 액정 표시장치를 풀 컬러 표시로 하는 경우, 적색(R), 녹색(G), 청색(B)을 나타내는 재료로 형성하면 좋고, 모노 컬러 표시로 하는 경우, 착색층을 없애거나, 또는 적어도 하나의 색을 나타내는 재료로 형성하면 좋다. 또한, 반도체장치의 시인(視認)측에, 반사 방지 기능을 가지는 반사 방지막을 설치하여도 좋다. 편광판과 액정층과의 사이에 위상차 판을 가진 상태로 적층하여도 좋다.

- <261> 또한, 백라이트에 RGB의 발광 다이오드(LED) 등을 배치하고, 시분할에 의해 컬러 표시하는 계시 가법 혼색법(successive additive color mixture method)(필드 시퀀셜(field sequential)법)을 채용할 때는, 컬러 필터를 설치하지 않는 경우가 있다. 블랙 매트릭스는, 트랜ジ스터나 CMOS 회로의 배선에 의한 외광의 반사를 저감하기 위해, 트랜ジ스터나 CMOS 회로와 겹치도록 형성하면 좋다. 또한, 블랙 매트릭스는 용량 소자와 겹치도록 형성해도 좋다. 용량 소자를 구성하는 금속막에 의한 반사를 방지할 수 있기 때문이다.

- <262> 액정층을 형성하는 방법으로서, 디스펜서식(적하식)이나, 소자를 가지는 지지 기판(310)과 대향 기판(395)을 부착시키고 나서 모세관 현상을 사용하여 액정을 주입하는 주입법을 사용할 수 있다. 적하법은 주입법을 적용하기 어려운 대형 기판을 취급할 때 적용하면 좋다.

- <263> 스페이서는 수  $\mu\text{m}$ 의 입자를 산포하여 형성하는 방법이어도 좋지만, 본 실시형태에서는 기판 전면에 수지막을 형성한 후 이것을 예칭 가공하여 형성하는 방법을 채용한다. 이와 같은 스페이서의 재료를 스피너로 도포한 후, 노광과 현상 처리에 의해 소정의 패턴으로 형성한다. 또한, 클린 오븐 등으로 150~200°C로 가열하여 경화시킨다. 이와 같이 하여 제조되는 스페이서는 노광과 현상 처리의 조건에 따라 형상을 다르게 할 수 있지만, 바람직하게는, 스페이서의 형상은 기둥 형상으로 정상부가 평탄한 형상이 되도록 하면, 대향측의 기판을 맞추었을 때 반도체장치로서의 기계적 강도를 확보할 수 있다. 스페이서의 형상은 원추형, 각추형 등도 사용할 수 있고, 특별한 한정은 없다.

- <264> 이어서, 화소 영역과 전기적으로 접속되어 있는 단자 전극층(378)에 이방성 도전체층(396)을 사이에 두고 접속 용 배선 기판인 FPC(394)를 제공한다. FPC(394)는, 외부로부터의 신호나 전위를 전달하는 역할을 담당한다. 상기 공정을 거쳐, 표시 기능을 가지는 반도체장치를 제작할 수 있다.

- <265> 본 실시형태의 반도체장치에서도, 실시형태 1에서 설명한 바와 같이, 단결정 반도체 기판으로부터 지지 기판에 전재되고, 전영역에서 레이저광 조사에 의한 용융 상태를 거쳐 재단결정화된 단결정 반도체층을 가지는 반도체 기판을 사용하기 때문에, 단결정 반도체층은 결정 결함도 저감되고 결정성이 높고, 또한, 평탄성도 높다.

- <266> 따라서, 고성능 및 고신뢰성의 반도체장치를 수율 좋게 제작할 수 있다.

- <267> 본 실시형태는 실시형태 1 내지 4와 적절히 조합할 수 있다.

- <268> [실시형태 6]

- <269> 본 발명을 적용하여 발광소자를 가지는 반도체장치를 형성할 수 있는데, 이 발광소자로부터 발해지는 광은 하면 방사, 상면 방사, 양면 방사 중 어느 하나를 행한다. 본 실시형태에서는, 하면 방사형, 양면 방사형, 상면 방사형의 고성능 및 고신뢰성이 부여된 반도체장치로서 표시 기능을 가지는 반도체장치(표시장치 또는 발광장치라고도 한다)를 수율 좋게 생산하는 것을 목적으로 한 반도체장치 제조방법의 예를 도 10(A) 및 도 10(B)와 도 11(A) 및 도 11(B)를 사용하여 설명한다.

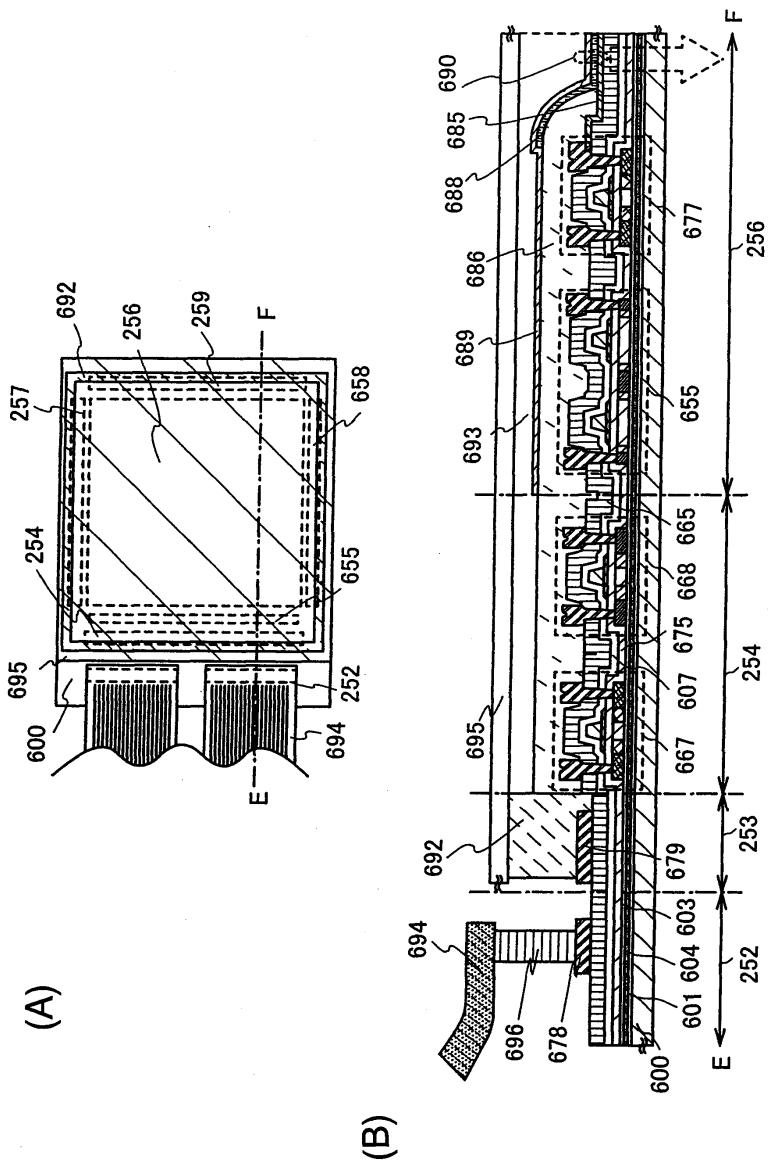

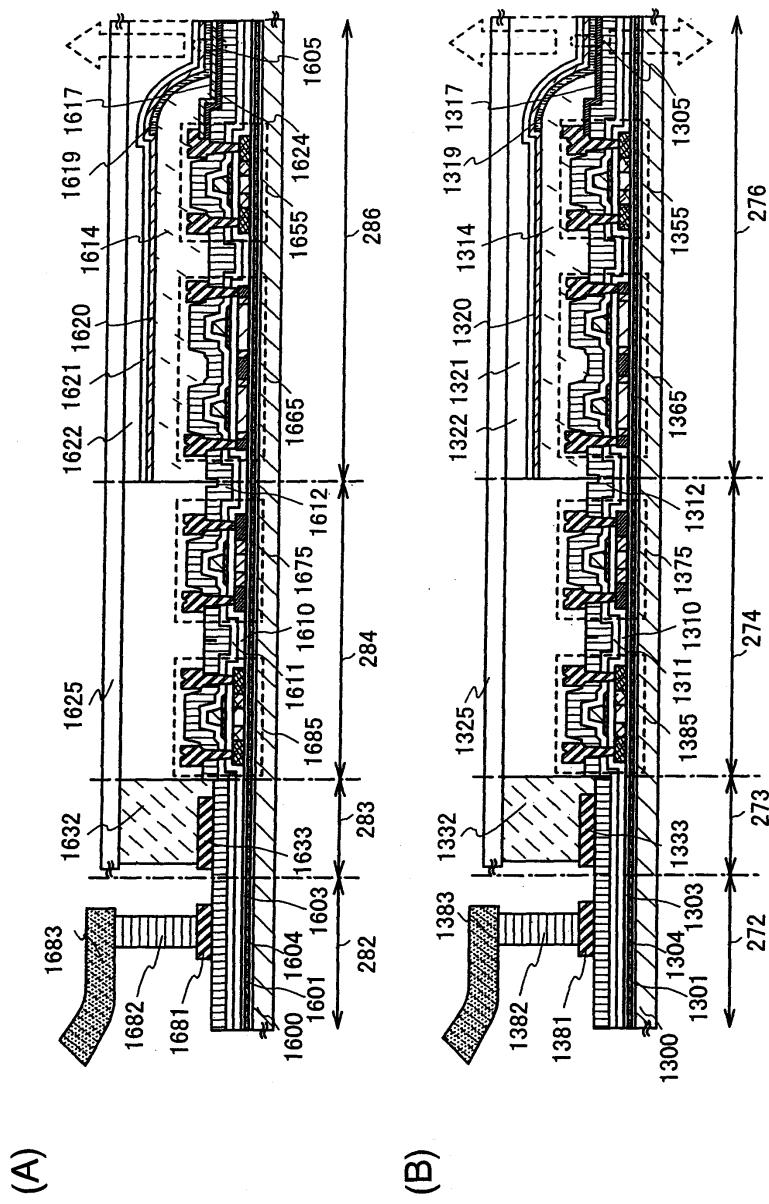

- <270> 도 10의 반도체장치는, 화살표 방향으로 하면 사출하는 구조이다. 도 10에서, 도 10(A)는 반도체장치의 평면도이고, 도 10(B)는 도 10(A)의 선 E-F에서의 단면도이다. 도 10에서, 반도체장치는 외부 단자 접속 영역(252), 봉지 영역(253), 구동회로 영역(254), 및 화소 영역(256)을 가지고 있다.

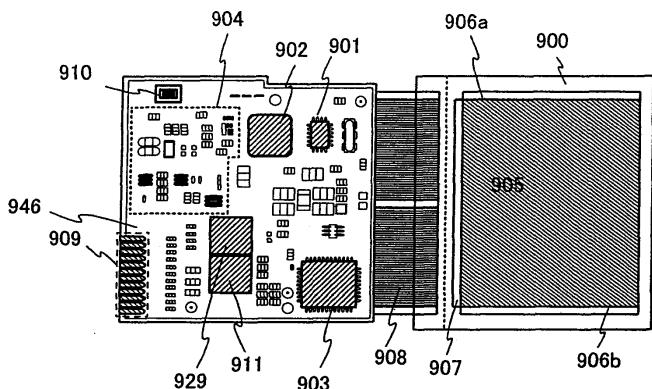

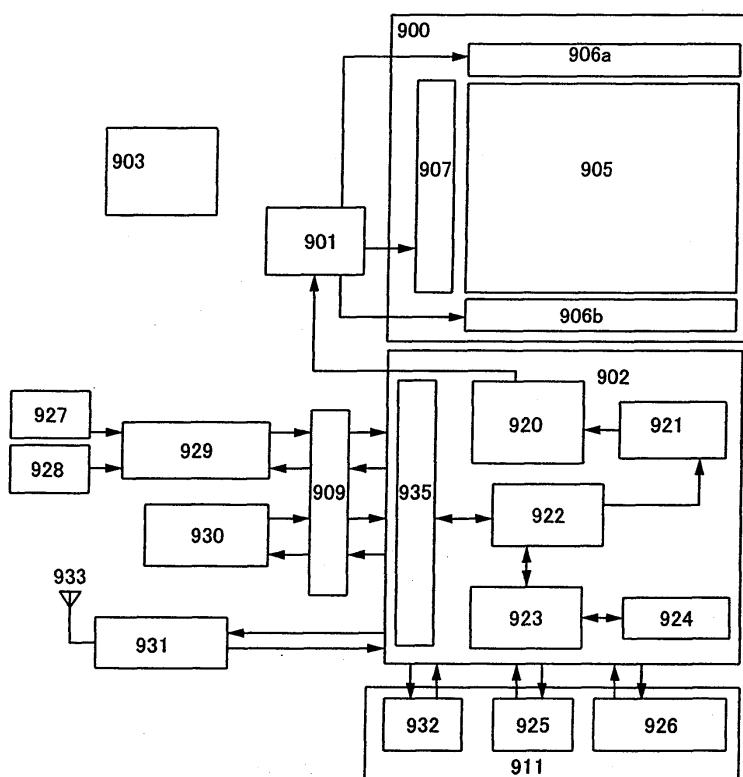

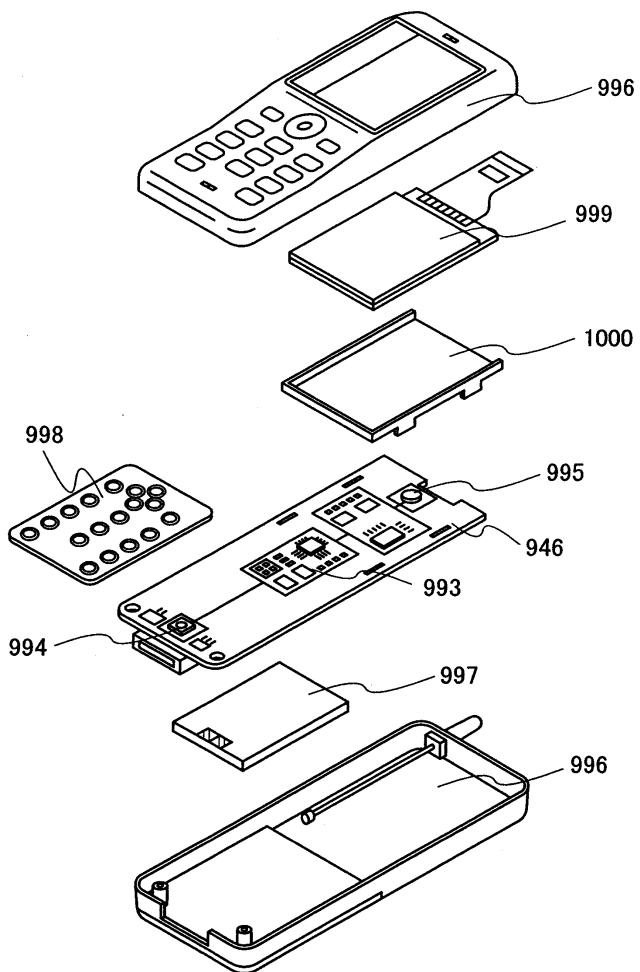

- <271> 도 10에 나타내는 반도체장치는, 소자 기판(600), 박막트랜지스터(655), 박막트랜지스터(677), 박막트랜지스터(667), 박막트랜지스터(668), 제1 전극층(685)과 발광층(688)과 제2 전극층(689)을 포함하는 발광소자(690), 충전재(693), 시일재(692), 블로킹층(601), 절연층(604), 산화막(603), 게이트 절연층(675), 절연막(607), 절연막(665), 절연층(686), 봉지 기판(695), 배선층(679), 단자 전극층(678), 이방성 도전층(696), FPC(694)에 의해 구성되어 있다. 반도체장치는, 외부 단자 접속 영역(252), 봉지 영역(253), 구동회로 영역(254), 화소 영역(256)을 가지고 있다. 충전재(693)는 액상의 조성물의 상태로 적하법에 의해 형성할 수 있다. 적하법에 의해 충전재가 형성된 소자 기판(600)과 봉지 기판(695)을 접합시켜 반도체장치(발광 표시장치)를 봉지한다.

- <272> 도 10의 반도체장치에서, 제1 전극층(685)은, 발광소자(690)로부터 사출하는 광을 투과할 수 있도록, 투광성을 가지는 도전성 재료를 사용하고, 한편 제2 전극층(689)은 발광소자(690)로부터 사출하는 광을 반사하는, 반사성을 가지는 도전성 재료를 사용하여 형성한다.

- <273> 제2 전극층(689)으로서는, 반사성을 가지면 좋기 때문에, 티탄, 텉스텐, 니켈, 금, 백금, 은, 구리, 탄탈, 몰리브덴, 알루미늄, 마그네슘, 칼슘, 리튬, 및 그들의 합금으로 이루어지는 도전막 등을 사용하면 좋다. 바람직하게는, 가시광의 영역에서 반사성이 높은 물질을 사용하는 것이 좋고, 본 실시형태에서는, 알루미늄막을 사용한다.

- <274> 제1 전극층(685)에, 구체적으로는, 투광성을 가지는 도전성 재료로 이루어지는 투명 도전막을 사용하면 좋고, 산화텅스텐을 함유하는 인듐 산화물, 산화텅스텐을 함유하는 인듐 아연 산화물, 산화티탄을 함유하는 인듐 산화물, 산화티탄을 함유하는 인듐 주석 산화물 등을 사용할 수 있다. 물론, 인듐 주석 산화물(ITO), 인듐 아연 산화물(IZO), 산화규소를 첨가한 인듐 주석 산화물(ITSO) 등도 사용할 수 있다.

- <275> 도 11(A)의 반도체장치는, 화살표 방향으로 상면 사출하는 구조이다. 도 11(A)에 나타내는 반도체장치는, 소자 기판(1600), 박막트랜지스터(1655), 박막트랜지스터(1665), 박막트랜지스터(1675), 박막트랜지스터(1685), 배선층(1624), 제1 전극층(1617), 발광층(1619), 제2 전극층(1620), 충전재(1622), 시일재(1632), 블로킹층(1601), 절연층(1604), 산화막(1603), 게이트 절연층(1610), 절연막(1611), 절연막(1612), 절연층(1614), 봉지 기판(1625), 배선층(1633), 단자 전극층(1681), 이방성 도전층(1682), FPC(1683)에 의해 구성되어 있다.

- <276> 도 11(A)에서, 반도체장치는, 외부 단자 접속 영역(282), 봉지 영역(283), 구동회로 영역(284), 화소 영역(286)을 가지고 있다. 도 11(A)의 반도체장치는, 제1 전극층(1617) 아래에, 반사성을 가지는 금속층인 배선층(1624)을 형성하고, 배선층(1624) 위에 투명 도전막인 제1 전극층(1617)을 형성한다. 배선층(1624)으로서는, 반사성을 가지면 좋기 때문에, 티탄, 텉스텐, 니켈, 금, 백금, 은, 구리, 탄탈, 몰리브덴, 알루미늄, 마그네슘, 칼슘, 리튬, 및 그들의 합금으로 이루어지는 도전막 등을 사용하면 좋다. 바람직하게는, 가시광의 영역에서 반사성이 높은 물질을 사용하는 것이 좋다. 또한, 제1 전극층(1617)에도 도전막을 사용해도 좋고, 그 경우, 반사성을 가지는 배선층(1624)은 형성하지 않아도 좋다.

- <277> 제1 전극층(1617) 및 제2 전극층(1620)에, 구체적으로는, 투광성을 가지는 도전성 재료로 이루어지는 투명 도전막을 사용하면 좋고, 산화텅스텐을 함유하는 인듐 산화물, 산화텅스텐을 함유하는 인듐 아연 산화물, 산화티탄을 함유하는 인듐 산화물, 산화티탄을 함유하는 인듐 주석 산화물 등을 사용할 수 있다. 물론, 인듐 주석 산화물(ITO), 인듐 아연 산화물(IZO), 산화규소를 첨가한 인듐 주석 산화물(ITSO) 등도 사용할 수 있다.

- <278> 또한, 투광성을 가지지 않는 금속막과 같은 재료이어도, 막 두께를 얇게(바람직하게는, 5 nm~30 nm 정도의 두께) 하여 광을 투과 가능한 상태로 해 둠으로써, 제1 전극층(1617) 및 제2 전극층(1620)으로부터 광을 방사하는 것이 가능하게 된다. 또한, 제1 전극층(1617) 및 제2 전극층(1620)에 사용할 수 있는 금속 박막으로서는, 티탄, 텉스텐, 니켈, 금, 백금, 은, 알루미늄, 마그네슘, 칼슘, 리튬, 및 그들의 합금으로 이루어지는 도전막 등을 사용할 수 있다.

- <279> 도 11(B)에 나타내는 반도체장치는, 소자 기판(1300), 박막트랜지스터(1355), 박막트랜지스터(1365), 박막트랜지스터(1375), 박막트랜지스터(1385), 제1 전극층(1317), 발광층(1319), 제2 전극층(1320), 충전재(1322), 시일재(1332), 블로킹층(1301), 절연층(1304), 산화막(1303), 게이트 절연층(1310), 절연막(1311), 절연막(1312), 절연층(1314), 봉지 기판(1325), 배선층(1333), 단자 전극층(1381), 이방성 도전층(1382), FPC(1383)에 의해 구성되어 있다. 이 반도체장치는, 외부 단자 접속 영역(272), 봉지 영역(273), 구동회로 영역(274), 화소 영역(276)을 가지고 있다.

- <280> 도 11(B)의 반도체장치는 양면 방사형이고, 화살표 방향으로 소자 기판(1300)측으로부터도, 봉지 기판(1325)측으로부터도 광을 방사하는 구조이다. 따라서, 제1 전극층(1317) 및 제2 전극층(1320)으로서 투광성 전극층을 사용한다.

- <281> 본 실시형태에서는, 투광성 전극층인 제1 전극층(1317) 및 제2 전극층(1320)에, 구체적으로는, 투광성을 가지는 도전성 재료 이루어지는 투명 도전막을 사용하면 좋고, 산화텅스텐을 함유하는 인듐 산화물, 산화텅스텐을 함유하는 인듐 아연 산화물, 산화티탄을 함유하는 인듐 산화물, 산화티탄을 함유하는 인듐 주석 산화물 등을 사용할 수 있다. 물론, 인듐 주석 산화물(ITO), 인듐 아연 산화물(IZO), 산화규소를 첨가한 인듐 주석 산화물(ITSO) 등도 사용할 수 있다.

- <282> 또한, 투광성을 가지지 않는 금속막과 같은 재료이어도, 막 두께를 얇게(바람직하게는, 5 nm~30 nm 정도의 두께) 하여 광을 투과 가능한 상태로 해둠으로써, 제1 전극층(1317) 및 제2 전극층(1320)으로부터 광을 방사하는 것이 가능하게 된다. 또한, 제1 전극층(1317) 및 제2 전극층(1320)에 사용할 수 있는 금속 박막으로서는, 티탄, 텅스텐, 니켈, 금, 백금, 은, 알루미늄, 마그네슘, 칼슘, 리튬, 및 그들의 합금으로 이루어지는 도전막 등을 사용할 수 있다.

- <283> 이상과 같이, 도 11(B)의 반도체장치는, 발광소자(1305)로부터 방사되는 광이 제1 전극층(1317) 및 제2 전극층(1320) 모두를 통과하여, 양면으로부터 광을 방사하는 구성이 된다.

- <284> 발광소자를 사용하여 형성하는 반도체장치의 화소는 단순 매트릭스 방식 또는 액티브 매트릭스 방식으로 구동할 수 있다. 또한, 디지털 구동과 아날로그 구동 중 어느 것이라도 적용할 수 있다.

- <285> 봉지 기판에 컬러 필터(착색층)를 형성해도 좋다. 컬러 필터(착색층)는 증착법이나 액적 토출법에 의해 형성할 수 있고, 컬러 필터(착색층)를 사용하면, 고정세한 표시를 행할 수도 있다. 컬러 필터(착색층)에 의해, 각 RGB의 발광 스펙트럼에서 넓은 피크가 예리한 피크가 되도록 보정할 수 있기 때문이다.

- <286> 단색 발광을 나타내는 재료를 형성하고, 컬러 필터나 색 변환층을 조합함으로써 풀 컬러 표시를 행할 수 있다. 컬러 필터(착색층)나 색 변환층은, 예를 들어, 봉지 기판에 형성하고, 소자 기판에 부착시키면 좋다.

- <287> 물론, 단색 발광의 표시를 행하여도 좋다. 예를 들어, 단색 발광을 사용하여 에리어(area) 컬러 타입의 반도체장치를 형성하여도 좋다. 에리어 컬러 타입은, 패시브 매트릭스형의 표시부가 적합하고, 주로 문자나 기호를 표시할 수 있다.

- <288> 단결정 반도체층을 사용함으로써, 화소 영역과 구동회로 영역을 동일 기판 위에 일체로 형성할 수 있다. 그 경우, 화소 영역의 트랜지스터와 구동회로 영역의 트랜지스터는 동시에 형성된다.

- <289> 본 실시형태에서도, 도 10 및 도 11(A), 도 11(B)에 나타내는 본 실시형태의 반도체장치에 설치되는 트랜지스터는, 실시형태 2에서 나타낸 트랜지스터와 마찬가지로 제작할 수 있다.

- <290> 본 실시형태의 반도체장치에서도, 실시형태 1에서 나타낸 바와 같이, 단결정 반도체 기판으로부터 지지 기판에 전재되고, 전영역에서 레이저광 조사에 의한 용융 상태를 거쳐 재단결정화된 단결정 반도체층을 가지는 반도체 기판을 사용하기 때문에, 단결정 반도체층은 결정 결함도 저감되고 결정성이 높고, 또한, 평탄성도 높다.

- <291> 따라서, 고성능 및 고신뢰성의 반도체장치를 수율 좋게 제작할 수 있다.

- <292> 본 실시형태는 상기의 실시형태 1 내지 4와 적절히 조합할 수 있다.

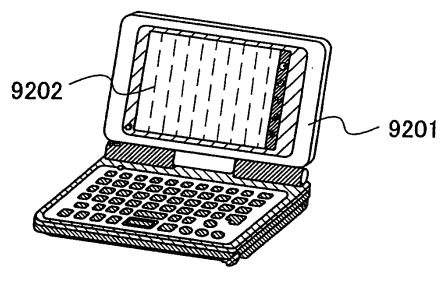

- <293> [실시형태 7]

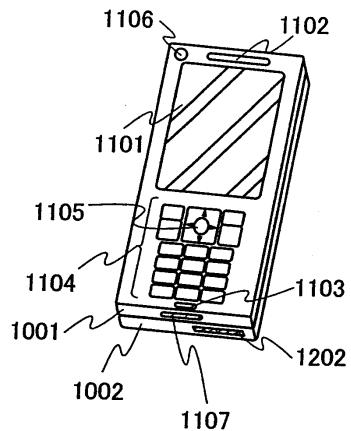

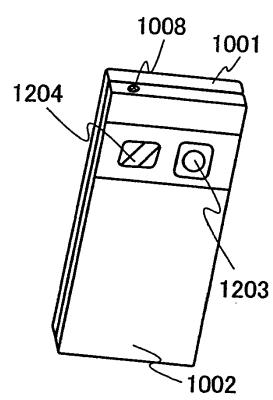

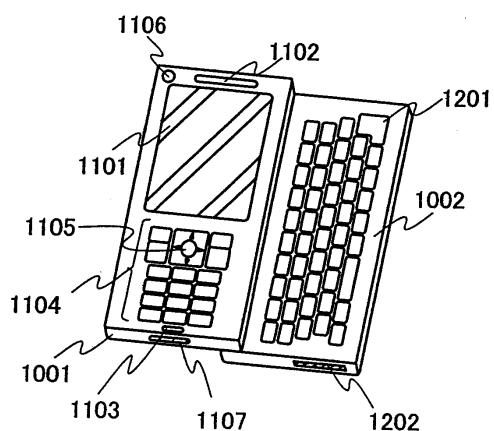

- <294> 본 실시형태에서는, 고성능 및 고신뢰성이 부여된 반도체장치로서 표시 기능을 가지는 반도체장치(표시장치 또는 발광장치라고도 한다)의 예에 대하여 설명한다. 상세하게는, 표시 소자에 발광소자를 사용하는 발광 표시장치에 대하여 설명한다.

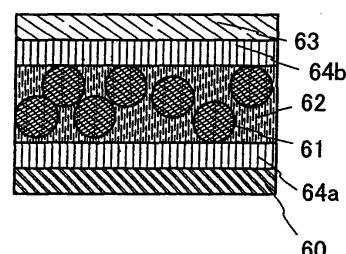

- <295> 본 실시형태에서는, 본 발명의 표시장치의 표시 소자로서 적용할 수 있는 발광소자의 구성을 도 13을 사용하여 설명한다.

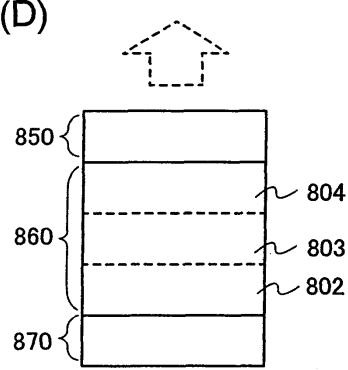

- <296> 도 13은 발광소자의 소자 구조이고, 제1 전극층(870)과 제2 전극층(850)과의 사이에 EL 층(860)이 끼워져 있는 발광소자이다. EL 층(860)은, 도시한 바와 같이, 제1 층(804), 제2 층(803), 제3 층(802)으로 구성되어 있다. 도 13에서, 제2 층(803)은 발광층이고, 제1 층(804) 및 제3 층(802)은 기능층이다.

- <297> 제1 층(804)은 제2 층(803)에 정공(홀)을 수송하는 기능을 담당하는 층이다. 도 13에서는, 제1 층(804)에 포함되는 정공 주입층은 정공 주입성이 높은 물질을 포함하는 층이다. 몰리브덴 산화물이나 바나듐 산화물, 루테늄 산화물, 텉스텐 산화물, 망간 산화물 등을 사용할 수 있다. 이 외에, 프탈로시아닌(약칭: H<sub>2</sub>Pc)이나 구리 프탈로시아닌(CuPC) 등의 프탈로시아닌계 화합물, 4,4'-비스[N-(4-디페닐아미노페닐)-N-페닐아미노]비페닐(약칭: DPAB), 4,4'-비스(N-[4-[N-(3-메틸페닐)-N-페닐아미노]페닐]-N-페닐아미노)비페닐(약칭: DNTPD) 등의 방향족 아민 화합물, 또는 폴리(에틸렌디옥시티오펜)/폴리(스티렌슬픈산)(약칭: PEDOT/PSS) 등의 고분자 등에 의해서도 제1 층(804)을 형성할 수 있다.

- <298> 또한, 정공 주입층으로서, 유기 화합물과 무기 화합물을 복합하여 이루어지는 복합 재료를 사용할 수 있다. 특히, 유기 화합물과, 유기 화합물에 대하여 전자 수용성을 나타내는 무기 화합물을 포함하는 복합 재료는, 유기 화합물과 무기 화합물과의 사이에서 전자를 수수(授受)하고 캐리어 밀도가 증대하기 때문에, 정공 주입성, 정공 수송성이 뛰어나다.

- <299> 또한, 정공 주입층으로서, 유기 화합물과 무기 화합물을 복합하여 이루어지는 복합 재료를 사용한 경우, 전극층과 음 접촉(ohmic contact)을 하는 것이 가능하게 되기 때문에, 일 함수에 상관없이 전극층을 형성하는 재료를 선택할 수 있다.

- <300> 복합 재료에 사용하는 무기 화합물로서는, 천이 금속의 산화물인 것이 바람직하다. 또한, 원소 주기율표의 제4족 내지 제8족에 속하는 금속의 산화물을 들 수 있다. 구체적으로는, 산화바나듐, 산화니오브, 산화탄탈, 산화크롬, 산화몰리브덴, 산화텅스텐, 산화망간, 산화레늄은 전자 수용성이 높기 때문에 바람직하다. 그 중에서도 특히, 산화몰리브덴은 대기 중에서 안정하고, 흡습성이 낮고, 취급하기 쉽기 때문에 바람직하다.

- <301> 복합 재료에 사용하는 유기 화합물로서는, 방향족 아민 화합물, 카르바졸 유도체, 방향족 탄화수소, 고분자 화합물(올리고머, 텐드리머, 폴리머 등) 등, 다양한 화합물을 사용할 수 있다. 또한, 복합 재료에 사용하는 유기 화합물로서는, 정공 수송성이 높은 유기 화합물인 것이 바람직하다. 구체적으로는,  $10^{-6} \text{ cm}^2/\text{Vs}$  이상의 정공 이동도를 가지는 물질인 것이 바람직하다. 단, 전자 수송성보다 정공 수송성이 높은 물질이라면, 이것들 이외의 것을 사용해도 좋다. 이하에서는, 복합 재료에 사용할 수 있는 유기 화합물을 구체적으로 열거한다.

- <302> 예를 들어, 방향족 아민 화합물로서는, N,N'-디(p-톨릴)-N,N'-디페닐-p-페닐렌디아민(약칭: DTDPPA), 4,4'-비스[N-(4-디페닐아미노페닐)-N-페닐아미노]비페닐(약칭: DPAB), 4,4'-비스(N-[4-[N-(3-메틸페닐)-N-페닐아미노]페닐]-N-페닐아미노)비페닐(약칭: DNTPD), 1,3,5-트리스[N-(4-디페닐아미노페닐)-N-페닐아미노]벤젠(약칭: DPA3B) 등을 들 수 있다.

- <303> 복합 재료에 사용할 수 있는 카르바졸 유도체로서는, 구체적으로는, 3-[N-(9-페닐카르바졸-3-일)-N-페닐아미노]-9-페닐카르바졸(약칭: PCzPCA1), 3,6-비스[N-(9-페닐카르바졸-3-일)-N-페닐아미노]-9-페닐카르바졸(약칭: PCzPCA2), 3-[N-(1-나프틸)-N-(9-페닐카르바졸-3-일)아미노]-9-페닐카르바졸(약칭: PCzPCN1) 등을 들 수 있다.

- <304> 또한, 4,4'-디(N-카르바졸릴)비페닐(약칭: CBP), 1,3,5-트리스[4-(N-카르바졸릴)페닐]벤젠(약칭: TCPB), 9-[4-(N-카르바졸릴)]페닐-10-페닐안트라센(약칭: CzPA), 1,4-비스[4-(N-카르바졸릴)페닐]-2,3,5,6-테트라페닐벤젠 등을 사용할 수 있다.