(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6372019号

(P6372019)

(45) 発行日 平成30年8月15日(2018.8.15)

(24) 登録日 平成30年7月27日(2018.7.27)

(51) Int.Cl.

H02J 7/02 (2016.01)

H01M 10/48 (2006.01)

F 1

H02J 7/02

H01M 10/48H

P

請求項の数 5 (全 51 頁)

(21) 出願番号 特願2014-10374 (P2014-10374)

(22) 出願日 平成26年1月23日 (2014.1.23)

(65) 公開番号 特開2014-150712 (P2014-150712A)

(43) 公開日 平成26年8月21日 (2014.8.21)

審査請求日 平成29年1月13日 (2017.1.13)

(31) 優先権主張番号 13/753,832

(32) 優先日 平成25年1月30日 (2013.1.30)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 300057230

セミコンダクター・コンポーネンツ・イン

ダストリーズ・リミテッド・ライアビリテ

ィ・カンパニー

アメリカ合衆国 アリゾナ州 85008

フェニックス イースト・マクドウェル

・ロード5005

(74) 代理人 100110799

弁理士 丸山 温道

(74) 代理人 100091915

弁理士 本城 雅則

(74) 代理人 100099106

弁理士 本城 吉子

最終頁に続く

(54) 【発明の名称】モニタおよび制御モジュールならびに方法

(57) 【特許請求の範囲】

【請求項 1】

モニタ及び制御回路において、

第1入力端子、第1共通入力端子、第1出力端子、第2出力端子、及び第1共通出力端子を有する第1フィルタ回路であって、前記第1フィルタ回路の前記第1入力端子は、第1バッテリセルの正極に接続され、かつ第1共通入力端子は、前記第1バッテリセルの負極に接続するとともに第2バッテリセルの正極に接続するため構成され、さらに、

第1及び第2端子を有する第1インピーダンス素子であって、前記第1インピーダンス素子の前記第1端子は、前記第1フィルタ回路の前記第1入力端子として動作し、かつ前記第1インピーダンス素子の前記第2端子は、前記第1フィルタ回路の前記第1出力端子として動作する、第1インピーダンス素子、

第1及び第2端子を有する第1共通インピーダンス素子であって、前記第1共通インピーダンス素子の前記第1端子は、前記第1フィルタ回路の前記第1共通入力端子として動作し、かつ前記第1共通インピーダンス素子の前記第2端子は、前記第1フィルタ回路の前記第1共通出力端子として動作する、第1共通インピーダンス素子、及び、

第1端子及び第2端子を有する第1キャパシタであって、前記第1キャパシタの前記第1端子は、前記第1フィルタ回路の前記第2出力端子に結合される第1キャパシタ、

を含む第1フィルタ回路と、

第1共通入力端子、第2共通入力端子、第1出力端子、第1共通出力端子、及び第2共通出力端子を有する第2フィルタ回路であって、前記第2共通入力端子は、前記第2バッ

10

20

テリセルの負極に接続するために構成され、さらに、

前記第1共通インピーダンス素子、

第1及び第2端子を有する第2共通インピーダンス素子であって、前記第2共通インピーダンス素子の前記第1端子は、前記第2フィルタ回路の前記第2共通入力端子として動作し、かつ前記第2共通インピーダンス素子の前記第2端子は、前記第2フィルタ回路の前記第2共通出力端子として動作する、第2共通インピーダンス素子、及び、

第1端子及び第2端子を有する第2キャパシタであって、前記第2キャパシタの第1端子は、前記第2フィルタ回路の前記第1出力端子に結合され、前記第2端子は前記第1共通インピーダンス素子の前記第2端子、または前記第1キャパシタの前記第1端子のいずれかに結合される、第2キャパシタ、

を含む第2フィルタ回路と、

第1、第2及び第3入力端子、並びに、第1及び第2スイッチング入力端子を有するスイッチングネットワークにおいて、前記スイッチングネットワークの前記第1入力端子は、前記第1フィルタ回路の前記第1出力端子に結合され、前記スイッチングネットワークの前記第2入力端子は、前記第1フィルタ回路の前記第1共通出力端子に結合され、前記第1スイッチング入力端子は、前記第1フィルタ回路の前記第2出力端子に結合され、前記第3入力端子は、前記第2フィルタ回路の前記第2共通出力端子に結合され、前記第2スイッチング入力端子は、前記第2フィルタ回路の前記第1出力端子に結合され、

さらに、

制御端子、第1電流供給端子、及び第2電流供給端子を有する第1スイッチング素子であって、前記第1スイッチング素子の前記第1電流供給端子は、前記第1フィルタ回路の前記第1共通出力端子に結合され、前記第1スイッチング素子の前記第2電流供給端子は、前記第1フィルタ回路の前記第2出力端子に結合される、第1スイッチング素子、及び、

制御端子、第1電流供給端子、及び第2電流供給端子を有する第2スイッチング素子であって、前記第2スイッチング素子の前記第1電流供給端子は、前記第2フィルタ回路の前記第2共通出力端子に結合され、前記第2スイッチング素子の前記第2電流供給端子は、前記第2フィルタ回路の前記第1出力端子に結合される、第2スイッチング素子、

を含むスイッチングネットワークと、

から構成されることを特徴とするモニタ及び制御回路。

## 【請求項2】

第1バッテリセルの正極に接続するために構成される第1端子、前記第1バッテリセルの負極に接続するために構成され、かつ第2バッテリセルの正極に接続するために構成される第2端子、及び、前記第2バッテリセルの負極に接続するために構成される第3端子を有するモニタ及び制御回路において、

第1共通端子、第2共通端子、第3共通端子、第1スイッチングネットワーク入力端子、及び、第2スイッチングネットワーク入力端子を有するスイッチングネットワークであって、

制御端子、及び、第1及び第2電流供給端子を有する第1サンプリングスイッチであって、前記第1サンプリングスイッチの前記第1電流供給端子は、前記スイッチングネットワークの前記第2共通端子に結合され、前記第1サンプリングスイッチの前記第2電流供給端子は、前記スイッチングネットワークの前記第1スイッチングネットワーク入力端子に結合される、第1サンプリングスイッチ、及び

制御端子、及び、第1及び第2電流供給端子を有する第2サンプリングスイッチであって、前記第2サンプリングスイッチの前記第1電流供給端子は、前記スイッチングネットワークの前記第3共通端子に結合され、前記第2サンプリングスイッチの前記第2電流供給端子は、前記スイッチングネットワークの前記第2スイッチングネットワーク入力端子に結合される、第2サンプリングスイッチ、を含むスイッチングネットワークと、

第1端子及び第2端子を有する第1インピーダンス素子であって、前記第1インピーダンス素子の前記第1端子は、前記モニタ及び制御回路の前記第1端子に結合され、前記

10

20

30

40

50

第1インピーダンス素子の前記第2端子は、前記スイッチングネットワークの前記第1共通端子に結合される、第1インピーダンス素子と、

第1端子及び第2端子を有する第1エネルギー貯蔵素子であって、前記第1エネルギー貯蔵素子の前記第1端子は、前記スイッチングネットワークの前記第1スイッチングネットワーク入力端子に結合される、第1エネルギー貯蔵素子と、

第1端子及び第2端子を有する第2インピーダンス素子であって、前記第2インピーダンス素子の前記第1端子は、前記モニタ及び制御回路の前記第2端子に結合され、前記第2インピーダンス素子の前記第2端子は、前記スイッチングネットワークの前記第2共通端子に結合される、第2インピーダンス素子と、

第1端子及び第2端子を有する第2エネルギー貯蔵素子であって、前記第2エネルギー貯蔵素子の前記第1端子は、前記スイッチングネットワークの前記第2スイッチングネットワーク入力端子に結合され、前記第2エネルギー貯蔵素子の前記第2端子は、前記第2インピーダンス素子の前記第2端子、もしくは前記第1エネルギー貯蔵素子の前記第1端子のいずれかに結合される、第2エネルギー貯蔵素子と、

第1端子及び第2端子を有する第3インピーダンス素子であって、前記第3インピーダンス素子の前記第1端子は、前記モニタ及び制御回路の前記第3端子に結合される、第3インピーダンス素子と、

から構成されることを特徴とするモニタ及び制御回路。

【請求項3】

第1及び第2端子を有する第4インピーダンス素子であって、前記第4インピーダンス素子の前記第1端子は、前記第1サンプリングスイッチの前記第2電流供給端子に結合され、前記第4インピーダンス素子の前記第2端子は、前記スイッチングネットワークの前記第1スイッチングネットワーク入力端子に結合される、第4インピーダンス素子と、

第1及び第2端子を有する第5インピーダンス素子であって、前記第5インピーダンス素子の前記第1端子は、前記第2サンプリングスイッチの前記第2電流供給端子に結合され、前記第5インピーダンス素子の前記第2端子は、前記スイッチングネットワークの前記第2スイッチングネットワーク入力端子に結合される、第5インピーダンス素子と、

から構成されることを特徴とする請求項2記載のモニタ及び制御回路。

【請求項4】

回路において、

第1バッテリセルの正極に接続するために構成される第1端子、前記第1バッテリセルの負極に接続するために構成され、かつ第2バッテリセルの正極に接続するために構成される第2端子、及び、前記第2バッテリセルの負極に接続するために構成される第3端子を有するフィルタ回路であって、前記フィルタ回路は、さらに第1共通出力端子、第2共通出力端子、第3共通出力端子、第1フィルタ出力端子、及び第2フィルタ出力端子を含み、

第1端子及び第2端子を有する第1インピーダンス素子であって、前記第1インピーダンス素子の前記第1端子は、前記フィルタ回路の前記第1端子として動作し、前記第2端子は前記第1共通出力端子に結合される第1インピーダンス素子、

第1端子及び第2端子を有する第2インピーダンス素子であって、前記第2インピーダンス素子の前記第1端子は、前記フィルタ回路の前記第2端子として動作し、前記第2インピーダンス素子の第2端子は前記第2共通出力端子に結合される第2インピーダンス素子、

第1端子及び第2端子を有する第3インピーダンス素子であって、前記第3インピーダンス素子の前記第1端子は、前記フィルタ回路の前記第3端子として動作し、前記第3インピーダンス素子の第2端子は前記第3共通出力端子に結合される第3インピーダンス素子、

第1端子及び第2端子を有する第1エネルギー貯蔵素子であって、前記第1エネルギー貯蔵素子の前記第1端子は、前記第1フィルタ出力端子に結合され、前記第2端子は前記第1共通出力端子に結合される第1エネルギー貯蔵素子、及び

10

20

30

40

50

第1端子及び第2端子を有する第2エネルギー貯蔵素子であって、前記第2エネルギー貯蔵素子の前記第1端子は、前記第2フィルタ出力端子に結合され、前記第2端子は前記第2共通出力端子に結合される第2エネルギー貯蔵素子を含むフィルタ回路と、

前記フィルタ回路の前記第1共通出力端子に結合される第1共通入力端子、前記フィルタ回路の前記第2共通出力端子に結合される第2共通入力端子、前記フィルタ回路の前記第3共通出力端子に結合される第3共通入力端子、前記第1フィルタ出力端子に結合される第1スイッチングネットワーク入力端子、及び前記第2フィルタ出力端子に結合される第2スイッチングネットワーク入力端子を有するスイッチングネットワークであって、前記スイッチングネットワークは、さらに制御端子、及び、第1及び第2電流供給端子を有する第1スイッチを備え、前記第1スイッチの前記第1端子は、前記スイッチングネットワークの前記第2共通入力端子に結合され、前記第1スイッチの前記第2端子は、前記スイッチングネットワークの前記第1スイッチングネットワーク入力端子に結合される、スイッチングネットワークと、

から構成されることを特徴とする回路。

【請求項5】

第1端子及び第2端子を有する第4インピーダンス素子であって、前記第4インピーダンス素子の前記第1端子は、前記第1スイッチの前記第2端子に直接結合され、前記第4インピーダンス素子の前記第2端子は、前記スイッチングネットワークの前記第1スイッチングネットワーク入力端子に直接結合される、第4インピーダンス素子と、

制御端子、及び、第1及び第2端子を有する第2スイッチであって、前記第2スイッチの前記第1端子は、前記スイッチングネットワークの前記第3共通入力端子に結合され、前記第2スイッチの前記第2端子は、前記スイッチングネットワークの前記第2スイッチングネットワーク入力端子に結合される、第2スイッチと、

第1端子及び第2端子を有する第5インピーダンス素子であって、前記第5インピーダンス素子の前記第1端子は、前記第2スイッチの前記第2端子に直接結合され、前記第5インピーダンス素子の前記第2端子は、前記スイッチングネットワークの前記第2スイッチングネットワーク入力端子に直接結合される、第5インピーダンス素子と、

から構成されることを特徴とする請求項4記載の回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般に、電子工学に関し、より詳細には、半導体デバイスおよび構造を形成する方法に関する。

【背景技術】

【0002】

電力貯蔵装置は、自動車、航空宇宙産業、航空会社、船舶、コンピュータ、通信、重機、遠隔感知等を含む多くの適用において用いられている。電力貯蔵装置は、電気負荷を駆動するために特定の定格電圧を提供する電源装置やバッテリとして機能し得る。電力貯蔵装置は、並列または直列に結合されるいくつかの個別のバッテリセルから成り得る。バッテリの寿命は、バッテリが充電および放電される方法に非常に依存し、セルを過充電したり過放電したりすることによって短くなる。加えて、バッテリスタックの全てのセルを同一のキャパシティで保持することが望ましい。これは、全てのセルをほぼ同一の開回路電圧で保持することに相当する。バッテリの使用および1つのセルの過放電が、そのセルとバッテリの寿命に影響を与える。バッテリ製造業者は、バッテリセルにわたる電圧を測定するためにより良好かつより正確な測定技術を見出すことを常に目指している。測定技術の改善とともに、バッテリ製造業者は、バッテリスタック内でセル電圧を平衡化させる方法を模索している。

【発明の概要】

【発明が解決しようとする課題】

【0003】

10

20

30

40

50

したがって、バッテリスタックの電圧およびバッテリスタック内のセルの電圧を監視して平衡化させるための回路および方法を有することが有益であろう。コスト効率の高い回路および方法がさらに有利であろう。

【課題を解決するための手段】

【0004】

同様の参照記号が同様の要素を指定する添付の図面と併用される以下の発明を実施するための形態を読むことで、本発明はより良く理解されるであろう。

【図面の簡単な説明】

【0005】

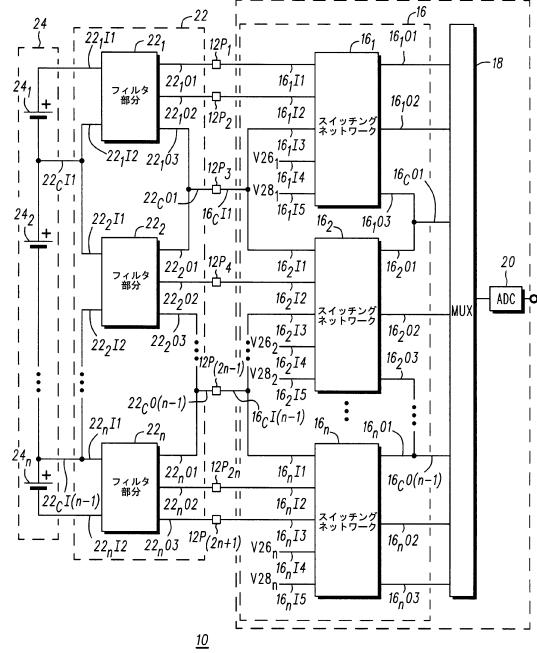

【図1】本発明のある実施形態に係る、バッテリ監視および平衡化システムの一部のプロック図である。 10

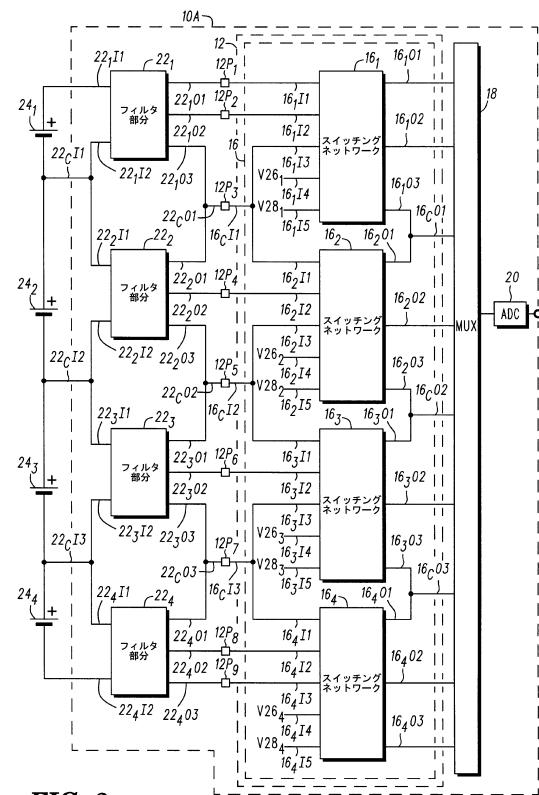

【図2】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部のプロック図である。

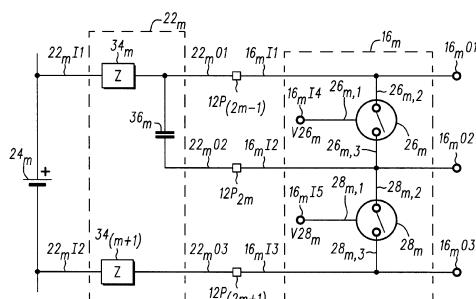

【図3】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

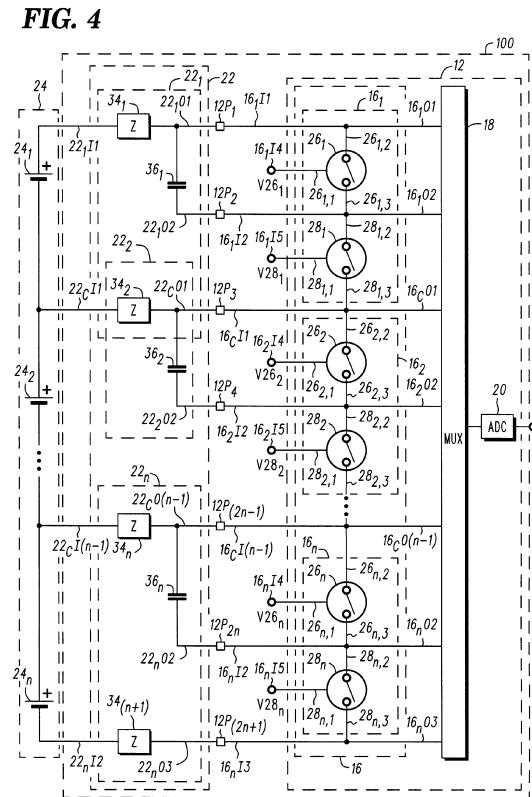

【図4】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【図5】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【図6】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。 20

【図7】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【図8】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【図9】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【図10】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【図11】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。 30

【図12】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【図13】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【図14】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【図15】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【図16】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。 40

【図17】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【図18】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【図19】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【図20】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【図21】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模 50

式図である。

【図22】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【図23】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【図24】本発明の別の実施形態に係る、バッテリ監視および平衡化システムの一部の模式図である。

【0006】

説明の簡潔化および明確化のために、図面中の要素は必ずしも原寸に比例しておらず、異なる図面中の同一の参照記号は、同じ要素を示す。加えて、周知のステップおよび要素の説明および詳細は、説明の簡潔化のために省略される。本明細書で用いられる、電流供給する電極とは、MOSトランジスタのソースまたはドレイン、バイポーラトランジスタのエミッタまたはコレクタ、ダイオードのカソードまたはアノード等のデバイス中に電流を供給するデバイス要素を意味し、制御電極とは、MOSトランジスタのゲートまたはバイポーラトランジスタのベース等のデバイス中の電流フローを制御するデバイス素子を意味する。本明細書では、デバイスはあるnチャネルもしくはpチャネルデバイスまたはあるn型もしくはp型ドープ領域と説明されているが、本発明の一実施形態によれば、相補的なデバイスも可能であることが当業者には理解されよう。「中」、「間」、「とき」という単語は、本明細書で用いられるとき、動作開始すると即座に起こる動作を意味する正確な用語ではなく、伝搬遅延等の最初の動作によって開始される反応と最初の動作との間に小さいがある程度の遅延が存在しえることを意味することが当業者は理解されるであろう。「ほぼ」、「約」、または「実質的に」という単語の使用は、要素の値が、述べられた値または位置に非常に近いことが想定されるパラメータを有することを意味する。しかしながら、当技術分野で周知であるように、値または位置が述べられたように正確であることを阻止する小さな差異が常に存在する。最大約10%（半導体のドープ濃度の場合、最大20%）の差異が、記載される精度の理想的な目標からの妥当な差異とみなされることが、当技術分野で定着している。

【0007】

論理ゼロレベル( $V_L$ )はまた、論理低レベルまたは論理低電圧レベルと呼ばれ、論理ゼロ電圧の電圧レベルは、電源電圧および論理ファミリのタイプの関数であることに留意されたい。例えば、相補型モス(CMOS)論理ファミリでは、論理ゼロ電圧は、電源電圧レベルの約30%であり得る。5Vで動作するトランジスタ・トランジスタ・ロジック(TTL)システムでは、論理0電圧レベルは約0.8ボルトであり、一方、5Vで動作するCMOSシステムでは、論理0電圧レベルは約1.5ボルトである。論理1電圧レベル( $V_H$ )はまた、論理高電圧レベル、論理高電圧または論理1電圧とも呼ばれ、論理0電圧レベルと同様に論理高電圧レベルもまた、電源および論理ファミリのタイプの関数であり得る。例えば、CMOSシステムでは、論理1電圧は、電源電圧レベルの約70%である。5ボルトで動作するTTLシステムでは、論理1電圧は約2.4ボルトであり、一方、5ボルトで動作するCMOSシステムの場合、論理1電圧は約3.5ボルトであり得る。

【発明を実施するための形態】

【0008】

概して、本発明は、とりわけ、例えば、1つ以上の電力セルを備えるコンポーネント等のコンポーネントの電圧を平衡化させるためのモジュールおよび方法を提供する。本発明の一実施形態によれば、インターフェース回路は、第1のコンポーネントの電圧を監視する動作モードで動作され、第1のコンポーネントの電圧をサンプリングする別の動作モードで動作され、かつ第1のコンポーネントの電圧を平衡化させるさらに別の動作モードで動作される。

【0009】

各種実施形態によれば、モジュールは、一体となって統合されたインターフェースまたは

10

20

30

40

50

スイッチングネットワーク、ならびに、例えば、トランジスタおよびレジスタ、または平衡化を達成するためにこのインターフェースまたはスイッチングネットワークと一体となって統合されるレジスタ等の素子を含む。

【0010】

本発明の別の実施形態によれば、1つ以上の電力セルとインターフェースをとる方法であつて、この方法が、第1スイッチング素子が第1スイッチング素子構成になるように構成され、第2スイッチング素子の第2スイッチング素子構成に形成されるとこれら1つ以上の電力セルの内の第1電力セルの電圧を監視することと、第1スイッチング素子が第2スイッチング素子構成になるように構成されており、第2スイッチング素子の第2スイッチング素子構成に形成されると第1電力セルからサンプリングされた電圧を発生させることと、第2スイッチング素子の第1スイッチング素子構成に形成されると第1電力セルの電圧を平衡化させることと、を含む。

10

【0011】

別の実施形態によれば、第1、第2および第3端子を有する第1スイッチングネットワークと、第1スイッチングネットワークの第1と第2端子間に結合された第1エネルギー貯蔵素子と、第1スイッチングネットワークの第1端子に結合された第1インピーダンス素子と、第1スイッチングネットワークの第3端子に結合された第2インピーダンス素子と、を備えるモジュールが提供される。

【0012】

図1は、フィルタ回路22に接続された制御モジュール12を備える電力セルモニタおよび制御回路10のブロック図である。電力セルモニタおよび制御回路10は、電力貯蔵装置24に接続されている。制御モジュール12は、制御モジュール12の入力部に接続されたまたは代替的に、制御モジュール12の入力部として機能する入力部と、アナログデジタルコンバータ(ADC)20に接続された出力部を有するマルチプレクサ(MUX)18の入力部に接続された出力部と、を有するインターフェースネットワーク16を含む。電源貯蔵装置24は、それぞれ、制御回路10の対応するフィルタ部分22<sub>1</sub>、22<sub>2</sub>、…、22<sub>n</sub>に接続される複数の電力セル24<sub>1</sub>、24<sub>2</sub>、…、24<sub>n</sub>から成り得る。あるいは、電力貯蔵装置は、キャパシタ、燃料セル、バッテリ等から成り得る。インターフェースネットワーク16は、複数のスイッチング素子16<sub>1</sub>、16<sub>2</sub>、…、16<sub>n</sub>から成り得るが、ここで、スイッチング素子16<sub>1</sub>は、入力端子16<sub>1</sub>I1、16<sub>1</sub>I2、16<sub>1</sub>I3、16<sub>1</sub>I4、16<sub>1</sub>I5と、出力端子16<sub>1</sub>O1、16<sub>1</sub>O2、16<sub>1</sub>O3とを有し、スイッチング素子16<sub>2</sub>は、入力端子16<sub>2</sub>I1、16<sub>2</sub>I2、16<sub>2</sub>I3、16<sub>2</sub>I4、16<sub>2</sub>I5と、出力端子16<sub>2</sub>O1、16<sub>2</sub>O2、16<sub>2</sub>O3とを有し、スイッチング素子16<sub>n</sub>は、入力端子16<sub>n</sub>I1、16<sub>n</sub>I2、16<sub>n</sub>I3、16<sub>n</sub>I4、16<sub>n</sub>I5と、出力端子16<sub>n</sub>O1、16<sub>n</sub>O2および16<sub>n</sub>O3を有する。ある実施形態によれば、入力端子16<sub>1</sub>I3は入力端子16<sub>2</sub>I1に接続されて入力端子16<sub>c</sub>I1を形成し、入力端子16<sub>(n-1)</sub>I3は入力端子16<sub>n</sub>I1に接続されて入力端子16<sub>c</sub>I(n-1)を形成し；出力端子16<sub>1</sub>O3は出力端子16<sub>2</sub>O1に接続されて出力端子16<sub>c</sub>O1を形成し、出力端子16<sub>(n-1)</sub>O3は出力端子16<sub>n</sub>O1に接続されて出力端子16<sub>c</sub>O(n-1)を形成する。添字「n」は整数を表すことに留意されたい。

20

30

【0013】

別の実施形態では、制御モジュール12は、入力ピンまたは入力リード線12P<sub>1</sub>、12P<sub>2</sub>、12P<sub>3</sub>、12P<sub>4</sub>、…、12P<sub>(2n-1)</sub>、12P<sub>2n</sub>、12P<sub>(2n+1)</sub>を有する半導体パッケージ中のモノリシック集積された半導体デバイスであり、ここで、nは、整数を表す。例えば、入力端子16<sub>1</sub>I1、16<sub>1</sub>I2、16<sub>c</sub>I1、16<sub>2</sub>I2、…、16<sub>c</sub>I(n-1)、16<sub>n</sub>I2および16<sub>n</sub>I3は、それぞれ、入力ピン12P<sub>1</sub>、12P<sub>2</sub>、12P<sub>3</sub>、12P<sub>4</sub>、…、12P<sub>(2n-1)</sub>、12P<sub>2n</sub>および12P<sub>(2n+1)</sub>に接続される。入力端子16<sub>1</sub>I1、16<sub>1</sub>I2、16<sub>c</sub>I1、16<sub>2</sub>I2、…、16<sub>c</sub>I(n-1)、16<sub>n</sub>I2、および16<sub>n</sub>I3は、それぞれ、入力ピン12P<sub>1</sub>、12P<sub>2</sub>、12P<sub>3</sub>、12P<sub>4</sub>、…、12P<sub>(2n-1)</sub>、

40

50

、 $12P_{2n}$ 、および $12P_{(2n+1)}$ に直接に接続されているように図示されているが、これは本発明を制限するものではなく、他の回路要素を介して相互に接続されてもよい。あるいは、入力端子 $16_1I1$ 、 $16_1I2$ 、 $16_cI1$ 、 $16_2I2$ 、 $\dots$ 、 $16_cI(n-1)$ 、 $16_nI2$ および $16_nI3$ は、それぞれ、入力ピン $12P_1$ 、 $12P_2$ 、 $12P_3$ 、 $12P_4$ 、 $\dots$ 、 $12P_{(2n-1)}$ 、 $12P_{2n}$ および $12P_{(2n+1)}$ として機能し得る。

【0014】

別の実施形態によれば、制御モジュール12およびフィルタ部分22はモノリシックに集積されて、集積半導体デバイスを形成している。制御モジュール12およびフィルタ部分22がモノリシックに集積されている実施形態では、入力ピン $12P_1$ 、 $12P_2$ 、 $12P_3$ 、 $12P_4$ 、 $\dots$ 、 $12P_{(2n-1)}$ 、 $12P_{2n}$ および $12P_{(2n+1)}$ は存在せず、入力端子 $22_1I1$ 、 $22_cI1$ 、 $22_cI(n-1)$ および $22_nI2$ が、入力ピンとして機能するか、あるいは、入力ピンに接続されている。

【0015】

スイッチング素子 $16_1$ の入力端子 $16_1I4$ および $16_1I5$ は、それぞれ制御信号 $V26_1$ および $V28_1$ を受信するように結合されており、スイッチング素子 $16_2$ の入力端子 $16_2I4$ および $16_2I5$ は、それぞれ、制御信号 $V26_2$ および $V28_2$ を受信するように結合されており、スイッチング素子 $16_n$ の入力端子 $16_nI4$ および $16_nI5$ は、それぞれ、制御信号 $V26_n$ および $V28_n$ を受信するように結合されている。

【0016】

スイッチング素子 $16_1$ 、 $\dots$ 、 $16_n$ の出力端子 $16_1O1$ 、 $16_1O2$ 、 $16_cO1$ 、 $16_2O2$ 、 $\dots$ 、 $16_cO(n-1)$ 、 $16_nO2$ および $16_nO3$ は、MUX18の対応する入力端子に接続されている。

【0017】

フィルタ22は複数のフィルタ部分 $22_1$ 、 $22_2$ 、 $\dots$ 、 $22_n$ から成り、ここで、各フィルタ部分は、電力貯蔵装置24の対応する電力セルに接続されている入力端子と、インタフェースネットワーク16の対応する入力ピンに接続されている出力端子とを含む。フィルタ部分 $22_1$ は、入力端子 $22_1I1$ および $22_1I2$ と、出力端子 $22_1O1$ 、 $22_1O2$ および $22_1O3$ とを有し、フィルタ部分 $22_2$ は、入力端子 $22_2I1$ および $22_2I2$ と、出力端子 $22_2O1$ 、 $22_2O2$ および $22_2O3$ とを有し、フィルタ部分 $22_n$ は、入力端子 $22_nI1$ および $22_nI2$ と、出力端子 $22_nO1$ 、 $22_nO2$ および $22_nO3$ とを有する。ある実施形態によれば、入力端子 $22_1I2$ は入力端子 $22_2I1$ に接続されて入力端子 $22_cI1$ を形成し、入力端子 $22_{(n-1)}I2$ は入力端子 $22_nI1$ に接続されて入力端子 $22_cI(n-1)$ を形成する。出力端子 $22_1O3$ は出力端子 $22_2O1$ に接続されて出力端子 $22_cO1$ を形成し、出力端子 $22_{(n-1)}O3$ は出力端子 $22_nO1$ に接続されて出力端子 $22_cO(n-1)$ を形成する。制御モジュール12がモノリシック集積された半導体デバイスで、フィルタ22が個別の回路素子から形成されている実施形態では、出力端子 $22_1O1$ 、 $22_1O2$ 、 $22_cO1$ 、 $22_2O2$ 、 $\dots$ 、 $22_cO(n-1)$ 、 $22_nO2$ および $22_nO3$ は、それぞれ、入力ピン $12P_1$ 、 $12P_2$ 、 $12P_3$ 、 $12P_4$ 、 $\dots$ 、 $12P_{(2n-1)}$ 、 $12P_{2n}$ および $12P_{(2n+1)}$ に接続される。

【0018】

入力端子 $22_1I1$ は、電力セル $24_1$ の正極に接続され、入力端子 $22_cI1$ は、それぞれ、電力セル $24_1$ および $24_2$ の負極および正極に接続される。入力端子 $22_cI(n-1)$ は電力セル $24_n$ の正極に接続される。入力端子 $22_nI2$ は電力セル $24_n$ の負極に接続される。

【0019】

スイッチング素子 $16_1$ 、 $16_2$ 、 $\dots$ 、 $16_n$ 、フィルタ部分 $22_1$ 、 $22_2$ 、 $\dots$ 、 $22_n$ および電力セル $24_1$ 、 $24_2$ 、 $\dots$ 、 $24_n$ の個数は、本発明の制限で

はないことに留意されたい。

【0020】

完全を期すために、図2は、それぞれ、4つのフィルタ部分22<sub>1</sub>、22<sub>2</sub>、22<sub>3</sub>、および22<sub>4</sub>に接続された4つのスイッチング素子16<sub>1</sub>、16<sub>2</sub>、16<sub>3</sub>、および16<sub>4</sub>を備える電力セルモニタおよび制御回路10Aを説明するために包含される。したがって、制御回路10Aは、4つの電力貯蔵装置24<sub>1</sub>、24<sub>2</sub>、24<sub>3</sub>および24<sub>4</sub>に接続される。4つのスイッチング素子、4つのフィルタ部分および4つの電力貯蔵装置が図2に図示されているが、これは本発明の制限ではない、すなわち、4つより多いまたは少ないスイッチング素子や、フィルタ部分や、電力貯蔵装置が存在し得る。より具体的には、スイッチング素子16<sub>1</sub>は、入力端子16<sub>1</sub>I1、16<sub>1</sub>I2、16<sub>1</sub>I3、16<sub>1</sub>I4および16<sub>1</sub>I5と、出力端子16<sub>1</sub>O1、16<sub>1</sub>O2および16<sub>1</sub>O3と、を有し；スイッチング素子16<sub>2</sub>は、入力端子16<sub>2</sub>I1、16<sub>2</sub>I2、16<sub>2</sub>I3、16<sub>2</sub>I4および16<sub>2</sub>I5と出力端子16<sub>2</sub>O1、16<sub>2</sub>O2および16<sub>2</sub>O3と、を有し、スイッチング素子16<sub>3</sub>は、入力端子16<sub>3</sub>I1、16<sub>3</sub>I2、16<sub>3</sub>I3、16<sub>3</sub>I4および16<sub>3</sub>I5と出力端子16<sub>3</sub>O1、16<sub>3</sub>O2および16<sub>3</sub>O3と、を有し、スイッチング素子16<sub>4</sub>は、入力端子16<sub>4</sub>I1、16<sub>4</sub>I2、16<sub>4</sub>I3、16<sub>4</sub>I4および16<sub>4</sub>I5と出力端子16<sub>4</sub>O1、16<sub>4</sub>O2および16<sub>4</sub>O3と、を有する。ある実施形態によれば、入力端子16<sub>1</sub>I3は入力端子16<sub>2</sub>I1に接続されて入力端子16<sub>c</sub>I1を形成し、入力端子16<sub>2</sub>I3は入力端子16<sub>3</sub>I1に接続されて入力端子16<sub>c</sub>I2を形成し、入力端子16<sub>3</sub>I3は入力端子16<sub>4</sub>I1に接続されて入力端子16<sub>c</sub>I3を形成し、出力端子16<sub>1</sub>O3は出力端子16<sub>2</sub>O1に接続されて出力端子16<sub>c</sub>O1を形成し、出力端子16<sub>2</sub>O3は出力端子16<sub>3</sub>O1に接続されて出力端子16<sub>c</sub>O2を形成し、出力端子16<sub>3</sub>O3は出力端子16<sub>4</sub>O1に接続されて出力端子16<sub>c</sub>O3を形成し得る。

【0021】

スイッチング素子16<sub>1</sub>の入力端子16<sub>1</sub>I4および16<sub>1</sub>I5は、それぞれ、制御信号V26<sub>1</sub>およびV28<sub>1</sub>を受信するように結合されており、スイッチング素子16<sub>2</sub>の入力端子16<sub>2</sub>I4および16<sub>2</sub>I5は、それぞれ、制御信号V26<sub>2</sub>およびV28<sub>2</sub>を受信するように結合されており、スイッチング素子16<sub>3</sub>の入力端子16<sub>3</sub>I4および16<sub>3</sub>I5は、それぞれ、制御信号V26<sub>3</sub>およびV28<sub>3</sub>を受信するように結合されており、スイッチング素子16<sub>4</sub>の入力端子16<sub>4</sub>I4および16<sub>4</sub>I5は、それぞれ、制御信号V26<sub>4</sub>およびV28<sub>4</sub>を受信するように結合されている。

【0022】

それぞれ、スイッチング素子16<sub>1</sub>、16<sub>2</sub>、16<sub>3</sub>および16<sub>4</sub>の出力端子16<sub>1</sub>O1、16<sub>1</sub>O2、16<sub>c</sub>O1、16<sub>2</sub>O2、16<sub>c</sub>O2、16<sub>3</sub>O2、16<sub>c</sub>O3、16<sub>4</sub>O2、および16<sub>4</sub>O3は、MUX18の対応する入力端子に接続される。

【0023】

フィルタ22は複数のフィルタ部分22<sub>1</sub>、22<sub>2</sub>、22<sub>3</sub>および22<sub>4</sub>から成り、ここで、各フィルタ部分は、電力貯蔵装置24の対応する電力セル24<sub>1</sub>、24<sub>2</sub>、24<sub>3</sub>および24<sub>4</sub>に接続された入力端子ならびに制御モジュール12のスイッチング素子の対応する入力ピンに接続された出力端子を含む。フィルタ部分22<sub>1</sub>は、入力端子22<sub>1</sub>I1および22<sub>1</sub>I2と出力端子22<sub>1</sub>O1、22<sub>1</sub>O2および22<sub>1</sub>O3と、を有し、フィルタ部分22<sub>2</sub>は、入力端子22<sub>2</sub>I1および22<sub>2</sub>I2と出力端子22<sub>2</sub>O1、22<sub>2</sub>O2および22<sub>2</sub>O3と、を有し、フィルタ部分22<sub>3</sub>は、入力端子22<sub>3</sub>I1および22<sub>3</sub>I2と出力端子22<sub>3</sub>O1、22<sub>3</sub>O2および22<sub>3</sub>O3と、を有し、フィルタ部分22<sub>4</sub>は、入力端子22<sub>4</sub>I1および22<sub>4</sub>I2と出力端子22<sub>4</sub>O1、22<sub>4</sub>O2および22<sub>4</sub>O3と、を有する。ある実施形態によれば、入力端子22<sub>1</sub>I2は入力端子22<sub>2</sub>I1に接続されて入力端子22<sub>c</sub>I1を形成し、入力端子22<sub>2</sub>I2は入力端子22<sub>3</sub>I1に接続されて入力端子22<sub>c</sub>I2を形成し、入力端子22<sub>3</sub>I2は入力端子22<sub>4</sub>I1に接続されて入力端子22<sub>c</sub>I3を形成する。入力端子22<sub>1</sub>I1は、電力セル24

<sub>1</sub> の正極に接続され、入力端子 22<sub>c</sub>I<sub>1</sub> は、それぞれ、電力セル 24<sub>1</sub> および 24<sub>2</sub> の負極および正極に接続される。入力端子 22<sub>c</sub>I<sub>2</sub> は、それぞれ、電力セル 24<sub>2</sub> および 24<sub>3</sub> の負極および正極に接続される。入力端子 22<sub>c</sub>I<sub>3</sub> は、それぞれ、電力セル 24<sub>3</sub> および 24<sub>4</sub> の負極および正極に接続される。入力端子 22<sub>c</sub>I<sub>4</sub> は、電力セル 24<sub>4</sub> の負極に接続される。

【0024】

出力端子 22<sub>c</sub>O<sub>3</sub> は出力端子 22<sub>c</sub>O<sub>1</sub> に接続されて出力端子 22<sub>c</sub>O<sub>1</sub> を形成し、出力端子 22<sub>c</sub>O<sub>3</sub> は出力端子 22<sub>c</sub>O<sub>1</sub> に接続されて出力端子 22<sub>c</sub>O<sub>2</sub> を形成し、出力端子 22<sub>c</sub>O<sub>3</sub> は出力端子 22<sub>c</sub>O<sub>1</sub> に接続されて出力端子 22<sub>c</sub>O<sub>3</sub> を形成し得る。

出力端子 22<sub>c</sub>O<sub>1</sub> は入力ピン 12P<sub>1</sub> に接続され、出力端子 22<sub>c</sub>O<sub>2</sub> は入力ピン 12P<sub>2</sub> に接続され、出力端子 22<sub>c</sub>O<sub>1</sub> は入力ピン 12P<sub>3</sub> に接続され、出力端子 22<sub>c</sub>O<sub>2</sub> は入力ピン 12P<sub>4</sub> に接続され、出力端子 22<sub>c</sub>O<sub>2</sub> は入力ピン 12P<sub>5</sub> に接続され、出力端子 22<sub>c</sub>O<sub>2</sub> は入力ピン 12P<sub>6</sub> に接続され、出力端子 22<sub>c</sub>O<sub>3</sub> は入力ピン 12P<sub>7</sub> に接続され、出力端子 22<sub>c</sub>O<sub>2</sub> は入力ピン 12P<sub>8</sub> に接続され、出力端子 22<sub>c</sub>O<sub>3</sub> は入力ピン 12P<sub>9</sub> に接続される。

10

【0025】

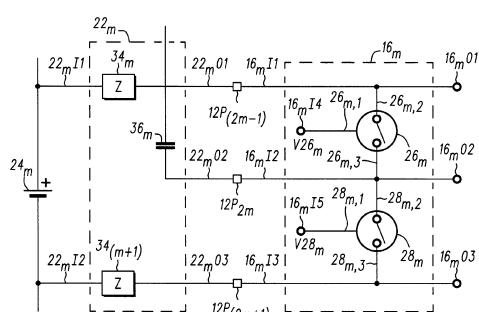

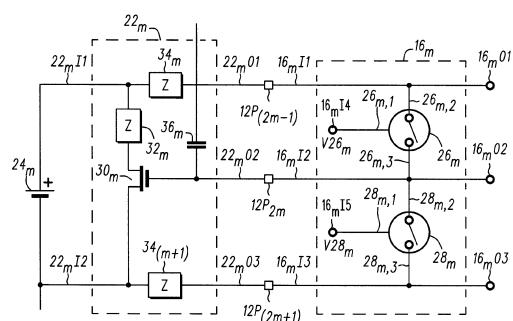

図 3 は、本発明の別の実施形態によれば、フィルタ部分 22<sub>m</sub> を介して電力セル 24<sub>m</sub> に接続されるインターフェースネットワーク 16 (図 1 および 2 を参照して説明した) のスイッチング素子またはスイッチング部分 16<sub>m</sub> の回路図である。図 1 のスイッチング素子 16<sub>1</sub>、16<sub>2</sub>、…、16<sub>n</sub> が、スイッチング素子 16<sub>m</sub> から成り、かつ変数 m が、整数 1、2、…、n を表すために用いられることに留意されたい。例えば、スイッチング素子 16<sub>1</sub> はスイッチング素子 16<sub>m</sub> に対応するが、ここで、m は、1 に置き換えられ、スイッチング素子 16<sub>2</sub> はスイッチング素子 16<sub>m</sub> に対応するが、ここで、m は、2 に置き換えられ、スイッチング素子 16<sub>n</sub> はスイッチング素子 16<sub>m</sub> に対応するが、ここで、m は、n に置き換えられる。同様に、図 2 のスイッチング素子 16<sub>1</sub>、16<sub>2</sub>、16<sub>3</sub>、16<sub>4</sub> は、スイッチング素子 16<sub>m</sub> から成り、変数 m は、整数 1、2、3 および 4 を表すために用いられている。例えば、スイッチング素子 16<sub>1</sub> はスイッチング素子 16<sub>m</sub> に対応するが、ここで、m は、1 に置き換えられ、スイッチング素子 16<sub>2</sub> はスイッチング素子 16<sub>m</sub> に対応するが、ここで、m は、2 に置き換えられ、スイッチング素子 16<sub>3</sub> はスイッチング素子 16<sub>m</sub> に対応するが、ここで、m は、3 に置き換えられ、スイッチング素子 16<sub>4</sub> はスイッチング素子 16<sub>m</sub> に対応するが、ここで、m は、4 に置き換えられる。

20

【0026】

スイッチング素子 16<sub>m</sub> はスイッチ 26<sub>m</sub> および 28<sub>m</sub> を含み、各スイッチ 26<sub>m</sub> および 28<sub>m</sub> は制御端子および 1 対の導電端子を含む。スイッチ 26<sub>m</sub> は電流制御素子または平衡化スイッチと呼ばれ、スイッチ 28<sub>m</sub> はサンプリングスイッチと呼ばれ得る。より具体的には、スイッチ 26<sub>m</sub> は、制御端子 26<sub>m,1</sub>、導電端子 26<sub>m,2</sub> および導電端子 26<sub>m,3</sub> を有する。導電端子 26<sub>m,2</sub> は、入力端子 16<sub>m</sub>I<sub>1</sub> および出力端子 16<sub>m</sub>O<sub>1</sub> に接続される。導電端子 26<sub>m,2</sub> は、端子 16<sub>m</sub>I<sub>1</sub> および 16<sub>m</sub>O<sub>1</sub> に接続され得るか、または代替的に、端子 16<sub>m</sub>I<sub>1</sub> および 16<sub>m</sub>O<sub>1</sub> は入/出力端子を形成し得ることに留意されたい。スイッチ 28<sub>m</sub> は、制御端子 28<sub>m,1</sub>、導電端子 28<sub>m,2</sub> および導電端子 28<sub>m,3</sub> を有する。導電端子 28<sub>m,2</sub> は、導電端子 26<sub>m,3</sub> ならびに端子 16<sub>m</sub>I<sub>2</sub> および 16<sub>m</sub>O<sub>2</sub> に接続される。導電端子 28<sub>m,3</sub> は、入力端子 16<sub>m</sub>I<sub>3</sub> および出力端子 16<sub>m</sub>O<sub>3</sub> に接続され得るか、または代替的に、端子 16<sub>m</sub>I<sub>3</sub> および 16<sub>m</sub>O<sub>3</sub> は入/出力端子を形成し得ることに留意されたい。さらに、端子 26<sub>m,1</sub> は、図 1 の端子 16<sub>1</sub>I<sub>4</sub>、16<sub>2</sub>I<sub>4</sub>、…、16<sub>n</sub>I<sub>4</sub> に対応し、端子 28<sub>m,1</sub> は、図 1 の端子 16<sub>1</sub>I<sub>5</sub>、16<sub>2</sub>I<sub>5</sub>、…、16<sub>n</sub>I<sub>5</sub> に対応することに留意されたい。

40

【0027】

フィルタ部分 22<sub>m</sub> は、入力端子 22<sub>m</sub>I<sub>1</sub> に接続された、または代替的に、入力端子

22<sub>m</sub>I1として機能する端子と、出力端子22<sub>m</sub>O1に接続された、または代替的に、端子22<sub>m</sub>O1として機能する端子と、を有するインピーダンス素子34<sub>m</sub>を備える。出力端子22<sub>m</sub>O1は、エネルギー貯蔵素子36<sub>m</sub>を介して出力端子22<sub>m</sub>O2に接続され得る。入力端子22<sub>m</sub>I2は、インピーダンス素子34<sub>(m+1)</sub>を介して出力端子22<sub>m</sub>O3に接続され得る。例えば、インピーダンス素子34<sub>m</sub>および34<sub>(m+1)</sub>はレジスタであり、エネルギー貯蔵素子36<sub>m</sub>はキャパシタである。インピーダンス素子34<sub>m</sub>および34<sub>(m+1)</sub>はレジスタにはかぎられないため、これらは図3では記号Zで表されている。スイッチング部分16<sub>m</sub>がモノリシック集積された半導体デバイスもしくはモノリシック集積された半導体デバイスのある部分であり、回路素子34<sub>m</sub>、34<sub>(m+1)</sub>および36<sub>m</sub>が個別の回路素子である実施形態では、回路素子34<sub>m</sub>、34<sub>(m+1)</sub>および36<sub>m</sub>は入力ピン12P<sub>(2m-1)</sub>、12P<sub>2m</sub>および12P<sub>(2m+1)</sub>を介してスイッチング部分16<sub>m</sub>に接続される、すなわち、出力端子22<sub>m</sub>O1は入力ピン12P<sub>(2m-1)</sub>に接続され、出力端子22<sub>m</sub>O2は入力ピン12P<sub>2m</sub>に接続され、出力端子22<sub>m</sub>O3は入力ピン12P<sub>(2m+1)</sub>に接続される。

10

#### 【0028】

電力セル24<sub>m</sub>は、フィルタ部分22<sub>m</sub>の入力端子22<sub>m</sub>I1に接続された正極と、フィルタ部分22<sub>m</sub>の入力端子22<sub>m</sub>I2に接続された負極と、を有するバッテリセルを備える。

#### 【0029】

出力端子22<sub>m</sub>O1は入力端子16<sub>m</sub>I1に電気的に接続され、出力端子22<sub>m</sub>O2は入力端子16<sub>m</sub>I2に電気的に接続され、出力端子22<sub>m</sub>O3は入力端子16<sub>m</sub>I3に電気的に接続されることに留意されたい。

20

#### 【0030】

引き続き図3を参照すると、スイッチング部分16<sub>m</sub>は、フィルタリング継続観察モード、サンプルアンドホールドモードおよび平衡化モードを含む少なくとも3つの互いに異なる動作モードで動作する。継続観察動作モードでは、電力セル24<sub>m</sub>にまたがる電圧を、スイッチング素子26<sub>m</sub>および28<sub>m</sub>をオープンまたはクローズするように構成することによって監視する。例えば、電力セル24<sub>m</sub>にまたがる電圧は、スイッチング素子26<sub>m</sub>をオープンするのに適切な制御電圧V26<sub>m</sub>をスイッチング素子26<sub>m</sub>の制御端子に印加し、スイッチング素子28<sub>m</sub>をクローズするのに適切な制御電圧V28<sub>m</sub>をスイッチング素子28<sub>m</sub>の制御端子に印加し、これによって、出力端子16<sub>m</sub>O2を出力端子16<sub>m</sub>O3に短絡させることによって監視することが可能である。

30

#### 【0031】

スイッチング素子28<sub>m</sub>をクローズすると、出力端子16<sub>m</sub>O2が出力端子16<sub>m</sub>O3に短絡され、キャパシタ36<sub>m</sub>が電力セル24<sub>m</sub>の電圧に実質的に充電される、すなわち、キャパシタ36<sub>m</sub>は、電力セル24<sub>m</sub>の電圧に実質的に等しい電圧にまで充電される。キャパシタ36<sub>m</sub>の電圧は、出力端子16<sub>m</sub>O1と16<sub>m</sub>O2間に输出される。MUX18(図1および2に示す)は、出力端子16<sub>m</sub>O1と16<sub>m</sub>O2間の電圧をADCコンバータ20に伝達するように構成されている。したがって、電力セル24<sub>m</sub>のフィルタリングされた電圧を表す電圧は、ADC20に伝達され、これによって電力セル24<sub>m</sub>にまたがる電圧を観察または監視する。

40

#### 【0032】

サンプルアンドホールド動作モードでは、電力セル24<sub>m</sub>にまたがる電圧を、スイッチング素子26<sub>m</sub>をオープンするのに適切な制御電圧V26<sub>m</sub>をスイッチング素子26<sub>m</sub>の制御端子に印加し、スイッチング素子28<sub>m</sub>をクローズするのに適切な制御電圧V28<sub>m</sub>をスイッチング素子28<sub>m</sub>の制御端子に印加し、これによって、出力端子16<sub>m</sub>O2を出力端子16<sub>m</sub>O3に短絡させることによって、サンプリングならびに記憶もしくは保持することが可能である。キャパシタ36<sub>m</sub>は、電力セル24<sub>m</sub>にまたがる電圧に実質的に等しい電圧に充電される、すなわち、キャパシタ36<sub>m</sub>は電力セル24<sub>m</sub>の電圧をサンプリングする。

50

## 【0033】

電力セル $24_m$ の電圧をサンプリングした後、スイッチング素子 $26_m$ をオープンするのに適した制御電圧 $V26_m$ がスイッチング素子 $26_m$ の制御端子に維持され、スイッチング素子 $28_m$ をオープンするのに適した制御電圧 $V28_m$ がスイッチング素子 $28_m$ の制御端子に印加される。MUX18およびADC20(図1および2に示す)は、出力端子 $16_mO1$ および $16_mO2$ が高インピーダンスネットワークに接続されるように構成される。キャパシタ $36_m$ の両端に現れるサンプリングされた電圧は保持される。キャパシタ $36_m$ にまたがる電圧は、出力端子 $16_mO1$ を出力端子 $16_mO2$ 間に出力される。MUX18は、出力端子 $16_mO1$ と出力端子 $16_mO2$ との間の電圧をADCコンバータ20に伝達するように構成される。したがって、電力セル $24_m$ の電圧を表すサンプリングされた電圧はADC20に伝達される。

## 【0034】

平衡化動作モードでは、電力セル $24_m$ にまたがる電圧は、スイッチング素子 $26_m$ をクローズするのに適切な制御電圧 $V26_m$ をスイッチング素子 $26_m$ の制御端子に印加し、スイッチング素子 $28_m$ をクローズするのに適切な制御電圧 $V28_m$ をスイッチング素子 $28_m$ の制御端子に印加することによって平衡化させることが可能である。したがって、インピーダンス素子 $34_m$ 、スイッチング素子 $26_m$ 、スイッチング素子 $28_m$ およびインピーダンス素子 $34_{(m+1)}$ を通過する平衡化電流によって、電力セル $24_m$ が放電される。スイッチング素子 $26_m$ は平衡化スイッチまたはスイッチと呼ばれ、スイッチング素子 $28_m$ はサンプリングスイッチまたはスイッチと呼ばれ得る。

## 【0035】

図4は、図1を参照して説明したように制御モジュール12およびフィルタ回路22を備え、図3を参照して説明したフィルタ回路22およびインターフェース回路16の回路実装物の実施形態をさらに含む電力セルモニタおよび制御回路100のブロック図である。図1の実施形態と同様に、図4に示すインターフェースネットワーク16のスイッチングネットワーク $16_1$ 、 $16_2$ 、 $\dots$ 、 $16_n$ はスイッチング素子 $16_m$ から成り、ここで、変数mは、図3を参照して説明されるように、整数1、2、 $\dots$ 、nを表すために用いられる。例えば、スイッチングネットワーク $16_1$ はスイッチング部分 $16_m$ に対応し、ここで、mは、1で置き換えられ、スイッチングネットワーク $16_2$ はスイッチング部分 $16_m$ に対応し、ここで、mは、2で置き換えられ、スイッチングネットワーク $16_n$ はスイッチング部分 $16_m$ に対応し、ここで、mは、nで置き換えられる。

## 【0036】

制御回路100はバッテリ装置24に接続される。上述したように、制御モジュール12は、制御モジュール12の入力部に結合されるか、または代替的に、制御モジュール12の入力部として機能する入力端子および、アナログツーデジタルコンバータ(ADC)20に接続される出力部を有するマルチプレクサ(MUX)18の入力部に結合される出力端子を有するインターフェースネットワーク16を含む。インターフェースネットワーク16は、図1および3を参照して説明した。

## 【0037】

フィルタ22は複数のフィルタ部分 $22_1$ 、 $22_2$ 、 $\dots$ 、 $22_n$ から成り、ここで、各フィルタ部分は、電力貯蔵装置24の対応する電力セル $24_1$ 、 $24_2$ 、 $\dots$ 、 $24_n$ に接続されている入力端子と、スイッチングネットワーク $16_1$ 、 $16_2$ 、 $\dots$ 、 $16_n$ の対応する入力端子に接続されている出力端子と、を含む。フィルタ部分 $22_1$ は、入力端子 $22_1I1$ および $22_cI1$ と、出力端子 $22_1O1$ 、 $22_1O2$ および $22_cO1$ と、を有し、フィルタ部分 $22_2$ は、入力端子 $22_cI1$ および $22_cI2$ と、出力端子 $22_cO1$ 、 $22_2O2$ および $22_cO2$ と、を有し、フィルタ部分 $22_n$ は、入力端子 $22_cI(n-1)$ および $22_nI2$ と、出力端子 $22_cO(n-1)$ 、 $22_nO2$ および $22_nO3$ と、を有する。

## 【0038】

入力端子 $22_1I1$ は、電力セル $24_1$ の正の端子に接続され、入力端子 $22_cI1$ は

、それぞれ、電力セル $24_1$ および $24_2$ の負の端子および正の端子に接続される。入力端子 $22_{cI}(n-1)$ は電力セル $24_n$ の正の端子に接続され、入力端子 $22_{nI2}$ は電力セル $24_n$ の負の端子に接続される。

【0039】

フィルタ部分 $22_1$ は、インピーダンス素子 $34_1$ および $34_2$ と、エネルギー貯蔵素子 $36_1$ と、を備える。より具体的には、出力端子 $22_{1O1}$ は、インピーダンス素子 $34_1$ を介して入力端子 $22_{1I1}$ に、エネルギー貯蔵素子 $36_1$ を介して出力端子 $22_{1O2}$ に接続される。入力端子 $22_{cI1}$ は、インピーダンス素子 $34_2$ を介して出力端子 $22_{cO1}$ に接続される。インピーダンス素子 $34_2$ はフィルタ部分 $22_1$ および $22_2$ に対して共通であることに留意されたい。例えば、インピーダンス素子 $34_1$ および $34_2$ はレジスタであり、エネルギー貯蔵素子 $36_1$ はキャパシタである。

【0040】

フィルタ部分 $22_2$ は、インピーダンス素子 $34_2$ およびエネルギー貯蔵素子 $36_2$ を備える。より具体的には、出力端子 $22_{cO1}$ は、インピーダンス素子 $34_2$ を介して入力端子 $22_{cI1}$ に、エネルギー貯蔵素子 $36_2$ を介して出力端子 $22_{2O2}$ に接続される。例えば、エネルギー貯蔵素子 $36_2$ はキャパシタである。類似の共有コンポーネントおよび接続部が、フィルタ部分 $22_1$ とフィルタ部分 $22_2$ との間に存在するように、フィルタ部分 $22_2$ と、フィルタ部分 $22_2$ に接続された別のフィルタ部分との間に存在することに留意されたい。明瞭さのために、フィルタ部分 $22_2$ の全てのコンポーネントが図示されているわけではない。

【0041】

フィルタ部分 $22_n$ は、インピーダンス素子 $34_n$ および $34_{(n+1)}$ と、エネルギー貯蔵素子 $36_n$ と、を備える。より具体的には、出力端子 $22_{cO(n-1)}$ は、インピーダンス素子 $34_n$ を介して入力端子 $22_{cI(n-1)}$ に、エネルギー貯蔵素子 $36_n$ を介して出力端子 $22_{nO2}$ に接続される。出力端子 $22_{cO(n-1)}$ はまた、入力ピン $12P_{(2n-1)}$ に接続される。入力端子 $22_nI2$ は、インピーダンス素子 $34_{(n+1)}$ を介して出力端子 $22_{nO3}$ に接続される。例えば、インピーダンス素子 $34_n$ および $34_{(n+1)}$ はレジスタであり、エネルギー貯蔵素子 $36_n$ はキャパシタである。インピーダンス素子 $34_n$ および $34_{(n+1)}$ はレジスタであることに限られないため、図4では記号 $Z$ で示されている、すなわち、これらは他のタイプのインピーダンス素子であり得る。スイッチング部分 $16_1$ 、 $16_2$ 、 $\dots$ 、 $16_n$ から成る図4のインターフェースネットワーク $16$ は、フィルタリング継続観察モード、サンプルアンドホールドモードおよび平衡化モードを含む少なくとも3つの互いに異なる動作モードで動作する。インターフェース回路 $16$ の動作モードは、図3を参照して説明されている。

【0042】

図5は、本発明の別の実施形態によれば、フィルタ部分 $22_m$ を介して電力セル $24_m$ に接続されるインターフェースネットワーク $16$ （図1および2を参照して説明した）のスイッチング部分 $16_m$ の回路図である。図1のスイッチングネットワーク $16_1$ 、 $16_2$ 、 $\dots$ 、 $16_n$ が、スイッチング部分 $16_m$ から成り、かつ変数 $m$ が、整数 $1$ 、 $2$ 、 $\dots$ 、 $n$ を表すために用いられることに留意されたい。例えば、スイッチングネットワーク $16_1$ はスイッチング部分 $16_m$ に対応するが、ここで、 $m$ は、 $1$ に置き換えられ、スイッチングネットワーク $16_2$ はスイッチング部分 $16_m$ に対応するが、ここで、 $m$ は、 $2$ に置き換えられ、スイッチング素子 $16_n$ はスイッチング部分 $16_m$ に対応するが、ここで、 $m$ は、 $n$ に置き換えられる。図5のスイッチング部分 $16_m$ は図3のスイッチング部分 $16_m$ に類似しているが、キャパシタ $36_m$ の端子のうちの1つが入力ピン $12P_{(2m-1)}$ に接続されていない点だけが異なる。したがって、キャパシタ $36_m$ は、一方の端子は入力ピン $12P_{2m}$ に接続されているが、他方の端子は別の回路（図6に示す）と共有されている。図3を参照して述べたように、スイッチング素子 $26_m$ は平衡化スイッチまたはスイッチと呼ばれ、スイッチング素子 $28_m$ はサンプリングスイッチまたはスイッチと呼ばれ得る。

## 【0043】

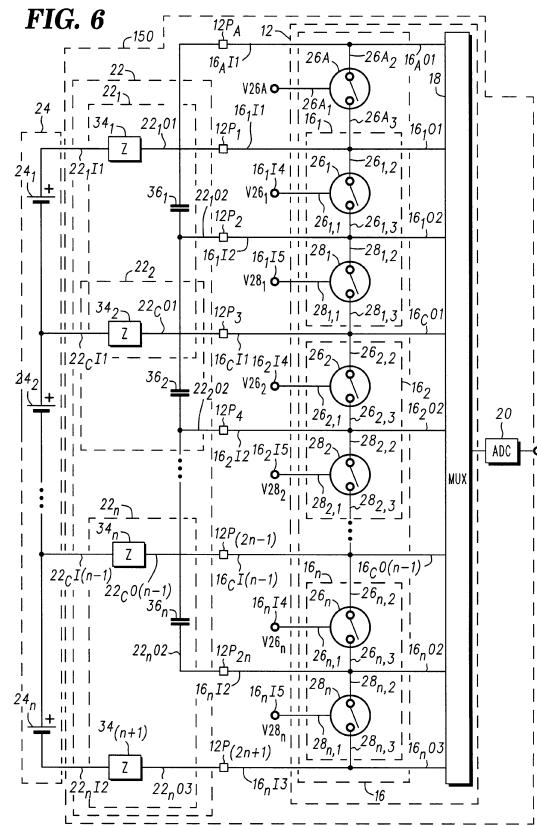

図6は、図1を参照して説明したように制御モジュール12およびフィルタ回路22を備え、図5を参照して説明したフィルタ回路22およびインターフェース回路16の実装物の実施形態をさらに含む電力セルモニタおよび制御モジュール150のブロック図である。制御モジュール150は、バッテリ装置24に接続される。上述したように、制御モジュール12は、制御モジュール12の入力部に接続されるか、または代替的に、制御モジュール12の入力部として機能する入力端子と、アナログツーデジタルコンバータ(ADC)20に接続される出力を有するマルチブレクサ(MUX)18の対応する入力部に接続される出力端子と、を有するインターフェースネットワーク16を含む。インターフェース回路16は、スイッチング部分16<sub>1</sub>、16<sub>2</sub>、…、16<sub>n</sub>およびスイッチング端子26Aから成る。スイッチング部分16<sub>1</sub>、16<sub>2</sub>、…、16<sub>n</sub>は、図4を参照して説明されている。10

## 【0044】

スイッチング素子26Aは、制御信号V26Aを受信するように結合された制御端子26A<sub>1</sub>、導電端子26A<sub>2</sub>および導電端子26A<sub>3</sub>を有する。導電端子26A<sub>2</sub>は、導電端子16<sub>A</sub>I<sub>1</sub>および出力端子16<sub>A</sub>O<sub>1</sub>に接続される。導電端子26A<sub>3</sub>は、入力端子16<sub>1</sub>I<sub>1</sub>、出力端子16<sub>1</sub>O<sub>1</sub>および導電端子26<sub>1</sub>、26<sub>2</sub>に接続される。

## 【0045】

出力端子16<sub>A</sub>O<sub>1</sub>、16<sub>1</sub>O<sub>1</sub>、16<sub>1</sub>O<sub>2</sub>、16<sub>C</sub>O<sub>1</sub>、16<sub>2</sub>O<sub>2</sub>、…、16<sub>C</sub>O<sub>(n-1)</sub>、16<sub>n</sub>O<sub>2</sub>、16<sub>n</sub>O<sub>3</sub>は、MUX18の対応する入力端子に接続される。20

## 【0046】

フィルタ22は複数のフィルタ部分22<sub>1</sub>、22<sub>2</sub>、…、22<sub>n</sub>から成り、ここで、各フィルタ部分は、電力貯蔵装置24の対応する電力セル24<sub>1</sub>、24<sub>2</sub>、…、24<sub>n</sub>に接続される入力端子と、スイッチングネットワーク16<sub>1</sub>、16<sub>2</sub>、…、16<sub>n</sub>の対応する入力端子に接続されている出力端子と、を含む。フィルタ部分22<sub>1</sub>は、入力端子22<sub>1</sub>I<sub>1</sub>および22<sub>C</sub>I<sub>1</sub>ならびに出力端子22<sub>1</sub>O<sub>1</sub>、22<sub>1</sub>O<sub>2</sub>および22<sub>C</sub>O<sub>1</sub>を有し、フィルタ部分22<sub>2</sub>は、入力端子22<sub>C</sub>I<sub>1</sub>および22<sub>C</sub>I<sub>2</sub>ならびに出力端子22<sub>C</sub>O<sub>1</sub>、22<sub>2</sub>O<sub>2</sub>および22<sub>C</sub>O<sub>2</sub>を有し、フィルタ部分22<sub>n</sub>は、入力端子22<sub>C</sub>I<sub>(n-1)</sub>および22<sub>n</sub>I<sub>2</sub>ならびに出力端子22<sub>C</sub>O<sub>(n-1)</sub>、22<sub>n</sub>O<sub>2</sub>および22<sub>n</sub>O<sub>3</sub>を有する。30

## 【0047】

入力端子22<sub>1</sub>I<sub>1</sub>は、電力セル24<sub>1</sub>の正極に接続され、入力端子22<sub>C</sub>I<sub>1</sub>は、それぞれ、電力セル24<sub>1</sub>および24<sub>2</sub>の負極および正極に接続される。入力端子22<sub>C</sub>I<sub>(n-1)</sub>は電力セル24<sub>n</sub>の正極に接続され、入力端子22<sub>n</sub>I<sub>2</sub>は電力セル24<sub>n</sub>の負極に接続される。

## 【0048】

フィルタ部分22<sub>1</sub>は、インピーダンス素子34<sub>1</sub>および34<sub>2</sub>とエネルギー貯蔵素子36<sub>1</sub>と、を備えるが、エネルギー貯蔵素子36<sub>1</sub>は、入力ピン12P<sub>A</sub>に接続された端子および入力ピン12P<sub>2</sub>に接続された端子を有する。出力端子22<sub>1</sub>O<sub>1</sub>は入力ピン12P<sub>1</sub>に接続される。入力端子22<sub>C</sub>I<sub>1</sub>はインピーダンス素子34<sub>2</sub>を介して出力端子22<sub>C</sub>O<sub>1</sub>に接続される。インピーダンス素子34<sub>2</sub>はフィルタ部分22<sub>1</sub>および22<sub>2</sub>に共通であることに留意されたい。例えば、インピーダンス素子34<sub>1</sub>および34<sub>2</sub>はレジスタであり、エネルギー貯蔵素子36<sub>1</sub>はキャパシタである。40

## 【0049】

フィルタ部分22<sub>2</sub>は、インピーダンス素子34<sub>2</sub>およびエネルギー貯蔵素子36<sub>2</sub>を備える。出力端子22<sub>C</sub>O<sub>1</sub>は、入力ピン12P<sub>3</sub>に接続される。エネルギー貯蔵素子36<sub>2</sub>の一方の端子は入力ピン12P<sub>2</sub>に接続され、キャパシタ36<sub>2</sub>の他方の端子は入力ピン12P<sub>4</sub>に接続される。例えば、インピーダンス素子34<sub>2</sub>はレジスタであり、エネルギー貯蔵素子36<sub>2</sub>はキャパシタである。類似の共有コンポーネントおよび接続部が、50

フィルタ部分 22<sub>1</sub> とフィルタ部分 22<sub>2</sub>との間に存在するように、フィルタ部分 22<sub>2</sub>と、フィルタ部分 22<sub>2</sub>に接続された別のフィルタ部分との間に存在することに留意されたい。明瞭さのために、フィルタ部分 22<sub>2</sub>の全てのコンポーネントが図示されているわけではない。

【0050】

フィルタ部分 22<sub>n</sub> は、インピーダンス素子 34<sub>n</sub> および 34<sub>(n+1)</sub> とエネルギー貯蔵素子 36<sub>n</sub> と、を備える。出力端子 22<sub>cO</sub>(n-1) は、入力ピン 12P<sub>(2n-1)</sub> に接続される。入力端子 22<sub>cI</sub>(n-1) はインピーダンス素子 34<sub>n</sub> を介して出力端子 22<sub>cO</sub>(n-1) に接続され、入力端子 22<sub>n</sub>I2 はインピーダンス素子 34<sub>(n+1)</sub> を介して出力端子 22<sub>n</sub>O3 に接続される。出力端子 22<sub>n</sub>O3 は、入力ピン 12P<sub>(2n+1)</sub> に接続される。エネルギー貯蔵素子 36<sub>n</sub> は、入力ピン 12P<sub>2n</sub> に接続された端子を有し、また、隣接するフィルタ部分に接続された端子を有する。例えば、3つのフィルタ部分が存在する実施形態によれば、エネルギー貯蔵素子 36<sub>n</sub> のインデックス n は 3 である、すなわち、エネルギー貯蔵素子 36<sub>n</sub> は参照文字 36<sub>3</sub> で識別され、フィルタ部分 22<sub>2</sub> のエネルギー貯蔵素子 36<sub>2</sub> の端子に接続される端子を有する。例えば、インピーダンス素子 34<sub>n</sub> および 34<sub>(n+1)</sub> はレジスタであり、エネルギー貯蔵素子 36<sub>n</sub> はキャパシタである。インピーダンス素子 34<sub>1</sub>、34<sub>2</sub>、…、34<sub>n</sub>、34<sub>(n+1)</sub> はレジスタであることに限られないため、これらは参照文字 Z で識別される、すなわち、他のタイプのインピーダンス素子であり得ることになる。

【0051】

別の実施形態によれば、セルの極性は、これらのセルが図 1、2、4 および 6 に示す反対の極性となるように切り替えられる。

【0052】

引き続き図 6 を参照すると、スイッチング部分 16<sub>1</sub>、…、16<sub>n</sub> を備えるインターフェースネットワーク 16 は、フィルタリング継続観察モード、微分サンプルアンドホールドモードおよび内部平衡化モードを含む少なくとも 3 つの互いに異なる動作モードで動作する。フィルタリング継続観察動作モードでは、電力セル 24<sub>1</sub>、…、24<sub>n</sub> にまたがる電圧を、スイッチング素子 26<sub>1</sub>、…、26<sub>n</sub> をオープンするように構成し、スイッチング素子 28<sub>1</sub>、…、28<sub>n</sub> と 26A をクローズするように構成することによって監視する。例えば、電力セル 24<sub>1</sub> にまたがる電圧は、MUX 18 の、出力端子 16<sub>A</sub>O1 および 16<sub>A</sub>O2 の電圧を AD コンバータ 20 に伝達する構成に応答して監視することが可能である。このように、電力セル 24<sub>1</sub> のフィルタリングされた電圧を表す電圧が ADC 20 に伝達され、これによって電力セル 24<sub>1</sub> にまたがる電圧が観察または監視される。

【0053】

同様に、電力セル 24<sub>2</sub> にまたがる電圧は、MUX 18 の、出力端子 16<sub>1</sub>O2 および 16<sub>2</sub>O2 の電圧を AD コンバータ 20 に伝達する構成に応答して監視することが可能である。このように、電力セル 24<sub>2</sub> にまたがる電圧を表す電圧が ADC 20 に伝達され、これによって電力セル 24<sub>2</sub> にまたがる電圧が観察または監視される。

【0054】

電力セル 24<sub>n</sub> にまたがる電圧は、MUX 18 の、出力端子 16<sub>(n-1)</sub>O2 および 16<sub>n</sub>O2 の電圧を AD コンバータ 20 に伝達する構成に応答して監視することが可能である。このように、電力セル 24<sub>n</sub> にまたがる電圧を表す電圧が ADC 20 に伝達され、これによって電力セル 24<sub>n</sub> にまたがる電圧が観察または監視される。

【0055】

微分サンプルアンドホールド動作モードでは、電力セル 24<sub>1</sub>、…、24<sub>n</sub> にまたがる電圧を、それぞれ、スイッチング素子 26A、26<sub>1</sub>、…、26<sub>n</sub> および 28<sub>1</sub>、…、28<sub>n</sub> の制御端子に対して適切な制御電圧 V26A、V26<sub>1</sub>、…、V26<sub>n</sub>、および V28<sub>1</sub>、…、V28<sub>n</sub> を印加することによってサンプリングならびに記憶もしくは保持することが可能である。サンプリングするために、スイッチング素子は

10

20

30

40

50

、フィルタリング継続観察モードを可能とするように構成される。このようなスイッチ構成に応答して、キャパシタ $36_1$ 、 $\dots$ 、 $36_n$ は、電力セル $24_1$ 、 $\dots$ 、 $24_n$ にまたがる電圧に実質的に等しい電圧まで充電される。キャパシタ $36_1$ 、 $\dots$ 、 $36_n$ は、フィルタとして機能し、サンプリングされた信号をフィルタリングする。スイッチング素子 $26A$ および $28_1$ 、 $\dots$ 、 $28_n$ のオン抵抗( $R_{ds0n}$ )は、キャパシタ $36_1$ 、 $\dots$ 、 $36_n$ の両端子と直列になっており、これによって、同相雑音に付きものの問題が軽減される。

#### 【0056】

電力セル $24_1$ 、 $\dots$ 、 $24_n$ の電圧をサンプリングした後、情報は、これらのスイッチング素子の開放に好適な制御電圧 $V26A$ および $V28_1$ 、 $\dots$ 、 $V28_n$ を、それぞれ、スイッチング素子 $26A$ および $28_1$ 、 $\dots$ 、 $28_n$ の制御端子に印加することによってキャパシタ $36_1$ 、 $\dots$ 、 $36_n$ 上に保持される。スイッチング素子 $26_1$ 、 $\dots$ 、 $26_n$ は、開放状態にとどまる、すなわち、フィルタリング継続観察モードのときと同じ状態を保つ。このスイッチング構成に応答して、キャパシタ $36_1$ 、 $\dots$ 、 $36_n$ は、電力セル $24_1$ 、 $\dots$ 、 $24_n$ のスタックから隔離され、これによって、それらの電圧が電力セル $24_1$ 、 $\dots$ 、 $24_n$ 上に出力される。

#### 【0057】

電力セル $24_1$ の電圧を表すサンプリングされた電圧は、 $MUX18$ の、出力端子 $16_AO1$ および $16_1O2$ の電圧を $ADC20$ に伝達する構成に応答して監視することができる。

#### 【0058】

$MUX18$ の、出力端子 $16_1O2$ および $16_2O2$ の電圧を $ADC20$ に伝達する構成に応答して、電力セル $24_2$ の電圧を表すサンプリングされた電圧が $ADC20$ に伝達される。

#### 【0059】

$MUX18$ の、出力端子 $16_{(n-1)}O2$ および $16_nO2$ の電圧を $ADC20$ に伝達する構成に応答して、電力セル $24_n$ の電圧を表すサンプリングされた電圧が $ADC20$ に伝達される。

#### 【0060】

内部平衡化動作モードでは、電力セル $24_1$ にまたがる電圧は、スイッチング素子 $26_1$ および $28_1$ の閉鎖に好適な制御信号 $V26_1$ および $V28_1$ を、それぞれ、スイッチング素子 $26_1$ および $28_1$ の制御端子に印加することによって平衡化され得る。したがって、インピーダンス素子 $34_1$ 、スイッチング素子 $26_1$ 、スイッチング素子 $28_1$ およびインピーダンス素子 $34_2$ を通過する平衡化電流によって、電力セル $24_1$ が放電される。

#### 【0061】

その他の電力セルにまたがる電圧は、同様の方法を用いることによって平衡化させることが可能であることに留意されたい。

#### 【0062】

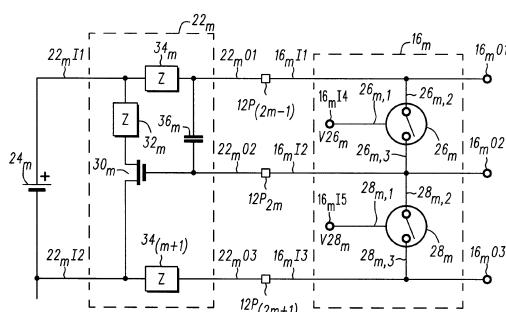

図7は、本発明の別の実施形態によれば、フィルタ部分 $22_m$ を介して電力セル $24_m$ に接続されるスイッチング部分 $16_m$ (図1および2を参照して説明した)の回路図である。図1のスイッチングネットワーク $16_1$ 、 $16_2$ 、 $\dots$ 、 $16_n$ が、スイッチング部分 $16_m$ から成り、かつ変数 $m$ が、整数 $1$ 、 $2$ 、 $\dots$ 、 $n$ を表すために用いられることに留意されたい。例えば、スイッチングネットワーク $16_1$ はスイッチング部分 $16_m$ に対応するが、ここで、 $m$ は、 $1$ に置き換えられ、スイッチングネットワーク $16_2$ はスイッチング部分 $16_m$ に対応するが、ここで、 $m$ は、 $2$ に置き換えられ、スイッチングネットワーク $16_n$ はスイッチング部分 $16_m$ に対応するが、ここで、 $m$ は、 $n$ に置き換えられる。同様に、図2のスイッチングネットワーク $16_1$ 、 $16_2$ 、 $16_3$ 、 $16_4$ は、スイッチング部分 $16_m$ から成り、変数 $m$ は、整数 $1$ 、 $2$ 、 $3$ および $4$ を表すために用いられている。例えば、スイッチングネットワーク $16_1$ はスイッチング部分 $16_m$ に対応

10

20

30

40

50

するが、ここで、 $m$ は、1に置き換えられ、スイッチングネットワーク $16_2$ はスイッチング部分 $16_m$ に対応するが、ここで、 $m$ は、2に置き換えられ、スイッチングネットワーク $16_3$ はスイッチング部分 $16_m$ に対応するが、ここで、 $m$ は、3に置き換えられ、スイッチングネットワーク $16_4$ はスイッチング部分 $16_m$ に対応するが、ここで、 $m$ は、4に置き換えられる。

【0063】

スイッチング部分 $16_m$ を、図3を参照して説明した。

【0064】

フィルタ部分 $22_m$ は、図3を参照して説明したフィルタ部分に類似しているが、平衡化素子 $30_m$ および $32_m$ も含む点だけが異なる。例えば、平衡化素子 $30_m$ および $32_m$ は、それぞれ、トランジスタおよびレジスタである。トランジスタ $30_m$ は、レジスタ $32_m$ を介して入力端子 $22_m I_1$ に接続されるドレン端子と、入力端子 $22_m I_2$ に接続されるソース端子と、出力端子 $22_m O_2$ として機能するか、または代替的に、出力端子 $22_m O_2$ に接続されるゲート端子と、を有する。出力端子 $22_m O_1$ は、インピーダンス素子 $34_m$ を介して入力端子 $22_m I_1$ に接続され、エネルギー貯蔵素子 $36_m$ を介して出力端子 $22_m O_2$ に接続される。入力端子 $22_m I_2$ は、インピーダンス素子 $34_{(m+1)}$ を介して出力端子 $22_m O_3$ に接続される。例えば、インピーダンス素子 $34_m$ および $34_{(m+1)}$ はレジスタであり、エネルギー貯蔵素子 $36_m$ はキャパシタである。レジスタ $32_m$ および $34_m$ は各々が、一般的には一緒に接続されて、入力端子 $22_m I_1$ に接続されるか、または代替的に、入力端子 $22_m I_1$ を形成する結節を形成する端子を有する。レジスタ $32_m$ の他方の端子はトランジスタ $30_m$ のドレン端子に接続され、レジスタ $34_m$ の他方の端子はキャパシタ $36_m$ の端子に接続されて、出力端子 $22_m O_1$ として機能するか、または代替的に、出力端子 $22_m O_1$ に接続される結節を形成し得る。キャパシタ $36_m$ の他方の端子はトランジスタ $30_m$ のゲート端子に接続され、また、出力端子 $22_m O_2$ に接続されるか、または代替的に、出力端子 $22_m O_2$ として機能する結節を形成し得る。レジスタ $34_{(m+1)}$ は、トランジスタ $30_m$ のソース端子に接続されて、入力端子 $22_m I_2$ に接続されるか、または代替的に、入力端子 $22_m I_2$ として機能する結節を形成する端子と、出力端子 $22_m O_3$ として機能するか、または代替的に、出力端子 $22_m O_3$ に接続される端子と、を有する。インピーダンス素子 $32_m$ 、 $34_m$ 、および $34_{(m+1)}$ はレジスタであることに限られないため、図7では記号 $Z$ で示されている、すなわち、これらは他のタイプのインピーダンス素子であり得る。

【0065】

電力セル $24_m$ は、フィルタ部分 $22_m$ の入力端子 $22_m I_1$ に接続された正極と、フィルタ部分 $22_m$ の入力端子 $22_m I_2$ に接続された負極と、を有するバッテリセルを備える。

【0066】

出力端子 $22_m O_1$ は入力ピン $12P_{(2m-1)}$ に電気的に接続され、出力端子 $22_m O_2$ は入力ピン $12P_{2m}$ に電気的に接続され、出力端子 $22_m O_3$ は入力ピン $12P_{(2m+1)}$ に電気的に接続されることに留意されたい。

【0067】

引き続き図7を参照すると、スイッチング部分 $16_m$ は、フィルタリング継続監視または観察モードと、サンプルアンドホールドモードと、平衡化モードと、を含む少なくとも3つの互いに異なる動作モードで動作する。フィルタリング継続監視モードでは、スイッチング素子 $26_m$ をオープンするのに適切な制御電圧 $V_{26_m}$ がスイッチング素子 $26_m$ の制御端子に印加され、スイッチング素子 $28_m$ をクローズするのに適切な制御電圧 $V_{28_m}$ がスイッチング素子 $28_m$ の制御端子に印加される。スイッチング素子 $28_m$ をクローズすることによって、平衡化トランジスタ $30_m$ のゲートツースース電圧が実質的にゼロに設定され、これによって、平衡化トランジスタ $30_m$ がオフとなる。加えて、フィルタのレジスタ $34_m$ および $34_{(m+1)}$ を流れる電流は実質的にゼロであり、したがつ

10

20

30

40

50

て、キャパシタ $36_m$ は、電力セル $24_m$ にまたがる電圧に実質的に等しい電圧にまで充電される。MUX18(図1および2に図示する)は、出力端子 $16_mO1$ および $16_mO2$ の電圧をADC20に伝達するように構成される。したがって、電力セル $24_m$ の電圧を表す電圧がADC20に伝達され、これによって、電力セル $24_m$ にまたがる電圧が観察または監視される。

#### 【0068】

サンプルアンドホールド動作モードでは、スイッチング素子 $26_m$ をオープンするのに適切な制御電圧 $V26_m$ をスイッチング素子 $26_m$ の制御端子に印加し、スイッチング素子 $28_m$ をクローズするのに適切な制御電圧 $V28_m$ をスイッチング素子 $28_m$ の制御端子に印加する。スイッチング素子 $28_m$ をクローズすることによって、平衡化トランジスタ $30_m$ のゲートツースース電圧が実質的にゼロに設定され、これによって、平衡化トランジスタ $30_m$ がオフとなる。加えて、フィルタのレジスタ $34_m$ および $34_{(m+1)}$ を流れる電流は実質的にゼロであり、したがって、キャパシタ $36_m$ は、電力セル $24_m$ にまたがる電圧に実質的に等しい電圧にまで充電される、すなわち、キャパシタ $36_m$ は電力セル $24_m$ の電圧をサンプリングする。次に、スイッチング素子 $26_m$ をオープンするのに適切な制御電圧 $V26_m$ がスイッチング素子 $26_m$ の制御端子に維持され、また、スイッチング素子 $28_m$ をオープンするのに適切な制御電圧 $V28_m$ がスイッチング素子 $28_m$ の制御端子に印加される。MUX18およびADC20(図1および2に図示する)は、出力端子 $16_mO1$ および $16_mO2$ が高インピーダンスネットワークに接続されるように構成される。トランジスタ $30_m$ のゲート端子は高インピーダンスの結節であるため、レジスタ $34_m$ およびキャパシタ $36_m$ を電流が流れることはない。したがって、キャパシタ $36_m$ に現れるサンプリングされた電圧が保持される。キャパシタ $36_m$ にまたがる電圧は、出力端子 $16_mO1$ と $16_mO2$ との間に現れる。MUX18(図1および2に図示する)は、出力端子 $16_mO1$ と出力端子 $16_mO2$ 間の電圧をADC20に伝達するように構成される。したがって、電力セル $24_m$ の電圧を表すサンプリングされた電圧はADC20に伝達される。

#### 【0069】

平衡化動作モードでは、スイッチング素子 $26_m$ をクローズするのに適切な制御電圧 $V26_m$ がスイッチング素子 $26_m$ の制御端子に印加され、スイッチング素子 $28_m$ をオープンするのに適切な制御電圧 $V28_m$ がスイッチング素子 $28_m$ の制御端子に印加される。したがって、キャパシタ $36_m$ はスイッチング素子 $26_m$ を通じて放電され、トランジスタ $30_m$ は導通状態になり、レジスタ $32_m$ およびトランジスタ $30_m$ を流れる平衡化電流によって電力セル $24_m$ が放電される。図3を参照して検討したように、スイッチング素子 $26_m$ は平衡化スイッチまたはスイッチと呼び得るし、スイッチング素子 $28_m$ はサンプリングスイッチまたはスイッチと呼び得る。

#### 【0070】

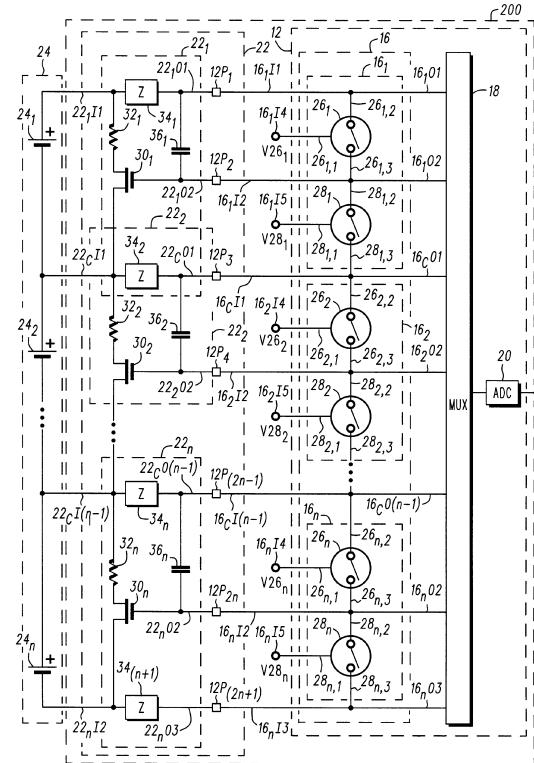

図8は、図1を参照して説明したように制御モジュール12およびフィルタ回路22を備え、図7を参照して説明したようにフィルタ回路 $22_m$ およびイスイッティングネットワーク $16_m$ の回路実装物の実施形態をさらに含む電力セルモニタおよび制御モジュール200のブロック図である。インターフェース回路16は、図4を参照して説明した。

#### 【0071】

フィルタ22は複数のフィルタ部分 $22_1$ 、 $22_2$ 、 $\dots$ 、 $22_n$ から成り、ここで、各フィルタ部分は、電力貯蔵装置24の対応する電力セル $24_1$ 、 $24_2$ 、 $\dots$ 、 $24_n$ に接続された入力端子と、インターフェースネットワーク16の対応する入力ピン $12P_1$ 、 $12P_2$ 、 $12P_3$ 、 $12P_4$ 、 $\dots$ 、 $12P_{(2n-1)}$ 、 $12P_{2n}$ 、 $12P_{(2n+1)}$ に接続される出力端子と、を含む。フィルタ部分 $22_1$ は、入力端子 $22_1I1$ および $22_cI1$ と、出力端子 $22_1O1$ 、 $22_1O2$ および $22_cO1$ と、を有し、フィルタ部分 $22_2$ は、入力端子 $22_cI1$ および $22_cI2$ と、出力端子 $22_cO1$ 、 $22_2O2$ および $22_cO2$ と、を有し、フィルタ部分 $22_n$ は、入力端子 $22_cI(n-1)$ および $22_cI2$ と、出力端子 $22_cO(n-1)$ 、 $22_nO2$ および $22_nO1$ と、を有する。

10

20

30

40

50

〇 3 と、を有する。フィルタ部分  $22_1$ 、 $22_2$ 、 $\dots$ 、 $22_n$  は図 4 を参照して説明した。加えて、図 8 の各フィルタ部分  $22_1$ 、 $22_2$ 、 $\dots$ 、 $22_n$  は、平衡化トランジスタおよび平衡化レジスタを含む。より具体的には、フィルタ部分  $22_1$  は、レジスタ  $32_1$  を介して入力端子  $22_1 I_1$  に接続されるドレン端子と、入力端子  $22_c I_1$  に接続されるソース端子と、出力端子  $22_1 O_2$  として機能するか、または代替的に、出力端子  $22_1 O_2$  に接続されるゲート端子と、を有するトランジスタ  $30_1$  を含む。レジスタ  $32_1$  およびインピーダンス  $34_1$  は各々が、一般的には一緒に接続されて、入力端子  $22_1 I_1$  に接続されるか、または代替的に、入力端子  $22_1 I_1$  を形成する結節を形成する端子を有する。レジスタ  $32_1$  の他方の端子はトランジスタ  $30_1$  のドレン端子に接続され、インピーダンス素子  $34_1$  の他方の端子はキャパシタ  $36_1$  の端子に接続されて、出力端子  $22_1 O_1$  として機能するか、または代替的に、出力端子  $22_1 O_1$  に接続される結節を形成する。キャパシタ  $36_1$  の他方の端子はトランジスタ  $30_1$  のゲート端子に接続され得るし、また、出力端子  $22_1 O_2$  に接続されるか、または代替的に、出力端子  $22_1 O_2$  として機能する結節を形成し得る。インピーダンス素子  $34_2$  は、トランジスタ  $30_1$  のソース端子に接続されて、入力端子  $22_c I_1$  に接続されるか、または代替的に、入力端子  $22_c I_1$  として機能する結節を形成する端子と、出力端子  $22_c O_1$  に接続されるか、または代替的に、出力端子  $22_c O_1$  として機能する端子と、を有する。インピーダンス素子  $34_2$  はフィルタ部分  $22_1$  および  $22_2$  に対して共通であることに留意されたい。

10

## 【0072】

フィルタ部分  $22_2$  は、レジスタ  $32_2$  を介して入力端子  $22_c I_1$  に接続されるドレン端子と、入力端子  $22_c I_2$  に接続されるソース端子と、出力端子  $22_2 O_2$  として機能するか、または代替的に、出力端子  $22_2 O_2$  に接続されるゲート端子と、を有するトランジスタ  $30_2$  を備える。レジスタ  $32_2$  およびインピーダンス素子  $34_2$  は各々が、一般的には一緒に接続されて、入力端子  $22_c I_1$  に接続される端子を有する。レジスタ  $32_2$  の他方の端子はトランジスタ  $30_2$  のドレン端子に接続され、レジスタ  $34_2$  の他方の端子はキャパシタ  $36_2$  の端子および出力端子  $22_c O_1$  に接続される。キャパシタ  $36_2$  の他方の端子は、トランジスタ  $30_2$  のゲート端子に接続され得る、また、出力端子  $22_2 O_2$  に接続されるか、または代替的に、出力端子  $22_2 O_2$  として機能する結節を形成する。類似の共有コンポーネントおよび接続部が、フィルタ部分  $22_1$  とフィルタ部分  $22_2$ との間に存在するように、フィルタ部分  $22_2$  とフィルタ部分  $22_3$  (図示せず)との間に存在することに留意されたい。明瞭さのために、フィルタ部分  $22_2$  の全てのコンポーネントが図示されているわけではない。

20

## 【0073】

フィルタ部分  $22_n$  は、レジスタ  $32_n$  を介して入力端子  $22_c I(n-1)$  に接続されるドレン端子と、入力端子  $22_n I_2$  に接続されるソース端子と、出力端子  $22_n O_2$  と、して機能するか、または代替的に、出力端子  $22_n O_2$  に接続されるゲート端子と、を有するトランジスタ  $30_n$  を備える。入力端子  $22_c I(n-1)$  は、インピーダンス素子  $34_n$  を介して出力端子  $22_c O(n=1)$  に接続される。レジスタ  $32_n$  およびインピーダンス素子  $34_n$  は各々が、一般的には一緒に入力端子  $22_c I(n-1)$  に接続される端子を有する。レジスタ  $32_n$  の他方の端子はトランジスタ  $30_n$  のドレン端子に接続され、インピーダンス素子  $34_n$  の他方の端子はキャパシタ  $36_n$  の端子に接続され、出力端子  $22_c O(n-1)$  として機能するか、または代替的に、出力端子  $22_c O(n-1)$  に接続され得る結節を形成し得る。出力端子  $22_c O(n-1)$  は入力ピン  $12P_{(2n-1)}$  に接続される。キャパシタ  $36_n$  の他方の端子はトランジスタ  $30_n$  のゲート端子に接続され、出力端子  $22_n O_2$  に接続され得るか、または代替的に、出力端子  $22_n O_2$  として機能する結節を形成し得る。インピーダンス素子  $34_{(n+1)}$  は、トランジスタ  $30_n$  のソース端子に接続されて、入力端子  $22_n I_2$  に接続され得るか、または代替的に、入力端子  $22_n I_2$  として機能する結節を形成する端子と、出力端子  $22_n O_3$  に接続され得るか、または代替的に、出力端子  $22_n O_3$  として機能する端子

30

と、を有する。

【0074】

引き続き図8を参照すると、スイッチング部分 $16_1$ 、 $16_2$ 、 $\dots$ 、 $16_n$ から成るインタフェースネットワーク $16$ は、フィルタリング継続観察モード、サンプルアンドホールドモードおよび平衡化モードを含む少なくとも3つの互いに異なる動作モードで動作する。インタフェース回路 $16$ の動作モードは、図7を参照して説明した。

【0075】

図9は、本発明の別の実施形態によれば、フィルタ部分 $22_m$ を介して電力セル $24_m$ に接続されるインタフェースネットワーク $16$ （図1および2を参照して説明した）のスイッチング部分 $16_m$ の回路図である。図1のスイッチングネットワーク $16_1$ 、 $16_2$ 、 $\dots$ 、 $16_n$ が、スイッチング部分 $16_m$ から成り、かつ変数 $m$ が、整数 $1$ 、 $2$ 、 $\dots$ 、 $n$ を表すために用いられることに留意されたい。例えば、スイッチングネットワーク $16_1$ はスイッチング部分 $16_m$ に対応するが、ここで、 $m$ は、 $1$ に置き換えられ、スイッチングネットワーク $16_2$ はスイッチング部分 $16_m$ に対応するが、ここで、 $m$ は、 $2$ に置き換えられ、スイッチングネットワーク $16_n$ はスイッチング部分 $16_m$ に対応するが、ここで、 $m$ は、 $n$ に置き換えられる。図9のスイッチング部分 $16_m$ は図7のスイッチング部分 $16_m$ に類似しているが、キャパシタ $36_m$ の端子の内の1つが入力ピン $12P_{(2m-1)}$ に接続されていない点だけが異なる。このように、キャパシタ $36_m$ は、入力ピン $12P_{2m}$ に接続された端子を有するが、その他の端子は図10に示すように別の回路と共有されている。図3を参照して検討したように、スイッチング素子 $26_m$ は、平衡化スイッチまたは平衡化スイッチング素子と呼ばれ、スイッチ $28_m$ は、サンプリングスイッチまたはサンプリングスイッチング素子と呼ばれ得る。

【0076】

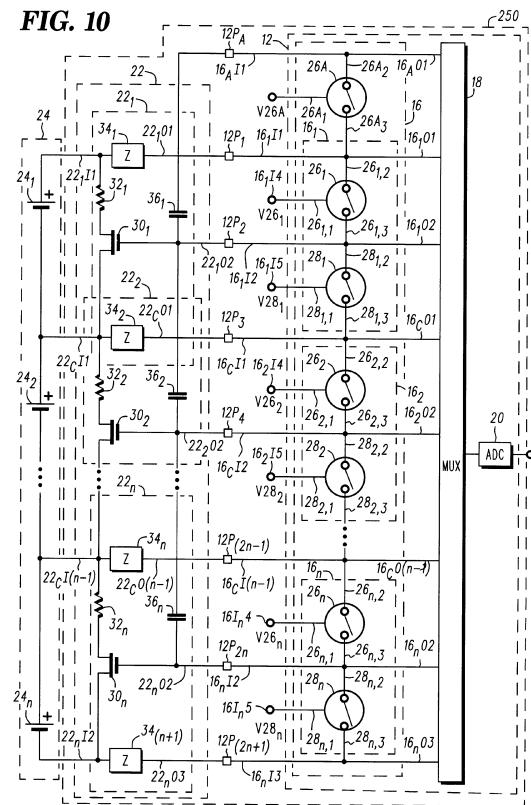

図10は、図6を参照して説明したように制御モジュール $12$ およびインタフェースネットワーク $16$ を備え、図9を参照して説明したフィルタ回路 $22$ およびインタフェース回路 $16$ の回路実装物の実施形態をさらに含む電力セルモニタおよび回路モジュール $250$ のブロック図である。制御モジュール $250$ はバッテリ装置 $24$ に接続される。制御モジュール $250$ は図6の制御モジュール $150$ に類似しているが、フィルタ回路 $22$ がトランジスタ $30_1$ 、 $\dots$ 、 $30_n$ およびインピーダンス素子 $32_1$ 、 $\dots$ 、 $32_n$ 等の平衡化素子をさらに含む点だけが異なる。より具体的には、フィルタ部分 $22_1$ は、レジスタ $32_1$ を介して入力端子 $22_1I1$ に接続されるドレイン端子と、入力端子 $22_cI1$ に接続されるソース端子と、出力端子 $22_1O2$ として機能するか、または代替的に、出力端子 $22_1O2$ に接続されるゲート端子と、を有するトランジスタ $30_1$ を含む。レジスタ $32_1$ およびインピーダンス $34_1$ は各々が、一般的には一緒に接続されて、入力端子 $22_1I1$ に接続されるか、または代替的に、入力端子 $22_1I1$ を形成する結節を形成する端子を有する。レジスタ $32_1$ の他方の端子はトランジスタ $30_1$ のドレイン端子に接続され、インピーダンス素子 $34_1$ の他方の端子は、出力端子 $22_1O1$ として機能するか、または代替的に、出力端子 $22_1O1$ に接続され得るが、この出力端子は入力ピン $12P_1$ に接続される。キャパシタ $36_1$ の1つの端子は入力ピン $12P_A$ に接続される。キャパシタ $36_1$ の他方の端子はトランジスタ $30_1$ のゲート端子に接続され、また、出力端子 $22_1O2$ に接続されるか、または代替的に、出力端子 $22_1O2$ として機能する結節を形成する。キャパシタ $36_1$ のこの端子および出力端子 $22_1O2$ は、入力ピン $12P_2$ に接続される。インピーダンス素子 $34_2$ は、トランジスタ $30_1$ のソース端子に接続されて、入力端子 $22_cI1$ に接続され得るか、または代替的に、入力端子 $22_cI1$ として機能する結節を形成する端子と、出力端子 $22_cO1$ に接続され得るか、または代替的に、出力端子 $22_cO1$ として機能する端子と、を有する。インピーダンス素子 $34_2$ はフィルタ部分 $22_1$ および $22_2$ に対して共通であることに留意されたい。

【0077】

フィルタ部分 $22_2$ は、レジスタ $32_2$ を介して入力端子 $22_1I1$ に接続されるドレ

10

20

30

40

50

イン端子と、入力端子  $22_c I_2$  に接続されるソース端子と、出力端子  $22_2 O_2$  として機能するか、または代替的に、出力端子  $22_2 O_2$  に接続されるゲート端子と、を有するトランジスタ  $30_2$  を含む。レジスタ  $32_2$  およびインピーダンス  $34_2$  は各々が、一般的には一緒に接続されて、入力端子  $22_c I_1$  に接続される端子を有する。レジスタ  $32_2$  の他方の端子はトランジスタ  $30_2$  のドレイン端子に接続され、インピーダンス素子  $34_2$  の他方の端子は、出力端子  $22_c O_1$  として機能するか、または代替的に、出力端子  $22_c O_1$  に接続され得るが、この出力端子は入力ピン  $12P_3$  に接続される。キャパシタ  $36_2$  の 1 つの端子は、トランジスタ  $30_1$  のゲート、キャパシタ  $36_1$  の端子および入力ピン  $12P_2$  に接続される。キャパシタ  $36_2$  の他方の端子はトランジスタ  $30_2$  のゲート端子に接続され、また、出力端子  $22_2 O_2$  に接続され得るか、または代替的に、出力端子  $22_2 O_2$  として機能する結節を形成するが、この出力部は入力ピン  $12P_4$  に接続される。類似の共有コンポーネントおよび接続部が、フィルタ部分  $22_1$  とフィルタ部分  $22_2$  との間に存在するように、フィルタ部分  $22_2$  とフィルタ部分  $22_3$  (図示せず) との間に存在することに留意されたい。明瞭さのために、フィルタ部分  $22_2$  の全てのコンポーネントが図示されているわけではない。10

#### 【0078】

フィルタ部分  $22_n$  は、レジスタ  $32_n$  を介して入力端子  $22_c I(n-1)$  に接続されるドレイン端子と、入力端子  $22_n I_2$  に接続されるソース端子と、入力ピン  $12P_2$  に接続される出力端子  $22_n O_2$  として機能するか、または代替的に、出力端子  $22_n O_2$  に接続され得るゲート端子と、を有するトランジスタ  $30_n$  を備える。インピーダンス素子  $34_n$  は、トランジスタのソース端子に接続されて、入力端子  $22_c I(n-1)$  に接続され得るか、または代替的に、入力端子  $22_c I(n-1)$  として機能する結節を形成する端子と、出力端子  $22_c O(n-1)$  に接続され得るか、または代替的に、入力端子  $22_c O(n-1)$  として機能する端子と、を有する。出力端子  $22_c O(n-1)$  は入力ピン  $12P_{(2n-1)}$  に接続される。レジスタ  $32_n$  およびインピーダンス素子  $34_n$  は各々が、一般的には一緒に接続されて、入力端子  $22_c I(n-1)$  に接続される端子を有する。レジスタ  $32_n$  の他方の端子はトランジスタ  $30_n$  のドレイン端子に接続され、インピーダンス素子  $34_n$  の他方の端子は、出力端子  $22_c O(n-1)$  として機能し得るか、または代替的に、出力端子  $22_c O(n-1)$  に接続され得る。キャパシタ  $36_n$  の他方の端子は、トランジスタ  $30_n$  のゲート端子に接続され、出力端子  $22_n O_2$  に接続され得るか、または代替的に、出力端子  $22_n O_2$  として機能する結節を形成する。インピーダンス素子  $34_{(n+1)}$  は、トランジスタ  $30_n$  のソース端子に接続されて、入力端子  $22_n I_2$  に接続され得るか、または代替的に、入力端子  $22_n I_2$  として機能する結節を形成する端子と、入力ピン  $12P_{(2n+1)}$  に接続される出力端子  $22_n O_3$  に接続され得るか、または代替的に、出力端子  $22_n O_3$  として機能する端子と、を有する。30

#### 【0079】

別の実施形態によれば、セルの極性は、これらのセルが図に示す反対の極性となるように切り替えられる。あるいは、 $n$  チャネルトランジスタを  $p$  チャネルトランジスタと置き換えることが可能である。40

#### 【0080】

制御モジュール  $250$  の動作は、平衡化動作モードを例外として、制御モジュール  $150$  (図 6) の動作に類似している。デフォルトの動作モードがフィルタリングされた継続観察モードであり、これによって、スイッチング素子  $26A$ 、 $28_1$ 、 $\dots$ 、 $28_n$  がクローズされ、スイッチング素子  $26_1$ 、 $\dots$ 、 $26_n$  が開いていると仮定すると、電力セル  $24_1$  にまたがる電圧は、スイッチング素子  $26_1$  の制御電圧に印加し、スイッチング素子  $28_1$  をオープンするのに適切な制御電圧  $V28_1$  をスイッチング素子  $26_1$  の制御電圧に印加することによって平衡化することが可能である。したがって、トランジスタ  $30_1$  は導通状態になり、レジスタ  $32_1$  およびトランジスタ  $30_1$  を流れる平衡化電流によって、電力50

セル24<sub>1</sub>は放電される。

【0081】

その他の電力セルにまたがる電圧は、同様の方法を用いることによって平衡化させることが可能であることに留意されたい。

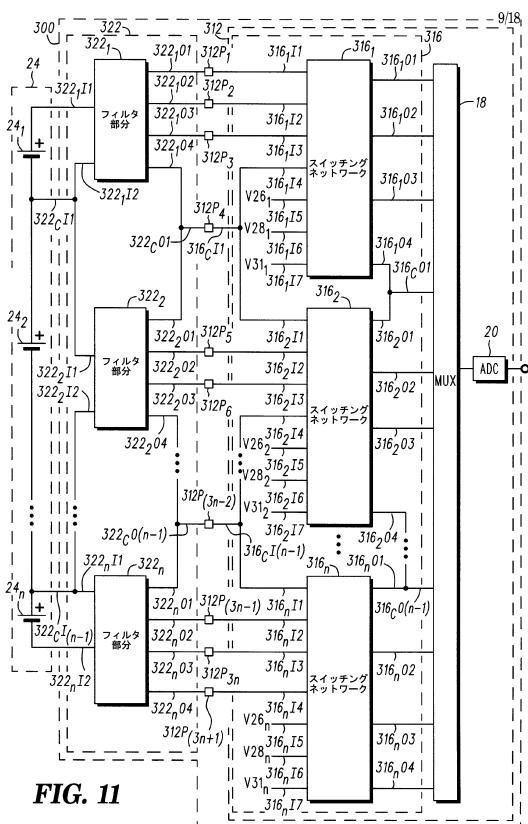

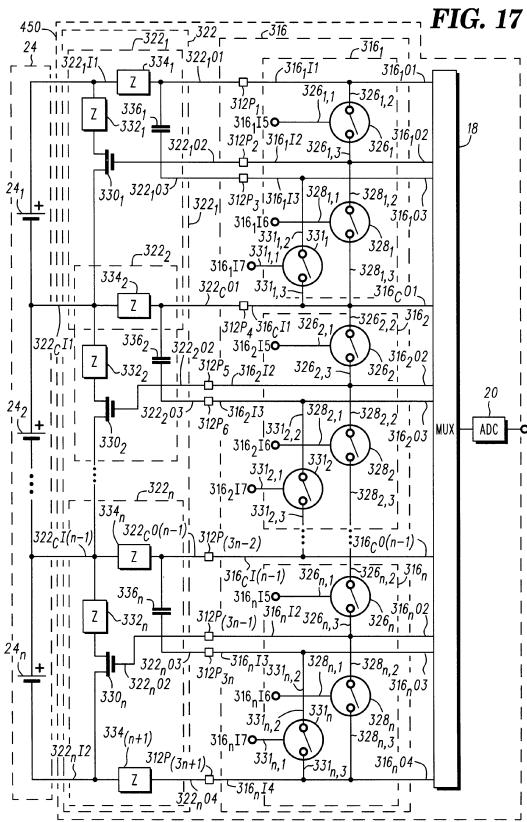

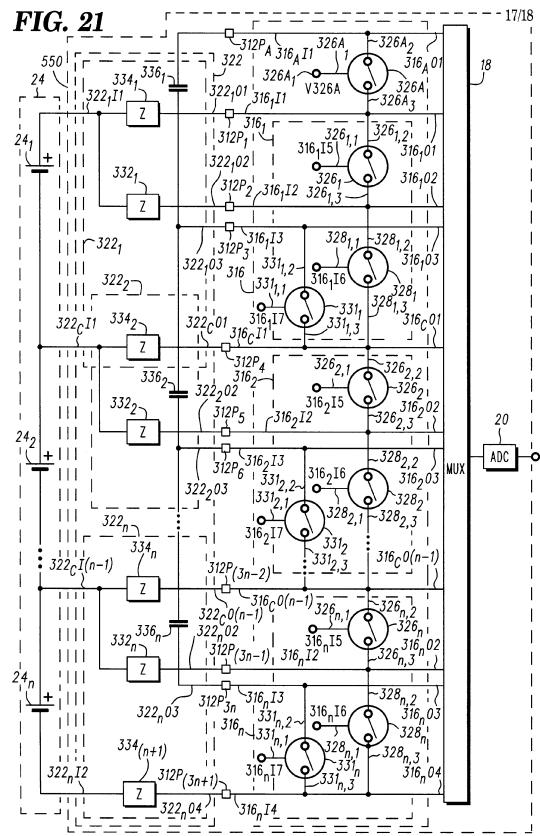

【0082】

図11は、本発明の実施形態による、フィルタ回路322に接続される制御モジュール312を備える電力セルモニタおよび制御回路300のブロック図である。電力セルモニタおよび制御回路300は、電力貯蔵装置24に接続される。制御モジュール312は、制御モジュール312の入力部に接続されるか、または代替的に、制御モジュール312の入力部として機能する入力部と、アナログツーデジタルコンバータ(ADC)20に接続される出力を有するマルチプレクサ(MUX)18の入力部に接続される出力部と、を有するインターフェースネットワーク316を含む。電力貯蔵装置24は、それぞれ、制御回路300の対応するフィルタ部分322<sub>1</sub>、322<sub>2</sub>、…、322<sub>n</sub>に接続される複数の電力セルまたはバッテリ24<sub>1</sub>、24<sub>2</sub>、…、24<sub>n</sub>から成り得る。あるいは、電力貯蔵装置は、キャパシタ、燃料セル等から成り得る。インターフェースネットワーク316は、複数のスイッティングネットワーク316<sub>1</sub>、316<sub>2</sub>、…、316<sub>n</sub>から成り得、ここで、スイッティングネットワーク316<sub>1</sub>は、入力端子316<sub>1</sub>I1、316<sub>1</sub>I2、316<sub>1</sub>I3、316<sub>1</sub>I4、316<sub>1</sub>I5、316<sub>1</sub>I6および316<sub>1</sub>I7と、出力端子316<sub>1</sub>O1、316<sub>1</sub>O2、316<sub>1</sub>O3および316<sub>1</sub>O4と、を有し、スイッティング素子316<sub>2</sub>は、入力端子316<sub>2</sub>I1、316<sub>2</sub>I2、316<sub>2</sub>I3、316<sub>2</sub>I4、316<sub>2</sub>I5、316<sub>2</sub>I6および316<sub>2</sub>I7と、出力端子316<sub>2</sub>O1、316<sub>2</sub>O2、316<sub>2</sub>O3および316<sub>2</sub>O4と、を有し、スイッティング素子316<sub>n</sub>は、入力端子316<sub>n</sub>I1、316<sub>n</sub>I2、316<sub>n</sub>I3、316<sub>n</sub>I4、316<sub>n</sub>I5、316<sub>n</sub>I6および316<sub>n</sub>I7と、出力端子316<sub>n</sub>O1、316<sub>n</sub>O2、316<sub>n</sub>O3および316<sub>n</sub>O4と、を有する。別の実施形態によれば、入力端子316<sub>1</sub>I4は入力端子316<sub>2</sub>I1に接続されて入力端子316<sub>c</sub>I1を形成し、入力端子316<sub>(n-1)</sub>I4は入力端子316<sub>n</sub>I1に接続されて入力端子316<sub>c</sub>I(n-1)を形成し、出力端子316<sub>1</sub>O4は出力端子316<sub>2</sub>O1に接続されて出力端子316<sub>c</sub>O1を形成し、出力端子316<sub>(n-1)</sub>O4は出力端子316<sub>n</sub>O1に接続されて出力端子316<sub>c</sub>O(n-1)を形成する。

【0083】

別の実施形態では、制御モジュール312は、入力ピンまたは入力リード線312P<sub>1</sub>、312P<sub>2</sub>、312P<sub>3</sub>、312P<sub>4</sub>、312P<sub>5</sub>、312P<sub>6</sub>、…、312P<sub>(3n-2)</sub>、312P<sub>(3n-1)</sub>、312P<sub>3n</sub>および312P<sub>(3n+1)</sub>を有する半導体パッケージ中のモノリシック集積された半導体デバイスであり、ここで、nは、整数を表す。例えば、入力端子316<sub>1</sub>I1、316<sub>1</sub>I2、316<sub>1</sub>I3、316<sub>c</sub>I1、316<sub>2</sub>I2、316<sub>2</sub>I3、…、316<sub>c</sub>I(n-1)、316<sub>n</sub>I2、316<sub>n</sub>I3および316<sub>n</sub>I4は、それぞれ、入力ピン312P<sub>1</sub>、312P<sub>2</sub>、312P<sub>3</sub>、312P<sub>4</sub>、312P<sub>5</sub>、312P<sub>6</sub>、…、312P<sub>(3n-2)</sub>、312P<sub>(3n-1)</sub>、312P<sub>3n</sub>および312P<sub>(3n+1)</sub>に接続される。入力端子316<sub>1</sub>I1、316<sub>1</sub>I2、316<sub>1</sub>I3、316<sub>c</sub>I1、316<sub>2</sub>I2、316<sub>2</sub>I3、…、316<sub>c</sub>I(n-1)、316<sub>n</sub>I2、316<sub>n</sub>I3および316<sub>n</sub>I4は、それぞれ、入力ピン312P<sub>1</sub>、312P<sub>2</sub>、312P<sub>3</sub>、312P<sub>4</sub>、312P<sub>5</sub>、312P<sub>6</sub>、…、312P<sub>(3n-2)</sub>、312P<sub>(3n-1)</sub>、312P<sub>3n</sub>および312P<sub>(3n+1)</sub>に直接に接続されていることが図示されているが、これは本発明の制限ではなく、例えば、入力端子316<sub>1</sub>I1、316<sub>1</sub>I2、316<sub>1</sub>I3、316<sub>c</sub>I1、316<sub>2</sub>I2、316<sub>2</sub>I3、…、316<sub>c</sub>I(n-1)、316<sub>n</sub>I2、316<sub>n</sub>I3および316<sub>n</sub>I4を他の回路素子を介して、それぞれ、入力ピン312P<sub>1</sub>、312P<sub>2</sub>、312P<sub>3</sub>、312P<sub>4</sub>、312P<sub>5</sub>、312P<sub>6</sub>、…、312P<sub>(3n-2)</sub>、312P<sub>(3n-1)</sub>、312P<sub>3n</sub>および312P<sub>(3n+1)</sub>に接続することが

可能である。

【0084】

別の実施形態によれば、制御モジュール312と、にフィルタ部分322またはフィルタ部分322の一部と、は、モノリシック集積されて、集積された半導体デバイスを形成する。このフィルタを部分的に集積した例を図22に示す。制御モジュール312と、フィルタ部分322またはフィルタ部分322の一部と、がモノリシック集積された実施形態では、入力ピン312P<sub>1</sub>、312P<sub>2</sub>、312P<sub>3</sub>、312P<sub>4</sub>、312P<sub>5</sub>、312P<sub>6</sub>、・・・、312P<sub>(3n-2)</sub>、312P<sub>(3n-1)</sub>、312P<sub>3n</sub>および312P<sub>(3n+1)</sub>は存在しない。

【0085】

10

スイッチングネットワーク316<sub>1</sub>の入力端子316<sub>1</sub>I5、316<sub>1</sub>I6および316<sub>1</sub>I7は、それぞれ、制御信号V26<sub>1</sub>、V28<sub>1</sub>およびV31<sub>1</sub>を受信するように結合されており、スイッチングネットワーク316<sub>2</sub>の入力端子316<sub>2</sub>I5、316<sub>2</sub>I6および316<sub>2</sub>I7は、それぞれ、制御信号V26<sub>2</sub>、V28<sub>2</sub>およびV31<sub>2</sub>を受信するように結合されており、スイッチングネットワーク316<sub>n</sub>の入力端子316<sub>n</sub>I5、316<sub>n</sub>I6および316<sub>n</sub>I7は、それぞれ、制御信号V26<sub>n</sub>、V28<sub>n</sub>およびV31<sub>n</sub>を受信するように結合される。

【0086】

スイッチングネットワーク316<sub>1</sub>、・・・、316<sub>n</sub>の出力端子316<sub>1</sub>O1、316<sub>1</sub>O2、316<sub>1</sub>O3、316<sub>c</sub>O1、316<sub>2</sub>O2、316<sub>2</sub>O3、316<sub>c</sub>O(n-1)、316<sub>n</sub>O2、316<sub>n</sub>O3および316<sub>n</sub>O4は、MUX18の対応する入力端子に接続される。

20

【0087】

フィルタ322は複数のフィルタ部分322<sub>1</sub>、322<sub>2</sub>、・・・、322<sub>n</sub>から成り、ここで、各フィルタ部分は、電力貯蔵装置24の対応する電力セルに接続された入力端子と、インターフェースネットワーク316の対応する入力ピンに接続された出力端子と、を含む。フィルタ部分322<sub>1</sub>は、入力端子322<sub>1</sub>I1および322<sub>1</sub>I2と、出力端子322<sub>1</sub>O1、322<sub>1</sub>O2、322<sub>1</sub>O3および322<sub>1</sub>O4と、を有し、フィルタ部分322<sub>2</sub>は、入力端子322<sub>2</sub>I1および322<sub>2</sub>I2と、出力端子322<sub>2</sub>O1、322<sub>2</sub>O2、322<sub>2</sub>O3および322<sub>2</sub>O4と、を有し、フィルタ部分322<sub>n</sub>は、入力端子322<sub>n</sub>I1および322<sub>n</sub>I2と出力端子322<sub>n</sub>O1、322<sub>n</sub>O2、322<sub>n</sub>O3および322<sub>n</sub>O4と、を有する。ある実施形態によれば、入力端子322<sub>1</sub>I2は入力端子322<sub>2</sub>I1に接続されて入力端子322<sub>c</sub>I1を形成し、入力端子322<sub>(n-1)</sub>I2は入力端子322<sub>n</sub>I1に接続されて入力端子322<sub>c</sub>I(n-1)を形成し得る。出力端子322<sub>(n-1)</sub>O4は出力端子322<sub>2</sub>O1に接続されて出力端子322<sub>c</sub>O1を形成し、出力端子322<sub>2</sub>O4は出力端子322<sub>n</sub>O1に接続されて出力端子322<sub>c</sub>O(n-1)を形成し得る。制御モジュール312がモノリシック集積された半導体デバイスであり、フィルタ322が個別の回路素子から形成される実施形態では、出力端子322<sub>1</sub>O1は入力ピン312P<sub>1</sub>に接続され、出力端子322<sub>1</sub>O2は入力ピン312P<sub>2</sub>に接続され、出力端子322<sub>1</sub>O3は入力ピン312P<sub>3</sub>に接続され、出力端子322<sub>c</sub>O1は入力ピン312P<sub>4</sub>に接続され、出力端子322<sub>2</sub>O2は入力ピン312P<sub>5</sub>に接続され；出力端子322<sub>2</sub>O3は入力ピン312P<sub>6</sub>に接続され、出力端子322<sub>c</sub>O(n-1)は入力ピン312P<sub>(3n-2)</sub>に接続され；出力端子322<sub>n</sub>O2は入力ピン312P<sub>(3n-1)</sub>に接続され；出力端子322<sub>n</sub>O3は入力ピン312P<sub>3n</sub>に接続され、出力端子322<sub>n</sub>O4は入力ピン312P<sub>(3n+1)</sub>に接続される。

30

【0088】

入力端子322<sub>1</sub>I1は電力セル24<sub>1</sub>の正極に接続され、入力端子322<sub>c</sub>I1は、それぞれ、電力セル24<sub>1</sub>および24<sub>2</sub>の負極および正極に接続される。入力端子322<sub>c</sub>I(n-1)は、電力セル24<sub>n</sub>の正極に接続され、入力端子322<sub>n</sub>I2は電力セル

40

50

24<sub>n</sub> の負極に接続される。

【0089】

添字「n」は整数を表すことに留意されたい。さらに、スイッチングネットワーク316<sub>1</sub>、316<sub>2</sub>、・・・、316<sub>n</sub>、フィルタ部分322<sub>1</sub>、322<sub>2</sub>、・・・、322<sub>n</sub>および電力セル24<sub>1</sub>、24<sub>2</sub>、・・・、24<sub>n</sub>の個数は、本発明の制限ではないことに留意されたい。

【0090】

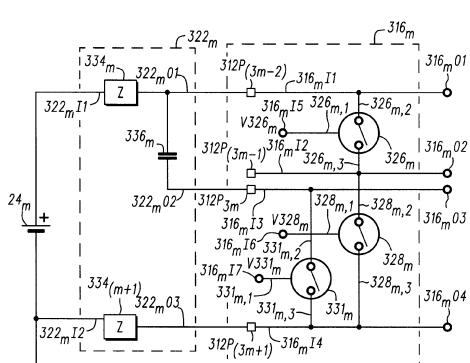

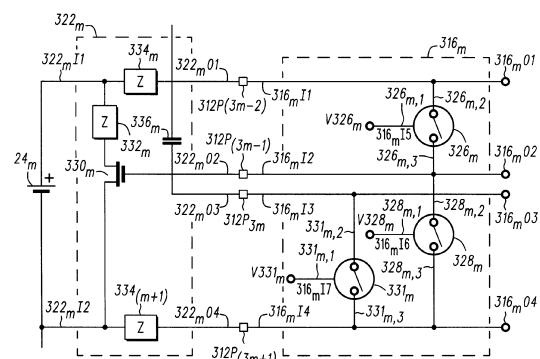

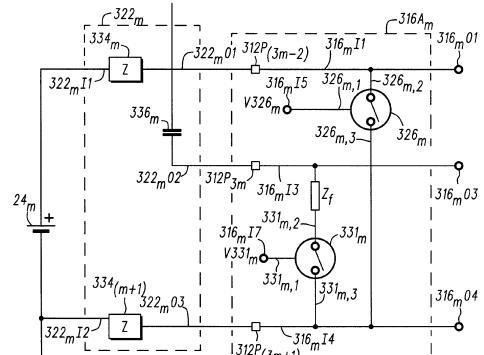

図12は、本発明の別の実施形態に従う、フィルタ部分322<sub>m</sub>を介して電力セル24<sub>m</sub>に接続されるインタフェースネットワーク316（図11を参照して説明した）のスイッチング部分316<sub>m</sub>の回路図である。図11のスイッチングネットワーク316<sub>1</sub>、316<sub>2</sub>、・・・、316<sub>n</sub>が、スイッチング部分316<sub>m</sub>から成り、変数mが、整数1、2、・・・、nを表すために用いられることに留意されたい。例えば、スイッチングネットワーク316<sub>1</sub>はスイッチング部分316<sub>m</sub>に対応するが、ここで、mは、1に置き換えられ、スイッチングネットワーク316<sub>2</sub>はスイッチング部分316<sub>m</sub>に対応するが、ここで、mは、2に置き換えられ、スイッチングネットワーク316<sub>n</sub>はスイッチング部分316<sub>m</sub>に対応するが、ここで、mは、nに置き換えられる。

【0091】

スイッチング部分316<sub>m</sub>は、スイッチング素子326<sub>m</sub>、328<sub>m</sub>および331<sub>m</sub>を備えるが、ここで、各スイッチング素子326<sub>m</sub>、328<sub>m</sub>および331<sub>m</sub>は、制御端子および1対の導電端子を含む。より具体的には、スイッチング素子326<sub>m</sub>は、制御端子326<sub>m</sub>、<sub>1</sub>、導電端子326<sub>m</sub>、<sub>2</sub>および導電端子326<sub>m</sub>、<sub>3</sub>を有する。導電端子326<sub>m</sub>、<sub>2</sub>は、端子316<sub>m</sub>I1および316<sub>m</sub>O1に接続され、または代替的に、端子316<sub>m</sub>I1および316<sub>m</sub>O1は入／出力端子を形成し得る。スイッチング素子328<sub>m</sub>は、制御端子328<sub>m</sub>、<sub>1</sub>、導電端子328<sub>m</sub>、<sub>2</sub>および導電端子328<sub>m</sub>、<sub>3</sub>を有する。導電端子328<sub>m</sub>、<sub>2</sub>は、導電端子326<sub>m</sub>、<sub>3</sub>と、端子316<sub>m</sub>I2および316<sub>m</sub>O2と、に接続される。導電端子328<sub>m</sub>、<sub>3</sub>は、入力端子316<sub>m</sub>I4および出力端子316<sub>m</sub>O4に接続される。導電端子328<sub>m</sub>、<sub>3</sub>は、端子316<sub>m</sub>I4および316<sub>m</sub>O4に接続されるか、または代替的に、端子316<sub>m</sub>I4および316<sub>m</sub>O4が入／出力端子を形成し得る。導電端子331<sub>m</sub>、<sub>2</sub>は、入力端子316<sub>m</sub>I3および出力端子316<sub>m</sub>O3に接続される。端子326<sub>m</sub>、<sub>1</sub>、328<sub>m</sub>、<sub>1</sub>、および331<sub>m</sub>、<sub>1</sub>は、それぞれ、図11の端子316<sub>n</sub>I5、316<sub>n</sub>I6、および316<sub>n</sub>I7に対応することに留意されたい。スイッチング素子331<sub>m</sub>はサンプリングスイッチと呼ばれ、スイッチング素子328<sub>m</sub>および326<sub>m</sub>は平衡化スイッチまたは電流制御スイッチと呼ばれ得る。

【0092】

フィルタ部分322<sub>m</sub>は、入力端子322<sub>m</sub>I1に接続されるか、または代替的に、入力端子322<sub>m</sub>I1として機能する端子と、出力端子322<sub>m</sub>O1に接続されるか、または代替的に、出力端子322<sub>m</sub>O1として機能する端子と、を有するインピーダンス素子334<sub>m</sub>を備える。出力端子322<sub>m</sub>O1は、エネルギー貯蔵素子336<sub>m</sub>を介して出力端子322<sub>m</sub>O2に接続され得る。入力端子322<sub>m</sub>I2は、インピーダンス素子334<sub>(m+1)</sub>を介して出力端子322<sub>m</sub>O3に接続され得る。例えば、インピーダンス素子334<sub>m</sub>および334<sub>(m+1)</sub>はレジスタであり、エネルギー貯蔵素子336<sub>m</sub>はキャパシタである。スイッチング部分316<sub>m</sub>がモノリシック集積された半導体デバイスまたはモノリシック集積された半導体デバイスの一部であり、回路素子334<sub>m</sub>、334<sub>(m+1)</sub>および336<sub>m</sub>が個別の回路素子である実施形態では、回路素子334<sub>m</sub>、336<sub>m</sub>および334<sub>(m+1)</sub>は、入力ピン312P<sub>(3m-2)</sub>、312P<sub>3m</sub>および312P<sub>(3m+1)</sub>を介してスイッチング部分316<sub>m</sub>に接続される、すなわち、出力端子322<sub>m</sub>O1は入力ピン312P<sub>(3m-2)</sub>に接続され、出力端子322<sub>m</sub>O2は入力ピン312P<sub>3m</sub>に接続され、出力端子322<sub>m</sub>O3は入力ピン312P<sub>(3m+1)</sub>に接続される。入力ピン312P<sub>(3m-1)</sub>は、別の回路素子には接続されないことがあ

10

20

30

40

50

る。別の実施形態では、フィルタが部分的にまたは完全にモノリシックに集積されており、それに従って出力ピンが変化する。インピーダンス素子はレジスタであることに限られないため、これらは記号Zで識別される、すなわち、他のタイプのインピーダンス素子であり得ることになる。

【0093】

電力セル24<sub>m</sub>は、フィルタ部分22<sub>m</sub>の入力端子322<sub>m</sub>I1に接続された正極と、フィルタ部分322<sub>m</sub>の入力端子322<sub>m</sub>I2に接続された負極と、を有するバッテリセルを備える。

【0094】

出力端子322<sub>m</sub>O1は入力ピン312P<sub>(3m-2)</sub>を介して入力端子316<sub>m</sub>I1に電気的に接続され、出力端子322<sub>m</sub>O2は入力ピン312P<sub>3m</sub>を介して入力端子316<sub>m</sub>I3に電気的に接続され、出力端子322<sub>m</sub>O3は入力ピン312P<sub>(3m+1)</sub>を介して入力端子316<sub>m</sub>I4に電気的に接続されることに留意されたい。10

【0095】

引き続き図12を参照すると、スイッチング部分316<sub>m</sub>は、フィルタリング継続観察モード、サンプルアンドホールドモードおよび平衡化モードを含む少なくとも3つの互いに異なる動作モードで動作する。フィルタリング継続観察動作モードでは、電力セル24<sub>m</sub>にまたがる電圧は、これらのスイッチング素子の開放に好適な制御電圧V326<sub>m</sub>およびV328<sub>m</sub>を、それぞれ、スイッチング素子326<sub>m</sub>および328<sub>m</sub>の制御端子に印加し、このスイッチング素子の閉鎖に好適な制御電圧V331<sub>m</sub>をスイッチング素子331<sub>m</sub>の制御端子に印加することによって監視される。したがって、電力セル24<sub>m</sub>にまたがる電圧は、出力端子316<sub>m</sub>O1と316<sub>m</sub>O3間に出力される。MUX18(図11に示す)は、出力端子316<sub>m</sub>O1と316<sub>m</sub>O3間に電圧をADCコンバータ20に伝達するように構成される。したがって、電力セル24<sub>m</sub>のフィルタリングされた電圧を表す電圧がADC20に伝達され、これによって電力セル24<sub>m</sub>にまたがる電圧を観察または監視する。20

【0096】

サンプルアンドホールド動作モードでは、電力セル24<sub>m</sub>にまたがる電圧は、これらのスイッチング素子の開放に好適な制御電圧V326<sub>m</sub>およびV328<sub>m</sub>を、それぞれ、スイッチング素子326<sub>m</sub>および328<sub>m</sub>の制御端子に印加し、このスイッチング素子の閉鎖に好適な制御電圧V331<sub>m</sub>をスイッチング素子331<sub>m</sub>の制御端子に印加することによってサンプリングして記憶または保持することが可能である。キャパシタ336<sub>m</sub>は、電力セル24<sub>m</sub>にまたがる電圧に実質的に等しい電圧に充電される、すなわち、キャパシタ336<sub>m</sub>は電力セル24<sub>m</sub>の電圧をサンプリングする。30

【0097】

電力セル24<sub>m</sub>の電圧をサンプリングした後、スイッチング素子331<sub>m</sub>をオープンするのに適した制御電圧V331<sub>m</sub>がスイッチング素子331<sub>m</sub>の制御端子に印加されるが、スイッチング素子331<sub>m</sub>を開放構成に維持するのに適切な制御電圧V326<sub>m</sub>およびV328<sub>m</sub>は、スイッチング素子326<sub>m</sub>および328<sub>m</sub>の制御端子に維持される。したがって、キャパシタ336<sub>m</sub>に現れるサンプリングされた電圧が保持されて、出力端子316<sub>m</sub>O1と316<sub>m</sub>O3間に現れる。MUX18は、出力端子316<sub>m</sub>O1と316<sub>m</sub>O3間に電圧をADC20に伝達するように構成される。したがって、電力セル24<sub>m</sub>のサンプルアンドホールド電圧を表すサンプリングされた電圧が、ADC20に伝達される。40

【0098】

平衡化動作モードでは、電力セル24<sub>m</sub>にまたがる電圧は、スイッチング素子326<sub>m</sub>および328<sub>m</sub>の閉鎖に好適な制御電圧V326<sub>m</sub>およびV328<sub>m</sub>を、それぞれ、スイッチング素子326<sub>m</sub>および328<sub>m</sub>の制御端子に印加することによって平衡化することが可能である。したがって、インピーダンス素子334<sub>m</sub>、スイッチング素子326<sub>m</sub>、スイッチング素子328<sub>m</sub>およびインピーダンス素子334<sub>(m+1)</sub>を通過する平衡化50

電流によって、電力セル $24_m$ が放電される。図3のスイッチング素子 $26_m$ および $28_m$ と同様に、スイッチング素子 $326_m$ は平衡化スイッチング素子または平衡化スイッチと呼ばれ、スイッチング素子 $331_m$ はサンプリングスイッチング素子またはサンプリングスイッチと呼ばれ得る。

#### 【0099】

スイッチング素子 $328_m$ はオプション素子であり、スイッチング素子 $328_m$ が存在しない実施形態によれば、出力端子 $316_mO2$ は出力端子 $316_mO4$ に短絡されることに留意されたい。

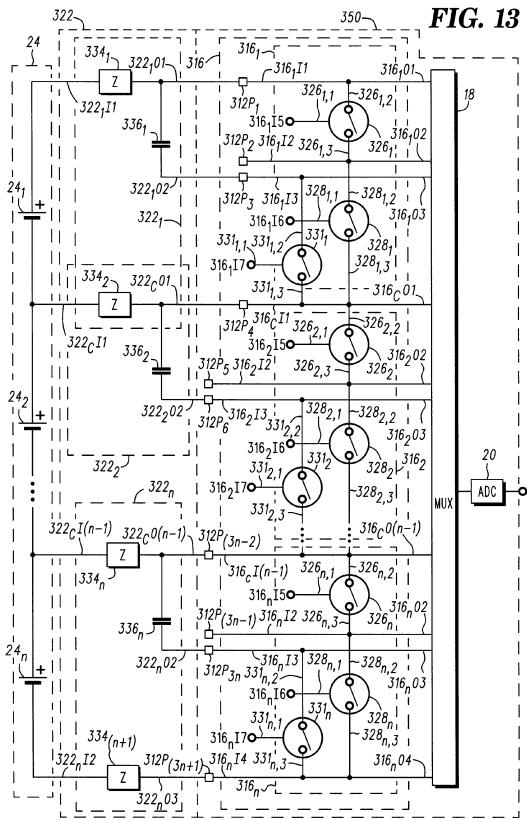

#### 【0100】

図13は、図11を参照して説明したように制御モジュール312およびフィルタ回路322を備え、図12を参照して説明したフィルタ回路322およびインターフェース回路316の回路実装物の実施形態をさらに含む電力セルモニタおよび制御回路350のブロック図である。図11の実施形態と同様に、図13に示すインターフェースネットワーク316のスイッチングネットワーク $316_1$ 、 $316_2$ 、 $\dots$ 、 $316_n$ は、スイッチング部分 $316_m$ から成り、変数 $m$ は、図12を参照して説明されるように、整数1、2、 $\dots$ 、 $n$ を表すために用いられる。例えば、スイッチングネットワーク $316_1$ はスイッチング部分 $316_m$ に対応し、ここで、 $m$ は、1で置き換えられ、スイッチングネットワーク $316_2$ はスイッチング部分 $316_m$ に対応し、ここで、 $m$ は、2で置き換えられ、スイッチングネットワーク $316_n$ はスイッチング部分 $316_m$ に対応し、ここで、 $m$ は、 $n$ で置き換えられる。

10

20

#### 【0101】

制御回路350はバッテリ装置24に接続される。上述したように、制御モジュール312は、制御モジュール312の入力部に結合されるか、または代替的に、制御モジュール312の入力部として機能する入力端子と、ADC20に接続される出力部を有するマルチプレクサ(MUX)18の入力部に結合される出力端子と、を有するインターフェースネットワーク316を含む。

#### 【0102】

スイッチングネットワーク $316_1$ は、スイッチング素子 $326_1$ 、 $328_1$ および $331_1$ を備えるが、ここで、各スイッチング素子 $326_1$ 、 $328_1$ および $331_1$ は、制御端子および1対の導電端子を含む。より具体的には、スイッチング素子 $326_1$ は、制御端子 $326_{1,1}$ 、導電端子 $326_{1,2}$ および導電端子 $326_{1,3}$ を有する。導電端子 $326_{1,1}$ 、 $2$ は端子 $316_{1,I1}$ および $316_{1,O1}$ に接続され得るか、または代替的に、端子 $316_{1,I1}$ および $316_{1,O1}$ は入／出力端子を形成し得る。スイッチング素子 $328_1$ は、制御端子 $328_{1,1}$ 、導電端子 $328_{1,2}$ および導電端子 $328_{1,3}$ を有する。導電端子 $328_{1,1}$ 、 $2$ は、導電端子 $326_{1,1}$ 、 $3$ と、端子 $316_{1,I2}$ および $316_{1,O2}$ と、に接続される。導電端子 $328_{1,3}$ は、入力端子 $316_{c,I1}$ および出力端子 $316_{c,O1}$ に接続され得るか、または代替的に、端子 $316_{c,I1}$ および $316_{c,O1}$ が入／出力端子を形成し得る。導電端子 $331_{1,1}$ 、 $2$ は、入力端子 $316_{1,I3}$ および出力端子 $316_{m,O3}$ に接続される。端子 $326_{1,1}$ 、 $328_{1,1}$ および $331_{1,1}$ は、それぞれ、図11の端子 $316_{1,I5}$ 、 $316_{1,I6}$ および $316_{1,I7}$ に対応することに留意されたい。

30

40

#### 【0103】

スイッチングネットワーク $316_2$ は、スイッチング素子 $326_2$ 、 $328_2$ および $331_2$ を備えるが、ここで、各スイッチング素子 $326_2$ 、 $328_2$ 、および $331_2$ は、制御端子および1対の導電端子を含む。より具体的には、スイッチング素子 $326_2$ は、制御端子 $326_{2,1}$ 、導電端子 $326_{2,2}$ 、および導電端子 $326_{2,3}$ を有する。導電端子 $326_{2,1}$ 、 $2$ は端子 $316_{c,I1}$ および $316_{c,O1}$ に接続され得るか、または代替的に、端子 $316_{c,I1}$ および $316_{c,O1}$ は入／出力端子を形成し得る。スイッチング素子 $328_2$ は、制御端子 $328_{2,1}$ 、導電端子 $328_{2,2}$ および導電端子 $3$

50

28<sub>2</sub>、3を有する。導電端子328<sub>2</sub>、2は、導電端子326<sub>2</sub>、3と、端子316<sub>2</sub>I2および316<sub>2</sub>O2と、に接続される。導電端子331<sub>2</sub>、2は、入力端子316<sub>2</sub>I3および出力端子316<sub>2</sub>O3に接続される。導電端子328<sub>2</sub>、3および331<sub>2</sub>、3は、以下に説明するスイッチングネットワーク316<sub>n</sub>に接続される。類似の共有コンポーネントおよび接続部が、スイッチングネットワーク316<sub>1</sub>とスイッチングネットワーク316<sub>2</sub>との間に存在するように、スイッチングネットワーク316<sub>2</sub>とスイッチングネットワーク316<sub>2</sub>に接続されたスイッチング部分との間に存在することに留意されたい。明瞭さのために、スイッチングネットワーク316<sub>2</sub>の全てのコンポーネントが図示されているわけではない。

## 【0104】

10

スイッチング部分316<sub>n</sub>は、スイッチング素子326<sub>n</sub>、328<sub>n</sub>および331<sub>n</sub>を備えるが、ここで、各スイッチング素子326<sub>n</sub>、328<sub>n</sub>、および331<sub>n</sub>は、制御端子および1対の導電端子を含む。より具体的には、スイッチング素子326<sub>n</sub>は、制御端子326<sub>n</sub>、1、導電端子326<sub>n</sub>、2、および導電端子326<sub>n</sub>、3を有する。導電端子326<sub>n</sub>、2は、端子316<sub>c</sub>I(n-1)および316<sub>c</sub>O(n-1)に接続され、または代替的に、端子316<sub>c</sub>I(n-1)および316<sub>c</sub>O(n-1)は入/出力端子を形成し得る。スイッチング素子328<sub>n</sub>は、制御端子328<sub>n</sub>、1、導電端子328<sub>n</sub>、2および導電端子328<sub>n</sub>、3を有する。導電端子328<sub>n</sub>、2は、導電端子326<sub>n</sub>、3と、端子316<sub>n</sub>I2および316<sub>n</sub>O2とに接続される。導電端子328<sub>n</sub>、3は、入力端子316<sub>n</sub>I4および出力端子316<sub>n</sub>O4に接続される。導電端子328<sub>n</sub>、3は、端子316<sub>n</sub>I4および316<sub>n</sub>O4に接続されるか、または代替的に、端子316<sub>n</sub>I4および316<sub>n</sub>O4が入/出力端子を形成し得る。導電端子331<sub>n</sub>、2は、入力端子316<sub>n</sub>I3および出力端子316<sub>n</sub>O3に接続され、導電端子331<sub>n</sub>、3は、入力端子316<sub>n</sub>I4および出力端子316<sub>n</sub>O4に接続される。

20

## 【0105】

フィルタ322は複数のフィルタ部分322<sub>1</sub>、322<sub>2</sub>、・・・、322<sub>n</sub>から成り、ここで、各フィルタ部分は、電力貯蔵装置24の対応する電力セル24<sub>1</sub>、24<sub>2</sub>、・・・、24<sub>n</sub>に接続される入力端子と、スイッチングネットワーク316<sub>1</sub>、316<sub>2</sub>、・・・、316<sub>n</sub>の対応する入力端子に接続される出力端子と、を含む。フィルタ部分322<sub>1</sub>は、入力端子322<sub>1</sub>I1および322<sub>c</sub>I1と、出力端子322<sub>1</sub>O1、322<sub>1</sub>O2および322<sub>c</sub>O1と、を有し、フィルタ部分322<sub>2</sub>は、入力端子322<sub>c</sub>I1および322<sub>c</sub>I2と、出力端子322<sub>c</sub>O1、322<sub>c</sub>O2および322<sub>c</sub>O2と、を有し、フィルタ部分322<sub>n</sub>は、入力端子322<sub>c</sub>I(n-1)および322<sub>c</sub>I2と、出力端子322<sub>c</sub>O(n-1)、322<sub>n</sub>O2および322<sub>n</sub>O3と、を有する。

30

## 【0106】

入力端子322<sub>1</sub>I1は、電力セル24<sub>1</sub>の正極に接続され、入力端子322<sub>c</sub>I1は、それぞれ、電力セル24<sub>1</sub>および24<sub>2</sub>の負極および正極に接続される。入力端子322<sub>c</sub>I(n-1)は電力セル24<sub>n</sub>の正極に接続され、入力端子322<sub>n</sub>I2は電力セル24<sub>n</sub>の負極に接続される。

40

## 【0107】

フィルタ部分322<sub>1</sub>は、インピーダンス素子334<sub>1</sub>および334<sub>2</sub>と、エネルギー貯蔵素子336<sub>1</sub>と、を備える。より具体的には、出力端子322<sub>1</sub>O1は、インピーダンス素子334<sub>1</sub>を介して入力端子322<sub>1</sub>I1に、エネルギー貯蔵素子336<sub>1</sub>を介して出力端子322<sub>1</sub>O2に接続される。入力端子322<sub>c</sub>I1は、インピーダンス素子334<sub>2</sub>を介して出力端子322<sub>c</sub>O1に接続される。インピーダンス素子334<sub>2</sub>はフィルタ部分322<sub>1</sub>および322<sub>2</sub>に対して共通であることに留意されたい。例えば、インピーダンス素子334<sub>1</sub>および334<sub>2</sub>はレジスタであり、エネルギー貯蔵素子336<sub>1</sub>はキャパシタである。

## 【0108】

フィルタ部分322<sub>2</sub>は、インピーダンス素子334<sub>2</sub>およびキャパシタ336<sub>2</sub>を備

50

える。より具体的には、出力端子 3 2 2<sub>c</sub> O 1 は、インピーダンス素子 3 3 4<sub>2</sub> を介して入力端子 3 2 2<sub>c</sub> I 1 に、エネルギー貯蔵素子 3 3 6<sub>2</sub> を介して出力端子 3 2 2<sub>c</sub> O 2 に接続される。例えば、インピーダンス素子 3 3 4<sub>2</sub> はレジスタであり、エネルギー貯蔵素子 3 3 6<sub>2</sub> はキャパシタである。類似の共有コンポーネントおよび接続部が、フィルタ部分 3 2 2<sub>1</sub> とフィルタ部分 3 2 2<sub>2</sub> との間に存在するように、フィルタ部分 3 2 2<sub>2</sub> と、フィルタ部分 3 2 2<sub>2</sub> に接続された別のフィルタ部分との間に存在することに留意されたい。明瞭さのために、フィルタ部分 3 2 2<sub>2</sub> の全てのコンポーネントが図示されているわけではない。

#### 【 0 1 0 9 】

フィルタ部分 3 2 2<sub>n</sub> は、レジスタ 3 3 4<sub>n</sub> および 3 3 4<sub>(n+1)</sub> と、エネルギー貯蔵素子 3 3 6<sub>n</sub> と、を備える。より具体的には、出力端子 3 2 2<sub>c</sub> O<sub>(n-1)</sub> は、インピーダンス素子 3 3 4<sub>n</sub> を介して入力端子 3 2 2<sub>c</sub> I<sub>(n-1)</sub> に、エネルギー貯蔵素子 3 3 6<sub>n</sub> を介して出力端子 3 2 2<sub>n</sub> O 2 に接続される。入力端子 3 2 2<sub>n</sub> I 2 は、インピーダンス素子 3 3 4<sub>(n+1)</sub> を介して出力端子 3 2 2<sub>n</sub> O 3 に接続される。例えば、インピーダンス素子 3 3 4<sub>n</sub> および 3 3 4<sub>(n+1)</sub> はレジスタであり、エネルギー貯蔵素子 3 3 6<sub>n</sub> はキャパシタである。

#### 【 0 1 1 0 】

引き続き図 1 3 を参照すると、インタフェースネットワーク 3 1 6 は、フィルタリング継続観察モード、サンプルアンドホールドモードおよび平衡化モードを含む少なくとも 3 つの互いに異なる動作モードで動作する。インタフェース回路 3 1 6 の動作モードは、図 1 2 を参照して説明されている。

#### 【 0 1 1 1 】

スイッチング素子 3 2 8<sub>1</sub>、3 2 8<sub>2</sub>、…、3 2 8<sub>n</sub> はオプション素子であり、スイッチング素子 3 2 8<sub>1</sub>、3 2 8<sub>2</sub>、…、3 2 8<sub>n</sub> が存在しない実施形態によれば、それぞれ、出力端子 3 1 6<sub>1</sub> O 2 が出力端子 3 1 6<sub>1</sub> O 4 に短絡され、出力端子 3 1 6<sub>2</sub> O 2 が出力端子 3 1 6<sub>2</sub> O 4 に短絡され、出力端子 3 1 6<sub>n</sub> O 2 が出力端子 3 1 6<sub>n</sub> O 4 に短絡されることに留意されたい。

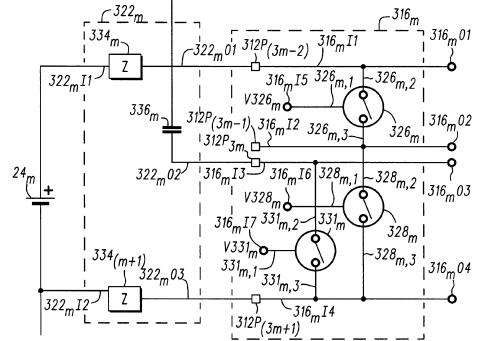

#### 【 0 1 1 2 】

図 1 4 は、本発明の別の実施形態による、フィルタ部分 3 2 2<sub>m</sub> を介して電力セル 2 4<sub>m</sub> に接続されるインタフェースネットワーク 3 1 6 (図 1 2 および 1 3 を参照して説明した) のスイッチング部分 3 1 6<sub>m</sub> の回路図である。図 1 1 および 1 5 のスイッチングネットワーク 3 1 6<sub>1</sub>、3 1 6<sub>2</sub>、…、3 1 6<sub>n</sub> が、スイッチング部分 3 1 6<sub>m</sub> から成り、変数 m が、整数 1、2、…、n を表すために用いられるに留意されたい。例えば、スイッチングネットワーク 3 1 6<sub>1</sub> はスイッチング部分 3 1 6<sub>m</sub> に対応し、ここで、m は、1 で置き換えられ、スイッチングネットワーク 3 1 6<sub>2</sub> はスイッチング部分 3 1 6<sub>m</sub> に対応し、ここで、m は、2 で置き換えられ、スイッチングネットワーク 3 1 6<sub>n</sub> はスイッチング部分 3 1 6<sub>m</sub> に対応し、ここで、m は、n で置き換えられる。図 1 4 のスイッチング部分 3 1 6<sub>m</sub> は図 1 2 のスイッチング部分 3 1 6<sub>m</sub> に類似しているが、キャパシタ 3 3 6<sub>m</sub> の端子のうちの 1 つが入力ピン 3 1 2 P<sub>(3m-2)</sub> に接続されていない点だけが異なる。したがって、キャパシタ 3 3 6<sub>m</sub> は、一方の端子は入力ピン 3 1 2 P<sub>3m</sub> に接続されているが、他方の端子は入力ピン 3 1 2 P<sub>(3m-2)</sub> には接続されない。図 1 2 を参照して検討したように、スイッチング素子 3 2 6<sub>m</sub> は平衡化スイッチング素子と呼ばれ、スイッチング素子 3 3 1<sub>m</sub> はサンプリングスイッチング素子と呼ばれ得る。

#### 【 0 1 1 3 】

スイッチング素子 3 2 8<sub>m</sub> はオプション素子であり、スイッチング素子 3 2 8<sub>m</sub> が存在しない実施形態によれば、出力端子 3 1 6<sub>m</sub> O 2 は出力端子 3 1 6<sub>m</sub> O 4 に短絡される。

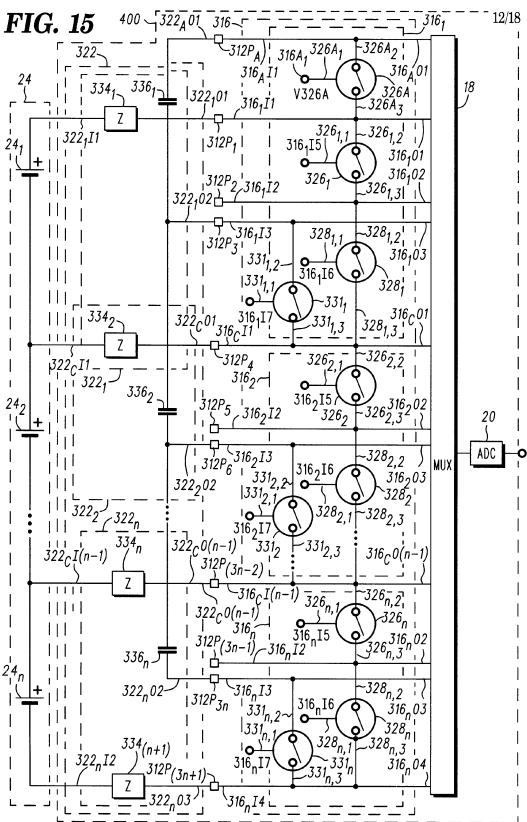

#### 【 0 1 1 4 】

図 1 5 は、図 1 1 を参照して説明したように制御モジュール 3 1 2 およびフィルタ回路 3 2 2 を備え、図 1 4 を参照して説明したフィルタ回路 3 2 2 およびインタフェース回路 3 1 6 の回路実装物の実施形態をさらに含む電力セルモニタおよび制御モジュール 4 0 0

10

20

30

40

50

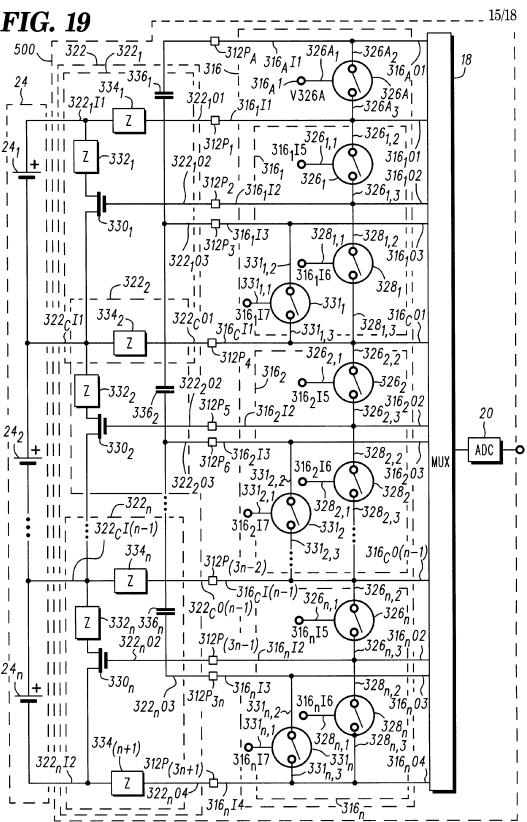

のブロック図である。図15の実施形態はまた、図15で入力ピン312P<sub>2</sub>、312P<sub>5</sub>および312P<sub>(3n-1)</sub>がフローティング状態に置かれている点が図11の実施形態と異なることに留意されたい。制御モジュール400はバッテリ装置24に接続される。上述したように、制御モジュール312は、制御モジュール312の入力部に接続されるか、または代替的に、制御モジュール312の入力部として機能する入力端子と、ADC20に接続される出力部を有するMUX18の入力部に接続される出力端子と、を有するインターフェースネットワーク316を含む。インターフェース回路316は、スイッチングネットワーク316<sub>1</sub>、316<sub>2</sub>、…、316<sub>n</sub>およびスイッチング素子326Aから成る。スイッチングネットワーク316<sub>1</sub>、316<sub>2</sub>、…、316<sub>n</sub>は、図13を参照して説明した。

10

#### 【0115】

スイッチング素子326Aは、制御信号V326Aを受信するように結合された制御端子326A<sub>1</sub>、導電端子326A<sub>2</sub>および導電端子326A<sub>3</sub>を有する。制御端子326A<sub>1</sub>は入力端子316A<sub>1</sub>として機能し得る。導電端子326A<sub>2</sub>は、導電端子316A<sub>I1</sub>および出力端子316A<sub>O1</sub>に接続される。導電端子326A<sub>3</sub>は、入力端子316<sub>1</sub>I<sub>1</sub>、出力端子316<sub>1</sub>O<sub>1</sub>および導電端子326<sub>1</sub>、<sub>2</sub>に接続される。

#### 【0116】

出力端子316<sub>1</sub>O<sub>1</sub>、316<sub>1</sub>O<sub>2</sub>、316<sub>1</sub>O<sub>3</sub>、316<sub>c</sub>O<sub>1</sub>、316<sub>2</sub>O<sub>2</sub>、316<sub>2</sub>O<sub>3</sub>、…、316<sub>c</sub>O<sub>(n-1)</sub>、316<sub>n</sub>O<sub>2</sub>、316<sub>n</sub>O<sub>3</sub>、316<sub>n</sub>O<sub>4</sub>および316<sub>A</sub>O<sub>1</sub>は、MUX18の対応する入力端子に接続される。

20

#### 【0117】

フィルタ322は複数のフィルタ部分322<sub>1</sub>、322<sub>2</sub>、…、322<sub>n</sub>から成り、ここで、各フィルタ部分は、電力貯蔵装置24の対応する電力セル24<sub>1</sub>、24<sub>2</sub>、…、24<sub>n</sub>に接続される入力端子と、スイッチングネットワーク316<sub>1</sub>、316<sub>2</sub>、…、316<sub>n</sub>の対応する入力端子に接続された出力端子と、を含む。フィルタ部分322<sub>1</sub>は、入力端子322<sub>1</sub>I<sub>1</sub>および322<sub>c</sub>I<sub>1</sub>と、出力端子322<sub>1</sub>O<sub>1</sub>、322<sub>1</sub>O<sub>2</sub>および322<sub>c</sub>O<sub>1</sub>と、を有し、フィルタ部分322<sub>2</sub>は、入力端子322<sub>c</sub>I<sub>1</sub>および322<sub>c</sub>I<sub>2</sub>と、出力端子322<sub>c</sub>O<sub>1</sub>、322<sub>c</sub>O<sub>2</sub>および322<sub>c</sub>O<sub>2</sub>と、を有し、フィルタ部分322<sub>n</sub>は、入力端子322<sub>c</sub>I<sub>(n-1)</sub>および322<sub>n</sub>I<sub>2</sub>と、出力端子322<sub>c</sub>O<sub>(n-1)</sub>、322<sub>n</sub>O<sub>2</sub>および322<sub>n</sub>O<sub>3</sub>と、を有する。

30

#### 【0118】

入力端子322<sub>1</sub>I<sub>1</sub>は、電力セル24<sub>1</sub>の正極に接続され、入力端子322<sub>c</sub>I<sub>1</sub>は、それぞれ、電力セル24<sub>1</sub>および24<sub>2</sub>の負極および正極に接続される。入力端子322<sub>c</sub>I<sub>(n-1)</sub>は電力セル24<sub>n</sub>の正極に接続され、入力端子322<sub>n</sub>I<sub>2</sub>は、電力セル24<sub>n</sub>の負極に接続される。

#### 【0119】

フィルタ部分322<sub>1</sub>は、インピーダンス素子334<sub>1</sub>および334<sub>2</sub>と、エネルギー貯蔵素子336<sub>1</sub>と、を備えるが、ここで、エネルギー貯蔵素子336<sub>1</sub>は、入力ピン312P<sub>A</sub>に接続された端子と、入力ピン312P<sub>3</sub>に接続された端子と、を有する。出力端子322<sub>1</sub>O<sub>1</sub>は入力ピン312P<sub>1</sub>に接続される。入力端子322<sub>c</sub>I<sub>1</sub>は、インピーダンス素子334<sub>2</sub>を介して出力端子322<sub>c</sub>O<sub>1</sub>に接続され、出力端子322<sub>c</sub>O<sub>1</sub>は入力ピン312P<sub>4</sub>に接続される。インピーダンス素子334<sub>2</sub>はフィルタ部分322<sub>1</sub>および322<sub>2</sub>に対して共通であることに留意されたい。例えば、インピーダンス素子334<sub>1</sub>および334<sub>2</sub>はレジスタであり、エネルギー貯蔵素子336<sub>1</sub>はキャパシタである。

40

#### 【0120】

フィルタ部分322<sub>2</sub>は、インピーダンス素子334<sub>2</sub>およびエネルギー貯蔵素子336<sub>2</sub>を備える。出力端子322<sub>c</sub>O<sub>1</sub>は、入力ピン312P<sub>4</sub>に接続される。エネルギー貯蔵素子336<sub>2</sub>の1つの端子は入力ピン312P<sub>3</sub>に接続され、キャパシタ336<sub>2</sub>の他方の端子は入力ピン312P<sub>6</sub>に接続される。例えば、インピーダンス素子334<sub>2</sub>は

50

レジスタであり、エネルギー貯蔵素子 $336_2$ はキャパシタである。類似の共有コンポーネントおよび接続部が、フィルタ部分 $322_1$ とフィルタ部分 $322_2$ との間に存在するよう、フィルタ部分 $322_2$ と、フィルタ部分 $322_2$ に接続された別のフィルタ部分との間に存在することに留意されたい。明瞭さのために、フィルタ部分 $322_2$ の全てのコンポーネントが図示されているわけではない。

#### 【0121】

フィルタ部分 $322_n$ は、インピーダンス素子 $334_n$ および $334_{(n+1)}$ と、エネルギー貯蔵素子 $336_n$ と、を備える。出力端子 $322_{CO}(n-1)$ は、入力ピン $312P_{(3n-2)}$ に接続される。入力端子 $322_{CI}(n-1)$ は、インピーダンス素子 $334_n$ を介して出力端子 $322_{CO}(n-1)$ に接続される。入力端子 $322_{nI2}$ は、インピーダンス素子 $334_{(n+1)}$ を介して出力端子 $322_nO3$ に接続される。エネルギー貯蔵素子 $336_n$ の1つの端子は入力ピン $312P_6$ に接続され、エネルギー貯蔵素子 $336_n$ の他方の端子は入力ピン $312P_{3n}$ に接続される。例えば、インピーダンス素子 $334_n$ および $334_{(n+1)}$ はレジスタであり、エネルギー貯蔵素子 $336_n$ はキャパシタである。

#### 【0122】

別の実施形態によれば、セルの極性は、これらのセルが図に示す反対の極性となるよう切り替えられる。

#### 【0123】

引き続き図15を参照すると、スイッチングネットワーク $316_1, \dots, 316_n$ は、フィルタリング継続観察モード、サンプルアンドホールドモードおよび内部平衡化モードを含む少なくとも3つの互いに異なる動作モードで動作する。既に検討したように、動作モードは、スイッチング素子 $326A, 326_1, \dots, 326_n, 328_1, \dots, 328_n$ および $331_1, \dots, 331_n$ の状態に従って、すなわち、これらのスイッチング素子がオープンされクローズされオープンまたはクローズされる組み合わせに従って選択し得る。

#### 【0124】

フィルタリング継続観察動作モードでは、電力セル $24_1, \dots, 24_n$ にまたがる電圧を、スイッチング素子 $326_1, \dots, 326_n$ および $328_1, \dots, 328_n$ がオープンされるように構成し、スイッチング素子 $331_1, \dots, 331_n$ および $326A$ がクローズされるように構成することによって監視される。例えば、電力セル $24_1$ にまたがる電圧は、MUX18の、出力端子 $316AO1$ および $316_1O3$ の電圧をADC20に伝達する構成に応答して監視することが可能である。このように、電力セル $24_1$ のフィルタリングされた電圧を表す電圧がADC20に伝達され、これによって、電力セル $24_1$ にまたがる電圧が観察または監視される。同様に、電力セル $24_2$ にまたがる電圧は、MUX18の、出力端子 $316_1O3$ および $316_2O3$ の電圧をADC20に伝達する構成に応答して監視することが可能である。このように、電力セル $24_2$ のフィルタリングされた電圧を表す電圧がADC20に伝達され、これによって、電力セル $24_2$ にまたがる電圧が観察または監視される。電力セル $24_n$ にまたがる電圧は、MUX18の、出力端子 $316_{(n-1)}O3$ および $316_nO3$ の電圧をADC20に伝達する構成に応答して監視することが可能である。このように、電力セル $24_n$ のフィルタリングされた電圧を表す電圧がADC20に伝達され、これによって、電力セル $24_n$ にまたがる電圧が観察または監視される。

#### 【0125】

微分サンプルアンドホールド動作モードでは、電力セル $24_1, \dots, 24_n$ にまたがる電圧を、スイッチング素子 $326A, 326_1, \dots, 326_n, 328_1, \dots, 328_n$ および $331_1, \dots, 331_n$ の制御端子に、それぞれ、適当な制御電圧 $V326A, V326_1, \dots, V326_n, V328_1, \dots, V328_n$ および $V331_1, \dots, V331_n$ を印加することによってサンプリングならびに記憶もしくは保持することが可能である。サンプリングするために、スイッチング素子は、

10

20

30

40

50

フィルタリング継続観察モードを可能とするように構成される。このようなスイッチ構成に応答して、キャパシタ $336_1$ 、 $\dots$ 、 $336_n$ は、電力セル $24_1$ 、 $\dots$ 、 $24_n$ にまたがる電圧に実質的に等しい電圧まで充電される、すなわち、キャパシタ $336_1$ 、 $\dots$ 、 $336_n$ は、電力セル $24_1$ 、 $\dots$ 、 $24_n$ の電圧をサンプリングする。キャパシタ $336_1$ 、 $\dots$ 、 $336_n$ は、フィルタとして機能し、サンプリングされた信号をフィルタリングする。スイッチング素子 $326A$ および $331_1$ 、 $\dots$ 、 $331_n$ のオン抵抗( $R_{dson}$ )は、キャパシタ $336_1$ 、 $\dots$ 、 $336_n$ の両端子と直列になっており、これによって、同相雑音に付きものの問題が軽減される。

#### 【0126】

電力セル $24_1$ 、 $\dots$ 、 $24_n$ の電圧をサンプリングした後、情報は、これらスイッチング素子の開放に好適な制御信号 $V326A$ および $V331_1$ 、 $\dots$ 、 $V331_n$ を、それぞれ、スイッチング素子 $326A$ および $331_1$ 、 $\dots$ 、 $331_n$ の制御端子に印加することによってキャパシタ $336_1$ 、 $\dots$ 、 $336_n$ 上に保持される。スイッチング素子 $326_1$ 、 $\dots$ 、 $326_n$ は、開放状態にとどまる、すなわち、フィルタリング継続観察モードのときと同じ状態を保つ。このスイッチング素子構成に応答して、キャパシタ $336_1$ 、 $\dots$ 、 $336_n$ は、電力セル $24_1$ 、 $\dots$ 、 $24_n$ のスタックから隔離され、これによって、電力セル $24_1$ 、 $\dots$ 、 $24_n$ 上に出力された電圧が保持される。

#### 【0127】

電力セル $24_1$ の電圧を表すサンプリングされた電圧は、 $MUX18$ の、出力端子 $316_{AO1}$ および $316_1O3$ の電圧を $ADC$ コンバータ $20$ に伝達する構成に応答して監視することが可能である。 $MUX18$ の、出力端子 $316_1O3$ および $316_2O3$ の電圧を $ADC20$ に伝達する構成に応答して、電力セル $24_2$ の電圧を表すサンプリングされた電圧が $ADC20$ に伝達される。 $MUX18$ の、出力端子 $316_{(n-1)}O3$ および $316_nO3$ の電圧を $ADC20$ に伝達する構成に応答して、電力セル $24_n$ の電圧を表すサンプリングされた電圧が $ADC20$ に伝達される。

#### 【0128】

内部平衡化動作モードでは、スイッチング素子 $331_1$ 、 $\dots$ 、 $331_n$ および $362A$ はオープンされたりクローズされたりするが、一方、電力セル $24_1$ 、 $\dots$ 、 $24_n$ は、図6とスイッチング素子 $26_1$ 、 $\dots$ 、 $26_n$ および $28_1$ 、 $\dots$ 、 $28_n$ を参照してした場合と同様にスイッチング素子 $326_1$ 、 $\dots$ 、 $326_n$ および $328_1$ 、 $\dots$ 、 $328_n$ を用いて平衡化される。

#### 【0129】

スイッチング素子 $328_1$ 、 $328_2$ 、 $\dots$ 、 $328_n$ はオプション素子であり、スイッチング素子 $328_1$ 、 $328_2$ 、 $\dots$ 、 $328_n$ が存在しない実施形態によれば、それぞれ、出力端子 $316_1O2$ が出力端子 $316_1O4$ に短絡され、出力端子 $316_2O2$ が出力端子 $316_2O4$ に短絡され、出力端子 $316_nO2$ が出力端子 $316_nO4$ に短絡されることに留意されたい。

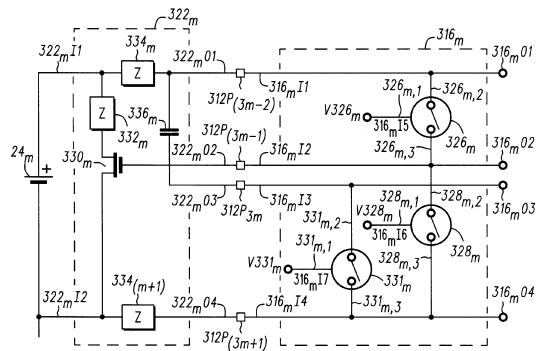

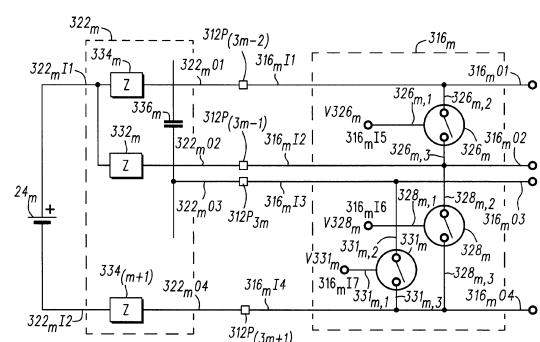

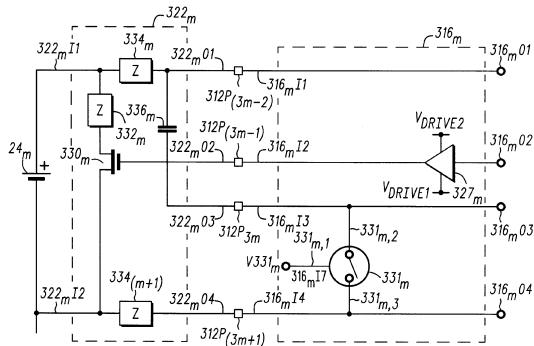

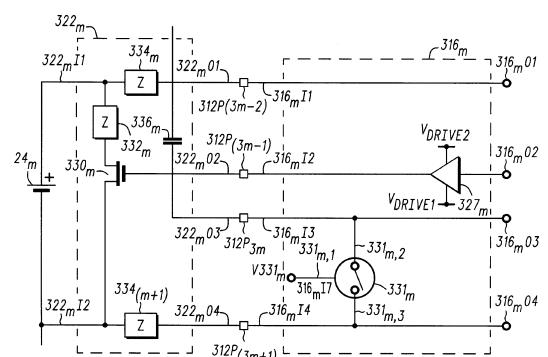

#### 【0130】

図16は、本発明の別の実施形態による、フィルタ部分 $322$ を介して電力セル $24$ に接続されるインターフェースネットワーク $316$ (図11を参照して説明した)のスイッチング部分 $316_m$ の回路図である。図13、15および17のスイッチングネットワーク $316_1$ 、 $316_2$ 、 $\dots$ 、 $316_n$ が、スイッチング部分 $316_m$ から成り、変数 $m$ が、整数 $1$ 、 $2$ 、 $\dots$ 、 $n$ を表すために用いられることに留意されたい。例えば、スイッチングネットワーク $316_1$ はスイッチング部分 $316_m$ に対応し、ここで、 $m$ は、 $1$ で置き換えられ、スイッチングネットワーク $316_2$ はスイッチング素子 $316_m$ に対応し、ここで、 $m$ は、 $2$ で置き換えられ、スイッチングネットワーク $316_n$ はスイッチング素子 $316_m$ に対応し、ここで、 $m$ は、 $n$ で置き換えられる。

#### 【0131】

スイッチング部分 $316_m$ を図12を参照して説明した。例えば、スイッチング素子 $3$

10

20

30

40

50

$26_m$  および  $328_m$  は単純なトランジスタプリドライバを形成するが、いずれかの極性を持つ外部平衡化素子を駆動することが可能な他のなんらかのプリドライバ回路で置き換えることが可能である。

#### 【0132】

図16のフィルタ部分  $322_m$  は、図12を参照して説明したフィルタ部分に類似しているが、平衡化素子  $330_m$  が平均化素子  $330_m$  および  $332_m$  を含む点だけが異なる。平均化素子  $330_m$  は、NPNバイポーラトランジスタ、PNPバイポーラトランジスタ、NチャネルMOSFET、PチャネルMOSFET等で有り得る。例えば、平衡化素子  $330_m$  および  $332_m$  は、それぞれ、NチャネルMOSFETトランジスタおよびレジスタである。NチャネルMOSFET  $330_m$  は、レジスタ  $332_m$  を介して入力端子  $322_m I1$  に接続されるドレイン端子と、入力端子  $322_m I2$  に接続されるソース端子と、入力ピン  $312P_{(3m-1)}$  に接続される出力端子  $322_m O2$  として機能するか、または代替的に、出力端子  $322_m O2$  に接続されるゲート端子と、を有する。出力端子  $322_m O1$  は、インピーダンス素子  $334_m$  を介して入力端子  $322_m I1$  に接続される。エネルギー貯蔵素子  $336_m$  は、入力ピン  $312P_{(3m-2)}$  に接続された端子と、入力ピン  $312P_{3m}$  に接続された端子と、を有する。例えば、インピーダンス素子  $334_m$  および  $334_{(m+1)}$  はレジスタであり、エネルギー貯蔵素子  $336_m$  はキャパシタである。レジスタ  $332_m$  および  $334_m$  は各々が、一般的には一緒に接続されて、入力端子  $322_m I1$  に接続されるか、または代替的に、入力端子  $322_m I1$  を形成する結節を形成する端子を有する。レジスタ  $332_m$  の他方の端子はトランジスタ  $330_m$  のドレイン端子に接続され、レジスタ  $334_m$  の他方の端子はキャパシタ  $336_m$  の端子に接続されて、出力端子  $322_m O1$  として機能するか、または代替的に、出力端子  $322_m O1$  に接続される結節を形成する。上述したように、キャパシタ  $336_m$  の他方の端子は出力ピン  $312P_{3m}$  に接続される。レジスタ  $334_{(m+1)}$  は、トランジスタ  $330_m$  のソース端子に接続されて、入力端子  $322_m I2$  に接続されるか、または代替的に、入力端子  $322_m I2$  として機能し得る結節を形成する端子を有し、そして、入力端子として機能し得るか、または代替的に、入力端子  $322_m O4$  に接続される端子をも有する。

#### 【0133】

電力セル  $24_m$  は、フィルタ部分  $322_m$  の入力端子  $322_m I1$  に接続された正極と、フィルタ部分  $322_m$  の入力端子  $322_m I2$  に接続された負極と、を有するバッテリセルを備える。

#### 【0134】

出力端子  $322_m O1$  は入力ピン  $312P_{(3m-2)}$  に電気的に接続され、出力端子  $322_m O2$  は入力ピン  $312P_{(3m-1)}$  に電気的に接続され、出力端子  $322_m O4$  は入力ピン  $312P_{(3m+1)}$  に電気的に接続されることに留意されたい。

#### 【0135】