(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6175294号

(P6175294)

(45) 発行日 平成29年8月2日(2017.8.2)

(24) 登録日 平成29年7月14日(2017.7.14)

(51) Int.Cl.

F 1

|             |           |

|-------------|-----------|

| H01L 21/02  | (2006.01) |

| H01L 27/12  | (2006.01) |

| H01L 21/336 | (2006.01) |

| H01L 29/786 | (2006.01) |

|      |       |      |

|------|-------|------|

| H01L | 27/12 | B    |

| H01L | 29/78 | 627D |

請求項の数 4 (全 34 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2013-131582 (P2013-131582) |

| (22) 出願日     | 平成25年6月24日 (2013.6.24)       |

| (65) 公開番号    | 特開2014-29992 (P2014-29992A)  |

| (43) 公開日     | 平成26年2月13日 (2014.2.13)       |

| 審査請求日        | 平成28年6月20日 (2016.6.20)       |

| (31) 優先権主張番号 | 特願2012-141666 (P2012-141666) |

| (32) 優先日     | 平成24年6月25日 (2012.6.25)       |

| (33) 優先権主張国  | 日本国 (JP)                     |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 飯窪 陽一<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 花岡 一哉<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 永松 翔<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (72) 発明者  | 藤井 照幸<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

最終頁に続く

(54) 【発明の名称】機能性基板の作製方法および半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

支持基板上に剥離層を形成する工程と、

前記剥離層上に平坦化膜を形成する工程と、

前記剥離層および前記平坦化膜に対して第1の加熱処理を行う工程と、を経て作製した

第1の基板と、

半導体基板上に絶縁膜を形成する工程と、

前記半導体基板中に脆化領域を形成する工程と、を経て作製した第2の基板を、前記平

坦化膜と前記絶縁膜が対向する状態に貼り合わせ、

前記第1の基板および前記第2の基板に対して第2の加熱処理を行い、

前記第1の基板と前記第2の基板を分離することで、前記脆化領域を界面として前記半

導体基板から分離した半導体薄膜を、前記絶縁膜を挟んで前記第1の基板上に形成し、

前記第1の加熱処理によって、前記第2の加熱処理を行う工程において前記第1の基板

の備える膜の応力変化を小さくすることを特徴とする、機能性基板の作製方法。

## 【請求項 2】

前記第1の加熱処理の温度が前記第2の加熱処理の温度以上である、請求項1に記載の

機能性基板の作製方法。

## 【請求項 3】

支持基板上に剥離層を形成する工程と、

前記剥離層上に平坦化膜を形成する工程と、

10

20

前記剥離層および前記平坦化膜に対して室温以上かつ前記支持基板の耐熱温度未満で第1の加熱処理を行う工程と、を経て作製した第1の基板と、

半導体基板上に絶縁膜を形成する工程と、

前記半導体基板中に脆化領域を形成する工程と、を経て作製した第2の基板を、前記平坦化膜と前記絶縁膜が対向する状態に貼り合わせ、

前記第1の基板および前記第2の基板に対して第2の加熱処理を行い、

前記第1の基板と前記第2の基板を分離することで、前記脆化領域を界面として前記半導体基板から分離した半導体薄膜を、前記絶縁膜を挟んで前記第1の基板上に形成し、

前記半導体薄膜を半導体層として用いたトランジスタを複数含む半導体回路を形成し、前記半導体回路上に固定基板を貼り合わせ、

前記固定基板と前記支持基板を分離することで、前記剥離層を界面として前記支持基板から分離した前記半導体回路を前記固定基板上に形成することを特徴とし、

前記第1の加熱処理によって、前記第2の加熱処理を行う工程において前記第1の基板の備える膜の応力変化を小さくすることを特徴とする、半導体装置の作製方法。

#### 【請求項4】

支持基板上に剥離層を形成する工程と、

前記剥離層上に平坦化膜を形成する工程と、

前記剥離層および前記平坦化膜に対して室温以上かつ前記支持基板の耐熱温度未満で第1の加熱処理を行う工程と、を経て作製した第1の基板と、

半導体基板上に絶縁膜を形成する工程と、

前記半導体基板中に脆化領域を形成する工程と、を経て作製した第2の基板を、前記平坦化膜と前記絶縁膜が対向する状態に貼り合わせ、

前記第1の基板および前記第2の基板に対して第2の加熱処理を行い、

前記第1の基板と前記第2の基板を分離することで、前記脆化領域を界面として前記半導体基板から分離した半導体薄膜を、前記絶縁膜を挟んで前記第1の基板上に形成し、

前記半導体薄膜を半導体層として用いたトランジスタを複数含む半導体回路を形成し、前記半導体回路上に仮固定基板を貼り合わせ、

前記仮固定基板と前記支持基板を分離することで、前記剥離層を界面として前記支持基板から分離した前記半導体回路を前記仮固定基板上に形成し、

前記半導体回路を挟んで前記仮固定基板と対向する面に固定基板を貼り合わせた後に前記仮固定基板を剥がすことで、前記半導体回路を前記固定基板上に形成することを特徴とし、

前記第1の加熱処理によって、前記第2の加熱処理を行う工程において前記第1の基板の備える膜の応力変化を小さくすることを特徴とする、半導体装置の作製方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

機能性基板の作製方法および半導体装置の作製方法に関する。

##### 【0002】

なお、本明細書中において「半導体装置」とは、半導体特性を利用することで機能しうる装置全般を指し、トランジスタ、半導体回路、電気光学装置および電子機器は全て半導体装置である。

##### 【0003】

また、本明細書等において、「支持基板」とは「支持基板以外の基板から分離した半導体薄膜を転載するための基板」を表しており、例えば、スマートカット法によりガラス基板上に単結晶シリコン薄膜を転載した場合は、ガラス基板が「支持基板」となる。

##### 【0004】

また、本明細書において、「可とう性を有する」とは、「機械等を用いることなく人が加えることのできる力により、目視可能な変形が生じるだけの柔軟性を有する」と解釈することができる。例えば、人の手により曲げることができる樹脂フィルム、ガラス、金属板

10

20

30

40

50

などは「可とう性を有する」基板であると言える。

【0005】

また、本明細書等において「機能性基板」とは、「可とう性を有する高性能な半導体装置の作製に用いる基板」を表すものであり、より具体的には「半導体薄膜を備え、当該半導体薄膜に対して各種成膜処理や微細加工処理を行うことができ、かつ当該処理により形成された回路層を他の基板上に転載することのできる機能を備える」基板と解釈することができる。

【背景技術】

【0006】

スパッタリング法などの各種成膜法により基板上に絶縁膜を挟んで半導体薄膜を形成する方法に代わり、絶縁膜および単結晶半導体薄膜を転載により基板上に形成し、当該基板を用いて半導体集積回路素子等を製造する技術が知られている。 10

【0007】

絶縁膜および単結晶半導体薄膜を転載により基板上に形成する方法としては、例えば、単結晶シリコン薄膜を合成石英などの基板上に形成する、スマートカット法（水素イオン注入剥離法などとも呼ばれる。）がある（例えば、特許文献1参照。）。

【0008】

スマートカット法は、特許文献1に記載されているように、支持基板上に絶縁膜を挟んで単結晶半導体薄膜の形成されたSOI基板を作製する技術であり、単結晶半導体基板と支持基板を貼り合わせた後、単結晶半導体基板の一部を分離するための加熱処理が行われる。例えは実施の形態1では、当該加熱処理として500℃以上の温度で熱処理を加える記載がある。 20

【0009】

また、近年フレキシブルディスプレイなどの可とう性を有する半導体装置の研究が盛んに行われてあり、また、可とう性を有する半導体装置の高性能化（例えば、半導体装置の高集積化や半導体装置の備えるトランジスタの移動度や信頼性の向上など。）についての研究も精力的に進められている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2000-124092号公報 30

【発明の概要】

【発明が解決しようとする課題】

【0011】

トランジスタの移動度や信頼性を向上させる観点から考えると、トランジスタの備える半導体層（少なくとも、チャネルが形成される領域。）には、単結晶状態などの結晶性の高い半導体薄膜を用いることが好ましい。

【0012】

可とう性を有する支持基板上に、スマートカット法を用いて結晶性の高い半導体薄膜を転載する方法も考えられるが、スマートカット法は特許文献1に記載されているように加熱処理を行う必要があり（例えば、特許文献1では、当該加熱処理として500℃以上の温度で熱処理を加える記載がある。）、支持基板が高温状態に曝されるため、当該方法で可とう性基板上に結晶性の高い半導体薄膜を形成することは、非常に困難である。 40

【0013】

また、仮に結晶性の高い半導体薄膜を可とう性を有する支持基板に転載できたとしても、支持基板の可とう性が高いほど、支持基板上に備えられた結晶性の高い半導体薄膜に対して各種の処理（例えば、結晶性の高い半導体薄膜上への各種成膜処理や微細加工処理など。）を行うことが困難である。

【0014】

そのため、これらの各種処理は、結晶性の高い半導体薄膜を可とう性を有する基板に転載 50

する前に行なうことが好ましいと言えるが、スマートカット法はその性質上、各種の処理を行った後に転載することは不可能である（例えば、単結晶シリコン基板を用いて半導体装置を作製した後にスマートカット法を行った場合、イオン注入処理により半導体装置自体がダメージを受けてしまう。）ため、可とう性を有する高性能な半導体装置の作製に用いることは難しいと言える。

#### 【0015】

上記内容を鑑み、本明細書では、可とう性を有する高性能な半導体装置の作製に用いる機能性基板、より具体的には、支持基板上に結晶性の高い半導体薄膜を備え、当該半導体薄膜に対して各種成膜処理や微細加工を行うことができ、かつ当該処理や加工により形成された回路層を他の基板上に転載することのできる、機能性基板の作製方法を提供することを目的の一つとする。10

#### 【0016】

また、上述の機能性基板を用いた、高性能な半導体装置（特に、可とう性を有する高性能な半導体装置。）の作製方法を提供することを目的の一つとする。

#### 【課題を解決するための手段】

#### 【0017】

本発明の一態様では、支持基板として剛性の高い基板を用い、支持基板と結晶性の高い半導体薄膜の間に剥離層を形成することで、結晶性の高い半導体薄膜に対して各種の処理（例えば、単結晶半導体薄膜上への各種成膜処理や、単結晶半導体薄膜等の微細加工など。）を行った後に、結晶性の高い半導体薄膜を含む層を支持基板から分離する。20

#### 【0018】

また、結晶性の高い半導体薄膜としては、結晶性の高い半導体基板の一部を分離することにより得られる膜を用い、分離処理の際に半導体薄膜に不具合（例えば、膜浮きや膜剥がれなど。）が生じないように、剥離層上には予め半導体薄膜層の密着性向上を目的とした平坦化膜を形成する。

#### 【0019】

なお、上述分離処理は加熱処理を含むため、当該加熱処理により剥離層と平坦化膜との界面で不具合（例えば、膜浮きや膜剥がれなど。）が生じないように、平坦化膜に対して半導体基板を貼り合わせる前に、支持基板の備える膜に対する加熱処理を行い、加熱に起因した応力変化を支持基板の備える膜に予め生じさせる。30

#### 【0020】

すなわち、本発明の一態様は、支持基板上に剥離層を形成する工程と、剥離層上に平坦化膜を形成する工程と、剥離層および平坦化膜に対して室温以上の温度で第1の加熱処理を行うことで支持基板上に形成された膜に応力変化を生じさせる工程と、を経て作製した第1の基板と、半導体基板上に絶縁膜を形成する工程と、半導体基板中に脆化領域を形成する工程と、を経て作製した第2の基板を、平坦化膜と絶縁膜が対向する状態に貼り合わせ、第1の基板および前記第2の基板に対して第2の加熱処理を行い、第1の基板から第2の基板を分離することで半導体基板から分離した半導体層を、絶縁膜を挟んで第1の基板上に形成することを特徴とする機能性基板の作製方法である。

#### 【0021】

上述の方法を用いることにより、支持基板の備える膜は第1の加熱処理により予め応力変化が生じているため、半導体基板を貼り合わせた後の状態（つまり、上面および下面の両側が基板により固定された状態。）で第2の加熱処理を行った場合に、膜の応力変化に起因した剥離層への物理的な力の付加を抑制できるため、機能性基板をトラブル（例えば、剥離層界面での膜剥がれなど。）無く作製することができる。40

#### 【0022】

なお、上述剥離層として、タンゲステン、モリブデンまたはタンゲステンとモリブデンの混合物のいずれかの酸化物、窒化物、酸化窒化物または窒化酸化物を主成分とする膜を形成することにより、半導体基板を分離して半導体薄膜を形成する際は、剥離層を界面とした剥離現象は生じず、半導体薄膜を用いて形成した回路層を転載する際は、剥離層を界面

10

20

30

40

50

とした剥離現象を容易に行うことができる。

【0023】

また、支持基板と半導体基板に同一の材料を用いることにより、第2の加熱処理の際に、支持基板と半導体基板の線熱膨張係数の違いに起因して剥離層界面で生じる膜剥がれを抑制することができる。

【0024】

また、第1の加熱処理を第2の加熱処理の温度以上で行うことにより、第2の加熱処理を行った場合における、膜の応力変化に起因した剥離層への物理的な力の付加をより小さくすることができるため、剥離層界面で生じる膜剥がれを更に抑制することができる。

【0025】

なお、剥離層の形成方法は、物理気相成長法により直接剥離層を形成する、支持基板上に金属膜を形成し、金属膜の表面に対して熱酸化処理、熱窒化処理、酸素を含むガスを用いてのプラズマ処理、窒素を含むガスを用いてのプラズマ処理、又は酸化力の強い溶液による酸化処理から選ばれたいずれかの一つ以上の表面変質処理を行うことにより剥離層を形成する、支持基板上に金属膜を形成し、金属膜上に酸化物絶縁膜を形成することにより金属膜の表面を含む一部を剥離層とする、の3つの方法を用いることができる。

10

【0026】

また、本発明の一態様は、支持基板上に剥離層を形成する工程と、剥離層上に平坦化膜を形成する工程と、剥離層および平坦化膜に対して室温以上かつ支持基板の耐熱温度未満で第1の加熱処理を行うことで、支持基板上に形成された膜に応力変化を生じさせる工程と、を経て作製した第1の基板と、半導体基板上に絶縁膜を形成する工程と、半導体基板中に脆化領域を形成する工程と、を経て作製した第2の基板を、平坦化膜と絶縁膜が対向する状態に貼り合わせ、第1の基板および第2の基板に対して第2の加熱処理を行い、第1の基板と第2の基板を分離することで脆化領域を界面として半導体基板から分離した半導体薄膜を、絶縁膜を挟んで第1の基板上に形成し、半導体薄膜を半導体層として用いたトランジスタを複数含む半導体回路を形成し、半導体回路上に固定基板を貼り合わせ、固定基板と支持基板を分離することで、剥離層を界面として支持基板から分離した半導体回路を固定基板上に形成することを特徴とする半導体装置の作製方法である。

20

【0027】

また、本発明の一態様は、支持基板上に剥離層を形成する工程と、剥離層上に平坦化膜を形成する工程と、剥離層および平坦化膜に対して室温以上かつ支持基板の耐熱温度未満で第1の加熱処理を行うことで、支持基板上に形成された膜に応力変化を生じさせる工程と、を経て作製した第1の基板と、半導体基板上に絶縁膜を形成する工程と、半導体基板中に脆化領域を形成する工程と、を経て作製した第2の基板を、平坦化膜と絶縁膜が対向する状態に貼り合わせ、第1の基板および第2の基板に対して第2の加熱処理を行い、第1の基板と第2の基板を分離することで、脆化領域を界面として半導体基板から分離した半導体薄膜を、絶縁膜を挟んで第1の基板上に形成し、半導体薄膜を半導体層として用いたトランジスタを複数含む半導体回路を形成し、半導体回路上に仮固定基板を貼り合わせ、仮固定基板と支持基板を分離することで、剥離層を界面として支持基板から分離した半導体回路を仮固定基板上に形成し、半導体回路を挟んで仮固定基板と対向する面に固定基板を貼り合わせた後に仮固定基板を剥がすことで、半導体回路を固定基板上に形成することを特徴とする半導体装置の作製方法である。

30

【発明の効果】

【0028】

上述の方法を用いることにより、結晶性の高い半導体薄膜を備え、当該半導体薄膜に対して各種成膜処理や微細加工を行うことができ、かつ当該処理や加工後に当該半導体薄膜を含む回路層を他の基板上に転載することの可能な、機能性基板を作製することができる。

【0029】

また、機能性基板を用い、結晶性の高い半導体薄膜を活性層（少なくともチャネルが形成される領域。）として用いたトランジスタを形成し、当該トランジスタを含む回路層を、

40

50

剥離層を用いて機能性基板から剥離して他の基板に転載することにより、高性能な半導体装置（例えば、高集積化された半導体装置や、移動度や信頼性の高いトランジスタを備える半導体装置など。）を作製することができる。

#### 【0030】

また、上述転載処理は物理的な力の付加により回路層を剥離するため、可とう性を有する基板上に回路層を転載できる。故に、可とう性を有する高性能な半導体装置を作製することができる。

#### 【図面の簡単な説明】

#### 【0031】

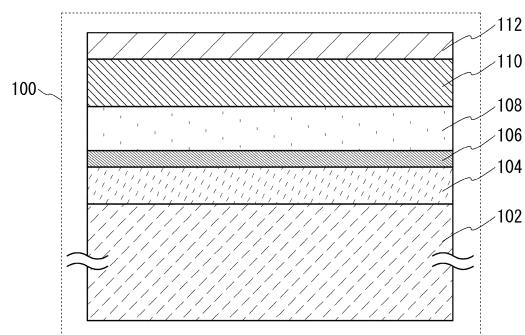

【図1】機能性基板の構造を説明する図。

10

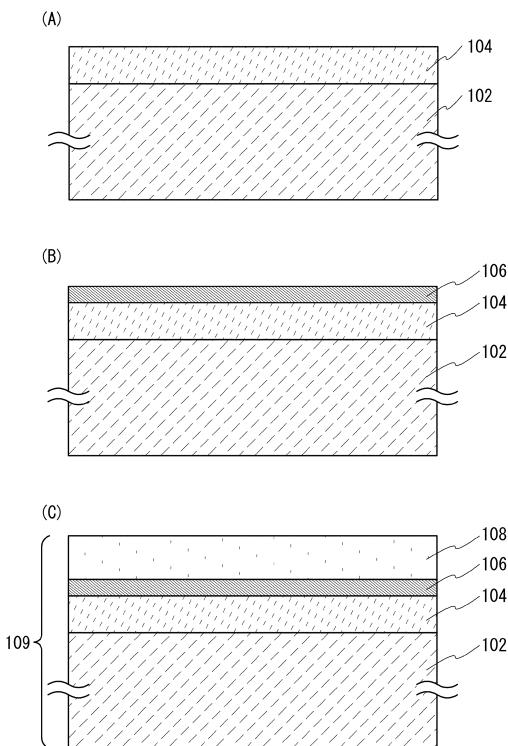

【図2】機能性基板の作製方法を説明する図。

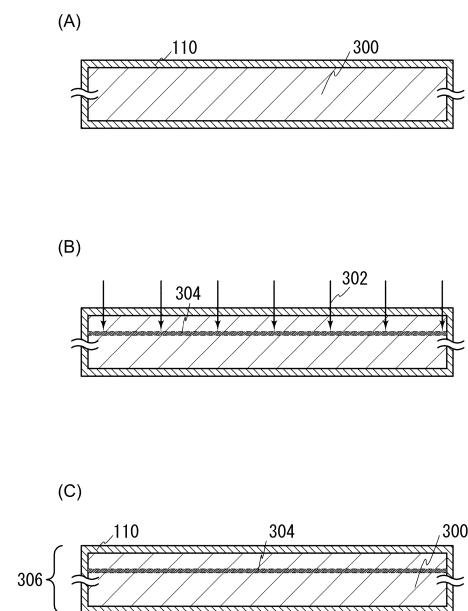

【図3】機能性基板の作製方法を説明する図。

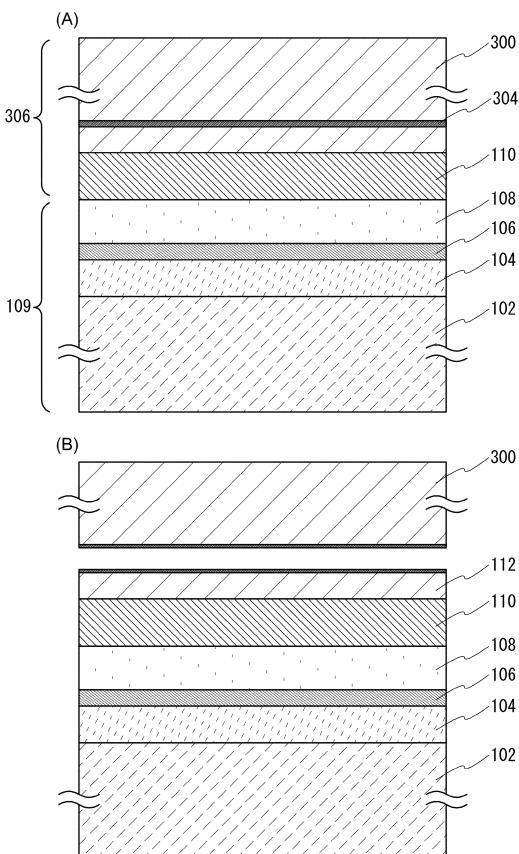

【図4】機能性基板の作製方法を説明する図。

【図5】機能性基板の作製方法を説明する図。

【図6】個体識別装置の構造を説明する図。

【図7】個体識別装置の作製方法を説明する図。

【図8】表示装置の構造を説明する図。

【図9】表示装置の作製方法を説明する図。

【図10】表示装置の作製方法を説明する図。

【図12】表示装置の作製方法を説明する図。

20

【図11】表示装置の作製方法を説明する図。

【図13】電子機器を説明する図。

#### 【発明を実施するための形態】

#### 【0032】

以下では、本明細書に開示する発明の実施の形態について図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

#### 【0033】

なお、以下に説明する実施の形態において、同一部分または同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する場合がある。

30

#### 【0034】

また、図面等において示す各構成の、位置、大きさ、範囲などは、理解の簡単のため、実際の位置、大きさ、範囲などを表していない場合がある。このため、開示する発明は、必ずしも、図面等に開示された位置、大きさ、範囲などに限定されない。

#### 【0035】

##### (実施の形態1)

本実施の形態では、図1を用いて機能性基板の構成を説明すると共に、当該機能性基板の作製方法の一例を、図2乃至図5を用いて説明する。

#### 【0036】

40

本実施の形態に記載の方法で作製される機能性基板100の構造は、図1に示すように、支持基板102、下地膜104、剥離層106、平坦化膜108、絶縁膜110および結晶性の高い半導体薄膜112を備えた構造となる。

#### 【0037】

以下、図2乃至図5を用いて、図1に記載の機能性基板100の作製方法についての説明を行う。

#### 【0038】

まず、支持基板102上に下地膜104を形成する（図2（A）参照。）。

#### 【0039】

支持基板102は、後の工程にて結晶性の高い半導体薄膜112が形成されるが、結晶性

50

の高い半導体薄膜 112 に対して各種の処理（例えば、半導体薄膜上への各種成膜処理や、単結晶半導体薄膜等の微細加工など。）を行うためには、支持基板 102 として、後の様々な処理に耐えうる程度の耐熱性及び耐薬品性を有し、且つ剛性の高い基板を用いる必要がある。

**【0040】**

当該基板としては、例えば、シリコン基板、ゲルマニウム基板、シリコンゲルマニウム基板などの第 14 族元素でなる半導体基板や、窒化ガリウム基板、ガリウム砒素基板、炭化シリコン基板、インジウムリン基板などの化合物半導体でなる基板を用いることができる。

**【0041】**

また、アルミニシリケートガラス、アルミニホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板、天然石英基板、合成石英基板などの絶縁体でなる基板を用いることもできる。

**【0042】**

また、ステンレス基板などの各種金属基板を用いることもできる。

**【0043】**

なお、支持基板 102 は、その線熱膨張係数が、後の工程にて行う結晶性の高い半導体基板 300（結晶性の高い半導体薄膜 112 の形成に用いる基板。図 3（A）参照。）に劈開現象を生じさせるための加熱の温度において、結晶性の高い半導体基板 300 の当該加熱温度における線熱膨張係数のプラスマイナス 10% 以内であることが好ましく、より望ましくは、結晶性の高い半導体基板と同じ材料を用いることが好ましい。

**【0044】**

これは、支持基板 102 と結晶性の高い半導体基板 300 を貼り合わせた状態で加熱した際に、支持基板 102 と結晶性の高い半導体基板 300 の線熱膨張係数が異なることに起因して、剥離層 106 で剥離現象が発生することを防止する目的がある。

**【0045】**

また、後の工程にて形成する結晶性の高い半導体薄膜 112 に対して、各種の処理を微細なサイズで行う（例えば、サブミクロンレベルの細かなパターン形成など。）ためには、サブミクロンレベルの細かなパターン形成が可能な基板を支持基板 102 として用いる必要がある。支持基板 102 として用いることのできる上述の各種材料のうち、例えばシリコン基板（特に、単結晶シリコン基板。）は、絶縁体でなる基板や各種金属基板と比較して平坦性や広範囲に於けるうねりが小さく、また、既に数十ナノメートルといった微細パターン形成に対応した加工装置が市販されているため、支持基板 102 として用いるのに適していると言える。勿論、支持基板 102 をシリコン基板に限定するものではない。

**【0046】**

下地膜 104 としては、例えば、酸化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜、窒化シリコン膜などを単層で、または積層させて形成すればよい。なお、当該膜の作製方法としては、熱酸化法、CVD 法、スパッタリング法などがある。

**【0047】**

なお、熱酸化処理により下地膜 104 を形成する場合、酸化性雰囲気中にハロゲンを添加して行うことが好ましい。例えば、塩素（Cl）が添加された酸化性雰囲気中で半導体基板 300 に熱酸化処理を行うことにより、塩素酸化された下地膜 104 を形成することができる。この場合、下地膜 104 は塩素原子を含有する膜となる。このような塩素酸化膜を用いた場合、後の工程にて下地膜 104 上に剥離層 106 を形成した際に、剥離層 106 の元素が支持基板 102 に拡散することを抑制できる。なお、下地膜 104 に含有させるハロゲン原子は塩素原子に限られず、フッ素原子を含有させてもよい。

**【0048】**

また、下地膜 104 の形成前に、塩酸過酸化水素水混合溶液（HPM）、硫酸過酸化水素水混合溶液（SPM）、アンモニア過酸化水素水混合溶液（APM）、希フッ酸（DHF）、フッ酸、過酸化水素水、オゾン水および純水の混合液（FPM）などを用いて支持基

10

20

30

40

50

板 102 の表面を洗浄しておくことが好ましい。

**【0049】**

次に、下地膜 104 上に剥離層 106 を形成する（図2（B）参照。）。

**【0050】**

剥離層 106 としては、スパッタリング法やプラズマ CVD 法、塗布法、印刷法等により、タンゲステン (W)、モリブデン (Mo)、チタン (Ti)、タンタル (Ta)、ニオブ (Nb)、ニッケル (Ni)、コバルト (Co)、ジルコニウム (Zr)、亜鉛 (Zn)、ルテニウム (Ru)、ロジウム (Rh)、パラジウム (Pd)、オスミウム (Os)、イリジウム (Ir)、珪素 (Si) から選択された元素を用いた金属、又は当該元素を主成分とする合金材料、又は当該元素を主成分とする化合物材料のいずれかの酸化物、窒化物、酸化窒化物または窒化酸化物を主成分とする膜を用いることができる。10

**【0051】**

上述の剥離層 106 を形成する方法としては、以下に記載する 3 つの方法がある。

**【0052】**

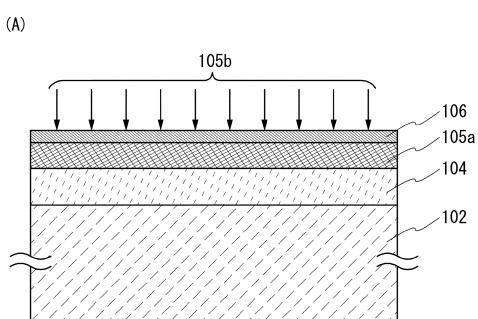

第 1 の方法は、図 2 (B) に示すように、スパッタリング法などの物理気相成長法 (PVD : Physical Vapor Deposition) を用いて、上述の剥離層 106 を下地膜 104 上に直接成膜する方法である。

**【0053】**

第 2 の方法は、図 5 (A) に示すように、下地膜 104 上に、まずスパッタリング法やプラズマ CVD 法、塗布法、印刷法等により、タンゲステン (W)、モリブデン (Mo)、チタン (Ti)、タンタル (Ta)、ニオブ (Nb)、ニッケル (Ni)、コバルト (Co)、ジルコニウム (Zr)、亜鉛 (Zn)、ルテニウム (Ru)、ロジウム (Rh)、パラジウム (Pd)、オスミウム (Os)、イリジウム (Ir)、珪素 (Si) から選択された元素を用いた金属、又は当該元素を主成分とする合金材料、又は当該元素を主成分とする化合物材料のいずれかである金属膜 105a を形成し、当該金属膜の表面に対して、熱酸化処理、熱窒化処理、酸素を含むガスを用いてのプラズマ処理、窒素を含むガスを用いてのプラズマ処理、又はオゾン水等の酸化力の強い溶液による処理から選ばれたいずれかの一つ以上の表面変質処理 105b を行って金属膜 105a の一部に上述の剥離層 106 を形成する方法である。20

**【0054】**

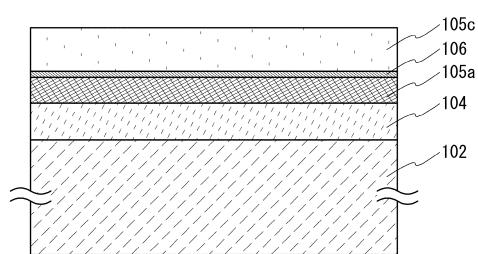

第 3 の方法は、図 5 (B) に示すように、下地膜 104 上に、まずスパッタリング法やプラズマ CVD 法、塗布法、印刷法等により、タンゲステン (W)、モリブデン (Mo)、チタン (Ti)、タンタル (Ta)、ニオブ (Nb)、ニッケル (Ni)、コバルト (Co)、ジルコニウム (Zr)、亜鉛 (Zn)、ルテニウム (Ru)、ロジウム (Rh)、パラジウム (Pd)、オスミウム (Os)、イリジウム (Ir)、珪素 (Si) から選択された元素を用いた金属、又は当該元素を主成分とする合金材料、又は当該元素を主成分とする化合物材料のいずれかである金属膜 105a を形成し、当該金属膜上に金属酸化物または金属窒化物を主成分とする絶縁膜 105c を形成することにより、金属膜 105a の表面を含む一部が変質（例えば、酸化や窒化など。）し、金属膜 105a と絶縁膜 105c との界面に上述の剥離層 106 を形成する方法である。30

**【0055】**

絶縁膜 105c としては、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜のいずれかを主成分とする膜を用いることができる。例えば、タンゲステンを主成分とする金属膜 105a 上に絶縁膜 105c として酸化シリコン膜を成膜して、タンゲステンと酸化シリコンとの間にタンゲステン酸化物を形成することができる。40

**【0056】**

上述の第 3 の方法については、金属膜 105a 上に絶縁膜 105c を形成した後に加熱処理を行うことにより、金属膜 105a と絶縁膜 105c 界面の上述剥離層の形成を促進させることができる。また、金属膜 105a 形成し、第 2 の方法にて説明した表面変質処理 105b を行った後に、絶縁膜 105c を形成してもよい。または、金属膜 105a を形50

成し、第2の方法にて説明した表面変質処理105bを行った後に、絶縁膜105cを形成し、更に加熱処理を行うことにより、金属膜105aと絶縁膜105c界面の上述剥離層の形成を促進させてもよい。

#### 【0057】

なお、上述の第3の方法で剥離層106を形成した場合は、図5(B)に示すように剥離層106上に絶縁膜105cが形成される構造となる。当該絶縁膜105cは、図1に示す機能性基板100の平坦化膜108の一部あるいは全部として用いることができる。

#### 【0058】

剥離層106は、後の工程にて剥離層106に対して物理的な力(例えば、支持基板102に貼り合わせた結晶性の高い半導体基板を、支持基板102から引き剥がす力。)を加えることで、剥離層106が劈開面となって剥離現象が生じる。このため、剥離層106の膜厚が薄すぎると剥離現象が生じず、剥離層106の膜厚が厚いと劈開面が生じる際に剥離層106と接する膜に悪影響が及ぶ(例えば、下地膜104や平坦化膜108にクラックや膜剥がれ等が生じるなど。)可能性が高まる。

#### 【0059】

このため、剥離層106の膜厚は、1nm以上15nm以下、より好ましくは2nm以上10nm以下、更に好ましくは3nm以上8nm以下であることが望ましい。

#### 【0060】

なお、上述膜厚の調整および物理的な力の付加により剥離についての容易性を鑑みると、剥離層106としては、タンゲステン、モリブデンまたはタンゲステンとモリブデンの混合物のいずれかの酸化物、窒化物、酸化窒化物または窒化酸化物を主成分とする膜を用いることが好ましい。剥離層106を上述の膜とすることにより、半導体基板を分離して半導体薄膜112を形成する際は、剥離層106を界面とした剥離現象は生じず、半導体薄膜112を用いて形成した回路層を転載する際は、剥離層106を界面とした剥離現象を容易に行うことができる。

#### 【0061】

このため、上述の第2の方法および第3の方法を用いて剥離層106を形成する場合、金属膜105aとしては、タンゲステン、モリブデンまたはタンゲステンとモリブデンの混合物のいずれかを主成分とする膜を用いることが好ましい。

#### 【0062】

次に、剥離層106上に平坦化膜108を形成する(図2(C)参照。)。

#### 【0063】

平坦化膜108としては、スパッタリング法などのPVD法や化学気相蒸着法(CVD: Chemical Vapour Deposition)を用いて、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、窒化酸化シリコン膜を単層でまたは積層させて形成すればよい。

#### 【0064】

CVD法を用いる場合、シランガス、ジシランガス、トリシランガス又は有機シランガス等のシラン系ガスを用いて化学気相成長法により作製される酸化シリコン膜が好ましい。シランガスを用いる場合、二酸化窒素又は一酸化二窒素との混合ガスを用いることが好ましい。

#### 【0065】

有機シランガスとしては、珪酸エチル(TEOS: 化学式Si(OCH<sub>3</sub>)<sub>4</sub>)、トリメチルシラン(TMDS: (CH<sub>3</sub>)<sub>3</sub>SiH)、テトラメチルシクロテトラシロキサン(TMCTS)、オクタメチルシクロテトラシロキサン(OMCTS)、ヘキサメチルジシラザン(HMDS)、トリエトキシシラン(SiH(OCH<sub>3</sub>)<sub>3</sub>)又はトリスジメチルアミノシラン(SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>)等のシリコン含有化合物を用いることができる。

#### 【0066】

また、プラズマCVD、熱CVD又は光CVDを用いてもよい。

10

20

30

40

50

**【 0 0 6 7 】**

平坦化膜 108 の膜厚は、5 nm 以上 500 nm 以下の厚さで設けるとよい。平坦化膜 108 を上記の厚さで形成することで、被成膜表面の表面荒れを平滑化すると共に、接合する基板との歪みを緩和することができる。

**【 0 0 6 8 】**

なお、平坦化膜 108 の形成後に、平坦化膜 108 に対して更に平坦化処理を行ってもよい。

**【 0 0 6 9 】**

平坦化処理としては、研磨処理（例えば、化学的機械研磨（C M P : C h e m i c a l M e c h a n i c a l P o l i s h i n g ）処理、ドライエッティング処理、プラズマ処理を行うことができる。10

**【 0 0 7 0 】**

プラズマ処理としては、例えば、アルゴンガスを導入してプラズマを発生させる逆スパッタリングを行うことができる。

**【 0 0 7 1 】**

平坦化処理として、研磨処理、ドライエッティング処理、プラズマ処理のいずれかを 1 回あるいは複数回行ってもよいし、研磨処理、ドライエッティング処理、プラズマ処理を組み合わせて複数回行ってもよい。また、組み合わせて行う場合、工程順は特に限定されない。

**【 0 0 7 2 】**

上記の工程を経ることにより、支持基板 102 上に下地膜 104、剥離層 106 および平坦化膜 108 を備える第 1 の基板 109 を形成することができる（図 2（C）参照）。20

**【 0 0 7 3 】**

また、上述の第 1 の基板 109 を形成する一方で、半導体基板 300 に対しても処理を行う。半導体基板 300 に対して行う処理を、以下に説明する。

**【 0 0 7 4 】**

まず、半導体基板 300 の表面に絶縁膜 110 を形成する（図 3（A）参照。）。

**【 0 0 7 5 】**

半導体基板 300 としては、結晶性の高い半導体基板を用いる。例えば、単結晶シリコン基板、単結晶ゲルマニウム基板または単結晶シリコンゲルマニウム基板などの第 14 族元素でなる基板を用いることができる。また、窒化ガリウム基板、ガリウム砒素基板、炭化シリコン基板またはインジウムリン基板などの化合物半導体基板を用いることもできる。なお、市販のシリコン基板としては、直径 5 インチ（125 mm）、直径 6 インチ（150 mm）、直径 8 インチ（100 mm）、直径 12 インチ（300 mm）、直径 16 インチ（700 mm）サイズの円形のものが代表的である。また、半導体基板 300 の形状は円形に限らず、例えば、矩形や正方形等に加工したものであっても良い。また、半導体基板 300 は、C Z（チョクラルスキー）法や F Z（フローティングゾーン）法を用いて作製することができる。30

**【 0 0 7 6 】**

絶縁膜 110 としては、例えば、酸化シリコン膜、酸化窒化シリコン膜、窒化酸化等を単層で、または積層させて形成すればよい。なお、当該膜の作製方法としては、熱酸化法、C V D 法、スパッタリング法などが挙げられる。また、C V D 法を用いて絶縁膜 110 を形成する場合、良好な貼り合わせを実現するためには、テトラエトキシシラン（略称；T E O S：化学式  $\text{Si}(\text{OC}_2\text{H}_5)_4$ ）等の有機シランを用いて酸化シリコン膜を形成することが好ましい。40

**【 0 0 7 7 】**

なお、熱酸化処理により絶縁膜 110 を形成する場合、酸化性雰囲気中にハロゲンを添加して行うことが好ましい。例えば、塩素（Cl）が添加された酸化性雰囲気中で半導体基板 300 に熱酸化処理を行うことにより、塩素酸化された絶縁膜 110 を形成することができる。この場合、絶縁膜 110 は、塩素原子を含有する膜となる。このような塩素酸化により、後の工程にて半導体基板 300 と接合基板を貼り合わせた後に、接合基板から混50

入するNaなどの不純物を固定して、半導体基板300の汚染を防止できる。なお、絶縁膜110に含有させるハロゲン原子は塩素原子に限られない。絶縁膜110にはフッ素原子を含有させてもよい。

#### 【0078】

また、絶縁膜110の形成前に、塩酸過酸化水素水混合溶液(HPM)、硫酸過酸化水素水混合溶液(SPM)、アンモニア過酸化水素水混合溶液(APM)、希フッ酸(DHF)、フッ酸、過酸化水素水、オゾン水および純水の混合液(FPM)などを用いて半導体基板300の表面を洗浄しておくことが好ましい。

#### 【0079】

次に、半導体基板300の一面からイオン照射処理302を行うことにより、半導体基板300中の所定の深さに、脆化領域304を形成する(図3(B)参照。)。

#### 【0080】

照射するイオン種としては、水素イオンを用いればよい。水素イオンとはH<sup>+</sup>、H<sub>2</sub><sup>+</sup>およびH<sub>3</sub><sup>+</sup>のいずれか一種、或いはこれらのイオンが二種以上混合したもの指す。加速された水素イオンを照射する場合は、H<sub>3</sub><sup>+</sup>の比率を高くすると良い。具体的には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>の総量に対してH<sub>3</sub><sup>+</sup>の割合が50%以上(より好ましくは80%以上)となるようにする。H<sub>3</sub><sup>+</sup>の割合を高めることで、イオン照射の効率を向上させることができる。また、水素イオン以外に、希ガスイオンを用いることもできる。具体的には、Heイオン、Neイオン、Arイオン、KrイオンまたはXeイオンを用いることができる。

10

20

#### 【0081】

脆化領域304が形成される深さは、照射するイオンの運動エネルギー、質量と電荷、入射角などによって調節することができる。また、脆化領域304は、イオンの平均侵入深さとほぼ同じ深さの領域に形成される。このため、照射するイオン種や照射条件を調整することにより、後の工程にて半導体基板300から分離する、半導体薄膜112の厚さを調節することができる。

#### 【0082】

なお、半導体薄膜112の厚さについては特段の限定は無いが、分離された半導体薄膜112を高性能な半導体回路を形成する用途に用いる場合は、当該膜厚を厚くしすぎるとトランジスタのS値が増加する、またトランジスタがノーマリーオンになるといった懼があるため、1nm以上200nm以下、好ましくは3nm以上100nm以下とすることが望ましい。

30

#### 【0083】

このため、半導体基板300中における脆化領域304の形成深さが、半導体基板300と絶縁膜110の界面から1nm以上200nm以下、好ましくは3nm以上100nm以下程度となるように、照射するイオンの平均侵入深さを調節すればよい。

#### 【0084】

当該イオン照射処理302は、イオンドーピング装置やイオン注入装置を用いて行うことができる。特にイオン注入装置では、プラズマ中のイオン種を質量分離し、ある特定の質量のイオン種のみを半導体基板中に照射することができるため、トランジスタの特性に影響を及ぼす不純物の混入を抑制できるため望ましい。

40

#### 【0085】

しかし、イオンドーピング装置を用いてイオン照射処理302を行う場合においても、絶縁膜110を介してイオン照射処理302を行うことにより、トランジスタの特性に影響を及ぼす物質(例えば重金属など)をトラップすることができる。

#### 【0086】

上記の工程を経ることにより、半導体基板300の表面に絶縁膜110が、内部に脆化領域304を備える第2の基板306を形成することができる(図3(C)参照)。

#### 【0087】

次に、第1の基板109と第2の基板306とを貼り合わせる前に、第1の基板109の

50

備える膜（本実施の形態では、下地膜104、剥離層106および平坦化膜108。）に対して第1の加熱処理を行う。

【0088】

当該加熱処理の目的は、第1の基板109と第2の基板306を貼り合わせる前に、第1の基板109の備える膜の応力を、後の工程で行う加熱処理（第2の加熱処理。）の際に極力応力変動が生じないよう、予め応力を変化させておくことにある。

【0089】

本明細書等に記載の機能性基板の作製方法では、第2の基板から絶縁膜110および半導体薄膜112を分離するために後の工程にて第2の加熱処理を行うが、当該加熱処理は比較的高温で加熱処理を行うため、第1の加熱処理を行わずに第1の基板109および第2の基板306を貼り合わせて第2の加熱処理を行うと、上面および下面の両側が基板により固定された状態で、第1の基板109の備える膜に大きな応力変化が生じる。そのため、当該応力変化は、膜の界面部分に物理的な力として加わりやすい。10

【0090】

第1の基板109の備える剥離層106は、物理的な力により剥離層106上の膜が剥離されるため、上述の膜の応力変化によって膜剥がれが生じる恐れがある。

【0091】

第1の加熱処理は、上述のような現象を防止するために行われるものである。したがって、平坦化膜108形成後から、第1の基板109と第2の基板306の貼り合わせを行う前のタイミングで行う必要がある。20

【0092】

なお、第1の加熱処理は、室温以上支持基板102の耐熱温度未満、好ましくは150以上支持基板102の耐熱温度未満、より好ましくは、後の工程にて行う第2の加熱処理の温度以上支持基板102の耐熱温度未満で行う。

【0093】

第1の加熱処理を第2の加熱処理以上の温度で行うことにより、第1の基板109の備える膜は、第2の加熱処理の際に生じる応力変化が無くなる、或いは非常に小さくなるため好ましい。

【0094】

次に、上記の工程を経ることにより完成した、第1の基板109および第2の基板306を、平坦化膜108と絶縁膜110が対向する状態で貼り合わせる（図4（A）参照。）30

【0095】

なお、第1の基板109または第2の基板306の一方あるいは両方は、貼り合わせを行う前に予め表面を洗浄しておくことが好ましい。具体的には、基板表面に対して、塩酸過酸化水素水混合溶液（HPM）、硫酸過酸化水素水混合溶液（SPM）、アンモニア過酸化水素水混合溶液（APM）、希フッ酸（DHF）、フッ酸、過酸化水素水、純水の混合液（FPM）、オゾン水等を用いて超音波洗浄を行う。このような洗浄処理を行うことによって、基板表面の平坦性向上、パーティクルや有機物などを除去することができる。

【0096】

また、第1の基板109と第2の基板306を貼り合わせる前に、貼り合わせに係る表面に対して清浄化処理を行うことが好ましい。清浄化処理としては、ウェット処理、ドライ処理、またはウェット処理とドライ処理の組み合わせを用いることができる。また、異なるウェット処理どうしを組み合わせて用いてもよいし、異なるドライ処理どうしを組み合わせて用いてもよい。40

【0097】

平坦化膜108と絶縁膜110を貼り合わせることによる両者の接合強度は、表面間引力（いわゆる、ファンデルワールス力。）によるところが大きいため、接合面を親水性表面として水酸基を付着させることにより接合強度を高めることができる。親水性処理としては、例えば、酸素プラズマ処理、N<sub>2</sub>プラズマ処理、Arプラズマ処理、オゾン処理、UVオゾン処理およびオゾン水処理のいずれか一つ、或いはこれらの処理を二種以上組み合50

わせて行えばよい。

**【 0 0 9 8 】**

次に、第1の基板109および第2の基板306に対して第2の加熱処理を行う。当加熱処理を行うことで、脆化領域304内にて体積変化が生じ（例えば、イオン照射処理302により半導体基板300中に添加されたイオンが脆化領域304内の欠陥部分に集中して体積変化が生じるなど。）、脆化領域304内にて劈開現象が生じる。なお、熱処理の温度は400以上、耐熱温度の低い基板（支持基板102または半導体基板300のいずれか。）の耐熱温度以下で行なうことが好ましい。例えば、400以上600以下の熱処理を行なうことが好ましい。その後、半導体基板300を第1の基板109から分離することにより、脆化領域304内の任意の位置を劈開面として、半導体基板300より分離された半導体薄膜112が、第1の基板109上に転置される（図4（B）参照。）。

**【 0 0 9 9 】**

上述の半導体薄膜112を分離するための加熱処理と同時に、脆化領域304にストレスを加えて（例えば、脆化領域304が形成された面に対して平行な方向に、脆化領域304に薄い刃物を挿入するなど。）、半導体基板300から半導体薄膜112を機械的に分離する方法を行なうこともよい。これにより、400未満の温度においても半導体基板300から半導体薄膜112を分離することができる。

**【 0 1 0 0 】**

また、上述工程により第1の基板109上に設けられた半導体薄膜112は、図4（B）のように、その表面近傍に脆化領域304の一部が存在している場合がある。脆化領域304は半導体基板300と比較して欠陥領域が多く存在する場合がある。また、半導体薄膜112は半導体基板300から分離された膜であるため、表面平坦性が低い場合がある。

**【 0 1 0 1 】**

このため、半導体基板300から分離した半導体薄膜112に対して脆化領域304の除去および表面の平坦化を目的とした処理を行なうことが好ましい。当該処理方法としては、化学機械研磨（C M P : C hemical M echanical P o l i s h i n g ）処理、ドライエッティング処理または逆スパッタ処理などを用いればよい。

**【 0 1 0 2 】**

また、半導体薄膜112の表面に対してレーザー光を照射することで半導体薄膜112の表面近傍を溶融させて表面を平坦化してもよい。

**【 0 1 0 3 】**

以上の工程により、図1に示す機能性基板100が完成する。

**【 0 1 0 4 】**

**（実施の形態2）**

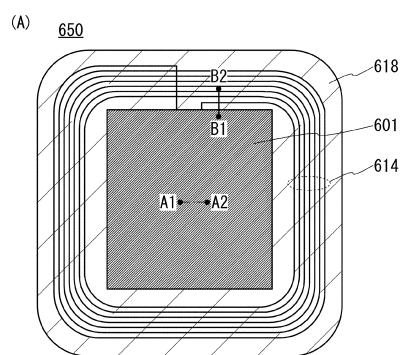

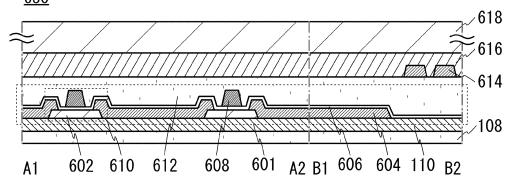

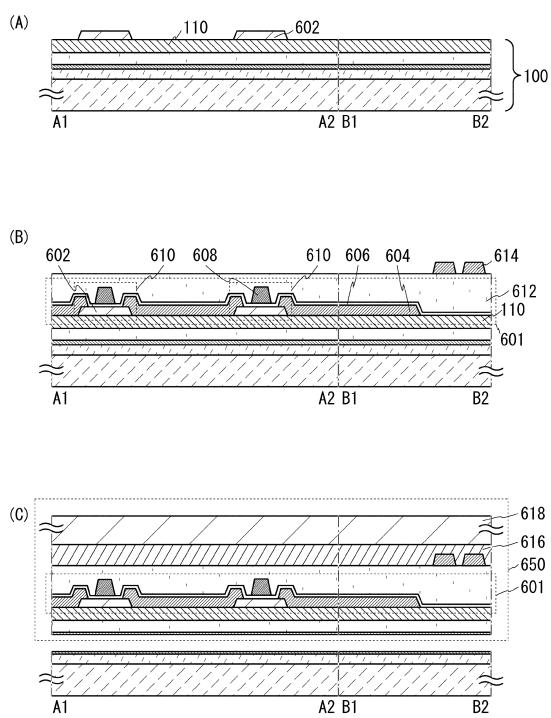

本実施の形態では、実施の形態1に記載した方法により作製された機能性基板100を用いた半導体装置の作製方法の一例として、機能性基板100を用いて形成されたトランジスタを備える個体識別装置650（個体識別装置：R a d i o F r e q u e n c y I D e n t i f i c a t i o n ）の作製方法の一例について説明する。図6は個体識別装置の全体構造を説明する図面であり、図7は図6の一点鎖線A1-A2部分および一点鎖線B1-B2部分の断面図に相当する。

**【 0 1 0 5 】**

**<半導体装置の構成例>**

本実施の形態に記載する個体識別装置650の全体構造は図6（A）に示すように、基材618、半導体回路601およびアンテナとして機能する導電膜614に大別される。なお、図6（A）の一点鎖線A1-A2およびB1-B2に係る部分の断面状態を図6（B）に示す。

**【 0 1 0 6 】**

図6（B）のA1-A2は、半導体回路601の一部を表す断面図であり、トランジスタ610が形成されている。勿論、半導体回路601は当該トランジスタ以外にも様々な素

10

20

30

40

50

子を有していることは言うまでもない。

**【0107】**

トランジスタ 610 を含む半導体回路 601 は、機能性基板 100 より分離された膜（図 6（B）では、平坦化膜 108 および絶縁膜 110。）上に設けられ、半導体層 602、ソース電極およびドレイン電極として機能する導電膜 604、ゲート絶縁膜として機能する絶縁膜 606、ゲート電極として機能する導電膜 608 により構成されている。また、トランジスタ 610 上には絶縁膜 612 が設けられ、絶縁膜 612 上にアンテナとして機能する導電膜 614 が形成され、導電膜 614 上に固定材料 616 が形成され、固定材料 616 上に基材 618 が設けられている。なお、半導体層 602 は、機能性基板 100 の備える半導体薄膜 112 を用いて形成される。

10

**【0108】**

本実施の形態では、半導体回路 601 はアンテナとして機能する導電膜 614 を含んでいないが、導電膜 614 を含んで半導体回路 601 としてもよい。また、導電膜 604 や導電膜 608 の形成時に同時にアンテナとして機能する導電膜を形成してもよい。

**【0109】**

<半導体装置の作製方法>

以下に、図 7 および図 8 を用い、機能性基板 100 を用いて形成されたトランジスタを備える個体識別装置の作製方法について説明を行う。

**【0110】**

まず、実施の形態 1 にて作製した機能性基板 100 の半導体薄膜 112 を加工して、島状の半導体層 602 を形成する（図 6（A）参照。）。

20

**【0111】**

半導体薄膜 112 の加工方法は、フォトリソグラフィ法などの公知の技術を用いればよい。

**【0112】**

次に、絶縁膜 110 および半導体層 602 上に、ソース線（ソース電極とも表現できる。）やドレイン線（ドレイン電極とも表現できる。）として機能する導電膜 604 と、ゲート絶縁膜として機能する絶縁膜 606 と、ゲート電極として機能する導電膜 608 を形成し、トランジスタ 610 を構成する。なお、トランジスタ 610 上には、トランジスタ 610 を覆う絶縁膜 612 および、絶縁膜 612 の開口部を介してトランジスタ 610 と電気的に接続された、アンテナとして機能する導電膜 614 が設けられている（図 6（B）参照。）。

30

**【0113】**

本実施の形態では、導電膜 614 はアンテナとして機能する（つまり、アンテナ内蔵型の個体識別装置。）と記載しているが、アンテナ外付け型の個体識別装置の場合、導電膜 614 を外付けアンテナとの接続部とすればよい。

**【0114】**

なお、半導体回路 601 を内蔵アンテナや外付けアンテナと接続する必要がない場合（例えば、導電膜 604 や導電膜 608 を用いてアンテナが形成されており、当該アンテナを用いて外部の装置とデータの供受を行う。）は、導電膜 614 は必ずしも必要な要素ではない。つまり、本実施の形態に記載の機能性基板 100 を用いて作製する半導体装置は、少なくとも、半導体薄膜 112 を半導体層として用いたトランジスタ含む半導体回路 601 を備えた構造であればよい。

40

**【0115】**

導電膜 604、導電膜 608 および導電膜 614 は、真空蒸着法やスパッタリング法などの物理気相成長法（PVD：Physical Vapor Deposition）やプラズマ CVD 法などの化学気相成長法（CVD：Chemical Vapor Deposition）を用いて金属膜を形成し、当該金属膜をフォトリソグラフィ法などの公知の技術を用いて加工すればよい。

**【0116】**

50

なお、導電膜 604、導電膜 608 および導電膜 614 を形成する金属膜としては、例えば、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンから選ばれた元素を含む金属膜、又は上述した元素を成分とする金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タングステン膜）を単層膜または積層膜として形成すればよい。また、アルミニウム、銅などの金属膜の下側又は上側の一方又は双方にチタン、モリブデン、タングステンなどの高融点金属膜又はそれらの金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タングステン膜）を積層させた膜を用いてもよい。又は、導電性の金属酸化物膜を成膜してもよい。導電性の金属酸化物膜としては酸化インジウム ( $In_2O_3$ )、酸化スズ ( $SnO_2$ )、酸化亜鉛 ( $ZnO$ )、酸化インジウム酸化スズ ( $In_2O_3 - SnO_2$ 、ITOと略記する)、酸化インジウム酸化亜鉛 ( $In_2O_3 - ZnO$ ) 又はこれらの金属酸化物膜に酸化シリコンを含ませたものを用いることができる。

10

#### 【0117】

また、半導体層 602 中に、選択的に n 型または p 型を付与する不純物元素（例えば、リンやボロンなど）をイオンドープ法やイオン注入法などの公知の技術を用いて添加し、n 型トランジスタと p 型トランジスタの作り分けや、低抵抗領域の形成を行ってもよい。

#### 【0118】

トランジスタ 610 のゲート絶縁膜として機能する絶縁膜 606 および絶縁膜 612 としては、下地膜 104 の説明にて記載された材料および方法を参照して形成することができる。

#### 【0119】

また、絶縁膜 612 として、スピンドル法、印刷法、ディスペンス法またはインクジェット法などを用いて塗布し、塗布した材料に応じた硬化処理（例えば、加熱処理や光照射処理など。）を行い形成してもよい。絶縁性を有する有機材料としては、例えば、アクリル樹脂、ポリイミド樹脂、ポリアミド樹脂、ポリアミドイミド樹脂、エポキシ樹脂等の有機樹脂を用いて形成することができる。また、低誘電率材料（low-k 材料）、シロキサン系樹脂、PSG（リンガラス）、BPSG（リンボロンガラス）等を用いることができる。

20

#### 【0120】

次に、絶縁膜 612 および導電膜 614 上に固定材料 616 を用いて基材 618 を貼り合わせた後、第 1 の基板 109 と基材 618 を分離する力（例えば、基材 618 を吸着装置や接着テープなどで台座に固定した状態で、第 1 の基板 109 を基材 618 から剥がすように加える力。）を加え、剥離層 106 を界面として第 1 の基板 109 から半導体回路 601 を含む個体識別装置を分離する。これにより、機能性基板 100 を用いて形成されたトランジスタ 610 を半導体回路 601 中に備える個体識別装置 650 を作製される（図 7 (C) 参照。）。

#### 【0121】

固定材料 616 としては、紫外線硬化型接着剤など光硬化型の接着剤、反応硬化型接着剤、熱硬化型接着剤、嫌気型接着剤など各種硬化型接着剤を用いることができる。

#### 【0122】

なお、固定材料 616 は、スピンドルコーター、スリットコーター、グラビアコーター、ロールコーターなどの各種コーティング装置や、フレキソ印刷装置、オフセット印刷装置、グラビア印刷装置、スクリーン印刷装置、インクジェット装置などの各種印刷装置を用いて薄く均一な膜厚で設けることが好ましい。

40

#### 【0123】

基材 618 としては、支持基板 102 と同様の基板を用いることができるが、当該基板は固定材料 616 を用いて貼り合わせるため、高い精度（例えば、高い平坦性など。）は要求されない。したがって、各種ガラス基板（電子工業用だけでなく一般用も含む。）や各種金属基板を用いることができる。

#### 【0124】

また、樹脂フィルムや金属薄膜などの可とう性を有する基板を用いてもよい。

50

## 【0125】

樹脂フィルムとしては、例えば、ポリエチレンテレフタレート樹脂( P E T )、ポリエーテルスルホン樹脂( P E S )、ポリエチレンナフタレート樹脂( P E N )、ポリビニルアルコール樹脂( P V A )、ポリカーボネート樹脂( P C )、ナイロン樹脂、アクリル樹脂、ポリアクリルニトリル樹脂、ポリエーテルエーテルケトン樹脂( P E E K )、ポリスチレン樹脂( P S )、ポリスルホン樹脂( P S F )、ポリエーテルイミド樹脂( P E I )、ポリアリレート樹脂( P A R )、ポリブチレンテレフタレート樹脂( P B T )、ポリイミド樹脂( P I )、ポリアミド樹脂( P A )、ポリアミドイミド樹脂( P A I )、ポリイソブチレン樹脂( P I B )、塩素化ポリエーテル樹脂( C P )、メラミン樹脂( M F )、エポキシ樹脂( E P )、塩化ビニリデン樹脂( P V d C )、ポリプロピレン樹脂( P P )、ポリアセタール樹脂( P O M )、フッ素樹脂、フェノール樹脂( P F )、フラン樹脂( F F )、不飽和ポリエステル樹脂( F R P )、酢酸セルロース樹脂( C A )、ユリア樹脂( U F )、キシレン樹脂( X R )、ジアリルフタレート樹脂( D A P )、ポリ酢酸ビニル樹脂( P V A c )、ポリエチレン樹脂( P E )、A B S樹脂のうち少なくとも1種類以上を構成成分として含む基板( 薄膜 )を用いることができる。

## 【0126】

上記分離に際し、第1の基板109と基材618のうち剛性の低い基板を吸着装置や接着テープなどにより固定( 好ましくは全面を固定。 )した状態で、他の基板( つまり、剛性の高い基板。 )に分離する力を加えることが好ましい。これにより、分離の際に回路層にクラックや膜剥がれが発生することを抑制できる。

## 【0127】

例えば、基材618として樹脂フィルムや金属薄膜などの可とう性を有する基板( つまり、剛性の低い基板。 )を用いる場合、基材618を固定( 好ましくは全面を固定。 )した状態で、第1の基板109に分離する力を加え、剥離層106を界面として第1の基板109から半導体回路601を含む個体識別装置を分離すればよい。

## 【0128】

なお、分離の際に剥離層106の一部が個体識別装置に残っているため、当該剥離層に対して除去処理を行ってもよい。

## 【0129】

また、当該分離処理により露出した平坦化膜108( 剥離層106を除去していない場合は、剥離層106。 )側を保護することを目的として、平坦化膜108に接して保護基材( 図示しない。 )を更に貼り合わせてもよい。

## 【0130】

以上が、本実施の形態に記載された個体識別装置の作製方法である。

## 【0131】

## ( 実施の形態3 )

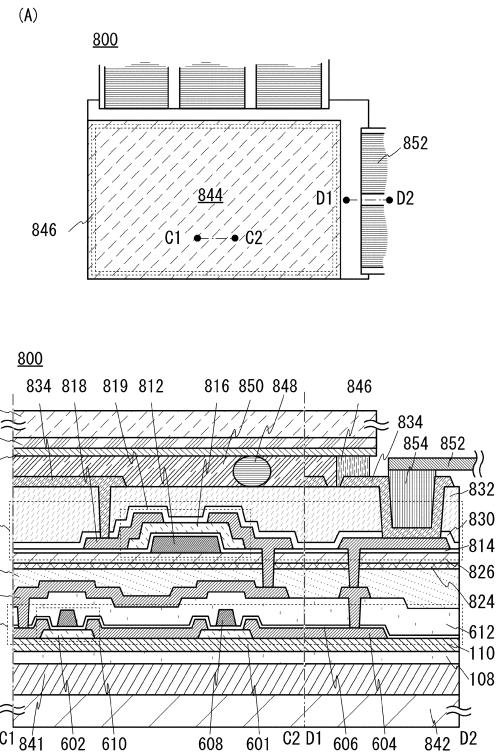

本実施の形態では、実施の形態2に記載した半導体装置とは異なる半導体装置の作製方法として、機能性基板100を用いて形成されたトランジスタを備える表示装置800の作製方法の一例について説明する。図8は表示装置800の全体構造を説明する図であり、図9は、図8の一点鎖線C1-C2部分および一点鎖線D1-D2部分の断面図に相当する。

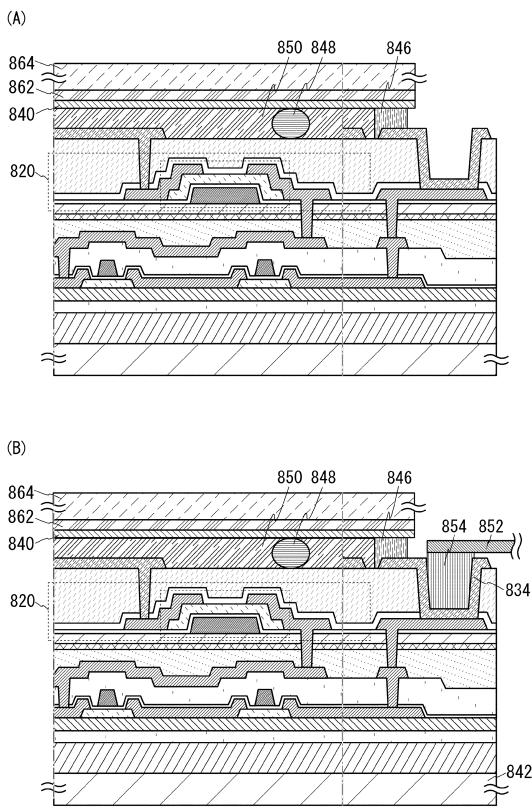

## 【0132】

## &lt; 半導体装置の構成例 &gt;

表示装置の一例として、本実施の形態では、一対の電極間に挟まれた液晶材料に対して電圧印加を行い、外部からの光を用いて画像を表示する表示装置800( 反射型表示装置とも表現できる。 )の構成を、図8を用いて説明する。図8( A )は表示装置の平面図である。また、図8( B )は図8( A )の一点鎖線C1-C2部分およびD1-D2部分の断面を示す図面である。なお、C1-C2断面における回路層の構造を全て記載することは難しいため、図8( B )では、駆動回路部および画像表示部ならびに、外部配線接続部についてのみ記載する。また、図8( A )では、表示装置800の平面状態の図面であるた

10

20

30

40

50

め、対向基板の下に存在する構成要素については記載していない。

**【0133】**

表示装置800は、平坦化膜108、平坦化膜108上の絶縁膜110、絶縁膜110上に設けられ、半導体層602、導電膜604、絶縁膜606、導電膜608を有するトランジスタ610を複数備える第1の回路層810が、固定材料841を介して基材842上に形成されている(図8(B)参照。)。

**【0134】**

また、第1の回路層810上には、ゲート電極として機能する導電膜812、ゲート絶縁膜として機能する絶縁膜814、半導体層816、ソース電極およびドレイン電極として機能する導電膜818を有するトランジスタ819を複数備える第2の回路層820が形成されている(図8(B)参照。)。

10

**【0135】**

また、第1の回路層810と第2の回路層820の間には、絶縁膜612、層間絶縁膜822、層間絶縁膜824、層間絶縁膜826が設けられており、これらの層間絶縁膜に設けられた開口部を介して、導電膜828および導電膜818により第1の回路層810と第2の回路層820(図8では、トランジスタ610とトランジスタ819。)が電気的に接続されている(図8(B)参照。)。

**【0136】**

また、トランジスタ819は絶縁膜830および絶縁膜832で覆われており、絶縁膜832上に形成された導電膜834が、絶縁膜830および絶縁膜832の一部に設けられた開口部を介して導電膜818と電気的に接続されている(図8(B)参照。)。なお、導電膜834は画素電極として機能する。

20

**【0137】**

また、絶縁膜832および導電膜834の上方には、表示装置800の共通電極として機能する導電膜840と、カラーフィルター862が形成された対向基板864が、設けられている。対向基板864は、導電膜834と導電膜840とが対向するように配置され、封止材料846によって、第2の回路層820と貼り合わされている。貼り合わせにより導電膜834と導電膜840間に形成される隙間は、スペーサー848により調整されており、スペーサー848により形成された当該隙間には、液晶材料850が注入されている(図8(B)参照。)。

30

**【0138】**

また、第1の回路層810の構成要素(例えばトランジスタなど。)に対して電源電圧を供給するための外部配線852が、導電材料854を介して導電膜834に接続されている。また、D1-D2部分に設けられた導電膜834は、外部配線852を接続するための接続電極として機能する。当該導電膜は、導電膜828および導電膜818を介して第1の回路層810と電気的に接続されている(図8(B)参照。)。

**【0139】**

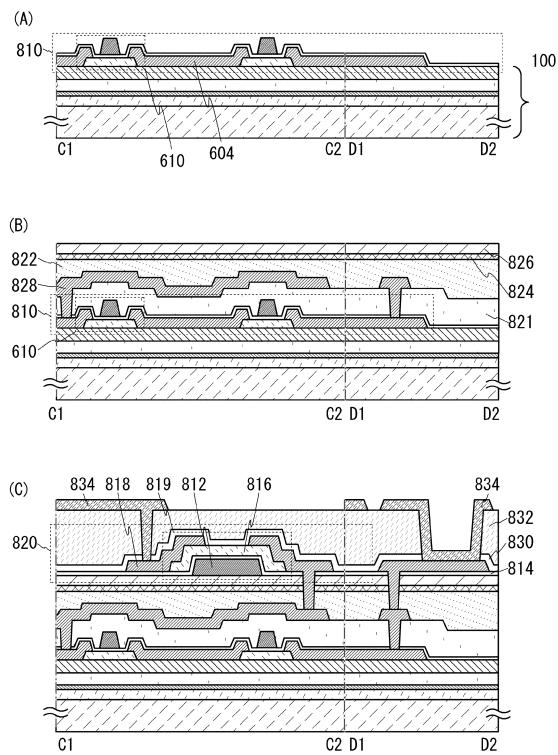

<半導体装置の作製方法>

機能性基板100を用いて形成されたトランジスタを備える表示装置の作製方法について、図9を用いて説明を行う。

40

**【0140】**

まず、実施の形態2と同様の方法で、機能性基板100の半導体薄膜112を用いてトランジスタ610を複数備える第1の回路層810を形成する(図9(A)参照。)。

**【0141】**

次に、トランジスタ610上に絶縁膜612を形成し、絶縁膜612に開口を形成し、開口を介して、トランジスタ610のソース電極及びドレイン電極として機能する導電膜604に電気的に接続するように導電膜828を形成する。次に、絶縁膜612及び導電膜828上に、層間絶縁膜822、層間絶縁膜824、層間絶縁膜826を形成する(図9(B)参照。)。

**【0142】**

50

絶縁膜 612、層間絶縁膜 822、層間絶縁膜 824 および層間絶縁膜 826 は、下地膜 104 の説明にて記載された材料および方法を参照して形成することができる。

#### 【0143】

なお、層間絶縁膜 822 は当該膜よりも下層の構造を作製することにより生じる表面凹凸を緩和する効果がある。当該効果を高めるためには、絶縁膜 612 の説明にて記載された材料（各種の樹脂）および方法を参照して層間絶縁膜 822 を形成することが好ましい。

#### 【0144】

次に、層間絶縁膜 826 上にトランジスタ 819 を複数備える第2の回路層 820 を形成し、トランジスタ 819 上に絶縁膜 830、絶縁膜 832 および画素電極として機能する導電膜 834 を形成する。なお、トランジスタ 819 は、ゲート電極として機能する導電膜 812、ゲート絶縁膜として機能する絶縁膜 814、半導体層 816、ソース電極およびドレイン電極として機能する導電膜 818 を用いて構成されている。また、D1 - D2 部分に設けられた導電膜 834 は、後の工程にて外部配線 852 を接続するための接続電極として機能する（図9（C）参照。）。

#### 【0145】

絶縁膜 814、絶縁膜 830 および絶縁膜 832 としては、下地膜 104 の説明にて記載された材料および方法を参照して形成することができる。

#### 【0146】

なお、絶縁膜 832 は当該膜よりも下層の構造を作製することにより生じる表面凹凸を緩和する効果がある。当該効果を高めるためには、絶縁膜 612 の説明にて記載された材料（各種の樹脂）および方法を参照して絶縁膜 832 を形成することが好ましい。

#### 【0147】

導電膜 812、導電膜 818 および導電膜 834 としては、導電膜 604 の説明にて記載された材料および方法を参照して形成することができる。なお、導電膜 818 は、層間絶縁膜 822、層間絶縁膜 824、層間絶縁膜 826 および絶縁膜 830 に設けた開口部を介して導電膜 828 と電気的に接続され、第1の回路層 810 と第2の回路層 820 が電気的に接続されている。

#### 【0148】

半導体層 816 としては、公知の半導体材料（例えば、シリコン、ゲルマニウムまたは化合物半導体など。化合物半導体としては、例えば、GaAs、InP、SiC、ZnSe、GaN、SiGeなどを用いることができる。）を用いて成膜を行い、当該膜を半導体薄膜 112 の説明にて記載された加工方法を参照して形成すればよい。

#### 【0149】

また、トランジスタ 819 の半導体層 816 として、酸化物半導体材料を用いてもよい。酸化物半導体材料は、比較的低温で成膜しても高い移動度を有し、また、大面積に対しての成膜法も確立されているため、例えばトランジスタ 819 を表示装置の表示部におけるスイッチング素子として用いる場合には適した選択であるといえる。

#### 【0150】

酸化物半導体材料としては、例えば、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn-Zn系酸化物、In-Mg系酸化物、In-Ga系酸化物、三元系金属の酸化物であるIn-Ga-Zn系酸化物（IGZOとも表記する）、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、In-Hf-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、四元系金属の酸化物であるIn-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物を用いることができる。

10

20

30

40

50

**【0151】**

なお、ここで、例えば、In-Ga-Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

**【0152】**

また、酸化物半導体材料として、 $InMO_3(ZnO)_m$  ( $m > 0$ 、且つ、 $m$ は整数でない) で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素又は複数の金属元素を示す。また、酸化物半導体材料として、 $In_2SnO_5(ZnO)_n$  ( $n > 0$ 、且つ、 $n$ は整数) で表記される材料を用いてもよい。

**【0153】**

以下では、酸化物半導体材料を用いて製膜された半導体層816の構造について説明する。

**【0154】**

酸化物半導体膜は、非単結晶酸化物半導体膜と単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、CAAC-OS (C Axis Aligned Crystalline Oxide Semiconductor) 膜、多結晶酸化物半導体膜、微結晶酸化物半導体膜、非晶質酸化物半導体膜などをいう。

**【0155】**

まずは、CAAC-OS膜について説明する。

**【0156】**

CAAC-OS膜は、c軸配向した複数の結晶部を有する酸化物半導体膜の一つである。

**【0157】**

CAAC-OS膜を透過型電子顕微鏡(TEM: Transmission Electron Microscope)によって観察すると、明確な結晶部同士の境界、即ち結晶粒界(グレインバウンダリーともいう。)を確認することができない。そのため、CAAC-OS膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

**【0158】**

CAAC-OS膜を、試料面と概略平行な方向からTEMによって観察(断面TEM観察)すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、CAAC-OS膜の膜を形成する面(被形成面ともいう。)または上面の凹凸を反映した形状であり、CAAC-OS膜の被形成面または上面と平行に配列する。

**【0159】**

一方、CAAC-OS膜を、試料面と概略垂直な方向からTEMによって観察(平面TEM観察)すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

**【0160】**

断面TEM観察および平面TEM観察より、CAAC-OS膜の結晶部は配向性を有していることがわかる。

**【0161】**

なお、CAAC-OS膜に含まれるほとんどの結晶部は、一辺が100nm未満の立方体内に収まる大きさである。従って、CAAC-OS膜に含まれる結晶部は、一辺が10nm未満、5nm未満または3nm未満の立方体内に収まる大きさの場合も含まれる。ただし、CAAC-OS膜に含まれる複数の結晶部が連結することで、一つの大きな結晶領域を形成する場合がある。例えば、平面TEM像において、 $2500\text{ nm}^2$ 以上、 $5\mu\text{m}^2$ 以上または $1000\mu\text{m}^2$ 以上となる結晶領域が観察される場合がある。

**【0162】**

CAAC-OS膜に対し、X線回折(XRD:X-Ray Diffraction)装置を用いて構造解析を行うと、例えば $InGaZnO_4$ の結晶を有するCAAC-OS膜のout-of-plane法による解析では、回折角(2)が $31^\circ$ 近傍にピークが

10

20

30

40

50

現れる場合がある。このピークは、 $\text{InGaZnO}_4$  の結晶の(009)面に帰属されることから、CAAC-OS 膜の結晶が c 軸配向性を有し、c 軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

#### 【0163】

一方、CAAC-OS 膜に対し、c 軸に概略垂直な方向から X 線を入射させる in-plane 法による解析では、 $2\theta$  が  $56^\circ$  近傍にピークが現れる場合がある。このピークは、 $\text{InGaZnO}_4$  の結晶の(110)面に帰属される。 $\text{InGaZnO}_4$  の単結晶酸化物半導体膜であれば、 $2\theta$  を  $56^\circ$  近傍に固定し、試料面の法線ベクトルを軸(c 軸)として試料を回転させながら分析(スキャン)を行うと、(110)面と等価な結晶面に帰属されるピークが 6 本観察される。これに対し、CAAC-OS 膜の場合は、 $2\theta$  を  $56^\circ$  近傍に固定してスキャンした場合でも、明瞭なピークが現れない。10

#### 【0164】

以上のことから、CAAC-OS 膜では、異なる結晶部間では a 軸および b 軸の配向は不規則であるが、c 軸配向性を有し、かつ c 軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、前述の断面 TEM 観察で確認された層状に配列した金属原子の各層は、結晶の ab 面に平行な面である。

#### 【0165】

なお、結晶部は、CAAC-OS 膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶の c 軸は、CAAC-OS 膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、CAAC-OS 膜の形状をエッティングなどによって変化させた場合、結晶の c 軸が CAAC-OS 膜の被形成面または上面の法線ベクトルと平行にならないこともある。20

#### 【0166】

また、CAAC-OS 膜中において、c 軸配向した結晶部の分布が均一でなくてもよい。例えば、CAAC-OS 膜の結晶部が、CAAC-OS 膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりも c 軸配向した結晶部の割合が高くなることがある。また、CAAC-OS 膜に不純物を添加する場合、不純物が添加された領域が変質し、部分的に c 軸配向した結晶部の割合の異なる領域が形成されることもある。

#### 【0167】

なお、 $\text{InGaZnO}_4$  の結晶を有する CAAC-OS 膜の out-of-plane 法による解析では、 $2\theta$  が  $31^\circ$  近傍のピークの他に、 $2\theta$  が  $36^\circ$  近傍にもピークが現れる場合がある。 $2\theta$  が  $36^\circ$  近傍のピークは、CAAC-OS 膜中の一部に、c 軸配向性を有さない結晶が含まれることを示している。CAAC-OS 膜は、 $2\theta$  が  $31^\circ$  近傍にピークを示し、 $2\theta$  が  $36^\circ$  近傍にピークを示さないことが好ましい。30

#### 【0168】

CAAC-OS 膜は、不純物濃度の低い酸化物半導体膜である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体膜の主成分以外の元素である。特に、シリコンなどの、酸化物半導体膜を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体膜から酸素を奪うことで酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径(または分子半径)が大きいため、酸化物半導体膜内部に含まれると、酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体膜に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。40

#### 【0169】

また、CAAC-OS 膜は、欠陥準位密度の低い酸化物半導体膜である。例えば、酸化物半導体膜中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

#### 【0170】

不純物濃度が低く、欠陥準位密度が低い(酸素欠損の少ない)ことを、高純度真性または50

実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないため、キャリア密度を低くすることができる。従って、当該酸化物半導体膜を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリアトラップが少ない。そのため、当該酸化物半導体膜を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体膜のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体膜を用いたトランジスタは、電気特性が不安定となる場合がある。

10

#### 【0171】

また、CAC-OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

#### 【0172】

次に、微結晶酸化物半導体膜について説明する。

#### 【0173】

微結晶酸化物半導体膜は、TEMによる観察像では、明確に結晶部を確認することができない場合がある。微結晶酸化物半導体膜に含まれる結晶部は、1nm以上100nm以下、または1nm以上10nm以下の大きさであることが多い。特に、1nm以上10nm以下、または1nm以上3nm以下の微結晶であるナノ結晶（nc：nanocrysta<sup>20</sup>l）を有する酸化物半導体膜を、nc-OS（nanocrystalline Oxide Semiconductor）膜と呼ぶ。また、nc-OS膜は、例えば、TEMによる観察像では、結晶粒界を明確に確認できない場合がある。

#### 【0174】

nc-OS膜は、微小な領域（例えば、1nm以上10nm以下の領域、特に1nm以上3nm以下の領域）において原子配列に周期性を有する。また、nc-OS膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。従つて、nc-OS膜は、分析方法によっては、非晶質酸化物半導体膜と区別が付かない場合がある。例えば、nc-OS膜に対し、結晶部よりも大きい径のX線を用いるXRD装置を用いて構造解析を行うと、out-of-plane法による解析では、結晶面を示すピークが検出されない。また、nc-OS膜に対し、結晶部よりも大きいプローブ径（例えば50nm以上）の電子線を用いる電子線回折（制限視野電子線回折ともいう。）を行うと、ハローパターンのような回折像が観測される。一方、nc-OS膜に対し、結晶部の大きさと近いか結晶部より小さいプローブ径（例えば1nm以上30nm以下）の電子線を用いる電子線回折（ナノビーム電子線回折ともいう。）を行うと、スポットが観測される。また、nc-OS膜に対しナノビーム電子線回折を行うと、円を描くように（リング状に）輝度の高い領域が観測される場合がある。また、nc-OS膜に対しナノビーム電子線回折を行うと、リング状の領域内に複数のスポットが観測される場合がある。

20

#### 【0175】

nc-OS膜は、非晶質酸化物半導体膜よりも規則性の高い酸化物半導体膜である。そのため、nc-OS膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低くなる。ただし、nc-OS膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、nc-OS膜は、CAC-OS膜と比べて欠陥準位密度が高くなる。

30

#### 【0176】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、微結晶酸化物半導体膜、CAC-OS膜のうち、二種以上を有する積層膜であってもよい。

#### 【0177】

CAC-OS膜は、例えば、多結晶である酸化物半導体スパッタリング用ターゲットを用い、スパッタリング法によって成膜する。当該スパッタリング用ターゲットにイオンが衝突すると、スパッタリング用ターゲットに含まれる結晶領域がa-b面を境界として劈

40

50

開し、a - b面に平行な面を有する平板状またはペレット状のスパッタリング粒子としてスパッタリング用ターゲットから剥離することがある。この場合、当該平板状（またはペレット状。）のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、C A A C - O S 膜を成膜することができる。

#### 【0178】

また、半導体層816をC A A C - O S 膜として成膜するために、以下の条件を適用することが好ましい。

#### 【0179】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物濃度（水素、水、二酸化炭素および窒素など。）を低減すればよい。また、成膜ガス中の不純物濃度（水素、水、二酸化炭素および窒素など。）を低減すればよい。具体的には、露点が-80以下、好ましくは-100以下である成膜ガスを用いる。10

#### 【0180】

また、成膜時の基板加熱温度を高めることで、基板付着後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板加熱温度を100以上740以下、好ましくは200以上500以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起り、スパッタリング粒子の平らな面が基板に付着する。

#### 【0181】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30体積%以上、好ましくは100体積%とする。成膜ガス中の酸素割合を高めることで、C A A C - O S 膜中に余分な原子（例えば、希ガス原子など。）が含まれないため、C A A C - O S 膜が形成されやすくなる。20

#### 【0182】

スパッタリング用ターゲットの一例として、In-Ga-Zn-O 化合物ターゲットについて以下に示す。

#### 【0183】

InO<sub>x</sub> 粉末、GaO<sub>y</sub> 粉末およびZnO<sub>z</sub> 粉末を所定のmol数比で混合し、加圧処理後、1000以上1500以下の温度で加熱処理することで多結晶であるIn-Ga-Zn-O 化合物ターゲットとする。なお、X、YおよびZは任意の正数である。ここで、所定のmol数比は、例えば、InO<sub>x</sub> 粉末、GaO<sub>y</sub> 粉末およびZnO<sub>z</sub> 粉末が、2:2:1、8:4:3、3:1:1、1:1:1、4:2:3または3:1:2である。なお、粉末の種類、およびその混合するmol数比は、作製するスパッタリング用ターゲットによって適宜変更すればよい。30

#### 【0184】

なお、酸化物半導体膜中の酸素欠損をできるだけ少なくことが好ましいため、成膜雰囲気中のガス種に占める酸素ガスの割合が高い状態で成膜することが好ましく、装置内に酸素を導入することが可能で、かつ、ガス流量の調整ができるスパッタリング装置を用いることが好ましいといえる。そして、スパッタリング装置の成膜チャンバー内への導入ガスは、全体の90%以上を酸素ガスとして、酸素ガスに加えて他のガスを用いる場合は、当該ガスは希ガスを用いることが望ましい。また、より好ましくは成膜チャンバー内への導入ガスを酸素ガスのみとし、成膜雰囲気中のガス種に占める酸素ガスの割合を極力100%に近づけることが望ましい。40

#### 【0185】

また、酸化物半導体膜に水素が多量に含まれると、酸化物半導体と結合することによって、水素の一部がドナーとなり、キャリアである電子を生じてしまう。これにより、トランジスタのしきい値電圧がマイナス方向にシフトしてしまう。そのため、酸化物半導体膜620において、水素濃度は、 $5 \times 10^{-8}$  atoms/cm<sup>3</sup>未満、好ましくは $1 \times 10^{-9}$ 50

$1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、より好ましくは  $5 \times 10^{17}$  atoms / cm<sup>3</sup> 以下、更に好ましくは  $1 \times 10^{16}$  atoms / cm<sup>3</sup> 以下とすることが望ましい。なお、上述の酸化物半導体膜 620 中の水素濃度は、二次イオン質量分析法 (S I M S : Second ary Ion Mass Spectrometry) で測定されるものである。

#### 【0186】

このため、半導体層 816 として酸化物半導体膜を成膜する際は、成膜に用いるガスとして、水、水素、水酸基又は水素化物などの不純物が含まれないことが好ましく、純度が 6 N 以上好ましくは 7 N 以上（即ち、ガス中の不純物濃度を 1 ppm 以下、好ましくは 0.1 ppm 以下）のガスを用いることが好ましい。また、成膜室内の水分（水、水蒸気、水素、水酸基または水素化物を含む）を除去するために、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段は、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水 (H<sub>2</sub>O) など水素原子を含む化合物（より好ましくは炭素原子を含む化合物も）等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる水素、水分などの不純物の濃度を低減できる。

#### 【0187】

加えて、半導体層 816 に接する膜（例えば、絶縁膜 814 や絶縁膜 830 など。）にも水素が極力含まれていないことが好ましい。具体的には半導体層と接する膜を加熱して TDS 測定を行った場合において、当該膜からの水素分子の放出量のピークが  $5.0 \times 10^{21}$  [分子 / cm<sup>3</sup>] 以下、好ましくは  $4.0 \times 10^{21}$  [分子 / cm<sup>3</sup>] 以下、より好ましくは  $1.0 \times 10^{21}$  [分子 / cm<sup>3</sup>] 以下である膜を用いることが望ましい。

#### 【0188】

また、半導体層 816 に接する膜には窒素も極力含まれていないことが好ましい。これは、水素の場合と同様に、酸化物半導体と結合することによって、窒素の一部がドナーとなり、キャリアである電子を生じてしまうためである。そのため、半導体層と接する膜を加熱して TDS 測定を行った場合において、当該膜からのアンモニア分子の放出量のピークが  $5.0 \times 10^{21}$  [分子 / cm<sup>3</sup>] 以下、好ましくは  $1.0 \times 10^{21}$  [分子 / cm<sup>3</sup>] 以下、より好ましくは  $8.0 \times 10^{20}$  [分子 / cm<sup>3</sup>] 以下である膜を用いることが望ましい。

#### 【0189】

また、半導体層 816 として酸化物半導体膜を成膜する際は、酸化物半導体膜中のアルカリ金属またはアルカリ土類金属の濃度が、 $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、さらによくは  $2 \times 10^{16}$  atoms / cm<sup>3</sup> 以下であることが望ましい。これは、上述の水素や窒素と同様に、アルカリ金属及びアルカリ土類金属が、酸化物半導体と結合するとキャリアが生成されることがあり、トランジスタのオフ電流の上昇の原因となるためである。

#### 【0190】

なお、酸化物半導体膜は、複数の酸化物半導体膜が積層された構造でもよい。

#### 【0191】

例えば、酸化物半導体膜を、第 1 の酸化物半導体膜、第 2 の酸化物半導体膜および第 3 の酸化物半導体膜の積層として、各々を異なる組成としてもよい。例えば、第 1 の酸化物半導体膜および第 3 の酸化物半導体膜に三元系金属の酸化物を用い、第 2 の酸化物半導体膜に二元系金属の酸化物を用いる、または、第 1 の酸化物半導体膜および第 3 の酸化物半導体膜に二元系金属の酸化物を用い、第 2 の酸化物半導体膜に三元系金属の酸化物を用い。

#### 【0192】

また、第 1 の酸化物半導体膜、第 2 の酸化物半導体膜および第 3 の酸化物半導体膜の構成元素を同一とし、組成を異なしてもよい。例えば、第 1 の酸化物半導体膜および第 3 の酸化物半導体膜の原子数比を In : Ga : Zn = 1 : 1 : 1 とし、第 2 の酸化物半導体膜の原子数比を In : Ga : Zn = 3 : 1 : 2 としてもよい。また、第 1 の酸化物半導体膜および第 3 の酸化物半導体膜の原子数比を In : Ga : Zn = 1 : 3 : 2 とし、第 2 の酸

10

20

30

40

50

化物半導体膜の原子数比を I n : G a : Z n = 3 : 1 : 2 としてもよい。

【 0 1 9 3 】

この時、第 2 の酸化物半導体膜は I n と G a の含有率を I n > G a とするときよい。また第 1 の酸化物半導体膜および第 3 の酸化物半導体膜の I n と G a の含有率を I n < G a とするときよい。

【 0 1 9 4 】

酸化物半導体では主として重金属の s 軌道がキャリア伝導に寄与しており、 I n の含有率を多くすることにより s 軌道のオーバーラップが多くなる傾向があるため、 I n > G a の組成となる酸化物は I n < G a の組成となる酸化物と比較して高い移動度を備える。また、 G a は I n と比較して酸素欠損の形成エネルギーが大きく酸素欠損が生じにくいため、 I n < G a の組成となる酸化物は I n > G a の組成となる酸化物と比較して安定した特性を備える。

10

【 0 1 9 5 】

なお、酸化物半導体膜に接して酸化物半導体膜とは異なる膜（図中では、絶縁膜 8 1 4 や絶縁膜 8 3 0 など。）を形成する際に、酸化物半導体膜に接して形成される膜から酸化物半導体膜中に不純物が拡散する恐れがある。たとえば、絶縁膜 8 1 4 や絶縁膜 8 3 0 中に含まれるシリコンやカーボンなどが酸化物半導体膜中に拡散すると、トランジスタの電気特性に悪影響を及ぼす可能性がある。

【 0 1 9 6 】

しかしながら、上述のように酸化物半導体膜を積層構造とし、高い移動度を備える酸化物半導体膜（つまり、 I n > G a の組成となる酸化物半導体膜。本実施の形態では第 2 の酸化物半導体膜に相当する。）に接して、当該酸化物半導体膜よりも酸素欠損が少なく安定した特性を備える酸化物半導体膜（つまり、 I n < G a の組成となる酸化物半導体膜。本実施の形態では第 1 の酸化物半導体膜および第 3 の酸化物半導体膜に相当する。）を形成し、酸化物半導体膜に接する膜から高い移動度を備える酸化物半導体膜を離すことにより、不純物拡散に起因したトランジスタの電気特性（例えば、移動度の低下など。）の悪影響を抑制することができる。したがって、トランジスタの移動度および信頼性を高めることが可能となる。

20

【 0 1 9 7 】

なお、導電膜 8 1 2 および半導体層 8 1 6 と重なる絶縁膜 8 3 0 上に、トランジスタ 8 1 9 のバックゲートとして機能する導電膜を形成してもよい。当該導電膜を形成することにより、トランジスタ 8 1 9 のしきい値をコントロールできるため、トランジスタ 8 1 9 がノーマリーオン状態となることを抑制できる。

30

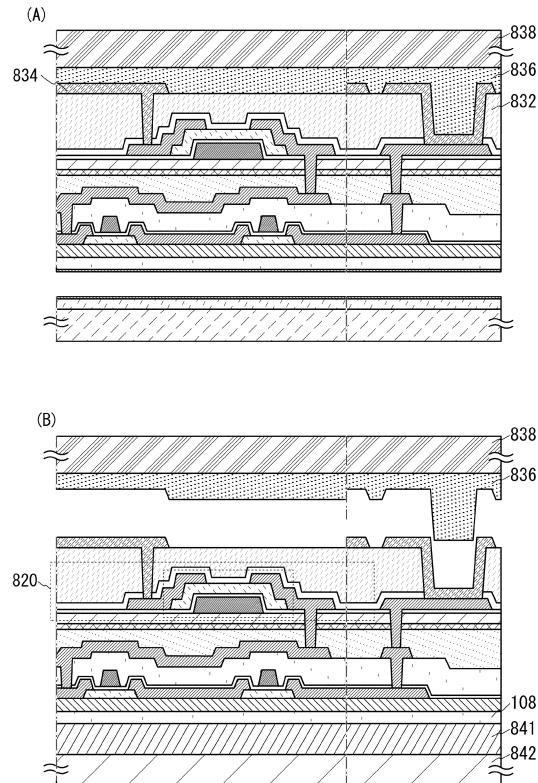

【 0 1 9 8 】

次に、絶縁膜 8 3 2 および導電膜 8 3 4 上に、仮固定材料 8 3 6 を用いて仮固定基板 8 3 8 を貼り合わせた後、第 1 の基板 1 0 9 と仮固定基板 8 3 8 を分離する力（例えば、仮固定基板 8 3 8 を吸着装置や接着テープなどで台座に固定した状態で、第 1 の基板 1 0 9 を仮固定基板 8 3 8 から剥がすように加える力。）を加え、剥離層 1 0 6 を界面として、剥離層 1 0 6 上に設けられた回路を、第 1 の基板 1 0 9 から分離する（図 1 0 ( A ) 参照。）。これにより、裏面側（仮固定基板 8 3 8 を貼り合っていない側。）には平坦化膜 1 0 8 （剥離層 1 0 6 を除去していない場合は、剥離層 1 0 6。）が露出する。

40

【 0 1 9 9 】

仮固定材料 8 3 6 としては、水や溶媒に可溶な性質を有する接着剤（または、当該接着剤が両面に塗布されたフィルム。）、通電により可塑化する性質を有する接着剤（または、当該接着剤が両面に塗布されたフィルム。）、紫外線照射により可塑化する性質を有する接着剤（または、当該接着剤が両面に塗布されたフィルム。）、紫外線照射により接着性の低下する性質を有する接着剤（または、当該接着剤が両面に塗布されたフィルム。）などの、必要に応じて仮固定基板 8 3 8 を剥がすことのできる材料を用いる。

【 0 2 0 0 】

なお、仮固定材料 8 3 6 は、固定材料 6 1 6 と同様の方法で設けることができる。

50

**【0201】**

仮固定材料836としては、支持基板102と同様の基板を用いることができるが、当該基板は第1の基板109から剥離した膜を一時的に固定しておくための基板であるため、高い精度（例えば、高い平坦性など。）は要求されない。したがって、各種ガラス基板（電子工業用だけでなく一般用も含む。）や各種金属基板を用いることができる。

**【0202】**

次に、露出した平坦化膜108（剥離層106を除去していない場合は、剥離層106。）に固定材料841を用いて基材842を貼り合わせた後、仮固定材料836および仮固定基板838を分離する（図10（B）参照。）。なお、図面では仮固定材料836は絶縁膜832および導電膜834の形状と同様の形で分離されているが、例えば水や溶媒に可溶な性質を有する接着剤などを用いた場合は仮固定材料836の形状は図面とは異なるものとなる。10

**【0203】**

固定材料841および基材842は、固定材料616および基材618と同様の材料を用いることができる。

**【0204】**

なお、基材842として樹脂フィルムや金属薄膜などの可とう性を有する材料を用いることにより、後の工程にて行う対向基板や外部配線の貼り合わせなどの処理により回路層にダメージが入る（例えば、回路層にクラックが発生するなど。）場合は、基材842に仮固定材料836を用いて更に仮固定基板838を貼り合わせて剛性を高めておくことが好ましい。20

**【0205】**

次に、カラーフィルター862と、表示装置800の共通電極として機能する導電膜840とが形成された対向基板864を、導電膜834と導電膜840とが対向するように配置する。その後、封止材料846によって、第2の回路層820と、対向基板864とを貼り合わせる。なお、貼り合わせに際し、導電膜834と導電膜840の間の隙間サイズを調整するために、スペーサー848を挟んだ状態で貼り合わせを行う。そして、スペーサー848により形成された隙間に液晶材料850を注入する（図11（A）参照。）。

**【0206】**

本実施の形態に記載の表示装置800は反射型表示装置であるため、対向基板864側から画像を視認する。そのため、対向基板864として透光性を有する基板を用いる。当該基板としては、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板、天然石英基板、合成石英基板などを用いることもできる。また、樹脂フィルムを用いることもできる。30

**【0207】**

カラーフィルター862、スペーサー848および液晶材料850については、材料や形成方法に特段の限定はなく、公知技術を用いることができる。また、封止材料846の材料および形成方法、ならびに、対向基板864の貼り合わせ方法についても、公知の技術を用いることができる。

**【0208】**

次に、接続電極として機能する導電膜840と、外部配線852とを導電材料854を用いて電気的に接続する（図11（B）参照。）。

**【0209】**

導電材料854および外部配線852としては、様々な公知材料を用いることができるが、例えば、導電材料854として異方性導電樹脂（ACP：Anisotropic Conductive Paste）や異方性導電フィルム（ACF：Anisotropic Conductive Film）を用いることができ、外部配線852としてはフレキシブルプリント基板（FPC：Flexible Printed Circuits）を用いることができる。

**【0210】**

10

20

30

40

50

なお、基材 842 として樹脂フィルムや金属薄膜などの可とう性を有する材料を用い、基材 842 に仮固定材料 836 を用いて更に仮固定基板 838 を貼り合わせて剛性を高めて居る場合は、上述の外部配線 852 を貼り合わせた後に、仮固定材料 836 および仮固定基板 838 を適宜分離すればよい。

#### 【0211】

以上の工程を経ることにより、図 8 に記載の表示装置 800 を形成できる。

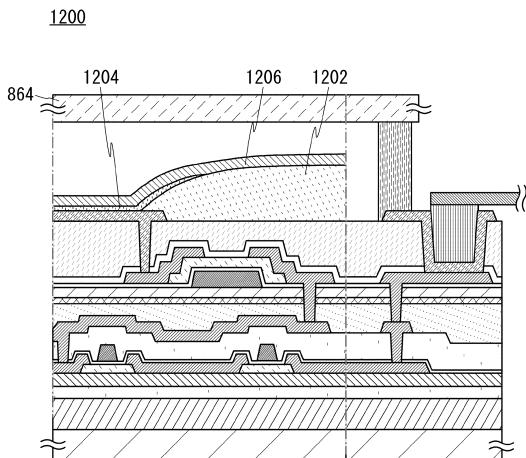

#### 【0212】

なお、本実施の形態における表示装置 800 は、導電膜 834 と導電膜 840 間に液晶材料を挟み、電極に対して電源電圧印加を行うことにより画像を表示する、いわゆる液晶表示装置の構成を記載したが、図 12 に示すように、導電膜 834 の端部を覆う状態に隔壁 1202 が形成され、導電膜 834 上に少なくとも発光性の有機化合物を含む発光層を有する EL 層 1204 が形成され、EL 層 1204 上に、EL 層 1204 を挟む状態に導電膜 834 と重なる導電膜 1206 が形成された構成の画像表示部を備える表示装置 1200 としてもよい。なお、図 12 に示す表示装置 1200 において、対向基板 864 に、カラーフィルターが設けられた構成であってもよい。

10

#### 【0213】

なお、隔壁 1202、EL 層 1204 および導電膜 1206 は公知の材料を用いて適宜形成すればよい。

#### 【0214】

##### (実施の形態 4)

20

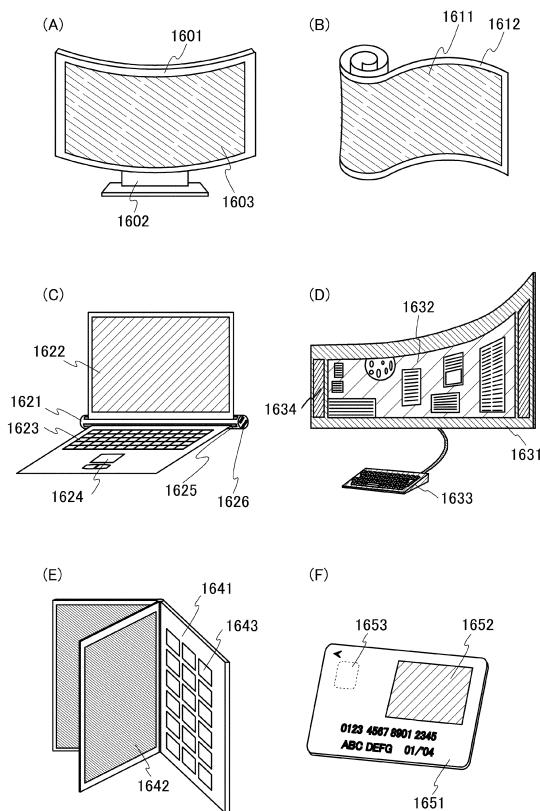

実施の形態 2 や実施の形態 3 に開示する半導体装置は、さまざまな電子機器（遊技機も含む）に適用することができる。電子機器としては、例えば、テレビジョン装置（テレビ、またはテレビジョン受信機ともいう）、コンピュータ用などのモニタ、デジタルカメラ、デジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機（携帯電話、携帯電話装置ともいう）、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。上記実施の形態で説明した半導体装置を具備する電子機器の例について説明する。

#### 【0215】

図 13 (A) はディスプレイ 1601 であり、支持台 1602、表示部 1603 を含む。表示部 1603 は可撓性を有する基板を用いて形成されており、軽量で薄型のディスプレイを実現できる。また、表示部 1603 を湾曲させることも可能であり、支持台 1602 から取り外して湾曲した壁に沿ってディスプレイを取り付けることも可能である。実施の形態 3 にて記載した方法を用いて作製した半導体装置を、表示部 1603 に用いることによって、可撓性を有するディスプレイを作製することができる。このように、可とう性を有するディスプレイは、フラットな面はもちろん湾曲した部分にも設置することが可能となるため、様々な用途に用いることができる。

30

#### 【0216】

図 13 (B) は巻き取り可能なディスプレイ 1611 であり、表示部 1612 を含む。実施の形態 3 にて記載した方法を用いて作製した半導体装置を、表示部 1612 に用いることによって、巻き取りが可能で薄型の大型ディスプレイを作製することができる。巻き取り可能なディスプレイ 1611 は可撓性を有する基板を用いて形成されているため、表示部 1612 と共に折り畳んだり、巻き取ったりして持ち運ぶことが可能である。そのため、巻き取り可能なディスプレイ 1611 が大型である場合でも折り畳んだり、巻き取ったりして鞄に入れて持ち運ぶことができる。

40

#### 【0217】

図 13 (C) は、シート型のコンピュータ 1621 であり、表示部 1622、キーボード 1623、タッチパッド 1624、外部接続ポート 1625、電源プラグ 1626 等を含んでいる。実施の形態 3 にて記載した方法を用いて作製した半導体装置を、表示部 1622 に用いることによって、薄型またはシート型のコンピュータを作製することができる。表示部 1622 は可撓性を有する基板を用いて形成されており、軽量で薄型のコンピュー

50

タを実現できる。また、シート型のコンピュータ 1621 の本体部分に収納スペースを設けることによって表示部 1622 を本体に巻き取って収納することができる。また、キーボード 1623 も可撓性を有するように設けることによって、表示部 1622 と同様にシート型のコンピュータ 1621 の収納スペースに巻き取って収納することができ、持ち運びが便利になる。また、使用しない場合にも折り畳むことによって場所をとらずに収納することが可能となる。

#### 【0218】

図 13 (D) は、20 ~ 120 インチの大型の表示部を有する表示装置 1631 であり、操作部であるキーボード 1633、表示部 1632、スピーカー 1634 等を含む。また、表示部 1632 は可撓性を有する基板を用いて形成されており、キーボード 1633 を取り外して表示装置 1631 を折り畳んだり巻き取ったりして持ち運ぶことが可能である。また、キーボード 1633 と表示部 1632 との接続は無線で行うことができ、例えば、湾曲した壁に沿って表示装置 1631 を取り付けながらキーボード 1633 で無線によって操作することができる。

#### 【0219】

図 13 (D) に示す例では、実施の形態 3 にて記載した方法を用いて作製した半導体装置を、表示部 1632 に用いている。これによって、薄型の大型表示装置を作製することができる。

#### 【0220】

図 13 (E) は電子ブック 1641 であり、表示部 1642、操作キー 1643 等を含む。またモデムが電子ブック 1641 に内蔵されていても良い。表示部 1642 は可撓性基板を用いて形成されており、折り曲げたり巻き取ったりすることができる。そのため、電子ブックの持ち運びも場所をとらずに行うことができる。さらに、表示部 1642 は文字等の静止画像はもちろん動画も表示することができる。

#### 【0221】

図 13 (E) に示す例では、実施の形態 3 にて記載した方法を用いて作製した半導体装置を、表示部 1642 に用いている。これによって、薄型の電子ブックを作製することができる。

#### 【0222】

図 13 (F) は I C カード 1651 であり、表示部 1652、個体識別装置 1653 等を含む。表示部 1652 は可撓性基板を用いて軽量、薄型のシート状になっているため、カードの表面に張り付けて形成することができる。また、I C カードが個体識別装置を用いて外部から取得した情報を表示部 1652 に表示することができる。

#### 【0223】

図 13 (F) に示す例では、実施の形態 2 にて記載した方法を用いて作製した半導体装置を、個体識別装置 1653 に、実施の形態 3 にて記載した方法を用いて作製した半導体装置を、表示部 1652 に用いている。これによって、薄型の I C カードを作製することができる。

#### 【0224】

このように、本発明に係る半導体装置を電子機器に用いることにより、曲げ等の外力が加わり応力が生じた場合であっても、トランジスタ等の素子の脆化を低減することができるため、半導体装置の歩留まりや信頼性を向上させることができる。

#### 【0225】

以上のように、本発明の適用範囲はきわめて広く、あらゆる分野の電子機器や情報表示手段に用いることができる。

#### 【0226】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

#### 【符号の説明】

#### 【0227】

|         |         |    |

|---------|---------|----|

| 1 0 2   | 支持基板    |    |

| 1 0 4   | 下地膜     |    |

| 1 0 5 a | 金属膜     |    |

| 1 0 5 b | 表面変質処理  |    |

| 1 0 5 c | 絶縁膜     |    |

| 1 0 6   | 剥離層     |    |

| 1 0 8   | 平坦化膜    |    |

| 1 0 9   | 基板      |    |

| 1 1 0   | 絶縁膜     |    |

| 1 1 2   | 半導体薄膜   | 10 |

| 3 0 0   | 半導体基板   |    |

| 3 0 2   | イオン照射処理 |    |

| 3 0 4   | 脆化領域    |    |

| 3 0 6   | 基板      |    |

| 6 0 1   | 半導体回路   |    |

| 6 0 2   | 半導体層    |    |

| 6 0 4   | 導電膜     |    |

| 6 0 6   | 絶縁膜     |    |

| 6 0 8   | 導電膜     |    |

| 6 1 0   | トランジスタ  | 20 |

| 6 1 2   | 絶縁膜     |    |

| 6 1 4   | 導電膜     |    |

| 6 1 6   | 固定材料    |    |

| 6 1 8   | 基材      |    |

| 6 2 0   | 酸化物半導体膜 |    |

| 6 5 0   | 個体識別装置  |    |

| 8 0 0   | 表示装置    |    |

| 8 1 0   | 回路層     |    |

| 8 1 2   | 導電膜     |    |

| 8 1 4   | 絶縁膜     | 30 |

| 8 1 6   | 半導体層    |    |

| 8 1 8   | 導電膜     |    |

| 8 1 9   | トランジスタ  |    |

| 8 2 0   | 回路層     |    |

| 8 2 2   | 層間絶縁膜   |    |

| 8 2 4   | 層間絶縁膜   |    |

| 8 2 6   | 層間絶縁膜   |    |

| 8 2 8   | 導電膜     |    |

| 8 3 0   | 絶縁膜     |    |

| 8 3 2   | 絶縁膜     | 40 |

| 8 3 4   | 導電膜     |    |

| 8 3 6   | 仮固定材料   |    |

| 8 3 8   | 仮固定基板   |    |

| 8 4 0   | 導電膜     |    |

| 8 4 1   | 固定材料    |    |

| 8 4 2   | 基材      |    |

| 8 4 6   | 封止材料    |    |

| 8 4 8   | スペーサー   |    |

| 8 5 0   | 液晶材料    |    |

| 8 5 2   | 外部配線    | 50 |

|         |          |    |

|---------|----------|----|

| 8 5 4   | 導電材料     |    |

| 8 6 2   | カラーフィルター |    |

| 8 6 4   | 対向基板     |    |

| 1 2 0 0 | 表示装置     |    |

| 1 2 0 2 | 隔壁       |    |

| 1 2 0 4 | E L 層    |    |

| 1 2 0 6 | 導電膜      |    |

| 1 6 0 1 | ディスプレイ   | 10 |

| 1 6 0 2 | 支持台      |    |

| 1 6 0 3 | 表示部      |    |

| 1 6 1 1 | ディスプレイ   |    |

| 1 6 1 2 | 表示部      |    |

| 1 6 2 1 | コンピュータ   |    |

| 1 6 2 2 | 表示部      |    |

| 1 6 2 3 | キーボード    |    |

| 1 6 2 4 | タッチパッド   |    |

| 1 6 2 5 | 外部接続ポート  |    |

| 1 6 2 6 | 電源プラグ    |    |

| 1 6 3 1 | 表示装置     |    |

| 1 6 3 2 | 表示部      | 20 |

| 1 6 3 3 | キーボード    |    |

| 1 6 3 4 | スピーカー    |    |

| 1 6 4 1 | 電子ブック    |    |

| 1 6 4 2 | 表示部      |    |

| 1 6 4 3 | 操作キー     |    |

| 1 6 5 1 | I C カード  |    |

| 1 6 5 2 | 表示部      |    |

| 1 6 5 3 | 個体識別装置   |    |

【図1】

【図2】

【図3】

【図4】

【図5】

(B)

【図6】

(B)

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

審査官 柴山 将隆

(56)参考文献 特開2008-288578(JP,A)

特開2010-258364(JP,A)

特開2001-189460(JP,A)

特開2004-056143(JP,A)

特開2009-135453(JP,A)

特開2009-027150(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/02

H01L 21/336

H01L 27/12

H01L 29/786