OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

(11) Número de publicación: **2 330 761**

(51) Int. Cl.:

**H03D 7/14** (2006.01)

(12)

### TRADUCCIÓN DE PATENTE EUROPEA

T3

(96) Número de solicitud europea: **05725330 .4**

(96) Fecha de presentación : **11.03.2005**

(97) Número de publicación de la solicitud: **1735905**

(97) Fecha de publicación de la solicitud: **27.12.2006**

(54) Título: **Mezclador y sintonizador de supresión armónica.**

(30) Prioridad: **12.03.2004 US 552864 P**

**16.12.2004 US 636584 P**

(73) Titular/es: **R.F. Magic Inc.**

**6290 Sequence Drive**

**San Diego, California 92121, US**

(45) Fecha de publicación de la mención BOPI:

**15.12.2009**

(72) Inventor/es: **Shah, Peter**

(45) Fecha de la publicación del folleto de la patente:

**15.12.2009**

(74) Agente: **Isern Jara, Jorge**

**ES 2 330 761 T3**

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín europeo de patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre concesión de Patentes Europeas).

# ES 2 330 761 T3

## DESCRIPCIÓN

Mezclador y sintonizador de supresión armónica.

### 5 Campo de la invención

Esta invención se refiere a los mezcladores de radiofrecuencia y particularmente a mezcladores para suprimir señales de conversión armónicas usadas en los sintonizadores de radiofrecuencia.

### 10 Antecedentes de la invención

Un mezclador realiza una operación combinada en dos señales de entrada para crear una señal de salida. En las aplicaciones de radiofrecuencia (RF), una señal de entrada de oscilador local (LO) se mezcla con la otra señal de entrada para lograr el traslado de la frecuencia, generalmente llamada super-conversión o sub-conversión. En una configuración de super-conversión, la señal de banda de base de entrada se convierte ascendente en una frecuencia intermedia (IF) o señal RF, o una señal IF se convierte ascendente en una señal RF. En una configuración de subconversión, la señal de entrada RF se subconvierte en una señal IF o una señal IF o RF se subconvierte en una señal de banda de base. Una señal de banda de base puede ser tanto una señal de valor real simple o una señal de valor complejo que comprende una señal de fase de entrada (I) o una señal de fase de cuadratura (Q). La conversión hacia o desde una señal compleja de banda de base requiere dos mezcladores, un mezclador se conduce mediante una fase de entrada LO y el otro mezclador se conduce mediante una fase de cuadratura LO. En el caso de la super-conversión, los otros puertos del mezclador se conducen por las señales de banda de base I y Q, y la salida de los dos mezcladores se suman para crear una señal IF o RF. En el caso de la subconversión, la IF o RF de entrada se divide para conducir dos mezcladores, y la salida de los dos mezcladores produce las señales de banda de base I y Q.

25 Un sintonizador es una combinación de circuitos que se usan para seleccionar y subconvertir un solo canal, o banda de canales, desde un canal de división de frecuencia de banda amplia múltiple (FDM). Ejemplos de usos de sintonizadores incluyen transmisiones inalámbrica (OTA), vía satélite, y receptores de televisión por cable. Un sintonizador selecciona un canal independiente de TV, una banda directa, desde el espectro de banda ancha RF, y produce una señal de banda limitada hacia una TV u otro circuito para un proceso adicional.

30 Un sintonizador utiliza varias combinaciones de mezcladores, amplificadores (LNAs) RF de bajo ruido, filtros preseleccionados RF, portador de rastreador y otras formas de control de frecuencia, la frecuencia sintetizada LO o LO controlada por un circuito de control de frecuencia automática (AFC), y filtros para sintonizar un canal seleccionado.

35 Las configuraciones comunes del sintonizador incluyen una conversión doble, conversión simple, y conversión directa. Un sintonizador de conversión simple, también llamado heterodino, convierte una señal RF recibida, en una señal IF utilizando una frecuencia LO que es la suma de o diferencia entre las frecuencias de señal RF e IF. La señal IF se subconvierte a una señal de banda de base fuera del sintonizador para la demodulación o puede ser demodulada directamente desde una señal IF. Un sintonizador de conversión doble convierte las señales RF entrantes en una primera señal IF, seguida por una segunda conversión para una segunda señal IF o para una señal de banda de base. La segunda señal IF se demodula o subconvierte en una señal de banda de base fuera del sintonizador. Un sintonizador de conversión directa, también llamado un homodino, convierte la señal RF directamente en una banda de base, utilizando una frecuencia LO que es la misma que la frecuencia de señal RF.

40 45 Se describen en el arte previo, sintonizadores en las siguientes referencias, cada una está incorporada en la presente mediante la referencia: Birleson *et al.*, patente U.S. 6,177,964, expedida el 1/23/2001, titulada “Sintonizador de televisión integrado de banda ancha” la cual describe un mezclador de super-conversión y un mezclador de sub-conversión en serie para convertir una señal RF en una señal IF; Rotzoll, patente U.S. 5,737,035 expedida 4/7/1998, titulada “Sintonizador de televisión altamente integrado en un circuito sencillo” que describe a un receptor que utiliza un mezclador de super-conversión y un mezclador de rechazo de imagen de subconversión en serie para producir una señal IF.

50 55 Para evitar la degradación de la señal que el sintonizador procesa, los mezcladores deben tener características de bajo ruido. Se usan dos tipos comunes de mezcladores en los sintonizadores: Al multiplicar los mezcladores se produce una salida análoga desde las entradas análogas; las dos entradas se multiplican linealmente para producir la salida. Los mezcladores de conmutación no son lineales debido a la conmutación discontinua de la señal de entrada con LO para producir la salida. Al multiplicar los mezcladores se tiene un ruido más alto en la banda, mientras que los mezcladores de conmutación tienen un ruido menor pero tienen una fuerte ganancia en armónico de la frecuencia LO, 60 específicamente armónico dispar debido a la acción de conmutación de ondas cuadráticas. La ganancia de conversión armónica es indeseable en los sistemas de banda ancha tales como la televisión debido a que las señales de interferencia pudieran residir en frecuencias que son convertidas por las armónicas LO en la frecuencia de salida del canal de interés. Las interferencias armónicas podrían ser otros canales de televisión, produciendo una interferencia dentro del canal sintonizado.

65 60 Los mezcladores en el arte previo se describen en las siguientes referencias, cada una incorporada en la presente mediante la referencia: Somayajula, patente U.S. 6,560,451, expedida 5/6/2003, titulada “Square wave analog multiplier” que describe las modalidades del mezclador análogo de ondas cuadráticas para la operación del heterodino;

Filoramo *et al.*, patente U.S. 6,433,647, expedida el 8/13/2002, titulada “Low noise I-Q mixer” que describe un modulador de fase I-Q de cuadratura de bajo ruido I-Q que tiene un par de estados de celda Gilbert conducidas por una onda LO cuadrática. Atherly *et al.* U.S. patent 5,140,198, expedida el 8/18/1992, titulada “Imagen canceling mixer circuit on a integrated circuit chip” la cual describe mezcladores doblemente balanceados inyectados con una fase de cuadratura LO, seguido por otro cambio de fase de 90 grados en la salida de un mezclador y sumando las dos salidas del mezclador para rechazar uno de los términos de mezclado.

Una metodología para resolver el problema de la conversión armónica es el uso de mezcladores de rechazo armónico. Esta metodología se ha descrito en Weldon *et al.*, “A 1.75-GHz highly integrated narrow-band CMOS transmitter with harmonic-rejection mixers”, IEEE Journal of Solid-state circuits, Vol. 36, No. 12, el Dic. 2001. Este trabajo describe el uso de un mezclador de rechazo armónico en un transmisor. El mezclador de rechazo armónico descrito utiliza una sinusode de amplitud cuantificada de 3 bit para LO. Esto cambia los armónicos de LO a 7 veces la frecuencia LO, relajando los requerimientos de filtro posterior al mezclador. La aproximación de la sinusode se forma usando las ondas cuadráticas de cambio de fases para conducir 3 mezcladores con una conducción de corriente ponderada, y las salidas son corrientes sumadas para producir la salida del mezclador compuesto. Un grupo separado de mezcladores se usa para los componentes I y Q de la señal. Esta arquitectura del mezclador se configura para una super-conversión en un transmisor y no es adecuada para el uso en señal de subconversión RF o IF para una señal de banda de base compleja.

## 20 Breve descripción de la invención

La presente invención utiliza una pluralidad de mezcladores conmutadores para formar un mezclador de supresión armónica para la subconversión de una señal RF dentro de una salida I y Q. La característica de supresión armónica suprime señales de alta frecuencia que interferirían con la frecuencia de sintonía deseada. Una serie de señales digitales alternadas impulsa el puerto LO de cada mezclador. El puerto RF de cada mezclador es controlado con la misma señal o una versión proporcional separada en memoria intermedia de la señal de entrada. Alternativamente, la división de la señal podría lograrse mediante una partición resistiva de la señal de entrada que conduce a los registros del mezclador. Una suma ponderada de las señales del mezclador individual produce la señal de salida del mezclador de supresión armónica. El mezclador de supresión armónica puede ser incluido en un circuito integrado monolítico junto con otros componentes de un sintonizador completo.

En las distintas configuraciones descritas, cada uno de los mezcladores individuales se alimenta de una señal que es proporcional a la señal de entrada RF; ya sea usando memorias intermedias, particiones resistivas, conexión directa, u otras redes de conducción que acoplan la señal de entrada a cada uno de los mezcladores en la proporción deseada.

35 Las etapas de ganancia en la entrada o salida o ambas de cada mezcla ponderan las señales antes de sumar la pluralidad de salidas del mezclador en un nodo sumador, que puede ser una suma de corriente o de voltaje. Los valores de ganancia pueden ir de menos de uno a más de uno. La ponderación produce una respuesta sinusode del conductor digital LO. En una modalidad, un solo banco de mezcladores se utiliza con dos bancos independientes de fases de ganancia acoplados a las salidas de los mezcladores. Las salidas de cada banco de etapas de ganancia forman la salida I y la salida Q, respectivamente. Alternativamente, dos bancos de mezcladores pueden ser utilizados, teniendo cada uno coeficientes de ponderación en las entradas o salidas o ambas. La suma de señales de varios mezcladores puede ayudar a promediar características no ideales de mezcladores causadas por las variaciones del proceso. La pérdida de LO causada por desajustes en cada mezclador puede reducirse debido a la cancelación estadística de variaciones. Además, la suma también puede cancelar ciertas propiedades determinísticas no ideales. Por ejemplo, si los mezcladores producen una corriente directa sistemática (DC) de desplazamiento o punto de intercepción de segundo orden sistemático (IP2), entonces esto puede ser cancelado en el proceso de sumado.

40 En una modalidad alternativa, las entradas RF pueden ser ponderadas y las salidas de los mezcladores sumadas directamente juntas o se podrían utilizar combinaciones de ponderación en entradas y salidas. La ponderación de las entradas del mezclador puede realizarse haciendo variar el parámetro de transconductancia de los mezcladores, sin necesidad de componentes adicionales.

45 Un generador de precisión de multifase LO se usa para producir las señales digitales escalonadas LO, que pueden ser ondas cuadráticas. En una modalidad, una máquina de estado produce una pluralidad de salidas alternas que pueden re-cronometrarse por un banco de registro para reducir el sesgo de la señal, proporcionando una relación del ciclo LO fraccional precisa. Una modalidad de un generador LO opera a una frecuencia de cronometración que es un múltiple de la frecuencia LO deseada para producir la señal de onda cuadrática de multifase LO.

50 La presente invención del mezclador de supresión armónica es adecuada para uso en un sintonizador completo donde el rango de sintonía puede cubrir un rango de expansión de frecuencia de 50 MHz a 860 MHz, o más amplia. Para facilitar este amplio rango de sintonía, la presente invención del mezclador puede tener coeficientes reconfigurables y mezcladores combinables efectivos. El número de mezcladores independientes puede variar de 8 o más, hasta 4, a 2 o cualquier número adecuado de mezcladores.

55 En una modalidad ejemplar, a bajas frecuencias de sintonía, una configuración de mezclador 8 puede usarse para lograr buena supresión de señales armónicas que se encuentran dentro de las señales de banda de TV ocupadas para prevenir la interferencia de canales superiores dentro de canales inferiores. A frecuencias de sintonía más altas, los

armónicos se encuentran fuera de las señales de banda activa de TV o los armónicos pueden ser suprimidos mediante el filtrado en el sintonizador. Por consiguiente, menos supresión armónica es necesaria en el mezclador, y es posible utilizar un mezclador de configuración 4 o un mezclador de configuración 2, que reduce la frecuencia requerida de las señales del generador de cronometración LO.

5 La Patente US 6 397 051 expone una imagen dual del sistema de rechazo en el cual se generan las primeras y segundas señales que corresponden a cada canal de las señales RF recibidas. Cada una de las primeras y segundas señales incluyen una señal deseada, una señal de imagen, y una señal de intermodulación, las últimas dos se reducen usando un acoplador híbrido y un controlador.

10 La solicitud de patente de E.U.A. 2004-0005869 publicada describe un transmisor que tiene un mezclador de rechazo armónico y un circuito de fase cerrada de salida RF en una arquitectura de super-conversión de dos etapas, y un receptor de conversión directa.

15 La patente de E.U.A. 6 226 509 describe un método para reducir las frecuencias de imagen, por el que se selecciona la mezcla de frecuencia tal que la señal de frecuencia intermedia generada tenga una frecuencia de desplazamiento relativa hacia DC que es substancialmente la de un solo espacio de canal entre las señales del portador de frecuencia adyacente.

20 J Wheldon *et al.* “A 1.75 GHz Highly Integrated Narrow-BAnd CMOS Transmitter with Harmonic-Rejection Mixers” (IEEE Tour, of Solid State Circuits, vol. 36, no. 12, Dec, 2001, pgs 2003-2015) describe un transmisor basado en CMOS IQ que emplea un mezclador armónico.

25 La patente US 6 433 647 describe un modulador de cuadratura de fase IQ que tiene un par o etapas de entrada de celda Gilbert conducidas por una línea de alimentación de voltaje y que reciben las respectivas señales de comando de ondas cuadráticas desde un oscilador local.

## Breve descripción de las figuras

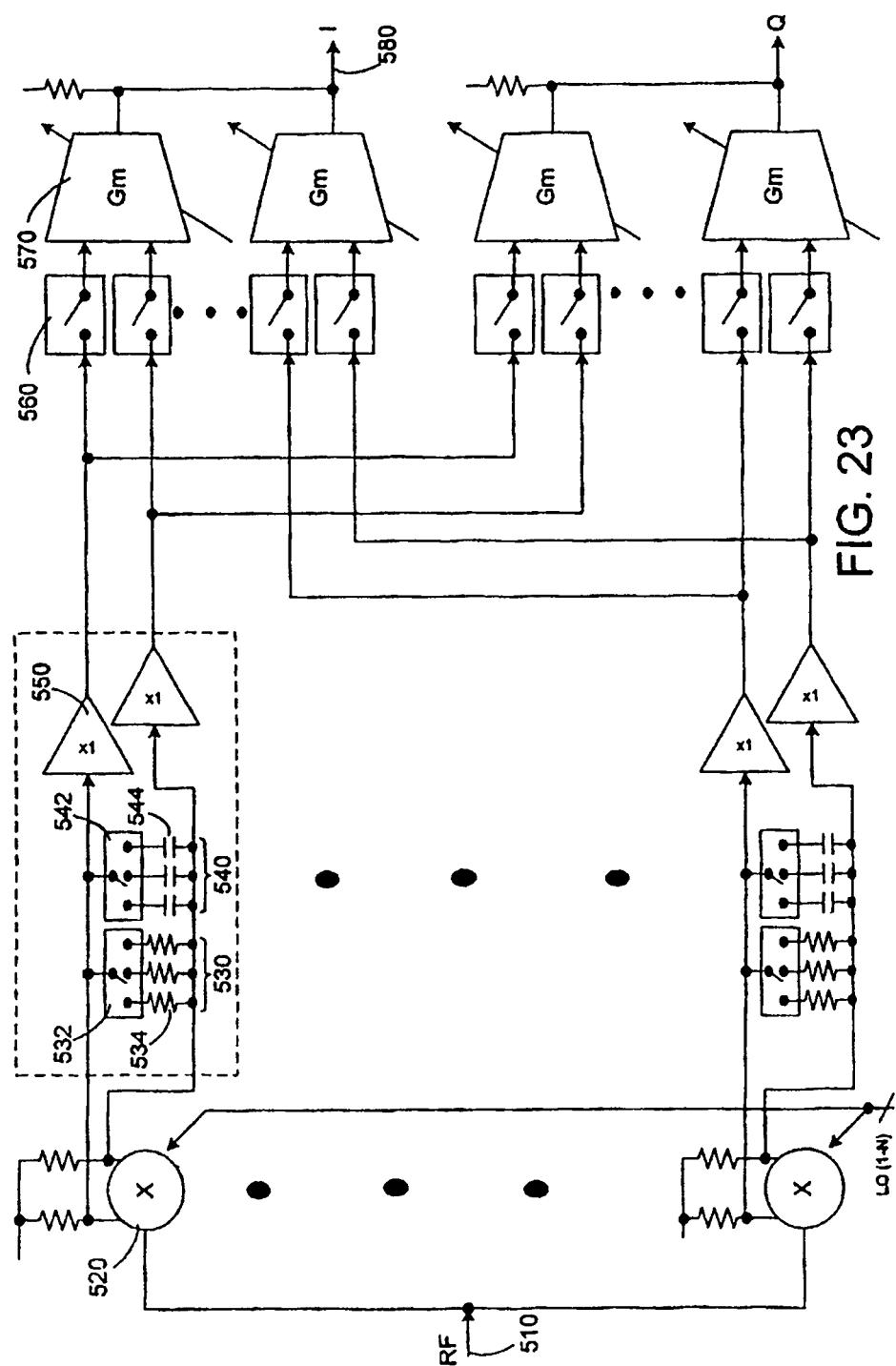

- 30 La figura 1 muestra un mezclador de supresión armónica según la presente invención.

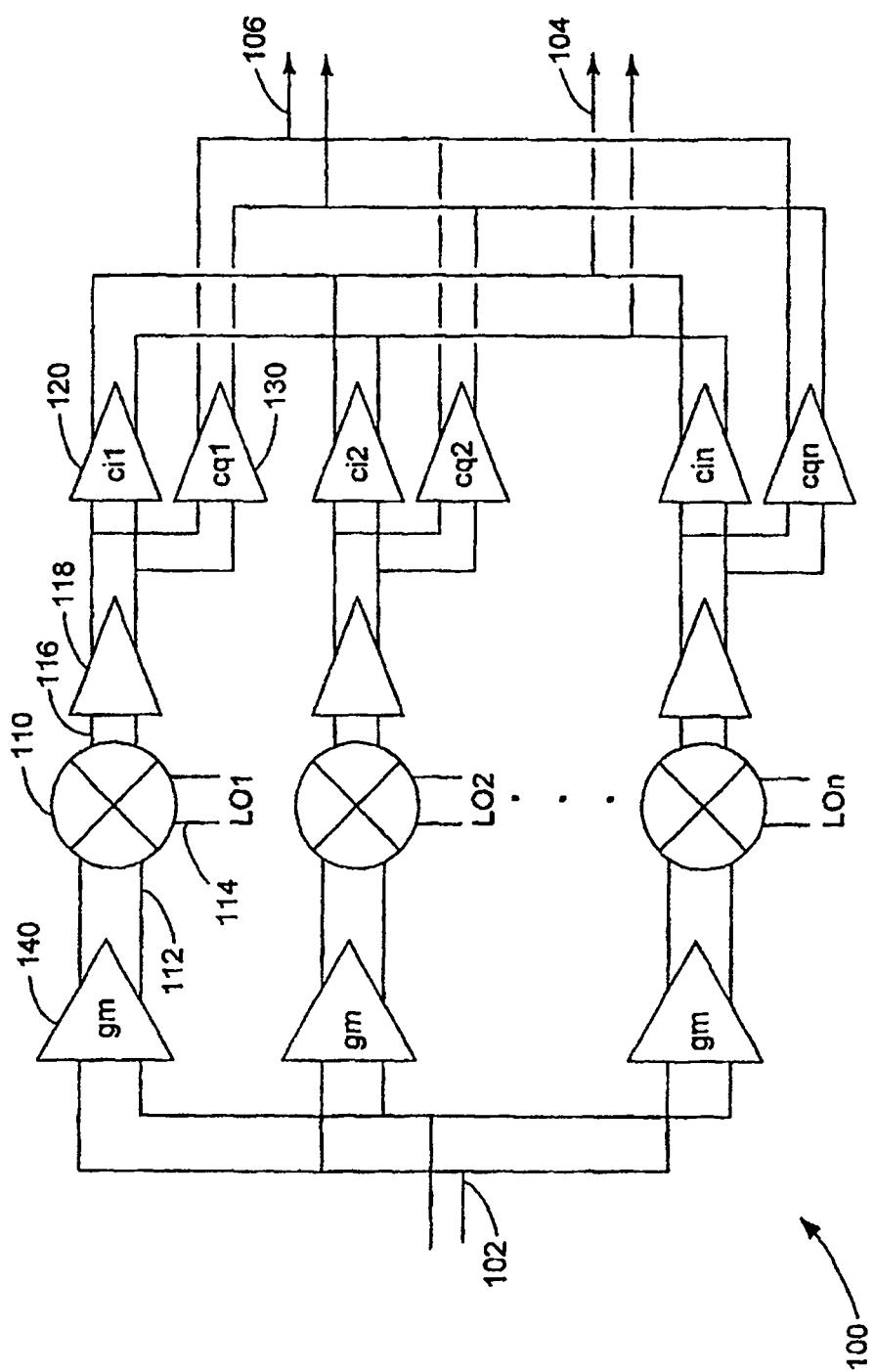

- La figura 2 muestra un generador LO de onda cuadrática escalonada.

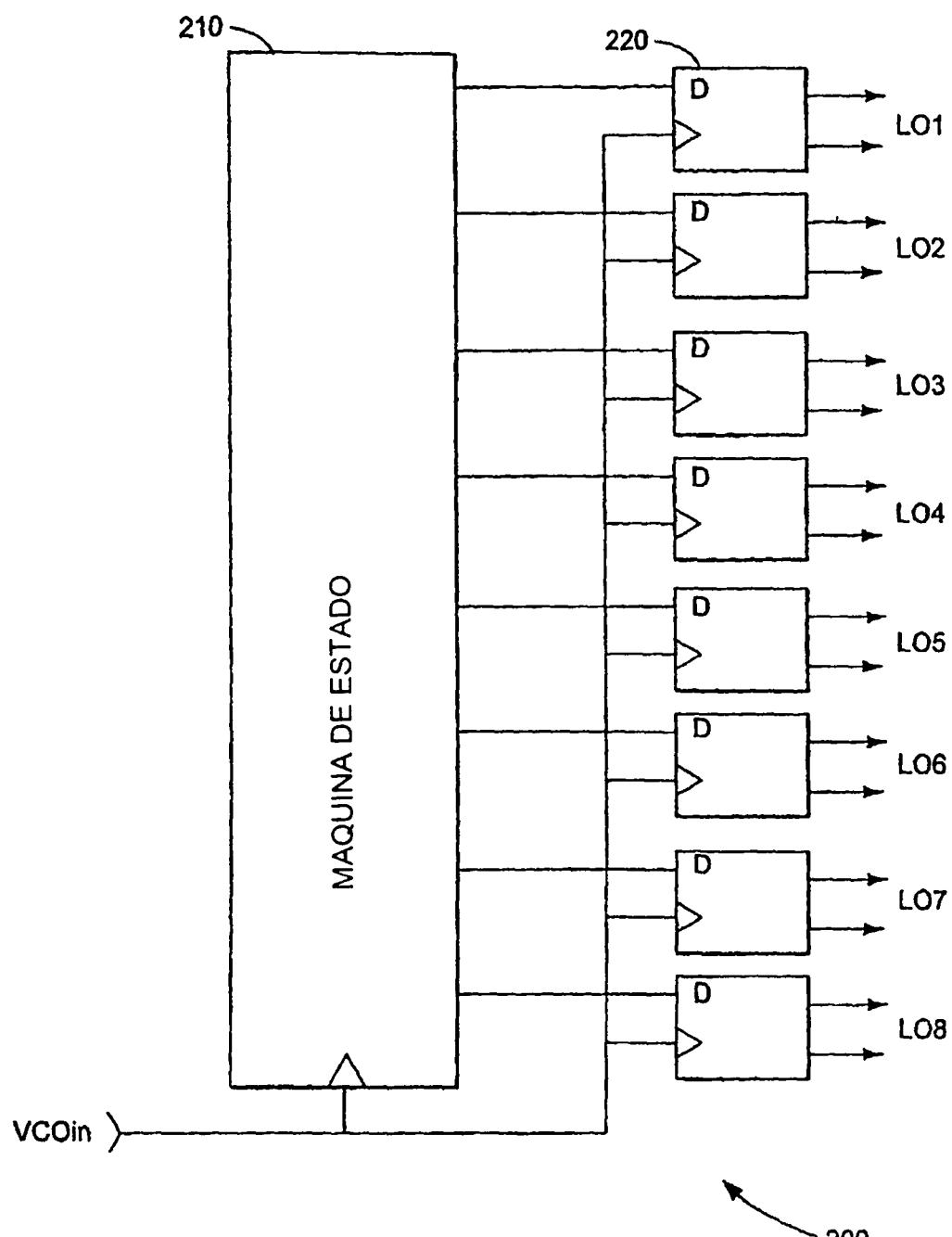

- 35 La figura 3 muestra el componente de la máquina de estado del generador LO.

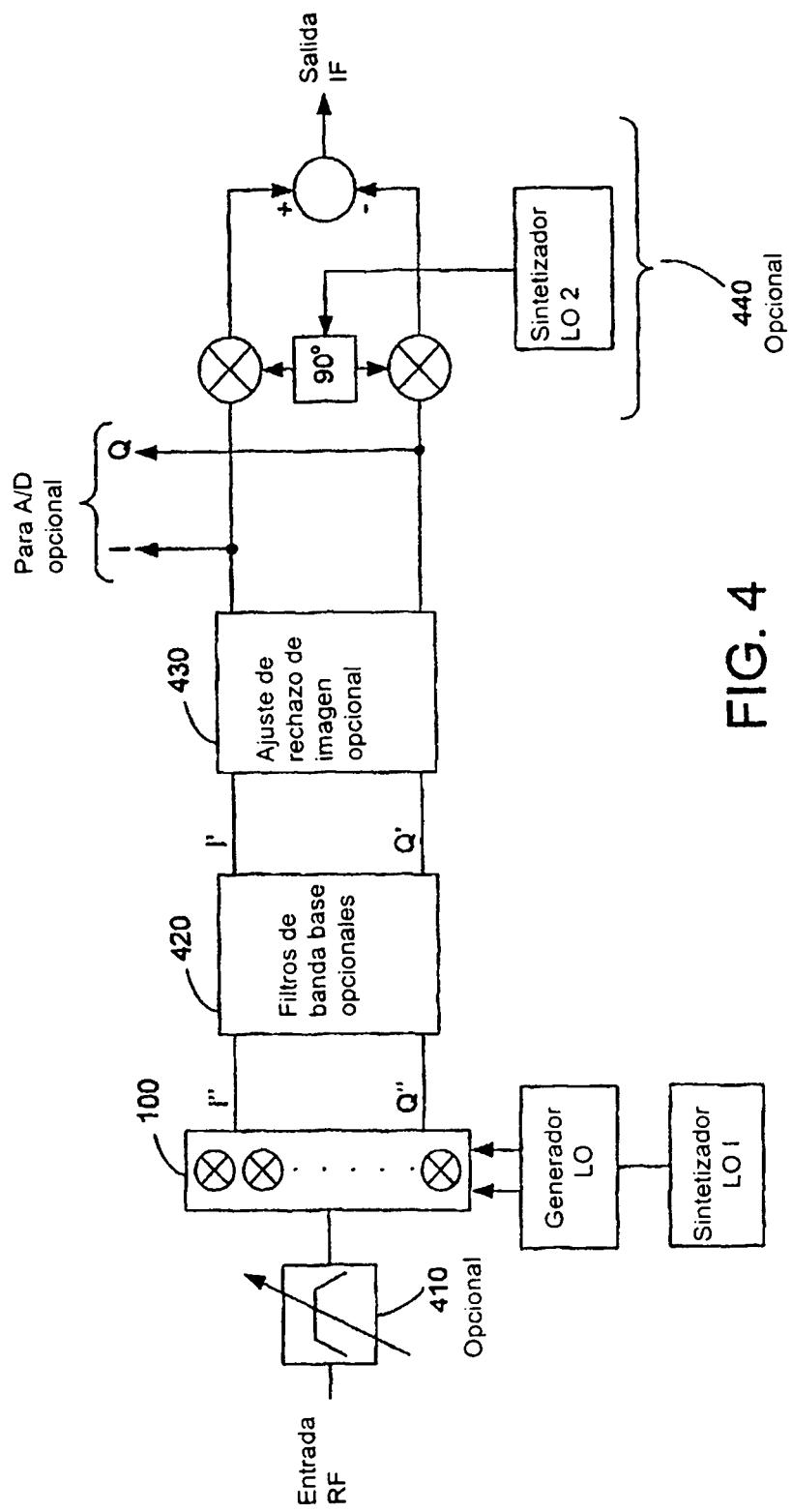

- La figura 4 muestra un sintonizador que emplea el mezclador de supresión armónica.

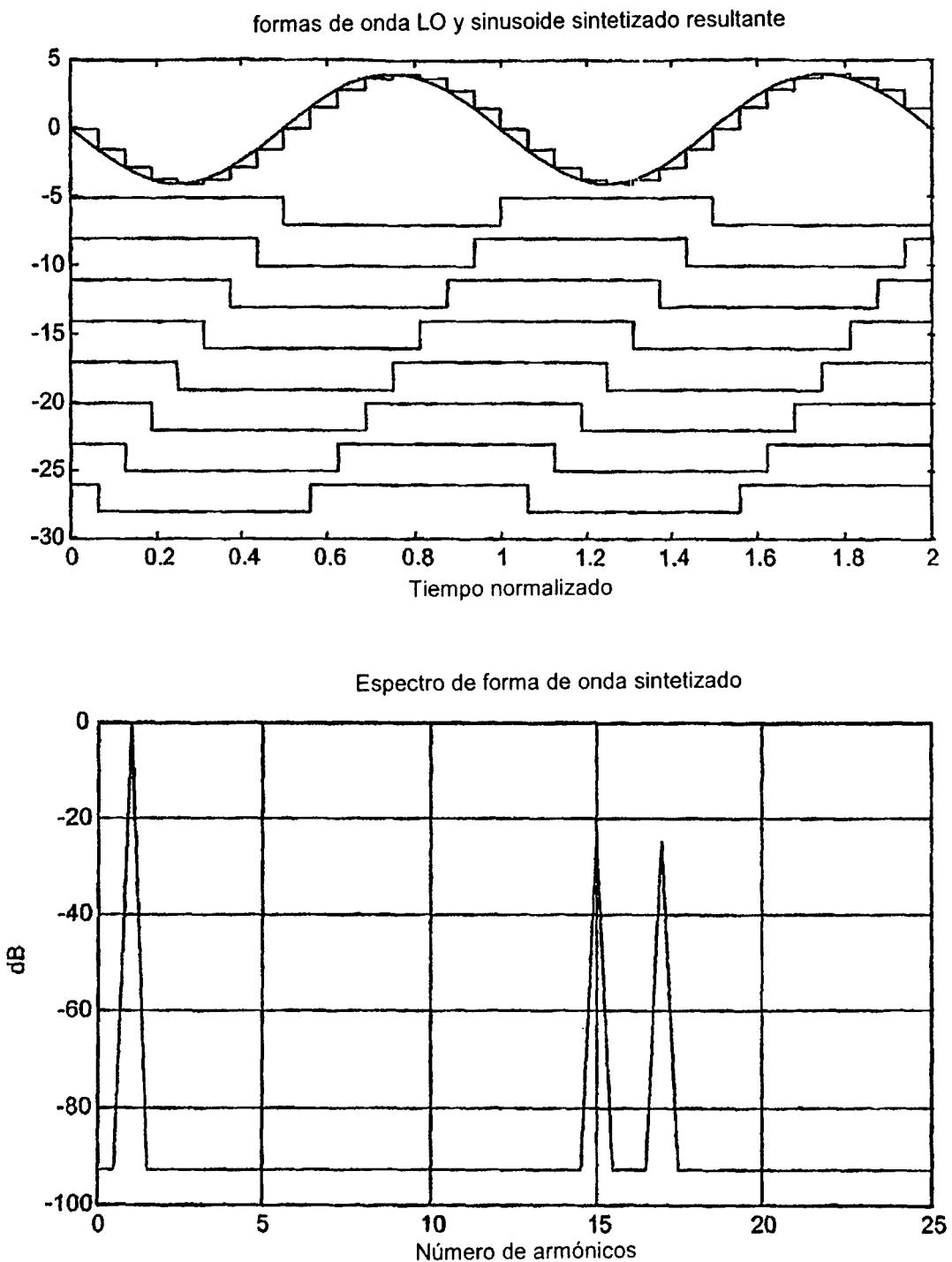

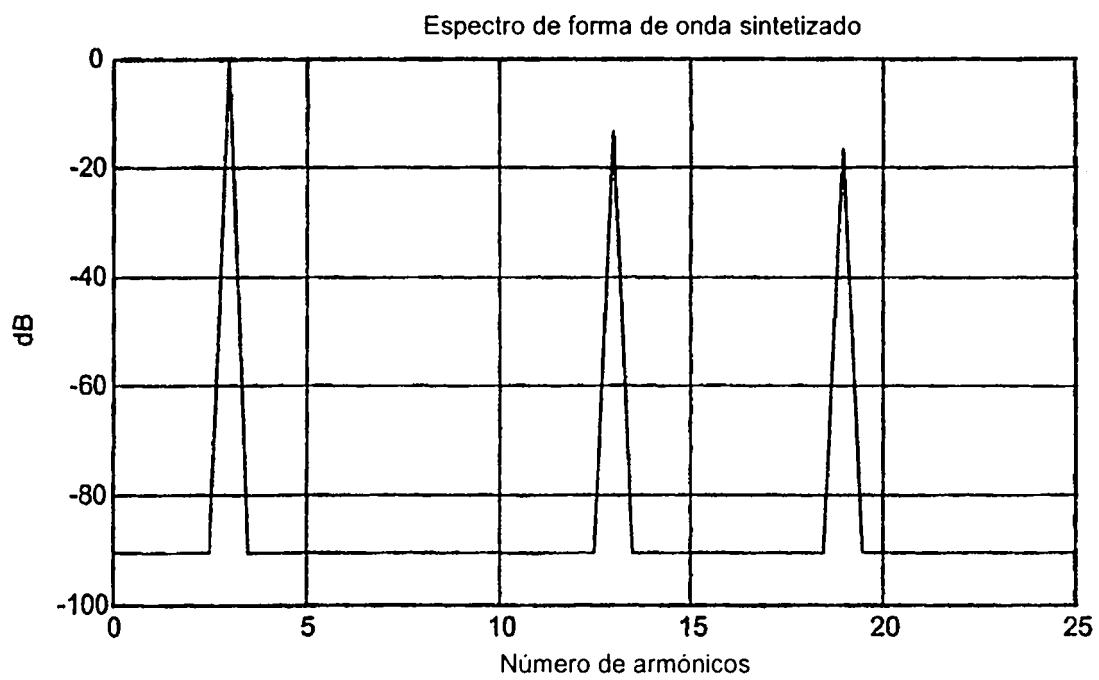

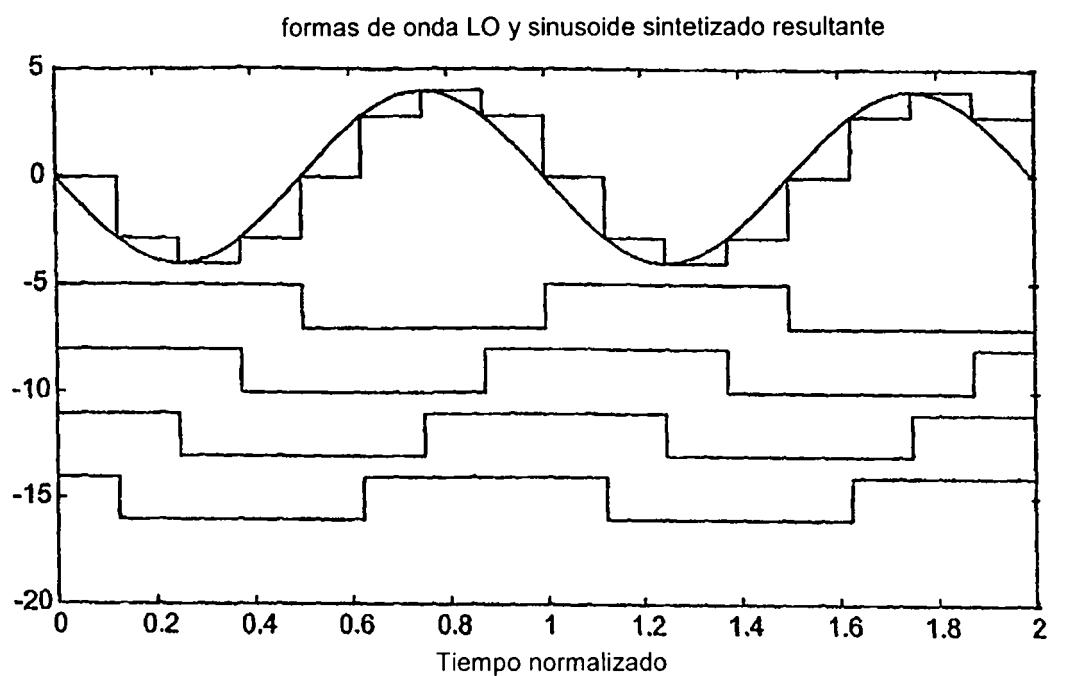

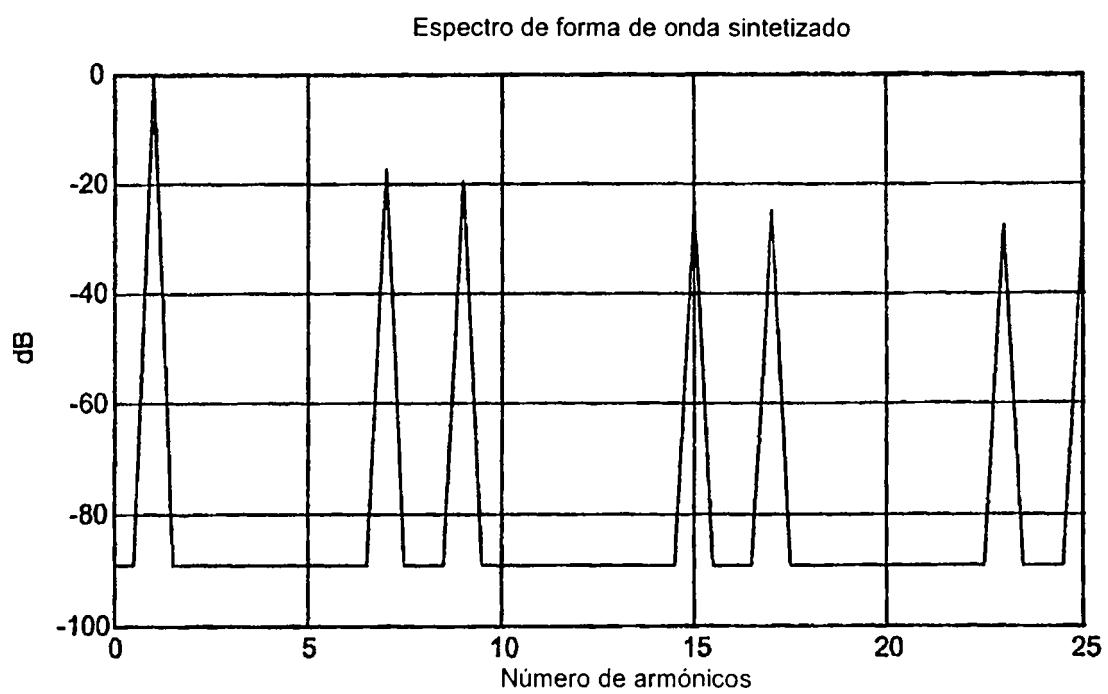

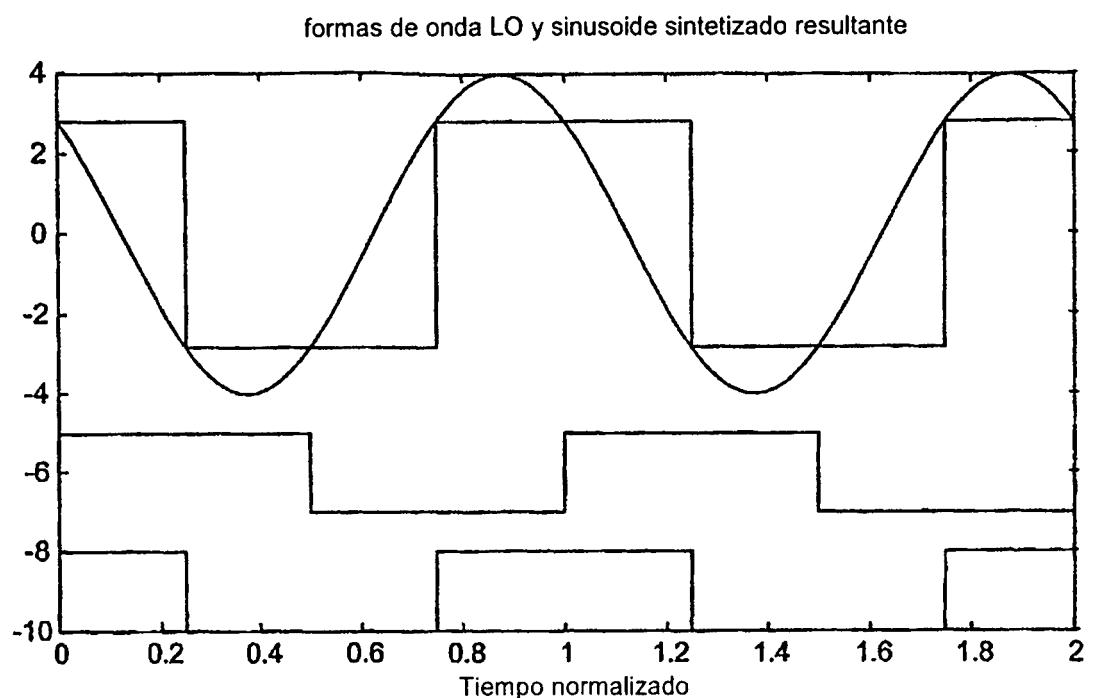

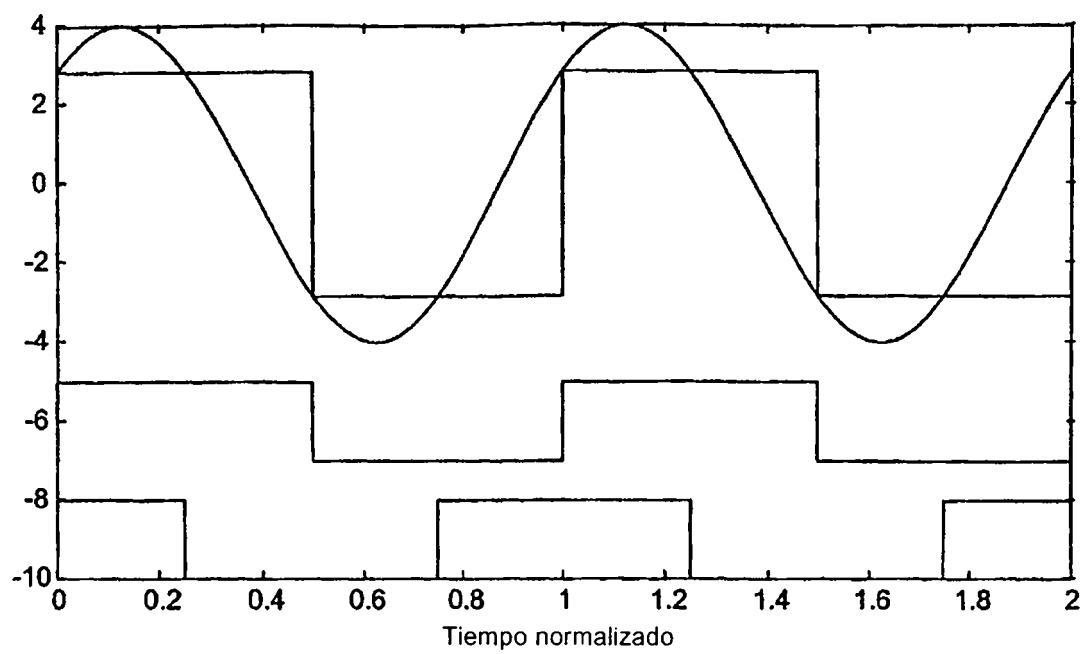

- 40 La figura 5 muestra formas de onda y el espectro resultante para un I LO de fase 8 ciclo 1.

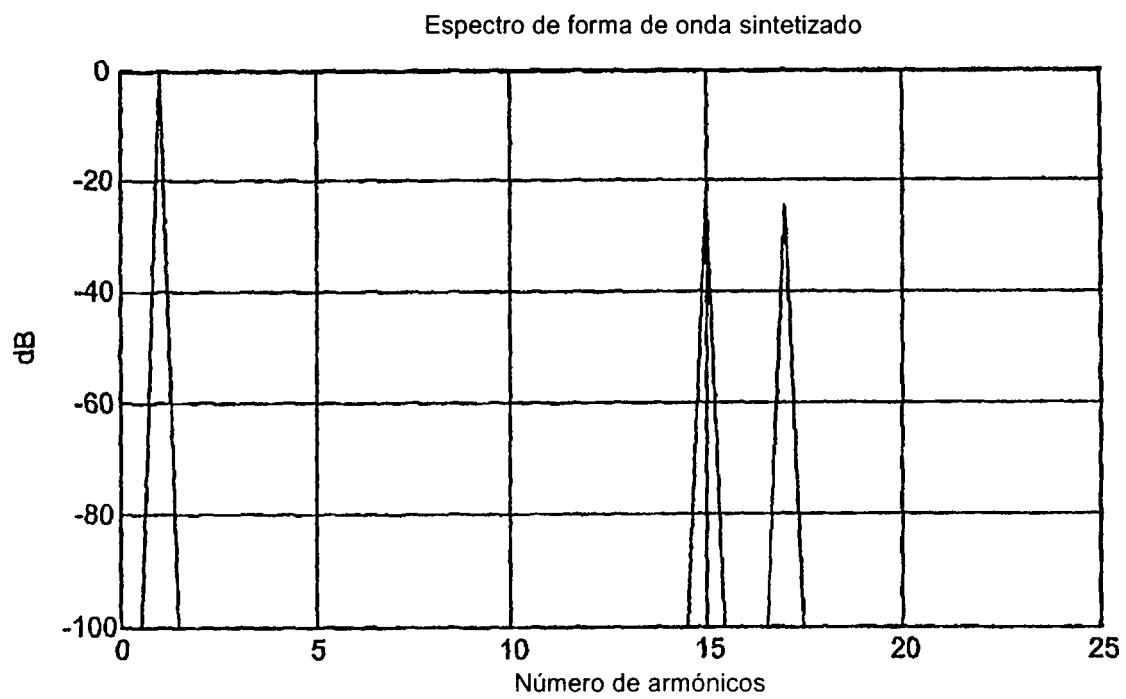

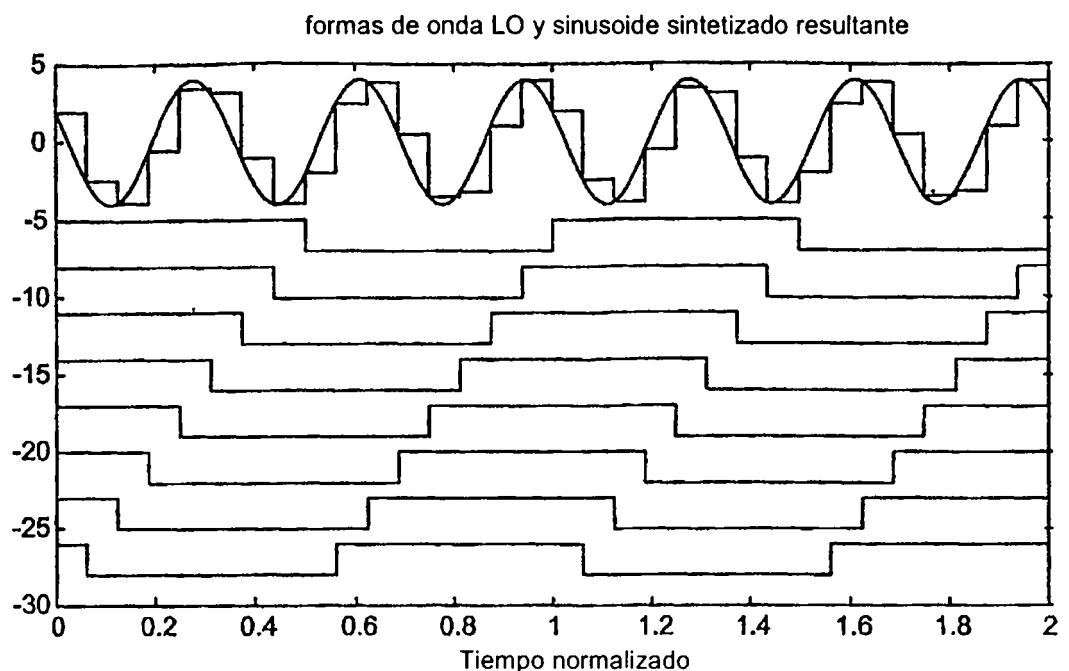

- La figura 6 muestra formas de onda y el espectro resultante para un Q LO de fase 8 ciclo 1.

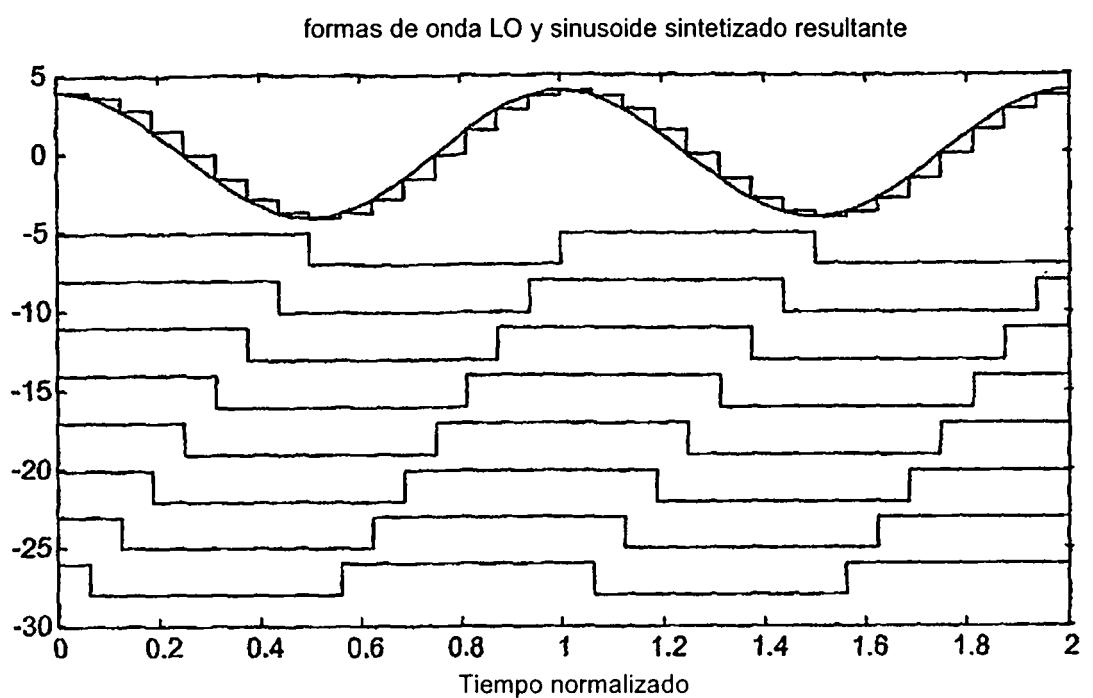

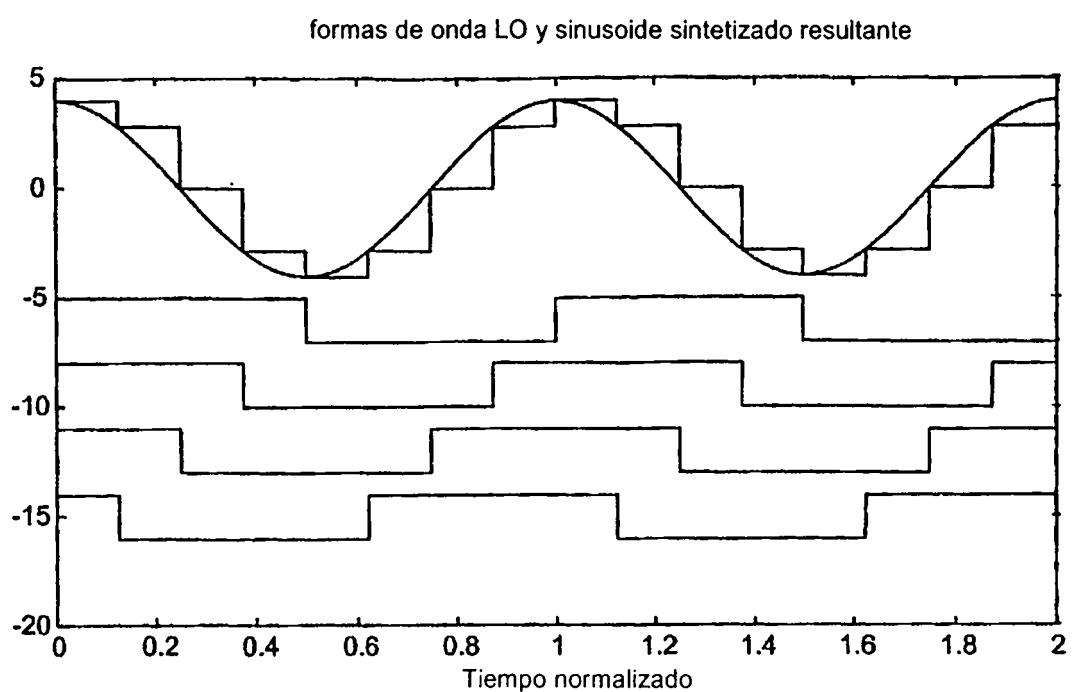

- 45 La figura 7 muestra formas de onda y el espectro resultante para un I LO de fase 8 ciclo 3.

- La figura 8 muestra formas de onda y el espectro resultante para un Q LO fase 8 de 3 ciclos.

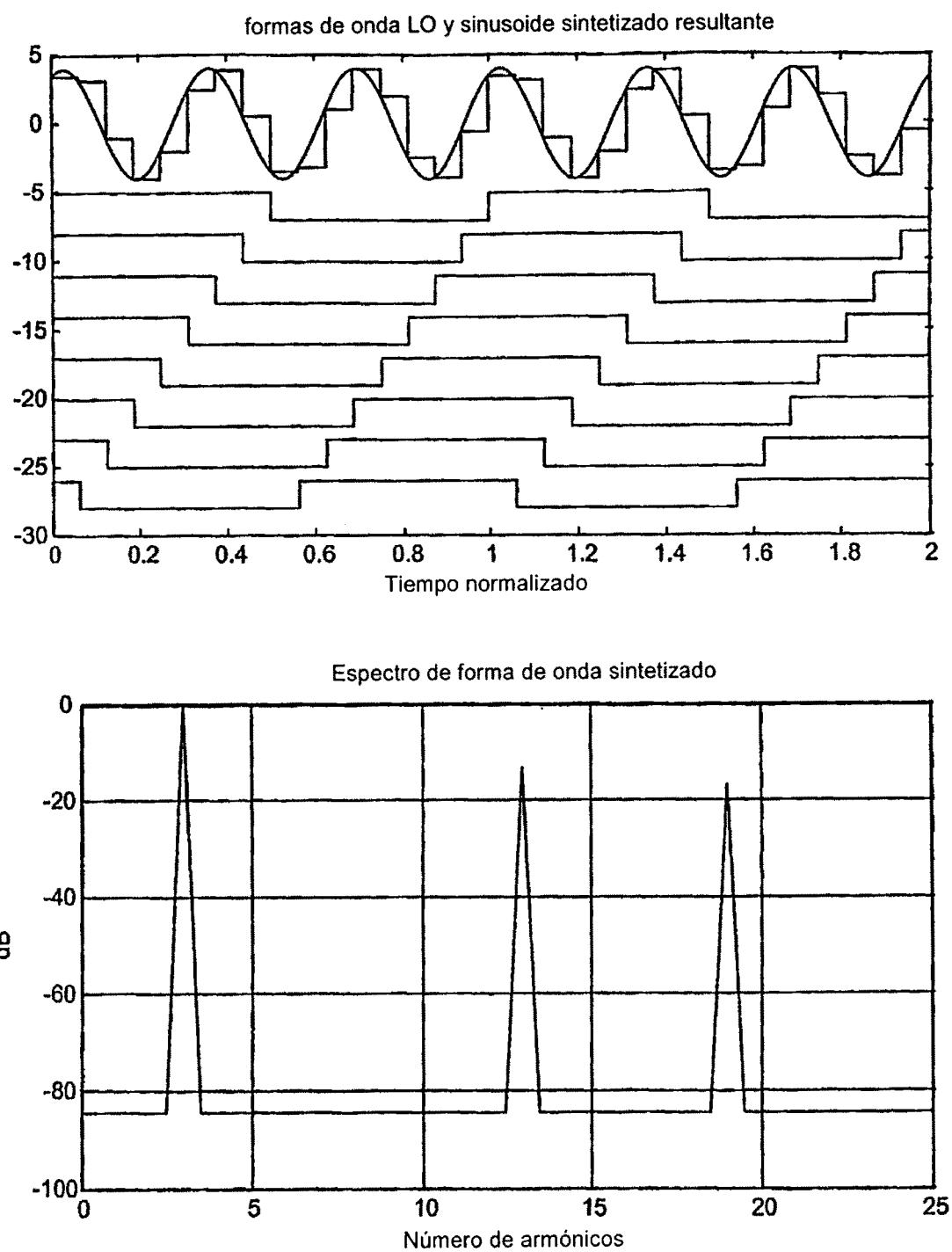

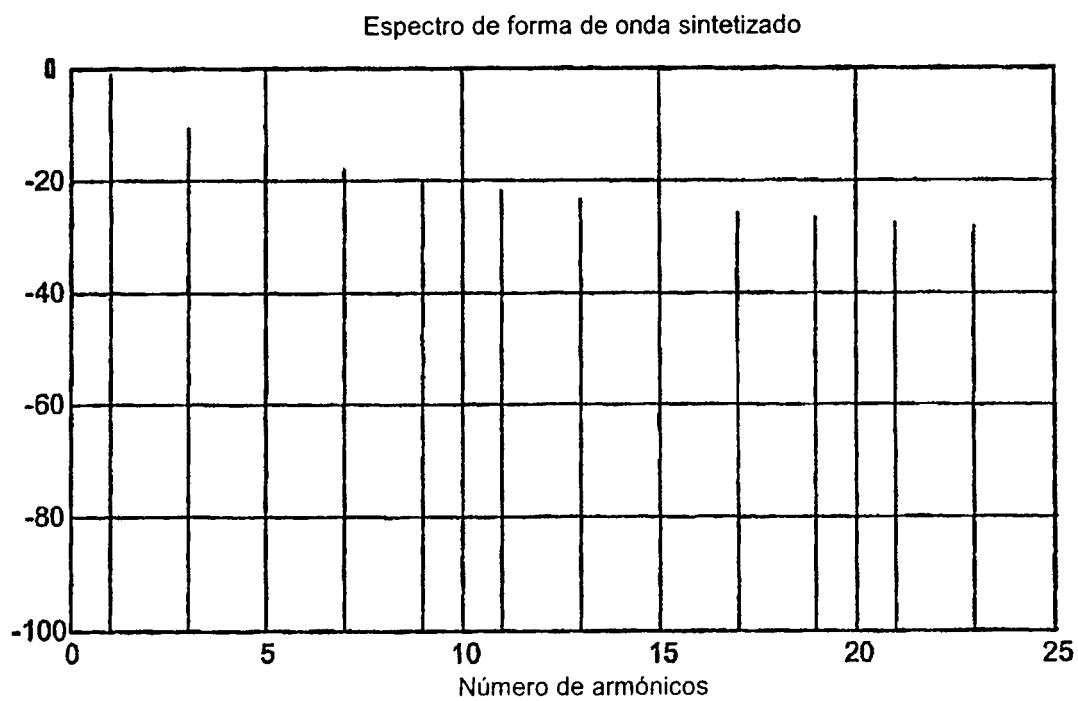

- La figura 9 muestra formas de onda y el espectro resultante para un I LO de fase 4 de un ciclo.

- 50 La figura 10 muestra formas de onda y el espectro resultante para un Q LO de fase 4 de 1 ciclo.

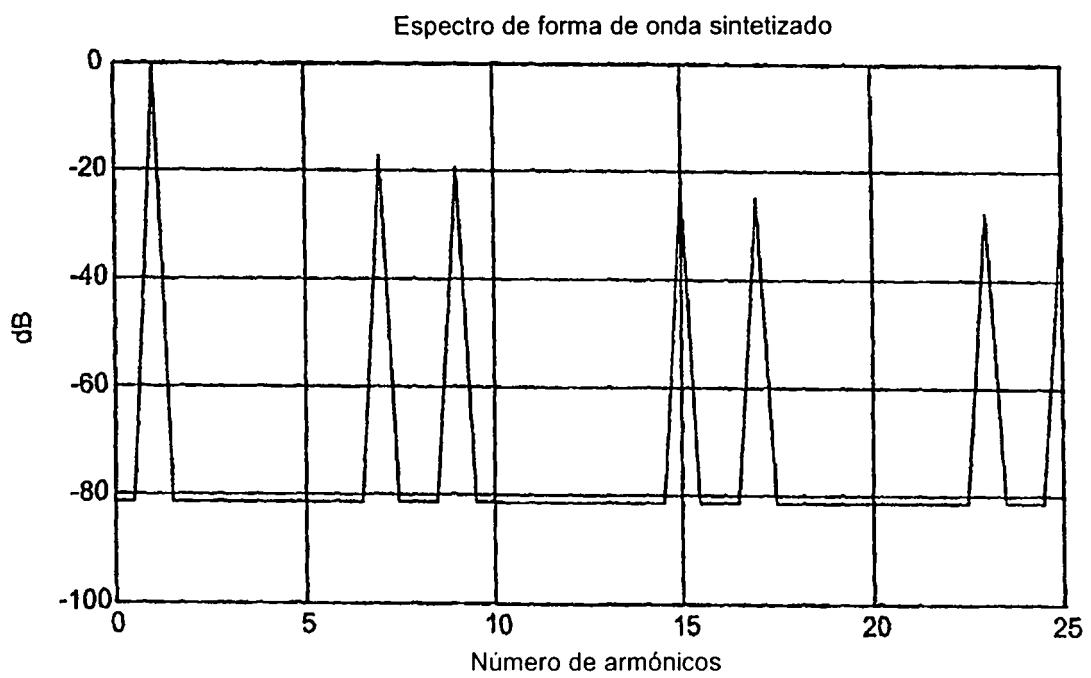

- La figura 11 muestra formas de onda y el espectro resultante para un I LO de fase 2 de 1 ciclo.

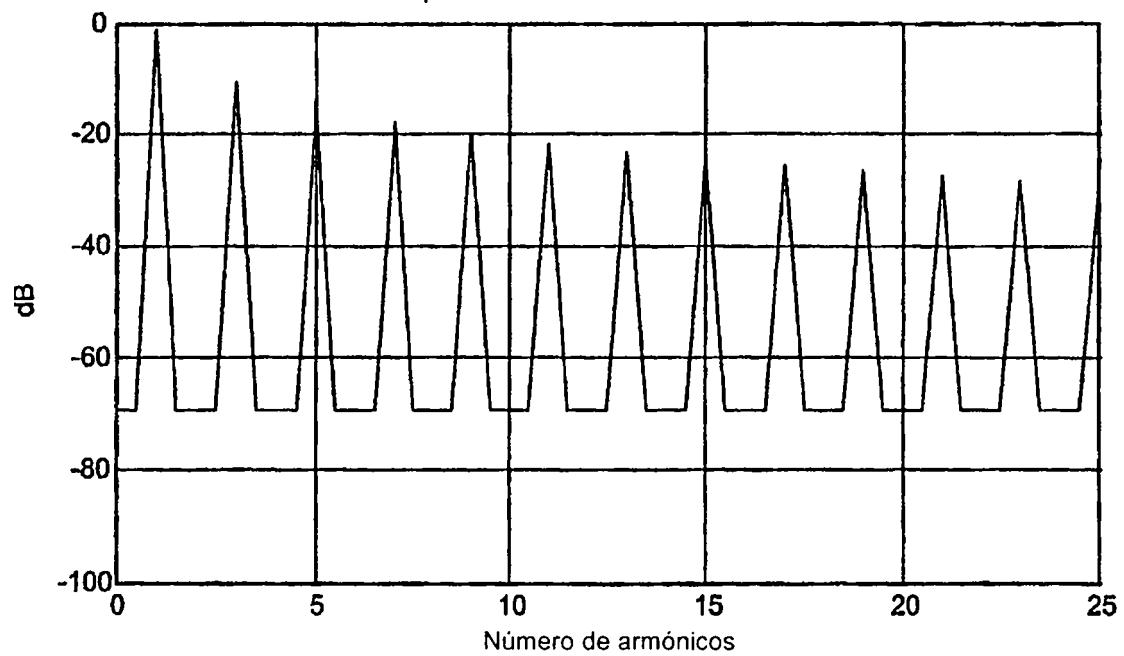

- 55 La figura 12 muestra formas de onda y el espectro resultante para un Q LO de una fase 2 de 1 ciclo.

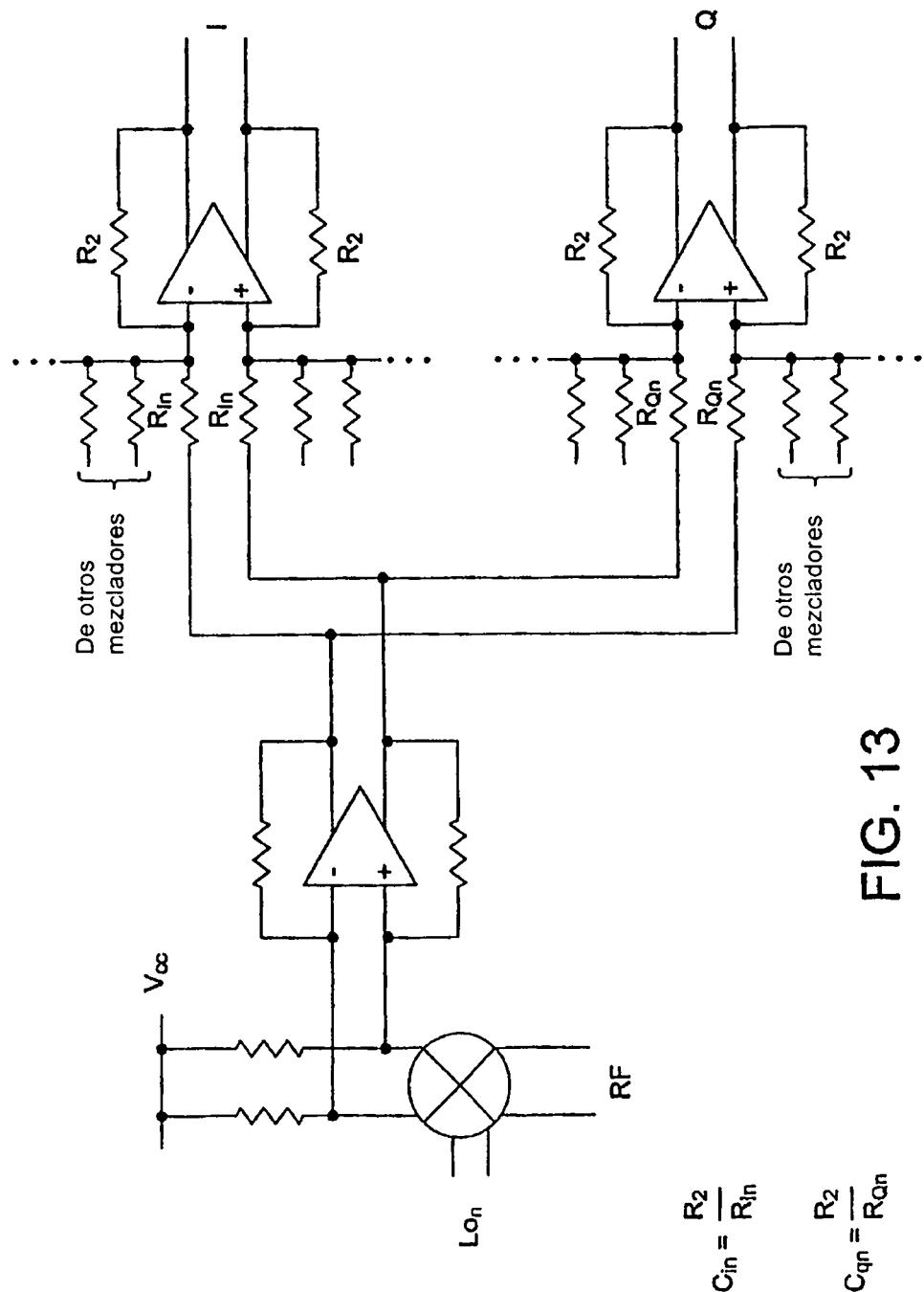

- La figura 13 muestra un diagrama esquemático de una etapa de adición resistiva para el uso con el mezclador de supresión armónica.

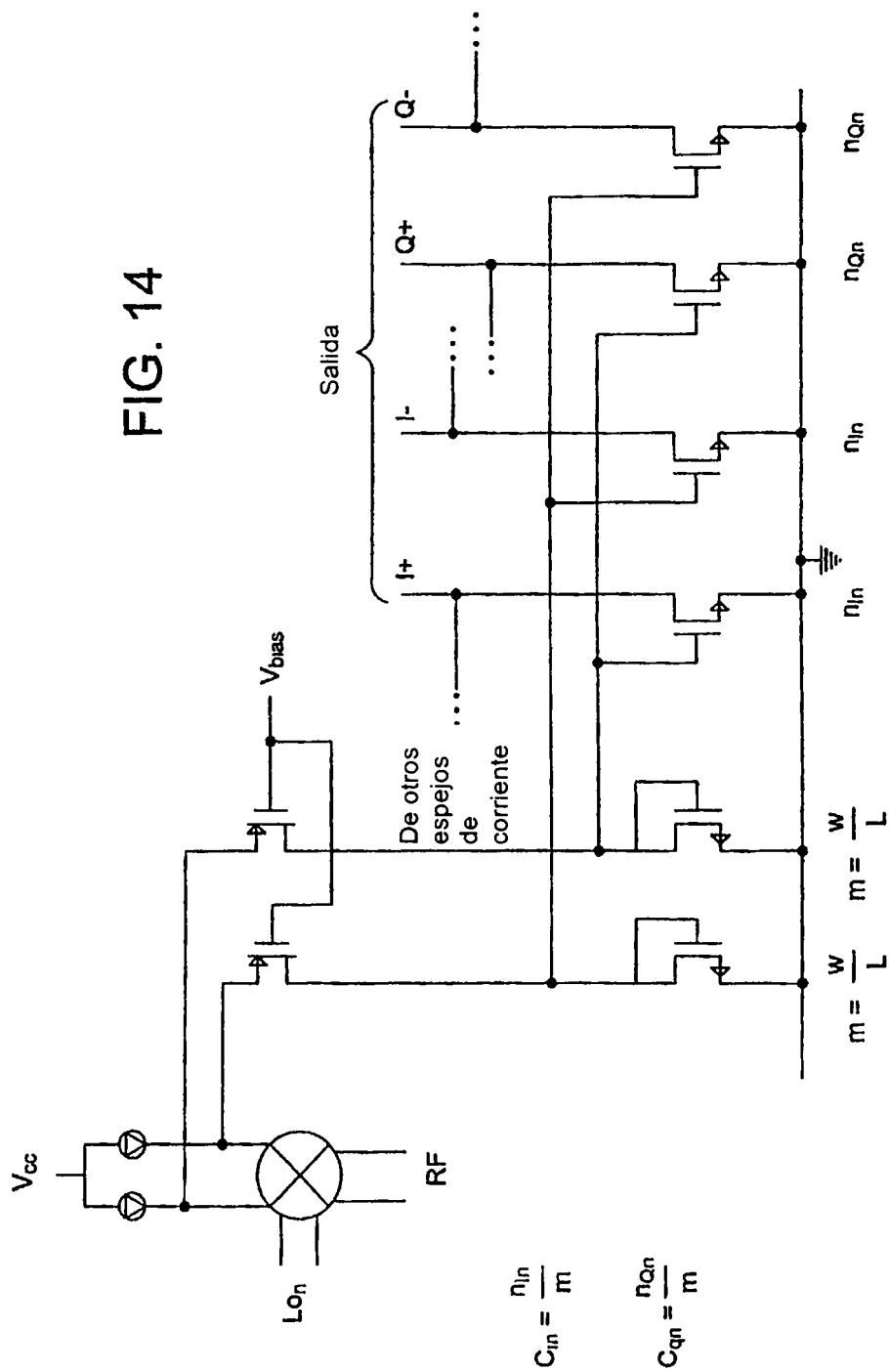

- 60 La figura 14 muestra un diagrama esquemático de una etapa de suma de espejo de corriente para el uso con el mezclador de supresión armónica.

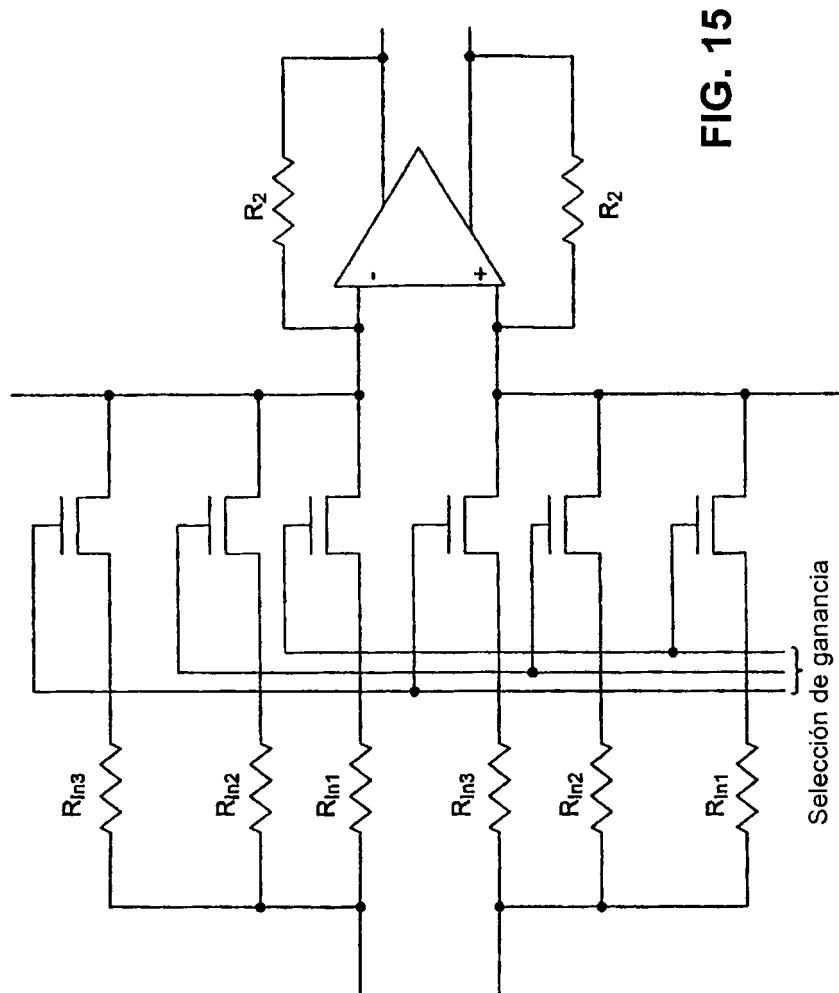

- La figura 15 muestra el detalle de un coeficiente programable para una etapa de suma resistiva.

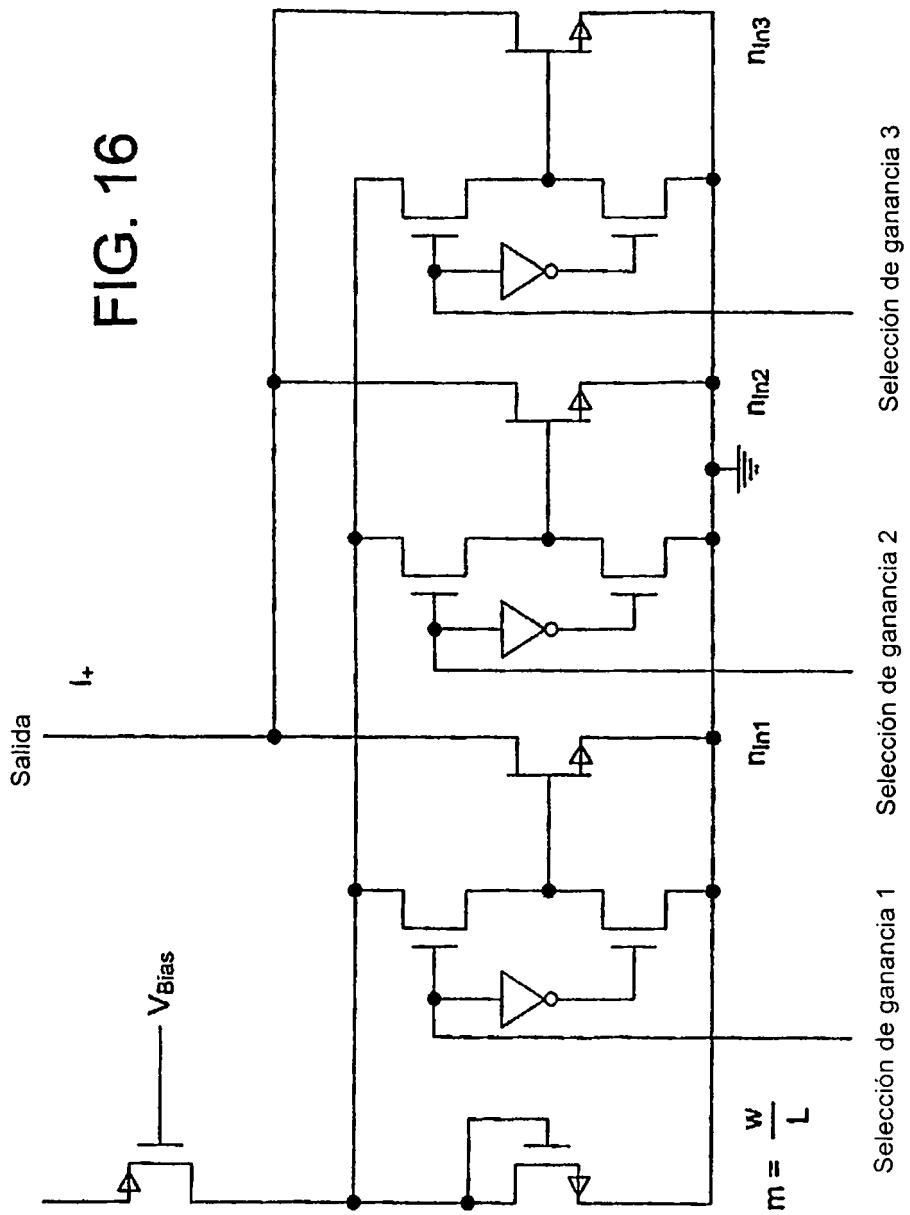

- 65 La figura 16 muestra el detalle de un coeficiente programable para una etapa de suma de espejo de corriente.

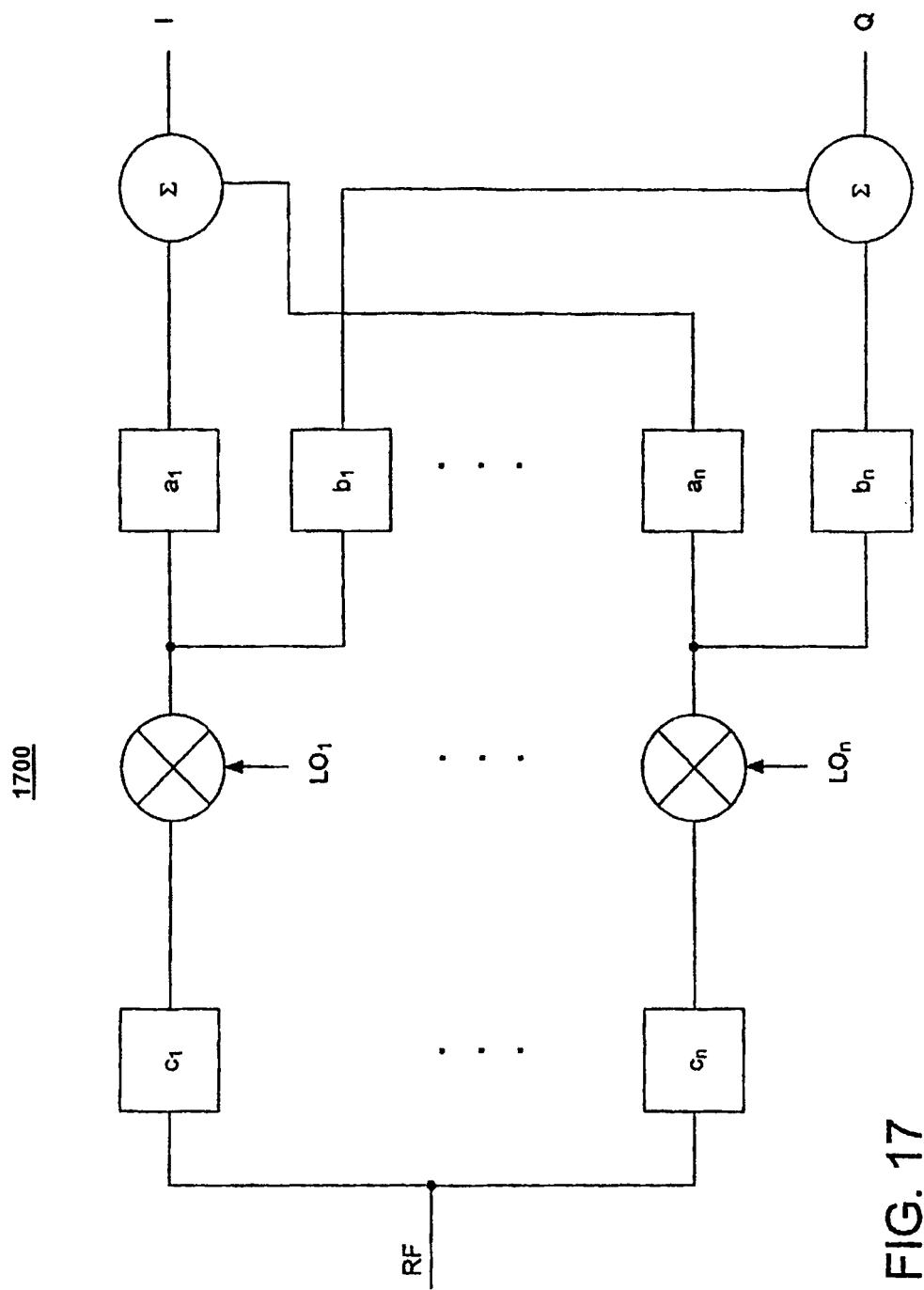

- La figura 17 muestra un diagrama de bloqueo de un mezclador de supresión armónica de acuerdo con la presente invención.

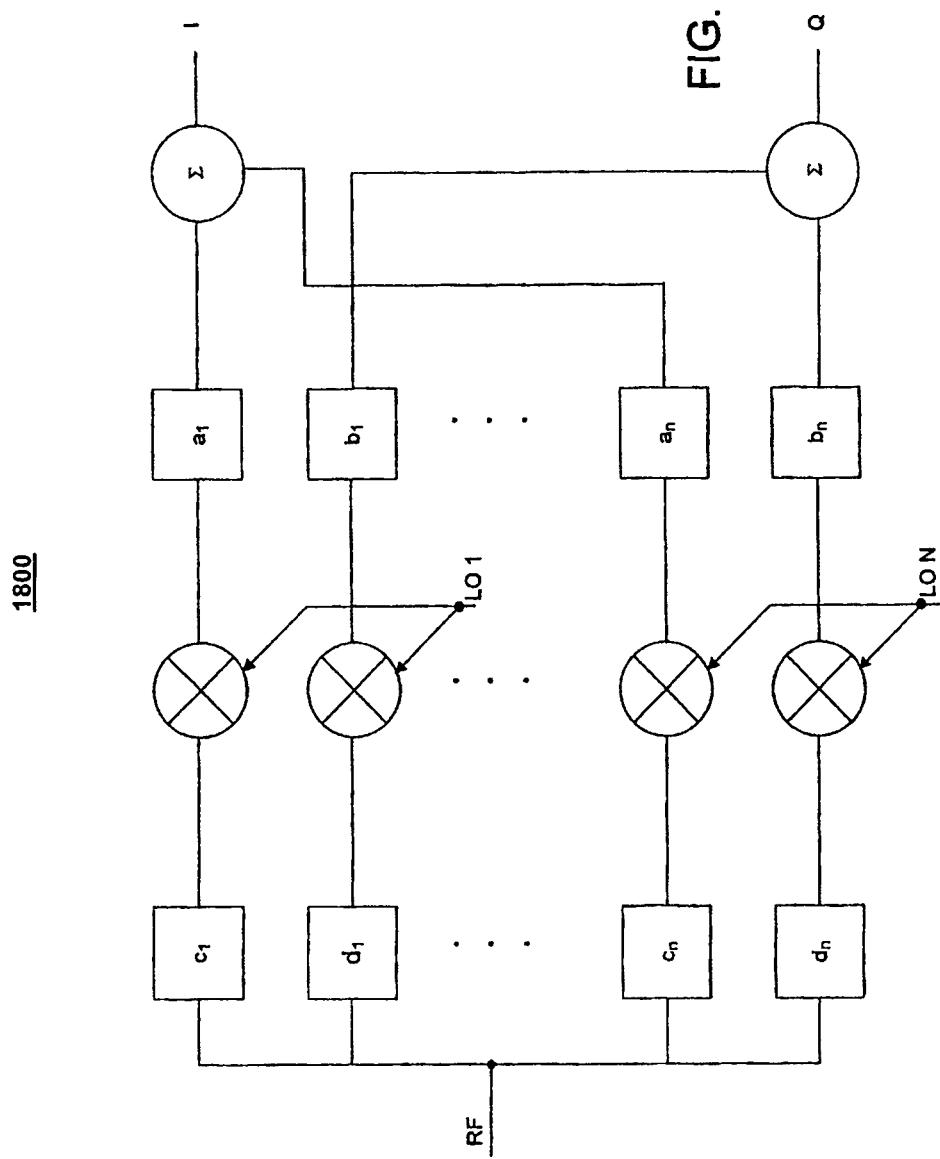

- La figura 18 muestra un diagrama de bloqueo de otra modalidad de un mezclador de supresión armónica de acuerdo con la presente invención.

# ES 2 330 761 T3

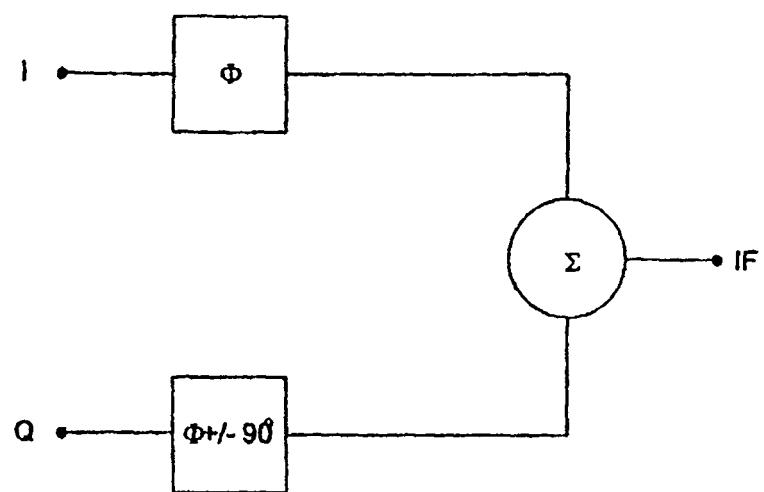

La figura 19 muestra un combinador de cuadratura para uso con el mezclador de supresión armónica.

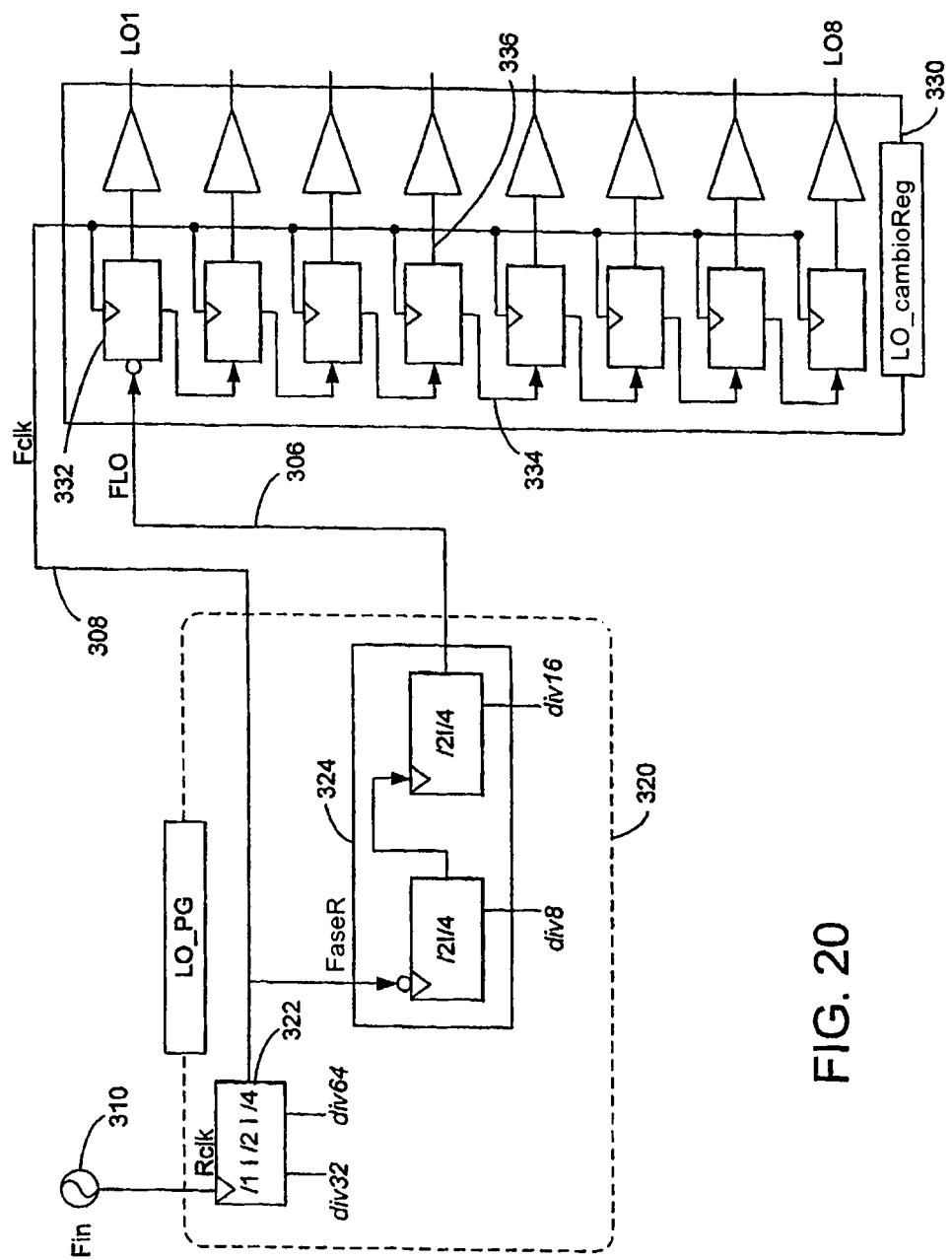

La figura 20 muestra un diagrama de bloqueo de un generador LO para uso con la presente invención.

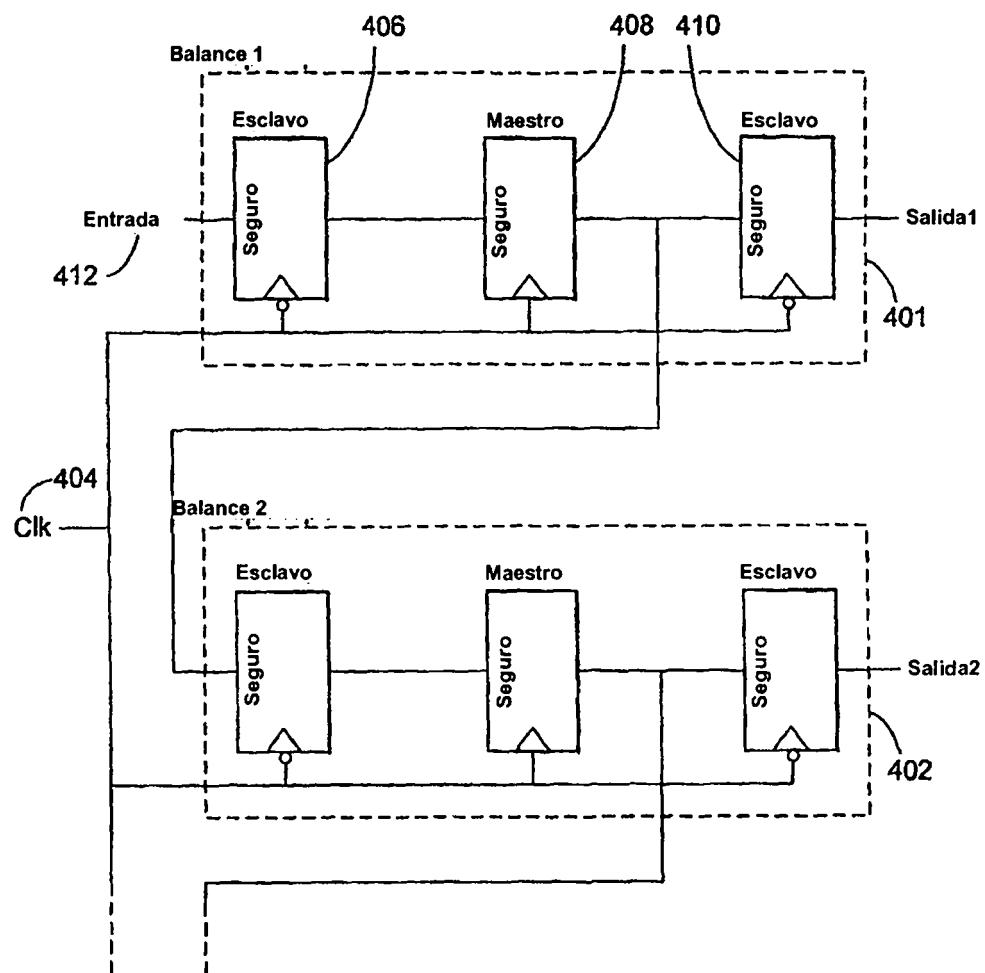

5 La figura 21 muestra un circuito basculante para ser utilizado con el generador LO de la presente invención.

La figura 22 muestra un esquema de circuito basculante de la presente invención.

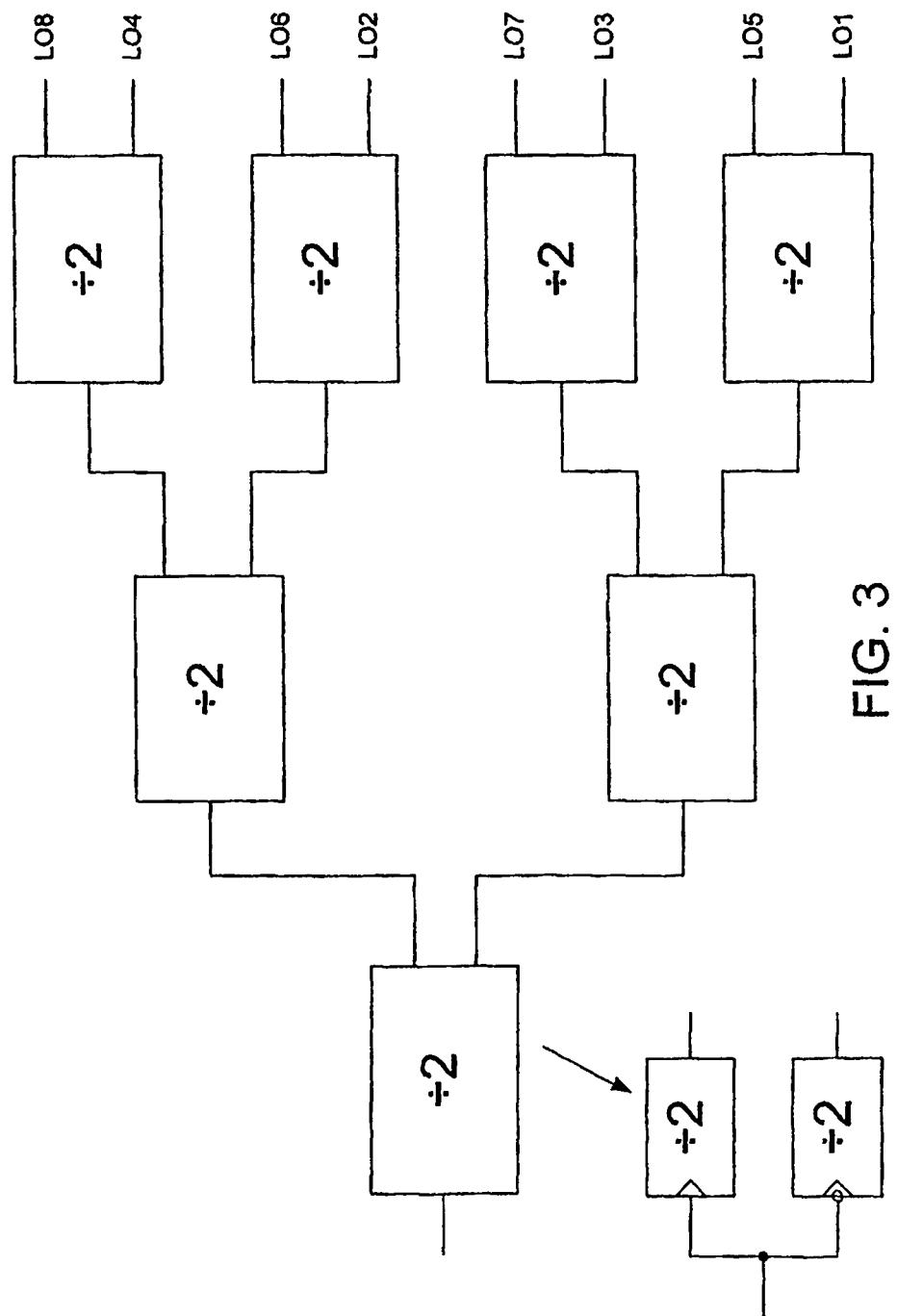

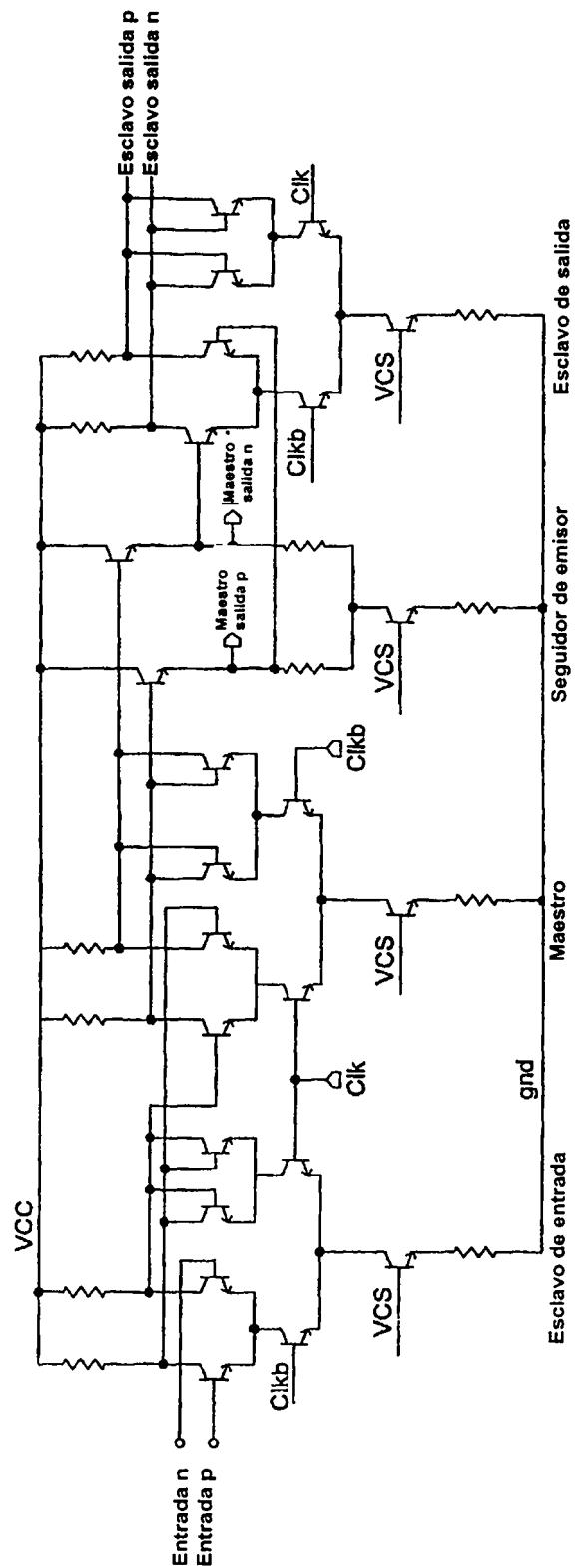

10 La figura 23 muestra una modalidad del mezclador armónico de acuerdo con la presente invención.

## Descripción detallada de la invención

La figura 1 muestra el mezclador 100 de supresión armónica de acuerdo con la presente invención. El mezclador 100 de supresión armónica tiene una señal de entrada 102 que conduce amplificadores de transconductancia 140 para proporcionar el aislamiento de señal entre cada mezclador comutador 110. El amplificador 140 de transconductancia previene la pérdida de señal LO en un mezclador comutador 110 de entrada al acoplarse a otros mezcladores y a una entrada común 102. La pérdida de señal LO anterior a la entrada común tiende a cancelar cada una de las otras, debido a la formación de fases de LO, aunque la amplificación 140 es opcional. El amplificador de transconductancia 140 puede ser cualquier tipo de amplificador dependiendo del tipo señal requerida en la entrada y salida y cada uno puede tener una ganancia diferente. El mezclador armónico 100 comprende mezcladores de conmutación múltiple 110, cada uno con una entrada de señal 112, entrada 114 oscilador local (LO), y la salida de señal 116. Todas las señales son conductores diferenciales y pueden ser de celda Gilbert o de otras topologías de mezcladores que se conocen. Se muestra un banco de mezcladores, que comprende por ejemplo 8 mezcladores. La señal LO 114 es conducida por un generador LO, descrito abajo. La frecuencia de LO1 a través de LO4 es idéntica y la fase es escalonada por  $1/(2^N)$  del período de LO, donde N es el número del mezcladores de conmutación 110 usados.

El amplificador 118 opcional puede ser un amplificador de corriente, de voltaje, transimpedancia o de transconductancia, dependiendo del tipo de salida de los mezcladores y del tipo de entrada de las etapas del coeficiente.

30 Las etapas del coeficiente 120 y 130 proporcionan una ganancia de varias magnitudes en cada salida del mezclador 110 de conmutación. Las etapas del coeficiente 120 y 130 son bien conocidas y pueden configurarse, por ejemplo, como espejos de corriente con ganancia y o como redes adicionales resistivas, posiblemente utilizando amplificadores operacionales. Al usar espejos de corriente, la salida de corriente de mezcladores comutadores 110 se refleja como 35 una nueva corriente con ganancia equivalente al valor del coeficiente deseado para la etapa. Los valores obtenidos pueden ir desde menos de uno a más de uno. La corriente de todas las etapas del coeficiente 120 se combina en un nodo suma de corriente para formar una señal de salida 104 en fase (I). La corriente de todas las etapas del coeficiente 130 se combina en un nodo sumador total de corriente de una fase de cuadratura (Q) de señal de salida 106.

40 Las etapas del coeficiente 120 y 130 tienen valores obtenidos que corresponden a una aproximación de ejemplo de tiempo equidistante de la mitad del período de una onda de seno. Más específicamente, los coeficientes se encuentran mediante la solución de la siguiente ecuación de matriz (mostrada aquí para las 4 fases LO):

$$\begin{array}{c} 45 \quad | s1 | \quad | 1 \quad 1 \quad 1 \quad 1 | \quad | w1 | \\ | s2 | \quad | -1 \quad 1 \quad 1 \quad 1 | \quad | w2 | \\ 50 \quad | s3 | = | -1 \quad -1 \quad 1 \quad 1 | \quad | w3 | \\ | s4 | \quad | -1 \quad -1 \quad 1 \quad 1 | \quad | w4 | \end{array}$$

55 donde s1... s4 son puntos de muestra equi-distantes de una mitad de onda de la forma de onda total deseada, preferentemente, una media onda de una onda de seno.

Cuando se suman, las salidas producen el equivalente de una señal sinusoidal LO. Una relación de fase de cuadratura se crea en los valores del coeficiente en las etapas 120 del coeficiente y las etapas 130 del coeficiente para producir una relación de la cuadratura en las salidas I y Q. Por ejemplo,  $c(i)(n)$  tiene un valor de  $\cos(\text{ángulo})$  y  $c(q)(n)$  tiene un valor  $\text{seno}(\text{ángulo})$ , donde n es el número de etapa y el ángulo es  $\pi^*n^*(I/N) + \text{desplazamiento}$ , donde N es el número total de etapas. El ángulo puede ser desplazado para evitar o lograr valores cero de coeficiente. Los coeficientes de valor cero no tienen ninguna contribución a la señal de salida como resultado, por lo tanto es posible eliminar los circuitos correspondientes, lo que es deseable en algunas aplicaciones para ahorrar en costos. Alternativamente, se puede introducir un ángulo de desplazamiento para lograr un valor mínimo de coeficiente de propagación, lo que ofrece una mejor adaptación del componente y por ello, una mejor supresión de la mezcla de armónicas y un área de silicio reducida.

# ES 2 330 761 T3

Las tablas 1 a 4 muestran conjuntos del ejemplo de coeficientes que generan formas de onda LO de fase 8, 4 y 2.

5 Tabla 1: LO de 8 fases y 1 ciclo, I (0 grados) y Q (90 grados)

I: -0.191342 -0.162212 -0.108386 -0.0380602 0.0380602 0.108386 0.162212 0.191342

Q: 0.0380602 0.108386 0.162212 0.191342 0.191342 0.162212 0.108386 0.0380602

10 Tabla 2: LO de 8 fases y 3 ciclos, I (30 grados) y Q (120 grados)

I: -0.245722 0.366313 0.526086 0.036336 -0.498276 -0.4177 0.178582 0.554381

15 Q: 0.498276 0.4177 -0.178582 -0.554381 -0.245722 0.366313 0.526086 0.036336

20 Tabla 3: 4 fases 1 ciclo, I (0 deg.) y Q (90 deg.)

I: -0.353553 -0.146447 0.146447 0.353553

Q: 0.146447 0.353553 0.353553 0.146447

25 Tabla 4: LO de 2 fases, 1 ciclo, I (45 deg.) y Q (135 deg.)

I: 0 1

Q: 1 0

30 Mientras este ejemplo ha sido descrito usando mezcladores de conmutación de corriente y de etapas de ganancia de corriente, el diseño puede ser implementado alternativamente con dispositivos de conducción de voltaje, tal como circuitos sumadores basados en un amplificador operacional. En una modalidad, los mezcladores conmutadores de corriente se usan con circuitos sumadores de modo de voltaje (basados en amplificadores operacionales).

35 Los coeficientes pueden ser seleccionados usando técnicas de circuitos programables. Una etapa de espejo de corriente programable utiliza interruptores para conectar derivaciones de salida MOSFET paralelas. Una etapa de amplificador operacional programable utiliza interruptores para conectarse en diferentes resistencias de ajuste de ganancia.

40 El mezclador de supresión armónica se configura para una operación de 8, 4, o 2 mezcladores mediante el cambio de valores del coeficiente. En las configuraciones 4 y 2 del mezclador, los mezcladores se programan con los valores del coeficiente duplicados para reducir el número de mezcladores únicos eficaces. La configuración de señales LO que conducen los mezcladores también puede cambiar, incluyendo las señales LO idénticas unas con otras, resultando en fases únicas 4 o 2. Aunque se muestran 8 mezcladores y señales LO, cualquier número de mezcladores y fases LO puede ser utilizado como se requiera para una aplicación, incluyendo los números impares.

45 Otras modalidades incluyen una configuración de entrada en la que la corriente de entrada para el mezclador central se obtiene conectando las resistencias de un voltaje de entrada común RF dentro de cada uno de los centros mezcladores; esto también logra la transformación deseada de voltaje a corriente. En otra modalidad, todas las entradas del mezclador central se conectan juntas y la corriente de entrada RF se fracciona de forma homogénea entre cada mezclador.

50 La figura 2 muestra un ejemplo del generador LO 200 para el uso con el mezclador de supresión armónica. La relativa precisión de la fase y baja fluctuación de cada LO es importante para lograr una ganancia de baja conversión de interferencia RF que se produce en las armónicas de LO y buen desempeño de mezclado recíproco del mezclador de supresión armónica. La máquina de estado 210 produce una serie de señales digitales de ondas cuadráticas cambiadas por una fracción  $1/(2^*N)$  del período LO, donde N es el número de señales LO generadas. Los registros 220 temporizan 55 nuevamente la salida de la máquina de estado 210 para asegurar que la transición de cada onda cuadrática se produzca en un momento relativo preciso. Los registros 220 y la máquina de estado 210 son conducidos por una temporización de alta frecuencia que es, por ejemplo, 4 veces la frecuencia de LO y puede alcanzar un rango desde 1 a 8 veces la frecuencia de LO. Reprogramar la temporización de salida de la máquina de estado es optativo.

55 La máquina de estado es reconfigurable para ofrecer fases LO que son escalonadas en  $1/(2^*8)$ ,  $1/(2^*4)$ , o  $1/(2^*2)$  de un período que depende de la frecuencia del canal deseado. En cada configuración, se utilizan 8 mezcladores, pero en los modos  $1/(2^*4)$  y  $1/(2^*2)$  los coeficientes de salida del mezclador se cambian de manera a que correspondan a una onda completa de muestra de onda seno en el caso  $1/(2^*4)$  o para mostrar dos ciclos de onda de seno en el caso

1/(2\*2). En esta forma de acción paralela, los 8 mezcladores colapsan eficazmente en cuatro únicos mezcladores, en el caso 1/(2\*4) o en dos únicos mezcladores en el caso 1/(2\*2). La frecuencia de la temporización múltiple relativa a la frecuencia LO es necesaria para que el generador LO se reduzca en las configuraciones de cuatro mezcladores y de dos mezcladores. En las frecuencias de más alta sintonía donde se usan las configuraciones de cuatro y dos mezcladores, las señales armónicas están fuera de la banda o son removidas por operaciones de filtrado en los circuitos de procesamiento de señal de sintonía que alimentan al mezclador.

La figura 3 muestra detalles de un ejemplo de máquina de estado 210. Los divisores de ondulación operan en fases alternadas de la entrada de la temporización para dividir la temporización de entrada en dos y producir salidas de fase de cuadratura para conducir una etapa sucesiva. Algunas variaciones aleatorias y sesgadas en el tiempo de 10 conmutación se introducen para cada etapa. Es posible utilizar registros 220 para volver a temporizar la salida de la máquina de estado, con el fin de alinear los extremos de la señal LO.

Otra modalidad del generador LO genera señales digitales rectangulares que varían en ancho de pulso o ciclo 15 de trabajo para producir señales con extremos alternados, para conducir los mezcladores. Por ejemplo, las señales digitales pueden tener un ancho de pulso periódico que varía de un octavo de período a siete octavos de período en incrementos de un octavo de período. Los centros de cada pulso pueden ser alineados.

Otras metodologías para implementar la máquina de estado 210 incluyen arquitectura de máquina Moore, arquitectura 20 de máquina Mealy, que codifica en caliente, y otras arquitecturas de máquinas de estado bien conocidas. En cada caso, es posible utilizar un segundo nivel de registros para de-sesgar las salidas de la máquina de estado.

La figura 4 muestra un ejemplo de diagrama de bloques de un sintonizador de subconversión directa que utiliza el 25 mezclador de supresión armónica. Un paso de la banda variable opcional o un filtro de paso bajo 410, preselecciona el canal de sintonía. El mezclador de supresión armónica 100 extrae una señal I y Q en filtros de paso de banda 420. Una etapa 430 de ajuste de rechazo de imagen opcional equilibra las señales I y Q para completar el rechazo de la imagen. Se puede elegir la salida del sintonizador analógica I/Q, digitalizada por convertidores A/D, o mezclada y combinada 30 por un modulador de cuadratura 440 para producir una señal de salida IF. En lugar de un modulador de cuadratura se puede utilizar un combinador de cuadratura. Alternativamente, cada mezclador de salida puede ser digitalizado y la combinación realizada en el dominio digital.

Los filtros de señal de banda limitada I y Q pueden ser implementados con dos valores reales separados filtrados o como un filtro complejo que opera en las señales I y Q conjuntamente, incluyendo los filtros de carril cruzados. El límite de banda I y Q puede ejecutarse en las señales IF o banda base.

En una arquitectura de sintonizador alterno, no mostrada, el nivel de la señal de entrada RF se reduce por un 35 atenuador opcional cuando se usa en aplicaciones inalámbricas (OTA). Un diplexor opcional divide la banda de frecuencia recibida en subbandas para filtrar mediante filtros de sintonía de preselección opcionales, típicamente cada uno para VHF baja, VHF alta, y UHF. Los filtros de preselección de sintonía proporcionan supresión armónica adicional además de la supresión proporcionada por el mezclador. Los filtros de preselección de sintonía también mejoran en gran medida la ejecución de distorsión debido a que las interferencias de afuera de la banda son atenuadas. Si la distorsión es menos crítica, es posible utilizar filtros mezclados. Para aplicaciones menos exigentes, se puede utilizar un amplificador de banda ancha sin filtros. La supresión armónica es proporcionada principalmente por el mezclador. Alternativamente, el amplificador puede ser eliminado y la señal conducida directamente dentro del mezclador. Una 40 terminación simple opcional para la conversión diferencial se usa para conducir el mezclador de supresión armónica diferencial. Alternativamente, una trayectoria de señal de extremo simple puede conducir un mezclador de terminación simple. La presente invención del mezclador puede ser implementada con extremos simples o circuitos diferenciales, o una combinación de circuitos diferenciales y de extremos simples.

Las salidas I y Q del mezclador de supresión armónica conducen filtros de banda base que rechazan las interferencias 50 subconvertidas así como las condiciones de producto del mezclador y la señal LO. Una etapa de ajuste de rechazo de la imagen equilibra los niveles de la señal I y Q y la fase para un completo rechazo de la imagen. Una técnica para calibrar el balance I y Q se describe en Der, L., Razavi, B., "A 2-GHz CMOS image-reject receiver with LMS calibration", IEEE Journal of Solid-State Circuits, Volume 38, Issue2, Feb. 2003, páginas 167-175. En general, los circuitos de 55 rechazo de imagen pueden realizar una corrección de amplitud, corrección de la fase, o ambos. Los circuitos de rechazo de imagen pueden operar tanto en la banda base como en IF.

Un circuito de rechazo de imagen está descrito en la solicitud provisional co-pendiente de la patente E.U.A. titulada "Amplitud de señal en fase de cuadratura y en fase y calibración de fases", presentada el 12/15/2004, número de serie 60 60/636,383.

Otra técnica que garantiza el alto rechazo de la imagen utiliza un IQ doble de subconversión, pero esta técnica es más compleja, consume más energía, y es más ruidosa; sin embargo no se requiere de una etapa de calibración. Esta técnica está descrita en Crols, J., Steyaert, M.S.J., "A single-chip 900 MHz CMOS receiver front-end with high 65 performance low-IF topology", IEEE Journal of Solid-State Circuits, Volume 30, Issue 12, Dec. 1995, páginas 1483 - 1492.

## ES 2 330 761 T3

Las señales ajustadas I y Q conducen un super-convertisor IF que produce una señal IF de frecuencia adecuada, por ejemplo 5 MHz, 36 MHz, 44 MHz, 57 MHz, o 63 MHz. Adicionalmente, la señal IF puede ser digitalizada. Las salidas de banda base I y Q, pueden ser conducidas externamente, ya sea como señales analógicas o digitales, para sistemas que realizan el procesamiento digital de señales en una señal receptora. Las configuraciones alternativas incluyen: la conversión RF a una señal de frecuencia alta IF usando un mezclador convencional, filtro de canal de paso de banda, y por ende una subconversión a la banda de base, utilizando un mezclador de supresión armónica y después la digitalización y salida; subconversión RF para un IF bajo, por ejemplo 5 MHz, con un mezclador de rechazo armónico seguido por un combinador de cuadratura I y Q y entonces la digitalización y salida.

Un sintetizador de frecuencia de circuito de fase cerrada (PLL) produce una señal para conducir el generador LO. La salida del oscilador controlada por el voltaje (VCO) del circuito PLL opera a un múltiple de la frecuencia del generador LO, por consiguiente, es necesaria una consideración del diseño para reducir la frecuencia máxima de operación del VCO. La tabla 6, debajo, muestra los rangos de frecuencia de operación del sintonizador junto con la configuración del mezclador y las frecuencias VCO requeridas. En la opción 1, el mezclador opera con un solo ciclo LO. El número de fases LO es reducido mientras el LO final aumenta. La opción 2 minimiza el rango de operación del VCO. La opción 3 optimiza el rechazo armónico en cada rango de sintonía. Se selecciona un divisor en la salida VCO para dividir el VCO, para que sea utilizado en la generación de LO para la reducción del rango de variación de operación de VCO.

El mezclador de supresión armónica puede ser utilizado como un mezclador RF IF, en el que se establece la frecuencia LO para producir una frecuencia IF en las salidas I y Q. Un filtro polifásico puede combinar las salidas I y Q y proporciona una sola conversión de RF a IF con o sin el rechazo de la imagen. La señal IF puede ser cualquier frecuencia, por ejemplo 36 MHz, 44 MHz, 57 MHz, 63 MHz o superior. La frecuencia IF puede ser cualquier frecuencia, por ejemplo 4 MHz. Un mezclador de supresión armónica alternativo adicional usa un solo banco del mezclador y una sola salida IF en lugar de salidas I y Q. Las configuraciones del sistema que usan el mezclador de supresión armónica incluyen RF a IF con rechazo de imagen, RF a IF sin rechazo de imagen, y RF para banda de base.

La figura 5 a la 12 muestran la forma de onda y los trazados de espectro para varias configuraciones del mezclador de supresión armónica usando la fase 8, fase 4, y fase 2 LOs. Las figuras muestran la frecuencia relativa de la señal de sintonía y las frecuencias de conversión armónicas más cercanas.

La figura 13 muestra un ejemplo de la etapa de suma de resistencia para combinar las salidas de las etapas del mezclador. El coeficiente de ganancia para cada mezclador se establece mediante las resistencias de entrada que conducen el nodo sumador en la entrada del amplificador operacional. Cada resistencia puede tener un valor fijo o programable. En una modalidad, el amplificador de transimpedancia diferencial puede ser retirado, dejando solo la resistencia para conectar pasivamente la salida del mezclador al sumador. Alternativamente, es posible utilizar las etapas de corriente adicional bien conocidas en lugar de la suma de voltajes.

La figura 14 muestra una etapa de suma del espejo de corriente para combinar la salida de las etapas mezcladas. El coeficiente de ganancia para cada mezclador se establece por las características del MOSFETs en el espejo de corriente. Los transistores de entrada tienen una relación de aspecto  $m=W/L$ ; en el que W es el ancho de canal y L es el largo del canal. Los transistores de salida tienen una relación de aspecto  $n=W/L$  que usan diferente W y L de los transistores de entrada. La proporción  $n/m$  determina la corriente obtenida. Cada relación de corrientes puede ser fija o programada. En una modalidad, se fija el valor de m y el valor de n varía para lograr diferentes coeficientes. Las señales de salida en  $I_{+/-}$  y  $Q_{+/-}$  también son nodos sumadores para las señales de corriente producidos por otros espejos de corriente de la etapa del mezclador.

La figura 15 muestra el detalle de un ejemplo de valores de resistencia programables para una etapa de suma de resistencia. Un transistor de conmutación controlado por una señal de ganancia selecta conecta a uno o más resistencias para el nodo sumador del amplificador operacional. El interruptor se pone al lado del nodo sumador de la resistencia debido a que una tierra virtual existe en este punto y que por consiguiente, el interruptor no experimenta un cambio en el voltaje potencial cuando la señal de entrada varía. Una resistencia puede ser conectada directamente al nodo adicional sin un interruptor para una ganancia mínima fija. La ganancia programable puede llevarse a cabo alternativamente usando un transistor de efecto de campo (FET) con un voltaje de puerta aplicado variable en lugar del transistor de conmutación para producir una resistencia variable.

La figura 16 muestra el detalle de un espejo de corriente programable para una etapa de suma de corriente. Un interruptor conecta uno o más transistores de salida al nodo sumador de salida. Cada transistor de salida se conecta a cualquier puerta de señal conductora desde el transistor de entrada o hacia tierra usando una señal de selección obtenida.

La figura 17 muestra un diagrama de bloques de un mezclador de supresión armónica 1700 de acuerdo con la presente invención. Este diagrama de bloques es funcionalmente equivalente a un diagrama más detallado mostrado en la figura 1. Cada mezclador tiene un coeficiente separado en cada entrada del mezclador.

La figura 18 muestra un diagrama de bloques de otra modalidad de un mezclador de supresión armónica 1800 de acuerdo con la presente invención. En esta modalidad, se proporciona un mezclador separado en la trayectoria de la señal para los componentes I y Q de la señal, cada mezclador tiene un coeficiente separado en el mezclador de entrada RF.

## ES 2 330 761 T3

La figura 19 muestra un combinador de cuadratura para el uso con el mezclador de supresión armónica que utiliza elementos de retraso diferencial en la trayectoria I y Q para crear un cambio relativo de 90 grados en las señales de la frecuencia IF. Las entradas I y Q para la combinación de cuadratura pueden ser conducidas desde cualquier modalidad de un mezclador de supresión armónica mostrada en la figura 1, Fig., 17, o Fig. 18. Un ejemplo de un

5 elemento de retraso diferencial es un filtro polifásico. La cuadratura de combinación IQ puede ser implementada tanto en el dominio analógico como digital. Los filtros polifásicos están descritos en Behbahani, F., Kishigami, Y.; Leete, J.; Abidi, A.A., "CMOS mixers and polyphase filters for large image rejection", IEEE Journal of Solid-State Circuits, Volume : 36, Issue : 6, June2001 páginas 873 - 887.

10 La figura 20 muestra un diagrama detallado de bloque de un generador multifásico LO que consiste en un modelo de generador 320 (LO\_PG) y que cambia cronológicamente el registro 330 (LO\_cambioReg). El generador de patrón 320 proporciona la señal de entrada 306 para el primer circuito basculante 332 del registro 330 de cambio. Cada circuito basculante en el registro de cambio es idéntico y está descrito debajo del circuito basculante. El generador de patrón 320 divide además la frecuencia de entrada (Fin) 310 mediante el divisor 322 para proveer la señal de resincronización 308 a la entrada de la temporización de todos los circuitos basculantes en el registro 330 de cambio. Es posible utilizar diferentes tipos de circuitos basculantes, pero en esta modalidad y a modo de ejemplo, se usan los circuitos basculantes de tipo D. Los circuitos basculantes mencionados aquí serán referidos como "DFF". Los circuitos basculantes, tienen una configuración subordinada de control maestro subordinado con el seguro maestro y el segundo seguro subordinado proporciona salidas. En esta modalidad particular, se describe un registro de cambio 15 20 con 8 circuitos basculantes. Otras modalidades podrían variar en el número de circuitos basculantes utilizado en el registro de cambio, dependiendo de la topología del patrón de circuito generador y del tipo de circuito para realizar la función de los circuitos basculantes.

En el circuito 330 generador del patrón, la frecuencia de entrada 310 (Fin) es dividida por debajo de la frecuencia 25 deseada LO 306 por un divisor 324 de dos etapas. Esta señal se vuelve a temporizar a una frecuencia 308 mediante los ocho registros de cambio de los circuitos basculantes. Para describir la funcionalidad, se consideran tres pruebas de división de frecuencia:

- 30 • Rclk es la proporción de división de frecuencia de la frecuencia de entrada 310 (Fin) y la nueva temporización de la frecuencia 308 (FcIk), donde  $Rclk=1, 2$  o  $4$ .

- 35 • fase R es la proporción de división de frecuencia y nueva temporización de la frecuencia 308 (FcIk) y la frecuencia de entrada 306 (FLO) del primer DFF, donde la fase  $R=4, 8$  o  $16$ .

- 35 • Rdiv es la proporción de división de frecuencia total de la entrada de frecuencia 310 (fin) y la frecuencia LO 306 (FLO). Esta es igual a  $Rphase \cdot Rclk$  que resulta en  $Rdiv = 4, 8, 16, 32$  o  $64$ .

40

TABLA 5

| Tabla 5 Relación entre fases y proporciones de división |       |      |                              |

|---------------------------------------------------------|-------|------|------------------------------|

| Relaciones de división                                  |       |      | Número de fases (nΦ) (Modos) |

| Rclk                                                    | Rfase | Rdiv |                              |

| 1                                                       | 4     | 4    | 2                            |

| 1                                                       | 8     | 8    | 4                            |

| 1                                                       | 16    | 16   | 8                            |

| 2                                                       | 16    | 32   | 8                            |

| 4                                                       | 16    | 64   | 8                            |

60 La proporción de la división de la fase R establece el número de las fases de salida del generador LO. Usando las proporciones de división de 4 hasta 16, la salida del banco de registro de cambio proporcionará dos, cuatro u ocho fases diferentes. Una apreciación de los diferentes modelos se proporciona en la tabla 5. El número de fases no depende del valor de Rclk, ya que ambas señales de entrada y de nueva temporización están divididas por esta proporción. Para valores de Rdiv superiores a dieciséis, la frecuencia de entrada se divide de manera descendente por un factor Rclk antes de la partición de la señal entre la trayectoria de entrada de circuitos basculantes y la trayectoria de nueva temporización. Por consiguiente los modelos con proporciones de división de 32 y 64 tienen aún una resolución de  $\pi/8$  (1/16 de un período), resultando ocho fases en la salida del registro de cambio.

## ES 2 330 761 T3

La salida 334 (salida del seguro maestro) de cada uno de los circuitos basculantes se usa como entrada para el próximo circuito basculante. Para evitar una carga extra (posiblemente asimétrica) en la salida sensitiva subordinada 336, un seguro extra nuevamente temporizado en la fase de temporización subordinada se inserta como etapa de entrada de cada DFF, y la salida se toma desde el seguro maestro del DFF previo. Para minimizar el efecto de la carga en el seguro maestro, se usa un seguidor emisor o seguidor de fuente para conducir los dos subordinados.

La figura 21 muestra los detalles de los circuitos basculantes de registro de cambio y la interconexión de dos circuitos basculantes consecutivos 401 y 402 que tienen cada uno dos seguros subordinados. Los seguros maestros y subordinados se activan o disparan en fases opuestas o extremos de fase de la señal de temporización 404 (Clk). El Clk 404 es conducido por Fclk 308. El seguro subordinado 406 en la entrada de cada circuito basculante conduce el seguro maestro 408 dentro del mismo circuito basculante. El seguro maestro 408 conduce al segundo seguro subordinado 410 dentro del mismo circuito basculante, y también, el primer seguro subordinado 406 del siguiente circuito basculante en el registro de cambio. El número total de circuitos basculantes interconectados de esta manera se fija mediante el número de señales de salida deseadas. La señal 412 es la señal de entrada del primer circuito basculante en el registro de cambio. Al usar este tipo de interconexión, la salida subordinada no se carga por el siguiente circuito basculante y las transiciones de extremo pueden ser más rápidas, mejor definidas en tiempo y alimentadas a través de la temporización maestra para que se evite una salida subordinada.

La conexión de la línea de temporización 404 limita la proporción de la frecuencia de nueva temporización y la frecuencia LO (Fclk/FLO) a un mínimo de 4. En este esquema de temporización, la exactitud de fase de señal de salida no es sensible al ciclo de trabajo de la señal de temporización.

Al usar un esquema de temporización alternativo, la proporción mínima de Fclk/FLO puede ser reducida a 2. Más específicamente, esto puede hacerse usando ambas fases o extremos de la señal de temporización. Por ejemplo, todos los circuitos basculantes pares numerados serían cronometrados en una fase positiva o extremo de temporización creciente y todos, incluso los circuitos basculantes numerados estarían temporizados en una fase negativa o extremo de descenso. El extremo o fase que temporiza el seguro maestro se considera borde o fase que temporiza los circuitos basculantes. Otras configuraciones podrían además ser usadas para realizar la misma proporción mínima de Fclk/FLO. Este esquema de temporización es sensible al ciclo de trabajo.

La figura 22 muestra un ejemplo de basculante de doble esclavo disparado en el extremo utilizando la lógica acoplada al emisor (ECL). Otras implementaciones podrían diferir en el tipo de evento que dispara a los circuitos basculantes (borde de temporización, nivel de temporización, etc.), en el tipo de tecnología utilizado (bipolar, BiCMOS, CMOS GaAS, etc.), o en el tipo de lógica o en cualquier detalle de la topología del circuito usado para realizar la funcionalidad de circuitos basculantes subordinados dobles.

La figura 23 muestra una modalidad del mezclador de supresión armónica. La entrada RF 510 conduce todos los mezcladores 520. El mezclador 520 de salida se acopla al control de ganancia 530 conmutable con las resistencias 534 que determinan la ganancia y conmutación 532 seleccionando que resistencias 534 determinadas de ganancia se conectan. El filtro 540 conmutable usa una conmutación 542 para conectar los capacitores 544, que determinan la frecuencia de un polo del filtro. Los amplificadores de memoria intermedia 550 conducen a los amplificadores 570 programables, que pueden ser utilizados para establecer el valor del coeficiente asociado a cada mezclador. Para aislar las señales del mezclador en configuraciones donde no se utilizan todos los mezcladores 520, se pueden utilizar interruptores 560. Los interruptores también pueden ser utilizados para invertir la polaridad de la señal. El nodo adicional 580 combina todas las señales de los mezcladores dentro de una señal compuesta. Las salidas I y Q son componentes de la señal subconvertida de una banda de base.

La tabla 6 muestra opciones de ejemplo que utilizan ciclos simples y múltiples dentro de un período LO y para optimizar el rango VCO de supresión armónica.

50

(Tabla pasa a página siguiente)

55

60

65

# ES 2 330 761 T3

## Opción 1

*Sin utilizar ciclos múltiples*

| fvco | min                |                            | max                               |                | 3440 MHz rango VCO maxf/minf = 2         |            |                                                        |

|------|--------------------|----------------------------|-----------------------------------|----------------|------------------------------------------|------------|--------------------------------------------------------|

|      | Número de fases LO | # de ciclos por periodo LO | Relación VCO div antes del gen LO | Rango LO final | Frecuencia de conversión armónica mínima | Comentario |                                                        |

| 1720 | 8                  | 1                          | 4                                 | 50.00          | 53.75                                    | 750.00     | Rechazo hasta el armónico 15                           |

|      | 8                  | 1                          | 2                                 | 53.75          | 107.50                                   | 806.25     | Rechazo hasta el armónico 15                           |

|      | 8                  | 1                          | 1                                 | 107.50         | 215.00                                   | 1612.50    | Rechazo hasta el armónico 15                           |

|      | 4                  | 1                          | 1                                 | 215.00         | 430.00                                   | 1505.00    | Rechazo hasta el armónico 7 Mezclador I/Q estándar: No |

|      | 2                  | 1                          | 1                                 | 430.00         | 860.00                                   | 1290.00    | Rechazo del armónico 3                                 |

## 35 Opción 2

*Ciclos múltiples usados - rango VCO minimizado - rechazo armónico mejorado en la banda alta*

| fvco       | min                |                            | max                               |                | 4586.667 MHz rango VCO maxf/minf = 1.5   |            |         |

|------------|--------------------|----------------------------|-----------------------------------|----------------|------------------------------------------|------------|---------|

|            | Número de fases LO | # de ciclos por periodo LO | Relación VCO div antes del gen LO | Rango LO final | Frecuencia de conversión armónica mínima | Comentario |         |

| 3057.77778 | 8                  | 1                          | 8                                 | 35.83          | 50.00                                    | 537.45     | 750.00  |

|            | 8                  | 3                          | 16                                | 50.00          | 53.75                                    | 216.67     | 232.92  |

|            | 8                  | 1                          | 4                                 | 53.75          | 71.67                                    | 806.25     | 1075.00 |

|            | 8                  | 3                          | 8                                 | 71.67          | 107.50                                   | 310.56     | 465.83  |

|            | 8                  | 1                          | 2                                 | 107.50         | 143.33                                   | 1612.50    | 2150.00 |

|            | 8                  | 3                          | 4                                 | 143.33         | 215.00                                   | 621.11     | 931.67  |

|            | 8                  | 1                          | 1                                 | 215.00         | 286.67                                   | 3225.00    | 4300.00 |

|            | 8                  | 3                          | 2                                 | 286.67         | 430.00                                   | 1242.22    | 1863.33 |

|            | 4                  | 1                          | 1                                 | 430.00         | 573.33                                   | 3010.00    | 4013.33 |

|            | 8                  | 3                          | 1                                 | 573.33         | 860.00                                   | 2484.44    | 3726.67 |

ES 2 330 761 T3

### Opción 3

### *Ciclos múltiples usados - rechazo armónico optimizado*

5 min max

fvco 2293.33333 4586.667 MHz rango VCO maxf/minf = 2

| Número de fases LO | # de ciclos por periodo LO | Relación VCO div antes del gen LO | Rango final LO |        | Frecuencia de conversión armónica mínima |         | Comentario                   |

|--------------------|----------------------------|-----------------------------------|----------------|--------|------------------------------------------|---------|------------------------------|

|                    |                            |                                   | min            | max    | min                                      | max     |                              |

| 8                  | 1                          | 4                                 | 50.00          | 71.67  | 750.00                                   | 1075.00 | Rechazo hasta el armónico 15 |

| 8                  | 1                          | 2                                 | 71.67          | 143.33 | 1075.00                                  | 2150.00 | Rechazo hasta el armónico 15 |

| 8                  | 1                          | 1                                 | 143.33         | 286.67 | 2150.00                                  | 4300.00 | Rechazo hasta el armónico 15 |

| 4                  | 1                          | 1                                 | 286.67         | 573.33 | 2006.67                                  | 4013.33 | Rechazo hasta el armónico 7  |

| 8                  | 3                          | 1                                 | 573.33         | 860.00 | 2484.44                                  | 3726.67 | Rechazo hasta el 4 1/3 x fLO |

40

45

50

60

65

## REIVINDICACIONES

5. 1. Un mezclador de supresión armónica (100, 1700, 1800) para la subconversión de una señal de radio frecuencia (RF) (102) **caracterizado** porque comprende:

- 10 una pluralidad de mezcladores de conmutación (110) cada uno con una entrada de oscilador local (LO) (114), una entrada RF (112), y una salida de mezclador (116) en donde cada entrada RF del mezclador de conmutación (112) se conduce mediante una versión proporcional de la señal RF (102);

- 15 medios de ponderación de señales (120, 130) para la ponderación de señales que son mezcladas por los mezcladores de conmutación (110);

- 20 Un sumador para sumar las señales ponderadas del mezclador con el fin de producir una salida (104, 106); y

- 25 un generador LO con una entrada de temporización para generar una pluralidad de señales LO (LO1-LON), en las que cada señal LO opera substancialmente a la misma frecuencia y tiene una fase predeterminada de desplazamiento relativa a cada otra señal LO, y en las que cada señal LO conduce una entrada LO (114) de uno de los respectivos mezcladores de conmutación (110).

- 30 2. El mezclador de supresión armónica (100, 1700, 1800) según la reivindicación 1, **caracterizado** porque las fases de las señales LO (LO1-LON) son variables, y los medios de ponderación de señales (120, 130) son variables para configurar el mezclador de supresión armónica (100) para un número variable de mezcladores efectivos, así como la proporción de temporización de entrada para la frecuencia de la señal LO, es variable.

- 35 3. El mezclador de supresión armónica (100, 1700, 1800) según la reivindicación 1 y 2 **caracterizado** porque los medios de ponderación de señales son una pluralidad de las primeras etapas (120) del coeficiente que ponderan las señales de salida del mezclador comutador con valores del coeficiente y las primeras etapas del coeficiente se acoplan al sumador.

- 40 4. El mezclador de supresión armónica (100, 1700, 1800) según la reivindicación 1 y 2, **caracterizado** porque los medios de ponderación de señales son una pluralidad de primeras etapas del coeficiente (120) que pondera las señales de salida del mezclador comutador, utilizando valores de coeficiente en fase, y porque el sumador produce una salida I (I) y además comprende una pluralidad de segundas etapas de coeficiente (130) que ponderan las señales de salida del mezclador comutador con valores del coeficiente de la fase de cuadratura y están acopladas a un segundo sumador para producir una salida Q (Q).

- 45 5. El mezclador de supresión armónica (1800) según la reivindicación 4, se **caracteriza** porque los mezcladores de conmutación (110) se agrupan dentro de un banco I y un banco Q, las primeras etapas del coeficiente (a1 - an) están conectadas al banco I y las segundas etapas del coeficiente (b1 - bn) están conectadas al banco Q, y también porque para cada una de las señales LO, son conducidos mediante la misma señal LO un mezclador del banco I y un mezclador del banco Q.

- 50 6. El mezclador de supresión armónica (100, 1700, 1800) según al menos una de las reivindicaciones 1 a 5 se **caracteriza** además porque comprende una pluralidad de amplificadores de transconductancia que conducen las entradas RF hacia los mezcladores de conmutación (110).

- 55 7. El mezclador de supresión armónica (100, 1700, 1800) agún al menos una de las reivindicaciones 1 a 6, se **caracteriza** porque, por lo menos dos mezcladores son conducidos con señales LO que tienen la misma fase, y los valores del coeficiente se establecen de modo tal que el número efectivo de mezcladores sea menor que el número total de mezcladores.

- 60 8. El mezclador de supresión armónica (100, 1700, 1800) según una de las reivindicaciones 1 a 7, se **caracteriza** porque comprende además, una pluralidad de etapas de coeficiente de entrada, en la que una etapa del coeficiente de entrada se acopla a cada entrada del mezclador de conmutación y la ganancia de las etapas del coeficiente de entrada pueden alcanzar desde menos de uno hasta más allá de uno.

- 65 9. El mezclador de supresión armónica (100, 1700, 1800) según al menos una de las reivindicaciones 1 a 8, se **caracteriza** porque las entradas RF se ponderan haciendo variar los parámetros de transconductancia de los mezcladores y las salidas del mezclador se suman directamente al mismo tiempo a un nodo sumador para producir la salida (104, 106).

10. El mezclador de supresión armónica (100, 1700, 1800) según una de las reivindicaciones 4 a 8 se **caracteriza** porque I y Q son salidas complejas en una frecuencia intermedia (IF).

- 65 11. El mezclador de supresión armónica (100, 1700, 1800) según una de las reivindicaciones 4 a la 8, se **caracteriza** porque I y Q son salidas complejas en una banda base.

# ES 2 330 761 T3

12. El mezclador de supresión armónica (100, 1700, 1800) según la reivindicación 10 u 11 se **caracteriza** porque comprende además un modulador de cuadratura (440) que acepta las señales I y Q y produce una salida.

- 5 13. El mezclador de supresión armónica (100, 1700, 1800) según la reivindicación 10 y 11 se **caracteriza** porque comprende además, un combinador de cuadratura que acepta las señales I y Q y produce una salida.

- 10 14. El mezclador de supresión armónica (100, 1700, 1800) según una de las reivindicaciones 4 a 13, se **caracteriza** porque las primeras etapas del coeficiente (a1-an) y las segundas etapas del coeficiente (b1-bn) son programables para una pluralidad de valores únicos obtenidos que producen un perfil de ponderación sinusoidal.

- 15 15. El mezclador de supresión armónica (100, 1700, 1800) según una de las reivindicaciones 8 a 14, se **caracteriza** porque las etapas del coeficiente de entrada (c1 - cn, d1 - dn) son programables para una pluralidad de valores de ganancia únicos que producen un perfil de ponderación sinusoidal.

- 20 16. El mezclador de supresión armónica (100, 1700, 1800) según una de las reivindicaciones 1 a 15, se **caracteriza** porque el generador LO (200) que produce series de señales digitales para conducir las entradas LO del mezclador de conmutación comprende:

- un generador de patrón (320) que determina una frecuencia LO; y

- 25 17. El mezclador de supresión armónica (100, 1700, 1800) según la reivindicación 16, se **caracteriza** porque el generador patrón (320) divide la señal de temporización por una proporción que puede ser cambiada.

- 30 18. El mezclador de supresión armónica (100, 1700, 1800) según una de las reivindicaciones 1 a 15, se **caracteriza** porque el generador LO (200) comprende una máquina de estado reconfigurable para producir una serie de señales digitales alternadas y conducir las entradas del mezclador de conmutación LO.

19. El mezclador de supresión armónica (100, 1700, 1800) según la reivindicación 18, se **caracteriza** porque comprende además un banco de registro para temporizar nuevamente las señales digitales escalonadas.

- 35 20. El mezclador de supresión armónica (100, 1700, 1800) según una de las reivindicaciones 1 a 19, se **caracteriza** porque el generador LO (200) para generar una primera pluralidad de señales LO se programa para producir una segunda pluralidad de fases únicas LO, en la que la segunda pluralidad puede ser menor que la primera y sea posible conducir por lo menos dos mezcladores con la misma fase LO.

- 40 21. El mezclador de supresión armónica (100, 1700, 1800) según una de las reivindicaciones 1 a 20, se **caracteriza** porque la salida de la adición se digitaliza mediante un convertidor análogo a digital.

22. El mezclador de supresión armónica (100, 1700, 1800) según una de las reivindicaciones 1 al 20, se **caracteriza** porque la salida del mezclador se digitaliza mediante un convertidor análogo a digital y la ponderación y combinación se ejecutan en un dominio digital.

- 45 23. El mezclador de supresión armónica (100, 1700, 1800) según una de las reivindicaciones 1 al 22, se **caracteriza** porque el mezclador de supresión armónica cubre un rango de frecuencia RF de entrada que abarca de 50 MHz a 860 MHz.

- 50 24. Un sintonizador RF **caracterizado** por una subconversión de la señal de entrada de banda ancha RF que utiliza el mezclador de supresión armónica según la reivindicación 1 a 23.

25. El sintonizador RF según la reivindicación 24, se **caracteriza** además porque comprende un amplificador de banda ancha acoplado entre la señal de entrada de banda ancha RF y el mezclador de entrada de supresión armónica.

- 55 26. El sintonizador RF según la reivindicación 24, se **caracteriza** además porque comprende un diplexor acoplado a la señal de entrada RF de banda ancha para dividir la frecuencia en sub bandas; y una pluralidad de filtros preseleccionados para filtrar las salidas del diplexor en los que las salidas del diplexor se acoplan a la entrada del mezclador de supresión armónica.

- 60 27. El sintonizador RF según la reivindicación 24, se **caracteriza** además porque comprende un atenuador acoplado entre la señal de entrada de banda ancha RF y la entrada del mezclador de supresión armónica.

28. El sintonizador RF según la reivindicación 24, se **caracteriza** además porque comprende por lo menos un filtro preseleccionado acoplado entre la señal de entrada RF de banda ancha y la entrada del mezclador de supresión armónica.

## ES 2 330 761 T3

29. El sintonizador RF según la reivindicación 28, se **caracteriza** porque comprende un filtro preseleccionado que es sintonizable (410).

30. El sintonizador RF según la reivindicación 24, se **caracteriza** además porque comprende,

5 un atenuador acoplado a la entrada de banda ancha RF;

y un filtro preseleccionado acoplado entre el atenuador y la entrada del mezclador de supresión armónica.

- 10 31. El sintonizador RF, según la reivindicación 24, se **caracteriza** además porque comprende

un atenuador acoplado a la entrada de banda ancha RF;

15 un amplificador de memoria intermedia acoplado a la salida del atenuador; y

un filtro preseleccionado acoplado entre la salida de la memoria intermedia y la entrada del mezclador de supresión armónica.

- 20 32. El sintonizador RF según una de las reivindicaciones 24 a 31, se **caracteriza** además porque comprende un filtro (420) de banda limitada I y Q acoplado a las salidas I y Q del mezclador de supresión armónica.

- 25 33. El sintonizador RF según una de las reivindicaciones 24 a la 31, se **caracteriza** además, porque comprende

Un filtro (420) acoplado de banda limitada I y Q para las salidas I y Q del mezclador de supresión armónica; y

25 un circuito de ajuste de rechazo de imagen (430) para suprimir la señal de la imagen acoplada a las salidas del filtro de banda limitada.

- 30 34. El sintonizador RF según una de las reivindicaciones 24 a la 31, se **caracteriza** además porque comprende

un circuito (430) de ajuste de rechazo de imagen acoplado a las salidas del mezclador de supresión armónica para

suprimir la señal de la imagen.

35. El sintonizador RF según una de las reivindicaciones 24 a 31, se **caracteriza** porque comprende:

35 un circuito (430) de ajuste de rechazo de imagen acoplado a las salidas del mezclador de supresión armónica para

suprimir la señal de la imagen; y

el filtro (420) de banda limitada I y Q acoplado a las salidas I y Q de balance y fase corregida.

- 40 36. El sintonizador RF según una de las reivindicaciones 24 a la 35, se **caracteriza** además porque comprende un

superconvertidor (440) IF en la salida del mezclador de supresión armónica para la super-conversión de la señal I y Q.

- 45 37. Un método de sintonización de señales desde una frecuencia de radio de banda ancha (RF) (102),**caracterizado**

porque comprende:

la recepción de la señal (102) RF de banda ancha;

- 50 la subconversión de la señal (102) de banda ancha RF a una señal de frecuencia más baja (104, 106), utilizando un

mezclador de supresión armónica, que comprende:

la conducción de una pluralidad de mezcladores de conmutación (110) con la señal (102) RF y con una pluralidad

de señales de oscilador local (LO1-LON) recibidas desde un generador LO (200) con una entrada de temporización

de frecuencia, en la que cada señal LO opera a substancialmente la misma frecuencia y tiene una fase predeterminada

de desplazamiento relativa a cada otra señal LO;

- 55 la aplicación de ponderación para cada señal del mezclador, para producir señales de mezclador ponderadas; y

sumar las señales del mezclador ponderadas, en la que cada señal de mezclador contribuye a una salida del mez-

clador compuesto para producir la señal de frecuencia más baja (104, 106); y

- 60 filtrar (420) la señal de frecuencia más baja (104, 106) para restringir la banda ancha de la misma con el fin de

producir una señal de salida.

- 65 38. El método según la reivindicación 37, se **caracteriza** porque las fases de las señales LO (LO1 - LON) son

configurables.

39. El método según la reivindicación 38 se **caracteriza** porque comprende: la configuración del generador LO

(200) para producir por lo menos dos señales LO que tienen la misma fase y conducir al menos dos mezcladores de

## ES 2 330 761 T3

comutación (110) con señales LO que tienen la misma fase con el fin de reducir el número efectivo de mezcladores de comutación (110), y de reducir la proporción entre la frecuencia de cronómetro y la frecuencia de la señal LO.

40. El método según una de las reivindicaciones 38 o 39 se **caracteriza** además porque comprende: el aislamiento de las salidas de alguno de los mezcladores de comutación (110) y la suma de las salidas remanentes para producir la señal de frecuencia más baja.

41. El método según una de las reivindicaciones 37 a 40, se **caracteriza** porque la ponderación de cada señal del mezclador se ejecuta mediante la pluralidad de las primeras etapas del coeficiente (a1 - an) y un segundo conjunto de señales de mezcladores ponderadas se produce mediante una pluralidad (b1 - bn) de segundas etapas del coeficiente;

la ganancia de las etapas del primer coeficiente puede variar desde menos de uno hasta mayor de uno y

la ganancia de las etapas del segundo coeficiente puede variar desde menos de uno hasta mayor de uno, y

15 sumar la salida de las etapas del segundo coeficiente para producir una segunda señal de frecuencia inferior.

42. El método según una de las reivindicaciones 38 a 41, se **caracteriza** además porque comprende la reconfiguración de las señales LO y el cambio de las etapas del primer y segundo coeficiente (a1 - an, b1 - bn) tal que el número efectivo de mezcladores se reduzca mediante la conducción de por lo menos dos mezcladores con señales LO que tienen la misma fase.

43. El método según una de las reivindicaciones 37 a 42, se **caracteriza** además porque comprende las etapas del coeficiente de entrada (c1 - cn, d1 - dn), en las que la ganancia se aplica a cada señal del mezclador de comutación antes y después de los mezcladores de comutación (110), y en las que el valor de cada etapa del coeficiente puede ser diferente.

44. El método según una de las reivindicaciones 37 a 43, se **caracteriza** porque después de recibir las señales de banda ancha RF, se logra la filtración de la señal RF (102) mediante un filtro pre-seleccionado de sintonía (410).

30 45. El método según una de las reivindicaciones 37 a 44, se **caracteriza** porque después de recibir la señal de banda ancha RF (102),

La señal se atenúa; y

35 la señal atenuada conduce un amplificador de memoria intermedia; y

la salida del amplificador de memoria intermedia se filtra mediante un filtro pre-seleccionado (410); y

40 la salida del filtro pre-seleccionado conduce al mezclador de supresión armónica (100).

46. El método según una de las reivindicaciones 37 a 45, se **caracteriza** porque comprende la digitalización de las salidas de cada mezclador (110) antes de combinarlas, y la ponderación y combinación se hacen en un dominio digital.

45 47. El método según una de las reivindicaciones 37 a 46, se **caracteriza** además porque comprende: la supresión de la señal de imagen (430).

48. El método según una de las reivindicaciones 37 a 47, se **caracteriza** porque la frecuencia inferior es una señal 50 I y Q de frecuencia IF y además comprende una cuadratura que combina las señales I y Q (440) para formar una señal de salida.

49. El método según la reivindicación 48, se **caracteriza** además, porque comprende la digitalización de la señal de salida.

55

60

65

FIG. 1

FIG. 2

FIG. 3

FIG. 4

**FIG. 5 fase 8, ciclo 1, I LO**

**FIG. 6 fase 8, ciclo 1, Q LO**

**FIG. 7 fase 8, ciclo 3, I LO**

**FIG. 8 fase 8, ciclo 3, Q LO**

**FIG. 9 fase 4, ciclo 1, I LO**

**FIG. 10 fase 4, ciclo 1, Q LO**

**FIG. 11 fase 2, ciclo 1, I LO**

**FIG. 12 fase 2, ciclo 1, Q LO**

formas de onda LO y sinusode sintetizado resultante

Espectro de forma de onda sintetizado

FIG. 13

$$C_{in} = \frac{R_2}{R_{in}}$$

$$C_{qn} = \frac{R_2}{R_{qn}}$$

FIG. 14

FIG. 16

FIG. 17

FIG. 18

FIG. 19

FIG. 20

FIG. 21

FIG. 22