(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5721742号

(P5721742)

(45) 発行日 平成27年5月20日(2015.5.20)

(24) 登録日 平成27年4月3日(2015.4.3)

|               |           |              |   |

|---------------|-----------|--------------|---|

| (51) Int.Cl.  | F 1       |              |   |

| H 01 L 23/02  | (2006.01) | H 01 L 23/02 | D |

| B 81 B 7/02   | (2006.01) | B 81 B 7/02  |   |

| B 81 C 3/00   | (2006.01) | B 81 C 3/00  |   |

| H 01 L 21/301 | (2006.01) | H 01 L 21/78 | Q |

|               |           | H 01 L 23/02 | C |

請求項の数 6 (全 9 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2012-544551 (P2012-544551)  |

| (86) (22) 出願日 | 平成22年11月22日(2010.11.22)       |

| (65) 公表番号     | 特表2013-513971 (P2013-513971A) |

| (43) 公表日      | 平成25年4月22日(2013.4.22)         |

| (86) 国際出願番号   | PCT/US2010/057624             |

| (87) 国際公開番号   | W02011/081741                 |

| (87) 国際公開日    | 平成23年7月7日(2011.7.7)           |

| 審査請求日         | 平成25年11月21日(2013.11.21)       |

| (31) 優先権主張番号  | 12/638,424                    |

| (32) 優先日      | 平成21年12月15日(2009.12.15)       |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                            |

|-----------|------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 504199127<br>フリースケール セミコンダクター イン<br>コーポレイテッド<br>アメリカ合衆国 テキサス州 78735<br>オースティン ウィリアム キャノン<br>ドライブ ウエスト 6501 |

| (74) 代理人  | 100142907<br>弁理士 本田 淳                                                                                      |

| (72) 発明者  | リウ、リエンジュン<br>アメリカ合衆国 85286 アリゾナ州<br>チャンドラー イースト ハニーサック<br>ル プレイス 2575                                      |

最終頁に続く

(54) 【発明の名称】ウェハ構造の電気的結合

## (57) 【特許請求の範囲】

## 【請求項 1】

第1ウェハを第2ウェハに電気的に結合する方法であって、

結合物質を用いて前記第1ウェハを前記第2ウェハに結合して、結合されたウェハを形成すること、

前記第1ウェハと前記第2ウェハのスクライブ領域における結合物質とに開口を形成して前記第2ウェハの導電性構造の少なくとも一部分を露出させること、

前記第1ウェハおよび前記第2ウェハにおける前記開口上に導電性層を形成して、前記導電性層が前記第2ウェハの導電性構造との電気的接続を形成して前記第1ウェハを前記第2ウェハに電気的に結合すること、

前記結合されたウェハを複数のダイに分離することを備え、

前記分離することは、前記第2ウェハの分離経路の物質を除去することを含み、

前記分離経路は、第1幅を有し、前記開口は第2幅を有し、

前記第1幅および前記第2幅は、分離されたダイの少なくとも1つの側壁に前記導電性層の少なくとも1つの部分を残して、前記第1ウェハと前記第2ウェハとの間の電気的結合を提供するように選択される、方法。

## 【請求項 2】

前記第2ウェハが複数のパッドを含み、

前記第1ウェハにおいて前記開口を形成した後に、前記第1ウェハに第2開口を形成して前記複数のパッドの露出させることをさらに備える、請求項1に記載の方法。

**【請求項 3】**

前記複数のダイの各々が、前記第1ウェハの構造の表面および前記第2ウェハの構造の表面によって画定されるキャビティを含む、請求項1に記載の方法。

**【請求項 4】**

前記第2ウェハが複数の微小電気機械システム（MEMS）デバイスを含む、請求項3に記載の方法。

**【請求項 5】**

前記結合物質は非導電性のグラスフリットである、請求項1に記載の方法。

**【請求項 6】**

前記第2ウェハの導電性構造は、前記第2ウェハのスクライブ領域に配置された部分を含み、10

前記結合物質は、前記第2ウェハのスクライブ領域において前記第2ウェハの導電性構造の上方に位置する、請求項1に記載の方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、概して半導体デバイスに関するものであり、さらに詳しくは2つのウェハ構造の電気的結合に関するものである。

**【背景技術】****【0002】**

MEMS半導体デバイスのようないくつかの半導体デバイスは、キャップウェハを利用して、動作におけるMEMSデバイスの保護キャビティを提供する。いくつかの実施形態では、MEMSデバイスは、半導体デバイス工程とともに通常に製造される微小電気機械デバイスである。MEMSデバイスの例は、加速度計、センサ、マイクロモータおよびスイッチを含む。いくつかの例において、MEMSデバイスは、動作中に移動する部分（例えば、プルーフマス（proof masses））を含む。この移動のため、キャビティは、この部分の移動中にこの部分を保護するように用いられる。

**【0003】**

キャップウェハに開口を形成し、デバイスウェハにキャップウェハを結合し、開口がMEMSデバイスを覆うことによって、キャビティは具体化される。その後、キャップウェハおよびデバイスウェハは分離されて、MEMSダイを形成する。

**【0004】**

いくつかの例におけるキャップウェハの具体化に関連する1つの問題は、デバイスウェハとの好適な接地結合（grounding coupling）が必要とされることである。いくつかの例において、接地結合は、キャップウェハからデバイスウェハへのワイヤ結合、キャップウェハからデバイスウェハへ貫通する導電性ビア、またはキャップウェハとデバイスウェハとの間の導電性結合材料によって形成される。

**【図面の簡単な説明】****【0005】**

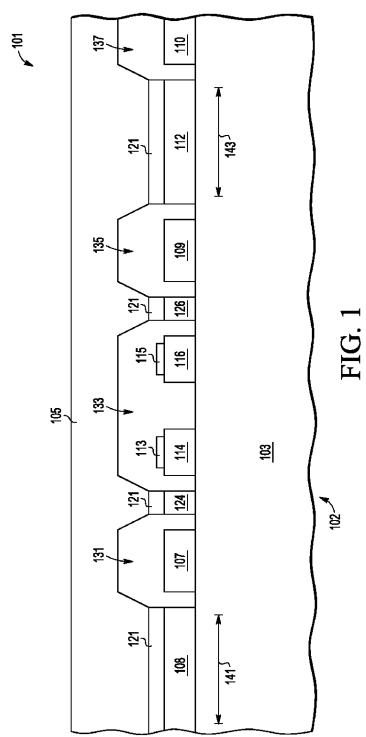

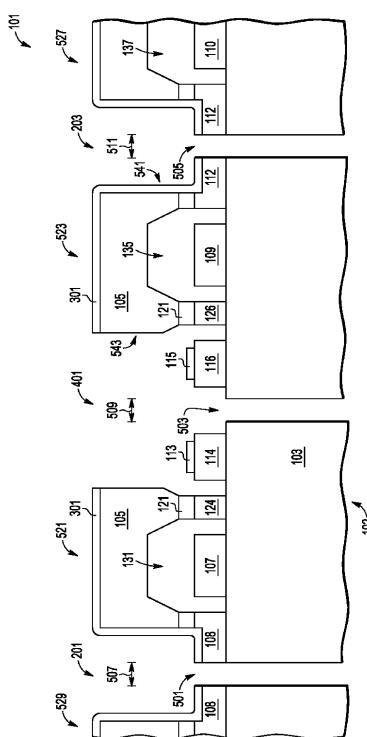

【図1】本発明の一実施形態にしたがった、キャップウェハ構造を有する半導体デバイスの製造における各段階の図を示す。

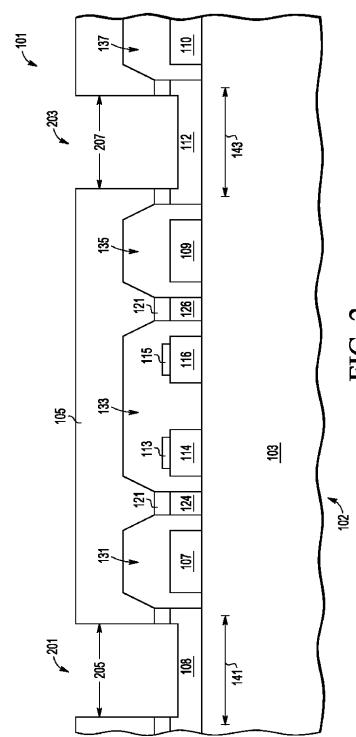

【図2】本発明の一実施形態にしたがった、キャップウェハ構造を有する半導体デバイスの製造における各段階の図を示す。

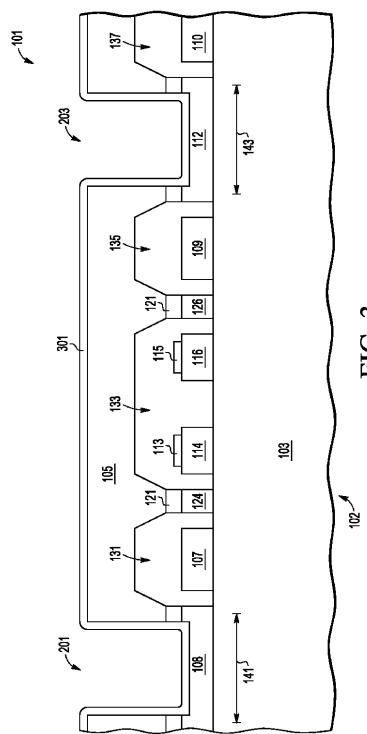

【図3】本発明の一実施形態にしたがった、キャップウェハ構造を有する半導体デバイスの製造における各段階の図を示す。

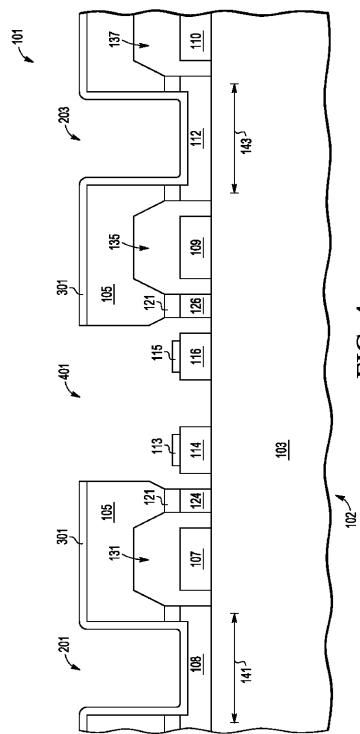

【図4】本発明の一実施形態にしたがった、キャップウェハ構造を有する半導体デバイスの製造における各段階の図を示す。

【図5】本発明の一実施形態にしたがった、キャップウェハ構造を有する半導体デバイスの製造における各段階の図を示す。

【図6】本発明の一実施形態にしたがった、キャップウェハ構造を有する半導体デバイス

10

20

30

40

50

の製造における各段階の図を示す。

【発明を実施するための形態】

【0006】

添付の図面を参照することによって、本発明はよりよく理解され、その多くの目的、特徴および利点が当業者に明らかになる。図面は、必ずしも一定の縮尺で描かれていない。例えば、本発明の特徴を明確に示すために、図示される構造の幅と高さとの比は、正確でなくてもよい。

【0007】

以下に述べるのは本発明を実施するための1つのモードの詳細な説明である。この説明は本発明の例示を意図するものであり、限定するものではない。

10

本明細書に記載されるように、一実施形態において、キャップウェハ構造からデバイスウェハ構造への電気的結合は、デバイスウェハの導電性構造のスクライプ領域におけるキャップウェハに開口を形成し、次に、開口および開口の側壁を含むキャップウェハ上に、デバイスウェハの導電性構造と接続する導電性層を形成することによって形成される。その後、キャップおよびデバイスウェハは、開口の側壁上に導電性材料が残るようにスクライプ領域において分離されて、キャップウェハ構造をデバイスウェハ構造に電気的に結合する。

【0008】

図1が、結合物質121を用いてキャップウェハ105に結合されたデバイスウェハ102を含む、製造されたウェハ101の部分断面側面図を示す。一実施形態において、結合物質121は非導電性グラスフリットである。しかしながら、他の実施形態において、導電性グラスフリット（例えば、鉛のような導電性材料）または半田のような結合材料等のほかの種類の結合物質が用いられてもよい。一実施形態において、複数のウェハは、所定期間に温度や圧力の下で互いに結合されて、2つのウェハとの間に機械的な固相結合を備える。一実施形態において、結合は密封結合（hermetic bond）である。

20

【0009】

デバイスウェハ102は、ウェハ102とウェハ105との結合を先立って形成される基板103に配置された複数の半導体デバイス107, 109, 110を含む。一実施形態において、このデバイスは、半導体製造工程によって形成される半導体、導電性および/または誘電性物質により構成された構造を含む。複数のデバイス107, 109, 110が、異なる構造を形成するように製造される複数の異なる材料の層を含んでもよい。一実施形態において、複数のデバイス107, 109, 110は多軸加速度計であるが、他の実施形態において、複数のデバイス107, 109, 110は、他のタイプの加速度計、センサ、モータまたはスイッチのようなMEMSデバイスであってもよい。また、他の実施形態において、複数のデバイス107, 109, 110は、集積回路、個別デバイスまたはセンサのような半導体デバイスであってよい。一実施形態において、複数のデバイス107, 109, 110は、基板103上に異なる層を成形・処理することによって形成される。

30

【0010】

ウェハ102が、複数のデバイス107, 109, 110を外部的に外部デバイスに結合する複数のパッド113, 115を含んで、外部デバイス（例えば、集積回路ダイ上）に信号を伝達する。複数のパッド113, 115は、導電性材料（例えば、銅、アルミニウム、及び金）から形成され、一実施形態において、該導電性材料はワイヤ結合可能である。複数のパッド113, 115は、複数のポリシリコン構造114, 116上にそれぞれ配置され、複数のポリシリコン構造114, 116と電気的にそれぞれ接続される。一実施形態において、基板103が、複数の半導体デバイス107, 109, 110の導電性構造を複数のパッド支持構造114, 116に電気的に結合する複数の導電性構造（図示せず）を含む。例えば、デバイス107は構造114に電気的に結合され、デバイス109は構造116に電気的に結合される。

40

【0011】

50

一実施形態において、基板 103 が、基板 103 の層に配置された導電性構造および誘電性構造を有する、シリコン等の半導性材料を含む。いくつかの実施形態において、半導体材料の部分は導電性になるように選択的にドープされる。しかしながら、他の実施形態において、ウェハ 102 が他の構成を有してもよい。

【0012】

デバイスウェハ 102 が、複数のスクライブ領域 141, 143 に配置された部分を含む複数のスクライブ導電性構造 108, 112 を含む。スクライブ領域は、ダイシング中に分離されるウェハの複数のデバイス領域間に配置されるウェハの領域であり、分離経路を含む。複数の構造 108, 112 は、ポリシリコンまたは金属のような導電性材料から形成されている。複数のスクライブ構造 108, 112 の各々は、基板 103 に配置された導電性構造（図示せず）によって（複数のデバイス 107, 109, 110 のうちの）2 つのデバイスに電気的に結合される。例えば、導電性構造 112 は、デバイス 109 およびデバイス 110 に電気的に結合される。

【0013】

また、ウェハ 102 は、デバイスとパッド領域との間に配置される、キャップウェハと結合するための複数の導電性構造 124, 126 を含み、複数のデバイス 107, 109 のシールを提供する。

【0014】

一実施形態において、キャップウェハ 105 は、半導体材料（例えば、シリコン）から形成され、デバイスウェハ 102 の構造に対するキャビティを形成するための（例えば、エッチングによって形成される）複数の開口 131, 133, 135, 137 を含む。一実施形態において、ウェハ 105 はウェハ 102 に貼り付けられた後、ウェハ 105 の上面にグラインド加工及びポリッシング加工を行って、ウェハ 105 の膜厚を薄くする。一実施形態では、ウェハ 105 は、100 ~ 400 マイクロメートルの範囲の薄くされた膜厚に研磨される。しかしながら、他の実施形態において、キャップは他の膜厚に研磨されてもよくまたは研磨しなくてもよい。いくつかの実施形態において、キャップウェハ 105 が、MEMS デバイスまたはそれに形成される他の半導体デバイスのようなデバイスを含んでもよい。一実施形態において、ウェハ 105 が、複数の開口 131, 133, 135, 137 を含まない。

【0015】

図 2 は、ウェハ 105 に複数の開口 201, 203 が形成されてウェハ 102 のスクライブ領域内の複数の導電性構造 108, 112 を露出させた後に得られるウェハ 101 の部分的断面側面図を示す。一実施形態において、ウェハ 105 および結合物質 121 が複数の構造 108, 112 の上方の位置から除去されて導電性構造を露出させることを保障するために、開口は特定の深さに形成される。このような除去は、複数の構造 108, 112 の上部分を除去することを含んでもよい。一実施形態において、開口は鋸を用いて形成される。図示される実施形態において、複数の開口 201, 203 が 80 マイクロメートルの幅 205, 207 を有するが、他の実施形態において、他の幅であってよい。

【0016】

他の実施形態において、結合物質 121 は、複数の開口 201, 203 の領域に形成されない。この領域において、キャップウェハ 105 と複数のスクライブ導電性構造 108, 112 との間に空洞がある。しかしながら、この領域に結合物質を形成することは、スクライブ導電性構造 108, 112 とキャップウェハ 105 との間に結合物質が配置されるため、開口の平らな側壁を提供する。平らな側壁が側壁により優れた導電性層を後に形成する。

【0017】

他の実施形態において、複数の開口 201, 203 は、両軸円鋸盤、レーザまたはエッチングのような方法によって形成されてもよい。

図 3 が、ウェハ 101 上に導電性層 301 を形成した後に得られるウェハ 101 の部分的断面図を示す。一実施形態において、層 301 は金属（例えば、銅、アルミニウム、ま

10

20

30

40

50

たは金)によって形成される。一実施形態において、層が2マイクロンの膜厚を有するが、他の実施形態において、他の膜厚を有してもよい。優れた電気導電性を備えるために、層301は、複数の開口201, 203の側壁に良好なステップカバレッジ(step coverage)を有するように形成される。一実施形態において、層301は、化学蒸着、物理蒸着、電気メッキまたは他の金属形成工程のような金属堆積工程によって形成される。一実施形態において、層301が異なる材料の複数の層を含んでもよい。

#### 【0018】

図4は、複数のパッド113, 115の上方に開口401が形成されて後のテストのためにパッドを露出させた後に得られるウェハ101の部分的断面図を示す。一実施形態において、開口401は両軸円鋸盤によって形成されるが、他の実施形態では他の方法(例えば、エッチング)によって形成されてもよい。開口を形成した後に、ウェハ101は、アッシングのような洗浄工程を受けて不要な有機物質を除去する。その後に、複数のデバイス107, 109, 110は、露出された複数のパッド113, 115に接触するテストプローブを用いて動作性をテストされる。

10

#### 【0019】

図5は、製造されたウェハ101が別個のダイ529, 521, 523, 527に個体化した後の後部分的断面図を示す。一実施形態において、個体化は、スクライブ領域141, 143及びパッド114, 116間ににおいてウェハ101を切削することによって実施される。一実施形態において、ウェハは、鋸、レーザまたは他のウェハカット用装置によって切断される。他の実施形態において、個体化は、スクライブ領域においてウェハ101をエッチングすることによって実施することができる。各ダイ529, 521, 523, 527が、(複数の開口131, 135, 137から形成される)キャビティに配置される半導体デバイス107, 109, 110を含む。一実施形態において、ウェハ102がウェハ105に結合するとき、このキャビティは密封される。

20

#### 【0020】

図示される実施形態において、複数の鋸経路501, 503, 515は、40~50マイクロン幅である幅507, 509, 511を有するが、他の実施形態において、他の幅であってよい。鋸経路の幅507, 509, 511は、前に形成された開口201, 203の幅205, 207未満である。したがって、層301の一部分が開口201, 203の側面に残って、各ダイのウェハ105の部分を個体化後に残った導電性スクライブ構造108, 112に電気的に結合する導電性経路を提供する。

30

#### 【0021】

図示される実施形態において、スクライブ導電性構造112, 108の残留部分は、構造124, 126のような導電性構造に沿ってシールリングを形成して、各ダイのキャビティをシールする。

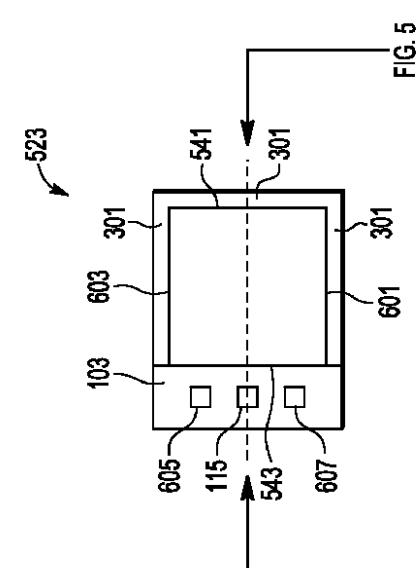

#### 【0022】

図6は、個体化後のダイ523の上面図を示す。図示される実施形態において、層301は、複数のパッド115, 605, 607を露出させる開口401によって形成される部分を除いてダイ523の上部のすべてを覆う。図示される実施形態において、層301が、スクライブ領域の上方の開口(例えば、201および203)によって形成される3つの側壁541, 603, 601を覆う。これにより、図示される実施形態において、2つのウェハ部分を互いに接続する比較的多くの導電性物質が設けられている。他の実施形態において、層301の形状および被覆は異なってよい。例えば、キャップウェハ構造の側壁部分のみまたはキャップウェハ構造のすべての4つの側壁を覆ってもよい。また、他の外部導体のために、層301の上側に開口があってもよい。

40

#### 【0023】

製造されたダイは、自身または他の集積回路ダイによって(例えば、密封物質において)さらにパッケージ化されてもよい。層301はパッケージの接地端子に電気的に結合されてもよい。製造されたパッケージは様々な電子システムに利用され得る。

#### 【0024】

50

結合された 2 つのウェハ間の電気的な結合を提供することは、スクライブ領域に開口を形成して、次に開口を被覆する導電性層を形成することを含み、他の従来技術よりも、2 つのウェハ間のより効率的および高信頼性の電気的な結合を提供する。2 つのウェハの電気的な結合は、電気的に導電性層により形成されるので、電気導電性特徴に関わらず、ウェハの結合物質 121 は、ウェハの結合物質 121 の結合特性によって選択され得る。

#### 【0025】

このような実施形態において、ワイヤ結合は 2 つのウェハ間の接地結合に必要とされない。これにより、通常キャップウェハを接地するワイヤボンドはキャップウェハの上面に形成される点で、最終的なパッケージの総計の高さは低くなる。

#### 【0026】

さらに、比較的大きな開口の側壁に導電性層を形成することは、キャップウェハ内に比較的小さな開口に貫挿される導電性ビアを形成することと比べて技術的に容易である。また、層 301 は、ダイを囲まれるスクライブ領域の大部分を覆うように構成され、内部デバイス領域はワイヤ結合またはビア形成と同様に必要ではない。さらに、複数のワイヤ結合および導電性ビアは、複数のウェハを電気的に結合するために、キャップウェハ構造の側壁に配置される同量の導電性物質を得ることを必要とする。

#### 【0027】

他の実施形態において、複数の初期スクライブ開口 201, 203 はデバイスウェハ 102 の下部により形成されて、キャップウェハ 105 の導電性表面を露出させる。次に、導電性層 301 は、デバイスウェハ 102 の底面上に形成され、開口を広げて、キャップウェハ 105 の露出された導電性表面と接続する。このような実施形態において、デバイスウェハ 102 の底部は研磨されてウェハ結合後の膜厚を薄くさせる。

#### 【0028】

本発明の一実施形態は、第 1 ウェハを第 2 ウェハに電気的に結合することを含む。この方法は、第 1 ウェハを第 2 ウェハに結合すること、第 2 ウェハのスクライブ領域内における第 1 ウェハに開口を形成して第 2 ウェハの導電性構造の表面を露出させること、導電性層が第 2 ウェハの導電性構造と電気的に接続部を形成するように第 1 ウェハおよび第 1 ウェハにおける開口上に導電性層を形成して第 1 ウェハを第 2 ウェハに電気的に結合することを含む。

#### 【0029】

別の実施形態が、キャップウェハをデバイスウェハに電気的に結合する方法を含む。該方法は、結合物質を用いてキャップウェハをデバイスウェハに結合することを含む。デバイスウェハは、基板を含む。該方法は、デバイスウェハのスクライブ領域に結合物質を形成し、且つキャップウェハに開口を形成して、デバイスウェハの導電性構造の表面を露出させることを含む。キャップウェハおよび結合材料を貫通する開口を形成することは、デバイスウェハのスクライブ領域におけるキャップウェハ及び結合物質を切削することを含む。該方法は、導電性層がデバイスウェハの導電性構造と電気的接続を形成するようにキャップウェハおよびキャップウェハにおける開口上に導電性層を形成して、キャップウェハをデバイスウェハに電気的に結合することを含む。

#### 【0030】

別の実施形態が、第 1 ウェハを第 2 ウェハに電気的に結合する方法を含む。該方法は、結合物質を用いて第 1 ウェハを第 2 ウェハに結合すること、第 2 ウェハのスクライブ領域に結合物質を形成し、且つ第 1 ウェハに開口を形成して、第 2 ウェハの導電性構造の表面を露出させること、および導電性層が第 2 ウェハの導電性構造と電気的接続部を形成するように第 1 ウェハ及び第 1 ウェハにおける開口上に導電性層を形成して、第 1 ウェハを第 2 ウェハに電気的に結合することを含む。該方法は、結合ウェハを複数のダイに分離することを含む。分離することは、第 2 ウェハの分離経路の物質を除去し、分離経路は第 1 幅を有する。開口が第 2 幅を有し、導電性層の少なくとも 1 つの部分が、分離されたダイの少なくとも 1 つの側壁に残るように、第 1 および第 2 幅を選択して、第 1 ウェハと第 2 ウェハとの間の電気的結合を提供する。

10

20

30

40

50

## 【 0 0 3 1 】

本発明の特定の実施態様を示して説明してきたが、本明細書の教示に基づいて、本発明およびそのより広範な態様から逸脱することなく、さらなる変更および修正がなされ得ることが当業者には認められるであろう。したがって添付の特許請求の範囲は、本発明の真の精神および範囲の内にあるそのような変更および修正の全てを、その範囲の内に包含するものである。

【 図 1 】

FIG. 1

【 図 2 】

FIG. 2

【 四 3 】

FIG. 3

【 义 4 】

FIG. 4

## 【図5】

FIG. 5

【図6】

FIG. 6

---

フロントページの続き

(72)発明者 カーリン、リサ エイチ .

アメリカ合衆国 85286 アリゾナ州 チャンドラー ダブリュ.メープルウッド ストリー

ト 1651

(72)発明者 マグナス、アラン ジェイ .

アメリカ合衆国 85233 アリゾナ州 ギルバート エヌ.ジャクソン ストリート 131

2

審査官 田中 晃洋

(56)参考文献 特開2004-214469 (JP, A)

特開2005-056999 (JP, A)

特表2007-510295 (JP, A)

米国特許出願公開第2007/0161210 (US, A1)

米国特許出願公開第2006/0001114 (US, A1)

(58)調査した分野(Int.Cl. , DB名)

H01L 23/02

H01L 21/301

B81B 7/02

B81C 3/00