(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-209925

(P2005-209925A)

(43) 公開日 平成17年8月4日(2005.8.4)

(51) Int.Cl.<sup>7</sup>

H01L 21/205

H01L 33/00

F 1

H01L 21/205

H01L 33/00

テーマコード(参考)

5 F O 4 1

5 F O 4 5

審査請求 未請求 請求項の数 16 O L (全 26 頁)

(21) 出願番号

特願2004-15612 (P2004-15612)

(22) 出願日

平成16年1月23日 (2004.1.23)

(71) 出願人 000226057

日亜化学工業株式会社

徳島県阿南市上中町岡491番地100

(74) 代理人 100058479

弁理士 鈴江 武彦

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100075672

弁理士 峰 隆司

(74) 代理人 100109830

弁理士 福原 淑弘

最終頁に続く

(54) 【発明の名称】積層半導体基板

## (57) 【要約】

【課題】高品質の窒化物半導体デバイスを歩留まり良く、低成本で実現することが可能になり、窒化物半導体デバイス形成用に好適な積層半導体基板を提供する。

【解決手段】LEDなどの窒化物半導体デバイスを形成するための積層半導体基板であって、c軸方向に面方位が揃ったAlN11上にそれよりも格子定数が大きく、かつ、c軸方向に面方位が揃ったGaN層12が成長形成され、その上にそれよりも格子定数が小さいn型Al<sub>0.07</sub>Ga<sub>0.93</sub>N層53、多重量子井戸(MQW)構造を有する活性層54、p型Al<sub>0.38</sub>Ga<sub>0.62</sub>N層55、p型Al<sub>0.07</sub>Ga<sub>0.93</sub>N層56が順次形成されている。さらに、p型オーミックコンタクト電極57が形成され、Al<sub>x</sub>S<sub>n</sub>膜58を介して熱伝導性が高いCuW基板59上にボンディングされた後、サファイア基板1、Al<sub>1</sub>N層11、GaN層12が除去されてn型Al<sub>0.07</sub>Ga<sub>0.93</sub>N層53が露出され、CMP研磨され、n電極60が形成されている。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

c 軸方向に面方位が揃った第1の半導体層と、該第1の半導体層上に設けられ、前記第1の半導体層よりも格子定数が大きい第2の半導体層とを具備することを特徴とする積層半導体基板。

**【請求項 2】**

前記第1の半導体層の上面は鏡面であることを特徴とする請求項1記載の積層半導体基板。

**【請求項 3】**

前記第1の半導体層は、XRC(0002)回折において半値幅が90arcsec以下であることを特徴とする請求項1記載の積層半導体基板。 10

**【請求項 4】**

前記第2の半導体層は、a軸方向に圧縮歪みがかかっていることを特徴とする請求項1記載の積層半導体基板。

**【請求項 5】**

前記第2の半導体層は、前記第1の半導体層と比べて、刃状転位および／または螺旋転位が少ないと特徴とする請求項1乃至4のいずれか1つに記載の積層半導体基板。

**【請求項 6】**

前記第1の半導体層は窒化アルミニウムであることを特徴とする請求項1記載の積層半導体基板。 20

**【請求項 7】**

前記第2の半導体層は窒化ガリウムであることを特徴とする請求項1または6記載の積層半導体基板。

**【請求項 8】**

前記第2の半導体層上に形成され、 $\text{Al}_x \text{Ga}_{1-x} \text{N}$ ( $0 < x < 0.1$ )からなる第3の半導体層をさらに具備することを特徴とする請求項7記載の積層半導体基板。

**【請求項 9】**

前記第2の半導体層および／または第3の半導体層は、螺旋転位密度が $3 \times 10^7 / \text{cm}^2$ 以下であることを特徴とする請求項8記載の積層半導体基板。

**【請求項 10】**

c軸方向に面方位が揃った第1の半導体層と、該第1の半導体層上に設けられ、前記第1の半導体層よりも格子定数が大きく、かつ、c軸方向に面方位が揃った第2の半導体層とを具備することを特徴とする積層半導体基板。 30

**【請求項 11】**

前記第2の半導体層は、前記第1の半導体層と比べて、刃状転位および／または螺旋転位が少ないと特徴とする請求項10記載の積層半導体基板。

**【請求項 12】**

前記第1の半導体層は窒化アルミニウムであることを特徴とする請求項10記載の積層半導体基板。

**【請求項 13】**

前記第2の半導体層は窒化ガリウムであることを特徴とする請求項10または12記載の積層半導体基板。

**【請求項 14】**

前記第2の半導体層上に形成され、該第2の半導体層の方向に引っ張り歪みがかかっている第3の半導体層をさらに具備することを特徴とする請求項10乃至13のいずれか1つに記載の積層半導体基板。 40

**【請求項 15】**

前記第3の半導体層は $\text{Al}_x \text{Ga}_{1-x} \text{N}$ ( $0 < x < 0.1$ )からなることを特徴とする請求項14記載の積層半導体基板。

**【請求項 16】**

50

前記第2の半導体層および／または第3の半導体層は、螺旋転位密度が $3 \times 10^7 / \text{cm}^2$ 以下であることを特徴とする請求項14または15記載の積層半導体基板。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、積層半導体基板に係り、特に窒化物半導体デバイスを形成するための積層半導体基板に関するもので、発光ダイオード(LED)、青色、紫色などの短波長レーザダイオード(LD)などの発光デバイス、受光素子、高周波トランジスタ、高耐圧トランジスタなどに使用されるものである。

##### 【背景技術】

##### 【0002】

III-V族化合物半導体のうちで窒化物系半導体を用いた発光デバイスは、青色LEDなどで既に実用化されている。窒化ガリウム(GaN)の半導体層を用いる窒化物半導体発光デバイスは、GaNの成長基板として格子定数や熱膨脹係数が適切な基板がないので、異種基板ではあるが高温安定性に優れ、強度の高いサファイア基板を用い、その上にGaNの単結晶膜を成長させた構造を有する場合が多い。しかし、基板とその上に堆積した単結晶膜との間における物理的な不整合の差が大きい場合に格子定数や結晶構造の違いなどに起因して線状欠陥(転位)が単結晶膜を貫通する欠陥(貫通転位)が発生する。この貫通転位は、非発光性の再結合中心として働くので、貫通転位の密度の影響を受けて発光特性が劣化する。

##### 【0003】

基板とその上に堆積される単結晶膜格子定数の不整合を緩和するために、サファイア基板上に従来よりも低い温度で窒化アルミニウム(AlN)もしくはGaNからなるバッファ層を形成し、その上にGaN単結晶膜を成膜する二段階成膜法が知られている。この方法を使用し、貫通転位の発生を抑制し、且つ、膜の平坦性を維持し、優れた発光特性を有するGaN系半導体発光素子を製造する方法が特許文献1に開示されている。

##### 【0004】

一方、GaN系半導体デバイスの基板の材料は、その上に成膜しようとするGaN系単結晶膜の材料と同種のGaN基板であることが好ましいと考えられている。つまり、GaN基板は、その上にGaN系単結晶の薄膜を成長させる場合に格子定数の不整合の問題が生じないので、GaN系半導体デバイスにとって最適な基板と考えられている。

##### 【0005】

また、GaN基板は、劈開性があるので、ウェハーから素子チップを切り出す工程が容易になり、LDを形成する場合には劈開面を共振器のミラー面として利用できる。しかも、GaN基板は導電性があるので、GaN基板の底面にn電極を設けることにより、p電極(アノード電極)とn電極(カソード電極)を上下に分散して配置することが可能になる。したがって、これらの二つの電極を同一平面上に設けないで済むので、電極配置を単純化し、チップ面積を節減することができる。また、GaN基板は熱伝導率が高いので、放熱性が良い。

##### 【0006】

このようなGaN基板は、GaN系半導体デバイスの基板材料として適當と考えられる。しかし、転位密度によって特性が大きく左右される高出力LEDや紫外領域で発光するLED、または高密度の電流が流れるLDにおいては、更なる低転位密度化が要求される。

##### 【0007】

このような問題に鑑み、GaN基板の製造に際して結晶欠陥を制御し、低い転位密度を実現し得る製造方法が特許文献2に開示されている。この製造方法は、単結晶GaNの気相成長表面が、平面状態でなく、三次元的なファセット構造を持つようにし、ファセット構造を持ったまま、ファセット構造を埋め込まないで成長させることで転位を低減し、その後、機械的な加工により平面性を与え、さらにその表面を研磨することにより平坦な表

10

20

30

40

50

面を得ることを特徴とするものである。また、特許文献2には、GaN基板上に単結晶GaNを複数枚分以上の厚さに気相成長させた後、厚さ方向にスライス切断する製造方法も示されている。さらに、特許文献2には、GaN基板の転位密度を低減するための結晶成長法として、ストライプマスク等を使用してGaNのラテラルオーバーグロースを行う方法が紹介されている。

#### 【0008】

なお、特許文献3には、ラテラルオーバーグロースを用いて形成したGaN基板の評価に際して基板表面を顕微鏡で詳細に観察すると、転位集中領域（高転位密度領域）に対応して約 $10\text{ }\mu\text{m} \sim 40\text{ }\mu\text{m}$ の幅の窪みが数百 $\mu\text{m}$ オーダーのピッチで存在していることが開示されている。

10

#### 【0009】

しかし、GaN基板の上面に転位集中領域に対応して窪み（凹部）が存在する場合、GaN基板上に所望の素子を形成するためにGaN系結晶膜を成膜しようとすると、通常の単結晶GaNの気相成長の反応条件では、高転位密度領域の溝がそのまま上方（膜の成長方向）に引き継がれるので溝上にGaN系結晶膜を成長させることができず、溝に対応して深い凹部が発生してしまい、上面の平坦性が十分には得られない。このような状態の基板は、発光領域の大面積が要求されるLEDには適さない。さらに、この窪みの存在は、結晶成長時において平坦部へ悪影響を及ぼすことにもなる。例え加工等の工夫により平坦化されたGaN基板であっても、c軸方向に配向性は揃っていない。これは、面内で結晶情報の異なる部分が存在することを意味する。そのため、各種成長条件の変更や、不純物ドープおよび混晶化を行う際に結晶成長の不均一化を引き起こすことになり、窪みの再発生を引き起こしてしまう。

20

#### 【0010】

また、このような深い凹部が発生すると、後の工程に悪影響を及ぼし、素子の特性に悪影響を及ぼすことになる。例えばフォトリソグラフィ工程に際して、レジスト膜厚の分布に悪影響を及ぼし、反応性エッチングによるレジストのパターニング精度が低下する。特に、LD製造に際して、リッジ部のパターニング形成の精度低下が問題となり、また、劈開工程で劈開面のずれが生じたり、量子井戸発光波長の周期的变化が生じたりする。

30

#### 【0011】

仮に転位集中領域に窪みがなく、平坦性が維持され、LEDなどの素子を形成できたとしても、発光領域の大面積が要求されるLEDとしては、チップ面内に高転位密度部分が存在することは素子の特性を悪化させることになる。

#### 【0012】

また、GaN系半導体デバイスは、紫外領域の発光デバイスとしても重要な役割を持っている。それには、発光層としてIn組成の少ないAlInGaN、AlGaNおよびGaNが用いられ、それらに合わせてバンドオフセットや吸収を考慮に入れた積層半導体構造となる。前記積層半導体にはAlGaNを含んだ構成とされることが多い。しかし、AlGaNは混晶系であるので、結晶品質が悪いのが現状である。また、クラックが発生し易く、Al組成比および膜厚にも制限がある。

40

#### 【0013】

窒化物半導体基板として考えられるAlNについては、原料種のAlの結合エネルギーが大きいので、高温成長が要求され、成長の制御が困難とされている。そのため、低転位密度の高品質のAlNが得られていない。

【特許文献1】特開2000-357820号公報

【特許文献2】特開2001-102307号公報

【特許文献3】特開2003-133650号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0014】

サファイア基板上に従来よりも低い温度でAlNもしくはGaNからなるバッファ層を

50

形成し、その上にGaN単結晶膜を成膜する二段階成膜法では、結晶成長初期に発生する3次元核の配向性が低いので、核合体時に歪みが生じて結晶粒界がモザイク状に発生する。結果として得られたGaN層の結晶粒界の境界に貫通転位が発生し、c軸に対する回転(ツイスト)や傾斜(チルト)に対応して刃状転位や螺旋転位が存在するようになる。

#### 【0015】

上記した貫通転位を低減するためには、結晶粒界の密度を低下させる、つまり、3次元核の密度(核密度)を低下させることにより達成でき、これにより全体の転位密度を低下させることができになる。しかし、核密度を低下させることは、核合体を遅らせ、核合体時における核を大きくさせることになる。一方、核合体時には、相互作用により圧縮応力が発生し、その応力はチルトを抑制し、ツイストを助長させる働きがあると考えられる。このような効果は、核合体時における核の大きさが小さいほど顕著であると考えられる。10

したがって、核密度を低下させ、核合体時における核を大きくさせると、核合体時にチルトが大きく残る。これによって、全体の転位密度が低下したにも拘らず、大きなバーガースペクトルを持つ螺旋転位が残留し、結果として、それに起因する成長ピットの発生や、GaN層上に形成された発光素子の特性を悪化させる原因となっている。この影響は、刃状転位よりも螺旋転位および/または混合転位の方が大きい。

#### 【0016】

上述したように低温で堆積された従来のAlN、もしくはGaNからなるバッファ層を形成し、その上にGaN層を成長させた場合には、螺旋転位が残留し、それに起因する成長ピットの発生や、GaN層上に形成された発光素子の特性を悪化させるという問題があ20った。

#### 【0017】

また、紫外領域の発光デバイスとしてGaNより格子定数が小さいAlGaN等をGaN上に積層させる場合において、クラックの発生等による緩和が起こる臨界膜厚があり、そのためAl組成比および膜厚に制限があった。

#### 【0018】

本発明は、上記の問題点に鑑みてなされたもので、c軸方向に面方位が揃った半導体基板上に、該半導体基板よりも格子定数の大きな半導体層を成長させ、かつ、前記半導体層を高品質化させるものである。これによって、高品質の窒化物半導体デバイスを歩留まり良く、低コストで実現することが可能になり、窒化物半導体デバイスを形成するために使用して好適な積層半導体基板を提供することを目的とする。また、前記半導体基板よりも格子定数の小さい結晶で構成される発光素子を提供することも目的とする。30

#### 【課題を解決するための手段】

#### 【0019】

本発明の積層半導体基板の第1の態様は、c軸方向に面方位が揃った第1の半導体層と、該第1の半導体層上に形成され、前記第1の半導体層よりも格子定数が大きい第2の半導体層とを具備することを特徴とする。また、前記第2の半導体層上に形成され、前記第2の半導体層よりも格子定数が小さい第3の半導体層を具備することを特徴とする。

#### 【0020】

本発明の積層半導体基板の第2の態様は、c軸方向に面方位が揃った第1の半導体層と、該第1の半導体層上に形成され、前記第1の半導体層よりも格子定数が大きく、かつ、c軸方向に面方位が揃った第2の半導体層とを具備することを特徴とする。また、前記第2の半導体層上に形成され、前記第2の半導体層よりも格子定数が小さく、かつ、c軸方向に面方位が揃った第3の半導体層を具備することを特徴とする。40

#### 【発明の効果】

#### 【0021】

本発明の積層半導体基板によれば、高品質の窒化物半導体デバイスを歩留まり良く、低コストで実現することが可能になり、窒化物半導体デバイスを形成するために使用して好適である。また、本発明の積層半導体基板を用いることにより、紫外領域から可視光までの広範囲で高出力を可能としたLEDまたはLDを形成することができる。50

## 【発明を実施するための最良の形態】

## 【0022】

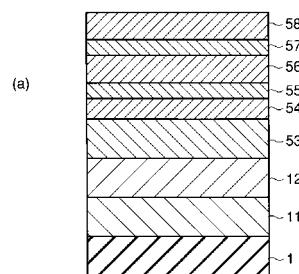

<第1の実施形態>（積層半導体基板）

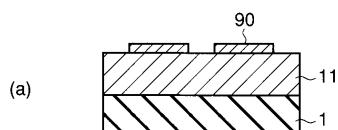

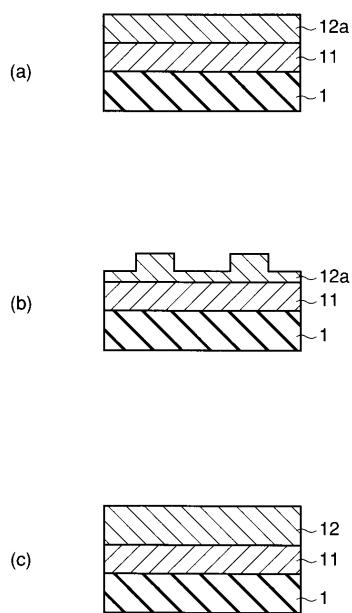

図1は、第1の実施形態に係る積層半導体基板の断面構造を模式的に示す。図1において、例えばC面を正面とするサファイア基板1上にc軸方向に面方位が揃った第1の半導体層11が成長形成され、この第1の半導体層11上にそれよりも格子定数が大きい第2の半導体層12が成長形成されている。これらは、窒化物半導体を積層するための積層半導体基板10を構成している。

## 【0023】

（第1の半導体層）第1の半導体層11は、III-V族化合物半導体であって、好ましくは窒化物半導体である。本発明における窒化物半導体は、一般式 $In_xAl_yGa_{1-x-y}N$ （0 < x < 1, 0 < y < 1, 0 < x+y < 1）で示すことができ、本例ではAl含有窒化物半導体であって、AlN単結晶、特にc軸方向に面方位が揃った平滑平坦な上面（鏡面）を有するAlN層である。以下、符号11を、第1の半導体層、AlN層で共通に使用する。

## 【0024】

（第2の半導体層）第2の半導体層12は、III-V族化合物半導体であって、前記第1の半導体層11よりも格子定数が大きい単結晶層を成長させる。前記III-V族化合物半導体は、好ましくは窒化物半導体である。これにより、第1の半導体層11と第2の半導体層12の界面には、格子不整合が大きいので格子整合した2次元成長が起こらず、成長初期から格子緩和した3次元成長が起こる。しかし、歪が完全には緩和されないので、第2の半導体層12には微視的にa軸方向に圧縮歪みがかかるようになる。第2の半導体層12の一具体例として、AlN層よりも格子定数が大きいGaN層が望ましい。以下、符号12を、第2の半導体層、GaN層で共通に使用する。

## 【0025】

因みに、六方晶系のAlNの格子定数（結晶軸aの長さ）は3.112 オングストローム、GaNの格子定数は3.189 オングストロームであり、両者の違いは約2.5 %である。

## 【0026】

上記したように第1の実施形態によれば、c軸方向に面方位が揃ったAlN層11上にGaN層12を成長させる際、AlNとGaNとの格子不整合が大きいので格子整合した2次元成長が起こらず、成長初期から格子緩和した3次元成長が起こる。その時、成長核はAlN層11のc軸配向性を帶びているので、その後の核合体時においてもチルトを抑制し、さらに核密度を低下させて低転位化を行うことが可能になる。結果として、GaN層12の転位密度を低下させると同時に、螺旋転位の発生を抑制することが可能になり、GaN層12は、AlN層11と比べて、刃状転位および/または螺旋転位が少なくなるように形成される。この場合、刃状転位が2桁以上減少しており、同時に螺旋転位も減少しており、従来は螺旋転位の減少が困難であったことを勘案すると、その効果は大きい。図1中には、GaN層12に存在する転位（刃状転位、螺旋転位および混合転位）Dを概略的に示している。

## 【0027】

前記したようにAlN層11のc軸配向性を利用してGaN層12での初期成長核の配向性を向上させるため、AlN層11のXRC（0002）回折による半値幅（Full Width at Half Maximum: FWHM）は、90秒角(arcsec)以下であることが好ましい。これは、一般的にサファイア上に低温バッファ層を介して成長させたGaN層が180秒以上の半値角であるのに対して約半分以下となっている。また、AlN層11は60秒角以下の高いc軸配向性のものが得られており、さらなる高品質化に適している。このAlN層11の作製時において、高いc軸配向性と表面平坦性を得るために数%以下のGaNを混晶化させることも効果がある。

## 【0028】

なお、前記したようにc軸方向に面方位が揃ったAlN層11上にGaN層12を成長

10

20

30

40

50

させる際、成長初期の結晶核の密度を低く制御するようにプロセス上の工夫を行うことによって、核合体を遅らせたとしても、該核のc軸配向性が良好であるから合体時のチルトによる大きな歪みの螺旋転位や混合転位が発生しないので、ピット等のない平坦面を形成することが可能である。

## 【0029】

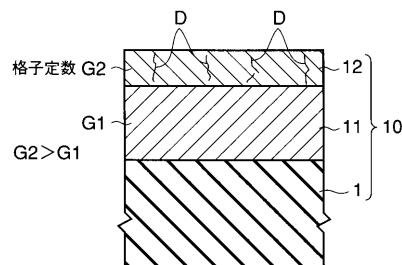

<第2の実施形態>(積層半導体基板)

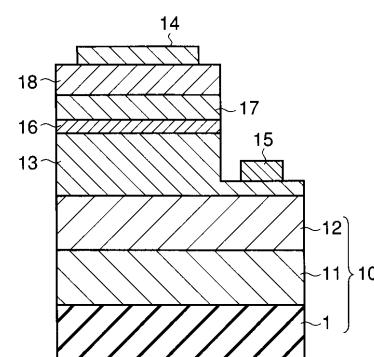

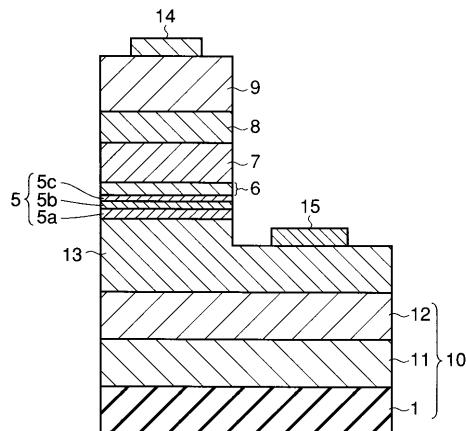

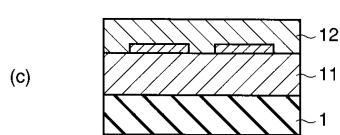

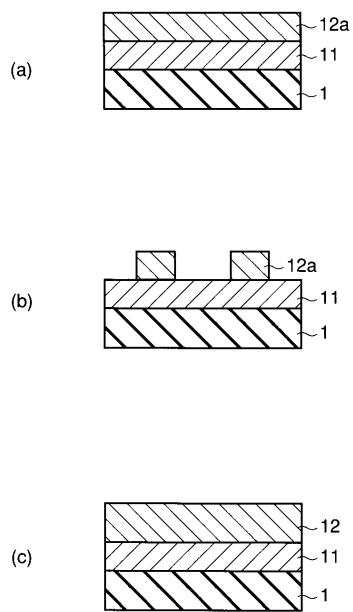

図2は、第2の実施形態に係る積層半導体基板を模式的に示す断面図である。図2に示す積層半導体基板は、第1の実施形態に係る積層半導体基板10を使用して窒化物半導体デバイス、例えばLED、受光素子などを実現する際、さらに、GaN層12上に第3の半導体層13が形成されたものである。

10

## 【0030】

第3の半導体層13は、第2の半導体層12上に格子整合が可能となる程度に格子定数が近いものである。第2の半導体層12は、第1の半導体層11に対して格子緩和と同時に3次元成長が起こり、その際に転位の伝搬を抑止している。第3の半導体層13は、第2の半導体層12上に格子整合しているので、第2の半導体層12の転位を引き継ぐことになる。そのため、第2の半導体層12が低転位であれば、第3の半導体層13も低転位になる。

## 【0031】

ここで、第2の半導体層12は、螺旋転位密度が $3 \times 10^7 / \text{cm}^2$ 以下、より好ましくは $3 \times 10^6 / \text{cm}^2$ 以下になるように形成されている。そして、第3の半導体層13の螺旋転位密度は、第2の半導体層12と同じ程度になるように形成されている。また、第2の半導体層12がc軸方向に面方位が揃った鏡面を有する場合は、その上に第2の半導体層12よりも格子定数が小さい第3の半導体層13を成長させても、クラックやピットおよび転位の発生が抑制される。

20

## 【0032】

(第3の半導体層) 第3の半導体層13として、第2の半導体層12よりも格子定数が小さい単結晶層を成長させた場合、第2の半導体層12と第3の半導体層13の界面に格子歪が発生し、第3の半導体層13には引っ張り歪みがかかるようになる。この場合、第2の半導体層12は第1の半導体層11から圧縮応力をかけられているので、第3の半導体層13は第2の半導体層12からの引っ張り歪みが小さくなる。したがって、第3の半導体層13の引っ張り歪みが緩和され、クラックやピットおよび転位の発生が抑制される。ここで、上記したような第1の半導体層11、第2の半導体層12、第3の半導体層13の各格子定数G1、G2、G3の大小関係を整理すると、G2 > G3 > G1である。

30

## 【0033】

第3の半導体層13の一具体例として、GaN層12と同種のGaN系材料であって、GaN単結晶よりも格子定数が小さいものとしては、Al<sub>x</sub>Ga<sub>1-x</sub>N(0 < x < 0.1)層が挙げられる。ここで、Alの混晶比は0.1以下であり、x>0.01、望ましくは、x=0.03~0.08に設定する。因みに、Al<sub>x</sub>Ga<sub>1-x</sub>N(0 < x < 0.1)層13の格子定数(結晶軸の長さ)は、x=0.05の場合に3.185 オングストローム、GaNの格子定数は3.189 オングストロームであり、両者の違いは0.125%程度である。これは、370 nm以下の紫外発光デバイスを形成する場合に主に用いられる。また、GaN単結晶と格子定数が同じものとしては、可視領域の発光デバイスに用いられる構造を示し、GaN/InGaNで構成されるものであり、これは全体として格子定数が大きくなる傾向ではあるが、この場合の歪みは圧縮系であり、クラック等の発生がないため大きな問題となりにくいので、同じ格子定数として扱う。

40

## 【0034】

なお、前記AlN層11上にGaN層12を成長させる際、ELO(Epitaxial Lateral Overgrown)成長法を組み合わせるようにしてもよい。この場合、ELO成長法として例えば図11乃至図15に模式的に示すような5つのバリエーション(I)~(V)が考えられる。

50

## 【0035】

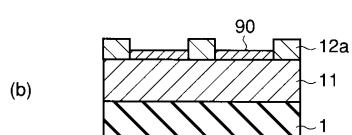

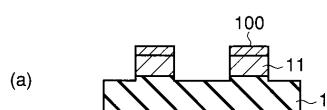

ELO成長法(I)では、まず、図11(a)に示すようにサファイア基板1上のc軸配向性が良いAlN層11の上面に開口部を有するマスク(例えばSiO<sub>2</sub>膜からなる)90を形成する。この場合、マスク90の開口幅は約3μm~10μm、開口部間のマスク幅は約5μm~30μmである。次に、図11(b)に示すように、AlN層11からマスク開口部を通してGaN層12aをc軸方向に成長させると、やがて、図11(c)に示すように、GaN層がc軸方向に成長しつつ、横方向(マスク上)にも成長して横方向に隣り合うGaN層同士が合体する。結果として、上面が平坦なGaN層12が形成される。この場合、開口部上に成長したGaN層はAlN層11のc軸配向性を引き継いでc軸配向性が良いので転位密度が低く、マスク上のGaN層もc軸配向性が良く、合体時の歪み(チルト)が抑制され、さらに転位密度が低く形成される。

## 【0036】

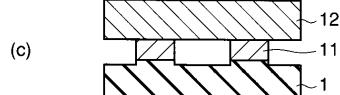

ELO成長法(II)では、まず、図12(a)に示すようにサファイア基板1上のc軸配向性が良いAlN層11の上面に開口部を有するエッチングマスク100を形成する。この場合、エッチングマスク100の開口幅は約3μm~30μm、開口部間のマスク幅は約3μm~15μmである。そして、図12(b)に示すように、異方性エッチングによりAlN層11を選択的にエッチングしてAlN層11に溝部を形成する。次に、エッチングマスク100を除去した後、AlN層11上にGaN層12aを成長させると、やがて、図12(c)に示すように、GaN層がc軸方向に成長しつつ、横方向(溝部の上方)にも成長して横方向に隣り合うGaN層同士が合体する。結果として、上面が平坦でc軸配向性が良いGaN層12が形成される。なお、AlN層11の溝部内は空洞状態にとってもよい。

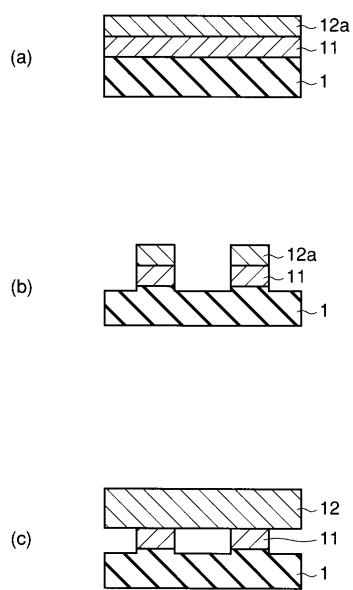

## 【0037】

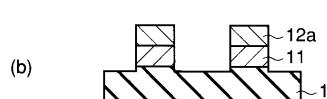

ELO成長法(III)では、まず、図13(a)に示すようにサファイア基板1上のc軸配向性が良いAlN層11の上にGaN層12aを形成する。そして、GaN層12aの上面に開口部を有するエッチングマスク(図示せず)を形成する。次に、図13(b)に示すように、異方性エッチングによりGaN層12aおよびAlN層11を選択的にエッチングしてGaN層12aおよびAlN層11に溝部を形成する。そして、エッチングマスクを除去した後、GaN層12aを再成長させると、やがて、図13(c)に示すように、GaN層がc軸方向に成長しつつ、横方向(溝部の上方)にも成長して横方向に隣り合うGaN層同士が合体する。結果として、上面が平坦でc軸配向性が良いGaN層12が形成される。なお、AlN層11の溝部内は空洞状態にとってもよい。

## 【0038】

ELO成長法(IV)では、まず、図14(a)に示すようにサファイア基板1上のc軸配向性が良いAlN層11の上にGaN層12aを形成し、GaN層12aの上面に開口部を有するエッチングマスク(図示せず)を形成する。そして、図14(b)に示すように、異方性エッチングによりGaN層12aを途中の深さまで選択的にエッチングしてGaN層12aに溝部を形成する。そして、エッチングマスクを除去した後、GaN層12aを再成長させると、やがて、図14(c)に示すように、GaN層がc軸方向に成長しつつ、横方向にも成長して横方向に隣り合うGaN層同士が合体する。結果として、上面が平坦でc軸配向性が良いGaN層12が形成される。

## 【0039】

ELO成長法(V)では、まず、図15(a)に示すようにサファイア基板1上のc軸配向性が良いAlN層11の上にGaN層12aを形成し、GaN層12aの上面に開口部を有するエッチングマスク(図示せず)を形成する。そして、図15(b)に示すように、異方性エッチングによりGaN層12aを底面まで選択的にエッチングしてGaN層12aに溝部を形成する。そして、エッチングマスクを除去した後、GaN層12aを再成長させると、やがて、図15(c)に示すように、GaN層がc軸方向に成長しつつ、横方向にも成長して横方向に隣り合うGaN層同士が合体する。結果として、上面が平坦でc軸配向性が良いGaN層12が形成される。

10

20

30

40

50

## 【0040】

(第2の半導体層の不純物濃度) 例えは第2の半導体層12をnコンタクト層として用いる場合がある。その場合には、第2の半導体層の不純物濃度を $1 \times 10^{18} / \text{cm}^3$ 以上、 $5 \times 10^{18} / \text{cm}^3$ 以下にする。上記n型不純物としては、Si、Ge、Se、S、O等の周期律表第IVB族、第VIB族元素を選択し、好ましくはSi、O、Ge、Sをn型不純物とする。

## 【0041】

(第3の半導体層の機能) GaN層12上に形成したSi<sub>x</sub>Al<sub>1-x</sub>GaN ( $0 < x < 0.1$ )層13は、クラッド層およびnコンタクト層として用いることが可能になる。この場合、第3の半導体層13の不純物濃度は $1 \times 10^{18} / \text{cm}^3$ 以上、 $1 \times 10^{20} / \text{cm}^3$ 以下にする。この上限の値は、第2の半導体層12の不純物濃度の上限の値よりも大きい。これは、AlGaNの方がGaNよりも不純物濃度に対する許容量が大きいためであり、デバイスの低抵抗化に有効である。

## 【0042】

ここで、この半導体基板を支持基板に貼り合わせ、その後、サファイア基板および一部の半導体層を除去し、素子を形成する方法がある。その場合、GaN層12はn型不純物を含有しており、その裏面にn電極を形成する際に良好なオーミックコンタクトが得られるnコンタクト層として用いることができる。サファイア基板1およびAlN層11を除去し、GaN層12の裏面にn電極を形成すると、発光素子全体の厚さを薄くし、発光による発熱を放散し易くなる。ここで、AlN層11等を除去するには、研磨、研削、レーザ照射等の方法を用いる。また、発光素子の活性層の発光波長を400nm以下の波長域とする場合は、AlGaN層をnコンタクト層として用い、GaN層12まで除去することが好ましい。

## 【0043】

上記した第2の実施形態によれば、第1の実施形態で述べたような効果を有する積層半導体基板10の第2の半導体層12上に第3の半導体層13が格子整合されているので、第2の半導体層12が低転位であれば、第3の半導体層13も低転位になる。

## 【0044】

したがって、第2の実施形態の積層半導体基板上に結晶性の良い窒化物半導体層を積層して窒化物半導体デバイスを形成する際、デバイスの製造工程を安定化し、所望のデバイスを歩留まり良く、低コストで実現することができる。

## 【0045】

なお、前記第1の実施例形態および第2の実施例形態において、窒化物半導体を成長させるための異種基板は、窒化物半導体と異なる材料よりなる基板であれば特に限定されず、例えは、C面、R面、およびA面のいずれかを正面とするサファイアやスピネル(MgAl<sub>2</sub>O<sub>4</sub>)のような絶縁性基板、またはSiC(6H、4H、3Cを含む)、ZnS、ZnO、Si、GaAs、ダイヤモンド、および窒化物半導体と格子結合するニオブ酸化リチウム、ガリウム酸ネオジウム等の酸化物基板が挙げられる。上記異種基板の中で好ましいのはサファイアであり、さらに好ましいのはC面を正面とするサファイア基板である。サファイアのC面はオフアングルしていてもよく、オフアングル角は、0.01°～0.5°、好ましくは0.05°～0.2°の範囲とする。

## 【0046】

また、異種基板上にバッファ層を介して窒化物半導体を成長させてもよい。このバッファ層としては、一般式Al<sub>a</sub>Ga<sub>1-a</sub>N ( $0 < a < 0.8$ )で表される窒化物半導体を用いる。バッファ層の膜厚は、好ましくは0.002～0.5μmである。バッファ層の成長温度は、好ましくは200～900である。これにより、窒化物半導体層上の転位やピットを低減させることができる。

## 【0047】

また、前記第1の半導体層としては、窒化物半導体基板を用いることもできる。この場合、窒化物半導体基板の厚膜としてはデバイス加工ができる程度の厚膜(数十μm以上)

10

20

20

30

40

50

が必要である。

【0048】

<第3の実施形態>（積層半導体基板）

第3の実施形態は、前記異種基板上に第1の半導体層11、その上に第2の半導体層12を成長させた後、前記したようなELO成長を行わせるためのマスク90を形成し、第3の半導体層13を横方向に成長させる。このようにマスク上に成長した第3の半導体層13も、c軸配向性が良く、転位密度が低い。

【0049】

<第1の適用例>（窒化物半導体デバイス）

本発明に係る積層半導体基板を使用して、例えばLED、受光素子などの窒化物半導体デバイスを実現する際、積層半導体基板上に、少なくともn型窒化物半導体層およびp型窒化物半導体層を含む半導体層を結晶性良く形成することによって、高品質の窒化物半導体デバイスを歩留まり良く得ることができる。

【0050】

<第2の適用例>（窒化物LD）

本発明に係る積層半導体基板を使用して窒化物LDを実現する際、積層半導体基板上に、光導波領域を形成する光ガイド層として用いられる少なくともn型窒化物半導体層および/またはp型窒化物半導体層を含む半導体層を結晶性良く形成することによって、高品質の窒化物LDを歩留まり良く得ることができる。

【0051】

[実施例]

以下、本発明の実施例を数例示すが、本発明はこれらの実施例に限定されるものではない。

【0052】

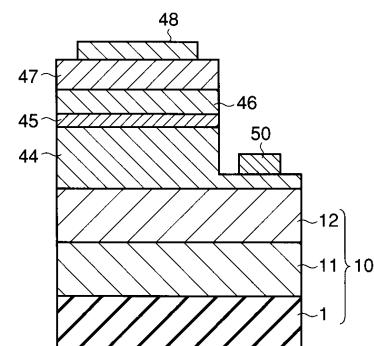

[実施例1] 図3は、本発明の積層半導体基板を使用した窒化物半導体デバイスの一例としてLEDの構造を模式的に示す断面図である。このLEDにおいては、C面を正面とするサファイア基板1上にc軸方向に面方位が揃った窒化物半導体基板として、特にc軸方向に面方位が揃ったAlN層11が形成されており、その上面は鏡面になっている。AlN層11上には、それよりも格子定数が大きいGaN層12が成長されている。これらのサファイア基板1、AlN層11およびGaN層12からなる積層半導体基板10の上に窒化物半導体層が積層されてLEDが構成される。

【0053】

次に、AlN層11、GaN層12、およびその上の窒化物半導体層を例え同一装置内で連続的に成長させる場合の工程について説明する。

【0054】

(第1の半導体層)

MOCVD装置の反応容器内にサファイア基板1をセットし、1000以上、好ましくは1200まで昇温させる。昇温中は、キャリアガスとして窒素(N<sub>2</sub>)および/または水素(H<sub>2</sub>)を流す。次に、1100以上で、好ましくは1200に到達してから、少なくともアンモニア(NH<sub>3</sub>)ガスと原料ガスを供給する。この際、NH<sub>3</sub>の供給量は、0.0005mol~0.01mol、好ましくは0.0008mol~0.008molである。また、原料ガス、例えばTMA(トリメチルアルミニウム)の供給量は、0.1μmol~10μmol、好ましくは0.5μmol~5μmolである。ここで、V/III比は50~100000、圧力は50~100torrである。上記条件で3時間以上の成長により、約0.2~3μmの厚みのAlN膜が成長する。

【0055】

なお、上記AlN膜はGaを含有すると、容易に表面を鏡面とすることができます。具体的には、AlN膜の成長中にTMG(トリメチルガリウム)を0.1μmol~10μmol程度供給すると、AlGaNが得られる。AlN膜にGaを好ましくは0.1~2%含有させる。

10

20

30

40

50

## 【0056】

なお、前記  $\text{NH}_3$  ガスの供給を開始するタイミングは、原料ガスと同時、または、少し遅らせる方が好ましい。また、原料ガスと  $\text{NH}_3$  ガスを交互に供給してもよい。

## 【0057】

## (第2の半導体層)

第1のステップとして、 $\text{NH}_3$  の供給量を  $0.0005 \text{ mol} \sim 0.05 \text{ mol}$ 、TMG の供給量を  $30 \mu\text{mol} \sim 100 \mu\text{mol}$  とする。ここで、V/III 比は  $5 \sim 1650$ 、圧力は  $700 \sim 850 \text{ torr}$  である。上記条件で5分間以上の成長により、 $0.05 \sim 0.3 \mu\text{m}$  の厚みの GaN の3次元成長核が成長する。

## 【0058】

第2のステップとして、 $\text{NH}_3$  の供給量を  $0.005 \text{ mol} \sim 0.3 \text{ mol}$ 、TMG の供給量を  $20 \mu\text{mol} \sim 200 \mu\text{mol}$  とする。ここで、V/III 比は  $2.5 \sim 1500$ 、圧力は  $700 \sim 850 \text{ torr}$  である。上記条件で0.5時間以上の成長により、 $1 \mu\text{m} \sim 10 \mu\text{m}$  の厚みの低転位の GaN 膜が成長する。

## 【0059】

なお、第1のステップと第2のステップにおける温度や圧力、またはV/III 比を個々に変更し、3次元核成長および平坦化に適した条件に合わせることが好ましい。例えば、結晶成長初期における3次元成長核の密度が低くなる条件にすることにより、核合体時に発生する転位密度を低く抑えることが可能になり、また、核のc軸配向性が高いため合体時のチルトも抑制される。換言すると、GaN層12は、AlN層11のc軸方向の情報は受け継ぐが、a軸方向は緩和した結晶状態を持つようになり、AlN層11と比べて刃状転位および/または螺旋転位が少なくなるように形成される。

## 【0060】

## (窒化物半導体層)

まず、GaN層12上にn型コンタクト層44を成長させる。このn型コンタクト層44としては、後で形成する活性層45のバンドギャップエネルギーより大きくなる組成であり、 $\text{Al}_j \text{Ga}_{1-j} \text{N}$  ( $0 < j < 0.3$ ) が好ましい。n型コンタクト層44の膜厚は特に限定されるものではないが、好ましくは  $1 \mu\text{m}$  以上、より好ましくは  $3 \mu\text{m}$  以上である。また、n型コンタクト層44の不純物濃度は特に限定されるものではないが、好ましくは  $1 \times 10^{18} \sim 1 \times 10^{20} / \text{cm}^3$ 、より好ましくは  $5 \times 10^{18} \sim 5 \times 10^{19} / \text{cm}^3$  である。また、n型不純物濃度に傾斜をつけてよい。また、Alの組成に傾斜をつけることにより、キャリアを閉じ込めるためのクラッド層としても機能する。

## 【0061】

次に、発光層(活性層)45を形成する。この活性層45は、少なくとも  $\text{Al}_a \text{In}_b \text{Ga}_{1-a-b} \text{N}$  ( $0 < a < 1, 0 < b < 1, a + b < 1$ ) からなる井戸層と、 $\text{Al}_c \text{In}_d \text{Ga}_{1-c-d} \text{N}$  ( $0 < c < 1, 0 < d < 1, c + d < 1$ ) からなる障壁層とを含む量子井戸構造を有する。

## 【0062】

井戸層の膜厚は、好ましくは  $1 \text{ nm}$  以上  $30 \text{ nm}$  以下、より好ましくは  $2 \text{ nm}$  以上  $20 \text{ nm}$  以下、さらに好ましくは  $3.5 \text{ nm}$  以上  $20 \text{ nm}$  以下である。また、井戸層の数は特に限定されるものではないが、少数キャリア拡散長を考慮して活性層全体の厚みを制御することが好ましい。

## 【0063】

また、障壁層は、井戸層の場合と同様に、好ましくはp型不純物またはn型不純物がドープされているか、またはアンドープであり、より好ましくはn型不純物がドープされているか、またはアンドープである。例えば障壁層中にn型不純物をドープする場合、その濃度は少なくとも  $5 \times 10^{16} / \text{cm}^3$  以上が必要である。例えば、LEDでは、 $5 \times 10^{16} / \text{cm}^3$  以上、 $1 \times 10^{20} / \text{cm}^3$  以下が好ましい。

## 【0064】

実施例1のLEDにおいては、障壁層は、井戸層よりもバンドギャップエネルギーが大

10

20

30

40

50

きな窒化物半導体を用いる必要がある。特に、井戸層の発光波長が380nm以下の領域では、障壁層として、一般式 $\text{Al}_c\text{In}_d\text{Ga}_{1-c-d}\text{N}$ ( $0 < c \leq 1$ 、 $0 \leq d \leq 1$ 、 $c + d < 1$ )で表わされるAlInGaNの4元混晶、またはAlGaNの3元混晶を用いることが好ましい。

#### 【0065】

次に、活性層45上にp型窒化物半導体層を複数層で形成する。まず、p型クラッド層46として、活性層45のバンドギャップエネルギーより大きくなる組成であり、キャリアを活性層45へ閉じ込めることができれば特に限定されないが、 $\text{Al}_k\text{Ga}_{1-k}\text{N}$ ( $0 < k < 1$ )が用いられ、特に $\text{Al}_k\text{Ga}_{1-k}\text{N}$ ( $0 < k < 0.4$ )が好ましい。p型クラッド層46の膜厚は、特に限定されるものではないが、好ましくは0.005~0.3μm、より好ましくは0.01~0.2μmである。また、p型クラッド層46のp型不純物濃度は、好ましくは $1 \times 10^{18} \sim 1 \times 10^{21} / \text{cm}^3$ 、より好ましくは $1 \times 10^{19} \sim 5 \times 10^{20} / \text{cm}^3$ である。p型不純物濃度が上記の範囲にあると、結晶性を低下させることなくバルク抵抗を低下させることができる。p型クラッド層46は、単一層でも多層膜層(超格子構造)でもよい。多層膜層の場合、上記の $\text{Al}_k\text{Ga}_{1-k}\text{N}$ ( $0 < k < 1$ )と、それよりバンドギャップエネルギーより小さい窒化物半導体層とからなる多層膜層であればよい。例えばバンドギャップエネルギーが小さい窒化物半導体層としては、n型クラッド層44の場合と同様に、 $\text{In}_l\text{Ga}_{1-l}\text{N}$ ( $0 < l < 1$ )、 $\text{Al}_m\text{Ga}_{1-m}\text{N}$ ( $0 < m < 1$ 、 $m > l$ )が挙げられる。多層膜層を形成する各層の膜厚は、超格子構造の場合は、一層の膜厚が好ましくは10nm以下、より好ましくは7nm以下、さらに好ましくは1~4nmとすることができる。また、p型クラッド層46がバンドギャップエネルギーの大きい層とバンドギャップエネルギーの小さい層とからなる多層膜層である場合は、バンドギャップエネルギーの大きい層および小さい層の一方にp型不純物をドープしてもよい。また、バンドギャップエネルギーの大きい層および小さい層の両方に不純物をドープする場合は、ドープ量は同一でも異なってもよい。

#### 【0066】

p型クラッド層46上にp型コンタクト層47を形成する。p型コンタクト層47は、 $\text{Al}_f\text{Ga}_{1-f}\text{N}$ ( $0 < f < 1$ )が用いられ、特に $\text{Al}_f\text{Ga}_{1-f}\text{N}$ ( $0 < f < 0.3$ )で構成することにより、後で形成されるオーミック電極であるp型電極48と良好なオーミックコンタクトが可能となる。p型コンタクト層47のp型不純物濃度は $1 \times 10^{18} / \text{cm}^3$ 以上が好ましい。

#### 【0067】

この後、p型コンタクト層47、p型クラッド層46、活性層45およびn型コンタクト層44の一部をエッティング除去することによってn型コンタクト層44の一部を露出させ、その露出面にn電極50を形成し、LEDを得る。

#### 【0068】

なお、窒化物半導体層の形成は、有機金属化学気相成長(MOCVD)法に限らず、ハライド気相エピタキシャル成長(HVPE)法、分子線エピタキシー(MBE)法等を用いて成長させることができる。

#### 【0069】

[実施例2]実施例2は、Daisuke Morita et.al, "High Output Power 365nm ULTRAVIOLET Light Emitting Diode of Gan-Free Structure" jpn.j.Appl.Phys.Vol.41(2002)pp.L1434-L1436に開示されている構造を参考にし、本発明の積層半導体基板を使用して製造したLEDである。

#### 【0070】

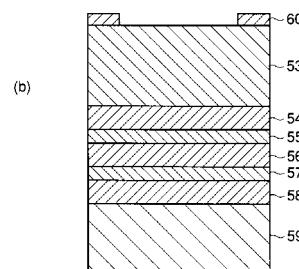

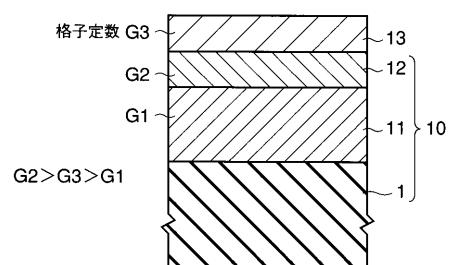

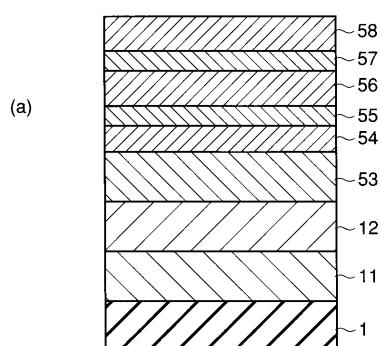

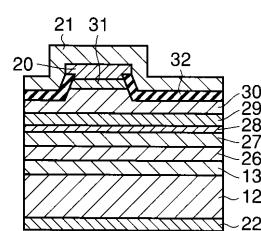

図4(a)、(b)は、実施例2のLEDの製造工程を模式的に示している。まず、図4(a)に示すように、実施例1と同様の工程によりサファイア基板1上にAlN層11、GaN層12を成長させた後、以下の各層を順次成長させる。まず、n型 $\text{Al}_{0.07}\text{Ga}_{0.93}\text{N}$ 層53を2.5μmの厚さで形成する。ここで、n型不純物はSiとする。次に、井戸層と障壁層の5ペアからなる多重量子井戸(MQW:Multi-Quantum-Well)構造を有す

10

20

30

40

50

る活性層（MQW活性層）54を形成する。ここで、井戸層は、アンドープ（undoped） $In_{0.01}Ga_{0.99}N$ であり、厚さ5nm程度である。障壁層は、 $Si-Al_{0.09}Ga_{0.91}N$ であり、厚さ20nmである。次に、p型 $Al_{0.38}Ga_{0.62}N$ 層55を30nmの厚さで形成する。ここで、p型不純物はMgとする。次に、p型 $Al_{0.07}Ga_{0.93}N$ 層56を0.12μmの厚さで形成する。ここで、p型不純物はMgとする。次に、p型オーミックコンタクト電極57を蒸着により形成する。この際、このp型オーミックコンタクト電極57が高い反射特性を有するようにRhを用いることにより、365nmの発光波長に対してp型 $Al_{0.07}Ga_{0.93}N$ 層56との境界面において高い反射率が得られる。次に、p型オーミックコンタクト電極57上にAu/Sn膜58を薄く形成する。

## 【0071】

次に、図4（b）に示すように、Au/Sn膜58を介してp型オーミックコンタクト電極57側を熱伝導性が高い基板（例えばCuW基板59）上にポンディングする。この後、例えばサファイア基板1の裏面側からレーザ照射を行うことによりサファイア基板1、AlN層11、GaN層12を除去してn型 $Al_{0.07}Ga_{0.93}N$ 層53を露出させる。このn型 $Al_{0.07}Ga_{0.93}N$ 層53の露出面を例えばCMP（化学的機械研磨）により研磨した後、研磨面にn電極60を例えば所定のメッシュ状に形成する。そして、CuW基板59を熱抵抗が低いリードフレーム（図示せず）上にマウントする。

## 【0072】

このようなプロセスを経て製造されたLEDの構造によれば、CuW基板59による放熱性が良く、高い発光出力が得られる。なお、前記したようにサファイア基板1、AlN層11、GaN層12が除去された後のLEDの構造は、従来のLEDの構造と一見類似しているが、n型 $Al_{0.07}Ga_{0.93}N$ 層53、MQW活性層54、p型 $Al_{0.38}Ga_{0.62}N$ 層55、p型 $Al_{0.07}Ga_{0.93}N$ 層56は、c軸方向に面方位が揃ったAlN層11、GaN層12の上に順次成長されたものである点で差異がある。

## 【0073】

[実施例3] 実施例3に係るLEDは、実施例2の一部を変更し、p型オーミックコンタクト電極57を形成した後、p型 $Al_{0.07}Ga_{0.93}N$ 層56、p型 $Al_{0.38}Ga_{0.62}N$ 層55、MQW活性層54およびn型 $Al_{0.07}Ga_{0.93}N$ 層53の一部をエッチング除去することによってGaN層12の一部を露出させ、その露出面にn電極（図示せず）を形成した構造を有するLEDを得ることも可能である。

## 【0074】

[実施例4] 実施例4に係るLEDは、前述した実施例2に係るLEDと比べて、MQW活性層の井戸層（undoped  $In_{0.01}Ga_{0.99}N$ ）の厚さが7nmである点と、障壁層のAl組成が11%、p型 $Al_{0.38}Ga_{0.62}N$ 層のAl組成が23%、厚さが25nmである点が異なり、その他は同じである。このような構造により、実施例2とほぼ同等の特性を有するLEDを得ることができる。

## 【0075】

[実施例5] 実施例4の一部を変更し、実施例3と同様に、GaN層12の上面の一部を露出させ、その露出面にn電極（図示せず）を形成した構造を有するLEDを得ることも可能である。

## 【0076】

[実施例6] 実施例6は、図2に示した積層半導体基板の実施例であり、図1に示した積層半導体基板（ウェハー）10のGaN層12上に、それよりも格子定数が小さい第3の半導体層として $Al_xGa_{1-x}N$ （ $0 < x \leq 0.1$ ）層13を成長させたものである。これらのサファイア基板1、AlN層11、GaN層12および $Al_xGa_{1-x}N$ （ $0 < x \leq 0.1$ ）層13は、その上に窒化物半導体を積層するための積層半導体基板を構成している。

## 【0077】

実施例6の積層半導体基板を形成する際、まず、実施例1で述べたようにGaN層12を形成した後、その上に $Al_xGa_{1-x}N$ （ $0 < x \leq 0.1$ ）層13を積層する。具体的

10

20

30

40

50

には、引き続き、基板の温度を所定の温度に設定し、キャリアガスに水素、原料ガスにアンモニアとTMGとTMAを用い、Al<sub>0.05</sub>Ga<sub>0.95</sub>N層13を10μm程度成長させる。このAl<sub>0.05</sub>Ga<sub>0.95</sub>N層13の平均的な成長方向はc軸方向である。

#### 【0078】

したがって、この積層半導体基板上に結晶性の良い窒化物半導体層を積層して窒化物半導体デバイス(LED、LDなど)を形成する際、デバイスの製造工程を安定化し、デバイスを歩留まり良く、低コストで実現することができる。

#### 【0079】

[実施例7] 実施例7は、本願出願人に係る特開平9-153642号公報に開示の窒化物半導体発光素子を参考にし、本発明の積層半導体基板を使用して製造したLEDである。

10

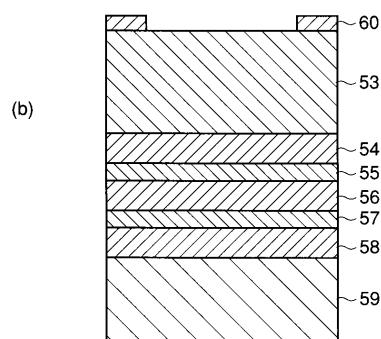

図5は、実施例7のLEDの構造を模式的に示す断面図である。図5に示すLEDは、図2を参照して前述した実施例6におけるサファイア基板1、AlN層11、GaN層12およびAl<sub>x</sub>Ga<sub>1-x</sub>N層13からなる積層半導体基板を使用して素子を形成した後にチップに切り出したものである。この場合、実施例6で得られた積層半導体基板のGaN層12をバッファ層として使用し、その上のSi-Al<sub>b</sub>Ga<sub>1-b</sub>N層13をn型コンタクト層およびn型クラッド層として使用している。Si-Al<sub>b</sub>Ga<sub>1-b</sub>N層13上に、単一量子井戸(SQW:Single-Quantum-Well)構造若しくはMQW構造を有する活性層16、p型クラッド層17、p型コンタクト層18が形成されている。p型コンタクト層18、p型クラッド層17および活性層16の一部がエッチングにより取り除かれてn型クラッド層13が露出している。p型コンタクト層18上にはp電極14が形成されており、n型クラッド層13上にはn電極15が形成されている。

20

#### 【0080】

そして、ウェハーが320μm角のチップにカットされた後、カップ形状を有するリードフレームに設置され、エポキシ樹脂でモールドされることによってLED素子が構成されている。

#### 【0081】

前記活性層16は、SQW構造またはMQW構造にすると、非常に出力の高い発光素子が得られる。ここで、SQWおよびMQWは、ノンドープのInGaNによる量子準位間の発光が得られる活性層の構造である。例えばSQW活性層は、単一組成のIn<sub>x</sub>Al<sub>y</sub>Ga<sub>1-x-y</sub>N(0<x,y<1)、例えばIn<sub>x</sub>Ga<sub>1-x</sub>N(0<x<1)で構成した層であり、In<sub>x</sub>Ga<sub>1-x</sub>Nの膜厚を10nm以下、さらに好ましくは7nm以下とすることにより量子準位間の強い発光が得られる。また、MQW活性層は、組成比の異なるIn<sub>x</sub>Ga<sub>1-x</sub>N(X=0、X=1を含む)の薄膜を複数積層した多層膜とする。このように活性層をSQW構造またはMQW構造とすることにより、量子準位間発光で約365nm~660nmまでの発光が得られる。量子構造の井戸層の厚さとしては、前記のように7nm以下が好ましい。MQW構造では井戸層はIn<sub>x</sub>Ga<sub>1-x</sub>Nで構成し、障壁層は同じくIn<sub>y</sub>Ga<sub>1-y</sub>N(y<x、y=0を含む)で構成することが望ましい。特に好ましくは井戸層と障壁層をInGaNで形成すると同一温度で成長できるので結晶性のよい活性層が得られる。障壁層の膜厚は15nm以下、さらに好ましくは12nm以下にすると高出力の発光素子が得られる。

30

#### 【0082】

前記したように量子構造の井戸層の厚さとしては7nm以下、さらに好ましくは5nm以下とすると発光出力の高い素子を実現できる。これは、この膜厚がInGaN活性層の臨界膜厚以下であることを示している。MQW構造の場合も同様に、井戸層の厚さは7nm以下に調整し、障壁層の厚さは15nm以下に調整することが望ましい。ここで、紫外発光の活性層においては、障壁層の膜厚を10~20nmとする。

#### 【0083】

活性層16に接するp型クラッド層17は、p型Al<sub>y</sub>Ga<sub>1-y</sub>N(0<y<1)とする必要があり、特に好ましくはy値を0.05以上とすると高出力の素子が得られる。さらに、AlGaNは高キャリア濃度のp型が得られやすく、また成長時に分解し難く、In

40

$n$  GaN 活性層 16 の分解を抑える作用がある。しかも、InGaN 活性層 16 に対して、バンドオフセットおよび屈折率差を他の窒化物半導体に比べて大きくできるので最も優れている。また、p 型クラッド層を p 型 GaN とすると、p 型 AlGaN に比べて発光出力が約 1 / 3 に低下してしまう。これは、AlGaN が電子障壁層として有効であるからである。したがって、p 型クラッド層としては、y 値が 0.05 以上の Mg ドープ p 型  $Al_y Ga_{1-y} N$  が最も好ましい。この p 型クラッド層 17 の膜厚は、1 nm 以上、2 μm 以下、さらに好ましくは 5 nm 以上、0.5 μm 以下にすることが望ましい。p 型クラッド層 17 の膜厚が 1 nm よりも薄いと、p 型クラッド層 17 が存在しないのに近い状態になり、発光出力が低下する傾向にあり、2 μm より厚いと結晶成長中に p 型クラッド層自体にクラックが入りやすくなり、クラックの入った層に次の層を積層しても、結晶性の良い半導体層が得られず、出力が低下する傾向にあるからである。なお、窒化物半導体を p 型とするには、結晶成長中に Mg、Zn、C、Be、Ca、Ba 等のアクセプター不純物をドープすることによって得られるが、高キャリア濃度の p 層を得るために、アクセプター不純物のドープ後、窒素、アルゴン等の不活性ガス雰囲気中、400 以上でアニーリングすることがより望ましい。アニーリングを行うことにより、通常、p 型 AlGaN で  $1 \times 10^{17} \sim 1 \times 10^{19} / cm^3$  のキャリア濃度が得られる。また、その他、電子線照射処理を行ってもよい。p 型コンタクト層 18 は、p 型 GaN、特に好ましくは Mg ドープ p 型 GaN とする。この p 型 GaN は、p 電極 14 と接する層であるので、発光素子の場合、オーミックコンタクトを得ることが重要である。p 型 GaN は、多くの金属とオーミックが取り易く、コンタクト層として最も好ましい電極材料としては、例えば Ni-Au、Ni-Ti 等を挙げることができる。p 型コンタクト層 18 の厚さは特に限定するものではないが、通常、50 nm ~ 2 μm 程度の厚さで成長する

10

20

30

ことが望ましい。

#### 【0084】

図 5 に示したデバイス構造によれば、必要最小限の構造で、発光出力に優れた窒化物 LED を得ることができる。その理由は、各層それが有効に作用しているからである。まず、Si-Al<sub>0.05</sub>Ga<sub>0.95</sub>N 層 13 からなる n 型クラッド層は、電流注入層にもなるし、キャリア閉じ込め層にもなる。Si-Al<sub>0.05</sub>Ga<sub>0.95</sub>N 層 13 は、n 型不純物を発光層への電流注入層として適切な量だけ含んでおり、過剰な n 型不純物を含まないので、発光層からの発熱を基板側から効率良く放熱することが可能になり、素子寿命に優れた LED を得ることができる。

#### 【0085】

[実施例 8] 実施例 8 は、実施例 7 の LED の変形例 1 であり、実施例 6 に示した積層半導体基板を使用して素子を形成し、サファイア基板および AlN 層を除去した後にチップに切り出したものである。

#### 【0086】

図 6 は、実施例 8 の LED の構造を模式的に示す断面図である。図 6 に示す LED の構造は、図 5 に示した LED と比べて、(1) n 型クラッド層 13 の上面は露出していない点、(2) サファイア基板 1 および AlN 層 11 が除去されている点、(3) GaN 層 12 の裏面側が研磨され、所定の厚さに調整された後で、n 電極 15 が形成され、GaN 層 12 が n コンタクト層として使用されている点が異なり、その他は同じであるので同じ符号を付している。

#### 【0087】

このような構造により、実施例 3 とほぼ同等の特性を有する薄型の LED を得ることができる。

#### 【0088】

[実施例 9] 実施例 9 は、本願出願人に係る特許第 3063757 号公報に開示の窒化物半導体素子の 1 つである LED を参考にし、本発明の積層半導体基板を使用して製造した LED である。

#### 【0089】

10

20

30

40

50

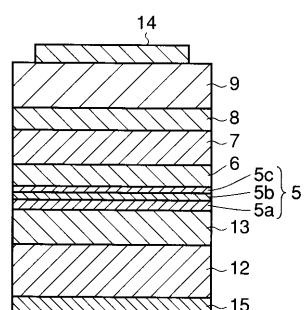

図7は、実施例9のLEDの構造を模式的に示す断面図である。図7に示すLEDは、図2を参照して前述した実施例6のサファイア基板1、AlN層11、GaN層12およびAl<sub>x</sub>Ga<sub>1-x</sub>N層13からなる積層半導体基板を使用して素子を形成した後にチップに切り出したものである。この場合、実施例6で得られた積層半導体基板のGaN層12をバッファ層として使用し、その上のSi-Al<sub>b</sub>Ga<sub>1-b</sub>N層13上には、アンドープ窒化物半導体の下層5a、n型不純物ドープ窒化物半導体の中間層5bおよびアンドープ窒化物半導体の上層5cの3層が順に積層されてなるn側第1多層膜5、第1および第2の窒化物半導体層よりなるn側第2多層膜層6、MQW構造の活性層7、p側クラッド層8、(Mgドープ)p側GaNコンタクト層9が順に積層されている。p側GaNコンタクト層9、p側クラッド層8、MQW構造の活性層7、n側第2多層膜層6、n側第1多層膜5およびn型コンタクト層(Si-Al<sub>b</sub>Ga<sub>1-b</sub>N層13)の一部がエッチングにより除去されてn型コンタクト層の上面の一部が露出している。p側GaNコンタクト層9上にはp電極およびpパット電極14が形成されており、n型コンタクト層の露出部上にはn電極15が形成されている。

10

## 【0090】

なお、前記活性層7は、In<sub>a</sub>Ga<sub>1-a</sub>N(0 < a < 1)を含んでなるMQW構造である。p側クラッド層8は、互いにバンドギャップエネルギーが異なり且つ互いにp型不純物濃度が異なる(または同一の)第3の窒化物半導体層および第4の窒化物半導体層が積層されてなるp側多層膜クラッド層、または、p型不純物を含みAl<sub>b</sub>Ga<sub>1-b</sub>N(0 < b < 1)よりなるp側単一膜クラッド層である。

20

## 【0091】

図7に示したデバイス構造によれば、発光出力に優れた窒化物LEDを得ることができる。その理由は、各層それぞれが有効に作用しているからである。Si-Al<sub>0.05</sub>Ga<sub>0.95</sub>N層13は、電流注入層にもなるし、キャリア閉じ込め層にもなる。

20

## 【0092】

次に、n側第1多層膜5、n側第2多層膜層6、MQW構造の活性層7、p側クラッド層8、p側GaNコンタクト層9、p電極およびpパット電極14、n電極15を形成する工程について説明する。

30

## 【0093】

(n側第1多層膜層5)実施例2で得られた積層半導体基板上に、1050度で、TMG、アンモニアガスを用いて、アンドープGaNからなる下層5aを2000オングストロームの膜厚で成長させ、続いて同温度にてシランガスを追加し、Siを4.5×10<sup>18</sup>/cm<sup>3</sup>ドープしたGaNからなる中間層5bを300オングストロームの膜厚で成長させ、更に続いてシランガスのみを止め、同温度にてアンドープGaNからなる上層5cを50オングストロームの膜厚で成長させ、3層からなる総膜厚2350オングストロームの第1多層膜層5を成長させる。

## 【0094】

(n側第2多層膜層6)次に、同様の温度で、アンドープGaNよりなる第2の窒化物半導体層を40オングストローム成長させ、次に温度を800にして、TMG、TMI(トリメチルインジウム)、アンモニアを用い、アンドープIn<sub>0.13</sub>Ga<sub>0.87</sub>Nよりなる第1の窒化物半導体層を20オングストローム成長させる。そしてこれらの操作を繰り返し、第2+第1の順で交互に10層づつ積層させ、最後にGaNよりなる第2の窒化物半導体層を40オングストローム成長させた超格子構造の多層膜よりなるn側第2多層膜層6を640オングストロームの膜厚で成長させる。

40

## 【0095】

(活性層7)次に、アンドープGaNよりなる障壁層を200オングストロームの膜厚で成長させ、続いて温度を800にして、TMG、TMI、アンモニアを用いアンドープIn<sub>0.4</sub>Ga<sub>0.6</sub>Nよりなる井戸層を30オングストロームの膜厚で成長させる。そして、障壁+井戸+障壁+井戸+障壁の順で障壁層を5層、井戸層を4層、交互に

50

積層して、総膜厚 1120 オングストロームの MQW 構造よりなる活性層 7 を成長させる。

#### 【0096】

(p 側多層膜クラッド層 8) 次に、温度 1050 で、TMG、TMA、アンモニア、 $C_{p_2}Mg$  (シクロペンタジエニルマグネシウム) を用い、Mg を  $1 \times 10^{20} / cm^3$  ドープした p 型  $Al_{0.2}Ga_{0.8}N$  よりなる第 3 の窒化物半導体層を 40 オングストロームの膜厚で成長させ、続いて温度を 800 にして、TMG、TMI、アンモニア、 $C_{p_2}Mg$  を用い、Mg を  $1 \times 10^{20} / cm^3$  ドープした  $In_{0.03}Ga_{0.97}N$  よりなる第 4 の窒化物半導体層を 25 オングストロームの膜厚で成長させる。そしてこれらの操作を繰り返し、第 3 + 第 4 の順で交互に 5 層ずつ積層し、最後に第 3 の窒化物半導体層を 40 オングストロームの膜厚で成長させた超格子構造の多層膜よりなる p 側多層膜クラッド層 8 を 365 オングストロームの膜厚で成長させる。10

#### 【0097】

(p 側 GaN コンタクト層 9) 続いて 1050 で、TMG、アンモニア、 $C_{p_2}Mg$  を用い、Mg を  $1 \times 10^{20} / cm^3$  ドープした p 型 GaN よりなる p 側コンタクト層 (Mg ドープ p 側 GaN コンタクト層) 9 を 700 オングストロームの膜厚で成長させる。

#### 【0098】

反応終了後、温度を室温まで下げ、さらに窒素雰囲気中、ウェハーを反応容器内において、700 でアニーリングを行い、p 型層をさらに低抵抗化する。この後、ウェハーを反応容器から取り出し、最上層の p 側コンタクト層 9 の表面に所定の形状のマスクを形成し、RIE (反応性イオンエッティング) 装置で p 側コンタクト層側からエッティングを行い、図 7 に示すように n 側コンタクト層の表面を露出させる。この後、最上層にある p 側コンタクト層 9 のほぼ全面に膜厚 200 オングストロームの Ni と Au を含む透光性の p 電極およびその上のボンディング用の Au よりなる p パッド電極 14 を  $0.5 \mu m$  の膜厚で形成する。一方、エッティングにより露出させた n 側コンタクト層の表面には W と Al を含む n 電極 15 を形成して LED 素子とした。20

#### 【0099】

[実施例 10] 実施例 10 は、実施例 9 の LED の変形例 1 であり、図 2 に示した積層半導体基板を使用して素子を形成し、サファイア基板および AlN 層を除去した後にチップに切り出したものである。30

#### 【0100】

図 8 は、実施例 10 の LED の構造を模式的に示す断面図である。図 8 に示す LED の構造は、図 7 に示した LED と比べて、(1) Si -  $Al_{0.05}Ga_{0.95}N$  層 13 の上面は露出していない点、(2) サファイア基板 1 と AlN 層 11 が除去されている点、(3) GaN 層 12 の裏面側が研磨され、所定の厚さに調整された後で、n 電極 15 が形成され、GaN 層 12 が n コンタクト層として使用されている点が異なり、その他は同じであるので同じ符号を付している。

#### 【0101】

このような構造により、実施例 10 とほぼ同等の特性を有する薄型の LED を得ることができる。40

#### 【0102】

次に、実施例 9 に示した工程と異なる部分について説明する。

#### 【0103】

ウェハーを反応容器から取り出した後、p 側コンタクト層 9 側からエッティングを行って n 側コンタクト層の表面の一部を露出させる処理を省略する。この後、p 電極およびその上のボンディング用の Au よりなる p パッド電極 14 を形成する。さらに、サファイア基板 1 および AlN 層 11 を除去した後、GaN 層 12 の裏面側をラッピングおよび研磨して所定の厚さに調整した後で、Ti と Al を含む n 電極 15 を形成する。この後、ウェハーを LD チップにカットした後、アセンブリして LD とする。

#### 【0104】

## [実施例 11～15]

次に、実施例 6 に示した積層半導体基板を使用して製造した窒化物半導体レーザ素子を、3つの形態に分けて説明する。

## 【0105】

第1の形態は、実施例 6 に示した積層半導体基板の第3の半導体層 13 をクラッド層として利用する形態であり、ベストモードと考える。

## 【0106】

第2の形態は、実施例 6 に示した積層半導体基板の第3の半導体層 13 上にn側超格子クラッド層を形成する形態である。この場合、第3の半導体層 13 は単一膜で形成する。

## 【0107】

第3の形態は、図2中に示した積層半導体基板の第3の半導体層 13 上に、クラック防止層とn側超格子クラッド層を積層形成する形態である。第3の半導体層 13 のA1の混晶比が比較的高くなると、その上に成長させる窒化物半導体層にクラックが発生する傾向にあるので、クラック防止層を形成するものである。

## 【0108】

## [実施例 11]

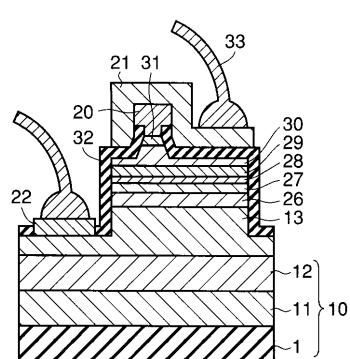

図9は、本願出願人に係る特開平10-326943号公報に開示されている窒化物半導体素子の1つであるLDを参考にし、本発明の積層半導体基板を使用して製造したLDのレーザ光の共振方向に垂直な位置で切断した際の構造を模式的に示す断面図である。このLDは、実施例6に示した積層半導体基板を使用して素子を形成した後にチップに切り出したものである。

## 【0109】

図9に示すLDは、実施例6で得られた積層半導体基板のn型GaN層12をnコンタクト層、Si-A1<sub>b</sub>Ga<sub>1-b</sub>N層13をクラッド層として利用している。Si-A1<sub>b</sub>Ga<sub>1-b</sub>N層13上に、n側光ガイド層26、活性層27、キャップ層28、p側光ガイド層29、p側クラッド層30、p側コンタクト層31が順に積層されている。そして、p側コンタクト層31およびp側クラッド層30は、4μmのストライプ幅を有するリッジストライプを形成するようにエッチングされている。また、このリッジストライプのストライプ幅の中心は後で形成される負電極22に接近している。このように、特に活性層よりも上にあるA1を含むp型窒化物半導体層以上の層がリッジ形状とされることにより、活性層の発光がリッジ下部に集中して、横モードが单一化し易く、閾値が低下し易い。

## 【0110】

さらに、リッジストライプの表面および露出しているp側クラッド層30の表面がマスクパターンで覆われてRIE法でエッチングが行われることにより、負電極22を形成すべきn側コンタクト層(n型GaN層12)の一部の表面が露出されている。そして、最上層にあるp側コンタクト層31のリッジストライプの最上層全面に正電極20が形成され、露出しているn側GaN層12の表面にリッジストライプと平行に負電極22が形成されている。

## 【0111】

そして、正電極20および負電極22の形成位置を除く上面を覆うようにSiO<sub>2</sub>よりも広い面積で形成されており、放熱性が向上し、ワイヤーボンディングが容易になっている。また、パッド電極21は、正電極20よりも膜厚が厚く形成されており、正電極20の剥がれを防止する。

## 【0112】

そして、基板1の厚さが100μmとなるように基板裏面がラッピングされた後、さらに細かい研磨剤で1μmポリシングされて基板裏面が鏡面状にされている。このように基板の厚さを100μm以下に薄くすることによって、レーザ素子の放熱性が高まる。

## 【0113】

10

20

30

40

50

この後、基板の研磨面側がスクライプされ、リッジストライプに垂直な方向でバー状に劈開されることによって、劈開面に共振器長 $500\text{ }\mu\text{m}$ の共振器を作製する。さらに、共振器面に $\text{SiO}_2$ と $\text{TiO}_2$ よりなる誘電体多層膜(図示せず)が形成され、最後にリッジストライプに平行な方向で、バーが切断されてLDチップとなる。このLDチップがフェースアップ状態(基板1とヒートシンクとが対向した状態)でヒートシンクに設置され、それぞれの電極が金線よりなるワイヤー33でボンディング接続されている。この際、図9中に示すように、ワイヤーボンディング時の位置は、リッジストライプの真上を避けてリッジストライプの位置から離れた位置とされている。これにより、リッジ部に衝撃を与えないでの、リッジ部の結晶が破壊されることはない。そして、このLDチップのレーザ発振を試みたところ、室温において、発振波長 $405\text{ nm}$ の連続発振が確認された。

10

## 【0114】

なお、パッド電極21はp側コンタクト層31とオーミック接触が得られていなくても良く、単に正電極20と電気的に接続するだけでよい。パッド電極21は、正電極20よりも膜厚を厚くして、正電極20の剥離を防止すると共に、表面積を正電極20よりも大きくしてあるので、本実施例のようなLDのような場合には、正電極20側でパッド電極21にワイヤーボンディングを行うことを容易にすると共に、正電極20側をヒートシンク、サブマウントのような放熱体に接続する際に、接着面積を大きくして放熱性を向上させる。

20

## 【0115】

図9に示したデバイス構造によれば、発光出力に優れたLDを得ることができる。その理由は、各層それぞれが有効に作用しているからである。 $\text{Si}-\text{Al}_{0.05}\text{Ga}_{0.95}\text{N}$ 層13からなるn型クラッド層は、電流注入層にもなるし、キャリア閉じ込め層にもなる。

20

## 【0116】

次に、n側光ガイド層26、活性層27、キャップ層28、p側光ガイド層29、p側クラッド層30、p側コンタクト層31、絶縁膜32、正電極20、パッド電極21、負電極22を形成する工程について説明する。

30

## 【0117】

(n側光ガイド層26)不純物ガスを止めた状態で、 $1050$ 度アンドープGaNよりなるn側光ガイド層26を $0.2\text{ }\mu\text{m}$ の膜厚で成長させる。

30

## 【0118】

(活性層27)次に、原料ガスにTMG、TMI、アンモニア、シランガスを用いて活性層27を成長させる。活性層27は温度を $800$ 度に保持して、まずSiを $8 \times 10^{18}/\text{cm}^3$ でドープした $\text{In}_{0.2}\text{Ga}_{0.8}\text{N}$ よりなる井戸層を $25$ オングストロームの膜厚で成長させる。次に、TMIのモル比を変化させるのみで同一温度で、Siを $8 \times 10^{18}/\text{cm}^3$ ドープした $\text{In}_{0.01}\text{Ga}_{0.95}\text{N}$ よりなる障壁層を $50$ オングストロームの膜厚で成長させる。この操作を2回繰り返し、最後に井戸層を積層した多重量子井戸構造とする。

30

## 【0119】

(p側キャップ層28)次に、温度を $1050$ 度に上げ、TMG、TMA、アンモニア、 $\text{Cp}_2\text{Mg}$ (シクロペンタジエニルマグネシウム)を用い、Mgを $1 \times 10^{20}/\text{cm}^3$ ドープしたp型 $\text{Al}_{0.1}\text{Ga}_{0.9}\text{N}$ よりなるp側キャップ層28を $300$ オングストロームの膜厚で成長させる。

40

## 【0120】

(p側光ガイド層29)不純物ガスを止め、 $1050$ 度、アンドープGaNよりなるp側光ガイド層29を $0.2\text{ }\mu\text{m}$ の膜厚で成長させる。

40

## 【0121】

(p側クラッド層30)続いて $1050$ 度、Mgを $1 \times 10^{20}/\text{cm}^3$ ドープしたp型 $\text{Al}_{0.20}\text{Ga}_{0.80}\text{N}$ よりなるA層を $20$ オングストロームと、Mgを $1 \times 10^{20}/\text{cm}^3$ ドープしたp型GaNよりなるB層を $20$ オングストローム成長させる。そしてこのペアを $125$ 回成長させ、総膜厚 $0.5\text{ }\mu\text{m}$ ( $5000$ オングストローム)の超格子構造のp側クラッド層30を成長させる。

50

## 【0122】

(p側コンタクト層31)最後に、p側クラッド層30の上に、1050でMgを $1 \times 10^{20} / \text{cm}^3$ ドープしたp型GaNよりなるp側コンタクト層31を150オングストロームの膜厚で成長させる。

## 【0123】

反応終了後、温度を室温まで下げ、さらに窒素雰囲気中、ウェハーを反応容器内において、700でアニーリングを行い、p型層をさらに低抵抗化する。アニーリング後、ウェハーを反応容器から取り出し、RIE装置でエッティングを行い、最上層のp側コンタクト層31とp側クラッド層30とをエッティングして、4μmのストライプ幅を有するリッジストライプを形成する。リッジストライプを形成する際は、予めストライプ幅の中心が後に形成する負電極22に接近しているように設計する。リッジストライプを形成する場合、特に活性層よりも上にあるAlを含むp型窒化物半導体層以上の層をリッジ形状とすることにより、活性層の発光がリッジ下部に集中して、横モードが单一化しやすく、閾値が低下しやすい。また、本実施例のように、絶縁性の基板を使用した場合には、リッジ部のストライプの中央を活性層のストライプの中央とずらして負電極22側に接近させる方が閾値を低下させる上で好ましい。

## 【0124】

次に、リッジストライプの表面と、露出しているp側クラッド層30の表面とにマスクを形成し、RIEでエッティングを行い、負電極22を形成すべきn側コンタクト層(GaN層12)の表面の一部を露出させる。この後、最上層にあるp側コンタクト層31のリッジストライプの最上層全面に、Ni、Pt、Auなどから選択された少なくとも1つを有する正電極、ここではNi/Auよりなる正電極20を、500オングストロームの膜厚で形成する。

## 【0125】

次に、n側コンタクト層の露出表面に、TiとAlよりなる負電極22をリッジストライプと平行に0.5μmの膜厚で形成する。なお、n側コンタクト層(GaN層12)と好ましいオーミックが得られる負電極22の材料としては、Al、Ti、W、Cu、Zn、Sn、In、V等の金属若しくは合金を挙げることができる。

## 【0126】

次に、正電極20および負電極22を形成した位置を除く窒化物半導体層の表面全面にSiO<sub>2</sub>よりなる絶縁膜32を0.5μmの膜厚で形成する。この後、p側クラッド層30上に絶縁膜32を介して、正電極20の上に電気的に接続したRuとAuとを含む取り出し用のパッド電極21を正電極20の表面積よりも広い面積で、2μmの膜厚で形成する。このパッド電極21は、p側コンタクト層31とオーミック接触が得られていなくても良く、単に正電極20と電気的に接続するだけでよい。パッド電極21は、正電極20よりも膜厚を厚くして、正電極の剥がれを防止すると共に、表面積を正電極よりも大きくしてあるので、本実施例のようなLDの場合には、正電極側にパッド電極からワイヤーボンディングするのを容易にすると共に、また正電極側をヒートシンク、サブマウントのような放熱体に接続する際に、接着面積を大きくして放熱性を向上させる。

## 【0127】

以上のようにして、負電極22と正電極20とを形成したウェハーを研磨装置に移送し、ダイヤモンド研磨剤を用いて、窒化物半導体を形成していない側の基板をラッピングし、基板の厚さを100μmとする。ラッピング後、さらに細かい研磨剤で1μmポリシングして基板表面を鏡面状とする。このように基板の厚さを100μm以下に薄くすることによって、LDの放熱性が高まる。

## 【0128】

基板研磨後、研磨面側をスクライプして、リッジストライプに垂直な方向でバー状に劈開し、劈開面に共振器長500μmの共振器を作製する。さらに共振器面にSiO<sub>2</sub>とTiO<sub>2</sub>よりなる誘電体多層膜を形成し、最後にリッジストライプに平行な方向で、バーを切断してLDチップとする。

## 【0129】

最後に、このLDチップをフェースアップ（基板とヒートシンクとが対向した状態）でヒートシンクに設置し、それぞれの電極を金線よりなるワイヤー33でボンディングする。なお、ワイヤーボンディング時の位置は、リッジストライプの位置から離れた位置とする。リッジストライプの真上を避けることにより、リッジ部に衝撃を与えないで、リッジ部の結晶が破壊されない。そして、このレーザチップのレーザ発振を試みたところ、室温において、発振波長405nmの連続発振が確認された。

## 【0130】

[実施例12] 実施例12は、実施例11のLDの変形例1であり、実施例11で述べたn側光ガイド層26を形成する前に、n側超格子クラッド層を形成するように変更したものであり、その他は同じである。10

## 【0131】

(n側超格子クラッド層)温度を1050にして、原料ガスにTMA、TMG、NH<sub>3</sub>、SiH<sub>4</sub>を用い、Siを $1 \times 10^{19} / \text{cm}^3$ ドープしたn型Al<sub>0.20</sub>Ga<sub>0.80</sub>NよりなるA層を20オングストロームと、Siを $1 \times 10^{19} / \text{cm}^3$ ドープしたn型GaNよりなるB層を20オングストローム成長させる。そしてこのペアを125回成長させ、総膜厚0.5μm(5000オングストローム)の超格子構造よりなるn側クラッド層を成長させる。その上に実施例4で述べたn側光ガイド層26の形成工程以降を実施する。これにより、実施例11とほぼ同等の特性のLDを得ることができる。

## 【0132】

[実施例13] 実施例13は、実施例11のLDの変形例2であり、実施例12で述べたn側超格子クラッド層を形成する前に、クラック防止層を形成するように変更したものであり、その他は同じである。20

## 【0133】

(クラック防止層)温度を800にして、原料ガスにTMG、TMI、アンモニア、シランガスを用い、Siを $1 \times 10^{19} / \text{cm}^3$ ドープしたIn<sub>0.1</sub>Ga<sub>0.9</sub>Nよりなるクラック防止層を500オングストロームの膜厚で成長させる。その上に実施例5で述べたn側超格子クラッド層を形成し、その上に実施例4で述べたn側光ガイド層26の形成工程以降を実施する。これにより、実施例11とほぼ同等の特性のLDを得ることができる。

[実施例14] 実施例14は、実施例11のLDの変形例3であり、実施例6に示した積層半導体基板を使用して素子を形成し、サファイア基板を除去した後にチップに切り出したものである。この場合、サファイア基板が省略され、AlN層の裏面側が研磨され、所定の厚さに調整されている。このような構造により、実施例11とほぼ同等の特性を有する薄型のLEDを得ることができる。30

## 【0134】

[実施例15] 実施例15は、実施例11のLDの変形例4であり、実施例6に示した積層半導体基板を使用して素子を形成し、サファイア基板およびAlN層を除去した後にチップに切り出したLEDである。

## 【0135】

図10は、実施例15のLEDの構造を模式的に示す断面図である。図10に示すLEDの構造は、図9に示したLEDと比べて、(1)Si-Al<sub>0.05</sub>Ga<sub>0.95</sub>N層13の上面は露出していない点、(2)サファイア基板1およびAlN層11が除去されている点、(3)GaN層12の裏面側が研磨され、所定の厚さに調整された後で、負電極(n電極)22が形成され、GaN層12がnコンタクト層として使用されている点が異なり、その他は同じであるので同じ符号を付している。40

## 【0136】

このような構造により、実施例11とほぼ同等の特性を有する薄型のLEDを得ることができる。

## 【0137】

次に、実施例11に示した工程と異なる部分について説明する。50

## 【0138】

リッジストライプを形成した後、n側コンタクト層（GaN層12）の表面の一部を露出させる処理を省略する。そして、正電極20の位置を除く上面を覆うようにSiO<sub>2</sub>よりなる絶縁膜32を形成し、正電極20上に電気的に接続された状態でパッド電極21を形成する。さらに、ウェハー裏面側（GaN層12側）をラッピングおよび研磨し、放熱性を高めるためにウェハーを薄くした後で、GaN層12の裏側にTiとAlよりなる負電極22を形成する。なお、GaN層12からなるn側コンタクト層と好ましいオーミックが得られる負電極22の材料としては、Al、Ti、W、Cu、Zn、Sn、In、V等の金属若しくは合金を挙げることができる。この後、ウェハーをLDチップにカットした後、アセンブリしてLDとする。

10

## 【図面の簡単な説明】

## 【0139】

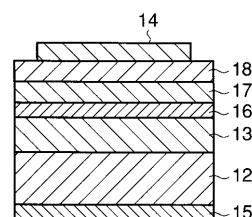

【図1】本発明の第1の実施形態の積層半導体基板の断面構造を模式的に示す図。

【図2】本発明の第2の実施形態の積層半導体基板の断面構造を模式的に示す図。

【図3】本発明の実施例1のLEDの構造を模式的に示す断面図。

【図4】本発明の実施例2のLEDの製造工程を模式的に示す断面図。

【図5】本発明の実施例7のLEDの構造を模式的に示す断面図。

【図6】本発明の実施例8のLEDの構造を模式的に示す断面図。

【図7】本発明の実施例9のLEDの構造を模式的に示す断面図。

【図8】本発明の実施例10のLDの構造を模式的に示す断面図。

20

【図9】本発明の実施例11のLDの構造を模式的に示す断面図。

【図10】本発明の実施例15のLDの構造を模式的に示す断面図。

【図11】図2中のGaN層を形成する際にELO成長法（I）を組み合わせて使用する場合の工程を模式的に示す図。

【図12】図2中のGaN層を形成する際にELO成長法（II）を組み合わせて使用する場合の工程を模式的に示す図。

【図13】図2中のGaN層を形成する際にELO成長法（III）を組み合わせて使用する場合の工程を模式的に示す図。

30

【図14】図2中のGaN層を形成する際にELO成長法（IV）を組み合わせて使用する場合の工程を模式的に示す図。

【図15】図2中のGaN層を形成する際にELO成長法（V）を組み合わせて使用する場合の工程を模式的に示す図。

## 【符号の説明】

## 【0140】

1...サファイア基板

10...積層半導体基板

11...第1の半導体層（AlN層）

12...第2の半導体層（GaN層）

53...第3の半導体層（n型Al<sub>0.07</sub>Ga<sub>0.93</sub>N層）

54...MQW活性層

40

55...p型Al<sub>0.38</sub>Ga<sub>0.62</sub>N層

56...p型Al<sub>0.07</sub>Ga<sub>0.93</sub>N層

57...p型オーミックコンタクト電極

58...Au/Sn膜

59...CuW基板

60...n電極

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 森田 大介

徳島県阿南市上中町岡491番地100 日亜化学工業株式会社内

F ターム(参考) 5F041 AA40 AA41 CA05 CA23 CA34 CA40 CA46 CA74 CB11

5F045 AA04 AB09 AB14 AC08 AC12 AC15 AD14 AD15 AE23 AE25

AF09 BB08 CA10 CA12 DA52