(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-287528

(P2008-287528A)

(43) 公開日 平成20年11月27日(2008.11.27)

(51) Int.Cl.

G06F 12/06 (2006.01)

G06F 12/00 (2006.01)

G06F 12/02 (2006.01)

F 1

G06F 12/06 550A

G06F 12/00 571B

G06F 12/02 590B

テーマコード(参考)

5B060

審査請求 未請求 請求項の数 18 O L (全 23 頁)

(21) 出願番号

(22) 出願日特願2007-132245 (P2007-132245)

平成19年5月18日 (2007.5.18)(71) 出願人 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人 100089233

弁理士 吉田 茂明

(74) 代理人 100088672

弁理士 吉竹 英俊

(74) 代理人 100088845

弁理士 有田 貴弘

(72) 発明者 泉 佑治

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

F ターム(参考) 5B060 CA13 CD13

(54) 【発明の名称】リクエスト調停装置及びメモリコントローラ

## (57) 【要約】

【課題】イニシエータが破綻しない待ち時間である許容時間を考慮し、かつ、効率的なリクエスト調停が行えるリクエスト調停装置及び制御対象のメモリの性能向上を図ったメモリコントローラを得る。

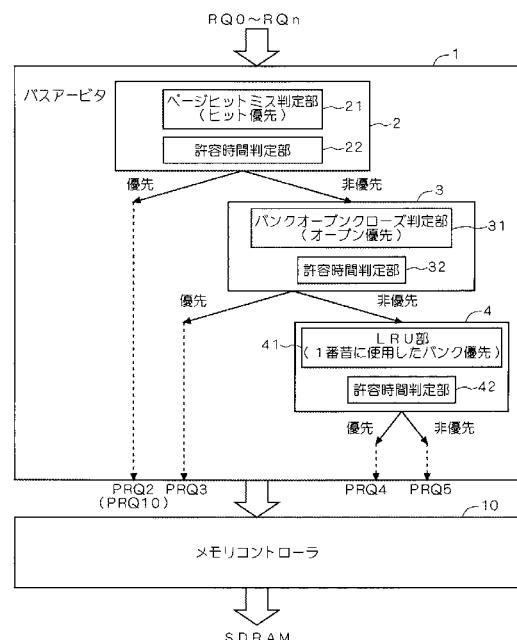

【解決手段】バスアービタ1は、イニシエータのリクエストRQ0～RQnを受け、内部に許容時間判定機能付きページヒットミス判定部2、許容時間判定機能付きバンクオープンクローズ判定部3、及び許容時間判定機能付きLRU部4を有している。そして、リクエストRQ0～RQnに対するリクエスト調停の優先順位はページヒット、バンクオープン、LRUの順で、SDRAMに対するバンク優先順位が決定する。さらに、各判定部2～4は内部に許容時間判定部22、32、42を有しており、判定部2～4の優先処理の際ににおいても、許容時間がカウント閾値LVthを下回ったイニシエータのリクエストRQを最優先処理する。

【選択図】図1

2 : 許容時間判定機能付きページヒットミス判定部

3 : 許容時間判定機能付きバンクオープンクローズ判定部

4 : 許容時間判定機能付きLRU部

## 【特許請求の範囲】

## 【請求項 1】

複数のイニシエータから得られる、所定のメモリに対するアクセス要求である複数のリクエストから、優先的に処理すべき優先リクエストを決定するリクエスト調停装置であって、前記所定のメモリは複数のバンクが割り当てられており、前記複数のバンクはそれぞれ複数のページが割り当てられ、

許容時間判定機能付きページヒットミス判定部を備え、

前記許容時間判定機能付きページヒットミス判定部は、

直前に決定した前記優先リクエストにおける前記所定のメモリへのアクセスアドレスである前回アクセスアドレスを保持する前回アクセスアドレス情報保持部を有し、前記複数のリクエストそれぞれの前記所定のメモリへのアクセスアドレスと前記前回アクセスアドレスとを比較して互いのアドレスが指定するバンク及びページが一致するページヒットの有無を前記複数のリクエストそれぞれについて判定し、前記複数のリクエストのうち、ページヒットしたリクエストの中から優先的に前記優先リクエストを決定するページヒットミス判定部と、

前記ページヒットミス判定部と連動して動作し、前記複数のイニシエータに対応して設定され、前記所定のメモリに対するアクセス待ち時間である複数の許容時間の残存時間を計数し、前記複数の許容時間の残存時間が所定時間以下に達したイニシエータである要メモリアクセスイニシエータが存在した場合、前記複数のリクエストのうち、前記要メモリアクセスイニシエータのリクエストを、前記ページヒットミス判定部の決定より優先させて前記優先リクエストとして決定可能なページヒットミス判定用許容時間判定部とを含む、

リクエスト調停装置。

## 【請求項 2】

請求項 1 記載のリクエスト調停装置であって、

許容時間判定機能付きバンクオープンクローズ判定部をさらに備え、

前記許容時間判定機能付きバンクオープンクローズ判定部は、

前記ページヒットミス判定部によってページヒットしたリクエストが存在しなかった場合に起動し、過去の前記所定のメモリに対するアクセスアドレスの履歴に基づき前記複数のリクエストそれぞれの前記所定のメモリへのアクセスバンクのオープンクローズ状態を判定し、前記複数のリクエストのうち、バンクオープンと判定したリクエストの中から優先的に前記優先リクエストを決定するバンクオープンクローズ判定部と、

バンクオープンクローズ判定部と連動して動作し、前記複数のイニシエータに対応する前記複数の許容時間の残存時間を計数し、前記複数のイニシエータ中に前記要メモリアクセスイニシエータが存在した場合、前記複数のリクエストのうち、前記要メモリアクセスイニシエータのリクエストを、前記バンクオープンクローズ判定部の決定より優先して前記優先リクエストとして決定可能なバンクオープンクローズ判定用許容時間判定部とを含む、

リクエスト調停装置。

## 【請求項 3】

請求項 2 記載のリクエスト調停装置であって、

許容時間判定機能付き L R U 部をさらに備え、

前記許容時間判定機能付き L R U 部は、

前記バンクオープンクローズ判定部によってバンクオープンと判定したリクエストが存在しなかった場合に起動し、過去の前記所定のメモリに対するアクセスアドレスの履歴に基づき、前記複数のリクエストそれぞれの前記所定のメモリへのアクセスバンクが最新アクセス時間が最も古い L R U バンクであるか否かを判定し、前記複数のリクエストのうち、前記 L R U バンクをアクセスバンクとするリクエストの中から優先的に前記優先リクエストを決定する L R U 判定部と、

前記 L R U 判定部と連動して動作し、前記複数のイニシエータに対応して前記複数の許

10

20

30

40

50

容時間の残存時間を計数し、前記複数のイニシエータ中に前記要メモリアクセスイニシエータが存在した場合、前記複数のリクエストのうち、前記要メモリアクセスイニシエータのリクエストを、前記LRU判定部の決定より優先して前記優先リクエストして決定可能なLRU判定用許容時間判定部とを含む、

リクエスト調停装置。

【請求項4】

請求項1ないし請求項3のうち、いずれか1項に記載のリクエスト調停装置であって、前記許容時間判定機能付きページヒットミス判定部は、

前記ページヒットしたリクエストが複数存在した場合、前記許容時間の残存時間がより小さいリクエストを優先的に前記優先リクエストとして決定するページヒット優先処理機能を有する、

リクエスト調停装置。

【請求項5】

請求項2あるいは請求項3に記載のリクエスト調停装置であって、

前記許容時間判定機能付きバンクオープンクローズ判定部は、前記バンクオープンと判定したリクエストが複数存在した場合、前記許容時間の残存時間がより小さいリクエストを優先的に前記優先リクエストとして決定するバンクオープン優先処理機能を有する、リクエスト調停装置。

【請求項6】

請求項3記載のリクエスト調停装置であって、

前記許容時間判定機能付きLRU部は、前記LRUバンクにアクセスするリクエストが複数存在した場合、前記許容時間の残存時間がより小さいリクエストを優先的に前記優先リクエストとして決定するLRU優先処理機能を有する、

リクエスト調停装置。

【請求項7】

所定のメモリに対するアクセス要求であるリクエストに基づき前記所定のメモリにアクセスするメモリコントローラであって、前記所定のメモリは複数のバンクが割り当てられており、前記複数のバンクの一部である所定数のバンクがオープン可能であり、

前記所定のメモリに対する過去のアクセス履歴に基づき、前記複数のバンクそれぞれの最新アクセス時間を示す情報をLRUバンク情報として記憶するLRU状態保持部と、

前記所定数のバンクのいずれかをクローズする際、前記LRUバンク情報に基づき、前記所定数のバンクの最新アクセス時間が最も古いLRUバンクを優先的にクローズするバンク切替を行うバンク切替部と、

を備えるメモリコントローラ。

【請求項8】

請求項7記載のメモリコントローラであって、

前記バンク切替部は、前記所定数のバンクのうち一部をオープン固定バンクとして常時オープン状態にする常時オープン制御を実行する、

メモリコントローラ。

【請求項9】

請求項8記載のメモリコントローラであって、

前記バンク切替部は、前記常時オープン制御を行うか否かを切り替える機能を有する、メモリコントローラ。

【請求項10】

複数のイニシエータから要求される、複数のバンクにそれぞれ複数のページが割り当てられたメモリに対する複数のリクエストの中から、優先的に処理すべき優先リクエストを決定するリクエスト調停装置であって、

前記優先リクエストにおける前記メモリへの前回アクセスアドレスを保持する前回アクセスアドレス情報保持部と、

前記複数のリクエストそれぞれの前記メモリへのアクセスアドレスと前記前回アクセス

10

20

30

40

50

アドレスとを比較して互いのアドレスが指定するバンク及びページが一致するページヒットの有無を前記複数のリクエストそれぞれについて判定し、前記複数のリクエストのうち、ページヒットしたリクエストの中から優先的に前記優先リクエストを決定するページヒットミス判定部と、

前記複数のイニシエータに対応して設定され、前記メモリに対する複数のアクセス許容時間の残存時間を計数し、前記複数のアクセス許容時間の残存時間が所定時間以下に達したイニシエータである要メモリアクセスイニシエータが存在した場合、前記複数のリクエストのうち、前記要メモリアクセスイニシエータのリクエストを、前記ページヒットミス判定部の決定より優先させて前記優先リクエストとして決定するページヒットミス判定用許容時間判定部と、

を備えるリクエスト調停装置。

【請求項 1 1】

請求項 1 0 記載のリクエスト調停装置であって、

前記ページヒットミス判定部によってページヒットしたリクエストが存在しなかった場合に、前記メモリに対するアクセスアドレスの履歴に基づき前記複数のリクエストそれぞれの前記メモリへのアクセスバンクのオープンクローズ状態を判定し、前記複数のリクエストのうち、バンクオープンと判定したリクエストの中から優先的に前記優先リクエストを決定するバンクオープンクローズ判定部をさらに備える、

リクエスト調停装置。

【請求項 1 2】

請求項 1 1 記載のリクエスト調停装置であって、

前記バンクオープンクローズ判定部によってバンクオープンと判定したリクエストが存在しなかった場合に、前記メモリに対するアクセスアドレスの履歴に基づき、前記複数のリクエストそれぞれの前記メモリへのアクセスバンクが最新アクセスが最も古い LRU バンクであるか否かを判定し、前記複数のリクエストのうち、前記 LRU バンクをアクセスバンクとするリクエストの中から優先的に前記優先リクエストを決定する LRU 判定部をさらに備える、

リクエスト調停装置。

【請求項 1 3】

請求項 1 0 ないし請求項 1 2 のうち、いずれか 1 項に記載のリクエスト調停装置であって、

前記ページヒットミス判定部は、前記ページヒットしたリクエストが複数存在した場合、前記許容時間の残存時間がより小さいリクエストを優先的に前記優先リクエストとして決定するページヒット優先処理機能を有する、

リクエスト調停装置。

【請求項 1 4】

請求項 1 1 あるいは請求項 1 2 記載のリクエスト調停装置であって、

前記バンクオープンクローズ判定部は、前記バンクオープンと判定したリクエストが複数存在した場合、前記許容時間の残存時間がより小さいリクエストを優先的に前記優先リクエストとして決定するバンクオープン優先処理機能を有する、

リクエスト調停装置。

【請求項 1 5】

請求項 1 2 記載のリクエスト調停装置であって、

前記 LRU 判定部は、前記 LRU バンクにアクセスするリクエストが複数存在した場合、前記許容時間の残存時間がより小さいリクエストを優先的に前記優先リクエストとして決定する LRU 優先処理機能を有する、

リクエスト調停装置。

【請求項 1 6】

複数のバンクが割り当てられ、前記複数のバンクの所定数のバンクがオープン可能なメモリに対するリクエスト要求に基づいて、前記メモリにアクセスするメモリコントローラ

10

20

30

40

50

であって、

前記メモリに対するアクセス履歴に基づき、前記複数のバンクそれぞれのアクセス情報を記憶するLRU状態保持部と、

前記所定数のバンクのいずれかをクローズする際、前記情報に基づき、前記所定数のバンクのうち、アクセスが最も古いLRUバンクを優先的にクローズするバンク切替部と、を備えるメモリコントローラ。

【請求項17】

請求項16記載のメモリコントローラであって、

前記バンク切替部は、前記所定数のバンクのうち一部をオープン固定バンクとして常時オープン状態にする常時オープン制御を実行する、

メモリコントローラ。

10

【請求項18】

請求項16記載のメモリコントローラであって、

前記バンク切替部は、前記常時オープン制御を行うか否かを切り替え機能を有する、メモリコントローラ。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、複数のイニシエータからの所定のメモリに対するアクセス等のリクエストを調停するバスアービタ等のリクエスト調停装置及びメモリコントローラに関する。

20

【背景技術】

【0002】

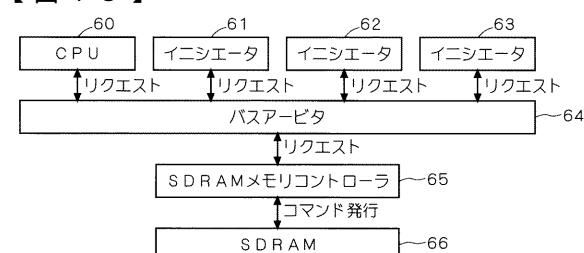

図15は従来のバスアービタとその周辺部とのシステム構成を示すブロック図である。同図に示すように、バスアービタ64はCPU60及びイニシエータ61～63とSDRAMメモリコントローラ65との間に設けられる。

【0003】

バスアービタ64はCPU60及びイニシエータ61～63からのリクエストを調停し、SDRAMメモリコントローラ65へリクエストを発行する。イニシエータ61～63それぞれは画像系(2D, 3D)や画像圧縮、音声などの多量のデータ転送を必要としている。このため、バスアービタ64ではイニシエータ61～63それからの要求を満たせるようにアービトレーション(調停)を行う必要がある。

30

【0004】

イニシエータ61～63それからバスアービタ64へは、SDRAM(Synchronous Dynamic Random Access Memory)66に関し異なるアドレスに対するリクエストが発行される。そこで、バスアービタ64にてSDRAM66のアクセス時におけるページミス、バンクミスや他のイニシエータによる割り込みによるペナルティが少なくなるようにアービトレーションを行うことにより、SDRAM66に対するコマンド発行効率を向上させることが必要となる。なお、上述したペナルティとして、例えば、バンクミスペナルティ、ページミスペナルティ等が挙げられる。

40

【0005】

SDRAM66に対するコマンド発行の効率を上げるため、バスアービタ64にてSDRAM66のバンクヒット/ミス、SDRAM66への先行PRE, ACTコマンド発行などを考慮に入れたアービトレーションを行う。

【0006】

なお、SDRAM66に対するコマンド発行の効率を上げたメモリアクセス要求の調停技術として例えば特許文献1に開示された技術がある。特許文献1では最終アクセスページと同一のページにアクセス要求するメモリマスタに優先的にアクセス許可を与えている調停技術が開示されている。

【0007】

図16はSDRAMメモリコントローラ65及びその周辺を示すブロック図である。一

50

般に S D R A M メモリコントローラ 6 5 では 8 バンク S D R A M のアクセス効率向上方式を採用している。

【 0 0 0 8 】

S D R A M メモリコントローラ 6 5 はバスアービタ 6 4 からのリクエストを受けて S D R A M 6 6 に対してコマンドを発行する。

【 0 0 0 9 】

また、 D D R 2 (Double-Data-Rate2)- S D R A M 等を含む S D R A M では 4 , 8 バンク品の S D R A M が存在する。 8 バンク品を用いた場合に S D R A M メモリコントローラでは、 8 バンク品の制御方式は 4 バンクまでをオープンするようにしているが、 5 個目のバンクをオープンするときにクローズするバンクは、 対となる決められたバンクである。

10

【 0 0 1 0 】

【特許文献 1】特開 2 0 0 6 - 9 9 1 9 9 号公報

【発明の開示】

【発明が解決しようとする課題】

【 0 0 1 1 】

バスアービタでは各イニシエータの処理データが破綻しない待ち時間を考慮する必要がある。イニシエータが破綻しない待ち時間を「許容時間」とする。イニシエータのデータ破綻とは、グラフィックス系のイニシエータでは画像が乱れること、音声系のイニシエータでは音声が途切れたりすることを指す。

20

【 0 0 1 2 】

しかしながら、従来のバスアービタや特許文献 1 で開示されたメモリアクセス要求の調停技術では、上記許容時間を考慮したリクエスト調停を行っていないという問題点があった。

【 0 0 1 3 】

また、上記した 8 バンク品の制御方式では、上記許容時間を全く考慮していない点は勿論、 5 個目のバンクをオープンするときにクローズするバンクは、 対となる決められたバンクであるため、アクセスされやすいバンクをクローズしてしまう可能性があった。このため、 S D R A M アクセス性能低下が起こるといった問題点があった。

【 0 0 1 4 】

この発明は上記問題点を解決するためになされたもので、イニシエータが破綻しない待ち時間である許容時間を考慮し、かつ、効率的なリクエスト調停が行えるリクエスト調停装置及び制御対象のメモリの性能向上を図ったメモリコントローラを得ることを目的とする。

30

【課題を解決するための手段】

【 0 0 1 5 】

この発明の一実施の形態によれば、許容時間判定機能付きページヒットミス判定部は、互いに連動して動作するページミスヒット判定部及び許容時間判定部を有している。

【 0 0 1 6 】

ページミスヒット判定部は、複数のリクエストそれぞれの S D R A M へのアクセスアドレスと前回アクセスアドレスとを比較する。そして、互いのアドレスが指定するバンク及びページが一致するページヒットの有無を前記複数のリクエストそれぞれについて判定し、複数のリクエストのうち、ページヒットしたリクエストの中から優先的に優先リクエストとして決定する。

40

【 0 0 1 7 】

許容時間判定部は、複数のイニシエータに対応して設定された複数の許容時間の残存時間が所定時間以下に達したイニシエータである要メモリアクセスイニシエータが存在した場合、複数のリクエストのうち、要メモリアクセスイニシエータのリクエストを、ページヒットミス判定部の決定より優先させて優先リクエストして決定可能な構成を呈している。

【発明の効果】

50

## 【0018】

この実施の形態によれば、ページヒット判定部及び許容時間判定部の連携により、ページヒットしたリクエストを優先することによりSDRAMに対するリクエストの発行効率が向上する効果を得ながら、許容時間判定部によって各イニシエータの許容時間を優先考慮したリクエスト調整を行うことができる。

## 【発明を実施するための最良の形態】

## 【0019】

<前提技術>

(バスアービトレーション方式)

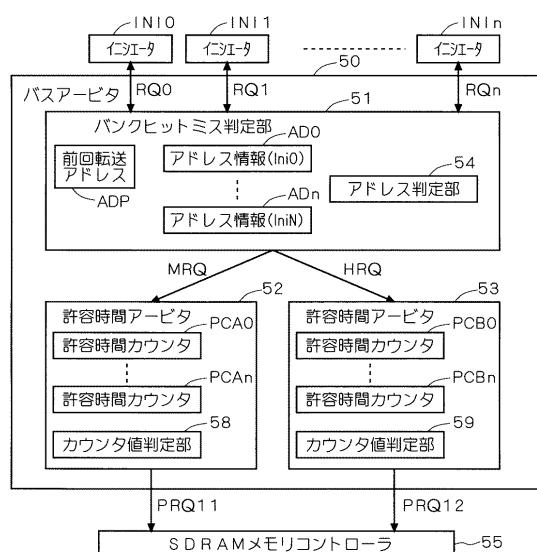

図12はこの発明の前提技術となるバスアービトレーション方式を示すプロック図である。同図に示すように、バスアービタ50は( $n+1$ )個( $n-1$ )のイニシエータIN<sub>0</sub>~IN<sub>n</sub>からのSDRAMに対するリクエストRQ<sub>0</sub>~RQ<sub>n</sub>のアービトレーション(調停)を行う。なお、以下ではリクエストRQ<sub>0</sub>~RQ<sub>n</sub>のいずれかを指す場合、単にリクエストRQと称する場合がある。

10

## 【0020】

まず、リクエストRQ<sub>0</sub>~RQ<sub>n</sub>はバンクヒットミス判定部51にてアービトレーションが行われる。バンクヒットミス判定部51では前回にSDRAMメモリコントローラ55に送られたリクエストの前回転送アドレスAD<sub>p</sub>とイニシエータIN<sub>0</sub>~IN<sub>n</sub>の現在のアドレス情報AD<sub>0</sub>~AD<sub>n</sub>を保持している。

20

## 【0021】

そして、バンクヒットミス判定部51は前回転送アドレスAD<sub>p</sub>とアドレス情報AD<sub>0</sub>~AD<sub>n</sub>とを比較して、前回送られたリクエストと異なるバンクアドレス(バンクミス)のアドレスを指定したリクエストを認識し、リクエストRQ<sub>0</sub>~RQ<sub>n</sub>のうち、前回転送アドレスAD<sub>p</sub>と異なるバンクアドレス(バンク)のリクエストを優先し、許容時間アービタ52の処理対象とする。一方、リクエストRQ<sub>0</sub>~RQ<sub>n</sub>のうち、前回転送アドレスAD<sub>p</sub>と同じバンクアドレス(バンク)のリクエストは優先度が下げられて、許容時間アービタ53の処理対象とする。

## 【0022】

以下、リクエストRQ<sub>0</sub>~RQ<sub>n</sub>のうち、バンクヒットミス判定部51でバンクミスと判定されたリクエストをバンクミスリクエストMRQとし、バンクヒットリクエストHRQとして説明する。

30

## 【0023】

許容時間アービタ52,53では、イニシエータIN<sub>0</sub>~IN<sub>n</sub>それぞれの処理データが破綻しない待ち時間である許容時間をレジスタ(図示せず)にて設定する。具体的には、各イニシエータがリクエストを発行してからイニシエータにレスポンスが帰って来るまでのサイクル数を満たせることができが可能な時間が許容時間となる。

## 【0024】

この許容時間を上記レジスタにて設定することによりシステムごとにアービトレーションを変更でき、イニシエータごとの使用可能な時間の割り振りを細かく設定することができる。すなわち、許容時間アービタ52,53では、イニシエータIN<sub>0</sub>~IN<sub>n</sub>それぞれの許容時間を設定してアービトレーションを行う。

40

## 【0025】

許容時間アービタ52,53は許容時間用いたアービトレーションを行うために、イニシエータごと許容時間をカウントするための許容時間カウンタPCA<sub>0</sub>~PCA<sub>n</sub>、許容時間カウンタPCB<sub>0</sub>~PCB<sub>n</sub>をそれぞれ有する。これら許容時間カウンタPCA<sub>0</sub>~PCA<sub>n</sub>及び許容時間カウンタPCB<sub>0</sub>~PCB<sub>n</sub>はイニシエータIN<sub>0</sub>~IN<sub>n</sub>に対応して設けられる。なお、許容時間カウンタPCA<sub>0</sub>~PCA<sub>n</sub>及び許容時間カウンタPCB<sub>0</sub>~PCB<sub>n</sub>のいずれかを示す場合、単に許容時間カウンタPCA及び許容時間カウンタPCBと称す場合がある。

## 【0026】

50

許容時間カウンタ P C A 0 ~ P C A n 及び許容時間カウンタ P C B 0 ~ P C B n はそれぞれ、対応するイニシエータのリクエストをメモリコントローラ 5 5 へ送っていない場合に許容時間カウント値をダウンカウントし、対応するイニシエータのリクエストをメモリコントローラ 5 5 に送った場合には対応する上記レジスタに設定した時間だけ許容時間をプラスする。

【 0 0 2 7 】

許容時間カウンタ P C A 0 ~ P C A n 及び許容時間カウンタ P C B 0 ~ P C B n それぞれの上記レジスタに設定する値は任意であるため、イニシエータ I N I 0 ~ I N I n に対するアービトレーションのチューニングが可能となる。カウント値 C T のレベル閾値（カウント閾値 L V t h ）を定め、許容時間カウンタのカウント値 C T がカウント閾値 L V t h より小さくなつたイニシエータのリクエスト R Q を最優先する。この場合、当該リクエスト R Q がバンクミスリクエスト M R Q であるかバンクヒットリクエスト H R Q であるかに関係なく、緊急処理として優先リクエスト P R Q 1 0 （優先リクエスト P R Q 1 1 , P R Q 1 2 ）が S D R A M メモリコントローラ 5 5 に送られる。

10

【 0 0 2 8 】

例えば、バンクミスリクエスト M R Q が少なくとも一つが存在する場合、許容時間アービタ 5 2 による処理が実行される。しかし、許容時間カウンタ P C A 0 ~ P C A n のカウント値 C T のうち、一つでもカウント閾値 L V t h を下回るが存在すれば、カウント値判定部 5 8 によって、当該カウント値 C T に対応するイニシエータのリクエスト R Q である許容時間低下リクエスト E R Q が最優先に優先リクエスト P R Q 1 0 とされる。この場合、許容時間低下リクエスト E R Q がバンクミスリクエスト M R Q であるか否かは関係なく優先される。

20

【 0 0 2 9 】

一方、許容時間カウンタ P C A 0 ~ P C A n ( 許容時間カウンタ P C B 0 ~ P C B n ) のカウント値 C T が全てカウント閾値 L V t h より大きい場合は通常のアービトレーションが許容時間アービタ 5 2 , 5 3 によって実行される。以下、許容時間アービタ 5 2 , 5 3 の通常処理について説明する。

30

【 0 0 3 0 】

許容時間アービタ 5 2 の対象となるバンクミスリクエスト M R Q が複数存在する場合、カウント値判定部 5 8 は、複数のバンクミスリクエスト M R Q に対応する複数の許容時間カウンタ P C A のカウント値 C T のうち、最も小さいカウント値 C T に対応するバンクミスリクエスト M R Q を優先リクエスト P R Q 1 1 として選択する。

【 0 0 3 1 】

一方、許容時間アービタ 5 2 の対象となるバンクミスリクエスト M R Q が存在しない場合、バンクヒットリクエスト H R Q の中から許容時間アービタ 5 3 が優先リクエスト P R Q 1 2 を選択する。許容時間アービタ 5 3 内のカウント値判定部 5 9 は、対象となるバンクヒットリクエスト H R Q のうち最も小さいカウント値 C T に対応するバンクヒットリクエスト H R Q を優先リクエスト P R Q 1 2 として選択する。

【 0 0 3 2 】

なお、許容時間アービタ 5 3 によるアービトレーション実行時に、許容時間カウンタ P C B 0 ~ P C B n のカウント値 C T のうち、一つでもカウント閾値 L V t h を下回るがカウント値 C T が存在すれば、カウント値判定部 5 9 によって、当該カウント値 C T に対応するリクエスト R Q である許容時間低下リクエスト E R Q が最優先に優先リクエスト P R Q 1 2 とされる。

40

【 0 0 3 3 】

図 1 3 はある許容時間カウンタ P C A ( P C B ) のカウント動作例を示す説明図である。同図に示すように、カウント値 C T は対応するリクエスト実発行の際、予め設定された許容時間分プラスされる。なお、リクエスト実発行とはカウント値 C T に対応するイニシエータから出力されたリクエストがバスアービタ 5 0 によって優先リクエスト P R Q 1 1 ( P R Q 1 2 ) として決定され、 S D R A M メモリコントローラ 5 5 から S D R A M に実

50

際に出力されたことを意味する。一方、リクエスト無発行時はクロックサイクル（サイクル数 C C L）の経過と共にカウントダウンされる。図 13 に示すように、タイミング  $t_1$ ,  $t_2$  時にはカウント閾値  $L V t h$  を下回ったため、最優先処理され必ずリクエストが発行される。

【0034】

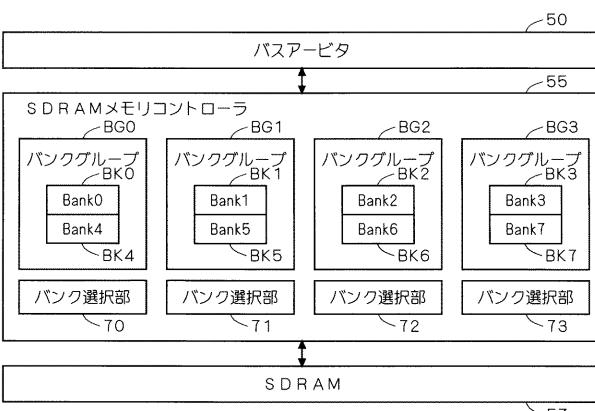

（SDRAMメモリコントローラ）

図 14 は SDRAM メモリコントローラ 55 の詳細を示す説明図である。SDRAM メモリコントローラ 55 は対象となる SDRAM 57 が 8 バンク品（バンク BK0 ~ BK7）の場合の構成を示している。

【0035】

同図に示すように、SDRAM メモリコントローラ 55 は 4 つのバンクグループ BG0 ~ BG3 によって、SDRAM 57 における 8 バンクのオープン / クローズ制御を行っている。すなわち、バンクグループ BG0 はバンク BK0 及びバンク BK4 をペアとし、バンク選択部 70 によって一方をオープン、他方をクローズしている。同様にして、バンクグループ BG1 はバンク BK1 及びバンク BK5 をペアとし、バンク選択部 71 によって一方をオープン、他方をクローズしている。バンクグループ BG2 はバンク BK2 及びバンク BK6 をペアとし、バンク選択部 72 によって一方をオープン、他方をクローズしている。バンクグループ BG3 はバンク BK3 及びバンク BK7 をペアとし、バンク選択部 73 によって一方をオープン、他方をクローズしている。

【0036】

このように、前提技術となる SDRAM メモリコントローラ 55 は、バンクグループ BG0 ~ BG3 で規定されるバンクの組合せを一対としてバンクグループ BG0 ~ BG3 それぞれにおいて一方のバンクのみバンクオープンする仕様としていた。したがって、5 バンク目のバンクアクセス要求がバスアービタ 50 により行われた場合は、バンクグループ BG0 ~ BG3 のうち、5 バンク目にオープンするバンクと対となる他方のバンクが強制的にクローズされていた。

【0037】

（前提技術の問題点）

図 12 及び図 13 で示した前提技術となるバスアービトレーション方式では、通常処理においては、バンクミスしたリクエストを優先してメモリコントローラへ送っていた。アドレスに関するアービトレーションがバンクアドレスのヒットミス判定のみである。

【0038】

しかしながら、バンクミス及びページミスした場合は、SDRAM 57 に対するアクセス時に必ず信号 PRE, ACT を発行するため、SDRAM 57 に十分な性能を発揮させることができないという問題点があった。

【0039】

図 14 で示した SDRAM メモリコントローラのバンク切替方式の場合、8 バンク品の 5 バンク目をオープンにするときにクローズするバンクアドレスは性能に依存してクローズするわけではない。このため、本来はバンクヒットするため信号 PRE, ACT を発行しなくても良い場合にでも、バンクがクローズされてしまっている場合は信号 PRE, ACT を発行しなければならないため、SDRAM へのコマンド発行効率が低下する。

【0040】

上述した問題点の解消を図り、本願発明のリクエスト調停装置であるバスアービタは、SDRAM のコマンド発行順を最適にする事で転送効率を向上させ、かつ許容時間を考慮することを可能にしている。また、本願発明のメモリコントローラは、SDRAM の性能向上を図ることができる。

【0041】

＜実施の形態 1＞

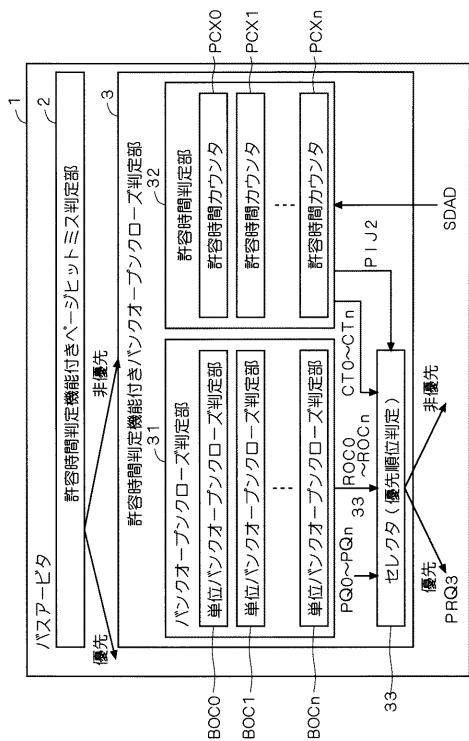

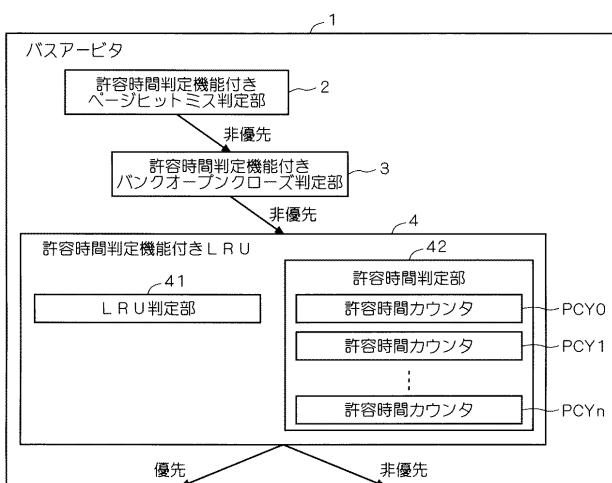

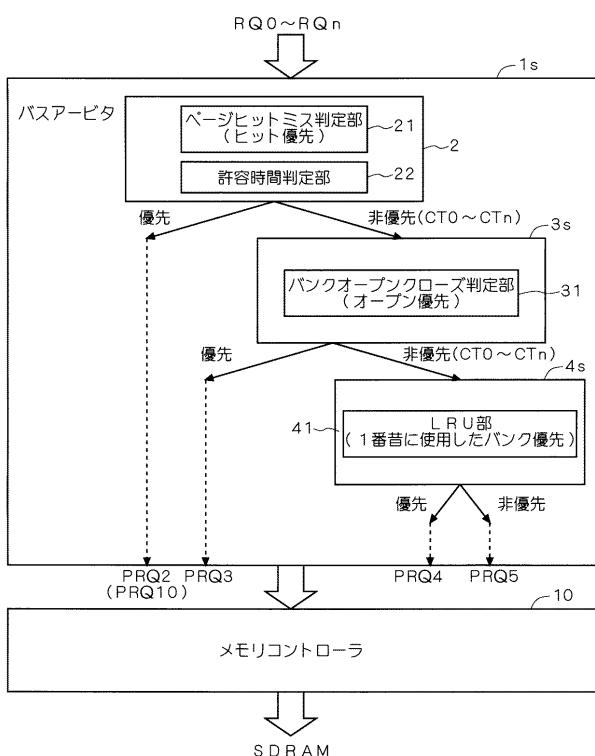

図 1 はこの発明の実施の形態 1 であるリクエスト調停装置であるバスアービタの構成を示すブロック図である。同図に示すように、実施の形態 1 のバスアービタ 1 は、イニシエ

10

20

30

40

50

ータ  $I_{N_1} \sim I_{N_n}$  (図示せず) のリクエスト  $R_{Q_0} \sim R_{Q_n}$  を受ける。バスアービタ 1 は、内部に許容時間判定機能付きページヒットミス判定部 2、許容時間判定機能付きバンクオープンクローズ判定部 3、及び許容時間判定機能付き LRU 部 4 を有している。

【0042】

同図に示すように、リクエスト調停の優先順位はページヒット、バンクオープン、 LRU (Least Recently Used (最も遅く使用されていたバンク)) の順で、 SDRAM に対するバンク優先順位が決定する。さらに、各判定部 2 ~ 4 は内部に許容時間判定部 22, 32, 42 を有しており、後に詳述するように、判定部 2 ~ 4 の優先処理においても、許容時間がカウント閾値  $LVT_{th}$  を下回ったイニシエータのリクエスト  $RQ$  を最優先処理する。

10

【0043】

なお、実施の形態 1 のバスアービタ 1 は、アクセス対象となる所定のメモリである SDRAM は、複数のバンクが割り当てられており、複数のバンクはそれぞれ複数のページ (通常、行アドレスによって割当) が割り当てられていることを前提としている。

【0044】

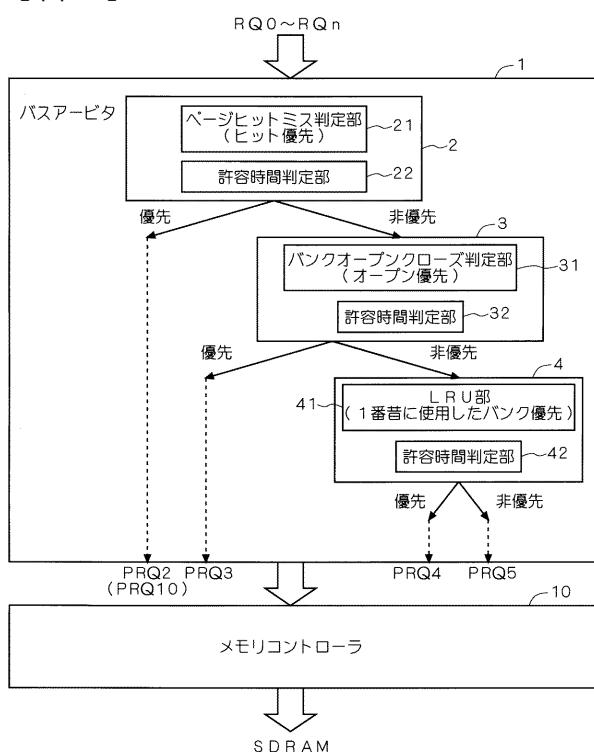

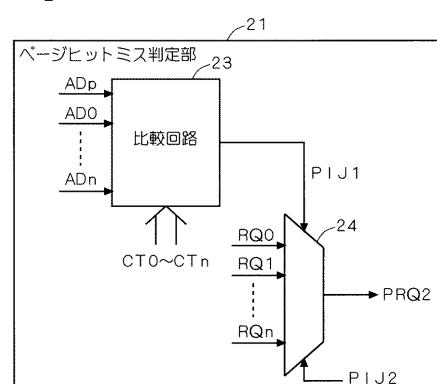

図 2 はバスアービタ 1 における許容時間判定機能付きページヒットミス判定部 2 の内部構成を示すブロック図である。同図に示すように、許容時間判定機能付きページヒットミス判定部 2 はページミスヒット判定部 21 及び許容時間判定部 22 を有している。

20

【0045】

ページミスヒット判定部 21 は前回転送アドレス情報保持部 PAIS、アドレス情報保持部 AIS0 ~ AISn を有している。前回転送アドレス情報保持部 PAIS は、直前にメモリコントローラ 10 に与えた優先リクエスト PRQ における前回転送アドレス ADp (前回アクセスアドレス) を保持している。アドレス情報保持部 AIS0 ~ AISn はイニシエータ  $I_{N_1} \sim I_{N_n}$  から現在発行されているリクエスト  $RQ_0 \sim RQ_n$  における SDRAM へのアクセスアドレスをアドレス情報 AD0 ~ ADn として保持している。

【0046】

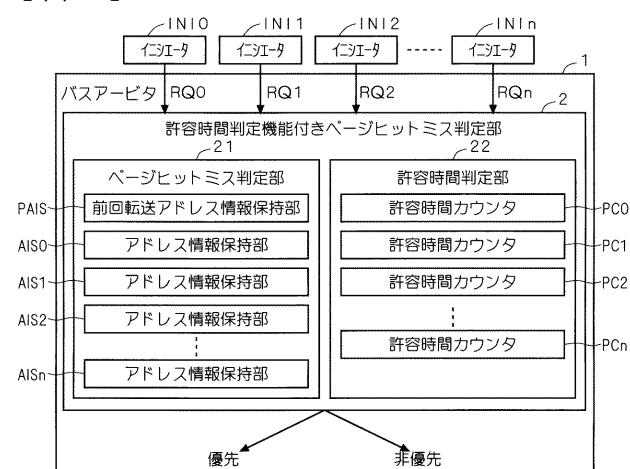

図 3 はページミスヒット判定部 21 の内部構成の内部構成を示す説明図である。なお、図 2 と図 3 とを合わせた構成がページミスヒット判定部 21 の内部構成となる。

【0047】

比較回路 23 は前回転送アドレス情報保持部 PAIS から得られる前回転送アドレス ADp と、アドレス情報保持部 AIS0 ~ AISn から得られるアドレス情報 AD0 ~ ADn と、許容時間判定部 22 の許容時間カウンタ  $PC_0 \sim PC_n$  から得られるカウント値  $CT_0 \sim CT_n$  とを受ける。そして、比較回路 23 は前回転送アドレス ADp とアドレス情報 AD0 ~ ADn とのバンクアドレス及びページアドレスを比較して、アドレス情報 AD0 ~ ADn それぞれのページヒットの有無を判定する。その結果、比較回路 23 はアドレス情報 AD0 ~ ADn のうちページヒットしたアドレスであるページヒットアドレス HAD を認識する。

30

【0048】

さらに、比較回路 23 は、ページヒットアドレス HAD が複数存在する場合は、カウント値  $CT_0 \sim CT_n$  からページヒットアドレス HAD それぞれに対応するカウント値 CT を比較し、カウント値 CT が最も小さいページヒットアドレス HAD を優先ページヒットアドレス PHAD とする。そして、比較回路 23 は、イニシエータ  $I_{N_1} \sim I_{N_n}$  のうち、優先ページヒットアドレス PHAD を含むリクエスト  $RQ$  を発行したイニシエータを優先イニシエータとして指示する優先イニシエータ情報 PIJ1 を出力する。

40

【0049】

セレクタ 24 は、後述する優先イニシエータ情報 PIJ2 が要メモリアクセスイニシエータ無しを指示する場合、リクエスト  $RQ_0 \sim RQ_n$  のうち優先イニシエータ情報 PIJ1 の指示するイニシエータに対応するリクエスト  $RQ$  を優先リクエスト PRQ2 として選択する。

【0050】

50

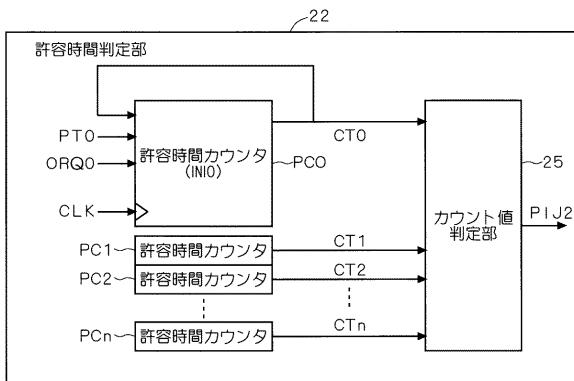

図4は許容時間判定部22の内部構成の詳細を示すブロック図である。同図に示すように、許容時間判定部22は許容時間カウンタPC0～PCn及びカウント値判定部25から構成される。許容時間カウンタPC0～PCnはイニシエータINI0～INI<sub>n</sub>に対応して設けられる。

【0051】

許容時間カウンタPC0はリクエスト実発行情報ORQ0、許容時間情報PT0、及びクロックCLKを受け、カウント値CT0を出力する。なお、リクエスト実発行情報ORQ0とは対応のリクエストRQ0が優先リクエストPRQとして実際にメモリコントローラ10に発行された場合に活性状態となる情報である。許容時間情報PTは図示しないレジスタ等の記憶部にイニシエータINI0～INI<sub>n</sub>それぞれに対応して格納されている許容時間を指示する情報である。

10

【0052】

許容時間カウンタPC0はクロックCLKに同期してカウント値CT0をカウントダウンする。この際、リクエスト実発行情報ORQ0が活性状態になると、許容時間情報PT0で指示された許容時間をカウント値CT0にプラスする。

【0053】

なお、許容時間カウンタPC1～PCnも許容時間カウンタPC0と同様、対応するリクエスト実発行情報ORQ、許容時間情報PTと共に、クロックCLKを受け、カウント値CT1～CTnを出力している。

20

【0054】

このように、許容時間カウンタPC0～PCnでカウントされるカウント値CT0～CTnは、イニシエータINI0～INI<sub>n</sub>の許容時間の残存時間を意味する。したがって、許容時間を考慮した場合、カウント値CTi(i=1～nのいずれか)の小さいイニシエータINIiのリクエストRQiを優先的に処理する方が望ましい。

【0055】

カウント値判定部25はカウント値CT0～CTnを受け、カウント値CT0～CTnとカウント閾値LVthとを比較して、カウント閾値LVthを下回るカウント値CTが存在する場合、当該カウント値CTに対応するイニシエータである要メモリアクセスイニシエータを指示する優先イニシエータ情報PIJ2を出力する。

30

【0056】

一方、カウント値判定部25は、カウント閾値LVthを下回るカウント値CTが存在しない場合は、要メモリアクセスイニシエータ無しを指示する優先イニシエータ情報PIJ2を出力する。

【0057】

図3に戻って、セレクタ24は優先イニシエータ情報PIJ2をさらに受け、優先イニシエータ情報PIJ2が指示する要メモリアクセスイニシエータが存在する場合は、優先イニシエータ情報PIJ1の指示内容に関係なく、優先イニシエータ情報PIJ2の指示する要メモリアクセスイニシエータのリクエストRQを最優先して優先リクエストPRQ2として選択する。

【0058】

このように、実施の形態1のバスアービタ1の許容時間判定機能付きページヒットミス判定部2は、互いに連動して動作するページミスヒット判定部21及び許容時間判定部22を有している。

40

【0059】

ページミスヒット判定部21は、リクエストRQ0～RQnのうちページヒットしたリクエストの中から優先的に優先リクエストPRQ2を決定する。許容時間判定部22は、イニシエータINI0～INI<sub>n</sub>の許容時間の残存時間であるカウント値CT0～CTnがカウント閾値LVth以下に達した要メモリアクセスイニシエータのリクエストを、ページミスヒット判定部21の決定(優先イニシエータ情報PIJ1の指示内容)より優先して優先リクエストPRQ2として決定させることができる。

50

## 【0060】

したがって、実施の形態1のバスアービタ1は、ページヒットしたリクエストを優先することによりSDRAMに対するコマンド(優先リクエスト)の発行効率が向上する効果を得ながら、イニシエータINI0～INI<sub>n</sub>それぞれの許容時間を優先考慮したリクエスト調停を行うことができる。

## 【0061】

また、実施の形態1のバスアービタ1のページミスヒット判定部21における比較回路23は、ページヒットしたリクエストが複数存在した場合、ページヒットしたリクエストに対応するイニシエータのうち、カウント値CT0～CT<sub>n</sub>に基づき許容時間の残存時間がより小さいイニシエータを指示する優先イニシエータ情報PIJ1をセレクタ24に出力している。すなわち、ページミスヒット判定部21の比較回路23及びセレクタ24によって、ページヒットしたリクエストが複数存在した場合、許容時間の残存時間がより小さいリクエストを優先的に優先リクエストPRQ2として決定するページヒット優先処理機能を実現している。

10

## 【0062】

したがって、優先イニシエータ情報PIJ2による要メモリアクセスイニシエータの指示がない場合に実行されるページヒット優先処理時においてもイニシエータINI0～INI<sub>n</sub>の許容時間を考慮したリクエスト調停が行える。

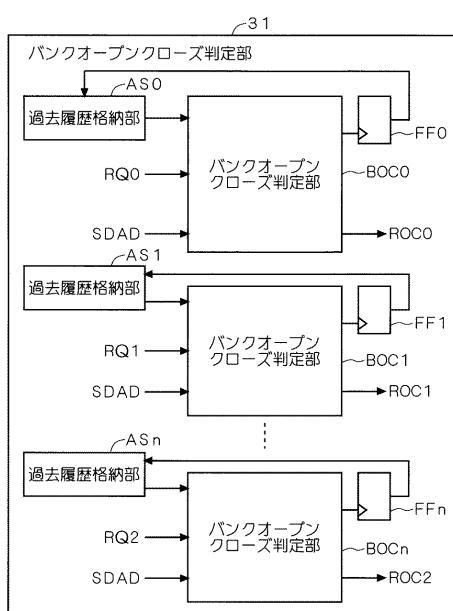

## 【0063】

図5はバスアービタ1における許容時間判定機能付きバンクオープンクローズ判定部3の内部構成を示すブロック図である。同図に示すように、許容時間判定機能付きバンクオープンクローズ判定部3はバンクオープンクローズ判定部31及び許容時間判定部32を有している。許容時間判定機能付きバンクオープンクローズ判定部3は、許容時間判定機能付きページヒットミス判定部2によってページヒットしたリクエストが存在しなかった場合に起動する。

20

## 【0064】

バンクオープンクローズ判定部31はイニシエータINI0～INI<sub>n</sub>に対応してバンクオープンクローズ判定部BOC0～BOC<sub>n</sub>を有している。バンクオープンクローズ判定部BOC0～BOC<sub>n</sub>はリクエストRQ0～RQ<sub>n</sub>のアクセス対象のバンクが現在オープンしているか否かのオープン／クローズ判定を行う。

30

## 【0065】

図6はバンクオープンクローズ判定部31の内部構成の詳細を示す説明図である。同図に示すように、バンクオープンクローズ判定部BOC0～BOC<sub>n</sub>はリクエストRQ0～RQ<sub>n</sub>を受け、共通にSDRAMアドレスSDADを受ける。なお、SDRAMアドレスSDADはSDRAMにアクセスした際のアドレスを意味する。なお、バンクオープンクローズ判定部BOC0～BOC<sub>n</sub>に取り込まれたSDRAMアドレスSDADはフリップフロップFF0～FF<sub>n</sub>を介して過去履歴格納部AS0～AS<sub>n</sub>内に過去履歴情報として所定量蓄積される。すなわち、過去履歴格納部AS0～AS<sub>n</sub>にはそれぞれ過去のSDRAMアドレスSDADの履歴が過去履歴情報として格納される。

30

## 【0066】

バンクオープンクローズ判定部BOCi(i=0～nのいずれか)はリクエストRQiと過去履歴格納部ASiの過去履歴情報を参照して、リクエストRQiの指示するSDRAMへのアクセスバンクがオープン状態であるかクローズ状態であるを判定し、オープン・クローズ判定結果ROC<sub>i</sub>を出力する。

40

## 【0067】

なお、許容時間判定部32の構成及び動作は許容時間判定機能付きページヒットミス判定部2内の許容時間判定部22と同様であるため説明を省略する。なお、許容時間判定部32の許容時間カウンタPCX0～PCX<sub>n</sub>が許容時間カウンタPC0～PC<sub>n</sub>に対応し、許容時間カウンタPCX0～PCX<sub>n</sub>のカウント値CT0～CT<sub>n</sub>及び優先イニシエータ情報PIJ2をセレクタ33に出力する。なお、カウント値CT0～CT<sub>n</sub>及び優先

50

イニシエータ情報 P I J 2 の内容は許容時間判定部 2 2 と同様である。

【 0 0 6 8 】

セレクタ 3 3 はオープン・クローズ判定結果 R O C 0 ~ R O C n と共に、許容時間判定部 3 2 から得られるカウント値 C T 0 ~ C T n 及び優先イニシエータ情報 P I J 2 を受ける。

【 0 0 6 9 】

そして、セレクタ 3 3 は、優先イニシエータ情報 P I J 2 が要メモリアクセスイニシエータを指示しない場合、オープン・クローズ判定結果 R O C 0 ~ R O C n 及びカウント値 C T 0 ~ C T n に基づき、バンクオープン状態を指示するリクエスト R Q のうちカウント値 C T が最も小さいものをリクエスト R Q 0 ~ R Q n から抽出して、優先リクエスト P R Q 3 として選択する。10

【 0 0 7 0 】

一方、セレクタ 3 3 は、優先イニシエータ情報 P I J 2 が要メモリアクセスイニシエータを指示する場合、リクエスト R Q 0 ~ R Q n のうち、優先イニシエータ情報 P I J 2 の指示するリクエスト R Q を最優先に優先リクエスト P R Q 3 として選択する。

【 0 0 7 1 】

このように、実施の形態 1 のバスアービタ 1 における許容時間判定機能付きバンクオープン・クローズ判定部 3 は、互いに連動して動作するバンクオープン・クローズ判定部 3 1 及び許容時間判定部 3 2 を有している。20

【 0 0 7 2 】

バンクオープン・クローズ判定部 3 1 は、各リクエストについてバンクオープンの有無を判定した情報をオープン・クローズ判定結果 R O C 0 ~ R O C n として出力する。許容時間判定部 2 2 は、要メモリアクセスイニシエータを指示する優先イニシエータ情報 P I J 2 をセレクタ 3 3 に与える。20

【 0 0 7 3 】

セレクタ 3 3 は、優先イニシエータ情報 P I J 2 が要メモリアクセスイニシエータを指示する場合、バンクオープン・クローズ判定部 3 1 の決定（オープン・クローズ判定結果 R O C i ）より優先イニシエータ情報 P I J 2 の指示する要メモリアクセスイニシエータのリクエストを優先して優先リクエスト P R Q 3 して決定する。30

【 0 0 7 4 】

一方、セレクタ 3 3 は、優先イニシエータ情報 P I J 2 が要メモリアクセスイニシエータを指示しない場合、バンクオープン・クローズ判定部 3 1 の決定（オープン・クローズ判定結果 R O C i ）に基づき優先リクエスト P R Q 3 を決定する。30

【 0 0 7 5 】

したがって、S D R A M におけるバンクのオープン・クローズ状態を考慮することにより S D R A M に対するコマンド発行効率の向上を図りながら、イニシエータ I N I 0 ~ I N I n それぞれの許容時間を優先的に考慮したリクエスト調停を行うことができる。

【 0 0 7 6 】

また、実施の形態 1 のバスアービタ 1 のセレクタ 3 3 は、バンクオープンと判定したりクエストが複数存在した場合、カウント値 C T 0 ~ C T n に基づき許容時間の残存時間がより小さいイニシエータのリクエストを優先的に優先リクエスト P R Q 3 として決定する。すなわち、許容時間判定機能付きバンクオープン・クローズ判定部 3 は、バンクオープン・クローズ判定部 3 1 及びセレクタ 3 3 によって、ページヒットしたリクエストが複数存在した場合、許容時間の残存時間がより小さいリクエストを優先的に優先リクエスト P R Q 3 として決定するバンクオープン優先処理機能を有している。40

【 0 0 7 7 】

このため、優先イニシエータ情報 P I J 2 が要メモリアクセスイニシエータを指示しない場合に実行されるバンクオープン優先処理時においても複数のイニシエータの許容時間を優先考慮したリクエスト調停が行える。

【 0 0 7 8 】

10

20

30

40

50

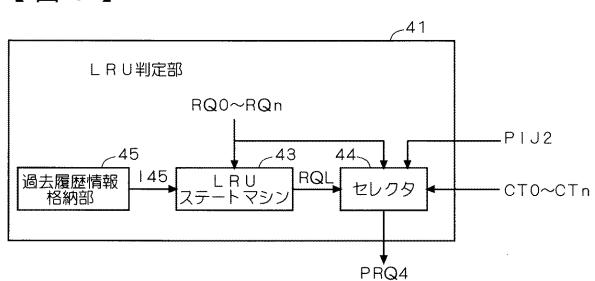

図7はバスアービタ1における許容時間判定機能付きLRU部4の内部構成を示すプロック図である。同図に示すように、許容時間判定機能付きLRU部4はLRU判定部41及び許容時間判定部42を有している。許容時間判定機能付きLRU部4は許容時間判定機能付きバンクオープンクローズ判定部3によってバンクオープンと判定したリクエストが存在しなかった場合に起動する。

【0079】

図8はLRU判定部41の内部構成の詳細を示す説明図である。同図において、過去履歴情報格納部45は過去のSDRAMアドレスSADに基づき、SDRAMに対するバンクアクセス履歴情報を格納している。LRUステートマシン43はリクエストRQ0～RQn及び過去履歴情報格納部45からのバンクアクセス履歴情報I45を受ける。そして、LRUステートマシン43は、バンクアクセス履歴情報I45によって最新アクセス時間が最も古いLRUバンク、すなわち、最も以前にアクセスされたLRUバンクを認識し、当該LRUバンクにバンクアクセスするリクエストRQを指示する情報をLRUリクエスト情報RQLとしてセレクタ44に出力する。

10

【0080】

なお、許容時間判定部42の構成及び動作は許容時間判定機能付きページヒットミス判定部2内の許容時間判定部22と同様であるため説明を省略する。また、許容時間判定部42の許容時間カウンタPCY0～PCYnが許容時間カウンタPC0～PCnに対応し、許容時間カウンタPCY0～PCYnのカウント値CT0～CTn及び優先イニシエータ情報PIJ2をセレクタ44に出力する。なお、カウント値CT0～CTn及び優先イニシエータ情報PIJ2の内容は許容時間判定部22の場合と同様である。

20

【0081】

セレクタ44はリクエストRQ0～RQn及びLRUリクエスト情報RQLと共に、許容時間判定部42から得られるカウント値CT0～CTn及び優先イニシエータ情報PIJ2を受ける。

【0082】

そして、セレクタ44は、優先イニシエータ情報PIJ2が優先イニシエータを指示しない場合、LRUリクエスト情報RQLに基づき、LRUバンクにアクセスするリクエストのうち、カウント値CTが最も小さいリクエストRQをリクエストRQ0～RQnから抽出して、優先リクエストPRQ4として選択する。

30

【0083】

一方、セレクタ44は、優先イニシエータ情報PIJ2が優先イニシエータを指示する場合、LRUリクエスト情報RQLの内容に関係なく、リクエストRQ0～RQnのうち、優先イニシエータ情報PIJ2の指示するリクエストRQを最優先に優先リクエストPRQ4として選択する。

【0084】

また、セレクタ44は、優先イニシエータ情報PIJ2が優先イニシエータを指示せず、LRUバンクにアクセスするリクエストが存在しない場合、単純にカウント値CT0～CTnの最小のリクエストRQをリクエストRQ0～RQnから抽出して、優先リクエストPRQ4として選択する（単純許容時間低下優先処理）。

40

【0085】

このように、実施の形態1のバスアービタ1における許容時間判定機能付きLRU部4は、互いに連動するLRU判定部41及び許容時間判定部42を有している。

【0086】

LRU判定部41は最新アクセス時間が最も古いLRUバンクをアクセスバンクとするリクエストを指示するLRUリクエスト情報RQLを出力する。許容時間判定部42は要メモリアクセスイニシエータを指示する優先イニシエータ情報PIJ2を出力する。LRU判定部41内のセレクタ44は、優先イニシエータ情報PIJ2が要メモリアクセスイニシエータを指示する場合、LRU判定部41の決定（LRUリクエスト情報RQLの指示内容）より優先して要メモリアクセスイニシエータのリクエストを優先リクエストPR

50

Q 4 として出力する。

【0087】

一方、優先イニシエータ情報 P I J 2 が要メモリアクセスイニシエータを指示しない場合、LRU判定部 4 1 の決定 (LRUリクエスト情報 R Q L ) に従い、LRUバンクにアクセスするリクエストを優先的に選択して優先リクエスト P R Q 4 を出力する。

【0088】

したがって、実施の形態 1 のバスアービタ 1 の許容時間判定機能付き LRU 部 4 は、SDRAM の LRU バンクをオープンさせてアクセスすることにより、SDRAM に対するコマンド発行効率の向上を図りながら、イニシエータ I N I 0 ~ I N I n それぞれの許容時間を優先的に考慮したリクエスト調停を行うことができる。

10

【0089】

バスアービタ 1 の許容時間判定機能付き LRU 部 4 の LRU 判定部 4 1 内のセレクタ 4 4 は、LRU リクエスト情報 R Q L が複数の LRU バンクを指示する場合、カウント値 C T 0 ~ C T n に基づき許容時間の残存時間がより小さいリクエストを優先的に優先リクエスト P R Q 4 と決定している。すなわち、LRU 判定部 4 1 は LRU ステートマシン 4 3 及びセレクタ 4 4 によって、LRU バンクへのバンクアクセスするリクエストが複数存在した場合、許容時間の残存時間がより小さいリクエストを優先的に優先リクエスト P R Q 4 として決定する LRU バンク優先処理機能を有している。

【0090】

したがって、実施の形態 1 のバスアービタ 1 は、カウント値 C T 0 ~ C T n を考慮した LRU バンク優先処理機能によって、LRU バンク優先処理時においても複数のイニシエータの許容時間を考慮したリクエスト調停が行える。

20

【0091】

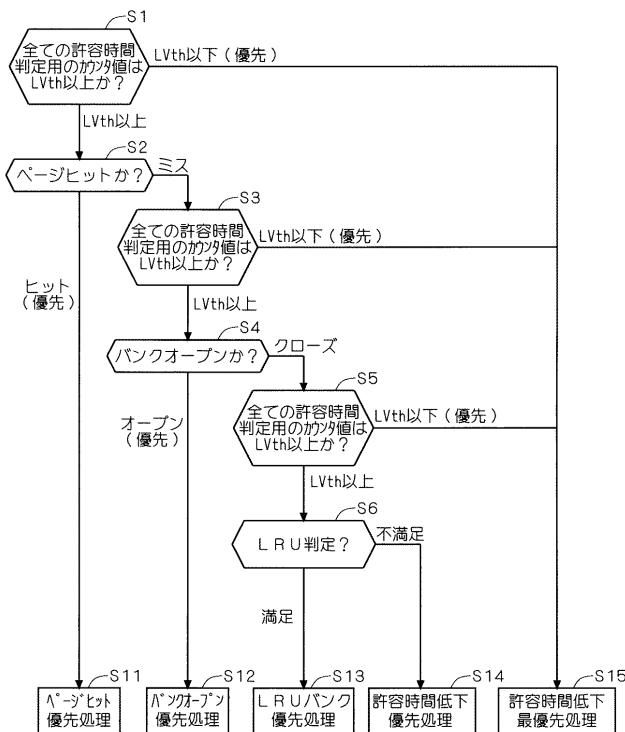

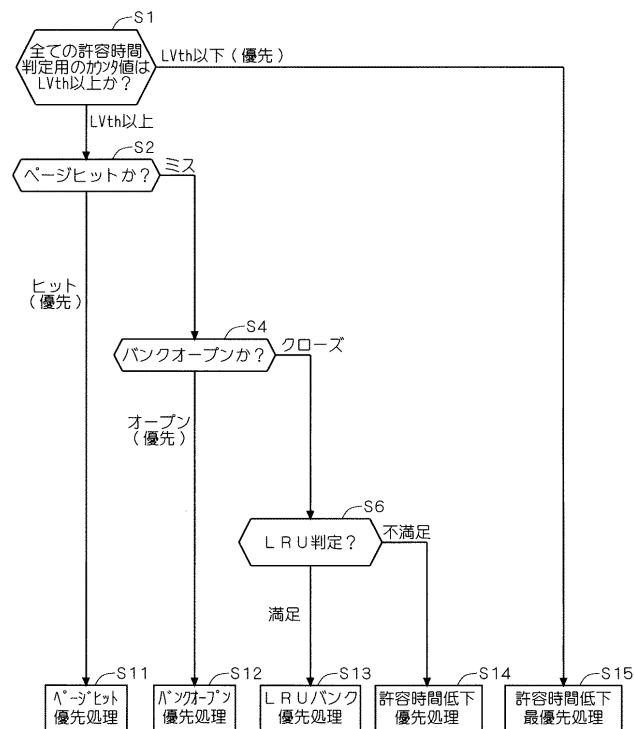

図 9 は図 1 ~ 図 8 で示した実施の形態 1 のバスアービタ 1 のバスアービトトレーション方式の処理手順を示すフローチャートである。以下、同図を参照して、実施の形態 1 のバスアービタ 1 によるバスアービトトレーション方式の処理手順を説明する。

【0092】

まず、ステップ S 1 によって、許容時間判定機能付きページヒットミス判定部 2 により、全ての許容時間判定用のカウント値 C T 0 ~ C T n がカウント閾値 L V t h 以上であるか否かを判定する。

30

【0093】

ステップ S 1 において、カウント閾値 L V t h 以上と判定するとステップ S 2 に移行し、カウント値 C T 0 ~ C T n のうち少なくとも一つにおいてカウント閾値 L V t h 以下と判定するとステップ S 1 5 の許容時間低下最優先処理を行う。

【0094】

ステップ S 1 からステップ S 1 5 に至る処理が、図 4 で示した許容時間判定部 2 2 から優先イニシエータを指示する優先イニシエータ情報 P I J 2 が output された場合、ページミスヒット判定部 2 1 のセレクタ 2 4 によって、優先イニシエータ情報 P I J 2 の指示するイニシエータのリクエスト R Q をリクエスト R Q 0 ~ R Q n から抽出し、優先リクエスト P R Q 2 として選択する処理に相当する。

40

【0095】

ステップ S 2 において、リクエスト R Q 0 ~ R Q n すべてについてページヒットの有無を判定する。すなわち、リクエスト R Q 0 ~ R Q n のうち少なくとも一つのリクエスト R Q がページヒットであると判定すると、ステップ S 1 1 のページヒット優先処理を行い、全リクエスト R Q 0 ~ R Q n がページミスであると判定するとステップ S 3 に移行する。

【0096】

ステップ S 2 からステップ S 1 1 に至る処理が、図 3 で示したページミスヒット判定部 2 1 内のセレクタ 2 4 によって、優先イニシエータ情報 P I J 1 及びカウント値 C T 0 ~ C T n に基づき、優先リクエスト P R Q 2 として選択するページヒット優先処理に相当する。

50

## 【0097】

ステップS3において、許容時間判定機能付きバンクオープンクローズ判定部3により、全ての許容時間判定用のカウント値CT0～CTnがカウント閾値LVth以上であるか否かを判定する。

## 【0098】

ステップS3において、全てのカウント値CT0～CTnがカウント閾値LVth以上と判定するとステップS4に移行し、少なくとも一つのカウント値CTiがカウント閾値LVth以下であると判定するとステップS15の許容時間低下最優先処理を行う。

## 【0099】

ステップS3からステップS15に至る処理が、図5で示した許容時間判定部32から優先イニシエータを指示する優先イニシエータ情報PIJ2が出力された場合、セレクタ33によって、優先イニシエータ情報PIJ2の指示するイニシエータのリクエストRQをリクエストRQ0～RQnから抽出し、優先リクエストPRQ3として選択する処理に相当する。

10

## 【0100】

ステップS4において、全てのリクエストRQ0～RQnに対しバンクオープンの有無を判定し、リクエストRQ0～RQnのうち少なくとも一つのリクエストRQでアクセス対象のバンクがオープン状態であると判定すると、ステップS12のバンクオープン優先処理を行い、全リクエストRQ0～RQnでアクセス対象のバンクがクローズである判定するとステップS5に移行する。

20

## 【0101】

ステップS4からステップS12に至る処理が、図5、図6で示したバンクオープンクローズ判定部31内のセレクタ33によって、オープン・クローズ判定結果ROC0～ROCn及びカウント値CT0～CTnに基づき、リクエストRQ0～RQnから優先リクエストPRQ3を選択するバンクオープン優先処理に相当する。

## 【0102】

ステップS5において、許容時間判定機能付きLRU部4により、全ての許容時間判定用のカウント値CT0～CTnがカウント閾値LVth以上であるか否かを判定する。

## 【0103】

ステップS5において、カウント値CT0～CTnが全てカウント閾値LVth以上と判定するとステップS6に移行し、少なくとも一つがカウント閾値LVth以下と判定するとステップS15の許容時間低下最優先処理を行う。

30

## 【0104】

ステップS5からステップS15に至る処理が、図7で示した許容時間判定部42から優先イニシエータを指示する優先イニシエータ情報PIJ2が出力された場合、セレクタ44によって、優先イニシエータ情報PIJ2の指示するイニシエータのリクエストRQをリクエストRQ0～RQnから抽出し、優先リクエストPRQ4として選択する処理に相当する。

## 【0105】

ステップ6において、LRU判定を行う。すなわち、リクエストRQ0～RQnのうち少なくとも一つのリクエストRQが最も使用されていないバンク（最新アクセス時間が最も古いバンク）にアクセスするリクエストであるか否かを判定する。そして、LRU判定を満足した（LRUバンクである）と判定すると、ステップS13のLRUバンク優先処理を行い、全リクエストRQ0～RQnでLRU判定を満足しないと判定するとステップS14の単純許容時間低下優先処理を実行する。

40

## 【0106】

ステップS6からステップS13に至る処理が、図8で示したLRU判定部41内のセレクタ44が、優先イニシエータ情報PIJ2が優先イニシエータを指示しない場合、LRUリクエスト情報RQLに基づき、LRUバンクにアクセスするリクエストのうち、カウント値CTが最も小さいリクエストRQをリクエストRQ0～RQnから抽出して、優

50

先リクエスト P R Q 4 として選択する処理に相当する。

【0107】

一方、ステップ S 6 からステップ S 14 に至る処理が、図 8 で示した L R U 判定部 41 内のセレクタ 44 によって、優先イニシエータ情報 P I J 2 が優先イニシエータを指示せず、L R U バンクにアクセスするリクエストが存在しない場合、単純にカウント値 C T 0 ~ C T n の最小のリクエスト R Q をリクエスト R Q 0 ~ R Q n から抽出して、優先リクエスト P R Q 4 として選択する処理に相当する。

【0108】

図 17 は実施の形態 1 のバスアービタの他の態様のバスアービトレーション方式の処理手順を示すフロー・チャートである。同図に示すように、ステップ S 3 及びステップ S 5 の処理を省略している。ステップ S 3 およびステップ S 5 は、ステップ S 1 と同内容の処理の繰り返しであるため、図 17 に示すフローのように、ステップ S 3 及びステップ S 5 の処理を省略することができる。すなわち、ステップ S 2 でミス判定した後にステップ S 4 の判定を実行し、ステップ S 4 でクローズ判定した後にステップ S 6 を判定するフローでも良い。

10

【0109】

図 18 は図 17 のフローに対応する実施の形態 1 の他の態様であるバスアービタ 1 s のハードウェア構成を示すブロック図である。同図に示すように、図 1 で示したバスアービタ 1 に対し、図 18 で示したバスアービタ 1 s は、許容時間判定機能付きバンクオープンクローズ判定部 3 を単純バンクオープンクローズ判定部 3 s に、許容時間判定機能付き L R U 部 4 を単純 L R U 部 4 s に置き換えている点が異なる。単純バンクオープンクローズ判定部 3 s はバンクオープンクローズ判定部 3 1 を内部に有し、許容時間判定部 3 2 に相当する構成部を省略している。同様にして、単純 L R U 部 4 s は L R U 判定部 4 1 を内部に有し許容時間判定部 4 2 に相当する構成部を省略している。

20

【0110】

さらに、図 18 に示すバスアービタ 1 s は、許容時間判定部 2 2 の許容時間カウンタ P C 0 ~ P C n から出力されるカウント値 C T 0 ~ C T n を、単純バンクオープンクローズ判定部 3 s 及び単純 L R U 部 4 s に入力する構成を呈している。なお、単純 L R U 部 4 s は単純バンクオープンクローズ判定部 3 s 経由でカウント値 C T 0 ~ C T n を入力している。

30

【0111】

すなわち、許容時間判定部 2 2 で得られたカウント値 C T 0 ~ C T n をバンクオープンクローズ判定部 3 1 および L R U 部 4 1 においても活用している。その結果、図 18 で示したバスアービタ 1 s においても、ステップ S 12 のバンクオープン優先処理、ステップ S 13 の L R U バンク優先処理、及びステップ S 14 の許容時間低下優先処理を支障無く行うことができる。

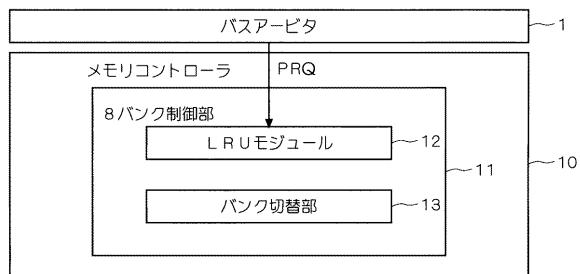

【0112】

< 実施の形態 2 >

図 10 はこの発明の実施の形態 2 であるメモリコントローラ 10 の構成を示す説明図である。実施の形態 2 のメモリコントローラ 10 は実施の形態 1 のバスアービタ 1 に対応し、バスアービタ 1 より得られる優先リクエスト P R Q ( P R Q 2 ~ P R Q 4 のいずれか ) に基づき制御対象となる S D R A M に対しアクセスする。

40

【0113】

なお、メモリコントローラ 10 は制御対象となる S D R A M が 8 バンク構成の場合を前提としている。すなわち、制御対象なる S D R A M は 8 バンクを有し、うち 4 バンク ( 所定数 = 4 ) をオープンできる構成を前提としている。

【0114】

図 10 に示すように、メモリコントローラ 10 は内部に 8 バンク制御部 11 を有し、8 バンク制御部 11 は L R U モジュール 12 及びバンク切替部 13 を備えている。8 バンク制御部 11 は優先リクエスト P R Q がクローズしているバンクにアクセスするリクエスト

50

である場合に、オープン状態の所定数のバンクのいずれかをクローズするバンククローズ制御を行う。

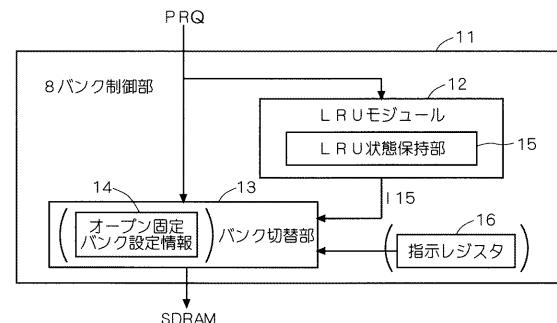

【0115】

図11は8バンク制御部11の詳細を示す説明図である。同図に示すように、優先リクエストPRQはLRUモジュール12及びバンク切替部13に入力される。

【0116】

LRUモジュール12はLRU状態保持部15内に制御対象のSDRAMにおける各バンクの最新アクセス時間を指示するLRUバンク情報I15を格納している。そして、LRUモジュール12は、LRU状態保持部15に格納したLRUバンク情報I15をバンク切替部13に出力する。LRUモジュール12はメモリコントローラ10からSDRAMに発行されるSDRAMアドレスSDAD(図示せず)に基づき、制御対象のSDRAMにおける各バンクの最新アクセス時間を常時更新し、LRUバンク情報I15としてLRU状態保持部15内に保持している。

10

【0117】

バンク切替部13はLRUバンク情報I15、現在、オープンしているバンクのうち、最新アクセス時間が最も古いLRUオープンバンクを認識し、当該LRUオープンバンクをクローズし、優先リクエストPRQの指示するバンクをオープンするバンク切替制御を制御対象のSDRAMに対して行う。

【0118】

実施の形態2のメモリコントローラ10は、オープン許容数を超える5バンク目のバンクをオープンにするためにはいずれかのバンクをクローズする際、SDRAMへのアクセスを向上させるため、LRUバンク情報I15に基づきLRUオープンバンクをクローズさせている。すなわち、メモリコントローラ10は、アクセス時間の古い順にクローズするというクローズバンクの優先順位を決めてバンク切替制御をSDRAMに対して行っている。

20

【0119】

このように、実施の形態2のメモリコントローラ10におけるバンク切替部13は、4個のバンクのいずれかをクローズする際、LRU状態保持部15からのLRUバンク情報I15に基づき、4個のバンクのうち最新アクセス時間が最も古いLRUオープンバンクを優先的にクローズするバンク切替を行っている。

30

【0120】

LRUオープンバンクは使用頻度が低いと推測されるバンクであるため、実施の形態2のメモリコントローラ10は、LRUオープンバンクを優先的にクローズすることにより、使用頻度が高いバンクがオープン状態となる確率が高くなるため、SDRAMの性能向上を図ることができる効果を奏する。

40

【0121】

また、図14で示したSDRAMメモリコントローラ55と比較した場合、バンクグループBG0～BG3によるオープンバンクとクローズバンクとが対となる制約がないマルチ制御が行うことができる。その結果、オープンすべきバンクに制約がない分、先行コマンド処理が実行できるため、SDRAMの転送効率を考慮したコマンドをSDRAMに発行することができる。

【0122】

なお、実施の形態2の第1の変形例として、イニシエータからのアクセスを予め考慮し、常時オープンにするバンクを決める様も考えられる。この場合、予め決定された常時オープンバンクに対し、バンク切替部13はクローズせず常時オープン状態となるように制御する。

【0123】

その結果、予め使用頻度が高いことが認識されている常時オープンバンクへのアクセス効率が向上し、全体としてのアクセス効率が向上する効果が得られる。

【0124】

50

なお、常時オープンバンクをハードウェア固定にする様も考えられる。例えば、図1に示すように、バンク切替部13はオープン固定バンク設定情報14を有し、オープン固定バンク設定情報14で指定されたバンクは常にオープンするように制御するようにしても良い。この場合、オープン固定バンク設定情報14の指示するバンクを常時オープンにしながら、他のオープンバンク内においてLRUオープンバンクをクローズ制御する常時バンクオープン制御を行うことになる。

【0125】

このように、実施の形態2の第1の変形例では、バンク切替部13は、オープン固定バンク設定情報14に従い4個のバンクのうち一部をオープン固定バンクとして常時オープン状態にする常時オープン制御を実行する。したがって、常時オープンするバンクを使用頻度の高いバンクに設定することにより、バンクミスペナルティを少なくして所定のメモリに対するリクエストの発行効率を向上させることができる効果を奏する。

10

【0126】

さらに、実施の形態2の第2の変形例として、常時オープンバンクを設定するか否かを指示する指示レジスタ16を8バンク制御部11内に設け、指示レジスタ16内の指示内容に基づき、オープンバンク固定の採用の有無を決定しても良い。すなわち、バンク切替部13は、指示レジスタ16の指示内容に基づき、全バンクに対してLRUバンクをクローズ制御する全LRU制御を行うか、上記常時バンクオープン制御を行うかを切り替えることができる。

20

【0127】

このように、実施の形態2の第2の変形例では、バンク切替部13は、指示レジスタ16の指示内容に基づき、上記常時オープン制御を行うか否かを切り換える機能を有することにより、状況に応じて常時オープン制御の利用の有無を使い分けることができる。

【0128】

<その他>

実施の形態1のバスアービタ1及び実施の形態2のメモリコントローラ10は、SDRAMを使用するシステムすべてについて適用可能であり、特にSDRAMに対して複数のイニシエータからのリクエストが重なる場合に有効である。

【図面の簡単な説明】

【0129】

30

【図1】この発明の実施の形態1であるバスアービタの構成を示すブロック図である。

【図2】図1で示したバスアービタにおける許容時間判定機能付きページヒットミス判定部の内部構成を示すブロック図である。

【図3】図2で示したページミスヒット判定部の内部構成の内部構成を示す説明図である。

【図4】図2で示した許容時間判定部の内部構成の詳細を示すブロック図である。

【図5】実施の形態1のバスアービタにおける許容時間判定機能付きバンクオープンクローズ判定部の内部構成を示すブロック図である。

【図6】図5で示したバンクオープンクローズ判定部の内部構成の詳細を示す説明図である。

40

【図7】実施の形態1のバスアービタにおける許容時間判定機能付きLRU部の内部構成を示すブロック図である。

【図8】図7で示したLRU判定部の内部構成の詳細を示す説明図である。

【図9】実施の形態1のバスアービタのバスアービトレーション方式の処理手順を示すフローチャートである。

【図10】この発明の実施の形態2であるメモリコントローラの構成を示す説明図である。

【図11】図10で示した8バンク制御部の詳細を示す説明図である。

【図12】この発明の前提技術となるバスアービトレーション方式を示すブロック図である。

50

【図13】許容時間カウンタのカウント動作例を示す説明図である。

【図14】SDRAMメモリコントローラの詳細を示す説明図である。

【図15】従来のバスアービタとその周辺部とのシステム構成を示すブロック図である。

【図16】従来のSDRAMメモリコントローラ及びその周辺を示すブロック図である。

【図17】実施の形態1のバスアービタの他の態様のバスアービトレーション方式の処理手順を示すフローチャートである。

【図18】図17のフローに対応する実施の形態1の他の態様であるバスアービタのハードウェア構成を示すブロック図である。

【符号の説明】

【0130】

10

1, 1s バスアービタ、2 許容時間判定機能付きページヒットミス判定部、3 許容時間判定機能付きバンクオープンクローズ判定部、3s 単純バンクオープンクローズ判定部、4 許容時間判定機能付きLRU部、4s 単純LRU部、10 メモリコントローラ、11~8 バンク制御部、12 LRUモジュール、13 バンク切替部、21 ページミスヒット判定部、22, 32, 42 許容時間判定部、31 バンクオープンクローズ判定部、41 LRU判定部、IN0~INn イニシエータ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図14】

【図13】

【図15】

【図16】

【図17】

【図18】

1s: バスアービタ

3s: 単純パンクオープンクローズ判定部

4s: 単純LRU部