(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3854087号

(P3854087)

(45) 発行日 平成18年12月6日(2006.12.6)

(24) 登録日 平成18年9月15日(2006.9.15)

(51) Int.C1.

F 1

HO3K 19/00

(2006.01)

HO3K 19/00

A

請求項の数 5 (全 14 頁)

(21) 出願番号 特願2001-95302 (P2001-95302)

(22) 出願日 平成13年3月29日 (2001.3.29)

(65) 公開番号 特開2002-300020 (P2002-300020A)

(43) 公開日 平成14年10月11日 (2002.10.11)

審査請求日 平成16年11月26日 (2004.11.26)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100058479

弁理士 鈴江 武彦

(74) 代理人 100084618

弁理士 村松 貞男

(74) 代理人 100092196

弁理士 橋本 良郎

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100070437

弁理士 河井 将次

最終頁に続く

(54) 【発明の名称】電源電位検知回路

## (57) 【特許請求の範囲】

## 【請求項 1】

回路内部で生成した内部電源電位が付与されたソース電極、及び第1の電流制御抵抗を介して接地されたドレイン電極、及び外部電源電位を分割する第1の電源電位分割回路の出力電位を入力するゲート電極を備えた第1のP型MISトランジスタと、

前記外部電源電位が付与されたソース電極、及び第2の電流制御抵抗を介して接地されたドレイン電極、及び前記外部電源電位を分割する第2の電源電位分割回路の出力電位を入力するゲート電極を備えた第2のP型MISトランジスタと、

前記第1のP型MISトランジスタのドレイン電位が入力される第1のインバータ列と、

前記第2のP型MISトランジスタのドレイン電位が入力される第2のインバータ列と、

前記第1及び第2のインバータ列の出力を受けて、前記第2のP型MISトランジスタのドレイン電位がハイレベルであって、前記第1のP型MISトランジスタのドレイン電位がロウレベルのときに、第1レベルの所定の論理信号を出力し、前記第2のP型MISトランジスタのドレイン電位がロウレベルであって、前記第1のP型MISトランジスタのドレイン電位がハイレベルのときに、前記第1レベルを反転した第2レベルの所定の論理信号を出力する論理回路と

を有することを特徴とする電源電位検知回路。

## 【請求項 2】

抵抗 / 容量遅延回路を介して電源電位が付与されたソース電極、及び第 1 の電流制御抵抗を介して接地されたドレイン電極、及び第 1 の電源電位分割回路の出力電位を入力するゲート電極を備えた第 1 の P 型 M I S トランジスタと、

電源電位が付与されたソース電極、及び第 2 の電流制御抵抗を介して接地されたドレイン電極、及び第 2 の電源電位分割回路の出力電位を入力するゲート電極を備えた第 2 の P 型 M I S トランジスタと、

前記第 1 の P 型 M I S トランジスタのドレイン電位を入力する偶数段の第 1 のインバータ列と、

前記第 2 の P 型 M I S トランジスタのドレイン電位を入力する奇数段の第 2 のインバータ列と、

前記第 1 及び第 2 のインバータ列の出力を受ける N O R ゲートと、

を有することを特徴とする電源電位検知回路。

#### 【請求項 3】

前記抵抗 / 容量遅延回路の時定数は、前記第 1 の電源電位分割回路、及び前記第 1 の電流制御抵抗よりも大であることを特徴とする請求項 2 記載の電源電位検知回路。

#### 【請求項 4】

前記抵抗 / 容量遅延回路と前記第 1 の P 型 M I S トランジスタとの間に、ダイオード、又はダイオード接続された M I S トランジスタが挿入されることを特徴とする請求項 2 又は 3 に記載の電源電位検知回路。

#### 【請求項 5】

電源電位が付与されたソース電極、及び直列接続された第 1 、第 2 の抵抗を有する電流制御抵抗を介して接地されたドレイン電極、及び直列接続された第 3 、第 4 の抵抗、又は直列接続された第 1 、第 2 の容量を有する電源電位分割回路の出力電位が入力されたゲート電極を備える P 型 M I S トランジスタと、

前記 P 型 M I S トランジスタのドレイン電極の電位が入力された第 1 のインバータと、

前記 P 型 M I S トランジスタのドレイン電極に直接、又は前記第 1 の抵抗を介して接続されたドレイン電極、及び接地されたソース電極、及び前記第 1 のインバータの出力電位を入力するゲート電極を備える N 型 M I S トランジスタと、

を具備し、

前記第 1 のインバータの出力電位が第 2 のインバータを介して出力されることを特徴とする電源電位検知回路。

#### 【発明の詳細な説明】

##### 【0 0 0 1】

##### 【発明の属する技術分野】

本発明は電位検知回路に係り、特に高速な電源電位の上昇 / 下降を検知する S R A M 、 D R A M 、 E E P R O M 、及び F e R A M (Ferro-electric Random Access Memory) 等の電源電位検知回路に関するものである。

##### 【0 0 0 2】

##### 【従来の技術】

従来の電源電位検知回路には、 P 型 M O S トランジスタのソース電極に電源電位を付与し、電流制御抵抗を介してドレイン電極を接地し、電源電位を抵抗分割する電源電位分割回路の出力電位をゲート電極に入力し、電源電位が所望の値以上になれば P 型 M O S トランジスタがオンすることにより電源電位の上昇を検知し、電源電位が所望の値以下になれば P 型 M O S トランジスタがオフすることにより電源電位の下降を検知するものが知られている。

##### 【0 0 0 3】

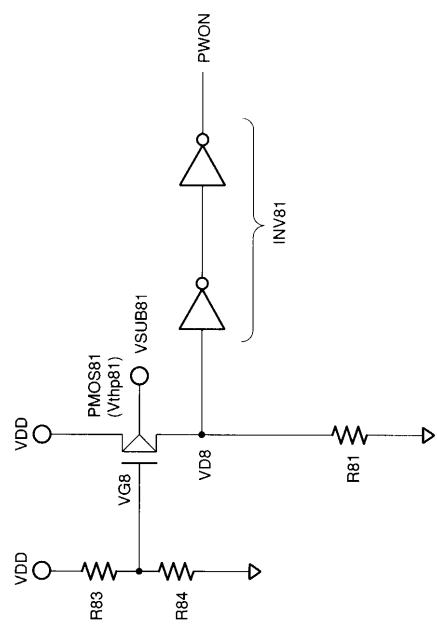

次に、図 8 乃至図 10 を用いて、従来の電源電位検知回路の構成と動作を具体的に説明する。以下、 P 型 M O S トランジスタを P M O S 、 N 型 M O S トランジスタを N M O S と略称する。

図 8 において、 P M O S 8 1 のソース電極は直接電源電位 V D D に接続され、ドレイン電

10

20

30

40

50

極はPMOS81の電流を抑制する電流制御抵抗R81を介して接地される。また、PMOS81のゲート電極には直列に接続された抵抗R83、R84からなる電源電位分割回路を用いて電源電位VDDと接地の間を抵抗分割した電位VG8が入力され、ドレイン電位VD8は2段のインバータからなるインバータ列INV81を介して電源電位検知回路の出力信号PWONとして出力される。電源電位検知回路の出力信号PWONは、半導体記憶装置の制御回路に入力される。なお、VSUB81はPMOS81の基板バイアス電位である。

## 【0004】

次に、電源電位VDDの変化とPMOS81のオン動作、オフ動作との関係について、式(1)、式(2)を用いて詳細に説明する。

$$VDD - VG8 = VDD - VDD \{ R84 / (R83 + R84) \}$$

$$> |Vthp81| \quad \dots (1)$$

$$VDD - VDD \{ R84 / (R83 + R84) \} < |Vthp81| \quad \dots (2)$$

ここで、 $Vthp81 (< 0)$  は PMOS81 (ノーマリオフ型) のしきい値電圧である。

## 【0005】

電源電位VDDがゼロから式(1)で示される範囲の値まで上昇すれば、PMOS81のゲート・ソース間の電位差がしきい値以上になるため、PMOS81はオフ状態からオン状態に変化し、PMOS81のドレイン電位VD8が上昇する。これを2段のインバタ回路INV81を介して出力信号PWONとして出力し、出力信号PWONを後段の回路で受けることにより電源電位VDDの上昇を検知する。

## 【0006】

次に、電源電位VDDが式(2)で示される範囲の値まで下降すれば、PMOS81のゲート・ソース間の電位差がしきい値以下になるため、PMOS81がオン状態からオフ状態に変化し、PMOS81のドレイン電位VD8が下降し、これを2段のインバタ回路INV81を介して出力信号PWONとして出力し、出力信号PWONを後段の回路で受けることにより電源電位VDDの下降を検知する。

## 【0007】

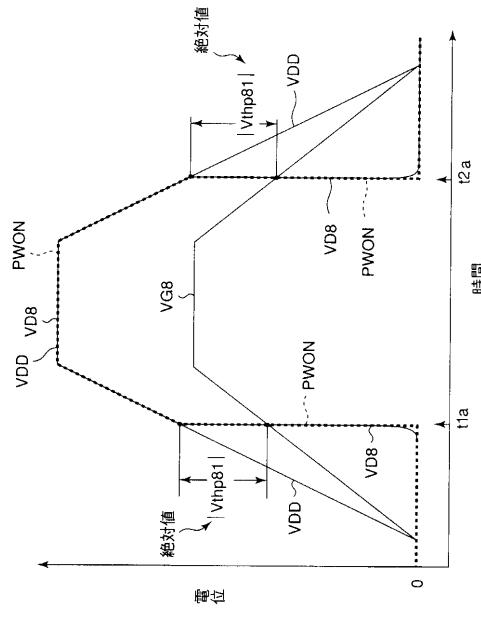

ここで、PMOS81の電流制限抵抗R81の抵抗をR、寄生容量をCとし、電流制限抵抗R81の $R * C$ 時定数を $RC_{81}$ とし、図9及び図10を用いて図8に示す各電位ノードの電位波形について説明する。はじめに、図9を用いて、電源電位VDDが電流制限抵抗の時定数 $RC_{81}$ に比べて十分遅く変化する場合について説明する。

## 【0008】

図9の実線VDDに示すように、電源電位VDDは、ゼロ電位から所定の電位までリニアに上昇し、一定時間所定の電位を維持した後再度ゼロ電位まで下降する台形状の時間変化を示すものとする。このとき図8の電源電位分割回路R83、R84の出力電位VG8は、図9の実線VG8に示すように、電源電位VDDを抵抗分割して得られる台形状の時間変化を示す。

## 【0009】

当初VDD及びVG8は共にゼロ電位であり、図8のPMOS81はノーマリオフ型であるからPMOS81はオフ状態である。PMOS81のドレイン電位VD8は電流制限抵抗R81を介して接地されるので、PMOS81のドレイン電位VD8もまたゼロ電位となる。

## 【0010】

時刻 $t_{1a}$ に達すれば、PMOS81のゲート・ソース間電圧VDD - VG8がPMOS81のしきい値電圧の絶対値 $|Vthp81|$ 以上になるため、PMOS81がオン状態となり、PMOS81のドレイン電位VD8はゼロ電位から高速に時刻 $t_{1a}$ における実線VDDの電位まで上昇する。このVD8の時間変化は、図8のINV81を介して電源電位

10

20

30

40

50

検知回路の出力信号 P W O N となり、図 9 の破線 P W O N に示すように V D 8 の時間変化に沿って出力される。

【 0 0 1 1 】

次に、時刻  $t_{2a}$  になれば PMOS 8 1 のゲート・ソース間電圧 V D D - V G 8 が PMOS 8 1 のしきい値電圧の絶対値  $|V_{thp81}|$  以下になるため、PMOS 8 1 がオフ状態となり、PMOS 8 1 のドレイン電位 V D 8 は時刻  $t_{2a}$  における実線 V D D の電位から電流制限抵抗 R 8 1 の時定数  $R_{C81}$  でゼロ電位まで下降する。

【 0 0 1 2 】

このとき、電源電位 V D D の下降速度が十分に遅ければ、時定数  $R_{C81}$  は無視できるので、PMOS 8 1 のドレイン電位 V D 8 は、時刻  $t_{2a}$  における実線 V D D の電位からゼロまでほぼ垂直に下降する。この V D 8 の時間変化は、図 8 の I N V 8 1 を介して電源電位検知回路の出力信号 P W O N となり、図 9 の破線に示すように V D 8 の時間変化に沿って出力される。

10

【 0 0 1 3 】

このようにして、図 9 に示す電源電位 V D D の時間変化を所定のタイミングで検知し、急峻な上昇 / 下降形状を備えた電源電位検出回路の出力信号 P W O N を得ることができる。P W O N の検知時刻やパルス幅は、電源電位分割回路 R 8 3、R 8 4 の電位分割比及び PMOS 8 1 のしきい値電圧  $V_{thp81}$  の値で定められる。

【 0 0 1 4 】

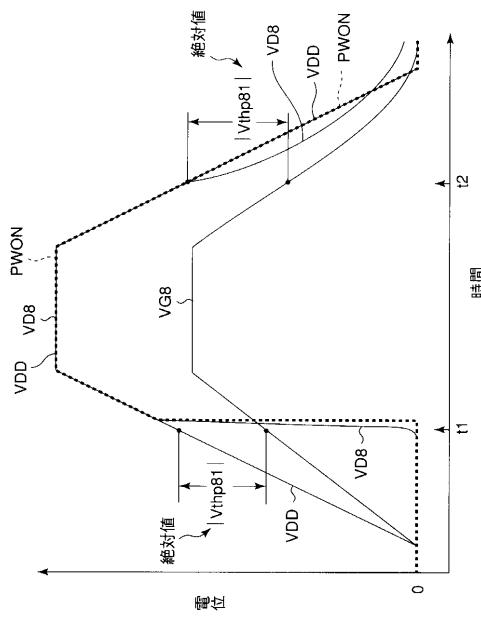

次に、電源電位 V D D の下降時間より電流制限抵抗 R 8 1 の時定数  $R_{C81}$  が長い場合に生じる問題点について説明する。電流制限抵抗 R 8 1 の時定数  $R_{C81}$  が電源電位 V D D の下降時間に比べて長ければ、時刻  $t_{2a}$  において PMOS 8 1 がオフ状態となり、ドレイン電位 V D 8 が、電流制限抵抗 R 8 1 を介して時定数  $R_{C81}$  で接地側に放電し始める際、それより早く電源電位 V D D がゼロ電位に達するので、結果的に電源電位 V D D の変化に対して電位 V D 8 の接地側への放電が追隨できなくなり、時刻  $t_{2a}$  における V D 8 の電位下降の開始時点が検知されないことになる。

20

【 0 0 1 5 】

図 10 を用いて、このときの各電位ノード波形を詳細に説明する。図 10 の電位波形は、高速な V D D の時間変化を見易くするため図 9 に比べて時間軸を拡大して示している。時刻  $t_1$  において PMOS 8 1 がオン状態になれば、PMOS 8 1 の大きなオン電流により、電流制限抵抗 R 8 1 の容量成分が高速に充電される。従って、ドレイン電位 V D 8 が高速に上昇し、図 10 の破線に示すように出力信号 P W O N は電源電位 V D D の上昇を検知することができる。

30

【 0 0 1 6 】

しかし、時刻  $t_2$  において PMOS 8 1 がオフ状態になれば、図 10 の時刻  $t_2$  以降の実線 V D 8 に示すように、PMOS 8 1 のドレイン電位 V D 8 は、時定数  $R_{C81}$  で指數関数的に減衰し、このドレイン電位 V D 8 の緩やかな変化がインバータ列 I N V 8 1 の初段を反転させるしきい値に達しなければ、次段のインバータから出力される出力信号 P W O N は、次段インバータの出力高レベル（通常、V D D に等しい）のままとなる。

【 0 0 1 7 】

従って、図 10 の破線に示す出力信号 P W O N は電源電位 V D D に沿って時間変化する。すなわち、出力信号 P W O N は時刻  $t_2$  における V D D の電位降下を検知することなく V D D の時間変化に沿って変化することになる。

40

【 0 0 1 8 】

このように、電源電位 V D D が高速に下降すれば、PMOS 8 1 のゲート・ソース間の電位差が PMOS 8 1 のしきい値以下になりオフ状態になってしまっても、ドレイン電位 V D 8 は電流制限抵抗 R 8 1 の時定数  $R_{C81}$  のため下降し終わることができず、ゆるやかな下降状態が後段の I N V 8 1 に伝達されないため、電源電位 V D D の下降の検知ができなくなるという問題があった。

【 0 0 1 9 】

10

20

30

40

50

**【発明が解決しようとする課題】**

上記したように、従来の電源電位検知回路は高速な電源電位の上昇を検知することは可能であるが、高速な電源電位の下降を検知することができないという問題があった。

**【0020】**

本発明は上記の問題点を解決すべくなされたもので、高速な電源電位の上昇と同様に、高速な電源電位の下降を検知することができる電源電位検知回路を提供することを目的とする。

**【0021】****【課題を解決するための手段】**

本発明の電源電位検知回路は、高速な電源電位の下降を検知するため、遅延回路を介して第1のPMOSトランジスタのソース電極に電源電位を付与し、ゲート電極に第1の電源電位分割回路の出力を付与することにより、電源電位の下降の際に第1のPMOSトランジスタがオンするように構成し、第1のPMOSトランジスタのオン電流を用いて高速な電源電位の下降を検知する出力信号を発生させることを特徴とする。

10

**【0022】**

一方、高速な電源電位の上昇は、第2のPMOSトランジスタのソース電極に直接電源電位を付与し、ゲート電極に第2の電源電位分割回路の出力を付与することにより、電源電位の上昇の際に第2のPMOSトランジスタがオンするようにし、第2のPMOSトランジスタの大きなオン電流を用いて高速な電源電位の上昇を検知する出力信号を発生させる。

20

**【0023】**

このようにして検知された出力信号を、インバータ列と論理回路を用いて合成すれば、高速な電源電位の上昇と下降を共に検知する電源電位検知回路を提供することができる。

**【0024】**

なお、以上の説明においてPMOS及びNMOSは例示であり、本発明は必ずしもMOSトランジスタに限定されるものではない。本発明は、一般にMISトランジスタ(Metal-Insulator-Semiconductor transistor)に対して同様に適用することができるので、特に請求項及び以下この項において、本発明の説明に例示したPMOSをP型MISトランジスタ、NMOSをN型MISトランジスタと呼ぶ。

30

**【0025】**

具体的には本発明の電源電位検知回路は、少なくとも抵抗/容量遅延回路を介して電源電位が付与されたソース電極、及び電流制御抵抗を介して接地されたドレイン電極、及び電源電位分割回路の出力電位を入力するゲート電極を備えたP型MISトランジスタを有することを特徴とする。

**【0026】**

また、本発明の電源電位検知回路は、第1のP型MISトランジスタと、第2のP型MISトランジスタと、第1のP型MISトランジスタのドレイン電位が入力される第1のインバータ列と、第2のP型MISトランジスタのドレイン電位が入力される第2のインバータ列と、第1及び第2のインバータ列の出力を受けて、第2のP型MISトランジスタのドレイン電位がハイレベルであって、第1のP型MISトランジスタのドレイン電位がロウレベルのときに、第1レベルの所定の論理信号を出力し、第2のP型MISトランジスタのドレイン電位がロウレベルであって、第1のP型MISトランジスタのドレイン電位がハイレベルのときに、第1レベルを反転した第2レベルの所定の論理信号を出力する論理回路とを有することを特徴とする。

40

**【0027】**

また、本発明の電源電位検知回路は、抵抗/容量遅延回路を介して電源電位が付与されたソース電極、及び第1の電流制御抵抗を介して接地されたドレイン電極、及び第1の電源電位分割回路の出力電位を入力するゲート電極を備えた第1のP型MISトランジスタと、電源電位が付与されたソース電極、及び第2の電流制御抵抗を介して接地されたドレイン電極、及び第2の電源電位分割回路の出力電位を入力するゲート電極を備えた第2のP

50

型M I Sトランジスタと、第1のP型M I Sトランジスタのドレイン電位を入力する偶数段の第1のインバータ列と、第2のP型M I Sトランジスタのドレイン電位を入力する奇数段の第2のインバータ列と、第1及び第2のインバータ列の出力を受けるN O Rゲートとを有することを特徴とする。

【0028】

好ましくは、前記抵抗 / 容量遅延回路は、単数又は複数の抵抗と容量との組み合わせ回路を有し、前記電源電位分割回路は、複数の抵抗が直列に接続された抵抗回路、又は複数の容量が直列に接続された容量回路、又は複数の抵抗と容量との組み合わせ回路を有し、前記抵抗 / 容量遅延回路の時定数は、前記電源電位分割回路、及び前記電流制御抵抗よりも大であることを特徴とする。

10

【0029】

また、好ましくは前記抵抗 / 容量遅延回路と前記P型M I Sトランジスタとの間に、ダイオード、又はダイオード接続されたM I Sトランジスタが挿入されることを特徴とする。

【0030】

また、好ましくは前記抵抗 / 容量遅延回路は、直列に接続された複数の抵抗と、前記複数の抵抗の一方の終端部と接地との間、並びに前記複数の抵抗の各接続ノードと接地との間にそれぞれ接続された容量とを具備し、複数の抵抗の一方の終端部には直接電源電位が付与され、各接続ノードにはダイオード、又はダイオード接続されたM I Sトランジスタを介して電源電位が付与され、かつ複数の抵抗の他方の終端部には、P型M I Sトランジスタのソース電極が接続されることを特徴とする。

20

【0031】

また、本発明の電源電位検知回路は、電源電位が付与されたソース電極、及び直列接続された第1、第2の抵抗を有する電流制御抵抗を介して接地されたドレイン電極、及び直列接続された第3、第4の抵抗、又は直列接続された第1、第2の容量を有する電源電位分割回路の出力電位が入力されたゲート電極を備えるP型M I Sトランジスタと、P型M I Sトランジスタのドレイン電極の電位が入力された第1のインバータと、P型M I Sトランジスタのドレイン電極に直接、又は前記第1の抵抗を介して接続されたドレイン電極、及び接地されたソース電極、及び前記第1のインバータの出力電位を入力するゲート電極を備えるN型M I Sトランジスタとを具備し、第1のインバータの出力電位が第2のインバータを介して出力されることを特徴とする。

30

【0032】

【発明の実施の形態】

以下、図面を参照して本発明の実施の形態を詳細に説明する。

<第1実施形態>

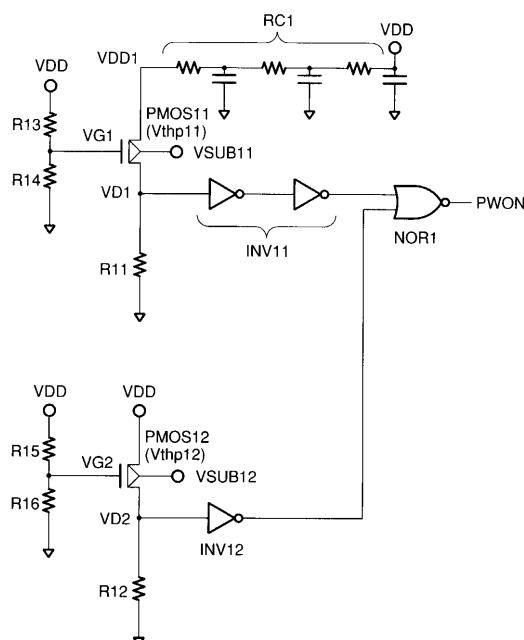

図1は、本発明の第1の実施の形態に係る電源電位検知回路の構成を示す図である。

【0033】

図1において、PMOS11のソース電極は、抵抗と容量からなる遅延回路R C 1を介して電源電位V D Dに接続され、ドレイン電極はPMOS11の電流を絞る電流制御抵抗R 11を介して接地される。また、PMOS11のゲート電極には、直列に接続された抵抗R 13、R 14からなる電源電位分割回路を用いて、電源電位V D Dと接地の間を抵抗分割することにより得られたゲート電位V G 1が入力され、ドレイン電位V D 1は2段のインバータからなるインバータ列INV11を介して2入力N O RゲートN O R 1の一方の入力端子に入力される。

40

【0034】

また、PMOS12のソース電極は直接電源電位V D Dに接続され、ドレイン電極はPMOS12の電流を絞る電流制御抵抗R 12を介して接地される。また、PMOS12のゲート電極には電源電位分割回路R 15、R 16を用いて電源電位V D Dと接地の間を抵抗分割することにより得られたゲート電位V G 2が入力され、ドレイン電位V D 2は1段のインバータINV12を介して、2入力N O RゲートN O R 1の他方の入力端子に入力され、N O R 1の出力端子から電源電位検知回路の出力信号P W O Nが出力される。ここで

50

、PMOS11、PMOS12は、それぞれしきい値電圧  $V_{thp11}$ 、 $V_{thp12}$ （いづれも負の値）のノーマリオフ型トランジスタである。

【0035】

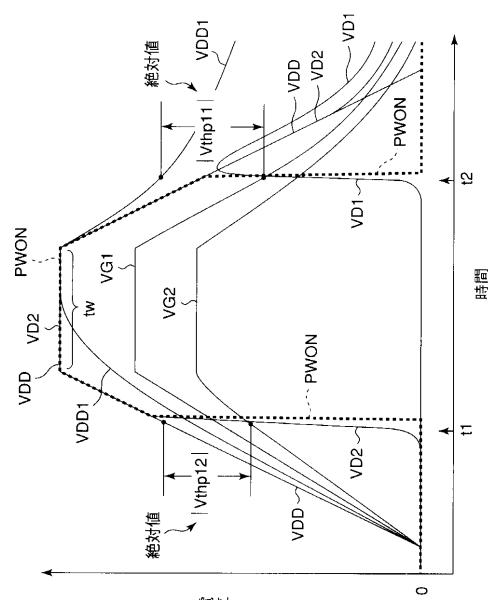

次に図2に示す各電位ノードの電位波形を用いて、第1の実施の形態に係る電源電位検知回路の動作について詳細に説明する。

電源電位  $V_{DD}$  の上昇過程で、電源電位  $V_{DD}$  と電源電位分割回路 R15、R16 から出力されるゲート電位  $V_{G2}$  との差が、時刻  $t_1$  において PMOS12 のしきい値電圧  $|V_{thp12}|$  を越えれば、当初オフ状態であった PMOS12 がオン状態に変化し、ドレイン電位  $V_{D2}$  が、ゼロから実線で示すように  $V_{DD}$  の電位まで高速に上昇する。

【0036】

10

PMOS12 のドレイン電位  $V_{D2}$  は、インバータ  $INV12$  及び NOR ゲート  $NOR1$  を介して、図2の破線で示すように電源電位検知回路の出力信号  $PWON$  として出力される。PMOS12 がオン状態に変化した後の出力信号  $PWON$  の電位は、 $NOR1$  の高レベルが電源電位  $V_{DD}$  に等しければ  $V_{DD}$  に沿って上昇する。このようにして、2入力 NOR ゲート  $NOR1$  の出力端子から電源電位検知回路の出力信号  $PWON$  の高速な立ち上がりが出力される。

【0037】

同様に電源電位  $V_{DD}$  の上昇過程で、当初オフ状態の PMOS11 のゲート電極には、電源電位分割回路 R13、R14 から出力されるゲート電位  $V_{G1}$  が印加されるが、PMOS11 のソース電極は、抵抗と容量からなる遅延回路  $RC1$  を介して電源電位  $V_{DD}$  に接続されるため、PMOS11 のソース電位  $V_{DD1}$  は、電源電位  $V_{DD}$  の上昇から遅延回路  $RC1$  の時定数  $RC1$  だけ遅れて上昇し、電源電位  $V_{DD}$  の平坦部後方（図2の時間幅  $t_w$  の後方）において電源電位  $V_{DD}$  の最大値に達する（ $RC1$  の容量の充電が完了する）ようになる。

20

【0038】

ここで、第1の実施の形態においては、この平坦部における電源電位  $V_{DD}$  の最大値と PMOS11 のゲート電位  $V_{G1}$  との電位差が、PMOS11 のしきい値電圧  $|V_{thp11}|$  を越えないように設定される。このため、電源電位  $V_{DD}$  が最大になる時間幅  $t_w$  を越えても、なお PMOS11 のオフ状態が維持される。

【0039】

30

次に電源電位が急速に下降する場合を考える。先の充電過程で遅延回路  $RC1$  の容量に蓄積された電荷が下降していくのに、 $RC1$  の抵抗が持つ時定数  $RC1$  を要するので、PMOS11 のソース電位  $V_{DD1}$  は、図2に示すように電源電位  $V_{DD}$  の直線的な下降に遅れてゆるやかに下降する。

【0040】

従って、PMOS11 のソース電位  $V_{DD1}$  と、電源電位分割回路 R13、R14 から出力されるゲート電位  $V_{G1}$  との電位差が、PMOS11 のしきい値電圧  $|V_{thp11}|$  を越える時点  $t_2$  で PMOS11 はオン状態となり、ドレイン電位  $V_{D1}$  が高速に上昇する。このようにして、2個のインバータ列  $INV11$  を介して、2入力 NOR ゲート  $NOR1$  の出力端子から電源電位検知回路の出力信号  $PWON$  の高速な立ち下りが出力される。

40

【0041】

第1の実施の形態に係る電源電位検知回路では、PMOS12 がオンすることにより、ドレイン電位  $V_{D2}$  の高速な上昇を介して電源電位  $V_{DD}$  の上昇が検知され、PMOS11 がオンすることによりドレイン電位  $V_{D1}$  の高速な上昇を介して電源電位  $V_{DD}$  の下降が検知される。

【0042】

すなわち、ドレイン電位  $V_{D2}$ 、 $V_{D1}$  の高速な上昇は、それぞれ奇数個のインバータ列からなる  $INV12$ 、偶数個のインバータ列からなる  $INV11$  を介して、2入力の NOR ゲート  $NOR1$  にそれぞれ入力し、 $NOR1$  の出力として電源電位検知回路の出力信号  $PWON$  の高速な立ち上がりと立ち下りが出力される。このようにして、従来困難であつ

50

た電源電位 V D D の下降を高速に検知することが可能になる。

【 0 0 4 3 】

なお、図 1 では I N V 1 1 及び I N V 1 2 がそれぞれ 1 個及び 2 個のインバータからなる場合が示されている。また、第 1 の実施の形態では、電流制限抵抗 R 1 1 の抵抗値と容量成分による  $R * C$  時定数  $R_{C11}$  及び電源電位分割回路 R 1 3、R 1 4 の  $R * C$  時定数  $R_{C13}$  及び  $R_{C14}$  は、いずれも抵抗 / 容量遅延回路の時定数  $R_{C1}$  に比べて小さく、電源電位検知回路の動作に大きな影響を及ぼさないものとしている。

【 0 0 4 4 】

また、第 1 の実施の形態において、電源電位分割回路は複数の抵抗 ( 図 1 では 2 個の抵抗 ) を直列に接続した場合について説明したが、電源電位分割回路は複数の容量を直列に接続しても同様に動作することができる。一般に、電源電位分割回路は複数の抵抗と容量とを結合して形成することが可能である。

【 0 0 4 5 】

< 第 2 実施形態 >

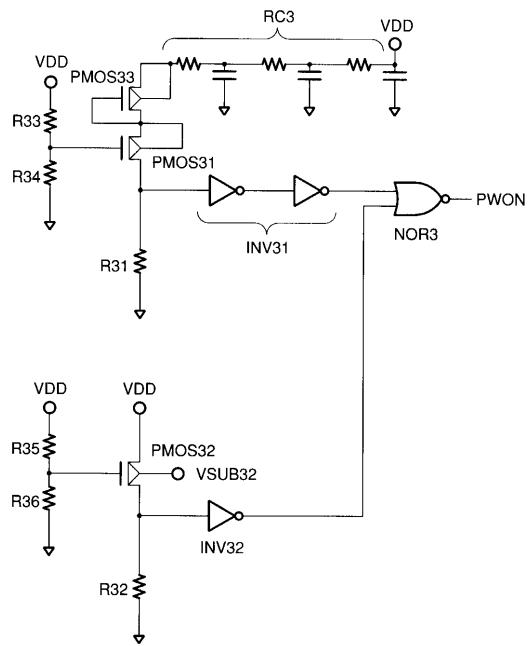

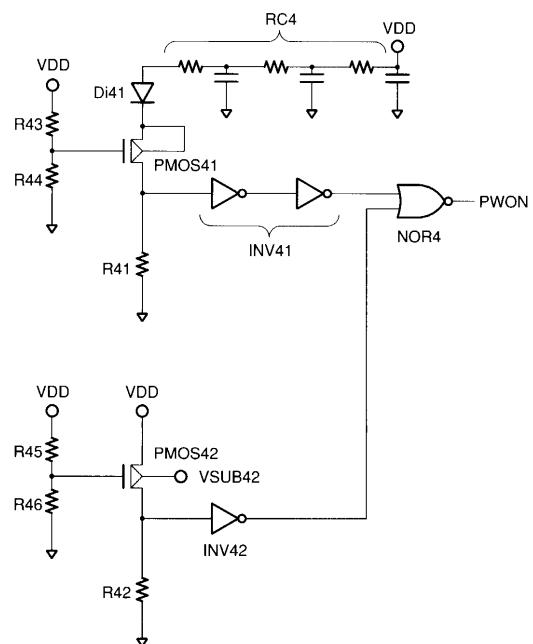

次に、図 3 及び図 4 を用いて第 2 の実施の形態に係る電源電位検知回路の構成と動作について説明する。図 3 及び図 4 に示す電源電位検知回路の構成は、第 1 の実施の形態の変形例であって、抵抗 / 容量遅延回路と P M O S のソース電極との間にダイオード接続された M O S トランジスタ、又はダイオードが接続される他は第 1 の実施の形態と同様であるため、対応する回路要素に対応する符号を付して説明を省略し相違点についてのみ説明する。

【 0 0 4 6 】

図 3 に示す電源電位検知回路は、抵抗 / 容量遅延回路 R C 3 と P M O S 3 1 のソース電極との間に、ゲート・ドレイン電極間が互いに接続されたダイオード接続のノーマリ・オフ型 P M O S 3 3 が、ゲート・ドレイン共通電極を P M O S 3 1 の側に、ソース電極を R C 3 の側にして挿入されることに特徴がある。このように、ダイオード接続された P M O S 3 3 は、ソース電極をアノード側、ゲート・ドレイン共通電極をカソード側とするダイオード特性を示すので、ダイオード特性の順方向電流に対して電位のレベルシフト作用を有する。

【 0 0 4 7 】

先に述べたように、図 3 に示す電源電位検知回路は、P M O S 3 2 がオンすることにより出力信号 P W O N が立ち上がり、P M O S 3 1 がオンすることにより出力信号 P W O N が立ち下がる。従って、ダイオード接続された P M O S 3 3 の電位のレベルシフト作用が P M O S 3 1 のソース側に加わることにより、P M O S 3 2 がオンする ( P W O N が立ち上がる ) V D D の電位と P M O S 3 1 がオンする ( P W O N が立ち下がる ) V D D の電位とを第 1 の実施の形態と異ならせることができる。

【 0 0 4 8 】

このようにして、電源電位検知回路における出力信号 P W O N の形状や出力タイミング設定の自由度を高めることができる。なお、第 2 の実施の形態において、P M O S をダイオード接続する場合について説明したが、N M O S のゲート・ドレイン共通電極をアノード電極としてダイオード接続し、ゲート・ドレイン共通電極を R C 4 の側に、N M O S のソース電極を P M O S 4 1 のソース側にして N M O S を挿入することにより同様な効果を得ることができる。

【 0 0 4 9 】

図 4 に示す電源電位検知回路では、抵抗 / 容量遅延回路 R C 4 と P M O S 4 1 のソース電極との間に、カソード電極を P M O S 4 1 の側に、アノード電極を R C 4 の側にしてダイオード D i 4 1 が挿入される。ダイオード接続された M O S トランジスタの代わりにダイオード自身を用いれば、同様な効果が得られることはいうまでもない。

【 0 0 5 0 】

< 第 3 実施形態 >

次に、図 5 を用いて第 3 の実施の形態について説明する。第 3 の実施の形態では、第 1 、

10

20

30

40

50

第2の実施の形態に係る抵抗/容量遅延回路の変形例について説明する。

【0051】

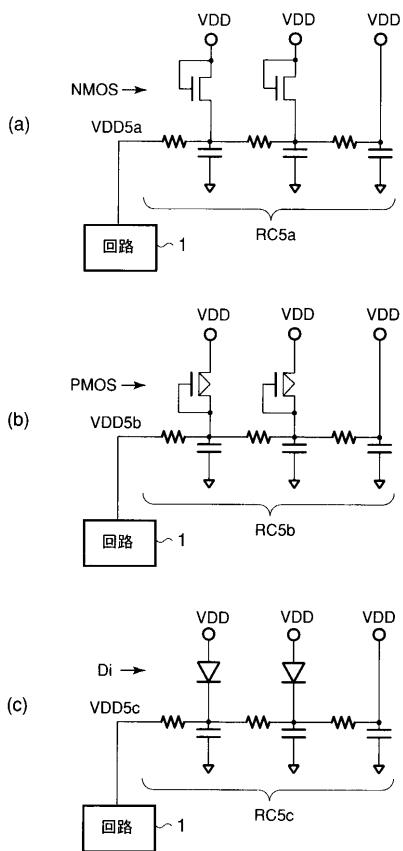

図5(a)は、抵抗/容量遅延回路RC5aを構成する抵抗と容量との各接続ノードに、それぞれダイオード接続されたN MOSを介して電源電位VDDが付与されることに特徴がある。図5(b)では同様に抵抗/容量遅延回路RC5bを構成する抵抗と容量との各接続ノードに、それぞれダイオード接続されたP MOSを介して電源電位VDDが付与される。また、図5(c)では同様に抵抗/容量遅延回路RC5cを構成する抵抗と容量との各接続ノードに、それぞれダイオードを介して電源電位VDDが付与される。なお、図5の回路1は、図1に示す回路から抵抗/容量遅延回路RC1を除去した回路である。

【0052】

このようにすれば、電源電位VDDの上昇の際、ダイオード接続のN MOS、ダイオード接続のP MOS、又はダイオードDiの順方向電流により抵抗/容量遅延回路を構成する各容量が高速にVDD - Vth、又はVDD - Vbi (Vbiはダイオードのビルトイン・ポテンシャル)まで充電されるので、これらの各容量と抵抗との接続ノード、及び図5(a)、図5(b)、図5(c)において、回路1に含まれるP MOS(図1のP MOS11)のソース電位VDD5a、VDD5b、VDD5cは電源電位VDDの上昇に沿って最大電位となる時間幅tw(図2参照)の領域まで上昇する。

【0053】

ここで、ダイオード接続のN MOS、P MOSを用いた時の電源電位VDDからの差分Vth、ダイオードDiを用いたときの電源電位VDDからの差分Vbiは、図5(a)、図5(b)、図5(c)に示すように、遅延回路RC5a、RC5b、RC5cの一方の終端部を直接VDDに接続することで補充され、ほぼVDDの上昇に沿って最大電位に到達することが可能になる。

【0054】

従って、先に図1、図2を用いて説明した、電源電位VDDの上昇過程における、抵抗/容量遅延回路RC1の時定数<sub>RC1</sub>によるP MOS11のソース電位VDD1での電位上昇の遅れが解消し、抵抗/容量遅延回路RC1の容量の充電が完了するまでの待ち時間として必要な時間幅twを、実質的にゼロにすることができます。

【0055】

次に、電源電位VDDの下降過程では、抵抗/容量遅延回路を構成する各容量の蓄積電荷がダイオード接続のN MOS、P MOS、又はダイオードDiを逆バイアスするので、これらの素子は電気的に抵抗/容量遅延回路から切り離され、第1の実施の形態と同様に、電源電位VDDの下降過程でP MOS11をオンさせることで電源電位VDDの下降を検知することができる。

【0056】

このように第3の実施の形態によれば、第1の実施の形態に比べて電源電位VDDの高速な下降を検出するのに必要なVDDの最大値を維持する時間幅twを短縮することができるのに特に高速な電源電位検知回路において、出力信号PWNの形状や出力タイミング設定の自由度をさらに高めることができる。

【0057】

<第4実施形態>

次に、図6、図7を用いて、第4の実施の形態について説明する。第4の実施の形態では、電源電位VDDの上昇と下降を検知するP MOSの他に、特に電源電位VDDの高速な下降の検知能力を高めるためのN MOSからなるフィードバック回路を形成することに特徴がある。

【0058】

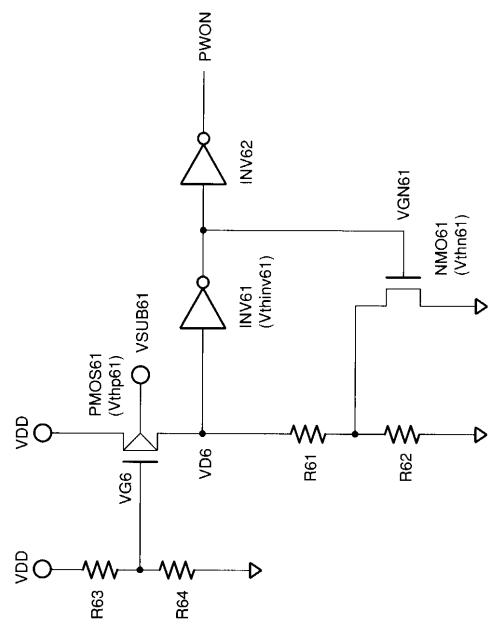

図6に示す電源電位検知回路は、電源電位VDDが直接付与されるソース電極、及び直列接続された抵抗R61、R62からなる電流制御抵抗を介して接地されたドレイン電極、及び直列接続された抵抗R63、R64(又は直列接続された第1、第2の容量)からなる電源電位分割回路の出力がゲート電位VG6として入力されるゲート電極を具備するP

10

20

30

40

50

MOS 61を備えている。

【0059】

PMOS 61のドレイン電位V D 6はインバータINV 61に入力され、インバータINV 61の出力はゲート電位V G N 61としてNMOS 61のゲートに入力される。NMOS 61のドレインは直接PMOS 61のドレインに、又は抵抗R 61を介してPMOS 61のドレインにフィードバックされる。

【0060】

また、NMOS 61のソースは接地され、インバータINV 61の出力電位は、インバータINV 62を介して出力信号PWONとして出力される。ここで、PMOS 61のしきい値電圧をV thp61、インバータINV 61の回路のしきい値電圧をV thinv61、NMOS 61のしきい値電圧をV thn61とする。

10

【0061】

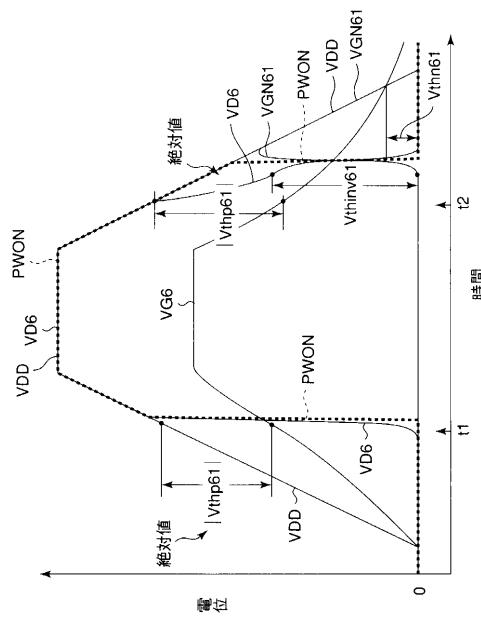

次に、図7を用いて、第4の実施の形態に係る電源電位検知回路の動作を説明する。時刻t<sub>1</sub>において電源電位V DDが所定の値に上昇し、電源電位分圧回路R 63、R 64から出力されるPMOS 61のゲート電位V G 6との電位差がPMOS 61のしきい値電圧|V thp61|を越えれば、PMOS 61がオン状態となり、出力信号PWONを高レベルにすることで電源電位V DDの上昇を検知する。

【0062】

次に、時刻t<sub>2</sub>において電源電位V DDが所定の値まで下降し、PMOS 61のゲート電位V G 6との電位差がPMOS 61のしきい値電圧|V thp61|以下となれば、PMOS 61がオフ状態となりドレイン電位V D 6が下降し始める。図7に示すように、ドレイン電位V D 6がインバータINV 61の回路のしきい値電圧V thinv61より低くなれば、INV 61の出力電位V G N 61が高レベルになり始める。

20

【0063】

NMOS 61のゲートに入力されるV G N 61がNMOS 61のしきい値電圧V thn61を越えれば、NMOS 61がオン状態となり、R 61とR 62との接続点が接地されるので、PMOS 61のドレイン電位V D 6は高速に引き下げられ、破線で示す出力信号PWONを低レベルにすることで、電源電位V DDの高速な下降を検知することができる。

【0064】

このようにすれば、第1乃至第3の実施の形態に係る電源電位検知回路に比べて、抵抗/容量遅延回路を必要とせず、また、他の回路構成も簡略化されるため抵抗列の数が少くなり、電源電位検知回路の低消費電力化とチップ面積の縮小を図ることができる。

30

【0065】

なお本発明は上記の実施の形態に限定されることはない。例えば第2、第3の実施の形態を組み合わせれば、より設計の自由度が高い電源電位検知回路を構成することができる。また、第3の実施の形態において、抵抗/容量遅延回路をR\*Cラダーからなる等価回路で表示し、電源電位V DDが直接付与される終端部を除く各等価容量に、ダイオード接続したMOSトランジスタやダイオードを接続するとして説明した。しかし現実の回路では、図5における回路1との接続点の電位V DD 5a、V DD 5b、V DD 5cは、容量成分を含めてその値が定まるので、回路1との接続点にもダイオード接続したMOSトランジスタやダイオードを接続することが望ましい。その他本発明の要旨を逸脱しない範囲で種々変形して実施することができる。

40

【0066】

【発明の効果】

上述したように本発明の電源電位検知回路によれば、高速な電源電位の上昇と同様に高速な電源電位の下降を検知する電源電位検知回路を提供することが可能になる。

【図面の簡単な説明】

【図1】第1の実施の形態に係る電源電位検知回路の構成を示す図。

【図2】第1の実施の形態に係る電源電位検知回路の動作を示す電位波形図。

【図3】第2の実施の形態に係る電源電位検知回路の構成を示す図。

50

【図4】第2の実施の形態に係る電源電位検知回路の他の構成を示す図。

【図5】第3の実施の形態に係る抵抗/容量遅延回路の構成を示す図であって、

(a)は、ダイオード接続されたN MOSを用いた回路構成を示す図。

(b)は、ダイオード接続されたP MOSを用いた回路構成を示す図。

(c)は、ダイオードを用いた回路構成を示す図。

【図6】第4の実施の形態に係る電源電位検知回路の構成を示す図。

【図7】第4の実施の形態に係る電源電位検知回路の動作を示す電位波形図。

【図8】従来の電源電位検知回路の構成を示す図。

【図9】従来の電源電位検知回路における電源電位の低速変化での動作を示す電位波形図

。

【図10】従来の電源電位検知回路における電源電位の高速変化での動作を示す電位波形図。

【符号の説明】

1 ... 抵抗/容量遅延回路を除く第1の実施の形態に係る回路

R C 1、R C 3、R C 4、R C 5 a、R C 5 b、R C 5 c ... 抵抗/容量遅延回路

I N V 1 1、I N V 3 1、I N V 4 1 ... 偶数段インバータ

I N V 1 2、I N V 3 2、I N V 4 2 ... 奇数段インバータ

I N V 6 1、I N V 6 2 ... インバータ

V thp11、V thp12、V thp61 ... P MOSのしきい値電圧

V thn61 ... N MOSのしきい値電圧

V thinv61 ... I N V 6 1 の回路しきい値電圧

V D D ... 電源電位

P W O N ... 電源電位検知回路の出力信号

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 荻原 隆

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

(72)発明者 伊藤 寧夫

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

(72)発明者 大脇 幸人

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

審査官 宮島 郁美

(56)参考文献 特開2000-058761(JP,A)

特開2000-295094(JP,A)

特開2000-252808(JP,A)

特開平05-022100(JP,A)

特開2002-100973(JP,A)

特開2002-033649(JP,A)

特開2002-100794(JP,A)

特開昭59-198024(JP,A)

特開平09-162712(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K19/00, 19/01-19/082, 19/092-19/096

H03K17/00-17/70