(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6222540号

(P6222540)

(45) 発行日 平成29年11月1日(2017.11.1)

(24) 登録日 平成29年10月13日(2017.10.13)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 29/78  | (2006.01) |

| HO 1 L 21/336 | (2006.01) |

| HO 1 L 29/12  | (2006.01) |

| HO 1 L 29/739 | (2006.01) |

| HO 1 L 21/20  | (2006.01) |

|               |           |

請求項の数 8 (全 36 頁) 最終頁に続く

(21) 出願番号 特願2013-19159 (P2013-19159)

(22) 出願日 平成25年2月4日 (2013.2.4)

(65) 公開番号 特開2014-150211 (P2014-150211A)

(43) 公開日 平成26年8月21日 (2014.8.21)

審査請求日 平成28年2月3日 (2016.2.3)

(73) 特許権者 301041553

株式会社パウデック

栃木県小山市若木町一丁目23番15号

(74) 代理人 100120640

弁理士 森 幸一

(72) 発明者 河合 弘治

神奈川県横浜市旭区市沢町739番地 株式会社パウデック内

審査官 早川 朋一

最終頁に続く

(54) 【発明の名称】絶縁ゲート型電界効果トランジスタの製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の基板上に六方晶系の結晶構造を有する第1の半導体層を成長させる工程と、

上記第1の半導体層を上記第1の基板がエッティングされるまでストライプ状にエッティングすることにより複数のストライプ状のシードを形成する工程と、

上記シードを形成した後の上記第1の基板の表面を六方晶系の結晶構造を有する半導体層が実質的に成長しないように処理する工程と、

それぞれの上記シードから六方晶系の結晶構造を有する第2の半導体層を相互に接触しないように横方向成長させる工程と、

上記第2の半導体層を横方向成長させた後、上記第2の半導体層を覆うように全面に六方晶系の結晶構造を有する第3の半導体層を成長させる工程と、

上記第3の半導体層上に第2の基板を設ける工程と、

上記シード、上記第2の半導体層、上記第3の半導体層および上記第2の基板から上記第1の基板を剥離する工程と、

上記第1の基板を剥離した後、上記第1の基板を剥離することにより露出した上記第2の半導体層および上記第3の半導体層側の剥離面において、上記シードを構成する上記第1の半導体層に接続されたソース電極を形成するとともに、少なくとも上記第2の半導体層および上記第3の半導体層上にゲート絶縁膜を形成する工程と、

上記ゲート絶縁膜上にゲート電極を形成する工程と、

上記ソース電極および上記ゲート電極側に第3の基板を設ける工程と、

10

20

上記第3の半導体層から上記第2の基板を剥離する工程と、

上記第3の半導体層上にドレイン電極を形成する工程とを有し、

上記ソース電極が接続された上記第1の半導体層はソース領域として機能し、上記ドレイン電極が形成された上記第3の半導体層はドレイン領域として機能する絶縁ゲート型電界効果トランジスタの製造方法。

## 【請求項2】

上記六方晶系の結晶構造を有する半導体層が実質的に成長しないように処理する工程が上記第1の基板を酸化または窒化する工程である請求項1記載の絶縁ゲート型電界効果トランジスタの製造方法。

## 【請求項3】

上記シードを形成する工程において、上記第1の基板がエッチングされることにより形成される上記第1の基板からなるストライプ状の柱の断面のアスペクト比が1以上となるまで、または、上記第1の基板からなるストライプ状の柱の高さが4μm以上になるまで上記第1の基板がエッチングされるようにする請求項1または2記載の絶縁ゲート型電界効果トランジスタの製造方法。

## 【請求項4】

上記第1の半導体層は第1の導電型、上記第2の半導体層は第2の導電型、上記第3の半導体層は第1の導電型である請求項1記載の絶縁ゲート型電界効果トランジスタの製造方法。

## 【請求項5】

上記第1の半導体層は第1の導電型、上記第2の半導体層は第2の導電型、上記第3の半導体層のうち最上層の部分は第2の導電型、その他の部分の上記第3の半導体層は第1の導電型である請求項1記載の絶縁ゲート型電界効果トランジスタの製造方法。

## 【請求項6】

上記第1の半導体層は第1の導電型、上記第2の半導体層は第2の導電型、上記第3の半導体層のうち最上層の部分は第1の導電型の半導体層およびその上の第2の導電型の半導体層からなり、その他の部分の上記第3の半導体層は第1の導電型である請求項1記載の絶縁ゲート型電界効果トランジスタの製造方法。

## 【請求項7】

上記第1の半導体層は第1の導電型、上記第2の半導体層は第1の導電型、上記第3の半導体層のうち上記第2の半導体層を覆う部分は第2の導電型、その他の部分は第1の導電型である請求項1記載の絶縁ゲート型電界効果トランジスタの製造方法。

## 【請求項8】

上記第1の半導体層および上記第2の半導体層または上記第1の半導体層、上記第2の半導体層および上記第3の半導体層は窒化物系I—I—V族化合物半導体からなる請求項1～7のいずれか一項記載の絶縁ゲート型電界効果トランジスタの製造方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

この発明は、半導体素子の製造方法、絶縁ゲート型電界効果トランジスタ、絶縁ゲート型電界効果トランジスタの製造方法、半導体発光素子の製造方法および太陽電池の製造方法に関し、例えば、窒化ガリウム(GaN)系半導体を用いた絶縁ゲート型電界効果トランジスタ、半導体発光素子または太陽電池に適用して好適なものである。

## 【背景技術】

## 【0002】

省エネ社会実現のために電気エネルギーの重要性が増しており、21世紀は益々電力に依存しようとしている。電気・電子機器のキーデバイスはトランジスタやダイオードなどの半導体素子である。従って、これらの半導体素子の省エネ性が非常に重要である。現在、電力変換素子はシリコン(Si)半導体素子が担っているが、そのSi半導体素子はほぼその物性限界まで性能向上が図られており、これ以上の省エネ化は難しい状況である。

10

20

30

40

50

## 【0003】

そこで、Siに代えて、シリコンカーバイド(SiC)や窒化ガリウム(GaN)などのワイドギャップ半導体による電力変換素子の研究開発が精力的になされてきている。その中でも、GaNは電力効率性・耐電圧性においてSiCよりも格段に優れた物性値を持つているので、GaN系半導体素子の研究開発が盛んに行われている。

## 【0004】

GaN系半導体素子は、電界効果トランジスタ(FET)型の横型、すなわち、基板に平行に走行チャネルが形成されている構成の素子が開発されている。例えば、サファイアやSiCなどからなるベース基板上にアンドープGaN層が厚さ数μm、その上にAl組成が約25%程度のAlGaN層が厚さ25~30nm程度積層され、AlGaN/GaNへテロ界面に生ずる2次元電子ガス(2DEG)を利用する素子である。この素子は通常はHFET(hetero-junction FET)と呼ばれている。10

## 【0005】

さて、電力変換素子として、現行の絶縁ゲート型バイポーラトランジスタ(IGBT)やパワーMOSトランジスタなどのSiパワー半導体素子から、GaN系半導体素子に置き換えるには、その製造コストが性能に見合うほどに低コストである必要がある。しかしながら、GaN系半導体素子を製造するために、サファイア基板やSiC基板をGaN系半導体成長用基板に用いることは基板コストの面で難しいとされている。

## 【0006】

そこで、Si基板は大口径および低コストであるので、その上のGaN系半導体素子は価格/性能比でSiパワー半導体素子を凌駕できると見られている。20

## 【0007】

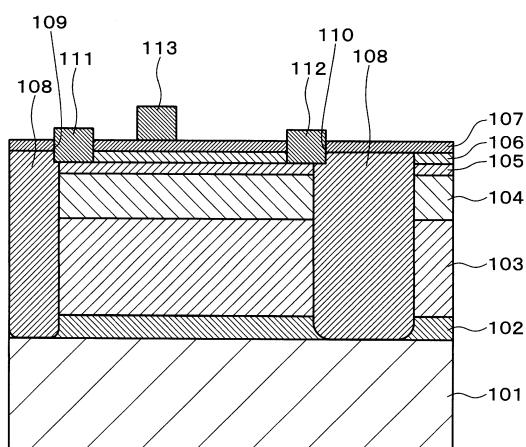

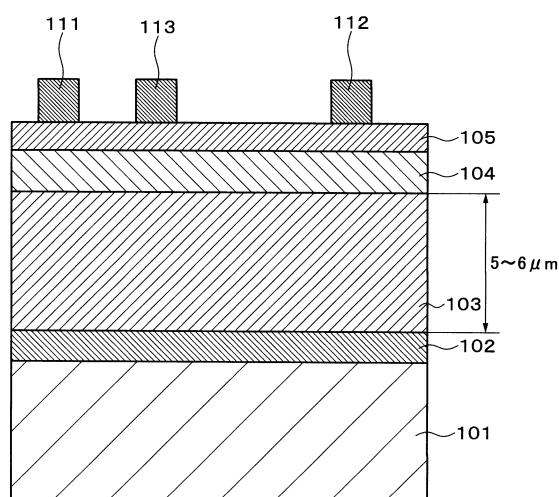

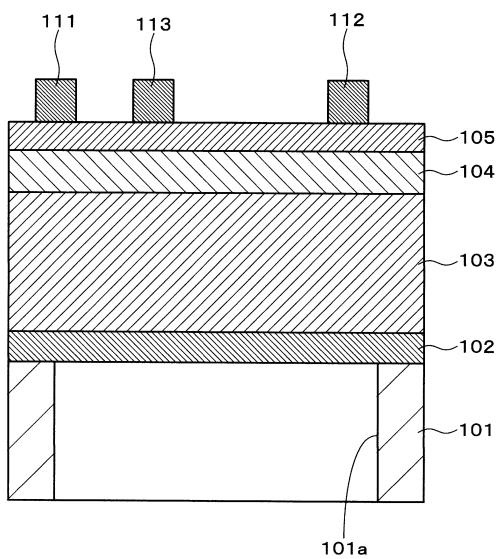

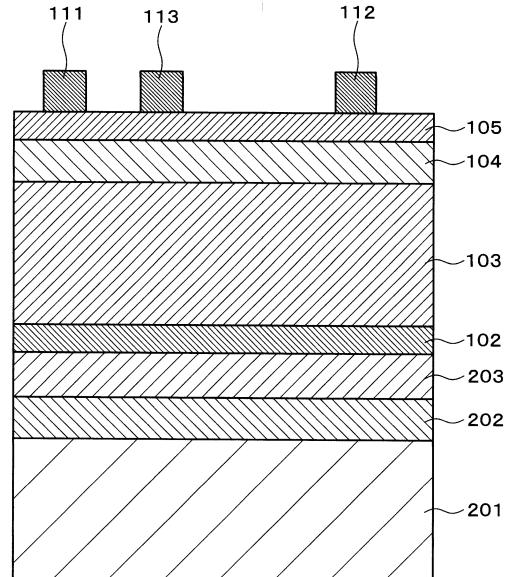

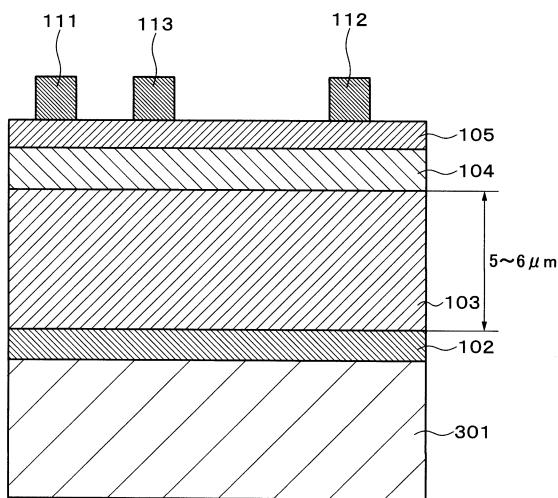

Si基板上に形成された従来のGaN系HFETを図27に示す。Si基板上のGaN系半導体成長技術としては、一般に有機金属化学気相成長(MOCVD)法が用いられている。このGaN系HFETの製造方法は次の通りである。

## 【0008】

図29に示すように、まず、Si(111)基板101上に、AlN膜102を厚さ数10~100nm程度成長させる。このAlN膜102は、後に成長するGaN系半導体層とSi(111)基板101との化学反応を防止するためのものである。

## 【0009】

次に、AlN/GaNまたはAlN/AlGaNのペア、例えば、厚さが5nm/20nmのペアを200層程度(総厚5μm程度)エピタキシャル成長し、バッファ層103を形成する。このバッファ層103は、その上にエピタキシャル成長させるGaN系半導体層の結晶品質を向上させ、反りやクラックなどを阻止するためのものである。30

## 【0010】

次に、バッファ層103上に厚さ1μm程度のGaN層104、厚さ20~30nm程度のAlGaN層105および厚さ5nm程度のGaNキャップ層106を順次エピタキシャル成長させる。

## 【0011】

歪による分極効果によりAlGaN層105とGaN層104との間のAlGaN/GaN界面に2次元電子ガス(2DEG)(図示せず)が自動的に発生し、それが電子チャネルとして用いられる。40

## 【0012】

上述のようにして形成された基板を用いて、以下のようにしてGaN系HFETを製造する。

## 【0013】

まず、GaNキャップ層106上に表面保護膜としてSiN膜やSiO<sub>2</sub>膜などの絶縁膜107を形成する。

## 【0014】

次に、絶縁膜107上に、フォトリソグラフィーにより、素子分離領域形成部に対応す50

る部分に開口を有するレジストパターンを形成した後、このレジストパターンをマスクとして、B(ホウ素)、Ga(ガリウム)、N(窒素)、C(炭素)、Cr(クロム)、Fe(鉄)などの元素をイオン注入することにより、このレジストパターンの開口の部分のAlN膜102、バッファ層103、GaN層104、AlGaN層105およびGaNキャップ層106を高抵抗化し、高抵抗層からなる素子分離領域108を形成する。

#### 【0015】

次に、フォトリソグラフィーにより、ソース電極およびドレイン電極の形成部に対応する部分に開口を有するレジストパターンを形成した後、このレジストパターンをマスクとして絶縁膜107およびGaNキャップ層106を順次エッチングすることにより開口109、110を形成する。

10

#### 【0016】

次に、基板全面にオーミック金属を蒸着した後、リフトオフ法により、レジストパターンをその上に形成されたオーミック金属膜とともに除去する。リフトオフ後には、AlGaN層105上のソース電極およびドレイン電極の形成部に開口109、110と同一形状のオーミック金属膜が残される。この後、オーミック金属膜のオーミック接触特性の改善のために熱処理を施す。こうして、ソース電極111およびドレイン電極112が形成される。

#### 【0017】

次に、絶縁膜107上にゲート電極113を形成する。この後、図示は省略するが、取り出し電極の形成およびその取り出し電極の低抵抗化のためのメッキ処理を行い、最後に表面にSiO<sub>2</sub>膜などの保護膜を形成する。

20

#### 【0018】

Si基板上に形成する上述の従来のGaN系HEMTにおいては、次のような問題がある。

(1) 基板の反りやクラックが発生し、歩留まりが著しく低下する。

(2) GaN系半導体層(AlN膜102、バッファ層103、GaN層104、AlGaN層105およびGaNキャップ層106)の厚さは現実には3~5μmであるが、この厚さでは、ドレイン電極112とSi(111)基板101との間の耐圧が不足しており、耐圧確保のためにGaN系半導体層の厚さをより大きくすると、(1)の問題が生じる。

30

#### 【0019】

(1)、(2)の問題についてより詳細に説明する。GaN(0001)とSi(111)とでは、基板面内の格子定数が互いに約16%異なり、また熱膨張係数差は3×10<sup>-6</sup>/Kと大きい。このため、GaN系半導体層には成長中に非常に大きな応力が発生し、貫通転位が多量に発生する。貫通転位密度は10<sup>9</sup>~10<sup>11</sup>cm<sup>-2</sup>程度で、サファイア基板上に成長させたGaN系半導体層の貫通転位密度よりも一桁大きい。従って、縦方向の耐圧は、このGaN系半導体層中の貫通転位の存在により、物性値から期待されるよりも小さい。Si基板上のGaN系半導体素子では、Si基板とGaN系半導体素子との間の耐圧として例えば1000V程度を確保するには、GaN系半導体層の厚さは5μm程度以上とすることが必要となる。

40

#### 【0020】

Si基板上にGaN系半導体層を成長させた基板で大きな問題は、Siの方がGaN系半導体より熱膨張係数が小さいため、高温から室温に戻るときにGaN系半導体層が収縮し、それによってGaN系半導体層が引っ張り力を受け、凹状に大きく反り、甚だしくはクラックが入ることである。

#### 【0021】

この反りやクラックを緩和するための手法として、AlN(5nm)/GaN(20nm)程度の極薄膜ペアを数100層積層したり、Al組成の異なるAlGaN層を順次積層し、合計3~5μm程度の厚さのバッファ層を形成したりすると、反りやクラックの程度が比較的緩和する。

50

## 【0022】

反りやクラックを低減するためには、バッファ層103、GaN層104、AlGaN層105などの厚さを小さくする必要があるが、それではドレイン電極112とSi(111)基板101との間の耐圧を確保することができない。

## 【0023】

Si基板上にGaN系半導体素子を製造する場合に、耐圧を向上させるための従来の技術としては次のような技術が提案されている。

(1) バッファ層103の厚膜化(非特許文献1~3参照)

(2) 素子直下のSi基板のエッチング(非特許文献4参照)

(3) SOI(Silicon on Insulator)基板上の結晶成長(非特許文献5参照) 10

(4) 絶縁基板の貼り合わせ(非特許文献6、7参照)

## 【0024】

(1) は耐圧向上のための最も一般的な方法である。図28に示すように、バッファ層103として厚さ5~6μm程度の厚いAlN/GaN多層膜を用いる。この厚いAlN/GaN多層膜上に厚さ1.0~1.5μm程度のAlGaN/GaN素子層を形成すると、素子-基板間の耐圧は1.8kV程度まで向上すると言われている。しかしながら、このような厚膜の結晶成長はコスト増加に繋がり採用できない。それどころか、バッファ層103の厚さが増加することにより、ドレイン電極112からSi(111)基板101までの距離が増加するので、電磁気学的な遮蔽効果が薄れ、電流コラプスが増加する。それによって素子性能が低下することになり、実用的ではない。また、基板の反りも大きくなり、歩留まりが低下する。 20

## 【0025】

(2)については、図29に示すように、素子直下のSi(111)基板101をエッチングにより除去して開口101aを形成する。高耐圧となるドレイン電極112の下を含む素子直下のSi(111)基板101を除去することにより、耐圧の向上は期待できるが、実験的にはその効果は報告されていない。除去されていない残りのSi(111)基板101を通じて耐圧が決定されているようであり、更なる工夫がいる。また、一般的に、パワー素子の場合、素子面積が大きく、チップの周辺だけにSi基板が存在することになり、素子作製に困難を生じる可能性がある。 30

## 【0026】

(3)については、図30に示すように、Si基板201上に形成されたSiO<sub>2</sub>膜202上にSi層203を形成したSOI基板上に、AlN膜102、バッファ層103、GaN層104、AlGaN層105などのGaN系半導体層を成長させる。この場合には、SiO<sub>2</sub>膜202が印加電圧のある割合を受け持ち、GaN系半導体層やSi基板201に掛かる電圧を軽減するので、潜在的には耐圧向上が期待できる手法である。しかしながら、SOI基板を用いることはコストの増加や絶縁膜であるSiO<sub>2</sub>膜202による熱伝導性の悪化を招く。 30

## 【0027】

(4)については、図30に示すように、Si基板上にGaN系半導体層を成長させた後にSi基板を何らかの方法で除去し、サファイア基板やガラス基板などの絶縁基板301に貼り合わせる。この方法によれば、高耐圧化は期待できるが、サファイア基板やガラス基板などは熱伝導性が悪く、高出力素子には適用できない。さらに、GaN系半導体層と絶縁基板との貼り合わせについては、直接接合は現状では難しく、間に接着層を介在させる必要があるが、そうすると熱伝導特性をさらに悪化させる。また、GaN系半導体層と絶縁基板との貼り合わせ界面には汚染や欠陥などが存在するため、これがソース電極111とドレイン電極112との間のリーク電流の増加に繋がる可能性が非常に大きく、信頼性の低下および歩留まりの低下に繋がる。 40

## 【先行技術文献】

## 【非特許文献】

## 【0028】 50

【非特許文献 1】W.Huang,T.P.Chow,Y.Niiyama,T.Nomura, and S.Yoshida,"Lateral Implanted RESURF GaN MOSFETs with BV Up to 2.5kV," in Proc.20th ISPSD(2008),291

【非特許文献 2】Selvaraj,S.L.;Suzue,T.;Egawa,T., "Breakdown Enhancement of AlGaN/GaN HEMTs on 4-in silicon by Improving the GaN Quality on Thick Buffer Layers" IEDM Electron Device Letters,30, No.6, (2009)587

【非特許文献 3】Rowena,I.B.;Selvaraj,S.L.;Egawa,T., "Buffer Thickness Contribution to Suppress Vertical Leakage Current With High Breakdown Field(2.3MV/cm) for GaN on Si" Electron Device Letters,32, No.11, (2011)1534

【非特許文献 4】Srivastava,P.;Das,J.;Visalli,D.;Van Hove,M.;Malinowski,P.E.;Marcon,D.;Lenci,S.;Geens,K.;Kai Cheng;Leys,M.;Decoutere,S.;Mertens,R.P.,Borghs,G., "Record Breakdown Voltage(2200V)of GaN DHFETs on Si With 2-um Buffer Thickness by Local Substrate Removal" Electron Device Letters,32, No.1, (2011)p.30

【非特許文献 5】S.Tripathy,L.S.Wang,S.J.Chua,"Characterization of GaN layers grown on silicon-on-insulator substrates"Applied Surface Science,253(2006)236-240

【非特許文献 6】Srivastava,P.;Das,J.;Visalli,D.;Derluyn,J.;Van Hove,M.;Malinowski,P.E.;Marcon,D.;Geens,K.;Kai Cheng;Degroote,S.;Leys,M.;Germain,M.;Decoutere,S.;Mertens,R.P.,Borghs,G., "Silicon Substrate Removal of GaN DHFETs for Enhanced( < 1100V) Breakdown voltage",Electron Device Letters,31, No.8, (2010)p.851

【非特許文献 7】Bin Lu; Palacios,T., "High Breakdown(1500V)AlGaN/GaN HEMTs by Substrate-Transfer Technology",Electron Device Letters,31, No.9, (2010)p.951

### 【発明の概要】

#### 【発明が解決しようとする課題】

##### 【0029】

以上のように、現在提案されている技術では、Si基板を用いて高耐圧高出力のGaN系半導体素子を高歩留まりで製造する最適な技術は提案されていない。

##### 【0030】

この発明は、従来技術が有する上記の課題を一挙に解決することを目的とする。

##### 【0031】

すなわち、この発明が解決しようとする課題は、Si基板を用いて高耐圧高出力の半導体電子素子、半導体発光素子、半導体受光素子などの各種の半導体素子を容易に製造することができる半導体素子の製造方法を提供することである。

この発明が解決しようとする他の課題は、Si基板を用いて高耐圧高出力の絶縁ゲート型電界効果トランジスタを容易に製造することができる絶縁ゲート型電界効果トランジスタの製造方法およびこの製造方法により製造することができる絶縁ゲート型電界効果トランジスタを提供することである。

##### 【0032】

この発明が解決しようとする他の課題は、Si基板を用いて高耐圧高出力の半導体発光素子を容易に製造することができる半導体発光素子の製造方法を提供することである。

##### 【0033】

この発明が解決しようとする他の課題は、Si基板を用いて高耐圧高出力の太陽電池を容易に製造することができる半導体発光素子の製造方法を提供することである。

#### 【課題を解決するための手段】

##### 【0034】

上記課題を解決するために、この発明は、

第1の基板上に六方晶系の結晶構造を有する第1の半導体層を成長させる工程と、

上記第1の半導体層を上記第1の基板がエッティングされるまでストライプ状にエッティングすることにより複数のストライプ状のシードを形成する工程と、

上記シードを形成した後の上記第1の基板の表面を六方晶系の結晶構造を有する半導体層が実質的に成長しないように処理する工程と、

それぞれの上記シードから六方晶系の結晶構造を有する第2の半導体層を横方向成長さ

10

20

30

40

50

せる工程とを有する半導体素子の製造方法である。

この半導体素子の製造方法は、典型的には、例えば、第2の半導体層を横方向成長させた後、第2の半導体層上に第2の基板を設ける工程と、シード、第2の半導体層および第2の基板から第1の基板を剥離する工程とをさらに有する。あるいは、この半導体素子の製造方法は、例えば、第2の半導体層を横方向成長させた後、第2の半導体層を覆うように全面に六方晶系の結晶構造を有する第3の半導体層を成長させる工程と、第3の半導体層上に第2の基板を設ける工程と、シード、第2の半導体層、第3の半導体層および第2の基板から第1の基板を剥離する工程とをさらに有する。第2の半導体層および第3の半導体層には、導電型が互いに同一または互いに異なる一種類または複数種類の半導体層が含まれる。一つの例では、第1の半導体層を成長させた後、シードを形成する前に、第1の半導体層上に絶縁膜を形成し、この絶縁膜および第1の半導体層を第1の基板がエッチングされるまでストライプ状にエッチングすることによりシードを形成する。必要に応じて、シード上にこの絶縁膜を残した状態で第2の半導体層を横方向成長させてもよい。あるいは、例えば、シードを形成する工程において、第1の基板が1 μm以上の深さにエッチングされるようにする。こうすることで、例えば、第1の基板の剥離（分離）の際にエッチング液が浸透する隙間が作られ、エッチングされやすくなる。また、典型的には、六方晶系の結晶構造を有する半導体層が実質的に成長しないように処理する工程は、第1の基板を酸化または窒化する工程である。あるいはまた、シードを形成する工程において、第1の基板がエッチングされることにより形成される第1の基板からなるストライプ状の柱の断面のアスペクト比（柱の高さ / 柱の幅）が1以上となるまで、または、第1の基板からなるストライプ状の柱の高さが4 μm以上になるまで第1の基板がエッチングされるようにする。こうすることで、第1の基板からなるストライプ状の柱が割れて、素子を構成する半導体層にクラックなどが入るのを防止する効果を得ることができる。好適には、シード、第2の半導体層および第2の基板から第1の基板を剥離する工程、あるいは、シード、第2の半導体層、第3の半導体層および第2の基板から第1の基板を剥離する工程は、第1の基板をウェットエッチングする工程である。こうすることで、第2の半導体層あるいは第3の半導体層にほとんど損傷を与えることなく、第1の基板を剥離（分離）することができる。

半導体素子は、基本的にはどのようなものであってもよいが、例えば、半導体電子素子、半導体発光素子、半導体受光素子などである。半導体電子素子は、例えば、絶縁ゲート型電界効果トランジスタ、超接合絶縁ゲート型電界効果トランジスタ、フィールドストップ絶縁ゲート型バイポーラトランジスタ、超接合絶縁ゲート型電界効果トランジスタとフィールドストップ絶縁ゲート型バイポーラトランジスタとの複合素子、ショットキーバリアダイオード（SBD）、pn接合ダイオードなどである。

半導体素子が半導体発光素子（例えば、半導体レーザや発光ダイオードなど）あるいは半導体受光素子（太陽電池やフォトダイオードなど）である場合、例えば、第2の半導体層には、少なくとも1層以上のn型半導体層と少なくとも1層以上のp型半導体層とが含まれ、上記のn型半導体層に接続されてカソード電極が設けられ、上記のp型半導体層に接続されてアノード電極が設けられる。半導体素子がショットキーバリアダイオードである場合、例えば、第3の半導体層には、少なくとも1層以上のノンドープまたはn<sup>-</sup>型半導体層と少なくとも1層以上のn型半導体層（n型コンタクト層）とが含まれ、第3の半導体層のうち第1の半導体層および第2の半導体層側の面のノンドープまたはn<sup>-</sup>型半導体層に接続されてショットキー電極が設けられ、第3の半導体層のうち第1の半導体層および第2の半導体層と反対側の面のn型半導体層に接続されてオーミック電極が設けられる。あるいは、半導体素子がショットキーバリアダイオードである場合、例えば、第2の半導体層には、少なくとも1層以上のp型またはp<sup>-</sup>型半導体層が含まれ、第3の半導体層には、少なくとも1層以上のノンドープまたはn<sup>-</sup>型半導体層と少なくとも1層以上のn型半導体層（n型コンタクト層）とが含まれ、第3の半導体層のうち、第1の半導体層および第2の半導体層側の面および第2の半導体層のp型またはp<sup>-</sup>型半導体層に接続されてショットキー電極が設けられ、第3の半導体層のうち、第1の半導体層および第2の

10

20

30

40

50

半導体層と反対側の面の n 型半導体層に接続されてオーミック電極が設けられる。半導体素子が絶縁ゲート型電界効果トランジスタ (MOSFET) である場合、例えば、第 1 の半導体層には、少なくとも 1 層以上の n 型半導体層が含まれ、第 2 の半導体層には、少なくとも 1 層以上の p 型半導体層が含まれ、第 3 の半導体層には、少なくとも 1 層以上のノンドープまたは n<sup>-</sup> 型半導体層と少なくとも 1 層以上の n 型半導体層 (n 型コンタクト層) とが含まれ、第 1 の半導体層の n 型半導体層に接続されてソース電極が設けられ、第 2 の半導体層の p 型半導体層上に絶縁膜を介してゲート電極が設けられ、第 3 の半導体層の n 型半導体層に接続されてドレイン電極が設けられる。また、半導体素子が絶縁ゲート型電界効果トランジスタあるいは超接合絶縁ゲート型電界効果トランジスタである場合、例えば、第 1 の半導体層には、少なくとも 1 層以上の n 型半導体層が含まれ、第 2 の半導体層には、少なくとも 1 層以上の p 型半導体層と少なくとも 1 層以上の p<sup>-</sup> 型半導体層が含まれ、第 3 の半導体層には、少なくとも 1 層以上のノンドープまたは n<sup>-</sup> 型半導体層と少なくとも 1 層以上の n 型半導体層とが含まれ、第 1 の半導体層の n 型半導体層に接続されてソース電極が設けられ、第 2 の半導体層の p 型半導体層および p<sup>-</sup> 型半導体層上に絶縁膜を介してゲート電極が設けられ、第 3 の半導体層の n 型半導体層に接続されてドレイン電極が設けられる。半導体素子が超接合絶縁ゲート型電界効果トランジスタである場合、例えば、第 1 の半導体層には、少なくとも 1 層以上の n 型半導体層が含まれ、第 2 の半導体層には、少なくとも 1 層以上の p 型半導体層と少なくとも 1 層以上の p<sup>-</sup> 型半導体層とが含まれ、第 3 の半導体層には、少なくとも 1 層以上のノンドープまたは n<sup>-</sup> 型半導体層と少なくとも 1 層以上の n 型半導体層 (n 型コンタクト層) とが含まれ、第 1 の半導体層の n 型半導体層に接続されてソース電極が設けられ、第 2 の半導体層の p 型半導体層および p<sup>-</sup> 型半導体層上に絶縁膜を介してゲート電極が設けられ、第 3 の半導体層の n 型半導体層に接続されてドレイン電極が設けられ、第 2 の半導体層の p 型半導体層および p<sup>-</sup> 型半導体層の厚さを A、第 3 の半導体層の上記ノンドープまたは n<sup>-</sup> 型半導体層の厚さを B としたとき、A / B が 0.5 以上 1 未満である。半導体素子がフィールドストップ絶縁ゲート型バイポーラトランジスタである場合、例えば、第 1 の半導体層には、少なくとも 1 層以上の n 型半導体層が含まれ、第 2 の半導体層には、少なくとも 1 層以上の p 型半導体層が含まれ、第 3 の半導体層には、少なくとも 1 層以上のノンドープまたは n<sup>-</sup> 型半導体層と少なくとも 1 層以上の n 型半導体層 (フィールドストップ層) および少なくとも 1 層以上の p 型半導体層が含まれ、第 1 の半導体層の n 型半導体層に接続されてソース電極が設けられ、第 2 の半導体層の p 型半導体層上に絶縁膜を介してゲート電極が設けられ、第 3 の半導体層の p 型半導体層に接続されてドレイン電極が設けられる。半導体素子が超接合絶縁ゲート型電界効果トランジスタとフィールドストップ絶縁ゲート型バイポーラとの複合素子である場合、例えば、第 1 の半導体層には、少なくとも 1 層以上の n 型半導体層が含まれ、第 2 の半導体層には、少なくとも 1 層以上の p 型半導体層と少なくとも 1 層以上の p<sup>-</sup> 型半導体層とが含まれ、第 3 の半導体層には、少なくとも 1 層以上のノンドープまたは n<sup>-</sup> 型半導体層と少なくとも 1 層以上の n 型半導体層 (フィールドストップ層) および少なくとも 1 層以上の p 型半導体層が含まれ、第 1 の半導体層の n 型半導体層に接続されてソース電極が設けられ、第 2 の半導体層の p 型半導体層および p<sup>-</sup> 型半導体層上に絶縁膜を介してゲート電極が設けられ、第 3 の半導体層の p 型半導体層に接続されてドレイン電極が設けられ、第 2 の半導体層の p 型半導体層および p<sup>-</sup> 型半導体層の厚さを A、第 3 の半導体層の n<sup>-</sup> 型半導体層の厚さを B としたとき、A / B が 0.5 以上 1 未満である。

第 1 の基板は、基本的にはどのようなものであってもよいが、好適には、Si 基板である。第 1 の半導体層、第 2 の半導体層および第 3 の半導体層は、基本的にはどのような半導体からなるものであってもよいが、典型的には、窒化物系 II - V 族化合物半導体からなる。あるいは、第 1 の半導体層、第 2 の半導体層および第 3 の半導体層は、B、Al、Ga および In からなる群より選ばれた少なくとも 1 種類以上の II - V 族元素と N、P および As からなる群より選ばれた少なくとも 1 種類以上の V 族元素とからなる II - V 族化合物半導体からなる。

10

20

30

40

50

また、この発明は、

第1の基板上に六方晶系の結晶構造を有する第1の半導体層を成長させる工程と、

上記第1の半導体層を上記第1の基板がエッチングされるまでストライプ状にエッチングすることにより複数のストライプ状のシードを形成する工程と、

上記シードを形成した後の上記第1の基板の表面を六方晶系の結晶構造を有する半導体層が実質的に成長しないように処理する工程と、

それぞれの上記シードから六方晶系の結晶構造を有する第2の半導体層を相互に接触しないように横方向成長させる工程と、

上記第2の半導体層を覆うように全面に六方晶系の結晶構造を有する第3の半導体層を成長させる工程と、

上記第3の半導体層上に第2の基板を設ける工程と、

上記シード、上記第2の半導体層、上記第3の半導体層および上記第2の基板から上記第1の基板を剥離する工程とを有する絶縁ゲート型電界効果トランジスタの製造方法である。

#### 【0035】

また、この発明は、

第1の基板上に六方晶系の結晶構造を有する第1の半導体層を成長させる工程と、

上記第1の半導体層を上記第1の基板がエッチングされるまでストライプ状にエッチングすることにより複数のストライプ状のシードを形成する工程と、

上記シードを形成した後の上記第1の基板の表面を六方晶系の結晶構造を有する半導体層が実質的に成長しないように処理する工程と、

それぞれの上記シードから六方晶系の結晶構造を有する第2の半導体層を相互に接触しないように横方向成長させる工程と、

上記第2の半導体層を覆うように全面に六方晶系の結晶構造を有する第3の半導体層を成長させる工程と、

上記第3の半導体層上に第2の基板を設ける工程と、

上記シード、上記第2の半導体層、上記第3の半導体層および上記第2の基板から上記第1の基板を剥離する工程と、

上記シードの幅方向の中央部に上記シードの長手方向に延びるストライプ状の第1の凹部を形成するとともに、互いに隣接する上記シードの間の部分に上記シードの長手方向に延びるストライプ状の第2の凹部を形成する工程と、

上記第1の凹部にソース電極を形成するとともに、上記第2の凹部にゲート絶縁膜を介してゲート電極を形成する工程と、

上記ソース電極および上記ゲート電極側に第3の基板を設ける工程と、

上記第3の半導体層から上記第2の基板を剥離する工程と、

上記第3の半導体層上にドレイン電極を形成する工程とを有する絶縁ゲート型電界効果トランジスタの製造方法である。

#### 【0036】

この絶縁ゲート型電界効果トランジスタの製造方法においては、例えば、第1の半導体層を第1の基板がエッチングされるまでストライプ状にエッチングすることにより複数のストライプ状のシードを形成する工程において、第1の基板がエッチングされることにより形成される第1の基板からなるストライプ状の柱の断面のアスペクト比が1以上、好適には2以上となるまで第1の基板がエッチングされるようにする。こうすることで、第3の半導体層の成長時にこのストライプ状の柱に力が加わって破壊されやすくなることができる。

#### 【0037】

典型的には、例えば、第1の基板上に六方晶系の結晶構造を有する第1の半導体層を成長させた後、上記複数のストライプ状のシードを形成する前に、上記第1の半導体層上に絶縁膜を形成し、この絶縁膜および上記第1の半導体層を上記第1の基板がエッチングされるまでストライプ状にエッチングすることにより上記複数のストライプ状のシードを

10

20

30

40

50

形成する。

【0038】

六方晶系の結晶構造を有する第1の半導体層、第2の半導体層および第3の半導体層は窒化物系III-V族化合物半導体のほか、例えば $ZnO$ 、 $-ZnS$ 、 $-CdS$ 、 $-CdSe$ などであってもよい。窒化物系III-V族化合物半導体は、最も一般的には $Al_xByGa_{1-x-y-z}In_zAs_uN_{1-u-v}P_v$ （ただし、 $0 \leq x \leq 1$ 、 $0 \leq y \leq 1$ 、 $0 \leq z \leq 1$ 、 $0 \leq u \leq 1$ 、 $0 \leq v \leq 1$ 、 $x+y+z < 1$ 、 $u+v < 1$ ）からなり、より具体的には $Al_xByGa_{1-x-y-z}In_zN$ （ただし、 $0 \leq x \leq 1$ 、 $0 \leq y \leq 1$ 、 $0 \leq z \leq 1$ 、 $x+y+z < 1$ ）からなり、典型的には $Al_xGa_{1-x-z}In_zN$ （ただし、 $0 \leq x \leq 1$ 、 $0 \leq z \leq 1$ ）からなる。

10

【0039】

第1の基板は、結晶性の窒化物系III-V族化合物半導体層を成長させることができるもの、基本的（技術的）にはどのようなものであってもよいが、工業的観点（価格、大口径化、得られる素子特性など）から、好適にはSi基板である。

【0040】

シード上に絶縁膜を残した状態で第2の半導体層を横方向成長させてもよい。また、例えば、第1の半導体層として第1の導電型の第4の半導体層および第2の導電型の第5の半導体層を順次成長させる。例えば、第2の半導体層は第2の導電型、第3の半導体層は第1の導電型であるが、これに限定されるものではない。また、必要に応じて、第3の半導体層は最上層に第3の半導体層よりも不純物濃度が高いコンタクト層を有する。また、コンタクト層を厚く成長させ、第2の基板として用いてもよい。同様に、第3の半導体層を厚く成長させ、第2の基板として用いてもよい。

20

【0041】

また、この発明は、

六方晶系の結晶構造を有するストライプ状の複数のn型の第4の半導体層と、それぞれの上記第4の半導体層を覆うように、かつ相互に接触しないように設けられた複数のp型の第5の半導体層と、

上記複数の第5の半導体層を覆い、かつ互いに隣接する上記第5の半導体層の間の部分を埋めるように連続膜として設けられたn型の第6の半導体層と、

上記第4の半導体層に設けられたソース電極と、

30

上記第5の半導体層上にゲート絶縁膜を介して設けられたゲート電極と、

上記第6の半導体層の上記ソース電極および上記ゲート絶縁膜が設けられた面と反対側の面に設けられたドレイン電極とを有する絶縁ゲート型電界効果トランジスタである。

【0042】

また、この発明は、

六方晶系の結晶構造を有するストライプ状の複数のn型の第7の半導体層と、

それぞれの上記第7の半導体層を覆うように、かつ相互に接触しないように設けられた複数のn型の第8の半導体層と、

それぞれの上記第8の半導体層を覆うように、かつ相互に接触しないように設けられた複数のp型の第9の半導体層と、

40

上記複数の第9の半導体層を覆い、かつ互いに隣接する上記第9の半導体層の間の部分を埋めるように連続膜として設けられたn型の第10の半導体層と、

上記第7の半導体層の上記第9の半導体層と反対側の面に設けられたソース電極と、

互いに隣接する上記第9の半導体層の間の部分の上記第10の半導体層の上記第7の半導体層側の面にゲート絶縁膜を介して設けられたゲート電極と、

上記第10の半導体層の上記ソース電極および上記ゲート絶縁膜が設けられた面と反対側の面に設けられたドレイン電極とを有し、

上記第9の半導体層のバンドギャップは上記第8の半導体層および上記第10の半導体層のバンドギャップより大きい絶縁ゲート型電界効果トランジスタである。

【0043】

50

また、この発明は、

六方晶系の結晶構造を有するストライプ状の複数の n 型の第 1 1 の半導体層と、

それぞれの上記第 1 1 の半導体層を覆うように、かつ相互に接触しないように設けられた複数の p 型の第 1 2 の半導体層と、

それぞれの上記第 1 2 の半導体層を覆うように、かつ相互に接触しないように設けられた複数の p<sup>-</sup> 型の第 1 3 の半導体層と、

上記複数の第 1 3 の半導体層を覆い、かつ互いに隣接する上記第 1 3 の半導体層の間の部分を埋めるように連続膜として設けられた n 型の第 1 4 の半導体層と、

上記第 1 4 の半導体層上に設けられた p 型の第 1 5 の半導体層と、

上記第 1 1 の半導体層に設けられたソース電極と、

上記第 1 2 の半導体層および上記第 1 3 の半導体層上にゲート絶縁膜を介して設けられたゲート電極と、

上記第 1 5 の半導体層上に設けられたドレイン電極とを有する絶縁ゲート型電界効果トランジスタである。

この絶縁ゲート型電界効果トランジスタは、超接合絶縁ゲート型電界効果トランジスタとして用いることができる。

#### 【 0 0 4 4 】

また、この発明は、

六方晶系の結晶構造を有するストライプ状の複数の n 型の第 1 6 の半導体層と、

それぞれの上記第 1 6 の半導体層を覆うように、かつ相互に接触しないように設けられた複数の p 型の第 1 7 の半導体層と、

上記複数の第 1 7 の半導体層を覆い、かつ互いに隣接する上記第 1 7 の半導体層の間の部分を埋めるように連続膜として設けられた n 型の第 1 8 の半導体層と、

上記第 1 8 の半導体層上に設けられた n 型の第 1 9 の半導体層と、

上記第 1 9 の半導体層上に設けられた p 型の第 2 0 の半導体層と、

上記第 1 6 の半導体層の上記第 1 7 の半導体層と反対側の面に設けられたソース電極と、

上記第 1 7 の半導体層上にゲート絶縁膜を介して設けられたゲート電極と、

上記第 2 0 の半導体層上に設けられたドレイン電極とを有する絶縁ゲート型電界効果トランジスタである。

この絶縁ゲート型電界効果トランジスタは、絶縁ゲート型バイポーラトランジスタとして用いることができる。

#### 【 0 0 4 5 】

また、この発明は、

六方晶系の結晶構造を有するストライプ状の複数の n 型の第 2 1 の半導体層と、

それぞれの上記第 2 1 の半導体層を覆うように、かつ相互に接触しないように設けられた複数の p 型の第 2 2 の半導体層と、

それぞれの上記第 2 2 の半導体層を覆うように、かつ相互に接触しないように設けられた複数の p 型の第 2 3 の半導体層と、

上記複数の第 2 3 の半導体層を覆い、かつ互いに隣接する上記第 2 3 の半導体層の間の部分を埋めるように連続膜として設けられた n 型の第 2 4 の半導体層と、

上記第 2 4 の半導体層上に設けられた n 型の第 2 5 の半導体層と、

上記第 2 5 の半導体層上に設けられた p 型の第 2 6 の半導体層と、

上記第 2 1 の半導体層に設けられたソース電極と、

上記第 2 2 の半導体層および上記第 2 3 の半導体層上にゲート絶縁膜を介して設けられたゲート電極と、

上記第 2 6 の半導体層上に設けられたドレイン電極とを有する絶縁ゲート型電界効果トランジスタである。

この絶縁ゲート型電界効果トランジスタは、超接合絶縁ゲート型電界効果トランジスタと絶縁ゲート型バイポーラトランジスタとの複合素子として用いることができる。

10

20

30

40

50

## 【0046】

また、この発明は、

六方晶系の結晶構造を有するストライプ状の複数のn型の第27の半導体層と、

それぞれの上記第27の半導体層を覆うように、かつ相互に接触しないように設けられた複数のp型の第28の半導体層と、

それぞれの上記第28の半導体層を覆うように、かつ相互に接触しないように設けられた複数のp型の第29の半導体層と、

上記複数の第29の半導体層を覆い、かつ互いに隣接する上記第29の半導体層の間の部分を埋めるように連続膜として設けられたn型の第30の半導体層と、

上記第30の半導体層上に設けられたn型の第31の半導体層と、

上記第31の半導体層上に設けられたp型の第32の半導体層と、

上記第30の半導体層の上記第28の半導体層と反対側の面に設けられたソース電極と、

上記第28の半導体層および上記第29の半導体層上にゲート絶縁膜を介して設けられたゲート電極と、

上記第32の半導体層上に設けられたドレイン電極とを有することを特徴とする絶縁ゲート型電界効果トランジスタである。

## 【0047】

また、この発明は、

第1の基板上に六方晶系の結晶構造を有する第1の半導体層を成長させる工程と、

上記第1の半導体層を上記第1の基板がエッティングされるまでストライプ状にエッティングすることにより複数のストライプ状のシードを形成する工程と、

上記シードを形成した後の上記第1の基板の表面を六方晶系の結晶構造を有する半導体層が実質的に成長しないように処理する工程と、

それぞれの上記シードから六方晶系の結晶構造を有する第2の半導体層を相互に接触しないように横方向成長させる工程と、

上記第2の半導体層を覆うように全面に六方晶系の結晶構造を有する第3の半導体層を成長させる工程と、

上記第3の半導体層上に第2の基板を設ける工程と、

上記シード、上記第2の半導体層、上記第3の半導体層および上記第2の基板から上記第1の基板を剥離する工程とを有する半導体発光素子の製造方法である。

## 【0048】

また、この発明は、

第1の基板上に六方晶系の結晶構造を有する第1の半導体層を成長させる工程と、

上記第1の半導体層を上記第1の基板がエッティングされるまでストライプ状にエッティングすることにより複数のストライプ状のシードを形成する工程と、

上記シードを形成した後の上記第1の基板の表面を六方晶系の結晶構造を有する半導体層が実質的に成長しないように処理する工程と、

それぞれの上記シードから六方晶系の結晶構造を有する第2の半導体層を相互に接触しないように横方向成長させる工程と、

上記第2の半導体層を覆うように全面に発光素子構造を構成する六方晶系の結晶構造を有する第3の半導体層を成長させる工程と、

上記第3の半導体層上に第2の基板を貼り付ける工程と、

上記シード、上記第2の半導体層、上記第3の半導体層および上記第2の基板から上記第1の基板を剥離する工程と、

上記第1の基板を剥離する前または上記第1の基板を剥離した後に上記第3の半導体層の両面にそれぞれ第1の電極および第2の電極を形成する工程とを有することを特徴とする半導体発光素子の製造方法である。

## 【0049】

半導体発光素子の製造方法の発明においては、その性質に反しない限り、上記の絶縁ゲ

10

20

30

40

50

ート型電界効果トランジスタの製造方法に関連して説明したことが成立する。

【0050】

また、この発明は、

第1の基板上に六方晶系の結晶構造を有する第1の半導体層を成長させる工程と、

上記第1の半導体層を上記第1の基板がエッティングされるまでストライプ状にエッティングすることにより複数のストライプ状のシードを形成する工程と、

上記シードを形成した後の上記第1の基板の表面を六方晶系の結晶構造を有する半導体層が実質的に成長しないように処理する工程と、

それぞれの上記シードから六方晶系の結晶構造を有する第2の半導体層を相互に接触しないように横方向成長させる工程と、

上記第2の半導体層を覆うように全面に六方晶系の結晶構造を有する第3の半導体層を成長させる工程と、

上記第3の半導体層上に第2の基板を設ける工程と、

上記シード、上記第2の半導体層、上記第3の半導体層および上記第2の基板から上記第1の基板を剥離する工程とを有する太陽電池の製造方法である。

【0051】

また、この発明は、

第1の基板上に六方晶系の結晶構造を有する第1の半導体層を成長させる工程と、

上記第1の半導体層を上記第1の基板がエッティングされるまでストライプ状にエッティングすることにより複数のストライプ状のシードを形成する工程と、

上記シードを形成した後の上記第1の基板の表面を六方晶系の結晶構造を有する半導体層が実質的に成長しないように処理する工程と、

それぞれの上記シードから六方晶系の結晶構造を有する第2の半導体層を相互に接触しないように横方向成長させる工程と、

上記第2の半導体層を覆うように全面に太陽電池構造を構成する六方晶系の結晶構造を有する第3の半導体層を成長させる工程と、

上記第3の半導体層上に第2の基板を貼り付ける工程と、

上記シード、上記第2の半導体層、上記第3の半導体層および上記第2の基板から上記第1の基板を剥離する工程と、

上記第1の基板を剥離する前または上記第1の基板を剥離した後に上記第3の半導体層の両面にそれぞれ第1の電極および第2の電極を形成する工程とを有することを特徴とする太陽電池の製造方法である。

【0052】

太陽電池の製造方法の発明においては、その性質に反しない限り、上記の絶縁ゲート型電界効果トランジスタの製造方法に関連して説明したことが成立する。

第4～第32の半導体層は、第1～第3の半導体層と同様な半導体からなる。

【発明の効果】

【0053】

この発明によれば、Si基板を用いて高耐圧高出力の半導体電子素子、半導体発光素子、半導体受光素子を容易に製造することができる。あるいは、この発明によれば、Si基板を用いて高耐圧高出力の絶縁ゲート型電界効果トランジスタあるいは半導体発光素子あるいは太陽電池を容易に製造することができる。

【図面の簡単な説明】

【0054】

【図1】この発明の第1の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図2】この発明の第1の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図3】この発明の第1の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

10

20

30

40

50

【図4】この発明の第1の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図5】この発明の第1の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図6】この発明の第1の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図7】この発明の第1の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図8】この発明の第2の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図9】この発明の第3の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図10】この発明の第4の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図11】この発明の第4の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図12】この発明の第4の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図13】この発明の第4の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図14】この発明の第4の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図15】この発明の第5の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図16】この発明の第6の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図17】この発明の第7の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図18】この発明の第8の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図19】この発明の第9の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図20】この発明の第10の実施の形態によるGaN系MOSFETの製造方法を説明するための断面図である。

【図21】この発明の第11の実施の形態によるノンラッチアップIGBT型GaN系MOSFETの製造方法を説明するための断面図である。

【図22】この発明の第12の実施の形態によるIGBTおよびSJ型GaN系MOSFETの製造方法を説明するための断面図である。

【図23】この発明の第13の実施の形態によるノンラッチアップIGBTおよびSJ型GaN系MOSFETの製造方法を説明するための断面図である。

【図24】この発明の第14の実施の形態によるGaN系半導体発光素子の製造方法を説明するための断面図である。

【図25】この発明の第15の実施の形態によるGaN系太陽電池の製造方法を説明するための断面図である。

【図26】この発明の第16の実施の形態によるGaN系ショットキーバリアダイオードの製造方法を説明するための断面図である。

【図27】第1の従来例のGaN系HFEETを示す断面図である。

【図28】第2の従来例のGaN系HFEETを示す断面図である。

【図29】第3の従来例のGaN系HFEETを示す断面図である。

【図30】第4の従来例のGaN系HFEETを示す断面図である。

10

20

30

40

50

【図31】第5の従来例のGaN系HFEトを示す断面図である。

【発明を実施するための形態】

【0055】

以下、発明を実施するための形態（以下、実施の形態と言う。）について説明する。

1. 第1の実施の形態

第1の実施の形態による縦型（vertical type）GaN系MOSFETの製造方法について説明する。

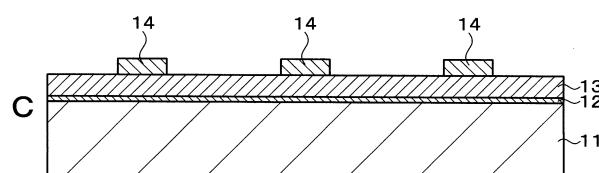

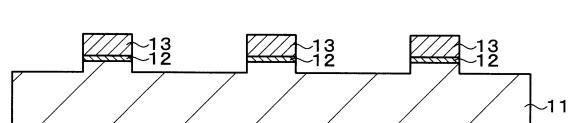

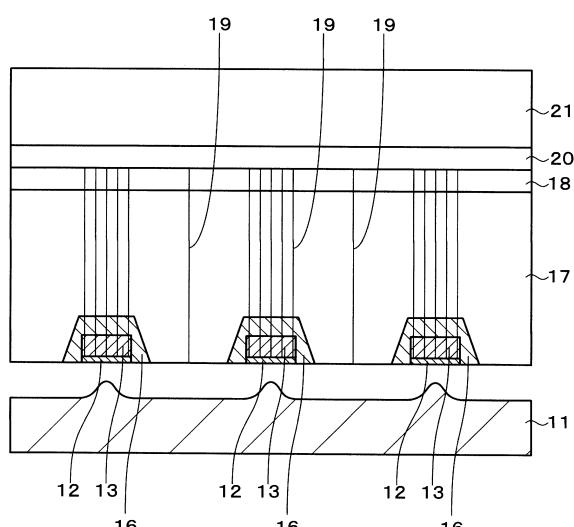

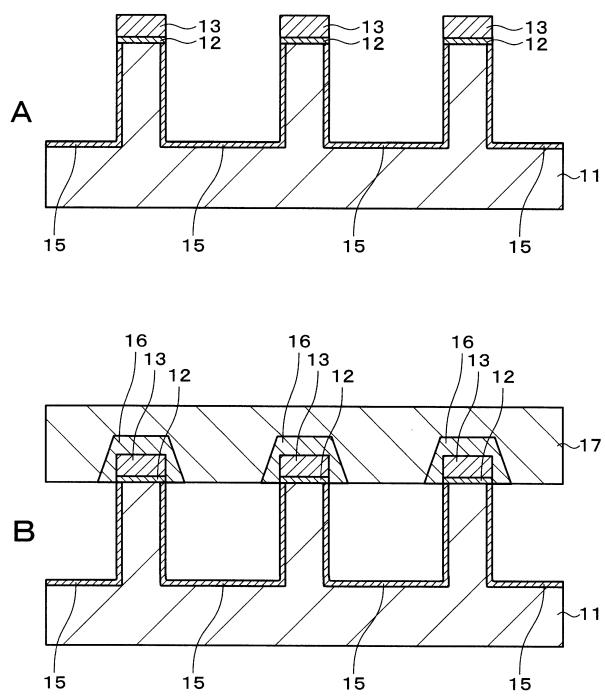

【0056】

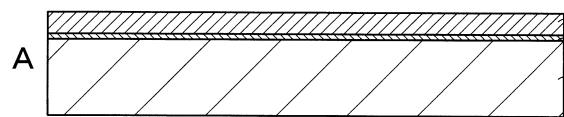

図1Aに示すように、Si基板などからなる第1の基板11上に例えば有機金属化学気相成長（MOCVD）法により例えば500程度の温度でAlNやGaNなどからなる低温バッファ層12を成長させた後、この低温バッファ層12上に例えば同じくMOCVD法により例えば1000～1100程度の温度、例えば1050でn<sup>+</sup>型GaN層13を成長させる。低温バッファ層12の厚さは特に限定されないが、一般的には10～50nm、例えば20nmである。n<sup>+</sup>型GaN層13の厚さは必要に応じて選ばれるが、例えば0.1～2μmである。n<sup>+</sup>型GaN層13にはn型不純物として例えばSiがドープされ、不純物濃度は例えば1×10<sup>18</sup>～1×10<sup>19</sup>cm<sup>-3</sup>程度である。

10

【0057】

次に、図1Bに示すように、n<sup>+</sup>型GaN層13上に例えば真空蒸着法やCVD法などにより例えばSiO<sub>2</sub>膜やSiN膜などの絶縁膜またはエッチングマスク14を形成する。絶縁膜またはエッチングマスク14を後で除去する場合には、この絶縁膜またはエッチングマスク14として金属膜やレジスト膜などを用いることもできる。

20

【0058】

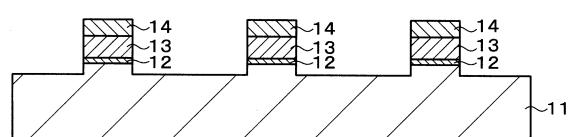

次に、図1Cに示すように、絶縁膜またはエッチングマスク14上にフォトリソグラフィーにより所定形状のストライプ状のレジストパターン（図示せず）を形成した後、このレジストパターンをマスクとして例えば反応性イオンエッチング（RIE）法などのドライエッチング法により絶縁膜またはエッチングマスク14をストライプ状にパターニングする。この後、レジストパターンを除去する。このストライプ状の絶縁膜またはエッチングマスク14の長手方向は、好適には、n<sup>+</sup>型GaN層13の1-100方向あるいは11-20方向に選ばれる。

【0059】

30

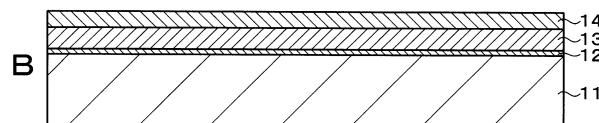

次に、図2Aに示すように、こうして形成されたストライプ状の絶縁膜またはエッチングマスク14をマスクとしてドライエッチング法またはウェットエッチング法により第1の基板11が深さDだけエッチングされるまでエッチングする。例えば、第1の基板11がSi基板である場合には、n<sup>+</sup>型GaN層13および低温バッファ層12はRIE法などのドライエッチング法によりエッチングし、第1の基板11、すなわちSi基板はウェットエッチング法によりエッチングする。このエッチングにより、n<sup>+</sup>型GaN層13、低温バッファ層12および第1の基板11の最上部はストライプ状にパターニングされる。ストライプ状のn<sup>+</sup>型GaN層13および低温バッファ層12の幅は例えば2～10μmとする。また、互いに隣接するn<sup>+</sup>型GaN層13とn<sup>+</sup>型GaN層13との間の距離は例えば6～20μmとする。第1の基板11のエッチング深さDは例えば0.2μm以上に選ばれ、一般的には0.2μm以上20μm以下に選ばれる。ストライプ状のn<sup>+</sup>型GaN層13は後に行う成長の際のシード（種結晶）となる。

40

【0060】

次に、図2Bに示すように、絶縁膜またはエッチングマスク14をウェットエッチング法などによりエッチング除去する。

【0061】

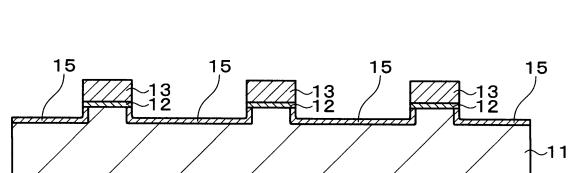

次に、図2Cに示すように、エッチングにより露出した第1の基板11の表面に成長防止膜15を形成する。この成長防止膜15としては、例えば、SiO<sub>x</sub>膜（SiO<sub>2</sub>膜を含む）やSiN<sub>x</sub>膜（Si<sub>3</sub>N<sub>4</sub>膜を含む）などが用いられる。この成長防止膜15の形成方法としては、酸化法、窒化法、CVD法などを用いることができ、第1の基板11の

50

種類などに応じて適宜選ばれる。例えば、第1の基板11がSi基板である場合、SiO<sub>x</sub>膜は、例えば、Si基板の表面を熱酸化法やプラズマ酸化法などにより酸化することにより形成される。熱酸化の条件の一例を挙げると、酸化炉中でO<sub>2</sub>雰囲気において1000、30分である。プラズマ酸化の条件の一例を挙げると、プラズマエンハンスト化学気相成長(PECVD)炉中で基板温度300～1000において酸素プラズマを照射する。Si基板の表面を酸化する際には、n<sup>+</sup>型GaN層13の表面が酸化され過ぎないようにする。SiN<sub>x</sub>膜は、例えば、Si基板の表面を熱窒化法やプラズマ窒化法などにより窒化することにより形成される。熱窒化の条件の一例を挙げると、MOCVD炉中でNH<sub>3</sub>雰囲気において1000以上の温度で10分間窒化する。プラズマ窒化の条件の一例を挙げると、PECVD炉中で基板温度300～1000において窒素プラズマを照射する。

#### 【0062】

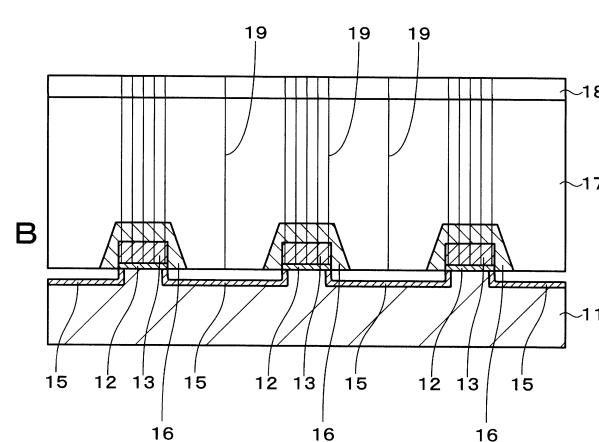

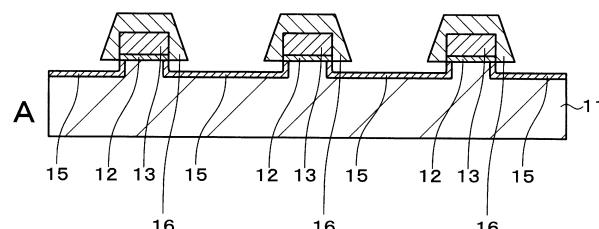

次に、図3Aに示すように、n<sup>+</sup>型GaN層13をシードとして例えばMOCVD法によりp型GaN層16を横方向成長(ELLO(Epitaxial Lateral Overgrowth))させる。このとき、第1の基板11の表面に成長防止膜15が形成されており、この成長防止膜15上ではGaNの成長が極めて抑制されるため、n<sup>+</sup>型GaN層13をシードとしてp型GaN層16を横方向成長させることができる。このp型GaN層16の横方向成長は、互いに隣接するn<sup>+</sup>型GaN層13から横方向成長するp型GaN層16同士が接触する前に停止させる。p型GaN層16の横方向成長の条件(温度、圧力、成長速度など)の選択により、p型GaN層16の両側面の成長面(ファセット)や縦横成長比率などを制御することができる。p型GaN層16にはp型不純物として例えばMgがドープされ、不純物濃度は例えば1×10<sup>18</sup>～1×10<sup>21</sup>cm<sup>-3</sup>である。

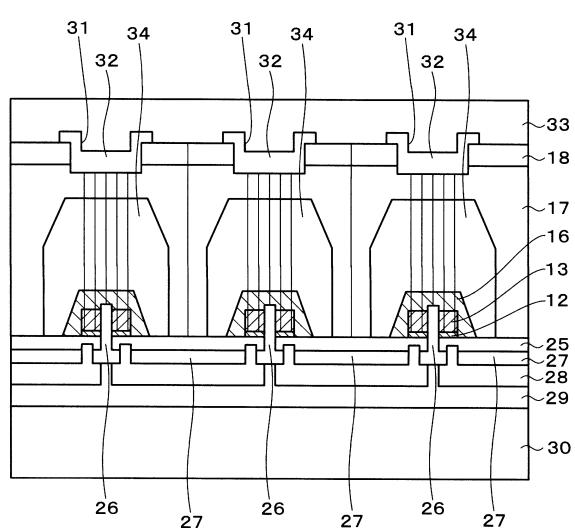

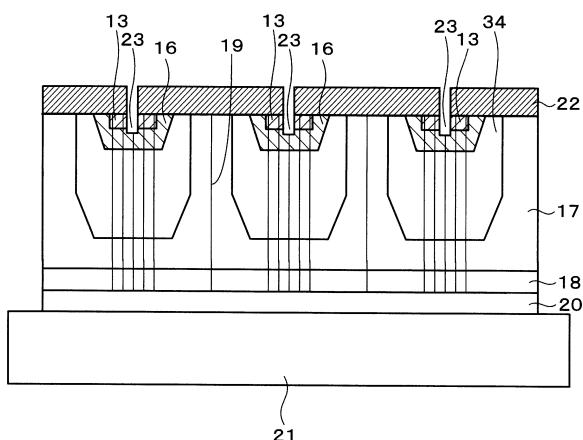

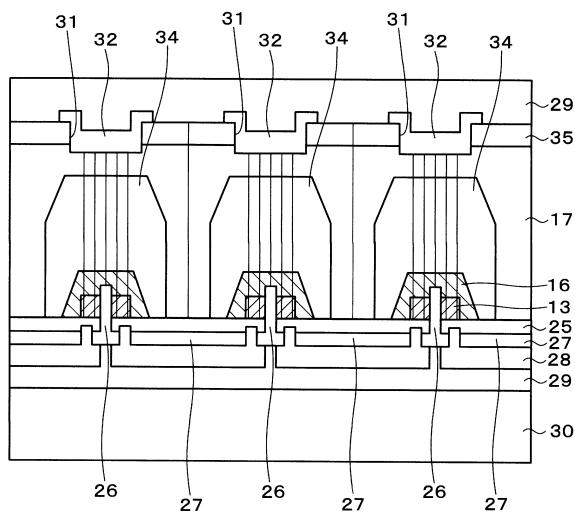

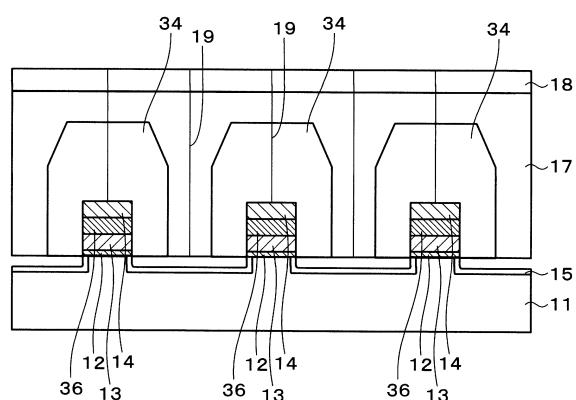

#### 【0063】

次に、図3Bに示すように、例えばMOCVD法によりn型GaN層17を全面に連続膜となるまで成長させ、その上にさらに、n型GaN層17より不純物濃度が高いn<sup>+</sup>型GaNコンタクト層18を成長させる。これらのn型GaN層17およびn<sup>+</sup>型GaNコンタクト層18の成長時には、n<sup>+</sup>型GaN層13と低温バッファ層12との界面から発生した転位が上方に伝播する結果、貫通転位19が発生する。この貫通転位19の密度は一般的には1×10<sup>-8</sup>～1×10<sup>-10</sup>m<sup>-2</sup>である。互いに隣接するp型GaN層16から横方向成長するn型GaN層17同士が接触する会合部にも同様に貫通転位19が発生する。n型GaN層17にはn型不純物として例えばSiがドープされ、不純物濃度は例えば1×10<sup>15</sup>～1×10<sup>17</sup>cm<sup>-3</sup>である。n<sup>+</sup>型GaNコンタクト層18にはn型不純物として例えばSiがドープされ、不純物濃度は例えば1×10<sup>18</sup>～1×10<sup>19</sup>cm<sup>-3</sup>である。n型GaN層17およびn<sup>+</sup>型GaNコンタクト層18の厚さは必要に応じて選ばれるが、n型GaN層17の厚さは例えば3～20μm、n<sup>+</sup>型GaNコンタクト層18の厚さは例えば10～100nmである。

#### 【0064】

次に、図4に示すように、n<sup>+</sup>型GaNコンタクト層18上に接着層20を介して第2の基板21を貼り付ける。接着層20は第2の基板21の種類などに応じて適宜選ばれるが、例えば、レジスト、ワックス、セラミックバインダーなどが用いられる。第2の基板21は、後の工程で行われるリン酸(H<sub>2</sub>PO<sub>4</sub>)や水酸化カリウム(KOH)、塩化ナトリウム(NaOH)などを用いたウェットエッティングに耐性のある基板である限り、特に限定されず、必要に応じて選ばれるが、例えばサファイア(Al<sub>2</sub>O<sub>3</sub>)基板を用いることができるほか、ウェットエッティングに耐性のある保護層(例えば、レジスト層)で表面を保護すれば、金属基板や他の基板などを用いることができる。金属基板としては、例えば銅(Cu)、CuW、Moなどからなるもの、他の基板としては例えばSi、AlN、AlSiなどからなるものを用いることができる。

#### 【0065】

次に、第1の基板11と低温バッファ層12との間を分離することにより、第1の基板11を第2の基板21上のn<sup>+</sup>型GaN層13、n型GaN層17、p型GaN層16お

10

20

30

40

50

および $n^+$ 型GaNコンタクト層18から剥離する。具体的には、例えば、成長防止膜15をエッティング除去した後、第1の基板11をウェットエッティングする。このウェットエッティングにおいては、第1の基板11の最上部に形成された深さDの溝内にエッティング液が浸透し、 $n^+$ 型GaN層13の下方の第1の基板11からなるストライプ状の柱がエッティング除去されることにより、第1の基板11を第2の基板21上の $n^+$ 型GaN層13、 $n$ 型GaN層17および $p$ 型GaN層16から剥離することができる。例えば、第1の基板11がSi基板である場合には、フッ硝酸(HF + HNO<sub>3</sub>)やKOH、水酸化テトラメチルアンモニウム(TMAB)などを用いてウェットエッティングする。第1の基板11の裏面からポリッシングやウェットエッティングなどを行うことにより第1の基板11を除去してもよい。なお、必要に応じて、第1の基板11を剥離または除去せず、そのまま残してもよい。10

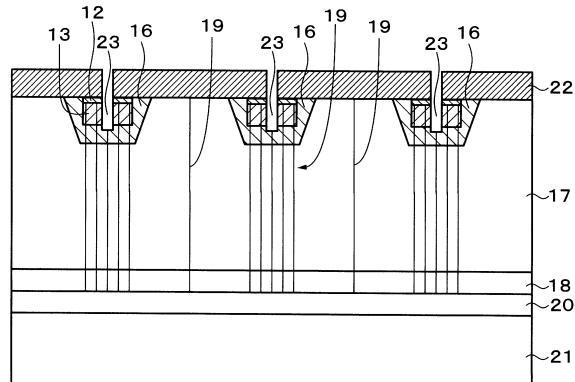

#### 【0066】

次に、図5に示すように、フォトリソグラフィーにより、 $n^+$ 型GaN層13の中央部に対応する部分がストライプ状に開口した所定形状のレジストパターン22を $n^+$ 型GaN層13、 $n$ 型GaN層17および $p$ 型GaN層16上に形成する。次に、このレジストパターン22をマスクとして $n^+$ 型GaN層13を少なくとも $p$ 型GaN層16に達する深さまでドライエッティングすることにより凹部23を形成する。次に、レジストパターン22を除去する。この後、 $p$ 型GaN層16の $p$ 型不純物の電気的活性化のために、例えば窒素雰囲気中において800で20分アニールする。 $p$ 型GaN層16に達する凹部23の形成は、このアニール工程において $p$ 型GaN層16からの水素の脱離を容易にすること、および、後に形成するゲート電極と $p$ 型GaN層16とのコンタクトを取ることが目的である。20

#### 【0067】

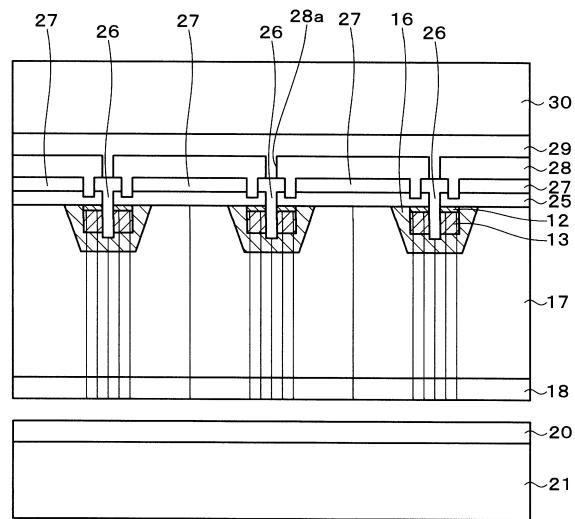

次に、図6に示すように、凹部23を形成した $n^+$ 型GaN層13、 $n$ 型GaN層17および $p$ 型GaN層16の全面にゲート絶縁膜25を形成する。このゲート絶縁膜25としては例えばSiO<sub>2</sub>膜やSiN膜やAl<sub>2</sub>O<sub>3</sub>膜やHfO<sub>2</sub>膜あるいはそれらの積層膜などを用いることができる。このゲート絶縁膜25は、下地にダメージを与えない成膜法、例えば真空蒸着法、原子層堆積法(ALD法)などにより形成することができる。次に、このゲート絶縁膜25のうちの $n^+$ 型GaN層13上の所定部分をエッティング除去して開口25aを形成する。次に、例えば真空蒸着法やスパッタリング法などにより全面に金属膜を形成した後、この金属膜を所定形状にパターニングすることにより、凹部23の内部を含めて全面にソース電極およびゲート電極形成用の金属膜を形成する。この金属膜は、必要に応じて選ばれるが、例えば、Ni/Ti/Pt/Au多層膜を用いることができる。次に、この金属膜をエッティングにより所定形状にパターニングすることにより、凹部23の内部にソース電極26を形成するとともに、 $p$ 型GaN層16や $n$ 型GaN層17上にゲート絶縁膜25を介してゲート電極27を形成する。次に、これらのソース電極26およびゲート電極27上に例えば真空蒸着法などにより全面にSiO<sub>2</sub>膜などの絶縁膜28を形成する。次に、この絶縁膜28のうちのソース電極26上の所定部分に開口28aを形成する。次に、例えば真空蒸着法やスパッタリング法などによりこの絶縁膜28の全面に金属膜を形成し、必要に応じてこの金属膜を所定形状にパターニングすることによりソースパッド電極29を形成する。次に、このソースパッド電極29上に第3の基板30を貼り付ける。この第3の基板30は必要に応じて選ばれるが、好適には熱伝導性の良好なセラミック基板や金属基板などが用いられ、具体的には、例えば、Si、AlN、Cu、CuW、AlSi、SiCなどからなるものを用いることができる。この後、 $n^+$ 型GaNコンタクト層18から接着層20および第2の基板21を剥離する。第2の基板21は必要に応じて再利用(リサイクル)することができる。30

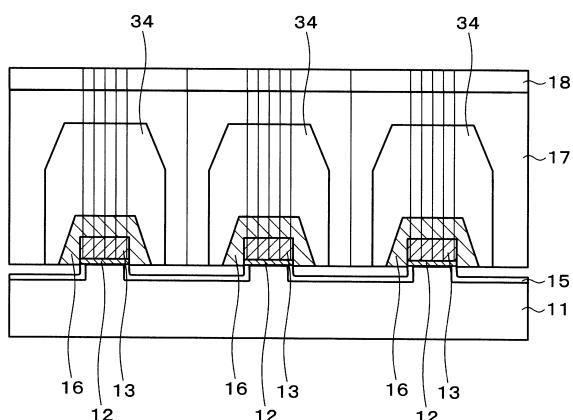

#### 【0068】

次に、図7に示すように、 $n^+$ 型GaN層13の上方の、貫通転位19が集中して存在する部分を含む所定部分の $n^+$ 型GaNコンタクト層18および $n$ 型GaN層17の最上部をエッティング除去して凹部31を形成する。次に、例えば真空蒸着法やスパッタリング40

法などにより全面に例えれば  $\text{SiO}_2$  膜などの絶縁膜 3 2 を形成した後、この絶縁膜 3 2 をエッティングにより所定形状にパターニングすることにより凹部 3 1 およびその近傍の部分のみ残す。この後、例えは真空蒸着法やスパッタリング法などによりこの絶縁膜 3 3 および  $n^+$  型  $\text{GaN}$  コンタクト層 1 8 の全面に金属膜を形成し、必要に応じてこの金属膜を所定形状にパターニングしてドレイン電極 3 3 を形成する。この場合、貫通転位 1 9 が集中して存在する部分の上部が絶縁膜 3 3 により覆われており、ドレイン電極 3 3 がこの貫通転位 1 9 が集中して存在する部分に直接接触していないので、貫通転位 1 9 を通してのリーキ電流の低減を図ることができる。

#### 【0069】

以上により、目的とする縦型  $\text{GaN}$  系 MOSFET を製造することができる。この縦型  $\text{GaN}$  系 MOSFET は、 $n$  型  $\text{GaN}$  層 1 7 の不純物濃度および厚さの選択により、ドレイン電極 3 3 側の  $n$  型  $\text{GaN}$  層 1 7 に空乏層を広範囲に広げることができるので、高耐圧かつ高出力とすることができます。

#### 【0070】

以上のように、この第 1 の実施の形態によれば、IGBT や超接合 (SJ) を用いないで高耐圧高出力の縦型  $\text{GaN}$  系 MOSFET を実現することができる。しかも、この縦型  $\text{GaN}$  系 MOSFET は  $\text{Si}$  基板を用いて容易に製造することができるため、製造コストの低減を図ることができます。

#### 【0071】

##### 2. 第 2 の実施の形態

第 2 の実施の形態においては、縦型  $\text{GaN}$  系 MOSFET の製造方法について説明する。

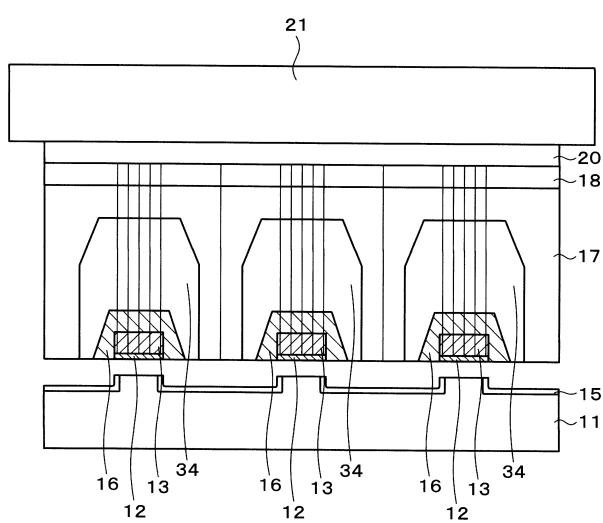

#### 【0072】

図 8 A に示すように、第 2 の実施の形態による縦型  $\text{GaN}$  系 MOSFET の製造方法においては、第 1 の基板 1 1 をエッティングする際に十分に深くエッティングし、具体的には、例えは、エッティング後に残される第 1 の基板 1 1 によりアスペクト比が 1 以上のストライプ状の柱が形成されるようにエッティングする。第 1 の基板 1 1 のエッティング深さ  $D$  は、例えは  $4 \sim 30 \mu\text{m}$  とする。第 1 の基板 1 1 のエッティングにより露出した第 1 の基板 1 1 の表面には第 1 の実施の形態と同様に成長防止膜 1 5 を形成する。

#### 【0073】

次に、図 8 B に示すように、 $n^+$  型  $\text{GaN}$  層 1 3 をシードとして  $p$  型  $\text{GaN}$  層 1 7 を横方向成長させた後、全面に  $n$  型  $\text{GaN}$  層 1 8 を連続膜となるまで成長させる。この場合、 $n$  型  $\text{GaN}$  層 1 8 の成長後の冷却段階で、例えは  $\text{Si}$  基板などからなる第 1 の基板 1 1 と  $n$  型  $\text{GaN}$  層 1 8 との熱膨張係数の差により第 1 の基板 1 1 および  $n$  型  $\text{GaN}$  層 1 7 の双方に応力が発生する。 $n$  型  $\text{GaN}$  層 1 7 の熱膨張係数が  $\text{Si}$  基板などからなる第 1 の基板 1 1 より大きい場合には、 $n$  型  $\text{GaN}$  層 1 7 には引っ張り応力が発生し、クラックが発生しやすくなる。しかしながら、第 1 の基板 1 1 からなるストライプ状の柱の断面のアスペクト比が 1 以上であり、機械的に弱いため、この柱が破断することにより、 $n$  型  $\text{GaN}$  層 1 7 に発生する引っ張り応力の低減を図ることができ、それによってクラックなどが発生するのを防止することができる。

#### 【0074】

この後、第 1 の実施の形態と同様に工程を進めて目的とする縦型  $\text{GaN}$  系 MOSFET を製造する。

#### 【0075】

この第 2 の実施の形態によれば、第 1 の実施の形態と同様な利点を得ることができる。

#### 【0076】

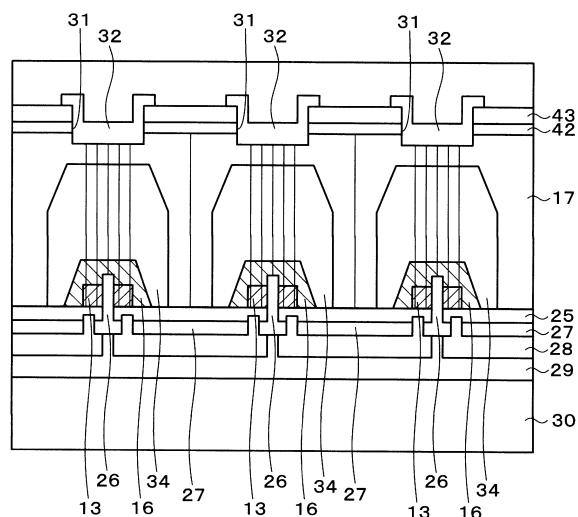

##### 3. 第 3 の実施の形態

第 3 の実施の形態においては、SJ 縦型  $\text{GaN}$  系 MOSFET およびその製造方法について説明する。

#### 【0077】

10

20

30

40

50

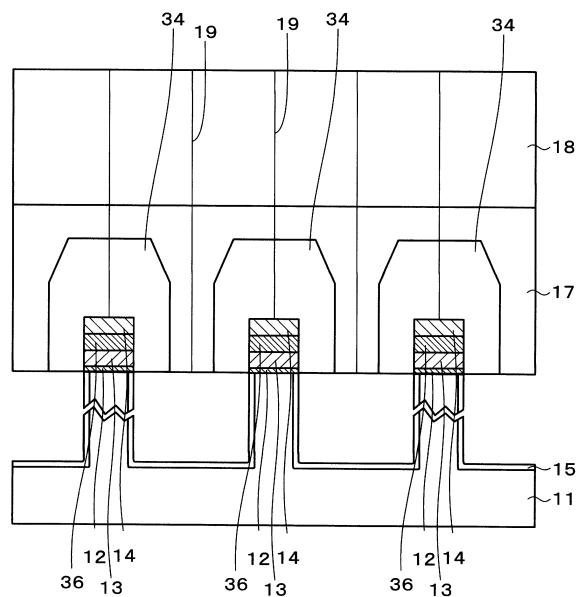

図9に示すように、第3の実施の形態においては、第1の実施の形態と同様にしてストライプ状のn<sup>+</sup>型GaN層13を形成した後、このn<sup>+</sup>型GaN層13をシードとしてp型GaN層16を横方向成長させる。次に、このp型GaN層16を覆うようにp型GaN層34を成長させた後、n型GaN層17を連続膜となるまで成長させ、さらにその上にn<sup>+</sup>型GaNコンタクト層18を成長させる。p型GaN層34の不純物濃度（ホール濃度）、高さ（厚さ）、幅などを制御することにより、n型GaN層17とこのp型GaN層34とにより良好な超接合を実現することができる。p型GaN層16にはp型不純物として例えばMgがドープされ、不純物濃度は例えば $1 \times 10^{19} \sim 1 \times 10^{21} \text{ cm}^{-3}$ 、p型GaN層34にはp型不純物として例えばMgがドープされ、不純物濃度は例えば $1 \times 10^{17} \sim 1 \times 10^{20} \text{ cm}^{-3}$ とする。p型GaN層34の不純物濃度（ホール濃度）、高さ（厚さ）、幅などの制御は、例えば、成長時に用いるGaN原料（トリメチルガリウム（TMG）など）やp型不純物としてのMgのドーパント（シクロペンタジエニル（Cp<sub>2</sub>Mg）など）の供給量、V/I/I比（I/I/I原料（アンモニア（NH<sub>3</sub>）の供給量に対するV族原料（GaN原料）の供給量の比）、成長温度、圧力などの成長条件を制御することにより行うことができる。必要に応じて、p型GaN層34にドープされるMgなどのp型不純物の電気的活性化のために、n<sup>+</sup>型GaNコンタクト層18を成長させた後、n<sup>+</sup>型GaNコンタクト層18からp型GaN層34に到達する溝を形成し、この状態で例えば窒素雰囲気中において800度で20分アニールすることにより、成長時にp型GaN層34に取り込まれた水素を水素ガスとして外部に放出させるようにしてもよい。この後、第1の実施の形態と同様に工程を進めてドレン電極33まで形成する。

## 【0078】

以上により、目的とするS-J縦型GaN系MOSFETを製造することができる。

## 【0079】

この第3の実施の形態によれば、第1の実施の形態と同様な利点に加えて、n型GaN層17とp型GaN層34とにより超接合が形成されるため、ソース電極23とドレン電極33との間のチャネル層の全体に空乏層を広げることができ、それによって縦型GaN系MOSFETの耐圧の大幅な向上を図ることができるという利点も得ることができる。

## 【0080】

## 4. 第4の実施の形態

第4の実施の形態においては、S-J縦型GaN系MOSFETの製造方法について説明する。

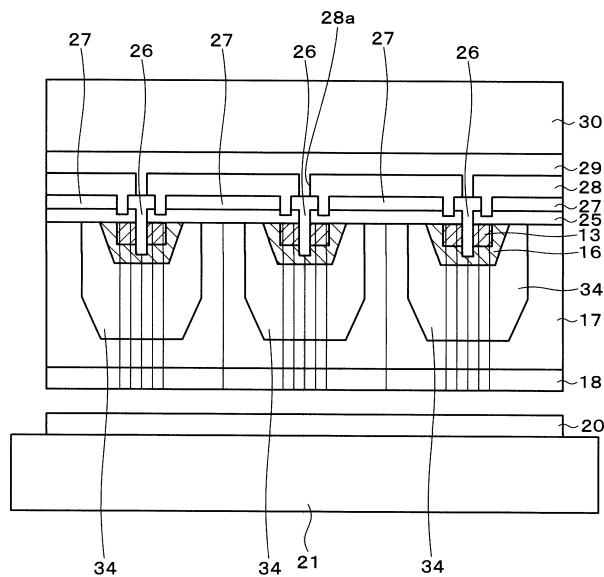

## 【0081】

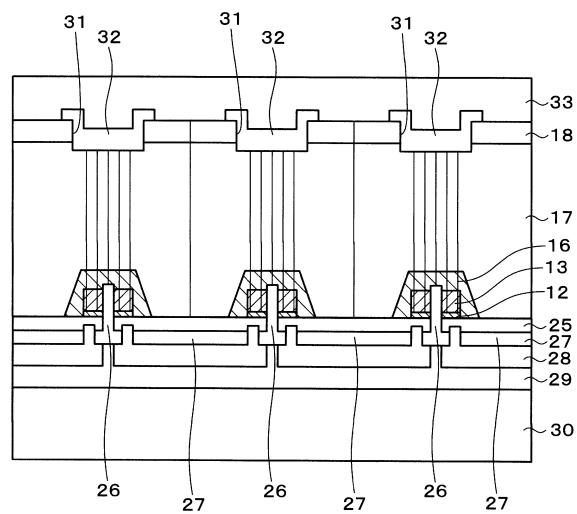

図10に示すように、第1の実施の形態と同様にしてストライプ状のn<sup>+</sup>型GaN層13を形成した後、このn<sup>+</sup>型GaN層13をシードとしてp型GaN層16を横方向成長させる。次に、このp型GaN層16を覆うようにp型GaN層34を成長させた後、n型GaN層17を連続膜となるまで成長させ、さらにその上にn<sup>+</sup>型GaNコンタクト層18を成長させる。第3の実施の形態と同様に、p型GaN層34の不純物濃度（ホール濃度）、高さ（厚さ）、幅などを制御することにより、n型GaN層18とこのp型GaN層34とにより良好な超接合を実現することができる。p型GaN層17にはp型不純物として例えばMgがドープされ、不純物濃度は例えば $1 \times 10^{19} \sim 1 \times 10^{21} \text{ cm}^{-3}$ 、p型GaN層34にはp型不純物として例えばMgがドープされ、不純物濃度は例えば $1 \times 10^{17} \sim 1 \times 10^{20} \text{ cm}^{-3}$ とする。

## 【0082】

次に、図11に示すように、第1の実施の形態と同様にして、n<sup>+</sup>型GaNコンタクト層18上に接着層20を介して第2の基板21を貼り付けた後、第1の基板11を剥離する。

## 【0083】

次に、図12に示すように、第1の実施の形態と同様にして、n<sup>+</sup>型GaN層13、p型GaN層16、p型GaN層34およびn型GaN層17上に所定形状のレジストパタ

10

20

30

40

50

ーン 2 2 を形成した後、このレジストパターン 2 2 をマスクとして  $n^+$  型 GaN 層 1 3 をエッティングすることにより凹部 2 3 を形成する。

【0084】

次に、図 1 3 に示すように、第 1 の実施の形態と同様にして、ゲート絶縁膜 2 5、開口 2 5 a、ソース電極 2 3、ゲート電極 2 4、絶縁膜 2 8、開口 2 8 a およびソースパッド電極 2 9 を形成し、このソースパッド電極 2 9 に第 3 の基板 3 0 を貼り付けた後、 $n^+$  型 GaN コンタクト層 1 8 から接着層 2 0 および第 2 の基板 2 1 を剥離する。

【0085】

次に、図 1 4 に示すように、開口 3 1 を形成し、この開口 3 1 の部分に絶縁膜 3 2 を形成した後、ドレイン電極 3 3 を形成する。

10

【0086】

以上により、目的とする SJ 縱型 GaN 系 MOSFET が製造される。

【0087】

この第 4 の実施の形態によれば、第 3 の実施の形態と同様な利点を得ることができる。

【0088】

5. 第 5 の実施の形態

第 5 の実施の形態においては、SJ 縱型 GaN 系 MOSFET の製造方法について説明する。

【0089】

図 1 5 に示すように、第 5 の実施の形態においては、第 4 の実施の形態に比べて、p 型 GaN 層 3 4 を薄く成長させる。その他のことは第 4 の実施の形態と同様である。

20

【0090】

この第 5 の実施の形態によれば、第 4 の実施の形態と同様な利点を得ることができる。

【0091】

6. 第 6 の実施の形態

第 6 の実施の形態においては、IGBT および SJ 縱型 GaN 系 MOSFET の製造方法について説明する。

【0092】

図 1 6 に示すように、第 6 の実施の形態は、n 型 GaN 層 1 7 上に、 $n^+$  型 GaN コンタクト層 1 8 の代わりに  $p^+$  型 GaN コンタクト層 3 5 を成長させることを除いて、第 4 の実施の形態と同様である。 $p^+$  型 GaN コンタクト層 3 5 には例えば Mg がドープされ、不純物濃度は例えば  $1 \times 10^{19} \sim 1 \times 10^{21} \text{ cm}^{-3}$  である。

30

【0093】

この第 6 の実施の形態によれば、第 1 の実施の形態と同様な利点に加えて、次のような利点を得ることができる。すなわち、n 型 GaN 層 1 7 上に  $p^+$  型 GaN コンタクト層 3 5 が設けられた構造により、IGBT と同等な構造を得ることができる。このため、IGBT の伝導度変調効果と超接合MOSFET の特徴である空乏層領域拡大効果とを同時に得ることができ、超低オン抵抗かつ高耐圧のIGBT および SJ 縱型 GaN 系 MOSFET を実現することができる。

【0094】

40

7. 第 7 の実施の形態

第 7 の実施の形態においては、縦型 GaN 系 MOSFET の製造方法について説明する。

【0095】

図 1 7 に示すように、第 7 の実施の形態においては、第 1 の基板 1 1 上に低温バッファ層 1 2 および  $n^+$  型 GaN 層 1 3 を成長させた後、引き続いて  $n^+$  型 GaN 層 1 3 上に  $p^+$  型 GaN 層 3 6 を成長させる。次に、 $p^+$  型 GaN 層 3 6 上に絶縁膜またはエッティングマスク 1 4 を形成する。次に、絶縁膜またはエッティングマスク 1 4 をストライプ状にパテーニングする。次に、こうして形成されたストライプ状の絶縁膜またはエッティングマスク 1 4 をマスクとして第 1 の基板 1 1 が深さ D だけエッティングされるまでエッティングする。

50

このエッティングにより、 $p^+$  型 GaN 層 36、 $n^+$  型 GaN 層 13、低温バッファ層 12 および第 1 の基板 11 の最上部はストライプ状にパターニングされる。次に、エッティングにより露出した第 1 の基板 11 の表面に成長防止膜 15 を形成する。次に、 $n^+$  型 GaN 層 13 および  $p^+$  型 GaN 層 36 をシードとして  $p$  型 GaN 層 34 を横方向成長させる。このとき、第 1 の基板 11 の表面に成長防止膜 15 が形成されており、この成長防止膜 15 上では GaN の成長が極めて抑制されるため、 $n^+$  型 GaN 層 13 をシードとして  $p$  型 GaN 層 34 を横方向成長させることができる。この  $p$  型 GaN 層 34 の横方向成長は、互いに隣接する  $n^+$  型 GaN 層 13 から横方向成長する  $p$  型 GaN 層 16 同士が接触する前に停止させる。次に、例えば MOCVD 法により  $n$  型 GaN 層 17 を全面に連続膜となるまで成長させ、その上にさらに、 $n$  型 GaN 層 17 より不純物濃度が高い  $n^+$  型 GaN コンタクト層 18 を成長させる。 $p$  型 GaN 層 16 上に絶縁膜またはエッティングマスク 14 が設けられており、 $n^+$  型 GaN 層 13 と低温バッファ層 12 との界面から発生した転位が  $p$  型 GaN 層 16 を貫通した貫通転位 19 は絶縁膜またはエッティングマスク 14 で止められていることにより、これらの  $p$  型 GaN 層 34、 $n$  型 GaN 層 17 および  $n^+$  型 GaN コンタクト層 18 の成長時には、 $p$  型 GaN 層 16 から貫通転位 19 が  $p$  型 GaN 層 34、 $n$  型 GaN 層 17 および  $n^+$  型 GaN コンタクト層 18 に伝播するのを防止することができる。この場合、 $p$  型 GaN 層 34、 $n$  型 GaN 層 17 および  $n^+$  型 GaN コンタクト層 18 に存在する貫通転位 19 は、絶縁膜またはエッティングマスク 14 の中央部の上の部分に形成される左右から横方向成長する  $p$  型 GaN 層 16 同士の会合部および互いに隣接する  $p$  型 GaN 層 34 から横方向成長する  $n$  型 GaN 層 17 同士が接触する会合部だけに存在し、貫通転位 19 の密度は極めて低い。

10

## 【0096】

この後、第 1 の実施の形態と同様に工程を進めて、目的とする SJ 縱型 GaN 系 MOSFET を製造する。

## 【0097】

この第 7 の実施の形態によれば、第 1 の実施の形態と同様な利点に加えて、 $p$  型 GaN 層 16、 $n$  型 GaN 層 17 および  $n^+$  型 GaN コンタクト層 18 に存在する貫通転位 19 の密度の大幅な低減を図ることができることにより、SJ 縱型 GaN 系 MOSFET の破壊電圧の向上およびリーキ電流の大幅な低減を図ることができるという利点も得ることができる。

20

## 【0098】

## 8. 第 8 の実施の形態

第 8 の実施の形態においては、縱型 GaN 系 MOSFET の製造方法について説明する。

## 【0099】

図 18 に示すように、第 8 の実施の形態においては、 $n$  型 GaN 層 17 上に成長させる  $n^+$  型 GaN コンタクト層 18 の厚さを十分に大きく、例えば 100 ~ 400  $\mu$ m にし、その代わりに第 2 の基板 21 を用いない。 $n^+$  型 GaN コンタクト層 18 の成長には、MOCVD 法のほか、ハイドライド気相エピタキシャル成長またはハイドライド気相エピタキシャル成長 (HVPE) 法を用いることができる。この場合、 $n$  型 GaN 層 17 および  $n^+$  型 GaN コンタクト層 18 の厚さが極めて大きいため、これらの  $n$  型 GaN 層 17 および  $n^+$  型 GaN コンタクト層 18 を成長後、冷却段階で  $n^+$  型 GaN 層 13 の下方の第 1 の基板 11 からなるストライプ状の柱が破断し、第 1 の基板 11 が剥離する。

40

## 【0100】

この後、第 1 の実施の形態と同様に工程を進めて、目的とする SJ 縱型 GaN 系 MOSFET を製造する。

## 【0101】

この第 8 の実施の形態によれば、第 1 の実施の形態と同様な利点に加えて、第 2 の基板 21 が不要となるため、SJ 縱型 GaN 系 MOSFET の製造コストのより一層の低減を図ることができるという利点を得ることができる。

50

## 【0102】

## 9. 第9の実施の形態

第9の実施の形態においては、縦型GaN系MOSFETの製造方法について説明する。

## 【0103】

図19に示すように、第9の実施の形態においては、第1の実施の形態と同様にしてn<sup>+</sup>型GaN層13をシードとしてn型GaN層40を横方向成長させ、引き続いてアンドープまたはp型AlGaN層41を成長させた後、n型GaN層17を連続膜となるまで成長させ、さらにその上にn<sup>+</sup>型GaNコンタクト層18を成長させる。

## 【0104】

次に、n<sup>+</sup>型GaNコンタクト層18上に接着層20(図19においては図示せず)を介して第2の基板21(図19においては図示せず)を貼り付ける。

## 【0105】

次に、n<sup>+</sup>型GaN層13、n型GaN層40、アンドープまたはp型AlGaN層41およびn型GaN層17の全面にゲート絶縁膜25を形成する。

## 【0106】

次に、フォトリソグラフィーにより、n<sup>+</sup>型GaN層13の中央部に対応する部分がストライプ状に開口した所定形状のレジストパターン22(図19においては図示せず)をn<sup>+</sup>型GaN層13、n型GaN層40、アンドープまたはp型AlGaN層41およびn型GaN層17上に形成する。次に、このレジストパターン22をマスクとしてゲート絶縁膜25をウェットエッティングすることにより開口25aを形成する。次に、例えば真空蒸着法やスパッタリング法などにより全面に金属膜を形成した後、この金属膜を所定形状にパターニングすることにより、開口25aの内部のn<sup>+</sup>型GaN層13上にソース電極26を形成するとともに、互いに隣接するn<sup>+</sup>型GaN層13とn<sup>+</sup>型GaN層13との間の部分におけるゲート絶縁膜25上にゲート電極27を形成する。次に、例えば真空蒸着法などにより全面にSiO<sub>2</sub>膜などの絶縁膜28を形成する。次に、この絶縁膜28のうちのソース電極26上の所定部分に開口28aを形成する。次に、例えば真空蒸着法やスパッタリング法などによりこの絶縁膜28の全面に金属膜を形成し、必要に応じてこの金属膜を所定形状にパターニングすることによりソースパッド電極29を形成する。次に、このソースパッド電極29上に第3の基板30を貼り付ける。この第3の基板30は必要に応じて選ばれるが、好適にはAusnなどからなるはんだのほか、熱伝導性の良好なセラミック基板や金属基板など、具体的には、例えば、Si、AlN、Cu、CuW、AlSi、SiCなどからなるものを用いることができる。この後、n<sup>+</sup>型GaNコンタクト層18から接着層20および第2の基板21を剥離する。

## 【0107】

次に、n<sup>+</sup>型GaN層13の上方の、貫通転位19が集中して存在する部分を含む所定部分のn<sup>+</sup>型GaNコンタクト層18およびn型GaN層17の最上部をエッティング除去して凹部31を形成する。次に、例えば真空蒸着法やスパッタリング法などにより全面に例えばSiO<sub>2</sub>膜などの絶縁膜32を形成した後、この絶縁膜32をエッティングにより所定形状にパターニングすることにより凹部31およびその近傍の部分のみ残す。この後、例えば真空蒸着法やスパッタリング法などによりこの絶縁膜33およびn<sup>+</sup>型GaNコンタクト層18の全面に金属膜を形成し、必要に応じてこの金属膜を所定形状にパターニングしてドレイン電極33を形成する。

## 【0108】

以上により、目的とするノーマリーオフ型の縦型GaN系MOSFETを製造することができる。図19に、この縦型GaN系MOSFETのオン時のソース電極26からドレイン電極33への電子の移動経路を矢印で模式的に示す。

## 【0109】

この第9の実施の形態によれば、高耐圧かつ高出力のノーマリーオフ型の縦型GaN系MOSFETを低成本で製造することができる。

10

20

30

40

50

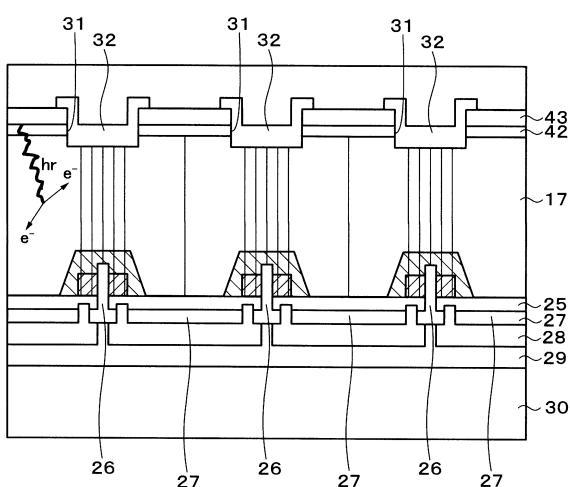

## 【0110】

## 10. 第10の実施の形態

第10の実施の形態においては、FS (Field Stop) - IGBT 縱型GaN系MOSFETの製造方法について説明する。

## 【0111】

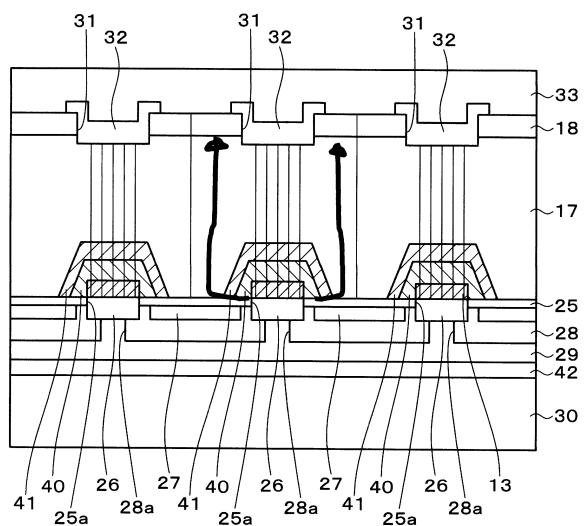

図20に示すように、第10の実施の形態においては、第1の実施の形態と同様にしてn型GaN層17まで成長させた後、その上にフィールドストップ層となるn<sup>+</sup>型GaN層42およびp<sup>+</sup>型GaN層43を順次成長させる。p<sup>+</sup>型GaN層43には例えばMgがドープされ、不純物濃度は例えば $1 \times 10^{18} \sim 1 \times 10^{21} \text{ cm}^{-3}$ である。

## 【0112】

この後、第1の実施の形態と同様に工程を進めて目的とするFS - IGBT 縱型GaN系MOSFETを製造する。

## 【0113】

図20に示すように、このFS - IGBT 縱型GaN系MOSFETにおいては、p<sup>+</sup>型GaN層43とn<sup>+</sup>型GaN層42とにより形成されるpn接合に電流が流れることにより光子(h<sup>-</sup>)が発生し、この光子の入射によりn型GaN層17中に電子(e<sup>-</sup>) - 正孔(e<sup>+</sup>)対が生成されることによりキャリアが増加することで、オン抵抗が低下する伝導度変調効果が得られる。

## 【0114】

この第10の実施の形態によれば、高耐圧かつ高出力のFS - IGBT 縱型GaN系MOSFETを低成本で製造することができる。

## 【0115】

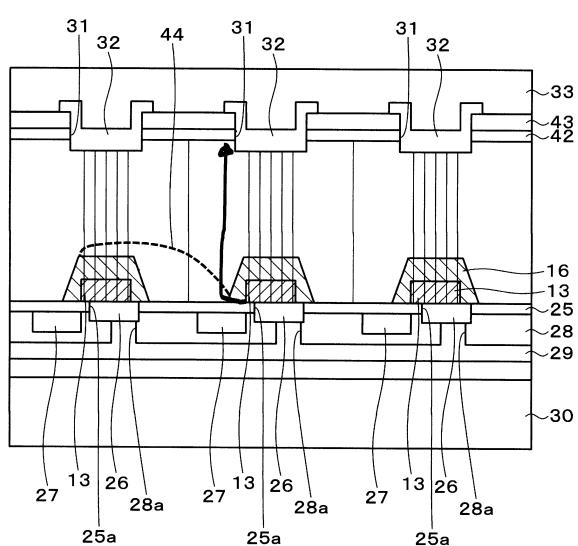

## 11. 第11の実施の形態

第11の実施の形態においては、FS - ノンラッチアップ - IGBT 縱型GaN系MOSFETの製造方法について説明する。

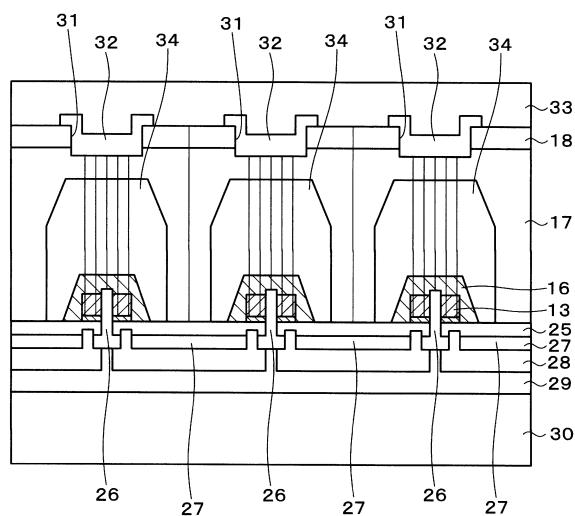

## 【0116】

図22に示すように、第11の実施の形態においては、第1の実施の形態と同様にしてn<sup>+</sup>型GaN層13をシードとしてp型GaN層16を横方向成長させた後、n型GaN層17を連続膜となるまで成長させ、さらにその上にフィールドストップ層となるn<sup>+</sup>型GaN層42およびp<sup>+</sup>型GaN層43を順次成長させる。

## 【0117】

次に、n<sup>+</sup>型GaNコンタクト層18上に接着層20(図20においては図示せず)を介して第2の基板21(図20においては図示せず)を貼り付ける。

## 【0118】

次に、n<sup>+</sup>型GaN層13、p型GaN層16およびn型GaN層17の全面にゲート絶縁膜25を形成する。

## 【0119】

次に、フォトリソグラフィーにより、n<sup>+</sup>型GaN層13から少しづれた部分がストライプ状に開口した所定形状のレジストパターン22(図22においては図示せず)をn<sup>+</sup>型GaN層13、p型GaN層16およびn型GaN層17上に形成する。次に、このレジストパターン22をマスクとしてゲート絶縁膜25をウェットエッティングすることにより開口25aを形成する。次に、例えば真空蒸着法やスパッタリング法などにより全面に金属膜を形成した後、この金属膜を所定形状にパターニングすることにより、開口25aの内部のn<sup>+</sup>型GaN層13上にエミッタ電極を兼用するソース電極26を形成するとともに、p型GaN層16の部分におけるゲート絶縁膜25上にゲート電極27を形成する。次に、例えば真空蒸着法などにより全面にSiO<sub>2</sub>膜などの絶縁膜28を形成する。次に、この絶縁膜28のうちのソース電極26上の所定部分に開口28aを形成する。次に、例えば真空蒸着法やスパッタリング法などによりこの絶縁膜28の全面に金属膜を形成し、必要に応じてこの金属膜を所定形状にパターニングすることによりソースパッド電極29を形成する。次に、このソースパッド電極29の全面に第3の基板30を貼り付ける

10

20

30

40

50

。この第3の基板30は必要に応じて選ばれるが、好適には $\text{AuSn}$ などからなるはんだのほか、熱伝導性の良好なセラミック基板や金属基板など、具体的には、例えば、 $\text{Si}$ 、 $\text{AlN}$ 、 $\text{Cu}$ 、 $\text{CuW}$ 、 $\text{AlSi}$ 、 $\text{SiC}$ などからなるものを用いることができる。この後、 $n^+$ 型 $\text{GaN}$ コンタクト層18から接着層20および第2の基板21を剥離する。

#### 【0120】

次に、 $n^+$ 型 $\text{GaN}$ 層13の上方の、貫通転位19が集中して存在する部分を含む所定部分の $p^+$ 型 $\text{GaN}$ 層43、 $n^+$ 型 $\text{GaN}$ 層42および $n$ 型 $\text{GaN}$ 層17の最上部をエッティング除去して凹部31を形成する。次に、例えば真空蒸着法やスパッタリング法などにより全面に例えば $\text{SiO}_2$ 膜などの絶縁膜32を形成した後、この絶縁膜32をエッティングにより所定形状にパターニングすることにより凹部31およびその近傍の部分のみ残す。この後、例えば真空蒸着法やスパッタリング法などによりこの絶縁膜33および $p^+$ 型 $\text{GaN}$ 層43の全面に金属膜を形成し、必要に応じてこの金属膜を所定形状にパターニングしてドレイン電極33を形成する。10

#### 【0121】

以上により、目的とする $\text{FS-NpnLatchUp-IGBT}$ 縦型 $\text{GaN}$ 系MOSFETを製造することができる。

#### 【0122】

この $\text{FS-NpnLatchUp-IGBT}$ 縦型 $\text{GaN}$ 系MOSFETにおいては、第10の実施の形態と同様にオン抵抗が低下する伝導度変調効果が得られることに加えて、オン時にチャネル層である $n$ 型 $\text{GaN}$ 層17に空乏層44が広がってピンチオフが生じる構造を有することにより、ソース-ドレイン電流をラッチアップ電流以下に制限し、ラッチアップを回避することができ、オフ時には、コレクタを構成する $p^+$ 型 $\text{GaN}$ 層43側に空乏層44が到達するのを $n^+$ 型 $\text{GaN}$ 層42により防止することができる。20

#### 【0123】

この第11の実施の形態によれば、高耐圧かつ高出力の $\text{FS-NpnLatchUp-IGBT}$ 縦型 $\text{GaN}$ 系MOSFETを低コストで製造することができる。

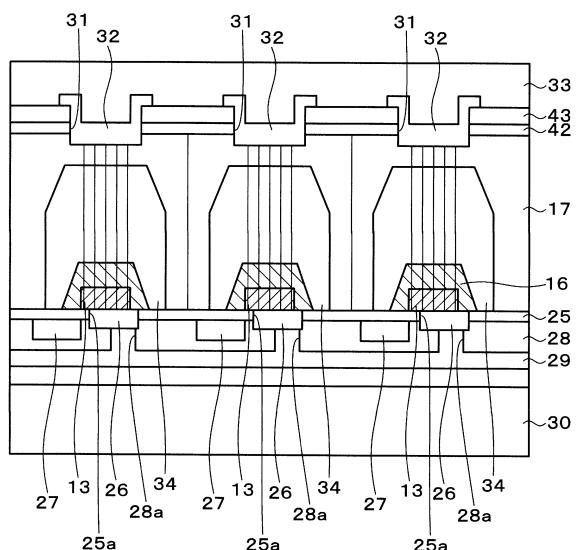

#### 【0124】

##### 12. 第12の実施の形態

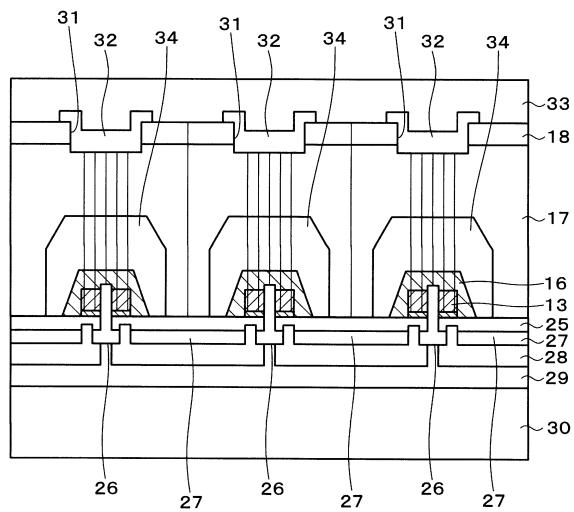

第12の実施の形態においては、 $\text{FS-IGBT-SJ}$ 縦型 $\text{GaN}$ 系MOSFETの製造方法について説明する。30

#### 【0125】

図23に示すように、第12の実施の形態においては、第3の実施の形態と同様にして $n^+$ 型 $\text{GaN}$ 層13をシードとして $p$ 型 $\text{GaN}$ 層16を横方向成長させ、さらに $p$ 型 $\text{GaN}$ 層34を成長させた後、 $n$ 型 $\text{GaN}$ 層17を連続膜となるまで成長させ、さらにその上にフィールドストップ層となる $n^+$ 型 $\text{GaN}$ 層42および $p^+$ 型 $\text{GaN}$ 層43を順次成長させる。

#### 【0126】

この後、第3の実施の形態と同様に工程を進めて目的とする $\text{FS-IGBT-SJ}$ 縦型 $\text{GaN}$ 系MOSFETを製造する。

#### 【0127】

この $\text{FS-IGBT-SJ}$ 縦型 $\text{GaN}$ 系MOSFETにおいては、第10の実施の形態と同様にオン抵抗が低下する伝導度変調効果と、第3の実施の形態と同様に超接合により得られる空乏層拡大効果とを得ることができる。すなわち、この $\text{FS-IGBT-SJ}$ 縦型 $\text{GaN}$ 系MOSFETは、超低オン抵抗かつ高耐圧の縦型 $\text{GaN}$ 系MOSFETを実現することができる。40

#### 【0128】

この第12の実施の形態によれば、高耐圧かつ高出力の $\text{FS-IGBT-SJ}$ 縦型 $\text{GaN}$ 系MOSFETを低コストで製造することができる。

#### 【0129】

##### 13. 第13の実施の形態

10

20

30

40

50

第13の実施の形態においては、FS-ノンラッチアップ-IGBT-SJ縦型GaN系MOSFETの製造方法について説明する。

【0130】

図24に示すように、第13の実施の形態においては、第3の実施の形態と同様にしてn<sup>+</sup>型GaN層13をシードとしてp型GaN層16を横方向成長させ、さらにp型GaN層34を成長させた後、n型GaN層17を連続膜となるまで成長させ、さらにその上にフィールドストップ層となるn<sup>+</sup>型GaN層42およびp<sup>+</sup>型GaN層43を順次成長させる。

【0131】

この後、第11の実施の形態と同様に工程を進めて目的とするFS-ノンラッチアップ-IGBT-SJ縦型GaN系MOSFETを製造する。 10

【0132】

この第13の実施の形態によれば、高耐圧かつ高出力のFS-ノンラッチアップ-IGBT-SJ縦型GaN系MOSFETを低成本で製造することができる。

【0133】

14. 第14の実施の形態

第14の実施の形態においては、GaN系半導体発光素子の製造方法について説明する。

【0134】

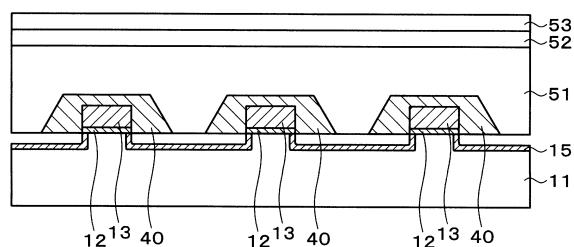

図24に示すように、第14の実施の形態においては、第1の実施の形態と同様にしてストライプ状のn<sup>+</sup>型GaN層13を形成した後、n<sup>+</sup>型GaN層13をシードとしてn型GaN層40を横方向成長させる。次に、n型AlGaNクラッド層51を全面に連続膜となるまで成長させ、さらにその上に例えばIn<sub>x</sub>Ga<sub>1-x</sub>N/In<sub>y</sub>Ga<sub>1-y</sub>N多重量子井戸(MQW)構造の活性層52およびp型AlGaNクラッド層53を順次成長させる。p型AlGaNクラッド層53上には一般的にはさらに、p<sup>+</sup>型GaNコンタクト層が成長される。 20

【0135】

次に、p型AlGaNクラッド層53あるいはその上のp<sup>+</sup>型GaNコンタクト層上に接着層20を介して第2の基板21を貼り付ける。

【0136】

次に、第1の基板11と低温バッファ層12との間を分離することにより、第1の基板11を第2の基板21上のn<sup>+</sup>型GaN層13、n型GaN層40およびn型AlGaNクラッド層51から剥離する。 30

【0137】

次に、第1の基板11の剥離により露出したn<sup>+</sup>型GaN層13、n型GaN層40およびn型AlGaNクラッド層51の表面にn側電極(図示せず)を形成する。

【0138】

次に、このn側電極の全面に第3の基板30を貼り付ける。この後、p型AlGaNクラッド層53あるいはその上のp<sup>+</sup>型GaNコンタクト層から接着層20および第2の基板21を剥離する。 40

【0139】

次に、p型AlGaNクラッド層53あるいはその上のp<sup>+</sup>型GaNコンタクト層上にp側電極を形成する。半導体発光素子が半導体レーザである場合には、例えば、p型AlGaNクラッド層53の上部をストライプ状のリッジ形状にパターニングした後、このリッジ部にコンタクトするようにp側電極を形成する。

【0140】

この後、従来公知のGaN系半導体レーザまたはGaN系発光ダイオードの製造方法に従って目的とするGaN系半導体発光素子を製造する。

【0141】

この第14の実施の形態によれば、GaN系半導体レーザまたはGaN系発光ダイオード

50

ドを Si 基板を用いて容易に製造することができ、製造コストの低減を図ることができる。

【0142】

15. 第15の実施の形態

第15の実施の形態においては、GaN系太陽電池の製造方法について説明する。

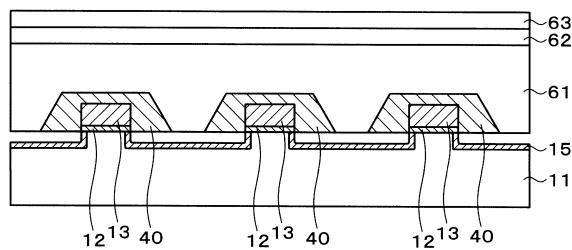

【0143】

図27に示すように、第15の実施の形態においては、第1の実施の形態と同様にしてストライプ状のn<sup>+</sup>型GaN層13を形成した後、n<sup>+</sup>型GaN層13をシードとしてn型GaN層40を横方向成長させる。次に、n型AlGaN層61を全面に連続膜となるまで成長させ、さらにその上に例えればi型AlGaN層62およびp型AlGaN層63を順次成長させる。p型AlGaN層63上には一般的にはp<sup>+</sup>型GaNコンタクト層が成長される。

【0144】

次に、p型AlGaN層63あるいはその上のp<sup>+</sup>型GaNコンタクト層上に接着層20を介して第2の基板21を貼り付ける。

【0145】

次に、第1の基板11と低温バッファ層12との間を分離することにより、第1の基板11を第2の基板21上のn<sup>+</sup>型GaN層13、n型GaN層40およびn型AlGaNクラッド層51から剥離する。

【0146】

次に、第1の基板11の剥離により露出したn<sup>+</sup>型GaN層13、n型GaN層40およびn型AlGaNクラッド層51の表面にカソード電極(図示せず)を形成する。

【0147】

次に、このカソード電極の全面に第3の基板30を貼り付ける。この後、p型AlGaN層63あるいはその上のp<sup>+</sup>型GaNコンタクト層から接着層20および第2の基板21を剥離する。

【0148】

次に、p型AlGaN層53あるいはその上のp<sup>+</sup>型GaNコンタクト層上にアノード電極を形成する。

【0149】

この後、必要な後工程を行って目的とするGaN系太陽電池を製造する。

【0150】

この第15の実施の形態によれば、GaN系太陽電池をSi基板を用いて容易に製造することができ、製造コストの低減を図ることができる。

【0151】

16. 第16の実施の形態

第16の実施の形態においては、縦型GaN系ショットキーバリアダイオードの製造方法について説明する。

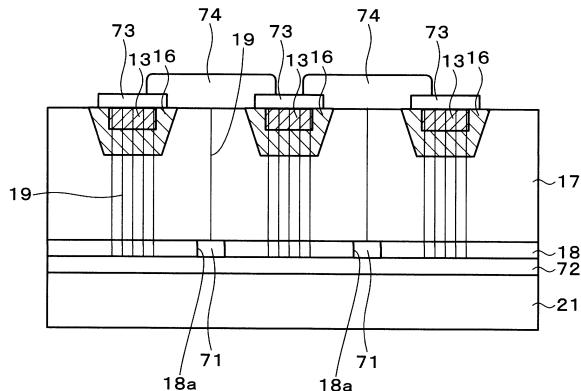

【0152】

図26に示すように、第16の実施の形態においては、第1の実施の形態と同様にしてストライプ状のn<sup>+</sup>型GaN層13を形成した後、n<sup>+</sup>型GaN層13をシードとしてp型GaN層16を横方向成長させる。次に、n型GaN層17を全面に連続膜となるまで成長させ、さらにその上にn<sup>+</sup>型GaNコンタクト層18を成長させる。

【0153】

次に、n<sup>+</sup>型GaNコンタクト層18のうちの互いに隣接するn<sup>+</sup>型GaN層13の間の部分に対応する部分をエッティング除去して開口18aを形成した後、この開口18aの内部にSiO<sub>2</sub>膜などの絶縁膜71を形成し、この絶縁膜71により貫通軌位19を覆う。

【0154】

次に、第2の基板21上にオーミック電極72を設けたものを用意し、n<sup>+</sup>型GaNコ

10

20

30

40

50

ンタクト層 18 上にこの第 2 の基板 21 上のオーミック電極 72 側を貼り付ける。

【0155】

次に、第 1 の基板 11 と低温バッファ層 12 との間を分離することにより、第 1 の基板 11 を第 2 の基板 21 上の  $n^+$  型 GaN 層 13、p 型 GaN 層 16 および n 型 GaN 層 17 から剥離する。

【0156】

次に、第 1 の基板 11 の剥離により露出した面の、貫通転位 19 が露出している  $n^+$  型 GaN 層 13 を覆うように  $SiO_2$  膜などの絶縁膜 73 を形成した後、この絶縁膜 73 で覆われていない部分の p 型 GaN 層 16 および n 型 GaN 層 17 に接触するようにショットキーエミッタ電極 74 を形成する。

10

【0157】

以上により、目的とする縦型 GaN 系ショットキーバリアダイオードを製造することができる。

【0158】

この第 16 の実施の形態によれば、Si 基板を用いて縦型 GaN 系ショットキーバリアダイオードを容易に製造することができ、製造コストの低減を図ることができる。

【0159】

以上、この発明の実施の形態について具体的に説明したが、この発明は、上述の実施の形態に限定されるものではなく、この発明の技術的思想に基づく各種の変形が可能である。

20

【0160】

例えば、上述の実施の形態において挙げた数値、構造、形状、材料、プロセスなどはあくまでも例に過ぎず、必要に応じてこれらと異なる数値、構造、形状、材料、プロセスなどを用いてもよい。また、必要に応じて、第 1 ~ 第 16 の実施の形態のうちの二つ以上を組み合わせてもよい。

【符号の説明】

【0161】

11 ... 第 1 の基板、12 ... 低温バッファ層、13 ...  $n^+$  型 GaN 層、14 ... 絶縁膜またはエッチングマスク、15 ... 成長防止膜、16 ... p 型 GaN 層、17 ... n 型 GaN 層、18 ...  $n^+$  型 GaN コンタクト層、19 ... 貫通転位、20 ... 接着層、21 ... 第 2 の基板、22 ... レジストパターン、23、24 ... 凹部、25 ... ゲート絶縁膜、25a ... 開口、26 ... ソース電極、27 ... ゲート電極、28 ... 絶縁膜、29 ... ソースパッド電極、30 ... 第 3 の基板、31 ... 開口、32 ... 絶縁膜、33 ... ドレイン電極、34 ... p 型 GaN 層、35 ... p<sup>+</sup> 型 GaN コンタクト層、36 ... p<sup>+</sup> 型 GaN 層、37 ... n 型 GaN 層、39 ... AlGaN 層、40 ... n 型 GaN 層、41 ... アンドープまたは p 型 AlGaN 层、42 ...  $n^+$  型 GaN 層、43 ... p<sup>+</sup> 型 GaN 層、44 ... 空乏層、45 ... 凹部、46 ... 2 次元電子ガス、51 ... n 型 AlGaN クラッド層、52 ... 活性層、53 ... p 型 AlGaN クラッド層、61 ... n 型 AlGaN 层、62 ... i 型 AlGaN 层、63 ... p 型 AlGaN 层、71 ... 73 ... 絶縁膜、72 ... オーミック電極、74 ... ショットキーエミッタ電極

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【 図 25 】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

---

フロントページの続き

|                         |                       |

|-------------------------|-----------------------|

| (51)Int.Cl.             | F I                   |

| H 0 1 L 21/02 (2006.01) | H 0 1 L 29/78 6 5 8 F |

|                         | H 0 1 L 29/78 6 5 8 K |

|                         | H 0 1 L 21/20         |

|                         | H 0 1 L 21/02 B       |

(56)参考文献 特開2002-289539 (JP, A)

特開2011-066390 (JP, A)

国際公開第03/012178 (WO, A1)

特開平11-145516 (JP, A)

米国特許出願公開第2008/0054292 (US, A1)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 9 / 7 8

H 0 1 L 2 1 / 3 3 6

H 0 1 L 2 9 / 7 3 9

H 0 1 L 2 1 / 3 3 1

H 0 1 L 2 1 / 2 0

H 0 1 L 2 1 / 2 0 5

H 0 1 L 2 1 / 0 2