(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-39299

(P2005-39299A)

(43) 公開日 平成17年2月10日(2005.2.10)

(51) Int.Cl.<sup>7</sup>

H01L 27/105

F 1

H01L 27/10

4 4 4 B

テーマコード(参考)

5 F 0 8 3

審査請求 有 請求項の数 23 O L (全 58 頁)

|              |                                                                    |

|--------------|--------------------------------------------------------------------|

| (21) 出願番号    | 特願2004-319616 (P2004-319616)                                       |

| (22) 出願日     | 平成16年11月2日 (2004.11.2)                                             |

| (62) 分割の表示   | 特願2001-288468 (P2001-288468)<br>の分割<br>原出願日 平成13年9月21日 (2001.9.21) |

| (31) 優先権主張番号 | 特願2000-316033 (P2000-316033)                                       |

| (32) 優先日     | 平成12年10月17日 (2000.10.17)                                           |

| (33) 優先権主張国  | 日本国 (JP)                                                           |

|          |                                             |

|----------|---------------------------------------------|

| (71) 出願人 | 000005821<br>松下電器産業株式会社<br>大阪府門真市大字門真1006番地 |

| (74) 代理人 | 100077931<br>弁理士 前田 弘                       |

| (74) 代理人 | 100094134<br>弁理士 小山 廣毅                      |

| (74) 代理人 | 100110939<br>弁理士 竹内 宏                       |

| (74) 代理人 | 100110940<br>弁理士 嶋田 高久                      |

| (74) 代理人 | 100113262<br>弁理士 竹内 祐二                      |

| (74) 代理人 | 100115059<br>弁理士 今江 克実                      |

最終頁に続く

(54) 【発明の名称】強誘電体メモリ及びその製造方法

## (57) 【要約】

【課題】 容量絶縁膜を構成する強誘電体膜の特性の劣化を防止することによって、強誘電体メモリの信頼性を向上させる。

【解決手段】 メモリセルトランジスタが形成された半導体基板300上に第1の層間絶縁膜307を形成した後、第1の層間絶縁膜307に、メモリセルトランジスタと接続する第1のプラグ308を形成し、その後、第1の層間絶縁膜307の上に第1のプラグ308と接続する容量下部電極309を形成する。その後、容量下部電極309の上に、強誘電体膜よりなる容量絶縁膜311、及び容量上部電極312を順次形成した後、容量上部電極312の上に導電性水素バリア膜313を形成する。その後、導電性水素バリア膜313を含む第1の層間絶縁膜307の上に第2の層間絶縁膜314を形成した後、第2の層間絶縁膜314に、導電性水素バリア膜313と第2の層間絶縁膜314上の配線316とを接続する第2のプラグ315を形成する。

【選択図】 図23

**【特許請求の範囲】****【請求項 1】**

半導体基板上に形成されたトランジスタと、

前記トランジスタを含む前記半導体基板の上に形成された第1の層間絶縁膜と、

前記第1の層間絶縁膜の上に形成された容量下部電極と、

前記容量下部電極の上に形成された強誘電体膜よりなる容量絶縁膜と、

前記容量絶縁膜の上に形成された容量上部電極と、

前記容量上部電極の上に形成された導電性水素バリア膜と、

前記導電性水素バリア膜を含む前記第1の層間絶縁膜の上に形成された第2の層間絶縁膜と、

前記第2の層間絶縁膜の上に形成された配線と、

前記第1の層間絶縁膜に形成され、前記トランジスタと前記容量下部電極とを接続する第1のプラグと、

前記第2の層間絶縁膜に形成され、前記導電性水素バリア膜と前記配線とを接続する第2のプラグとを備えていることを特徴とする強誘電体メモリ。

**【請求項 2】**

前記容量上部電極の少なくとも一部は、Pt膜又はPtを含む合金膜よりなることを特徴とする請求項1に記載の強誘電体メモリ。

**【請求項 3】**

前記導電性水素バリア膜は、Ti膜、Ta膜、TiON膜、TiN膜、TaN膜、TiAlN膜、TiAlON膜、又は、Ti、Ta、TiON、TiN、TaN、TiAlN若しくはTiAlONを含む合金膜よりなることを特徴とする請求項1に記載の強誘電体メモリ。

**【請求項 4】**

半導体基板上にトランジスタを形成する工程と、

前記トランジスタを含む前記半導体基板の上に第1の層間絶縁膜を形成する工程と、

前記第1の層間絶縁膜に、前記トランジスタと接続する第1のプラグを形成する工程と、

前記第1の層間絶縁膜の上に前記第1のプラグと接続するように容量下部電極を形成する工程と、

前記容量下部電極の上に、強誘電体膜よりなる容量絶縁膜を形成する工程と、

前記容量絶縁膜の上に容量上部電極を形成する工程と、

前記容量上部電極の上に導電性水素バリア膜を形成する工程と、

前記導電性水素バリア膜を含む前記第1の層間絶縁膜の上に第2の層間絶縁膜を形成する工程と、

前記第2の層間絶縁膜に、前記導電性水素バリア膜と接続する第2のプラグを形成する工程と、

前記第2の層間絶縁膜の上に前記第2のプラグと接続するように配線を形成する工程とを備えていることを特徴とする強誘電体メモリの製造方法。

**【請求項 5】**

前記容量上部電極の少なくとも一部は、Pt膜又はPtを含む合金膜よりなることを特徴とする請求項4に記載の強誘電体メモリの製造方法。

**【請求項 6】**

前記導電性水素バリア膜は、Ti膜、Ta膜、TiON膜、TiN膜、TaN膜、TiAlN膜、TiAlON膜、又は、Ti、Ta、TiON、TiN、TaN、TiAlN若しくはTiAlONを含む合金膜よりなることを特徴とする請求項4に記載の強誘電体メモリの製造方法。

**【請求項 7】**

半導体基板上における一の領域に形成されたトランジスタと、

前記半導体基板上における他の領域に形成された導電層と、

前記トランジスタ及び導電層を含む前記半導体基板の上に形成された第1の層間絶縁膜と、

前記第1の層間絶縁膜の上に形成された容量下部電極と、

前記容量下部電極の上に形成された強誘電体膜よりなる容量絶縁膜と、

前記容量絶縁膜の上に形成された容量上部電極と、

前記容量上部電極の上に前記容量上部電極の外側まで延びるように形成された導電性水素バリア膜と、

前記導電性水素バリア膜を含む前記第1の層間絶縁膜の上に形成された第2の層間絶縁膜と、

前記第2の層間絶縁膜の上に形成された配線と、

前記第1の層間絶縁膜に形成され、前記トランジスタと前記容量下部電極とを接続する第1のプラグと、

前記第1の層間絶縁膜に形成され、前記導電層と前記導電性水素バリア膜とを電気的に接続する第2のプラグと、

前記第1の層間絶縁膜及び第2の層間絶縁膜に形成され、前記導電層と前記配線とを接続する第3のプラグとを備えていることを特徴とする強誘電体メモリ。

#### 【請求項8】

前記導電層は、前記半導体基板の表面部に形成された不純物拡散層、又は前記不純物拡散層の表面部がシリサイド化された層であることを特徴とする請求項7に記載の強誘電体メモリ。

#### 【請求項9】

前記第1の層間絶縁膜は下層膜とその上に形成された上層膜とを有しており、

前記導電層は前記下層膜と前記上層膜との間に形成されていることを特徴とする請求項7に記載の強誘電体メモリ。

#### 【請求項10】

前記容量上部電極の少なくとも一部は、Pt膜又はPtを含む合金膜よりなることを特徴とする請求項7に記載の強誘電体メモリ。

#### 【請求項11】

前記導電性水素バリア膜は、Ti膜、Ta膜、TiON膜、TiN膜、TaN膜、TiAlN膜、TiAlON膜、又は、Ti、Ta、TiON、TiN、TaN、TiAlN若しくはTiAlONを含む合金膜よりなることを特徴とする請求項7に記載の強誘電体メモリ。

#### 【請求項12】

前記第1の層間絶縁膜の上に形成された接続パッドをさらに備え、

前記第2のプラグは、前記接続パッドを介して前記容量上部電極と接続することを特徴とする請求項7に記載の強誘電体メモリ。

#### 【請求項13】

半導体基板上における一の領域にトランジスタを形成する工程と、

前記半導体基板上における他の領域に導電層を形成する工程と、

前記トランジスタ及び導電層を含む前記半導体基板の上に第1の層間絶縁膜を形成する工程と、

前記第1の層間絶縁膜に、前記トランジスタと接続する第1のプラグと、前記導電層と接続する第2のプラグとを形成する工程と、

前記第1の層間絶縁膜の上に前記第1のプラグと接続するように容量下部電極を形成する工程と、

前記容量下部電極の上に、強誘電体膜よりなる容量絶縁膜を形成する工程と、

前記容量絶縁膜の上に容量上部電極を形成する工程と、

前記容量上部電極の上に、前記容量上部電極の外側まで延び且つ前記第2のプラグと電気的に接続するように導電性水素バリア膜を形成する工程と、

前記導電性水素バリア膜を含む前記第1の層間絶縁膜の上に第2の層間絶縁膜を形成す

10

20

20

30

40

50

る工程と、

前記第1の層間絶縁膜及び第2の層間絶縁膜に、前記導電層と接続する第3のプラグを形成する工程と、

前記第2の層間絶縁膜の上に前記第3のプラグと接続するように配線を形成する工程とを備えていることを特徴とする強誘電体メモリの製造方法。

#### 【請求項14】

前記容量下部電極を形成する工程は、前記第1の層間絶縁膜の上に前記第2のプラグと接続するように接続パッドを形成する工程を含み、

前記導電性水素バリア膜を形成する工程は、前記導電性水素バリア膜を前記接続パッドと接続するように形成する工程を含むことを特徴とする請求項13に記載の強誘電体メモリの製造方法。 10

#### 【請求項15】

前記容量絶縁膜を形成する工程は、前記容量絶縁膜を、その端部が前記接続パッドの上に位置するように形成する工程を含むことを特徴とする請求項14に記載の強誘電体メモリの製造方法。

#### 【請求項16】

前記導電性水素バリア膜を形成する工程は、前記容量絶縁膜となる絶縁性膜及び前記容量上部電極となる第1の導電性膜をパターン化するために用いられたマスクパターンを用いて、前記導電性水素バリア膜となる第2の導電性膜をパターン化した後、前記導電性水素バリア膜の側面に前記第2のプラグと電気的に接続するように導電性のサイドウォールを形成する工程を含むことを特徴とする請求項13に記載の強誘電体メモリの製造方法。 20

#### 【請求項17】

前記サイドウォールは水素バリア性を有することを特徴とする請求項16に記載の強誘電体メモリの製造方法。

#### 【請求項18】

前記容量下部電極を形成する工程は、前記第1の層間絶縁膜の上に前記第2のプラグと接続するように接続パッドを形成する工程を含み、

前記導電性水素バリア膜を形成する工程は、前記サイドウォールを前記接続パッドと接続するように形成する工程を含むことを特徴とする請求項16に記載の強誘電体メモリの製造方法。 30

#### 【請求項19】

前記容量絶縁膜を形成する工程は、前記容量絶縁膜を、その端部が前記接続パッドの上に位置するように形成する工程を含むことを特徴とする請求項18に記載の強誘電体メモリの製造方法。

#### 【請求項20】

前記導電層は、前記半導体基板の表面部に形成された不純物拡散層、又は前記不純物拡散層の表面部がシリサイド化された層であることを特徴とする請求項13に記載の強誘電体メモリの製造方法。

#### 【請求項21】

前記第1の層間絶縁膜は下層膜とその上に形成された上層膜とを有しており、

前記導電層は前記下層膜と前記上層膜との間に形成されていることを特徴とする請求項13に記載の強誘電体メモリの製造方法。 40

#### 【請求項22】

前記容量上部電極の少なくとも一部は、Pt膜又はPtを含む合金膜よりなることを特徴とする請求項13に記載の強誘電体メモリの製造方法。

#### 【請求項23】

前記導電性水素バリア膜は、Ti膜、Ta膜、TiON膜、TiN膜、TaN膜、TiAlN膜、TiAlON膜、又は、Ti、Ta、TiON、TiN、TaN、TiAlN若しくはTiAlONを含む合金膜よりなることを特徴とする請求項13に記載の強誘電体メモリの製造方法。 50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、容量絶縁膜として強誘電体膜が用いられている容量素子を備えた強誘電体メモリ及びその製造方法に関する。

**【背景技術】****【0002】**

強誘電体メモリを実現するための最重要課題は、容量素子の特性を劣化させることなく集積化を実現するための構造及びその製造方法を開発することである。

**【0003】**

特に、強誘電体膜は酸素原子を持つ層状の酸化物膜であるので、水素雰囲気中では容易に還元され、それによって分極率又は耐圧の低下等といった強誘電体膜の特性の劣化が引き起こされる。一方、半導体メモリの製造工程においては、水素雰囲気中又は還元性雰囲気中の集積化工程が多く用いられている。従って、容量素子の容量絶縁膜として強誘電体膜を使用する場合、耐還元性の強いプロセスを構築することが重要である。

**【0004】**

そこで、従来、強誘電体メモリの製造工程における容量素子の特性劣化を防ぐために、容量素子を形成した後の工程での、水素の発生量の低減若しくは還元性雰囲気の抑制が図られたり、又は、絶縁性水素バリア膜により容量素子部を被覆する等の工夫がなされてきた。

**【0005】**

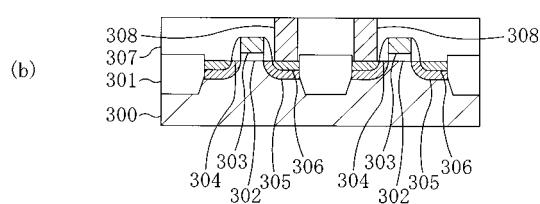

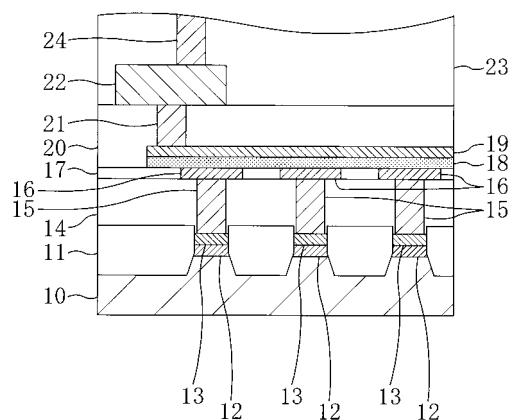

以下、第1の従来例に係る強誘電体メモリについて図36を参照しながら説明する。

**【0006】**

図36に示すように、半導体基板10の表面部には、STI(shallow trench isolation)構造を有する素子分離領域11が形成されていると共に、半導体基板10における素子分離領域11により囲まれた領域の表面部には、下層となる低濃度不純物拡散層12及び上層となる高濃度不純物拡散層13が形成されている。低濃度不純物拡散層12及び高濃度不純物拡散層13は、メモリセルを構成するトランジスタ(以下、メモリセルトランジスタと称する)のソース領域又はドレイン領域となる。

**【0007】**

また、メモリセルトランジスタが形成されている半導体基板10上には第1の層間絶縁膜14が形成されていると共に、第1の層間絶縁膜14には、高濃度不純物拡散層13と接続し且つタングステンよりなる第1のプラグ15が形成されている。第1の層間絶縁膜14の上には、酸素バリア性を有する導電性膜よりも且つ第1のプラグ15の上面を覆う容量下部電極16が形成されている。容量下部電極16同士の間の領域には、絶縁膜17が、その上面と容量下部電極16の上面とが面一になるように形成されている。

**【0008】**

また、容量下部電極16の上には、強誘電体膜よりもなる容量絶縁膜18が容量下部電極16の上面を覆うように形成されていると共に、容量絶縁膜18の上には、Pt(白金)よりもなる容量上部電極19が容量絶縁膜18の上面を覆うように形成されている。これにより、容量下部電極16、容量絶縁膜18及び容量上部電極19よりもなる容量素子が形成される。

**【0009】**

また、容量素子を含む第1の層間絶縁膜14の上には、第2の層間絶縁膜20が形成されていると共に、第2の層間絶縁膜20には、容量上部電極19と接続し且つタングステンよりなる第2のプラグ21が形成されている。

**【0010】**

また、第2の層間絶縁膜20の上には、第2のプラグ21と接続し且つアルミニウム等よりもなる配線22が形成されていると共に、配線22を含む第2の層間絶縁膜20の上には、第3の層間絶縁膜23が形成されている。第3の層間絶縁膜23には、配線22と接

10

20

30

40

50

続する第3のプラグ24が形成されている。

【0011】

図示は省略しているが、第3の層間絶縁膜23の上には、さらに上層の層間絶縁膜、配線又は表面保護膜等が形成されており、それによって強誘電体メモリが完成する。

【0012】

第1の従来例に係る強誘電体メモリの構造によると、集積化を実現できる。

【0013】

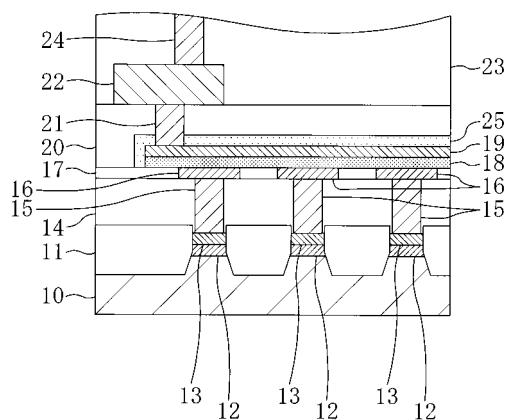

以下、第2の従来例に係る強誘電体メモリについて図37を参照しながら説明する。

【0014】

第2の従来例に係る強誘電体メモリが第1の従来例と異なっている点は、図37に示すように、容量下部電極16、容量絶縁膜18及び容量上部電極19により構成される容量素子部を絶縁性水素バリア膜25が被覆していることである（特開平11-121704 参照）。尚、絶縁性水素バリア膜25としては、SiN膜、SiON膜、TiO<sub>2</sub>膜、又はTaO<sub>x</sub>（但し $x > 0$ ）膜等が用いられる。

【0015】

第2の従来例に係る強誘電体メモリの構造によると、製造工程中における容量素子の特性劣化を防止できる。

【発明の開示】

【発明が解決しようとする課題】

【0016】

しかしながら、第1の従来例においては、容量上部電極19と配線22とを接続する第2のプラグ21を形成するためのコンタクトホールを第2の層間絶縁膜20に形成したときに、容量上部電極19の一部が露出する結果、エッティングガス又はレジストに含まれる水素が容量上部電極19つまりPt膜に吸収されてしまう。また、前記のコンタクトホールに第2のプラグ21を埋め込むために、WF<sub>6</sub>（6フッ化タンゲステン）ガスを水素ガス又はシランガス（ともにWF<sub>6</sub>ガスを還元してW（タンゲステン）を生成する）等と共に用いたときにも、水素（シランガスが分解されて生成した水素も含む）が容量上部電極19を構成するPt膜に吸収されてしまう。さらに、Pt膜に吸収された水素は、後の工程で活性の高い水素（以下、活性水素と称する）としてPt膜から吐き出される。すなわち、Pt膜は触媒作用を有している。その結果、Pt膜の触媒作用に起因して生じた活性水素によって、容量絶縁膜18を構成する強誘電体膜における第2のプラグ21の近傍部分が還元されて該近傍部分から酸素が失われる所以、強誘電体膜の特性が劣化し、それによって強誘電体メモリにピット不良等が発生することがあった。

【0017】

それに対して、第2の従来例においては、図37に示すように、容量素子部を絶縁性水素バリア膜25が被覆している一方、第2のプラグ21を形成するためのコンタクトホールの下部を絶縁性水素バリア膜25に形成したときに、容量上部電極19の一部が露出するので、結局、第1の従来例と同様の問題が生じる可能性が高い。

【0018】

また、第1又は第2の従来例において、容量上部電極19の材料として、強誘電体膜の結晶を成長させるとき（通常、容量上部電極19の形成後に行なわれる）に有利なPt膜を使用しない場合でも、容量絶縁膜18を構成する強誘電体膜における第2のプラグ21の近傍部分が水素によってダメージを受ける事態を完全に防止することは難しい。

【0019】

前記に鑑み、本発明は、容量絶縁膜を構成する強誘電体膜の特性の劣化を防止することによって、強誘電体メモリの信頼性を向上させることを目的とする。

【課題を解決するための手段】

【0020】

前記の目的を達成するために、本発明に係る第1の強誘電体メモリは、半導体基板上における一の領域に形成されたトランジスタと、半導体基板上における他の領域に形成され

た導電層と、トランジスタ及び導電層を含む半導体基板の上に形成された第1の層間絶縁膜と、第1の層間絶縁膜の上に形成された容量下部電極と、容量下部電極の上に形成された強誘電体膜よりなる容量絶縁膜と、容量絶縁膜の上に容量絶縁膜の外側まで延びるように形成された容量上部電極と、容量上部電極を含む第1の層間絶縁膜の上に形成された第2の層間絶縁膜と、第2の層間絶縁膜の上に形成された配線と、第1の層間絶縁膜に形成され、トランジスタと容量下部電極とを接続する第1のプラグと、第1の層間絶縁膜に形成され、導電層と容量上部電極とを電気的に接続する第2のプラグと、第1の層間絶縁膜及び第2の層間絶縁膜に形成され、導電層と配線とを接続する第3のプラグとを備えている。

## 【0021】

10

第1の強誘電体メモリによると、半導体基板上に形成されたトランジスタが、該トランジスタ上の第1の層間絶縁膜に形成された第1のプラグを介して、第1の層間絶縁膜上の容量下部電極と接続されている。また、容量絶縁膜の上に容量絶縁膜の外側まで延びるように形成された容量上部電極が、第1の層間絶縁膜に形成された第2のプラグを介して、半導体基板上に形成された導電層と電気的に接続されている。さらに、容量上部電極上に第2の層間絶縁膜を介して形成された配線が、第1の層間絶縁膜及び第2の層間絶縁膜に形成された第3のプラグを介して導電層と接続されている。このため、容量上部電極の形成前に、具体的には、トランジスタと容量下部電極とを接続する第1のプラグの形成とともに、容量上部電極と導電層とを電気的に接続する第2のプラグを第1の層間絶縁膜に形成できる。これにより、第2のプラグ、導電層及び第3のプラグを介して容量上部電極と配線とを電気的に接続することができる。すなわち、予め容量素子よりも下側に形成されている第2のプラグ及び導電層を用いて、容量上部電極と配線とを電気的に接続することができる。従って、容量上部電極の形成後に、容量上部電極と配線とを直接接続するプラグを形成するためのコントクトホールを形成する必要がないので、容量上部電極が露出して水素雰囲気又は還元性雰囲気にさらされる事態を回避できる。その結果、容量上部電極として強い触媒作用を有するPt膜を用いる場合にも、容量絶縁膜を構成する強誘電体膜の特性の劣化を防止して、強誘電体メモリの信頼性を向上させることができる。

20

## 【0022】

30

本発明に係る第2の強誘電体メモリは、半導体基板上における一の領域に形成されたトランジスタと、半導体基板上における他の領域に形成された導電層と、トランジスタ及び導電層を含む半導体基板の上に形成された第1の層間絶縁膜と、第1の層間絶縁膜の上に形成された容量下部電極と、容量下部電極の上に容量下部電極の外側まで延びるように形成された強誘電体膜よりなる容量絶縁膜と、容量絶縁膜における容量下部電極の外側に形成されている部分に設けられた開口部と、開口部を含む容量絶縁膜の上に形成された容量上部電極と、容量上部電極を含む第1の層間絶縁膜の上に形成された第2の層間絶縁膜と、第2の層間絶縁膜の上に形成された配線と、第1の層間絶縁膜に形成され、トランジスタと容量下部電極とを接続する第1のプラグと、第1の層間絶縁膜に形成され、導電層と容量上部電極とを開口部を介して電気的に接続する第2のプラグと、第1の層間絶縁膜及び第2の層間絶縁膜に形成され、導電層と配線とを接続する第3のプラグとを備えている。

40

## 【0023】

50

第2の強誘電体メモリによると、半導体基板上に形成されたトランジスタが、該トランジスタ上の第1の層間絶縁膜に形成された第1のプラグを介して、第1の層間絶縁膜上の容量下部電極と接続されている。また、容量下部電極の外側まで延び且つ該外側に開口部を有する容量絶縁膜の上に形成された容量上部電極が、第1の層間絶縁膜に形成された第2のプラグを介して、半導体基板上に形成された導電層と電気的に接続されている。さらに、容量上部電極上に第2の層間絶縁膜を介して形成された配線が、第1の層間絶縁膜及び第2の層間絶縁膜に形成された第3のプラグを介して導電層と接続されている。このため、容量上部電極の形成前に、具体的には、トランジスタと容量下部電極とを接続する第1のプラグの形成とともに、容量上部電極と導電層とを電気的に接続する第2のプラグを

第1の層間絶縁膜に形成できる。これにより、第2のプラグ、導電層及び第3のプラグを介して容量上部電極と配線とを電気的に接続することができる。すなわち、予め容量素子よりも下側に形成されている第2のプラグ及び導電層を用いて、容量上部電極と配線とを電気的に接続することができる。従って、容量上部電極の形成後に、容量上部電極と配線とを直接接続するプラグを形成するためのコンタクトホールを形成する必要がないので、容量上部電極が露出して水素雰囲気又は還元性雰囲気にさらされる事態を回避できる。その結果、容量上部電極として強い触媒作用を有するP<sub>t</sub>膜を用いる場合にも、容量絶縁膜を構成する強誘電体膜の特性の劣化を防止して、強誘電体メモリの信頼性を向上させることができる。

## 【0024】

10

また、第2の強誘電体メモリによると、容量絶縁膜に設けた開口部を介して容量上部電極と第2のプラグとを接続するため、容量上部電極の段差は開口部の周縁部に沿って形成される。具体的には、開口部の形状を例えば方形にすると、容量上部電極の段差は開口部の周縁部である4辺に沿って4方向に形成される。このため、容量上部電極形成材料の段差部における被覆率に方向依存性があつても、容量上部電極の段差が容量絶縁膜の1端辺に沿って1方向に形成されている場合（例えば第1の強誘電体メモリ）と比べて、容量上部電極と第2のプラグとの間の電流パスが確実に確保される。また、容量絶縁膜となる絶縁性膜に開口部を設けた後、該絶縁性膜と容量上部電極となる導電性膜とを同時にパターン化することによって、容量絶縁膜形成用のマスクパターンと容量上部電極形成用のマスクパターンとの間でマスク合わせマージンを考慮する必要がなくなる。その結果、強誘電体メモリのセルサイズを小さくでき、それによってメモリセルアレイ全体の占有面積を縮小することができる。

20

## 【0025】

本発明に係る第3の強誘電体メモリは、半導体基板上に形成されたトランジスタと、トランジスタを含む半導体基板の上に形成された第1の層間絶縁膜と、第1の層間絶縁膜の上に形成された容量下部電極と、容量下部電極の上に形成された強誘電体膜よりなる容量絶縁膜と、容量絶縁膜の上に形成された容量上部電極と、容量上部電極の上に形成された導電性水素バリア膜と、導電性水素バリア膜を含む第1の層間絶縁膜の上に形成された第2の層間絶縁膜と、第2の層間絶縁膜の上に形成された配線と、第1の層間絶縁膜に形成され、トランジスタと容量下部電極とを接続する第1のプラグと、第2の層間絶縁膜に形成され、導電性水素バリア膜と配線とを接続する第2のプラグとを備えている。

30

## 【0026】

第3の強誘電体メモリによると、半導体基板上に形成されたトランジスタが、該トランジスタ上の第1の層間絶縁膜に形成された第1のプラグを介して、第1の層間絶縁膜上の容量下部電極と接続されている。また、容量下部電極の上に容量絶縁膜を介して形成された容量上部電極が導電性水素バリア膜によって覆われている。さらに、導電性水素バリア膜上に第2の層間絶縁膜を介して形成された配線が、第2の層間絶縁膜に形成された第2のプラグを介して導電性水素バリア膜と接続されている。このため、導電性水素バリア膜及び第2のプラグ（導電性水素バリア膜と配線とを接続する）を介して容量上部電極と配線とを電気的に接続することができる。従って、容量上部電極の形成後に、容量上部電極と配線とを直接接続するプラグを形成するためのコンタクトホールを形成する必要がないので、容量上部電極が露出して水素雰囲気又は還元性雰囲気にさらされる事態を回避できる。その結果、容量上部電極として強い触媒作用を有するP<sub>t</sub>膜を用いる場合にも、容量絶縁膜を構成する強誘電体膜の特性の劣化を防止して、強誘電体メモリの信頼性を向上させることができる。

40

## 【0027】

また、第3の強誘電体メモリによると、導電性水素バリア膜によって容量素子が覆われているため、容量素子の耐還元性を向上させることができる。

## 【0028】

本発明に係る第4の強誘電体メモリは、半導体基板上における一の領域に形成されたト

50

ランジスタと、半導体基板上における他の領域に形成された導電層と、トランジスタ及び導電層を含む半導体基板の上に形成された第1の層間絶縁膜と、第1の層間絶縁膜の上に形成された容量下部電極と、容量下部電極の上に形成された強誘電体膜よりなる容量絶縁膜と、容量絶縁膜の上に形成された容量上部電極と、容量上部電極の上に容量上部電極の外側まで延びるように形成された導電性水素バリア膜と、導電性水素バリア膜を含む第1の層間絶縁膜の上に形成された第2の層間絶縁膜と、第2の層間絶縁膜の上に形成された配線と、第1の層間絶縁膜に形成され、トランジスタと容量下部電極とを接続する第1のプラグと、第1の層間絶縁膜に形成され、導電層と導電性水素バリア膜とを電気的に接続する第2のプラグと、第1の層間絶縁膜及び第2の層間絶縁膜に形成され、導電層と配線とを接続する第3のプラグとを備えている。

10

## 【0029】

第4の強誘電体メモリによると、半導体基板上に形成されたトランジスタが、トランジスタ上の第1の層間絶縁膜に形成された第1のプラグを介して、第1の層間絶縁膜上の容量下部電極と接続されている。また、容量下部電極の上に容量絶縁膜を介して形成された容量上部電極が導電性水素バリア膜によって覆われていると共に、該導電性水素バリア膜が、第1の層間絶縁膜に形成された第2のプラグを介して、半導体基板上に形成された導電層と電気的に接続されている。さらに、導電性水素バリア膜上に第2の層間絶縁膜を介して形成された配線が、第1の層間絶縁膜及び第2の層間絶縁膜に形成された第3のプラグを介して導電層と接続されている。このため、容量上部電極の形成前に、具体的には、トランジスタと容量下部電極とを接続する第1のプラグの形成と同時に、導電性水素バリア膜と導電層とを接続する第2のプラグを第1の層間絶縁膜に形成できる。これにより、導電性水素バリア膜、第2のプラグ、導電層及び第3のプラグを介して容量上部電極と配線とを電気的に接続することができる。すなわち、予め容量素子よりも下側に形成されている第2のプラグ及び導電層を用いて、容量上部電極と配線とを電気的に接続することができる。従って、容量上部電極の形成後に、容量上部電極と配線とを直接接続するプラグを形成するためのコンタクトホールを形成する必要がないので、容量上部電極が露出して水素雰囲気又は還元性雰囲気にさらされる事態を回避できる。その結果、容量上部電極として強い触媒作用を有するPt膜を用いる場合にも、容量絶縁膜を構成する強誘電体膜の特性の劣化を防止して、強誘電体メモリの信頼性を向上させることができる。

20

## 【0030】

また、第4の強誘電体メモリによると、導電性水素バリア膜によって容量素子が覆われているため、容量素子の耐還元性を向上させることができる。

30

## 【0031】

第1、第2又は第4の強誘電体メモリにおいて、導電層は、半導体基板の表面部に形成された不純物拡散層、又は前記不純物拡散層の表面部がシリサイド化された層であることが好ましい。

## 【0032】

このようにすると、導電層として、半導体基板上に形成されたポリシリコン層等を用いる場合と比べて、導電層を低抵抗化できる。

40

## 【0033】

第1、第2又は第4の強誘電体メモリにおいて、第1の層間絶縁膜は下層膜とその上に形成された上層膜とを有しており、導電層は下層膜と上層膜との間に形成されていることが好ましい。

## 【0034】

このようにすると、導電層として、半導体基板の表面部に形成された不純物拡散層を用いる場合と比べて、基板電位を簡単に設定できると共に強誘電体メモリのセルサイズを小さくできる。また、導電層と接続する第2又は第3のプラグが埋め込まれるホールのアスペクト比が小さくなるので、各プラグの形成不良や高抵抗化を防止できる。

## 【0035】

第1、第2、第3又は第4の強誘電体メモリにおいて、容量上部電極の少なくとも一部

50

は、Pt膜又はPtを含む合金膜よりなることが好ましい。

【0036】

このようにすると、容量絶縁膜を構成する強誘電体膜の結晶を、整合性の良いPt結晶面から十分に成長させることができる。

【0037】

第3又は第4の強誘電体メモリにおいて、導電性水素バリア膜は、Ti膜、Ta膜、TiON膜、TiN膜、TaN膜、TiAlN膜、TiAlON膜、又は、Ti、Ta、TiON、TiN、TaN、TiAlN若しくはTiAlONを含む合金膜よりなることが好ましい。

【0038】

このようにすると、容量素子の耐還元性を確実に向上させることができると共に、導電性水素バリア膜を介して容量上部電極とプラグ等とを電気的に確実に接続することができる。

【0039】

本発明に係る第1の強誘電体メモリの製造方法は、半導体基板上における一の領域にトランジスタを形成する工程と、半導体基板上における他の領域に導電層を形成する工程と、トランジスタ及び導電層を含む半導体基板の上に第1の層間絶縁膜を形成する工程と、第1の層間絶縁膜に、トランジスタと接続する第1のプラグと、導電層と接続する第2のプラグとを形成する工程と、第1の層間絶縁膜の上に第1のプラグと接続するように容量下部電極を形成する工程と、容量下部電極の上に、強誘電体膜よりなる容量絶縁膜を形成する工程と、容量絶縁膜の上に、容量絶縁膜の外側まで延び且つ第2のプラグと電気的に接続するように容量上部電極を形成する工程と、容量上部電極を含む第1の層間絶縁膜の上に第2の層間絶縁膜を形成する工程と、第1の層間絶縁膜及び第2の層間絶縁膜に、導電層と接続する第3のプラグを形成する工程と、第2の層間絶縁膜の上に第3のプラグと接続するように配線を形成する工程とを備えている。

【0040】

第1の強誘電体メモリの製造方法によると、トランジスタ及び導電層が形成された半導体基板上に第1の層間絶縁膜を形成した後、第1の層間絶縁膜に、トランジスタと接続する第1のプラグと、導電層と接続する第2のプラグとを形成する。その後、第1の層間絶縁膜の上に第1のプラグと接続する容量下部電極を形成した後、容量下部電極の上に、強誘電体膜よりなる容量絶縁膜、及び容量絶縁膜の外側まで延び且つ第2のプラグと電気的に接続する容量上部電極を順次形成する。その後、容量上部電極を含む第1の層間絶縁膜の上に第2の層間絶縁膜を形成した後、第1の層間絶縁膜及び第2の層間絶縁膜に、導電層と第2の層間絶縁膜上の配線とを接続する第3のプラグを形成する。このため、容量上部電極の形成前に、具体的には、トランジスタと容量下部電極とを接続する第1のプラグの形成と同時に、容量上部電極と導電層とを電気的に接続する第2のプラグを第1の層間絶縁膜に形成できる。これにより、第2のプラグ、導電層及び第3のプラグを介して容量上部電極と配線とを電気的に接続することができる。すなわち、予め容量素子よりも下側に形成されている第2のプラグ及び導電層を用いて、容量上部電極と配線とを電気的に接続することができる。従って、容量上部電極の形成後に、容量上部電極と配線とを直接接続するプラグを形成するためのコンタクトホールを形成する必要がないので、容量上部電極が露出して水素雰囲気又は還元性雰囲気にさらされる事態を回避できる。その結果、容量上部電極として強い触媒作用を有するPt膜を用いる場合にも、容量絶縁膜を構成する強誘電体膜の特性の劣化を防止して、強誘電体メモリの信頼性を向上させることができる。

【0041】

第1の強誘電体メモリの製造方法において、容量下部電極を形成する工程は、第1の層間絶縁膜の上に第2のプラグと接続するように接続パッドを形成する工程を含み、容量上部電極を形成する工程は、容量上部電極を接続パッドと接続するように形成する工程を含むことが好ましい。

10

20

30

40

50

## 【0042】

このようにすると、容量下部電極の材料として用いられ且つ酸素バリア性を有する導電性膜を第2のプラグの上面全体を覆うようにパターン化することによって、容量下部電極の形成と同時に接続パッドを形成できる。このため、工程の増加を招くことなく、第2のプラグの酸化を防止でき且つ容量上部電極と第2のプラグとを接続パッドを介して接続できる。

## 【0043】

容量下部電極を形成する工程が接続パッドを形成する工程を含む場合、容量絶縁膜を形成する工程は、容量絶縁膜を、その端部が接続パッドの上に位置するように形成する工程を含むことが好ましい。

10

## 【0044】

このようにすると、容量絶縁膜となる絶縁性膜に対して大きなエッチング選択比を有する導電性膜を接続パッドの材料として用いると共に、該接続パッドをエッチングストップーとして前記の絶縁性膜をパターン化することによって、オーバーエッチングに起因する段差形成を防止しながら容量絶縁膜を形成できる。

## 【0045】

第1の強誘電体メモリの製造方法において、容量上部電極を形成する工程は、容量絶縁膜となる絶縁性膜をパターン化するために用いられたマスクパターンを用いて、容量上部電極となる導電性膜をパターン化した後、容量上部電極の側面に第2のプラグと電気的に接続するように導電性のサイドウォールを形成する工程を含むことが好ましい。

20

## 【0046】

このようにすると、製造工程で用いられるマスクパターンの数を低減できると共に、容量上部電極と第2のプラグとをサイドウォールを介して電気的に接続できる。

## 【0047】

容量上部電極を形成する工程がサイドウォールを形成する工程を含む場合、容量下部電極を形成する工程は、第1の層間絶縁膜の上に第2のプラグと接続するように接続パッドを形成する工程を含み、容量上部電極を形成する工程は、サイドウォールを接続パッドと接続するように形成する工程を含むことが好ましい。

## 【0048】

このようにすると、容量下部電極の材料として用いられ且つ酸素バリア性を有する導電性膜を第2のプラグの上面全体を覆うようにパターン化することによって、容量下部電極の形成と同時に接続パッドを形成できる。このため、工程の増加を招くことなく、第2のプラグの酸化を防止でき且つサイドウォールと第2のプラグとを接続パッドを介して接続できる。

30

## 【0049】

容量上部電極を形成する工程がサイドウォールを形成する工程を含み、且つ容量下部電極を形成する工程が接続パッドを形成する工程を含む場合、容量絶縁膜を形成する工程は、容量絶縁膜を、その端部が接続パッドの上に位置するように形成する工程を含むことが好ましい。

## 【0050】

このようにすると、容量絶縁膜となる絶縁性膜に対して大きなエッチング選択比を有する導電性膜を接続パッドの材料として用いると共に、該接続パッドをエッチングストップーとして前記の絶縁性膜をパターン化することによって、オーバーエッチングに起因する段差形成を防止しながら容量絶縁膜を形成できる。

40

## 【0051】

本発明に係る第2の強誘電体メモリの製造方法は、半導体基板上における一の領域にトランジスタを形成する工程と、半導体基板上における他の領域に導電層を形成する工程と、トランジスタ及び導電層を含む半導体基板の上に第1の層間絶縁膜を形成する工程と、第1の層間絶縁膜に、トランジスタと接続する第1のプラグと、導電層と接続する第2のプラグとを形成する工程と、第1の層間絶縁膜の上に第1のプラグと接続するように容量

50

下部電極を形成する工程と、容量下部電極の上に、少なくとも第2のプラグの上側まで伸び且つ強誘電体膜よりなる容量絶縁膜を形成する工程と、容量絶縁膜における第2のプラグの上側に形成されている部分に開口部を形成する工程と、開口部を含む容量絶縁膜の上に、開口部を介して第2のプラグと電気的に接続するように容量上部電極を形成する工程と、容量上部電極を含む第1の層間絶縁膜の上に第2の層間絶縁膜を形成する工程と、第1の層間絶縁膜及び第2の層間絶縁膜に、導電層と接続する第3のプラグを形成する工程と、第2の層間絶縁膜の上に第3のプラグと接続するように配線を形成する工程とを備えている。

#### 【0052】

第2の強誘電体メモリの製造方法によると、トランジスタ及び導電層が形成された半導体基板上に第1の層間絶縁膜を形成した後、第1の層間絶縁膜に、トランジスタと接続する第1のプラグと、導電層と接続する第2のプラグとを形成する。その後、第1の層間絶縁膜の上に第1のプラグと接続する容量下部電極を形成した後、容量下部電極の上に、第2のプラグの上側まで伸び且つ強誘電体膜よりなる容量絶縁膜を形成する。その後、容量絶縁膜における第2のプラグの上側に形成されている部分に開口部を形成した後、該開口部を介して第2のプラグと電気的に接続するように容量上部電極を形成する。その後、容量上部電極を含む第1の層間絶縁膜の上に第2の層間絶縁膜を形成した後、第1の層間絶縁膜及び第2の層間絶縁膜に、導電層と第2の層間絶縁膜上の配線とを接続する第3のプラグを形成する。このため、容量上部電極の形成前に、具体的には、トランジスタと容量下部電極とを接続する第1のプラグの形成と同時に、容量上部電極と導電層とを電気的に接続する第2のプラグを第1の層間絶縁膜に形成できる。これにより、第2のプラグ、導電層及び第3のプラグを介して容量上部電極と配線とを電気的に接続することができる。すなわち、予め容量素子よりも下側に形成されている第2のプラグ及び導電層を用いて、容量上部電極と配線とを電気的に接続することができる。従って、容量上部電極の形成後に、容量上部電極と配線とを直接接続するプラグを形成するためのコンタクトホールを形成する必要がないので、容量上部電極が露出して水素雰囲気又は還元性雰囲気にさらされる事態を回避できる。その結果、容量上部電極として強い触媒作用を有するPt膜を用いる場合にも、容量絶縁膜を構成する強誘電体膜の特性の劣化を防止して、強誘電体メモリの信頼性を向上させることができる。

#### 【0053】

また、第2の強誘電体メモリの製造方法によると、容量絶縁膜に設けた開口部を介して容量上部電極と第2のプラグとを接続するため、容量上部電極の段差は開口部の周縁部に沿って形成される。具体的には、開口部の形状を例えば方形にすると、容量上部電極の段差は開口部の周縁部である4辺に沿って4方向に形成される。このため、容量上部電極形成材料の段差部における被覆率に方向依存性があっても、容量上部電極の段差が容量絶縁膜の1端辺に沿って1方向に形成される場合（例えば第1の強誘電体メモリの製造方法）と比べて、容量上部電極と第2のプラグとの間の電流バスが確実に確保される。

#### 【0054】

第2の強誘電体メモリの製造方法において、容量下部電極を形成する工程は、第1の層間絶縁膜の上に第2のプラグと接続するように接続パッドを形成する工程を含み、容量上部電極を形成する工程は、容量上部電極を接続パッドと接続するように形成する工程を含むことが好ましい。

#### 【0055】

このようにすると、容量下部電極の材料として用いられ且つ酸素バリア性を有する導電性膜を第2のプラグの上面全体を覆うようにパターン化することによって、容量下部電極の形成と同時に接続パッドを形成できる。このため、工程の増加を招くことなく、第2のプラグの酸化を防止でき且つ容量上部電極と第2のプラグとを接続パッドを介して接続できる。

#### 【0056】

第2の強誘電体メモリの製造方法において、開口部を形成する工程は容量絶縁膜となる

10

20

30

40

50

絶縁性膜をパターン化する前に行なわれ、容量上部電極を形成する工程は、容量絶縁膜となる絶縁性膜と、容量上部電極となる導電性膜とを同時にパターン化する工程を含むことが好ましい。

【0057】

このようにすると、容量絶縁膜形成用のマスクパターンと容量上部電極形成用のマスクパターンとの間でマスク合わせマージンを考慮する必要がなくなる結果、強誘電体メモリのセルサイズを小さくでき、それによってメモリセルアレイ全体の占有面積を縮小することができる。

【0058】

本発明に係る第3の強誘電体メモリの製造方法は、半導体基板上にトランジスタを形成する工程と、トランジスタを含む半導体基板の上に第1の層間絶縁膜を形成する工程と、第1の層間絶縁膜に、トランジスタと接続する第1のプラグを形成する工程と、第1の層間絶縁膜の上に第1のプラグと接続するように容量下部電極を形成する工程と、容量下部電極の上に、強誘電体膜よりなる容量絶縁膜を形成する工程と、容量絶縁膜の上に容量上部電極を形成する工程と、容量上部電極の上に導電性水素バリア膜を形成する工程と、導電性水素バリア膜を含む第1の層間絶縁膜の上に第2の層間絶縁膜を形成する工程と、第2の層間絶縁膜に、導電性水素バリア膜と接続する第2のプラグを形成する工程と、第2の層間絶縁膜の上に第2のプラグと接続するように配線を形成する工程とを備えている。

【0059】

第3の強誘電体メモリの製造方法によると、トランジスタが形成された半導体基板上に第1の層間絶縁膜を形成した後、第1の層間絶縁膜に、トランジスタと接続する第1のプラグを形成し、その後、第1の層間絶縁膜の上に第1のプラグと接続する容量下部電極を形成する。その後、容量下部電極の上に、強誘電体膜よりなる容量絶縁膜、及び容量上部電極を順次形成した後、容量上部電極の上に導電性水素バリア膜を形成する。その後、導電性水素バリア膜を含む第1の層間絶縁膜の上に第2の層間絶縁膜を形成した後、第2の層間絶縁膜に、導電性水素バリア膜と第2の層間絶縁膜上の配線とを接続する第2のプラグを形成する。このため、導電性水素バリア膜及び第2のプラグを介して容量上部電極と配線とを電気的に接続することができる。従って、容量上部電極の形成後に、容量上部電極と配線とを直接接続するプラグを形成するためのコンタクトホールを形成する必要がないので、容量上部電極が露出して水素雰囲気又は還元性雰囲気にさらされる事態を回避できる。その結果、容量上部電極として強い触媒作用を有するPt膜を用いる場合にも、容量絶縁膜を構成する強誘電体膜の特性の劣化を防止して、強誘電体メモリの信頼性を向上させることができる。

【0060】

また、第3の強誘電体メモリの製造方法によると、導電性水素バリア膜によって容量素子を常に覆っているため、容量素子の耐還元性を向上させることができる。

【0061】

本発明に係る第4の強誘電体メモリの製造方法は、半導体基板上における一の領域にトランジスタを形成する工程と、半導体基板上における他の領域に導電層を形成する工程と、トランジスタ及び導電層を含む半導体基板の上に第1の層間絶縁膜を形成する工程と、第1の層間絶縁膜に、トランジスタと接続する第1のプラグと、導電層と接続する第2のプラグとを形成する工程と、第1の層間絶縁膜の上に第1のプラグと接続するように容量下部電極を形成する工程と、容量下部電極の上に、強誘電体膜よりなる容量絶縁膜を形成する工程と、容量絶縁膜の上に容量上部電極を形成する工程と、容量上部電極の上に、容量上部電極の外側まで延び且つ第2のプラグと電気的に接続するように導電性水素バリア膜を形成する工程と、導電性水素バリア膜を含む第1の層間絶縁膜の上に第2の層間絶縁膜を形成する工程と、第1の層間絶縁膜及び第2の層間絶縁膜に、導電層と接続する第3のプラグを形成する工程と、第2の層間絶縁膜の上に第3のプラグと接続するように配線を形成する工程とを備えている。

【0062】

10

20

30

40

50

第4の強誘電体メモリの製造方法によると、トランジスタ及び導電層が形成された半導体基板上に第1の層間絶縁膜を形成した後、第1の層間絶縁膜に、トランジスタと接続する第1のプラグと、導電層と接続する第2のプラグとを形成する。その後、第1の層間絶縁膜の上に第1のプラグと接続する容量下部電極を形成した後、容量下部電極の上に、強誘電体膜よりなる容量絶縁膜、及び容量上部電極を順次形成し、その後、容量上部電極の上に、容量上部電極の外側まで延び且つ第2のプラグと電気的に接続する導電性水素バリア膜を形成する。その後、導電性水素バリア膜を含む第1の層間絶縁膜の上に第2の層間絶縁膜を形成した後、第1の層間絶縁膜及び第2の層間絶縁膜に、導電層と第2の層間絶縁膜上の配線とを接続する第3のプラグを形成する。このため、容量上部電極の形成前に、具体的には、トランジスタと容量下部電極とを接続する第1のプラグの形成と同時に、導電性水素バリア膜と導電層とを接続する第2のプラグを第1の層間絶縁膜に形成できる。これにより、導電性水素バリア膜、第2のプラグ、導電層及び第3のプラグを介して容量上部電極と配線とを電気的に接続することができる。すなわち、予め容量素子よりも下側に形成されている第2のプラグ及び導電層を用いて、容量上部電極と配線とを電気的に接続することができる。従って、容量上部電極の形成後に、容量上部電極と配線とを直接接続するプラグを形成するためのコンタクトホールを形成する必要がないので、容量上部電極が露出して水素雰囲気又は還元性雰囲気にさらされる事態を回避できる。その結果、容量上部電極として強い触媒作用を有するPt膜を用いる場合にも、容量絶縁膜を構成する強誘電体膜の特性の劣化を防止して、強誘電体メモリの信頼性を向上させることができる。

10

20

30

40

50

#### 【0063】

また、第4の強誘電体メモリの製造方法によると、導電性水素バリア膜によって容量素子を常に覆っているため、容量素子の耐還元性を向上させることができる。

#### 【0064】

第4の強誘電体メモリの製造方法において、容量下部電極を形成する工程は、第1の層間絶縁膜の上に第2のプラグと接続するように接続パッドを形成する工程を含み、導電性水素バリア膜を形成する工程は、導電性水素バリア膜を接続パッドと接続するように形成する工程を含むことが好ましい。

#### 【0065】

このようにすると、容量下部電極の材料として用いられ且つ酸素バリア性を有する導電性膜を第2のプラグの上面全体を覆うようにパターン化することによって、容量下部電極の形成と同時に接続パッドを形成できる。このため、工程の増加を招くことなく、第2のプラグの酸化を防止でき且つ導電性水素バリア膜と第2のプラグとを接続パッドを介して接続できる。

#### 【0066】

容量下部電極を形成する工程が接続パッドを形成する工程を含む場合、容量絶縁膜を形成する工程は、容量絶縁膜を、その端部が接続パッドの上に位置するように形成する工程を含むことが好ましい。

#### 【0067】

このようにすると、容量絶縁膜となる絶縁性膜に対して大きなエッティング選択比を有する導電性膜を接続パッドの材料として用いると共に、該接続パッドをエッティングストップーとして前記の絶縁性膜をパターン化することによって、オーバーエッティングに起因する段差形成を防止しながら容量絶縁膜を形成できる。

#### 【0068】

第4の強誘電体メモリの製造方法において、導電性水素バリア膜を形成する工程は、容量絶縁膜となる絶縁性膜及び容量上部電極となる第1の導電性膜をパターン化するために用いられたマスクパターンを用いて、導電性水素バリア膜となる第2の導電性膜をパターン化した後、導電性水素バリア膜の側面に第2のプラグと電気的に接続するように導電性的サイドウォールを形成する工程を含むことが好ましい。

#### 【0069】

このようにすると、製造工程で用いられるマスクパターンの数を低減できると共に、導電性水素バリア膜と第2のプラグとをサイドウォールを介して電気的に接続できる。

#### 【0070】

導電性水素バリア膜を形成する工程がサイドウォールを形成する工程を含む場合、サイドウォールは水素バリア性を有することが好ましい。

#### 【0071】

このようにすると、水素バリア膜によって容量素子全体を確実に覆うことができるため、容量素子の耐還元性を向上させることができる。

#### 【0072】

また、導電性水素バリア膜を形成する工程がサイドウォールを形成する工程を含む場合<sup>10</sup>、容量下部電極を形成する工程は、第1の層間絶縁膜の上に第2のプラグと接続するよう接続パッドを形成する工程を含み、導電性水素バリア膜を形成する工程は、サイドウォールを接続パッドと接続するように形成する工程を含むことが好ましい。

#### 【0073】

このようにすると、容量下部電極の材料として用いられ且つ酸素バリア性を有する導電性膜を第2のプラグの上面全体を覆うようにパターン化することによって、容量下部電極の形成と同時に接続パッドを形成できる。このため、工程の増加を招くことなく、第2のプラグの酸化を防止でき且つサイドウォールと第2のプラグとを接続パッドを介して接続できる。

#### 【0074】

導電性水素バリア膜を形成する工程がサイドウォールを形成する工程を含み、且つ容量下部電極を形成する工程が接続パッドを形成する工程を含む場合、容量絶縁膜を形成する工程は、容量絶縁膜を、その端部が接続パッドの上に位置するように形成する工程を含むことが好ましい。

#### 【0075】

このようにすると、容量絶縁膜となる絶縁性膜に対して大きなエッティング選択比を有する導電性膜を接続パッドの材料として用いると共に、該接続パッドをエッティングストップーとして前記の絶縁性膜をパターン化することによって、オーバーエッティングに起因する段差形成を防止しながら容量絶縁膜を形成できる。

#### 【0076】

第1、第2又は第4の強誘電体メモリの製造方法において、導電層は、半導体基板の表面部に形成された不純物拡散層、又は前記不純物拡散層の表面部がシリサイド化された層であることが好ましい。

#### 【0077】

このようにすると、導電層として、半導体基板上に形成されたポリシリコン層等を用いる場合と比べて、導電層を低抵抗化できる。

#### 【0078】

第1、第2又は第4の強誘電体メモリの製造方法において、第1の層間絶縁膜は下層膜とその上に形成された上層膜とを有しており、導電層は下層膜と上層膜との間に形成されていることが好ましい。

#### 【0079】

このようにすると、導電層として、半導体基板の表面部に形成された不純物拡散層を用いる場合と比べて、基板電位を簡単に設定できると共に強誘電体メモリのセルサイズを小さくできる。また、導電層と接続する第2又は第3のプラグが埋め込まれるホールのアスペクト比が小さくなるので、各プラグの形成不良や高抵抗化を防止できる。

#### 【0080】

第1、第2、第3又は第4の強誘電体メモリの製造方法において、容量上部電極の少なくとも一部は、P<sub>t</sub>膜又はP<sub>t</sub>を含む合金膜よりなることが好ましい。

#### 【0081】

このようにすると、容量絶縁膜を構成する強誘電体膜の結晶を、整合性の良いP<sub>t</sub>結晶<sup>50</sup>

面から十分に成長させることができる。

【0082】

第3又は第4の強誘電体メモリの製造方法において、導電性水素バリア膜は、Ti膜、Ta膜、TiON膜、TiN膜、TaN膜、TiAlN膜、TiAlON膜、又は、Ti、Ta、TiON、TiN、TaN、TiAlN若しくはTiAlONを含む合金膜となることが好ましい。

【0083】

このようにすると、容量素子の耐還元性を確実に向上させることができると共に、導電性水素バリア膜を介して容量上部電極とプラグ等とを電気的に確実に接続することができる。

10

【発明の効果】

【0084】

本発明によると、容量上部電極の形成後に、容量上部電極と配線とを直接接続するプラグを形成するためのコンタクトホールを形成する必要がないので、容量上部電極が露出して水素雰囲気又は還元性雰囲気にさらされる事態を回避できる。その結果、容量上部電極として強い触媒作用を有するPt膜を用いる場合にも、容量絶縁膜を構成する強誘電体膜の特性の劣化を防止して、強誘電体メモリの信頼性を向上させることができる。

【発明を実施するための最良の形態】

【0085】

(第1の実施形態)

20

以下、本発明の第1の実施形態に係る強誘電体メモリ及びその製造方法について図面を参照しながら説明する。

【0086】

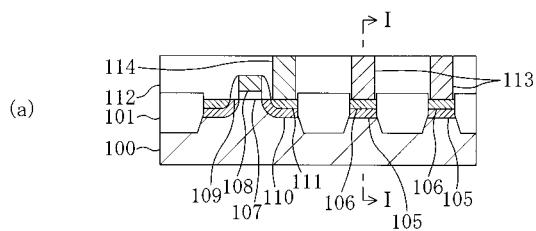

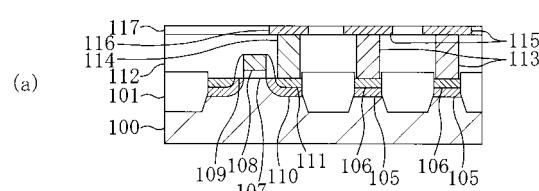

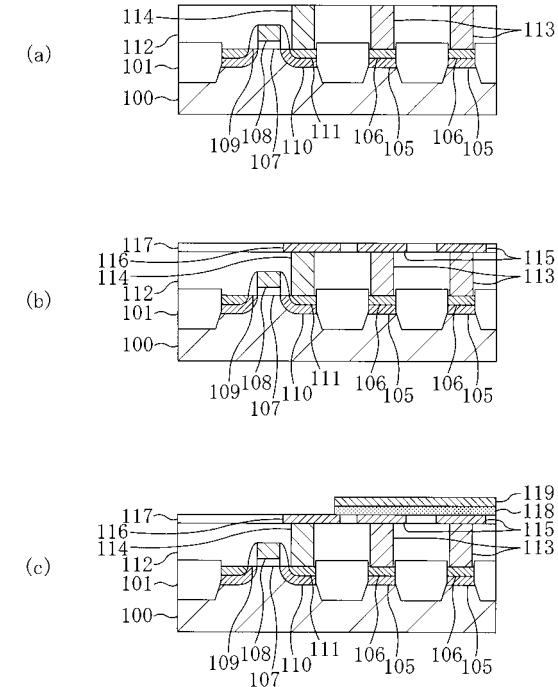

図1(a)、(b)、図2(a)、(b)、図3(a)～(c)及び図4(a)、(b)は、第1の実施形態に係る強誘電体メモリの製造方法の各工程を示す断面図である。尚、図1(b)は図1(a)におけるI-I線の断面図であり、図4(b)は図4(a)におけるIV-IV線の断面図である。

【0087】

まず、図1(a)及び(b)に示すように、半導体基板100の表面に、STI構造を有する素子分離領域101を形成する。その後、半導体基板100における素子分離領域101により囲まれた領域のうち、メモリセルが形成される各領域(以下、メモリセル領域と称する)の上に、第1のゲート絶縁膜102を介して、メモリセルトランジスタを構成する第1のゲート電極103を形成する。その後、第1のゲート電極103の側面に絶縁性の第1のサイドウォール104を形成すると共に、半導体基板100における各メモリセル領域の表面部に、下層となる第1の低濃度不純物拡散層105及び上層となる第1の高濃度不純物拡散層106を形成する。第1の低濃度不純物拡散層105及び第1の高濃度不純物拡散層106は、メモリセルトランジスタのソース領域又はドレイン領域となる。

30

【0088】

また、図1(a)に示すように、半導体基板100における素子分離領域101により囲まれた領域のうち、メモリセル領域以外の他の領域(以下、非メモリセル領域と称する)の上に、第2のゲート絶縁膜107を介して、制御トランジスタを構成する第2のゲート電極108を形成する。その後、第2のゲート電極108の側面に絶縁性の第2のサイドウォール109を形成すると共に、半導体基板100における非メモリセル領域の表面部に、下層となる第2の低濃度不純物拡散層110及び上層となる第2の高濃度不純物拡散層111を形成する。第2の低濃度不純物拡散層110及び第2の高濃度不純物拡散層111は、制御トランジスタのソース領域又はドレイン領域となる。

40

【0089】

尚、第1の実施形態において、メモリセルトランジスタ及び制御トランジスタのそれぞれを構成するゲート電極等の各要素を要素毎に同時に形成してもよい。

50

## 【0090】

次に、図1(a)及び(b)に示すように、メモリセルトランジスタ及び制御トランジスタが形成されている半導体基板100上に第1の層間絶縁膜112を形成する。その後、第1の層間絶縁膜112に、第1の高濃度不純物拡散層106(ソース領域となる部分)と接続し且つタングステンよりなる第1のプラグ113、及び、第2の高濃度不純物拡散層111(ソース領域となる部分及びドレイン領域となる部分のうちのいずれか一方)と接続し且つタングステンよりなる第2のプラグ114を形成する。

## 【0091】

次に、第1の層間絶縁膜112の上面に全面に亘って、酸素バリア性を有する導電性膜(例えはIr膜又はIrO<sub>2</sub>膜等)を全面に成膜した後、該導電性膜をパターン化することによって、図2(a)に示すように、酸素バリア性を有する導電性膜よりなり且つ第1のプラグ113の上面を覆う容量下部電極115、及び酸素バリア性を有する導電性膜よりなり且つ第2のプラグ114の上面を覆う接続パッド116を形成する。これにより、メモリセルトランジスタと容量下部電極115とが第1のプラグ113を介して接続される。その後、容量下部電極115同士の間の領域又は容量下部電極115と接続パッド116との間の領域に、絶縁膜117を、その上面と容量下部電極115及び接続パッド116のそれぞれの上面とが面一になるように埋め込む。

## 【0092】

次に、絶縁膜117が形成された第1の層間絶縁膜112の上面に全面に亘って、PZT(PbZr<sub>x</sub>Ti<sub>1-x</sub>O<sub>3</sub>(但し0<x<1))系又はSBT(SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>)系の材料よりなる強誘電体膜を成膜した後、該強誘電体膜をパターン化することによって、図2(b)に示すように、容量下部電極115の上面を覆う容量絶縁膜118を形成する。

## 【0093】

次に、容量絶縁膜118が形成された第1の層間絶縁膜112の上面に全面に亘って、Pt又はPtを含む合金よりなる導電性膜を成膜した後、該導電性膜をパターン化することによって、図3(a)に示すように、容量絶縁膜118の上面を覆い且つ容量絶縁膜118の外側まで延びる容量上部電極119を形成する。具体的には、容量上部電極119は、接続パッド116の上面の少なくとも一部分を覆う張り出し部119aを有しており、該張り出し部119aは、容量上部電極119となる導電性膜をパターン化するときに形成される。これにより、容量上部電極119と第2のプラグ114とが接続パッド116を介して接続されるので、容量上部電極119と第2の高濃度不純物拡散層111とが第2のプラグ114を介して電気的に接続される。尚、容量下部電極115、容量絶縁膜118及び容量上部電極119により容量素子が構成されている。

## 【0094】

次に、図3(b)に示すように、容量素子が形成された第1の層間絶縁膜112の上面に第2の層間絶縁膜120を形成する。その後、第1の層間絶縁膜112、絶縁膜117及び第2の層間絶縁膜120に、タングステンよりなる第3のプラグ121を、第2の高濃度不純物拡散層111(ソース領域となる部分及びドレイン領域となる部分のうち第2のプラグ114が接続されていない方)と接続するように形成する。

## 【0095】

次に、図3(c)に示すように、第2の層間絶縁膜120の上面に、アルミニウム等による配線122を第3のプラグ121と接続するように形成する。これにより、配線122と第2の高濃度不純物拡散層111とが第3のプラグ121を介して接続される。その後、図4(a)及び(b)に示すように、配線122を含む第2の層間絶縁膜120の上面に第3の層間絶縁膜123を形成した後、第3の層間絶縁膜123に、タングステンよりなる第4のプラグ124を、配線122と接続するように形成する。尚、図4(b)に示すように、第1の層間絶縁膜112、絶縁膜117及び第2の層間絶縁膜120には第5のプラグ125が形成されており、それによって第1の高濃度不純物拡散層106(ドレイン領域となる部分)と配線122とが接続されている。その後、図示は省略しているが、第3の層間絶縁膜123の上面に、さらに上層の層間絶縁膜、配線又は表面保護膜等を形

10

20

30

40

50

成することによって、強誘電体メモリを完成させる。

#### 【0096】

以上に説明したように、第1の実施形態によると、メモリセルトランジスタ、及び第2の高濃度不純物拡散層111を含む制御トランジスタが形成された半導体基板100上に第1の層間絶縁膜112を形成した後、第1の層間絶縁膜112に、メモリセルトランジスタと接続する第1のプラグ113、及び第2の高濃度不純物拡散層111と接続する第2のプラグ114を形成する。その後、第1の層間絶縁膜112の上に第1のプラグ113と接続する容量下部電極115を形成した後、容量下部電極115の上に、強誘電体膜よりなる容量絶縁膜118、及び容量絶縁膜118の外側まで延び且つ第2のプラグ114と電気的に接続する容量上部電極119を順次形成する。その後、容量上部電極119を含む第1の層間絶縁膜112の上に第2の層間絶縁膜120を形成した後、第1の層間絶縁膜112及び第2の層間絶縁膜120に、第2の高濃度不純物拡散層111と第2の層間絶縁膜120上の配線122とを接続する第3のプラグ121を形成する。このため、容量上部電極119の形成前に、具体的には、メモリセルトランジスタと容量下部電極115とを接続する第1のプラグ113の形成と同時に、容量上部電極119と第2の高濃度不純物拡散層111とを接続する第2のプラグ114を第1の層間絶縁膜112に形成できる。これにより、第2のプラグ114、第2の高濃度不純物拡散層111及び第3のプラグ121を介して容量上部電極119と配線122とを電気的に接続することができる。すなわち、予め容量素子よりも下側に形成されている第2のプラグ114及び第2の高濃度不純物拡散層111を用いて、容量上部電極119と配線122とを電気的に接続することができる。従って、容量上部電極119の形成後に、容量上部電極119と配線122とを直接接続するプラグを形成するためのコンタクトホールを形成する必要がないので、容量上部電極119が露出して水素雰囲気又は還元性雰囲気にさらされる事態を回避できる。その結果、容量上部電極119として強い触媒作用を有するPt膜を用いる場合にも、容量絶縁膜118を構成する強誘電体膜の特性の劣化を防止して強誘電体メモリの信頼性を向上させることができる。

10

20

#### 【0097】

また、第1の実施形態によると、酸素バリア性を有する容量下部電極115が第1のプラグ113の上面を覆っていると共に、酸素バリア性を有する接続パッド116が第2のプラグ114の上面を覆っている。このため、容量絶縁膜118を構成する強誘電体膜を酸素雰囲気中で焼結するときに、第1のプラグ113及び第2のプラグ114が酸化されることを防止できる。

30

#### 【0098】

また、第1の実施形態によると、容量下部電極115の材料として用いられ且つ酸素バリア性を有する導電性膜を第2のプラグ114の上面全体を覆うようにパターン化することによって、容量下部電極115の形成と同時に接続パッド116を形成するため、工程の増加を招くことなく第2のプラグ114の酸化を防止できる。また、容量上部電極119を接続パッド116と接続するように形成するため、容量上部電極119と第2のプラグ114とを接続パッド116を介して接続できる。

40

#### 【0099】

また、第1の実施形態によると、容量下部電極115同士の間の領域又は容量下部電極115と接続パッド116との間の領域に、絶縁膜117を、その上面と容量下部電極115及び接続パッド116のそれぞれの上面とが面一になるように埋め込む。このため、容量絶縁膜118等の堆積工程を平坦な下地上で行なえるので、容量素子の信頼性つまり強誘電体メモリの信頼性を向上させることができる。

40

#### 【0100】

また、第1の実施形態によると、第2の高濃度不純物拡散層111の表面部をシリサイド化してシリサイド層を形成しておき、該シリサイド層を、第2のプラグ114と第3のプラグ121とを接続する導電層として用いた場合、次のような効果が得られる。すなわち、第2のプラグ114と第3のプラグ121とを接続する導電層として、半導体基板1

50

00上に形成されたポリシリコン層等を用いる場合と比べて、該導電層を低抵抗化できる。

#### 【0101】

尚、第1の実施形態において、第1のプラグ113、第2のプラグ114、又は第3のプラグ121等の材料として、タンクスチンを用いたが、これに代えて、ポリシリコン等を用いてもよい。

#### 【0102】

また、第1の実施形態において、容量下部電極115としては、酸素含有率の少ないTiON膜若しくはTiN膜、又はTiを含む合金膜等を下層膜（密着層として機能する）とし、且つ耐酸化性の強いPt膜若しくはPtを含む合金膜、酸化物が酸素バリア性及び導電性を有するRu膜若しくはIr膜、又はRuO<sub>2</sub>膜若しくはIrO<sub>2</sub>膜等を上層膜とする積層膜を用いることが好ましい。10

#### 【0103】

また、第1の実施形態において、容量下部電極115同士の間に埋め込まれる絶縁膜117としては、SiO<sub>2</sub>膜、Si<sub>3</sub>N<sub>4</sub>膜、又はSiON膜等を用いることが好ましい。

#### 【0104】

また、第1の実施形態において、容量絶縁膜118を構成する強誘電体膜の材料としては、PZT系の材料又はSBT系の材料等を用いることが好ましい。

#### 【0105】

また、第1の実施形態において、容量上部電極119としては、耐酸化性の強いPt膜若しくはPtを含む合金膜、酸化物が酸素バリア性及び導電性を有するRu膜若しくはIr膜、又はRuO<sub>2</sub>膜若しくはIrO<sub>2</sub>膜等を少なくとも一部分に用いることが好ましい。このようにすると、容量絶縁膜118を構成する強誘電体膜の結晶を十分に成長させることができること20ができる。

#### 【0106】

また、第1の実施形態において、半導体基板100上における非メモリセル領域に、第2のゲート電極108等により構成される制御トランジスタ（容量上部電極119つまりメモリセルプレートをON/OFFするドライバーとしての機能を有している）を形成した。すなわち、第1の実施形態においては、制御トランジスタがONになっている場合のみ、容量上部電極119と配線122とは、第2のプラグ114、第2の高濃度不純物拡散層111（つまり制御トランジスタのソース領域又はドレイン領域）及び第3のプラグ121を介して電気的に接続される。それに対して回路構成上、制御トランジスタを必要としない強誘電体メモリにおいては、例えば図5に示すように、半導体基板100上における非メモリセル領域に第2の高濃度不純物拡散層111のみを形成してもよい。この場合、容量上部電極119と配線122とは、第2のプラグ114、第2の高濃度不純物拡散層111及び第3のプラグ121を介して常に電気的に接続される。また、この場合、第2の高濃度不純物拡散層111の表面部をシリサイド化してもよい。30

#### 【0107】

また、第1の実施形態において、第2のプラグ114の上面を酸素バリア性を有する接続パッド116により覆ったが、これに代えて、例えば第2のプラグ114が酸素バリア性を有する材料となる場合には、接続パッド116を形成しなくてもよい。このようにすると、強誘電体メモリの集積度を向上させることができる。また、このとき、容量上部電極119の張り出し部119aは、第2のプラグ114の上面の少なくとも一部分を覆うことが好ましい。40

#### 【0108】

また、第1の実施形態において、容量下部電極115同士の間の領域又は容量下部電極115と接続パッド116との間の領域に、絶縁膜117を埋め込んだが、これに代えて、絶縁膜117を形成しなくてもよい。

#### 【0109】

また、第1の実施形態において、容量上部電極119を形成する前に、容量絶縁膜11

50

8の側面にサイドウォールを形成しておくことが好ましい。このようにすると、容量上部電極119となる導電性膜の段差被覆性が向上して、容量上部電極119の張り出し部119aに断線が生じる事態を防止できるので、強誘電体メモリの信頼性を向上させることができる。

#### 【0110】

また、第1の実施形態において、第2の層間絶縁膜120の上に第3のプラグ121と接続するように配線122を形成したが、これに代えて、第2の層間絶縁膜120に第3のプラグ121と接続するように配線122を埋め込んでもよい。

#### 【0111】

(第1の実施形態の第1変形例)

10

以下、本発明の第1の実施形態の第1変形例に係る強誘電体メモリ及びその製造方法について図面を参照しながら説明する。

#### 【0112】

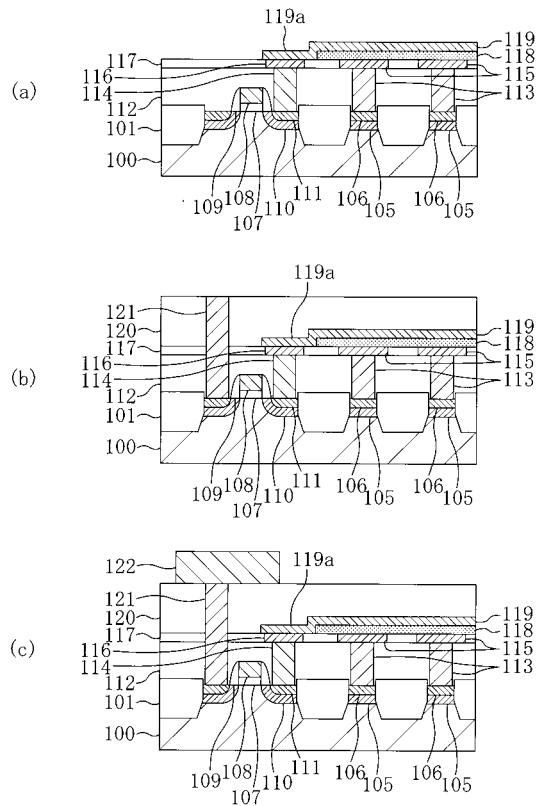

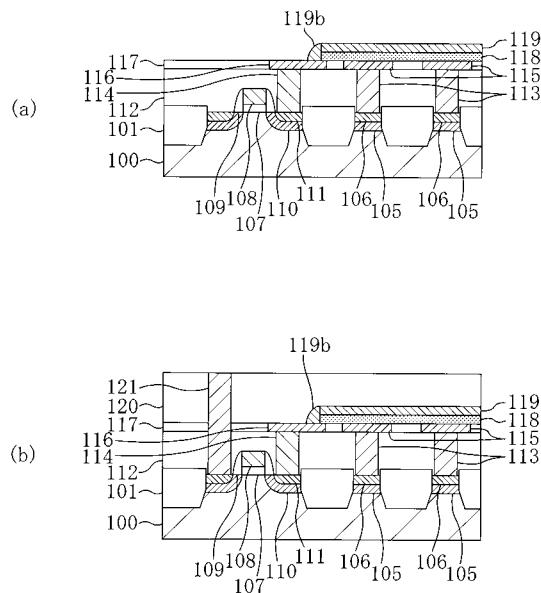

図6(a)～(c)、図7(a)、(b)及び図8(a)、(b)は、第1の実施形態の第1変形例に係る強誘電体メモリの製造方法の各工程を示す断面図である。

#### 【0113】

まず、図6(a)に示すように、半導体基板100の表面に、STI構造を有する素子分離領域101を形成する。その後、半導体基板100における素子分離領域101により囲まれた領域のうち各メモリセル領域の表面部に、下層となる第1の低濃度不純物拡散層105及び上層となる第1の高濃度不純物拡散層106を形成する。第1の低濃度不純物拡散層105及び第1の高濃度不純物拡散層106は、メモリセルトランジスタ(ゲート電極等の図示省略)のソース領域又はドレイン領域となる。

20

#### 【0114】

また、図6(a)に示すように、半導体基板100における非メモリセル領域の上に、第2のゲート絶縁膜107を介して、制御トランジスタを構成する第2のゲート電極108を形成する。その後、第2のゲート電極108の側面に絶縁性の第2のサイドウォール109を形成すると共に、半導体基板100における非メモリセル領域の表面部に、下層となる第2の低濃度不純物拡散層110及び上層となる第2の高濃度不純物拡散層111を形成する。第2の低濃度不純物拡散層110及び第2の高濃度不純物拡散層111は、制御トランジスタのソース領域又はドレイン領域となる。

30

#### 【0115】

尚、第1の実施形態の第1変形例において、メモリセルトランジスタ及び制御トランジスタのそれぞれを構成するゲート電極等の各要素を要素毎に同時に形成してもよい。

#### 【0116】

次に、図6(a)に示すように、メモリセルトランジスタ及び制御トランジスタが形成されている半導体基板100上に第1の層間絶縁膜112を形成する。その後、第1の層間絶縁膜112に、第1の高濃度不純物拡散層106(ソース領域となる部分)と接続し且つタングステンよりなる第1のプラグ113、及び、第2の高濃度不純物拡散層111(ソース領域となる部分及びドレイン領域となる部分のうちのいずれか一方)と接続し且つタングステンよりなる第2のプラグ114を形成する。

40

#### 【0117】

次に、第1の層間絶縁膜112の上に全面に亘って、酸素バリア性を有する導電性膜(例えばIr膜又はIrO<sub>2</sub>膜等)を全面に成膜した後、該導電性膜をパターン化することによって、図6(b)に示すように、酸素バリア性を有する導電性膜よりなり且つ第1のプラグ113の上面を覆う容量下部電極115、及び酸素バリア性を有する導電性膜よりなり且つ第2のプラグ114の上面を覆う接続パッド116を形成する。これにより、メモリセルトランジスタと容量下部電極115とが第1のプラグ113を介して接続される。その後、容量下部電極115同士の間の領域又は容量下部電極115と接続パッド116との間の領域に、絶縁膜117を、その上面と容量下部電極115及び接続パッド116のそれぞれの上面とが面一になるように埋め込む。

50

## 【0118】

次に、絶縁膜117が形成された第1の層間絶縁膜112の上に全面に亘って、PZT系又はSBT系の材料よりなる強誘電体膜、及びPt又はPtを含む合金よりなる導電性膜を順次成膜した後、該導電性膜及び強誘電体膜を同一のマスクパターン(図示省略)を用いてパターン化する。これにより、図6(c)に示すように、容量下部電極115の上面を覆う容量絶縁膜118、及び容量絶縁膜118の上面を覆う容量上部電極119を形成する。このとき、容量絶縁膜118及び容量上部電極119を、それぞれの端部が接続パッド116の上に位置するように形成する。尚、容量下部電極115、容量絶縁膜118及び容量上部電極119により容量素子が構成されている。

## 【0119】

次に、容量素子が形成された第1の層間絶縁膜112の上に全面に亘って、導電性膜(図示省略)を堆積した後、該導電性膜に対してエッチバックを行なうことによって、図7(a)に示すように、容量上部電極119の側面に導電性の第3のサイドウォール119bを接続パッド116と接続するように形成する。これにより、容量上部電極119と第2の高濃度不純物拡散層111とが第2のプラグ114を介して電気的に接続される。

## 【0120】

次に、図7(b)に示すように、容量素子が形成された第1の層間絶縁膜112の上に第2の層間絶縁膜120を形成する。その後、第1の層間絶縁膜112、絶縁膜117及び第2の層間絶縁膜120に、タングステンよりなる第3のプラグ121を、第2の高濃度不純物拡散層111(ソース領域となる部分及びドレイン領域となる部分のうち第2のプラグ114が接続されていない方)と接続するように形成する。

## 【0121】

次に、図8(a)に示すように、第2の層間絶縁膜120の上に、アルミニウム等による配線122を第3のプラグ121と接続するように形成する。これにより、配線122と第2の高濃度不純物拡散層111とが第3のプラグ121を介して接続される。その後、図8(b)に示すように、配線122を含む第2の層間絶縁膜120の上に第3の層間絶縁膜123を形成した後、第3の層間絶縁膜123に、タングステンよりなる第4のプラグ124を、配線122と接続するように形成する。その後、図示は省略しているが、第3の層間絶縁膜123の上に、さらに上層の層間絶縁膜、配線又は表面保護膜等を形成することによって、強誘電体メモリを完成させる。

## 【0122】

以上に説明したように、第1の実施形態の第1変形例によると、メモリセルトランジスタ、及び第2の高濃度不純物拡散層111を含む制御トランジスタが形成された半導体基板100上に第1の層間絶縁膜112を形成した後、第1の層間絶縁膜112に、メモリセルトランジスタと接続する第1のプラグ113、及び第2の高濃度不純物拡散層111と接続する第2のプラグ114を形成する。その後、第1の層間絶縁膜112の上に第1のプラグ113と接続する容量下部電極115を形成した後、容量絶縁膜118となる強誘電体膜及び容量上部電極119となる導電性膜を同一のマスクパターンを用いてパターン化することにより、容量下部電極115の上面を覆う容量絶縁膜118、及び容量絶縁膜118の上面を覆う容量上部電極119を形成する。その後、容量上部電極119の側面に導電性の第3のサイドウォール119bを第2のプラグ114と電気的に接続するように形成する。その後、容量上部電極119を含む第1の層間絶縁膜112の上に第2の層間絶縁膜120を形成した後、第1の層間絶縁膜112及び第2の層間絶縁膜120に、第2の高濃度不純物拡散層111と第2の層間絶縁膜120上の配線122とを接続する第3のプラグ121を形成する。このため、容量上部電極119の形成前に、具体的には、メモリセルトランジスタと容量下部電極115とを接続する第1のプラグ113の形成と同時に、第3のサイドウォール119bを介して容量上部電極119と第2の高濃度不純物拡散層111とを接続する第2のプラグ114を第1の層間絶縁膜112に形成できる。これにより、第2のプラグ114、第2の高濃度不純物拡散層111及び第3のプラグ121を介して容量上部電極119と配線122とを電気的に接続することができる

10

20

30

40

50

。すなわち、予め容量素子よりも下側に形成されている第2のプラグ114及び第2の高濃度不純物拡散層111を用いて、容量上部電極119と配線122とを電気的に接続することができる。従って、容量上部電極119の形成後に、容量上部電極119と配線122とを直接接続するプラグを形成するためのコンタクトホールを形成する必要がないので、容量上部電極119が露出して水素雰囲気又は還元性雰囲気にさらされる事態を回避できる。その結果、容量上部電極119として強い触媒作用を有するPt膜を用いる場合にも、容量絶縁膜118を構成する強誘電体膜の特性の劣化を防止して強誘電体メモリの信頼性を向上させることができる。

#### 【0123】

また、第1の実施形態の第1変形例によると、酸素バリア性を有する容量下部電極115が第1のプラグ113の上面を覆っていると共に、酸素バリア性を有する接続パッド116が第2のプラグ114の上面を覆っている。このため、容量絶縁膜118を構成する強誘電体膜を酸素雰囲気中で焼結するときに、第1のプラグ113及び第2のプラグ114が酸化されることを防止できる。10

#### 【0124】

また、第1の実施形態の第1変形例によると、容量下部電極115の材料として用いられ且つ酸素バリア性を有する導電性膜を第2のプラグ114の上面全体を覆うようにパターン化することによって、容量下部電極115の形成と同時に接続パッド116を形成するため、工程の増加を招くことなく第2のプラグ114の酸化を防止できる。また、容量上部電極119の側面に導電性の第3のサイドウォール119bを接続パッド116と接続するように形成するため、容量上部電極119と第2のプラグ114とを第3のサイドウォール119b及び接続パッド116を介して接続できる。20

#### 【0125】

また、第1の実施形態の第1変形例によると、容量絶縁膜118を、その端部が接続パッド116の上に位置するように形成する。このため、容量絶縁膜118となる絶縁性膜に対して大きなエッチング選択比を有する導電性膜を接続パッド116の材料として用いると共に、該接続パッド116をエッチングストッパーとして前記の絶縁性膜をパターン化することによって、オーバーエッチングに起因する段差形成を防止しながら容量絶縁膜118を形成できる。

#### 【0126】

また、第1の実施形態の第1変形例によると、容量絶縁膜118となる絶縁性膜をパターン化するために用いられたマスクパターンを用いて、容量上部電極119となる導電性膜をパターン化するため、製造工程で用いられるマスクパターンの数を低減できる。30

#### 【0127】

また、第1の実施形態の第1変形例によると、容量下部電極115同士の間の領域又は容量下部電極115と接続パッド116との間の領域に、絶縁膜117を、その上面と容量下部電極115及び接続パッド116のそれぞれの上面とが面一になるように埋め込む。このため、容量絶縁膜118等の堆積工程を平坦な下地上で行なえるので、容量素子の信頼性つまり強誘電体メモリの信頼性を向上させることができる。

#### 【0128】

また、第1の実施形態の第1変形例によると、第2の高濃度不純物拡散層111の表面部をシリサイド化してシリサイド層を形成しておき、該シリサイド層を、第2のプラグ114と第3のプラグ121とを接続する導電層として用いた場合、次のような効果が得られる。すなわち、第2のプラグ114と第3のプラグ121とを接続する導電層として、半導体基板100上に形成されたポリシリコン層等を用いる場合と比べて、該導電層を低抵抗化できる。40

#### 【0129】

尚、第1の実施形態の第1変形例において、第3のサイドウォール119bを構成する導電性膜としては、容量上部電極119又は容量下部電極115を構成する導電性膜に対して大きなエッチング選択比を有する導電性膜、例えばTiN膜又はTaN膜等を用いる50

ことが好ましい。このようにすると、第3のサイドウォール119bの形成時に容量上部電極119又は容量下部電極115が受ける損傷を抑制することができる。

#### 【0130】

また、第1の実施形態の第1変形例において、第1のプラグ113、第2のプラグ114、又は第3のプラグ121等の材料として、タンゲステンを用いたが、これに代えて、ポリシリコン等を用いてもよい。

#### 【0131】

また、第1の実施形態の第1変形例において、容量下部電極115としては、酸素含有率の少ないTiON膜若しくはTiN膜、又はTiを含む合金膜等を下層膜（密着層として機能する）とし、且つ耐酸化性の強いPt膜若しくはPtを含む合金膜、酸化物が酸素バリア性及び導電性を有するRu膜若しくはIr膜、又はRuO<sub>2</sub>膜若しくはIrO<sub>2</sub>膜等を上層膜とする積層膜を用いることが好ましい。

#### 【0132】

また、第1の実施形態の第1変形例において、容量下部電極115同士の間に埋め込まれる絶縁膜117としては、SiO<sub>2</sub>膜、Si<sub>3</sub>N<sub>4</sub>膜、又はSiON膜等を用いることが好ましい。

#### 【0133】

また、第1の実施形態の第1変形例において、容量絶縁膜118を構成する強誘電体膜の材料としては、PZT系の材料又はSBT系の材料等を用いることが好ましい。

#### 【0134】

また、第1の実施形態の第1変形例において、容量上部電極119としては、耐酸化性の強いPt膜若しくはPtを含む合金膜、酸化物が酸素バリア性及び導電性を有するRu膜若しくはIr膜、又はRuO<sub>2</sub>膜若しくはIrO<sub>2</sub>膜等を少なくとも一部分に用いることが好ましい。このようにすると、容量絶縁膜118を構成する強誘電体膜の結晶を十分に成長させることができる。

#### 【0135】

また、第1の実施形態の第1変形例において、半導体基板100上における非メモリセル領域に、第2のゲート電極108等により構成される制御トランジスタを形成したが、回路構成上、制御トランジスタを必要としない強誘電体メモリにおいては、半導体基板100上における非メモリセル領域に第2の高濃度不純物拡散層111のみを形成してもよい。この場合、第2の高濃度不純物拡散層111の表面部をシリサイド化してもよい。

#### 【0136】

また、第1の実施形態の第1変形例において、第2のプラグ114の上面を酸素バリア性を有する接続パッド116により覆ったが、これに代えて、例えば第2のプラグ114が酸素バリア性を有する材料よりなる場合には、接続パッド116を形成しなくてもよい。このようにすると、強誘電体メモリの集積度を向上させることができる。また、このとき、第3のサイドウォール119bは、第2のプラグ114の上面の少なくとも一部分を覆うことが好ましい。

#### 【0137】

また、第1の実施形態の第1変形例において、容量下部電極115同士の間の領域又は容量下部電極115と接続パッド116との間の領域に、絶縁膜117を埋め込んだが、これに代えて、絶縁膜117を形成しなくてもよい。

#### 【0138】

また、第1の実施形態の第1変形例において、第2の層間絶縁膜120の上に第3のプラグ121と接続するように配線122を形成したが、これに代えて、第2の層間絶縁膜120に第3のプラグ121と接続するように配線122を埋め込んでもよい。

#### 【0139】

（第1の実施形態の第2変形例）

以下、本発明の第1の実施形態の第2変形例に係る強誘電体メモリ及びその製造方法について図面を参照しながら説明する。

10

20

30

40

50

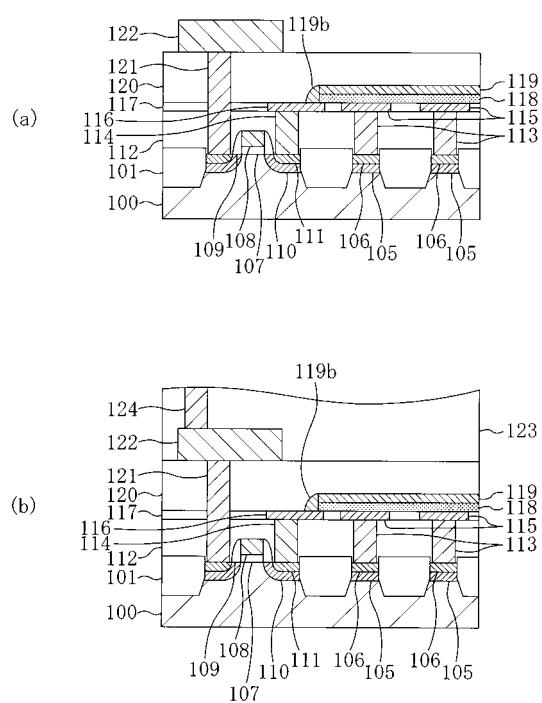

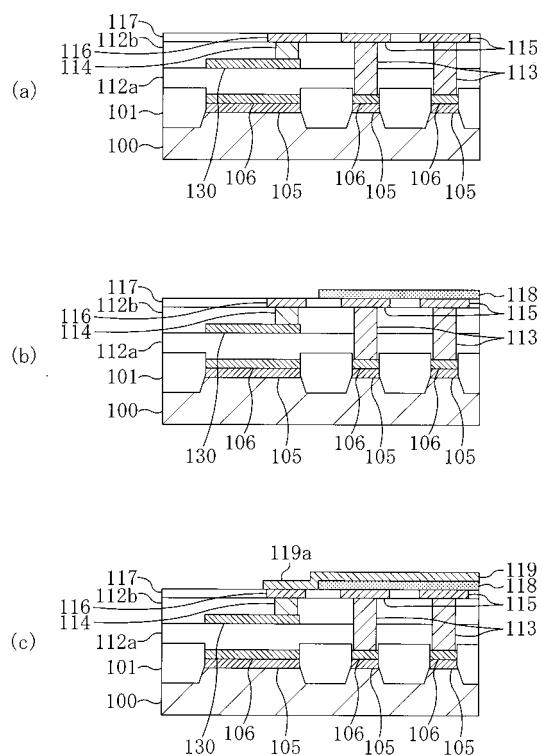

## 【0140】

図9(a)～(c)、図10(a)～(c)及び図11(a)～(c)は、第1の実施形態の第2変形例に係る強誘電体メモリの製造方法の各工程を示す断面図である。

## 【0141】

まず、図9(a)に示すように、半導体基板100の表面に、STI構造を有する素子分離領域101を形成する。その後、半導体基板100における素子分離領域101により囲まれた領域のうち各メモリセル領域の表面部に、下層となる第1の低濃度不純物拡散層105及び上層となる第1の高濃度不純物拡散層106を形成する。第1の低濃度不純物拡散層105及び第1の高濃度不純物拡散層106は、メモリセルトランジスタ(ゲート電極等の図示省略)のソース領域又はドレイン領域となる。このとき、半導体基板100における非メモリセル領域の表面部に第1の低濃度不純物拡散層105又は第1の高濃度不純物拡散層106が形成されていてもよい。その後、メモリセルトランジスタが形成されている半導体基板100上に第1の層間絶縁膜112の下層膜112aを形成する。10

## 【0142】

次に、図9(b)に示すように、下層膜112aが形成された半導体基板100における非メモリセル領域の上に、例えばポリシリコンよりなる導電層130を形成した後、導電層130の上及び下層膜112aの上に、第1の層間絶縁膜112の上層膜112bを形成する。

## 【0143】

次に、図9(c)に示すように、第1の層間絶縁膜112の上層膜112b及び下層膜112aに、第1の高濃度不純物拡散層106(ソース領域となる部分)と接続し且つタングステンよりなる第1のプラグ113を形成すると共に、第1の層間絶縁膜112の上層膜112bに、導電層130と接続し且つタングステンよりなる第2のプラグ114を形成する。20

## 【0144】

次に、第1の層間絶縁膜112の上に全面に亘って、酸素バリア性を有する導電性膜(例えばIr膜又はIrO<sub>2</sub>膜等)を全面に成膜した後、該導電性膜をパターン化することによって、図10(a)に示すように、酸素バリア性を有する導電性膜よりなり且つ第1のプラグ113の上面を覆う容量下部電極115、及び酸素バリア性を有する導電性膜よりなり且つ第2のプラグ114の上面を覆う接続パッド116を形成する。これにより、メモリセルトランジスタと容量下部電極115とが第1のプラグ113を介して接続される。その後、容量下部電極115同士の間の領域又は容量下部電極115と接続パッド116との間の領域に、絶縁膜117を、その上面と容量下部電極115及び接続パッド116のそれぞれの上面とが面一になるように埋め込む。30

## 【0145】

次に、絶縁膜117が形成された第1の層間絶縁膜112の上に全面に亘って、PZT系又はSBT系の材料よりなる強誘電体膜を成膜した後、該強誘電体膜をパターン化することによって、図10(b)に示すように、容量下部電極115の上面を覆う容量絶縁膜118を形成する。

## 【0146】

次に、容量絶縁膜118が形成された第1の層間絶縁膜112の上に全面に亘って、Pt又はPtを含む合金よりなる導電性膜を成膜した後、該導電性膜をパターン化することによって、図10(c)に示すように、容量絶縁膜118の上面を覆い且つ容量絶縁膜118の外側まで延びる容量上部電極119を形成する。具体的には、容量上部電極119は、接続パッド116の上面の少なくとも一部分を覆う張り出し部119aを有しており、該張り出し部119aは、容量上部電極119となる導電性膜をパターン化するときに形成される。これにより、容量上部電極119と第2のプラグ114とが接続パッド116を介して接続されるので、容量上部電極119と導電層130とが第2のプラグ114を介して電気的に接続される。尚、容量下部電極115、容量絶縁膜118及び容量上部電極119により容量素子が構成されている。4050

## 【0147】

次に、図11(a)に示すように、容量素子が形成された第1の層間絶縁膜112の上に第2の層間絶縁膜120を形成する。その後、第1の層間絶縁膜112の上層膜112b、絶縁膜117、及び第2の層間絶縁膜120に、タングステンよりなる第3のプラグ121を導電層130と接続するように形成する。

## 【0148】

次に、図11(b)に示すように、第2の層間絶縁膜120の上に、アルミニウム等よりなる配線122を第3のプラグ121と接続するように形成する。これにより、配線122と導電層130とが第3のプラグ121を介して接続される。その後、図11(c)に示すように、配線122を含む第2の層間絶縁膜120の上に第3の層間絶縁膜123を形成した後、第3の層間絶縁膜123に、タングステンよりなる第4のプラグ124を、配線122と接続するように形成する。その後、図示は省略しているが、第3の層間絶縁膜123の上に、さらに上層の層間絶縁膜、配線又は表面保護膜等を形成することによって、強誘電体メモリを完成させる。

## 【0149】

以上に説明したように、第1の実施形態の第2変形例によると、メモリセルトランジスタが形成された半導体基板100上に第1の層間絶縁膜112の下層膜112aを形成した後、非メモリセル領域の下層膜112aの上に導電層130を形成し、その後、第1の層間絶縁膜112の上層膜112bを形成する。その後、第1の層間絶縁膜112に、メモリセルトランジスタと接続する第1のプラグ113、及び導電層130と接続する第2のプラグ114を形成する。その後、第1の層間絶縁膜112の上に第1のプラグ113と接続する容量下部電極115を形成した後、容量下部電極115の上に、強誘電体膜よりなる容量絶縁膜118、及び容量絶縁膜118の外側まで延び且つ第2のプラグ114と電気的に接続する容量上部電極119を順次形成する。その後、容量上部電極119を含む第1の層間絶縁膜112の上に第2の層間絶縁膜120を形成した後、第1の層間絶縁膜112及び第2の層間絶縁膜120に、導電層130と第2の層間絶縁膜120上の配線122とを接続する第3のプラグ121を形成する。このため、容量上部電極119の形成前に、具体的には、メモリセルトランジスタと容量下部電極115とを接続する第1のプラグ113の形成と同時に、容量上部電極119と導電層130とを接続する第2のプラグ114を第1の層間絶縁膜112に形成できる。これにより、第2のプラグ114、導電層130及び第3のプラグ121を介して容量上部電極119と配線122とを電気的に接続することができる。すなわち、予め容量素子よりも下側に形成されている第2のプラグ114及び導電層130を用いて、容量上部電極119と配線122とを電気的に接続することができる。従って、容量上部電極119の形成後に、容量上部電極119と配線122とを直接接続するプラグを形成するためのコンタクトホールを形成する必要がないので、容量上部電極119が露出して水素雰囲気又は還元性雰囲気にさらされる事態を回避できる。その結果、容量上部電極119として強い触媒作用を有するPt膜を用いる場合にも、容量絶縁膜118を構成する強誘電体膜の特性の劣化を防止して強誘電体メモリの信頼性を向上させることができる。

## 【0150】

また、第1の実施形態の第2変形例によると、酸素バリア性を有する容量下部電極115が第1のプラグ113の上面を覆っていると共に、酸素バリア性を有する接続パッド116が第2のプラグ114の上面を覆っている。このため、容量絶縁膜118を構成する強誘電体膜を酸素雰囲気中で焼結するときに、第1のプラグ113及び第2のプラグ114が酸化されることを防止できる。

## 【0151】

また、第1の実施形態の第2変形例によると、容量下部電極115の材料として用いられ且つ酸素バリア性を有する導電性膜を第2のプラグ114の上面全体を覆うようにパターン化することによって、容量下部電極115の形成と同時に接続パッド116を形成するため、工程の増加を招くことなく第2のプラグ114の酸化を防止できる。また、容量

上部電極 119 を接続パッド 116 と接続するように形成するため、容量上部電極 119 と第 2 のプラグ 114 とを接続パッド 116 を介して接続できる。

#### 【0152】

また、第 1 の実施形態の第 2 変形例によると、容量下部電極 115 同士の間の領域又は容量下部電極 115 と接続パッド 116 との間の領域に、絶縁膜 117 を、その上面と容量下部電極 115 及び接続パッド 116 のそれぞれの上面とが面一になるように埋め込む。このため、容量絶縁膜 118 等の堆積工程を平坦な下地上で行なえるので、容量素子の信頼性つまり強誘電体メモリの信頼性を向上させることができる。

#### 【0153】

また、第 1 の実施形態の第 2 変形例によると、第 2 のプラグ 114 と第 3 のプラグ 12 10 とを接続する導電層 130 が、第 1 の層間絶縁膜 112 の下層膜 112a と上層膜 112b との間に形成されている。このため、第 2 のプラグ 114 と第 3 のプラグ 121 とを接続する導電層として、半導体基板 100 の表面部に形成された不純物拡散層を用いる場合と比べて、基板電位を簡単に設定できると共に強誘電体メモリのセルサイズを小さくできる。また、導電層 130 と接続する第 2 のプラグ 114 又は第 3 のプラグ 121 が埋め込まれるホールのアスペクト比が小さくなるので、各プラグの形成不良や高抵抗化を防止できる。

#### 【0154】

尚、第 1 の実施形態の第 2 変形例において、導電層 130 の材料は特に限定されるものではないが、導電層 130 が本変形例のように容量上部電極 119 の引き出し配線に使用されることを考慮して、導電層 130 の材料として低抵抗材料、例えばポリシリコン若しくはそれをシリサイド化したもの又はタングステン等を用いることが好ましい。

#### 【0155】

また、第 1 の実施形態の第 2 変形例において、導電層 130 として、強誘電体キャパシタ（容量下部電極 115、容量絶縁膜 118 及び容量上部電極 119 により構成される容量素子）よりも下側の配線層、例えばビット線に使用される配線層を利用してもよい。或いは、導電層 130 として、例えば図 12 に示すように、半導体基板 100 上に層間絶縁膜を介さずに形成された配線層、例えばメモリセルトランジスタ又は制御トランジスタのゲート電極と同時に形成された配線層を用いてもよい。このとき、該配線層は、素子分離領域 101 の上に形成されていてもよいし、半導体基板 100 における素子分離領域 101 が形成されていない領域の上に形成されていてもよい。

#### 【0156】

また、第 1 の実施形態の第 2 変形例において、第 1 のプラグ 113、第 2 のプラグ 114、又は第 3 のプラグ 121 等の材料として、タングステンを用いたが、これに代えて、ポリシリコン等を用いてもよい。

#### 【0157】

また、第 1 の実施形態の第 2 変形例において、容量下部電極 115 としては、酸素含有率の少ない TiON 膜若しくは TiN 膜、又は Ti を含む合金膜等を下層膜（密着層として機能する）とし、且つ耐酸化性の強い Pt 膜若しくは Pt を含む合金膜、酸化物が酸素バリア性及び導電性を有する Ru 膜若しくは Ir 膜、又は RuO<sub>2</sub> 膜若しくは IrO<sub>2</sub> 膜等を上層膜とする積層膜を用いることが好ましい。

#### 【0158】

また、第 1 の実施形態の第 2 変形例において、容量下部電極 115 同士の間に埋め込まれる絶縁膜 117 としては、SiO<sub>2</sub> 膜、Si<sub>3</sub>N<sub>4</sub> 膜、又は SiON 膜等を用いることが好ましい。

#### 【0159】

また、第 1 の実施形態の第 2 変形例において、容量絶縁膜 118 を構成する強誘電体膜の材料としては、PZT 系の材料又は SBT 系の材料等を用いることが好ましい。

#### 【0160】

また、第 1 の実施形態の第 2 変形例において、容量上部電極 119 としては、耐酸化性 50

の強いPt膜若しくはPtを含む合金膜、酸化物が酸素バリア性及び導電性を有するRu膜若しくはIr膜、又はRuO<sub>2</sub>膜若しくはIrO<sub>2</sub>膜等を少なくとも一部分に用いることが好ましい。このようにすると、容量絶縁膜118を構成する強誘電体膜の結晶を十分に成長させることができる。

#### 【0161】

また、第1の実施形態の第2変形例において、第2のプラグ114の上面を酸素バリア性を有する接続パッド116により覆ったが、これに代えて、例えば第2のプラグ114が酸素バリア性を有する材料となる場合には、接続パッド116を形成しなくてもよい。このようにすると、強誘電体メモリの集積度を向上させることができる。また、このとき、容量上部電極119の張り出し部119aは、第2のプラグ114の上面の少なくとも一部分を覆うことが好ましい。10

#### 【0162】

また、第1の実施形態の第2変形例において、容量下部電極115同士の間の領域又は容量下部電極115と接続パッド116との間の領域に、絶縁膜117を埋め込んだが、これに代えて、絶縁膜117を形成しなくてもよい。

#### 【0163】

また、第1の実施形態の第2変形例において、容量上部電極119を形成する前に、容量絶縁膜118の側面にサイドウォールを形成しておくことが好ましい。このようにすると、容量上部電極119となる導電性膜の段差被覆性が向上して、容量上部電極119の張り出し部119aに断線が生じる事態を防止できるので、強誘電体メモリの信頼性を向上させることができる。20

#### 【0164】

また、第1の実施形態の第2変形例において、第2の層間絶縁膜120の上に第3のプラグ121と接続するように配線122を形成したが、これに代えて、第2の層間絶縁膜120に第3のプラグ121と接続するように配線122を埋め込んでもよい。

#### 【0165】

##### (第2の実施形態)

以下、本発明の第2の実施形態に係る強誘電体メモリ及びその製造方法について図面を参照しながら説明する。

#### 【0166】

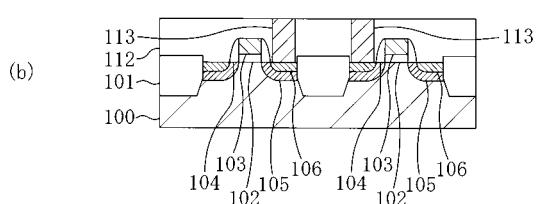

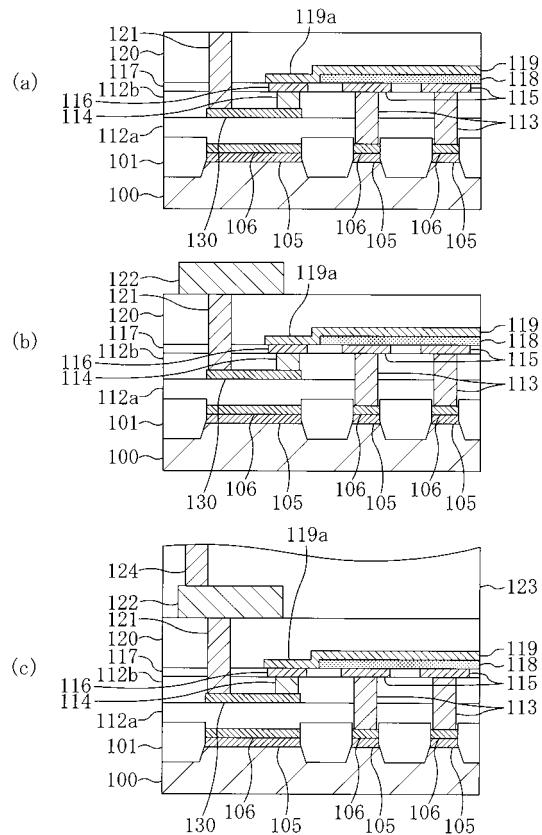

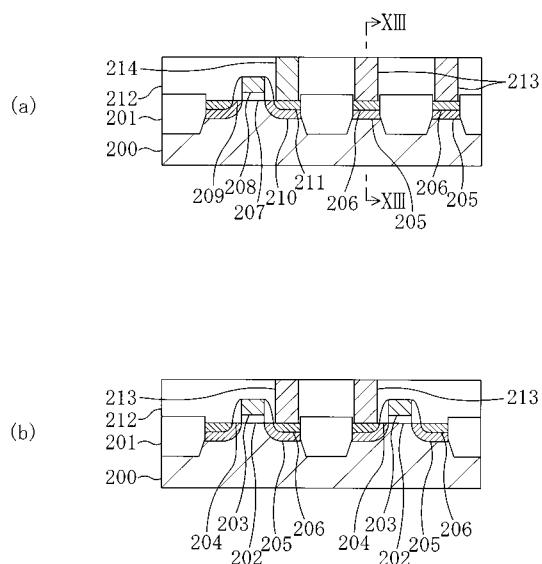

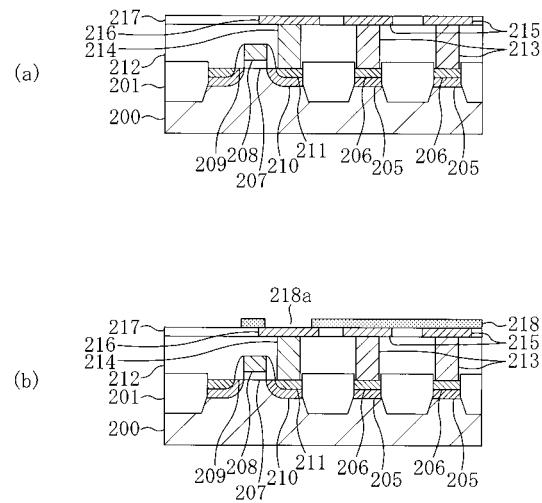

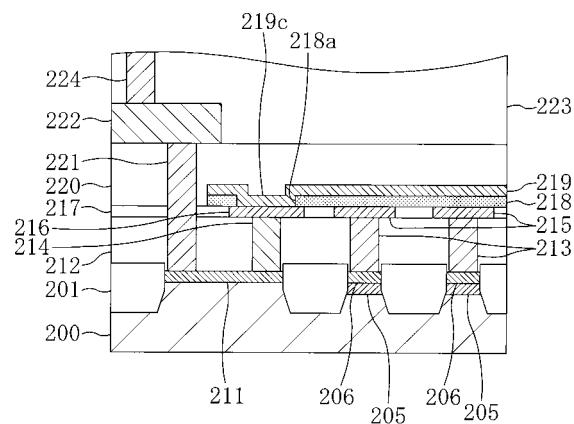

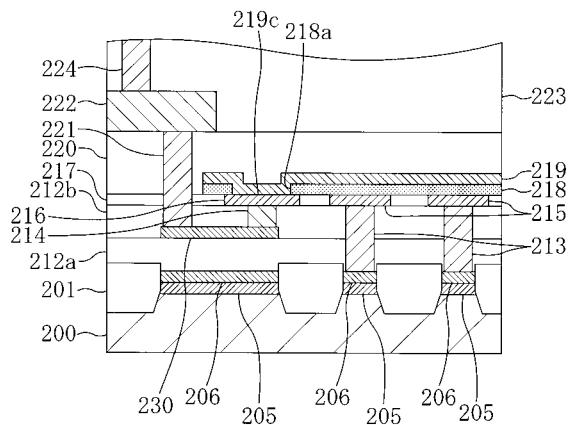

図13(a)、(b)、図14(a)、(b)、図15(a)～(c)及び図16(a)、(b)は、第2の実施形態に係る強誘電体メモリの製造方法の各工程を示す断面図である。尚、図13(b)は図13(a)におけるXIII-XIII線の断面図であり、図16(b)は図16(a)におけるXVI-XVI線の断面図である。30

#### 【0167】

まず、図13(a)及び(b)に示すように、半導体基板200の表面に、STI構造を有する素子分離領域201を形成する。その後、半導体基板200における素子分離領域201により囲まれた領域のうち各メモリセル領域の上に、第1のゲート絶縁膜202を介して、メモリセルトランジスタを構成する第1のゲート電極203を形成する。その後、第1のゲート電極203の側面に絶縁性の第1のサイドウォール204を形成すると共に、半導体基板200における各メモリセル領域の表面部に、下層となる第1の低濃度不純物拡散層205及び上層となる第1の高濃度不純物拡散層206を形成する。第1の低濃度不純物拡散層205及び第1の高濃度不純物拡散層206は、メモリセルトランジスタのソース領域又はドレイン領域となる。40

#### 【0168】

また、図13(a)に示すように、半導体基板200における非メモリセル領域の上に、第2のゲート絶縁膜207を介して、制御トランジスタを構成する第2のゲート電極208を形成する。その後、第2のゲート電極208の側面に絶縁性の第2のサイドウォール209を形成すると共に、半導体基板200における非メモリセル領域の表面部に、下層となる第2の低濃度不純物拡散層210及び上層となる第2の高濃度不純物拡散層211を形成する。50

1を形成する。第2の低濃度不純物拡散層210及び第2の高濃度不純物拡散層211は、制御トランジスタのソース領域又はドレイン領域となる。

#### 【0169】

尚、第2の実施形態において、メモリセルトランジスタ及び制御トランジスタのそれを構成するゲート電極等の各要素を要素毎に同時に形成してもよい。

#### 【0170】

次に、図13(a)及び(b)に示すように、メモリセルトランジスタ及び制御トランジスタが形成されている半導体基板200上に第1の層間絶縁膜212を形成する。その後、第1の層間絶縁膜212に、第1の高濃度不純物拡散層206(ソース領域となる部分)と接続し且つタングステンよりなる第1のプラグ213、及び、第2の高濃度不純物拡散層211(ソース領域となる部分及びドレイン領域となる部分のうちのいずれか一方)と接続し且つタングステンよりなる第2のプラグ214を形成する。10

#### 【0171】

次に、第1の層間絶縁膜212の上面に全面に亘って、酸素バリア性を有する導電性膜(例えばIr膜又はIrO<sub>2</sub>膜等)を全面に成膜した後、該導電性膜をパターン化することによって、図14(a)に示すように、酸素バリア性を有する導電性膜よりなり且つ第1のプラグ213の上面を覆う容量下部電極215、及び酸素バリア性を有する導電性膜よりなり且つ第2のプラグ214の上面を覆う接続パッド216を形成する。これにより、メモリセルトランジスタと容量下部電極215とが第1のプラグ213を介して接続される。その後、容量下部電極215同士の間の領域又は容量下部電極215と接続パッド216との間の領域に、絶縁膜217を、その上面と容量下部電極215及び接続パッド216のそれぞれの上面とが面一になるように埋め込む。20

#### 【0172】

次に、絶縁膜217が形成された第1の層間絶縁膜212の上面に全面に亘って、PZT系又はSBT系の材料よりなる強誘電体膜を成膜した後、該強誘電体膜をパターン化することによって、図14(b)に示すように、容量下部電極215の上面を覆う容量絶縁膜218を形成する。このとき、容量絶縁膜218を接続パッド216つまり第2のプラグ214の上側まで延びるように形成しておくと共に、容量絶縁膜218となる強誘電体膜における接続パッド216の上側に形成されている部分に開口部218aを形成しておく。30

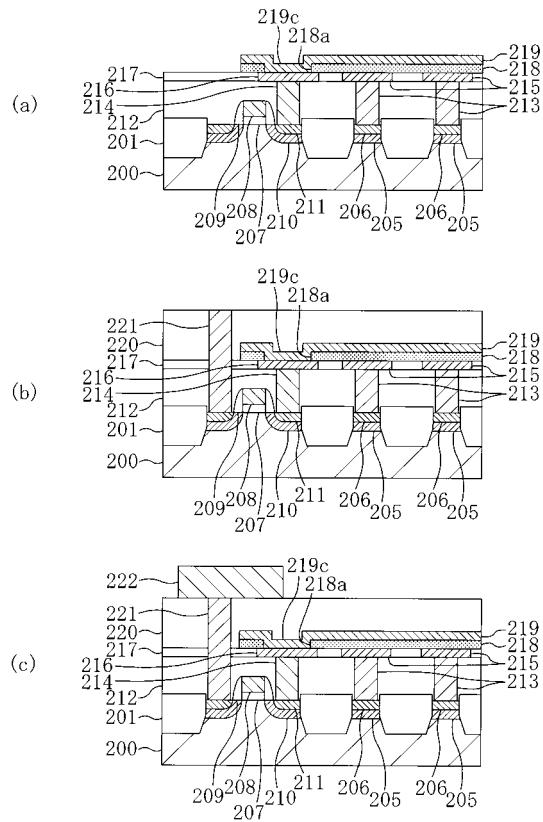

#### 【0173】

次に、開口部218aを有する容量絶縁膜218が形成された第1の層間絶縁膜212の上面に全面に亘って、Pt又はPtを含む合金よりなる導電性膜を成膜した後、該導電性膜をパターン化することによって、図15(a)に示すように、容量絶縁膜218の上面を覆い且つ開口部218aを介して接続パッド216と接続する容量上部電極219を形成する。具体的には、容量上部電極219は、接続パッド216の上面の少なくとも一部分を覆う接続部219cを開口部218a内に有しており、これによって容量上部電極219と第2のプラグ214とが接続パッド216を介して電気的に接続される結果、容量上部電極219と第2の高濃度不純物拡散層211とが第2のプラグ214を介して電気的に接続される。尚、容量下部電極215、容量絶縁膜218及び容量上部電極219により容量素子が構成されている。40

#### 【0174】

次に、図15(b)に示すように、容量素子が形成された第1の層間絶縁膜212の上面に第2の層間絶縁膜220を形成する。その後、第1の層間絶縁膜212、絶縁膜217及び第2の層間絶縁膜220に、タングステンよりなる第3のプラグ221を、第2の高濃度不純物拡散層211(ソース領域となる部分及びドレイン領域となる部分のうち第2のプラグ214が接続されていない方)と接続するように形成する。

#### 【0175】

次に、図15(c)に示すように、第2の層間絶縁膜220の上面に、アルミニウム等よりなる配線222を第3のプラグ221と接続するように形成する。これにより、配線250

22と第2の高濃度不純物拡散層211とが第3のプラグ221を介して接続される。その後、図16(a)及び(b)に示すように、配線222を含む第2の層間絶縁膜220の上に第3の層間絶縁膜223を形成した後、第3の層間絶縁膜223に、タングステンよりなる第4のプラグ224を、配線222と接続するように形成する。尚、図16(b)に示すように、第1の層間絶縁膜212、絶縁膜217及び第2の層間絶縁膜220には第5のプラグ225が形成されており、それによって第1の高濃度不純物拡散層206(ドレイン領域となる部分)と配線222とが接続されている。その後、図示は省略しているが、第3の層間絶縁膜223の上に、さらに上層の層間絶縁膜、配線又は表面保護膜等を形成することによって、強誘電体メモリを完成させる。

## 【0176】

10

以上に説明したように、第2の実施形態によると、メモリセルトランジスタ、及び第2の高濃度不純物拡散層211を含む制御トランジスタが形成された半導体基板200上に第1の層間絶縁膜212を形成した後、第1の層間絶縁膜212に、メモリセルトランジスタと接続する第1のプラグ213、及び第2の高濃度不純物拡散層211と接続する第2のプラグ214を形成する。その後、第1の層間絶縁膜212の上に第1のプラグ213と接続する容量下部電極215を形成した後、容量下部電極215の上に、第2のプラグ214の上側まで延び且つ強誘電体膜よりなる容量絶縁膜218を形成する。その後、容量絶縁膜218における第2のプラグ214の上側に形成されている部分に開口部218aを形成した後、該開口部218aを介して第2のプラグ214と電気的に接続するよう容量上部電極219を形成する。その後、容量上部電極219を含む第1の層間絶縁膜212の上に第2の層間絶縁膜220を形成した後、第1の層間絶縁膜212及び第2の層間絶縁膜220に、第2の高濃度不純物拡散層211と第2の層間絶縁膜220上の配線222とを接続する第3のプラグ221を形成する。このため、容量上部電極219の形成前に、具体的には、メモリセルトランジスタと容量下部電極215とを接続する第1のプラグ213の形成と同時に、容量上部電極219と第2の高濃度不純物拡散層211とを接続する第2のプラグ214を第1の層間絶縁膜212に形成できる。これにより、第2のプラグ214、第2の高濃度不純物拡散層211及び第3のプラグ221を介して容量上部電極219と配線222とを電気的に接続することができる。すなわち、予め容量素子よりも下側に形成されている第2のプラグ214及び第2の高濃度不純物拡散層211を用いて、容量上部電極219と配線222とを電気的に接続することができる。従って、容量上部電極219の形成後に、容量上部電極219と配線222とを直接接続するプラグを形成するためのコンタクトホールを形成する必要がないので、容量上部電極219が露出して水素雰囲気又は還元性雰囲気にさらされる事態を回避できる。その結果、容量上部電極219として強い触媒作用を有するPt膜を用いる場合にも、容量絶縁膜218を構成する強誘電体膜の特性の劣化を防止して強誘電体メモリの信頼性を向上させることができる。

20

30

40

## 【0177】

また、第2の実施形態によると、酸素バリア性を有する容量下部電極215が第1のプラグ213の上面を覆っていると共に、酸素バリア性を有する接続パッド216が第2のプラグ214の上面を覆っている。このため、容量絶縁膜218を構成する強誘電体膜を酸素雰囲気中で焼結するときに、第1のプラグ213及び第2のプラグ214が酸化されることを防止できる。

## 【0178】

また、第2の実施形態によると、容量下部電極215の材料として用いられ且つ酸素バリア性を有する導電性膜を第2のプラグ214の上面全体を覆うようにパターン化することによって、容量下部電極215の形成と同時に接続パッド216を形成するため、工程の増加を招くことなく第2のプラグ214の酸化を防止できる。また、容量上部電極219を接続パッド216と接続するように形成するため、容量上部電極219と第2のプラグ214とを接続パッド216を介して接続できる。

## 【0179】

50

また、第2の実施形態によると、容量下部電極215同士の間の領域又は容量下部電極215と接続パッド216との間の領域に、絶縁膜217を、その上面と容量下部電極215及び接続パッド216のそれぞれの上面とが面一になるように埋め込む。このため、容量絶縁膜218等の堆積工程を平坦な下地上で行なえるので、容量素子の信頼性つまり強誘電体メモリの信頼性を向上させることができる。

#### 【0180】

また、第2の実施形態によると、第2の高濃度不純物拡散層211の表面部をシリサイド化してシリサイド層を形成しておき、該シリサイド層を、第2のプラグ214と第3のプラグ221とを接続する導電層として用いた場合、次のような効果が得られる。すなわち、第2のプラグ214と第3のプラグ221とを接続する導電層として、半導体基板200上に形成されたポリシリコン層等を用いる場合と比べて、該導電層を低抵抗化できる。10

#### 【0181】

さらに、第2の実施形態によると、以下に説明するような効果が得られる。

#### 【0182】

図17(a)は、第1の比較例としての第1の実施形態に係る強誘電体メモリにおける、第2のプラグ214、接続パッド216、容量絶縁膜218及び容量上部電極219の積層部分の断面図と該断面図と対応する平面図を示している。

#### 【0183】

図17(b)は、第2の実施形態に係る強誘電体メモリにおける、第2のプラグ214、接続パッド216、容量絶縁膜218及び容量上部電極219の積層部分の断面図と該断面図と対応する平面図を示している。20

#### 【0184】

第1の比較例においては、図17(a)に示すように、容量上部電極219の段差が容量絶縁膜218の1端辺に沿って1方向に形成されている(領域R1参照)。また、容量絶縁膜218となる絶縁性膜と容量上部電極219となる導電性膜とが別々にパターン化されるため、容量絶縁膜形成用のマスクパターンと容量上部電極形成用のマスクパターンとの間でマスク合わせマージンD1を考慮する必要がある。

#### 【0185】

一方、第2の実施形態においては、図17(b)に示すように、容量絶縁膜218に設けた開口部218aを介して容量上部電極219と接続パッド216つまり第2のプラグ214とを接続するため、容量上部電極219の段差は開口部218aの周縁部に沿って形成される(領域R2参照)。具体的には、開口部218aの形状を例えば方形にすると、容量上部電極219の段差は開口部218aの周縁部となる4辺に沿って4方向に形成される。このため、容量上部電極形成材料の段差部における被覆率に方向依存性があっても、第1の比較例(容量上部電極219の段差が容量絶縁膜218の1端辺に沿って1方向に形成されている)と比べて、容量上部電極219と第2のプラグ214との間の電流パスが確実に確保される。30

#### 【0186】

尚、第2の実施形態において、図14(b)及び図15(a)に示す工程で、容量絶縁膜218となる絶縁性膜をパターン化する前に、該絶縁性膜に開口部218aを設けた後、該絶縁性膜と容量上部電極219となる導電性膜とを同時にパターン化することが好ましい。このようにすると、容量絶縁膜形成用のマスクパターンと容量上部電極形成用のマスクパターンとの間でマスク合わせマージンを考慮する必要がなくなる。その結果、強誘電体メモリのセルサイズを小さくでき、それによってメモリセルアレイ全体の占有面積を縮小することができる。40

#### 【0187】

また、第2の実施形態において、第1のプラグ213、第2のプラグ214、又は第3のプラグ221等の材料として、タンゲステンを用いたが、これに代えて、ポリシリコン等を用いてもよい。

## 【0188】

また、第2の実施形態において、容量下部電極215としては、酸素含有率の少ないTiON膜若しくはTiN膜、又はTiを含む合金膜等を下層膜（密着層として機能する）とし、且つ耐酸化性の強いPt膜若しくはPtを含む合金膜、酸化物が酸素バリア性及び導電性を有するRu膜若しくはIr膜、又はRuO<sub>2</sub>膜若しくはIrO<sub>2</sub>膜等を上層膜とする積層膜を用いることが好ましい。

## 【0189】

また、第2の実施形態において、容量下部電極215同士の間に埋め込まれる絶縁膜217としては、SiO<sub>2</sub>膜、Si<sub>3</sub>N<sub>4</sub>膜、又はSiON膜等を用いることが好ましい。

## 【0190】

また、第2の実施形態において、容量絶縁膜218を構成する強誘電体膜の材料としては、PZT系の材料又はSBT系の材料等を用いることが好ましい。

## 【0191】

また、第2の実施形態において、容量上部電極219としては、耐酸化性の強いPt膜若しくはPtを含む合金膜、酸化物が酸素バリア性及び導電性を有するRu膜若しくはIr膜、又はRuO<sub>2</sub>膜若しくはIrO<sub>2</sub>膜等を少なくとも一部分に用いることが好ましい。このようにすると、容量絶縁膜218を構成する強誘電体膜の結晶を十分に成長させることができる。

## 【0192】

また、第2の実施形態において、半導体基板200上における非メモリセル領域に、第2のゲート電極208等により構成される制御トランジスタ（容量上部電極219つまりメモリセルプレートをON/OFFするドライバーとしての機能を有している）を形成した。すなわち、第2の実施形態においては、制御トランジスタがONになっている場合のみ、容量上部電極219と配線222とは、第2のプラグ214、第2の高濃度不純物拡散層211（つまり制御トランジスタのソース領域又はドレイン領域）及び第3のプラグ221を介して電気的に接続される。それに対して、回路構成上、制御トランジスタを必要としない強誘電体メモリにおいては、例えば図18に示すように、半導体基板200上における非メモリセル領域に第2の高濃度不純物拡散層211のみを形成してもよい。この場合、容量上部電極219と配線222とは、第2のプラグ214、第2の高濃度不純物拡散層211及び第3のプラグ221を介して常に電気的に接続される。また、この場合、第2の高濃度不純物拡散層211の表面部をシリサイド化してもよい。

## 【0193】

また、第2の実施形態において、第2のプラグ214と第3のプラグ221とを接続する導電層として第2の高濃度不純物拡散層211を用いたが、これに代えて、例えば図19に示すように、第1の層間絶縁膜212の下層膜212aと上層膜212bとの間に形成された導電層230を用いてもよい。図19に示す構造の形成方法（詳しくは第1の実施形態の第2変形例を参照）のうち、本実施形態の方法と大きく異なる点は次の通りである。すなわち、メモリセルトランジスタが形成された半導体基板200上に第1の層間絶縁膜212の下層膜212aを形成した後、非メモリセル領域の下層膜212aの上に導電層230を形成し、その後、第1の層間絶縁膜212の上層膜212bを形成する。その後、第1の層間絶縁膜212に、メモリセルトランジスタと接続する第1のプラグ213、及び導電層230と接続する第2のプラグ214を形成する。ここで、導電層230の材料は特に限定されるものではないが、導電層230が容量上部電極219の引き出し配線に使用されることを考慮して、導電層230の材料として低抵抗材料、例えばポリシリコン若しくはそれをシリサイド化したもの又はタンゲステン等を用いることが好ましい。また、導電層230として、強誘電体キャパシタ（容量下部電極215、容量絶縁膜218及び容量上部電極219により構成される容量素子）よりも下側の配線層、例えばビット線に使用される配線層を利用してよい。或いは、導電層230として、例えば図20に示すように、半導体基板200上に層間絶縁膜を介さずに形成された配線層、例えばメモリセルトランジスタ又は制御トランジスタのゲート電極と同時に形成された配線層を

10

20

30

40

50

用いてもよい。このとき、該配線層は、素子分離領域 201 の上に形成されてもよいし、半導体基板 200 における素子分離領域 201 が形成されていない領域の上に形成されてもよい。

#### 【0194】

また、第2の実施形態において、第2のプラグ 214 の上面を酸素バリア性を有する接続パッド 216 により覆ったが、これに代えて、例えば第2のプラグ 214 が酸素バリア性を有する材料となる場合には、接続パッド 216 を形成しなくてもよい。このようにすると、強誘電体メモリの集積度を向上させることができる。また、このとき、容量上部電極 219 の接続部 219c は、第2のプラグ 214 の上面の少なくとも一部分を覆うことが好ましい。

#### 【0195】

また、第2の実施形態において、容量下部電極 215 同士の間の領域又は容量下部電極 215 と接続パッド 216との間の領域に、絶縁膜 217 を埋め込んだが、これに代えて、絶縁膜 217 を形成しなくてもよい。

#### 【0196】

また、第2の実施形態において、容量上部電極 219 を形成する前に、開口部 218a の壁面にサイドウォールを形成しておくことが好ましい。このようにすると、容量上部電極 219 となる導電性膜の段差被覆性が向上して、容量上部電極 219 の接続部 219c に断線が生じる事態を防止できるので、強誘電体メモリの信頼性を向上させることができる。

#### 【0197】

また、第2の実施形態において、第2の層間絶縁膜 220 の上に第3のプラグ 221 と接続するように配線 222 を形成したが、これに代えて、第2の層間絶縁膜 220 に第3のプラグ 221 と接続するように配線 222 を埋め込んでもよい。

#### 【0198】

##### (第3の実施形態)

以下、本発明の第3の実施形態に係る強誘電体メモリ及びその製造方法について図面を参照しながら説明する。

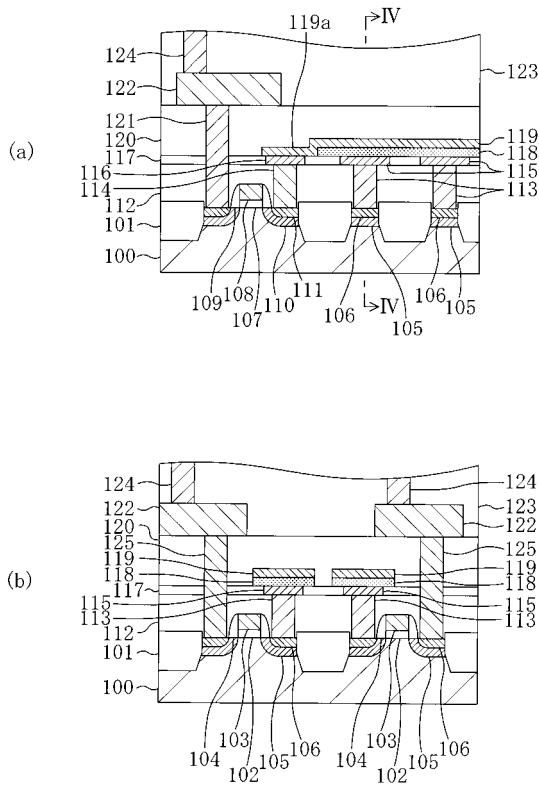

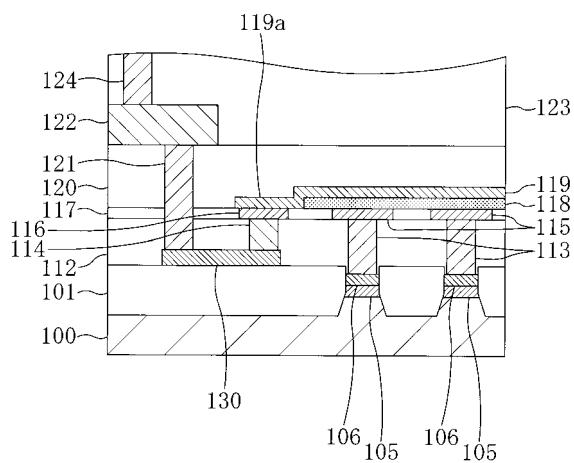

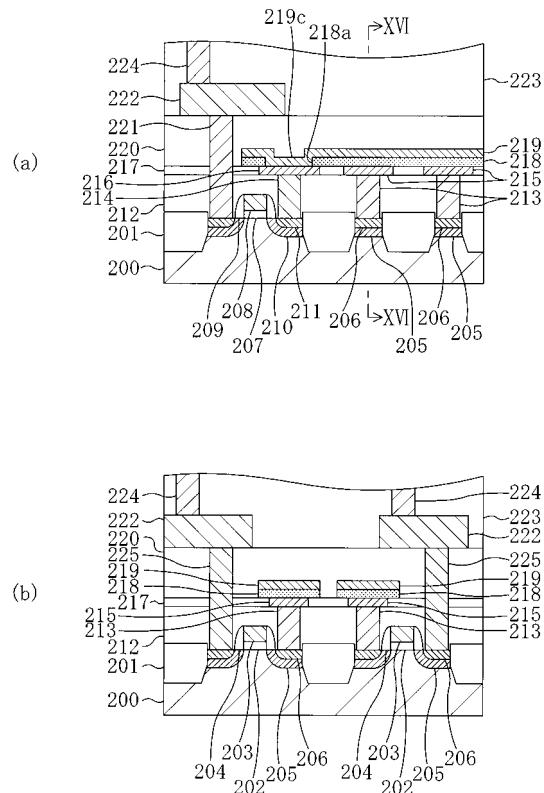

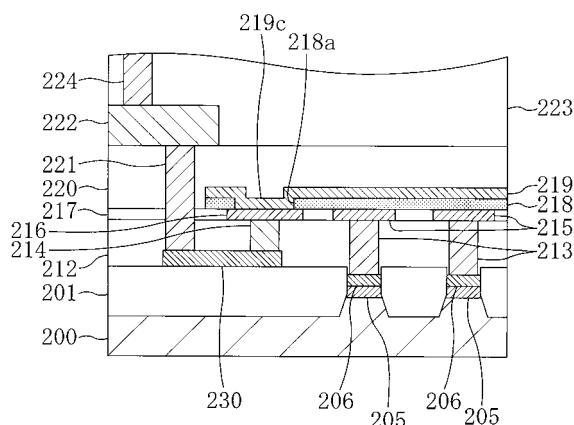

#### 【0199】

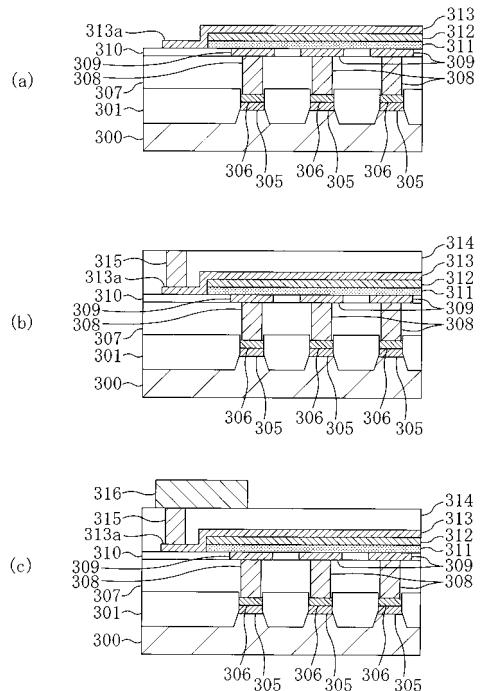

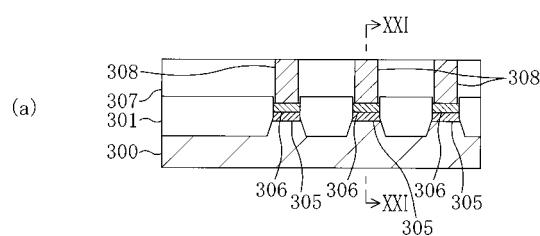

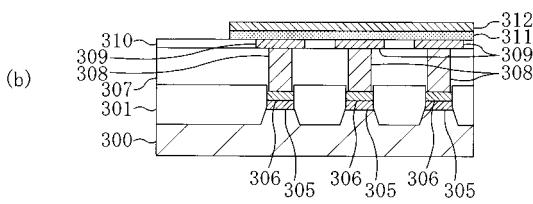

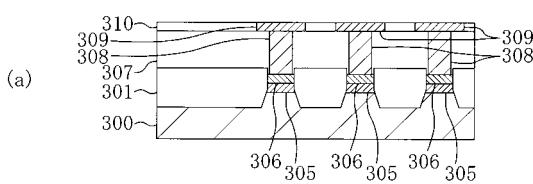

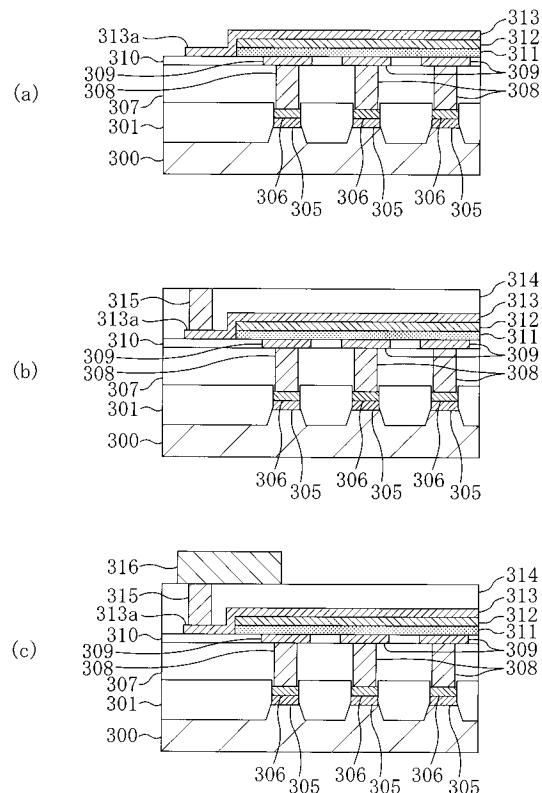

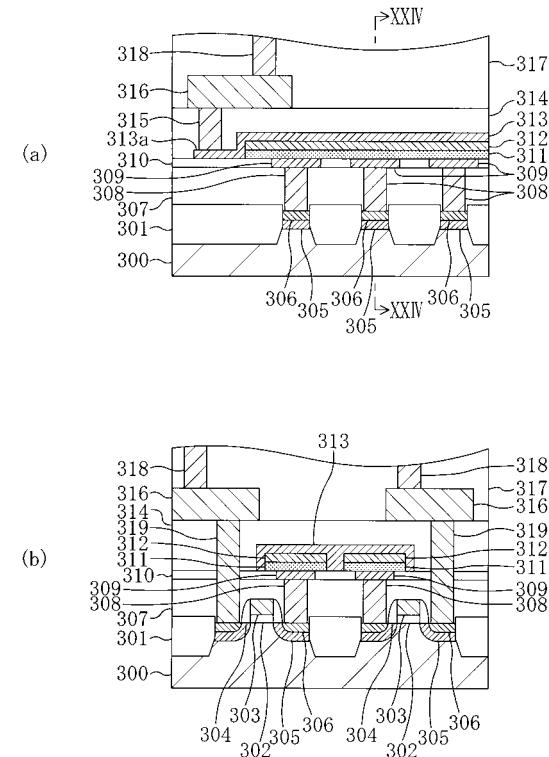

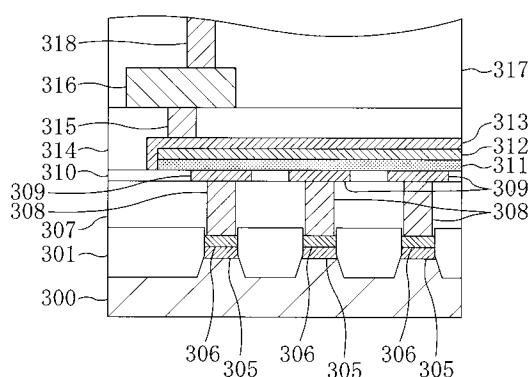

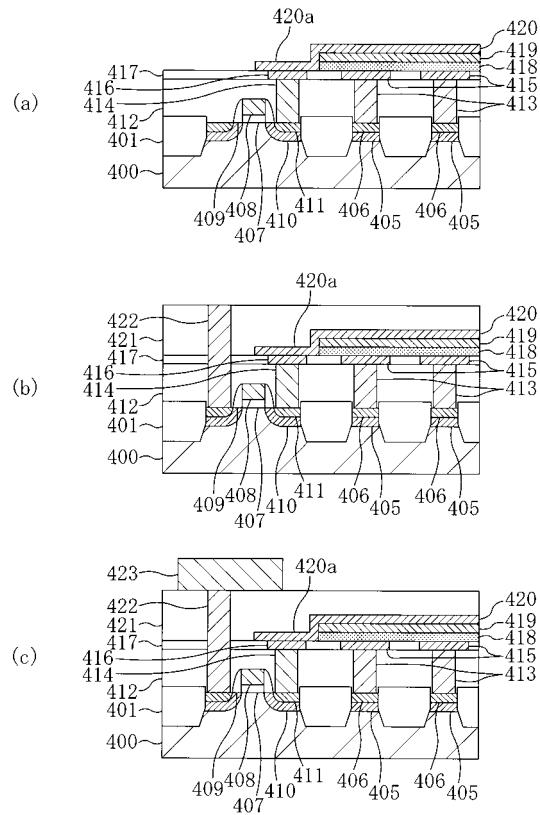

図 21 (a)、(b)、図 22 (a)、(b)、図 23 (a)～(c) 及び図 24 (a)、(b) は、第3の実施形態に係る強誘電体メモリの製造方法の各工程を示す断面図である。尚、図 21 (b) は図 21 (a) における XXI - XXI 線の断面図であり、図 24 (b) は図 24 (a) における XXIV - XXIV 線の断面図である。

#### 【0200】

まず、図 21 (a) 及び (b) に示すように、半導体基板 300 の表面に、STI構造を有する素子分離領域 301 を形成する。その後、半導体基板 300 における素子分離領域 301 により囲まれた領域のうち各メモリセル領域の上に、ゲート絶縁膜 302 を介して、メモリセルトランジスタを構成するゲート電極 303 を形成する。その後、ゲート電極 303 の側面に絶縁性のサイドウォール 304 を形成すると共に、半導体基板 300 における各メモリセル領域の表面部に、下層となる低濃度不純物拡散層 305 及び上層となる高濃度不純物拡散層 306 を形成する。低濃度不純物拡散層 305 及び高濃度不純物拡散層 306 は、メモリセルトランジスタのソース領域又はドレイン領域となる。その後、メモリセルトランジスタが形成されている半導体基板 300 上に第1の層間絶縁膜 307 を形成した後、第1の層間絶縁膜 307 に、高濃度不純物拡散層 306 (ソース領域となる部分) と接続し且つタングステンよりなる第1のプラグ 308 を形成する。

#### 【0201】

次に、第1の層間絶縁膜 307 の上に全面に亘って、酸素バリア性を有する導電性膜 (例えば Ir 膜又は IrO<sub>2</sub> 膜等) を全面に成膜した後、該導電性膜をパターン化することによって、図 22 (a) に示すように、酸素バリア性を有する導電性膜よりなり且つ第1のプラグ 308 の上面を覆う容量下部電極 309 を形成する。これにより、メモリセルト

ランジスタと容量下部電極 309 とが第1のプラグ 308 を介して接続される。その後、容量下部電極 309 同士の間に領域に、絶縁膜 310 を、その上面と容量下部電極 309 の上面とが面一になるように埋め込む。

#### 【0202】

次に、絶縁膜 310 が形成された第1の層間絶縁膜 307 の上に全面に亘って、PZT 系又は SBT 系の材料よりなる強誘電体膜、及び Pt 又は Pt を含む合金よりなる導電性膜を順次成膜した後、該導電性膜及び強誘電体膜を同一のマスクパターン（図示省略）を用いてパターン化することによって、図 22 (b) に示すように、容量下部電極 309 の上面を覆う容量絶縁膜 311、及び容量絶縁膜 311 の上面を覆う容量上部電極 312 を形成する。尚、容量下部電極 309、容量絶縁膜 311 及び容量上部電極 312 により容量素子が構成されている。10

#### 【0203】

次に、容量素子が形成された第1の層間絶縁膜 307 の上に全面に亘って、水素バリア性を有する導電性膜、例えば Ti 膜若しくは Ta 膜又は Ti 若しくは Ta を含む合金膜を成膜した後、該導電性膜をパターン化することによって、図 23 (a) に示すように、容量素子を覆う導電性水素バリア膜 313 を形成する。このとき、導電性水素バリア膜 313 を容量上部電極 312 の外側まで延びるように形成する。すなわち、導電性水素バリア膜 313 は、絶縁膜 310 における容量上部電極 312 が形成されていない領域の上側を覆う張り出し部 313a を有している。20

#### 【0204】

次に、図 23 (b) に示すように、導電性水素バリア膜 313 が形成された第1の層間絶縁膜 307 の上に第2の層間絶縁膜 314 を形成する。その後、第2の層間絶縁膜 314 に、タンゲステンよりなる第2のプラグ 315 を、導電性水素バリア膜 313 の張り出し部 313a、つまり導電性水素バリア膜 313 における容量上部電極 312 にオーバーラップしていない部分と接続するように形成する。30

#### 【0205】

次に、図 23 (c) に示すように、第2の層間絶縁膜 314 の上に、アルミニウム等よりなる配線 316 を第2のプラグ 315 と接続するように形成する。これにより、容量上部電極 312 と配線 316 とが導電性水素バリア膜 313 及び第2のプラグ 315 を介して接続される。その後、図 24 (a) 及び (b) に示すように、配線 316 を含む第2の層間絶縁膜 314 の上に第3の層間絶縁膜 317 を形成した後、第3の層間絶縁膜 317 に、タンゲステンよりなる第3のプラグ 318 を、配線 316 と接続するように形成する。尚、図 24 (b) に示すように、第1の層間絶縁膜 307、絶縁膜 310 及び第2の層間絶縁膜 314 には第4のプラグ 319 が形成されており、それによって高濃度不純物拡散層 306 (ドレイン領域となる部分) と配線 316 とが接続されている。その後、図示は省略しているが、第3の層間絶縁膜 317 の上に、さらに上層の層間絶縁膜、配線又は表面保護膜等を形成することによって、強誘電体メモリを完成させる。30

#### 【0206】

以上に説明したように、第3の実施形態によると、メモリセルトランジスタが形成された半導体基板 300 上に第1の層間絶縁膜 307 を形成した後、第1の層間絶縁膜 307 に、メモリセルトランジスタと接続する第1のプラグ 308 を形成し、その後、第1の層間絶縁膜 307 の上に第1のプラグ 308 と接続する容量下部電極 309 を形成する。その後、容量下部電極 309 の上に、強誘電体膜よりなる容量絶縁膜 311、及び容量上部電極 312 を順次形成した後、容量上部電極 312 の上に導電性水素バリア膜 313 を形成する。その後、導電性水素バリア膜 313 を含む第1の層間絶縁膜 307 の上に第2の層間絶縁膜 314 を形成した後、第2の層間絶縁膜 314 に、導電性水素バリア膜 313 と第2の層間絶縁膜 314 上の配線 316 とを接続する第2のプラグ 315 を形成する。このため、導電性水素バリア膜 313 及び第2のプラグ 315 を介して容量上部電極 312 と配線 316 とを電気的に接続することができる。従って、容量上部電極 312 の形成後に、容量上部電極 312 と配線 316 とを直接接続するプラグを形成するためのコンタ4050

クトホールを形成する必要がないので、容量上部電極312が露出して水素雰囲気又は還元性雰囲気にさらされる事態を回避できる。その結果、容量上部電極312として強い触媒作用を有するPt膜を用いる場合にも、容量絶縁膜311を構成する強誘電体膜の特性の劣化を防止して、強誘電体メモリの信頼性を向上させることができる。

#### 【0207】

また、第3の実施形態によると、導電性水素バリア膜313を容量上部電極312の外側まで延びるように形成することによって、導電性水素バリア膜313における容量上部電極312にオーバーラップしていない部分(張り出し部313a)の上に第2のプラグ315を形成する。このため、第2のプラグ315を形成するためのコンタクトホールを第2の層間絶縁膜314に形成するときに、オーバーエッチングに起因して導電性水素バリア膜313が除去されて容量上部電極312が露出する事態を確実に回避することができる。10

#### 【0208】

また、第3の実施形態によると、容量下部電極309、容量絶縁膜311及び容量上部電極312より構成される容量素子の全体を導電性水素バリア膜313によって常に覆っているため、容量素子の耐還元性を向上させることができる。

#### 【0209】

また、第3の実施形態によると、酸素バリア性を有する容量下部電極309によって第1のプラグ308の上面を覆うため、容量絶縁膜311を構成する強誘電体膜を酸素雰囲気中で焼結するときに、第1のプラグ308が酸化されることを防止できる。20

#### 【0210】

また、第3の実施形態によると、容量下部電極309同士の間の領域に、絶縁膜310を、その上面と容量下部電極309の上面とが面一になるように埋め込む。このため、容量絶縁膜311等の堆積工程を平坦な下地上で行なえるので、容量素子の信頼性つまり強誘電体メモリの信頼性を向上させることができる。

#### 【0211】

尚、第3の実施形態において、第1のプラグ308又は第2のプラグ315等の材料として、タンゲステンを用いたが、これに代えて、ポリシリコン等を用いてもよい。

#### 【0212】

また、第3の実施形態において、容量下部電極309としては、酸素含有率の少ないTiON膜若しくはTiN膜、又はTiを含む合金膜等を下層膜(密着層として機能する)とし、且つ耐酸化性の強いPt膜若しくはPtを含む合金膜、酸化物が酸素バリア性及び導電性を有するRu膜若しくはIr膜、又はRuO<sub>2</sub>膜若しくはIrO<sub>2</sub>膜等を上層膜とする積層膜を用いることが好ましい。30

#### 【0213】

また、第3の実施形態において、容量下部電極309同士の間に埋め込まれる絶縁膜310としては、SiO<sub>2</sub>膜、Si<sub>3</sub>N<sub>4</sub>膜、又はSiON膜等を用いることが好ましい。

#### 【0214】

また、第3の実施形態において、容量絶縁膜311を構成する強誘電体膜の材料としては、PZT系の材料又はSBT系の材料等を用いることが好ましい。40

#### 【0215】

また、第3の実施形態において、容量上部電極312としては、耐酸化性の強いPt膜若しくはPtを含む合金膜、酸化物が酸素バリア性及び導電性を有するRu膜若しくはIr膜、又はRuO<sub>2</sub>膜若しくはIrO<sub>2</sub>膜等を少なくとも一部分に用いることが好ましい。このようにすると、容量絶縁膜311を構成する強誘電体膜の結晶を十分に成長させることができる。

#### 【0216】

また、第3の実施形態において、導電性水素バリア膜313としては、Ti膜、Ta膜、TiON膜、TiN膜、TaN膜、TiAlN膜、TiAlON膜、又は、Ti、Ta、TiON、TiN、TaN、TiAlN若しくはTiAlONを含む合金膜を用いるこ50

とが好ましい。このようにすると、T<sub>i</sub>やT<sub>a</sub>の水素を吸収する性質を利用して、容量上部電極312まで水素が拡散することを防止し、それによって容量素子の耐還元性を確実に向上させることができる。また、導電性水素バリア膜313の導電性が確実に保たれるので、導電性水素バリア膜313を介して容量上部電極312と第2のプラグ315とを電気的に確実に接続することができる。

#### 【0217】

また、第3の実施形態において、容量下部電極309同士の間の領域に、絶縁膜310を埋め込んだが、これに代えて、絶縁膜310を形成しなくてもよい。

#### 【0218】

また、第3の実施形態において、容量絶縁膜311となる強誘電体膜及び容量上部電極312となる導電性膜を同一のマスクパターンを用いてパターン化したが、これに代えて、該導電性膜及び強誘電体膜を互いに異なるマスクパターンを用いてパターン化してもよい。

#### 【0219】

また、第3の実施形態において、導電性水素バリア膜313を形成する前に、容量上部電極312及び容量絶縁膜311のそれぞれの側面にサイドウォールを形成しておくことが好ましい。このようにすると、導電性水素バリア膜313となる導電性膜の段差被覆性が向上して、導電性水素バリア膜313の張り出し部313aに断線が生じる事態を防止できるので、強誘電体メモリの信頼性を向上させることができる。

#### 【0220】

また、第3の実施形態において、導電性水素バリア膜313を容量上部電極312の外側まで延びるように形成することによって、導電性水素バリア膜313の張り出し部313aの上に第2のプラグ315を形成したが、これに代えて、例えば図25に示すように、張り出し部313aを形成せずに、導電性水素バリア膜313における容量上部電極312にオーバーラップしている部分の上に第2のプラグ315を形成してもよい。この場合、第2のプラグ315を形成するためのコンタクトホールを第2の層間絶縁膜314に形成するときに、導電性水素バリア膜313と第2の層間絶縁膜314との間のエッチング選択比が高くなるようなエッチング条件を使用することが好ましい。このようにすると、オーバーエッチングを行なっても導電性水素バリア膜313が除去されることがないので、容量上部電極312が露出する事態を防止できる。

#### 【0221】

また、第3の実施形態において、第2の層間絶縁膜314の上に第2のプラグ315と接続するように配線316を形成したが、これに代えて、第2の層間絶縁膜314に第2のプラグ315と接続するように配線316を埋め込んでもよい。

#### 【0222】

##### (第4の実施形態)

以下、本発明の第4の実施形態に係る強誘電体メモリ及びその製造方法について図面を参照しながら説明する。

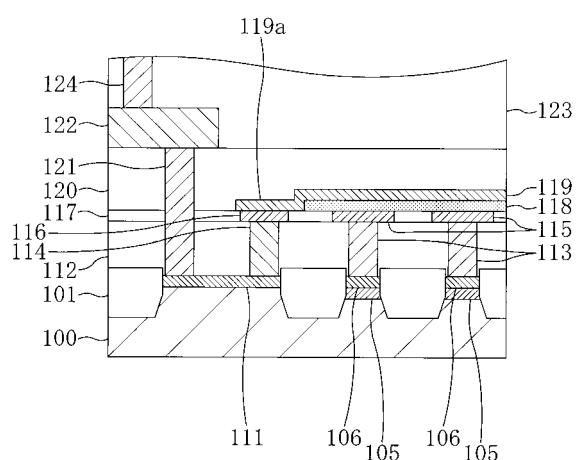

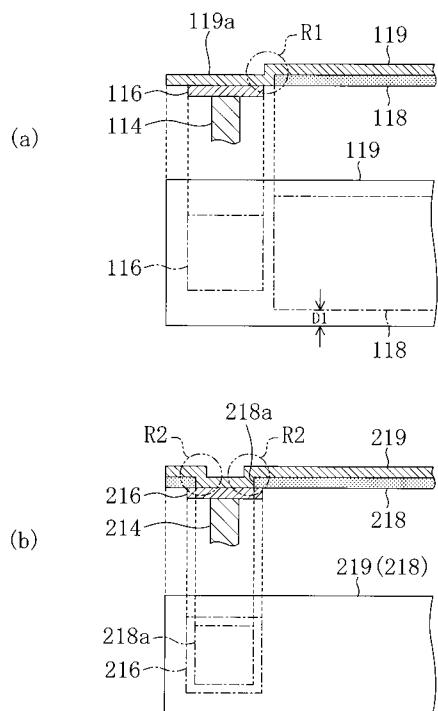

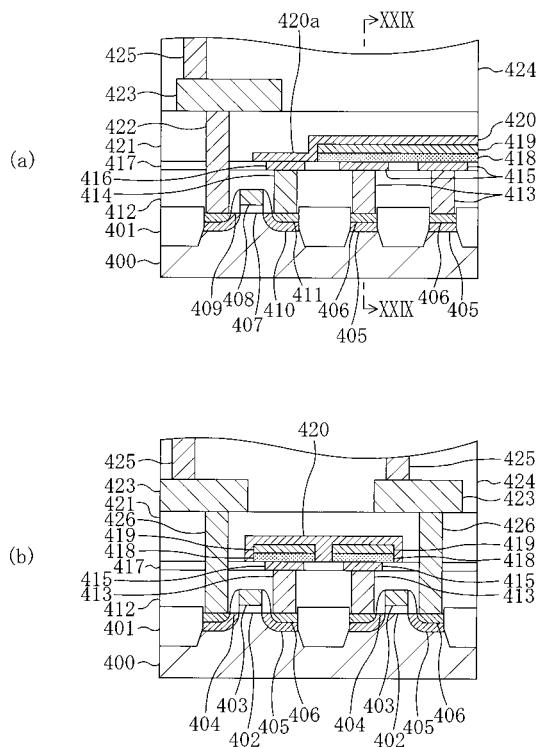

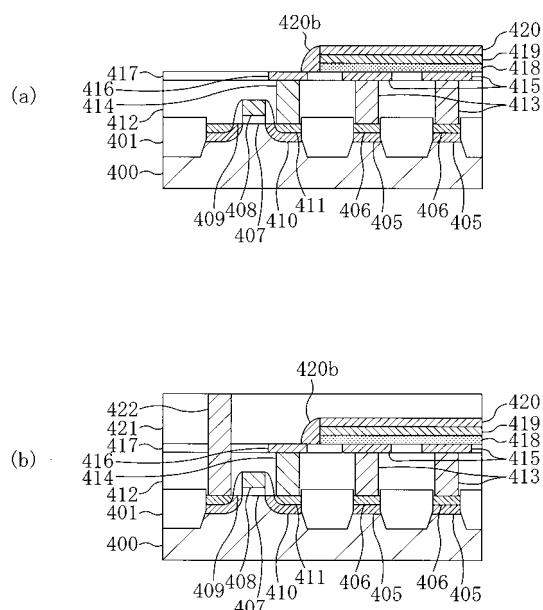

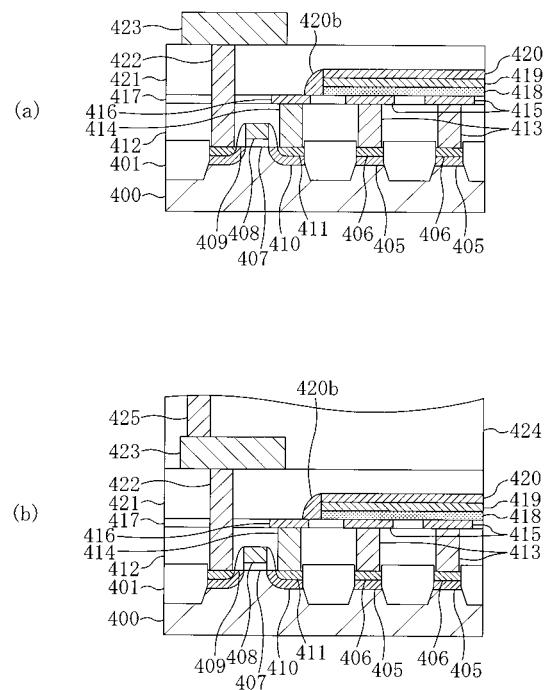

#### 【0223】

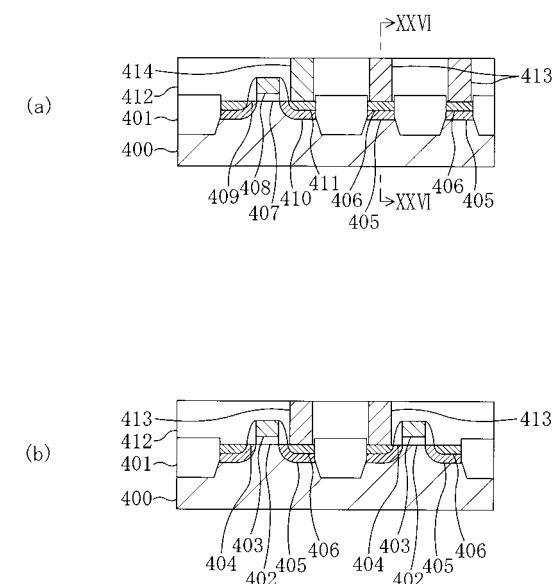

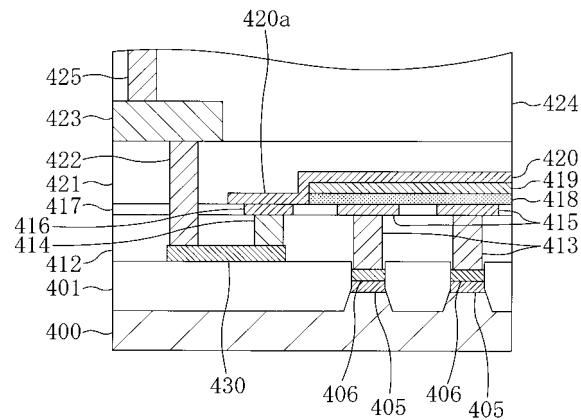

図26(a)、(b)、図27(a)、(b)、図28(a)～(c)及び図29(a)、(b)は、第4の実施形態に係る強誘電体メモリの製造方法の各工程を示す断面図である。尚、図26(b)は図26(a)におけるXXVI-XXVI線の断面図であり、図29(b)は図29(a)におけるXXIX-XXIX線の断面図である。

#### 【0224】

まず、図26(a)及び(b)に示すように、半導体基板400の表面に、STI構造を有する素子分離領域401を形成する。その後、半導体基板400における素子分離領域401により囲まれた領域のうち各メモリセル領域の上に、第1のゲート絶縁膜402を介して、メモリセルトランジスタを構成する第1のゲート電極403を形成する。その後、第1のゲート電極403の側面に絶縁性の第1のサイドウォール404を形成すると共に、半導体基板400における各メモリセル領域の表面部に、下層となる第1の低濃度

10

20

30

40

50

不純物拡散層 405 及び上層となる第 1 の高濃度不純物拡散層 406 を形成する。第 1 の低濃度不純物拡散層 405 及び第 1 の高濃度不純物拡散層 406 は、メモリセルトランジスタのソース領域又はドレイン領域となる。

#### 【0225】

また、図 26(a) に示すように、半導体基板 400 における非メモリセル領の上に、第 2 のゲート絶縁膜 407 を介して、制御トランジスタを構成する第 2 のゲート電極 408 を形成する。その後、第 2 のゲート電極 408 の側面に絶縁性の第 2 のサイドウォール 409 を形成すると共に、半導体基板 400 における非メモリセル領域の表面部に、下層となる第 2 の低濃度不純物拡散層 410 及び上層となる第 2 の高濃度不純物拡散層 411 を形成する。第 2 の低濃度不純物拡散層 410 及び第 2 の高濃度不純物拡散層 411 は、10 制御トランジスタのソース領域又はドレイン領域となる。

#### 【0226】

尚、第 4 の実施形態において、メモリセルトランジスタ及び制御トランジスタのそれぞれを構成するゲート電極等の各要素を要素毎に同時に形成してもよい。

#### 【0227】

次に、図 26(a) 及び(b) に示すように、メモリセルトランジスタ及び制御トランジスタが形成されている半導体基板 400 上に第 1 の層間絶縁膜 412 を形成する。その後、第 1 の層間絶縁膜 412 に、第 1 の高濃度不純物拡散層 406(ソース領域となる部分)と接続し且つタングステンよりなる第 1 のプラグ 413、及び、第 2 の高濃度不純物拡散層 411(ソース領域となる部分及びドレイン領域となる部分のうちのいずれか一方)と接続し且つタングステンよりなる第 2 のプラグ 414 を形成する。20

#### 【0228】

次に、第 1 の層間絶縁膜 412 の上に全面に亘って、酸素バリア性を有する導電性膜(例えは Ir 膜又は IrO<sub>2</sub> 膜等)を全面に成膜した後、該導電性膜をパターン化することによって、図 27(a) に示すように、酸素バリア性を有する導電性膜よりなり且つ第 1 のプラグ 413 の上面を覆う容量下部電極 415、及び酸素バリア性を有する導電性膜よりなり且つ第 2 のプラグ 414 の上面を覆う接続パッド 416 を形成する。これにより、メモリセルトランジスタと容量下部電極 415 とが第 1 のプラグ 413 を介して接続される。その後、容量下部電極 415 同士の間の領域又は容量下部電極 415 と接続パッド 416との間の領域に、絶縁膜 417 を、その上面と容量下部電極 415 及び接続パッド 416 のそれぞれの上面とが面一になるように埋め込む。30

#### 【0229】

次に、絶縁膜 417 が形成された第 1 の層間絶縁膜 412 の上に全面に亘って、PZT 系又は SBT 系の材料よりなる強誘電体膜、及び Pt 又は Pt を含む合金よりなる導電性膜を順次成膜した後、該導電性膜及び強誘電体膜を同一のマスクパターン(図示省略)を用いてパターン化することによって、図 27(b) に示すように、容量下部電極 415 の上面を覆う容量絶縁膜 418、及び容量絶縁膜 418 の上面を覆う容量上部電極 419 を形成する。尚、容量下部電極 415、容量絶縁膜 418 及び容量上部電極 419 により容量素子が構成されている。

#### 【0230】

次に、容量素子が形成された第 1 の層間絶縁膜 412 の上に全面に亘って、水素バリア性を有する導電性膜、例えは Ti 膜若しくは Ta 膜又は Ti 若しくは Ta を含む合金膜を成膜した後、該導電性膜をパターン化することによって、図 28(a) に示すように、容量素子を覆い且つ容量上部電極 419 の外側まで延びるように導電性水素バリア膜 420 を形成する。具体的には、導電性水素バリア膜 420 は、接続パッド 416 の上面の少なくとも一部分を覆う張り出し部 420a を有しており、該張り出し部 420a は、導電性水素バリア膜 420 となる導電性膜をパターン化するときに形成されている。これにより、導電性水素バリア膜 420 と第 2 のプラグ 414 とが接続パッド 416 を介して接続されるので、導電性水素バリア膜 420 と第 2 の高濃度不純物拡散層 411 とが第 2 のプラグ 414 を介して電気的に接続される。4050

## 【0231】

次に、図28(b)に示すように、導電性水素バリア膜420が形成された第1の層間絶縁膜412の上に第2の層間絶縁膜421を形成する。その後、第1の層間絶縁膜412、絶縁膜417及び第2の層間絶縁膜421に、タングステンよりなる第3のプラグ422を、第2の高濃度不純物拡散層411(ソース領域となる部分及びドレイン領域となる部分のうち第2のプラグ414が接続されていない方)と接続するように形成する。

## 【0232】

次に、図28(c)に示すように、第2の層間絶縁膜421の上に、アルミニウム等よりなる配線423を第3のプラグ422と接続するように形成する。これにより、配線423と第2の高濃度不純物拡散層411とが第3のプラグ422を介して接続される。その後、図29(a)及び(b)に示すように、配線423を含む第2の層間絶縁膜421の上に第3の層間絶縁膜424を形成した後、第3の層間絶縁膜424に、タングステンよりなる第4のプラグ425を、配線423と接続するように形成する。尚、図29(b)に示すように、第1の層間絶縁膜412、絶縁膜417及び第2の層間絶縁膜421には第5のプラグ426が形成されており、それによって第1の高濃度不純物拡散層406(ドレイン領域となる部分)と配線423とが接続されている。その後、図示は省略しているが、第3の層間絶縁膜424の上に、さらに上層の層間絶縁膜、配線又は表面保護膜等を形成することによって、強誘電体メモリを完成させる。

## 【0233】

以上に説明したように、第4の実施形態によると、メモリセルトランジスタ、及び第2の高濃度不純物拡散層411を含む制御トランジスタが形成された半導体基板400上に第1の層間絶縁膜412を形成した後、第1の層間絶縁膜412に、メモリセルトランジスタと接続する第1のプラグ413と、第2の高濃度不純物拡散層411と接続する第2のプラグ414とを形成する。その後、第1の層間絶縁膜412の上に第1のプラグ413と接続する容量下部電極415を形成した後、容量下部電極415の上に、強誘電体膜よりなる容量絶縁膜418、及び容量上部電極419を順次形成し、その後、容量上部電極419の上に、容量上部電極419の外側まで延び且つ第2のプラグ414と電気的に接続する導電性水素バリア膜420を形成する。その後、導電性水素バリア膜420を含む第1の層間絶縁膜412の上に第2の層間絶縁膜421を形成した後、第1の層間絶縁膜412及び第2の層間絶縁膜421に、第2の高濃度不純物拡散層411と第2の層間絶縁膜421上の配線423とを接続する第3のプラグ422を形成する。このため、容量上部電極419の形成前に、具体的には、メモリセルトランジスタと容量下部電極415とを接続する第1のプラグ413の形成と同時に、導電性水素バリア膜420と第2の高濃度不純物拡散層411とを接続する第2のプラグ414を第1の層間絶縁膜412に形成できる。これにより、導電性水素バリア膜420、第2のプラグ414、第2の高濃度不純物拡散層411及び第3のプラグ422を介して容量上部電極419と配線423とを電気的に接続することができる。すなわち、予め容量素子よりも下側に形成されている第2のプラグ414及び第2の高濃度不純物拡散層411を用いて、容量上部電極419と配線423とを電気的に接続することができる。従って、容量上部電極419の形成後に、容量上部電極419と配線423とを直接接続するプラグを形成するためのコンタクトホールを形成する必要がないので、容量上部電極419が露出して水素雰囲気又は還元性雰囲気にさらされる事態を回避できる。その結果、容量上部電極419として強い触媒作用を有するPt膜を用いる場合にも、容量絶縁膜418を構成する強誘電体膜の特性の劣化を防止して、強誘電体メモリの信頼性を向上させることができる。

## 【0234】

また、第4の実施形態によると、容量下部電極415、容量絶縁膜418及び容量上部電極419より構成される容量素子の全体を導電性水素バリア膜420によって常に覆っているため、容量素子の耐還元性を向上させることができる。

## 【0235】

また、第4の実施形態によると、酸素バリア性を有する容量下部電極415が第1のプ

10

20

30

40

50

ラグ 413 の上面を覆っていると共に、酸素バリア性を有する接続パッド 416 が第 2 のプラグ 414 の上面を覆っている。このため、容量絶縁膜 418 を構成する強誘電体膜を酸素雰囲気中で焼結するときに、第 1 のプラグ 413 及び第 2 のプラグ 414 が酸化されることを防止できる。

#### 【0236】

また、第 4 の実施形態によると、容量下部電極 415 の材料として用いられ且つ酸素バリア性を有する導電性膜を第 2 のプラグ 414 の上面全体を覆うようにパターン化することによって、容量下部電極 415 の形成と同時に接続パッド 416 を形成するため、工程の増加を招くことなく第 2 のプラグ 414 の酸化を防止できる。また、導電性水素バリア膜 420 を接続パッド 416 と接続するように形成するため、導電性水素バリア膜 420 と第 2 のプラグ 414 とを接続パッド 416 を介して接続できる。10

#### 【0237】

また、第 4 の実施形態によると、容量下部電極 415 同士の間の領域又は容量下部電極 415 と接続パッド 416との間の領域に、絶縁膜 417 を、その上面と容量下部電極 415 及び接続パッド 416 のそれぞれの上面とが面一になるように埋め込む。このため、容量絶縁膜 418 等の堆積工程を平坦な下地上で行なえるので、容量素子の信頼性つまり強誘電体メモリの信頼性を向上させることができる。

#### 【0238】

また、第 4 の実施形態によると、第 2 の高濃度不純物拡散層 411 の表面部をシリサイド化してシリサイド層を形成しておき、該シリサイド層を、第 2 のプラグ 414 と第 3 のプラグ 422 とを接続する導電層として用いた場合、次のような効果が得られる。すなわち、第 2 のプラグ 414 と第 3 のプラグ 422 とを接続する導電層として、半導体基板 400 上に形成されたポリシリコン層等を用いる場合と比べて、該導電層を低抵抗化できる。20

#### 【0239】

尚、第 4 の実施形態において、第 1 のプラグ 413、第 2 のプラグ 414、又は第 3 のプラグ 422 等の材料として、タンゲステンを用いたが、これに代えて、ポリシリコン等を用いてもよい。

#### 【0240】

また、第 4 の実施形態において、容量下部電極 415 としては、酸素含有率の少ない TiON 膜若しくは TiN 膜、又は Ti を含む合金膜等を下層膜（密着層として機能する）とし、且つ耐酸化性の強い Pt 膜若しくは Pt を含む合金膜、酸化物が酸素バリア性及び導電性を有する Ru 膜若しくは Ir 膜、又は RuO<sub>2</sub> 膜若しくは IrO<sub>2</sub> 膜等を上層膜とする積層膜を用いることが好ましい。30

#### 【0241】

また、第 4 の実施形態において、容量下部電極 415 同士の間に埋め込まれる絶縁膜 417 としては、SiO<sub>2</sub> 膜、Si<sub>3</sub>N<sub>4</sub> 膜、又は SiON 膜等を用いることが好ましい。

#### 【0242】

また、第 4 の実施形態において、容量絶縁膜 418 を構成する強誘電体膜の材料としては、PZT 系の材料又は SBT 系の材料等を用いることが好ましい。40

#### 【0243】

また、第 4 の実施形態において、容量上部電極 419 としては、耐酸化性の強い Pt 膜若しくは Pt を含む合金膜、酸化物が酸素バリア性及び導電性を有する Ru 膜若しくは Ir 膜、又は RuO<sub>2</sub> 膜若しくは IrO<sub>2</sub> 膜等を少なくとも一部分に用いることが好ましい。このようにすると、容量絶縁膜 418 を構成する強誘電体膜の結晶を十分に成長させることができることができる。

#### 【0244】

また、第 4 の実施形態において、導電性水素バリア膜 420 としては、Ti 膜、Ta 膜、TiON 膜、TiN 膜、TaN 膜、TiAlN 膜、TiAlON 膜、又は、Ti、Ta、TiON、TiN、TaN、TiAlN 若しくは TiAlON を含む合金膜を用いるこ50

とが好ましい。このようにすると、T<sub>i</sub>やT<sub>a</sub>の水素を吸収する性質を利用して、容量上部電極419まで水素が拡散することを防止し、それによって容量素子の耐還元性を確実に向上させることができる。また、導電性水素バリア膜420の導電性が確実に保たれるので、導電性水素バリア膜420を介して容量上部電極419と第2のプラグ414とを電気的に確実に接続することができる。

#### 【0245】

また、第4の実施形態において、半導体基板400上における非メモリセル領域に、第2のゲート電極408等により構成される制御トランジスタ（容量上部電極419つまりメモリセルプレートをON/OFFするドライバーとしての機能を有している）を形成した。すなわち、第4の実施形態においては、制御トランジスタがONになっている場合のみ、容量上部電極419と配線423とは、導電性水素バリア膜420、第2のプラグ414、第2の高濃度不純物拡散層411（つまり制御トランジスタのソース領域又はドレンイン領域）及び第3のプラグ422を介して電気的に接続される。それに対して、回路構成上、制御トランジスタを必要としない強誘電体メモリにおいては、例えば図30に示すように、半導体基板400上における非メモリセル領域に第2の高濃度不純物拡散層411のみを形成してもよい。この場合、容量上部電極419と配線423とは、導電性水素バリア膜420、第2のプラグ414、第2の高濃度不純物拡散層411及び第3のプラグ422を介して常に電気的に接続される。また、この場合、第2の高濃度不純物拡散層411の表面部をシリサイド化してもよい。

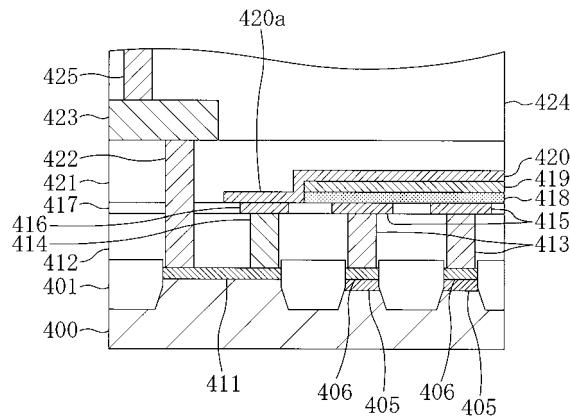

#### 【0246】

また、第4の実施形態において、第2のプラグ414と第3のプラグ422とを接続する導電層として第2の高濃度不純物拡散層411を用いたが、これに代えて、例えば図31に示すように、第1の層間絶縁膜412の下層膜412aと上層膜412bとの間に形成された導電層430を用いてもよい。図31に示す構造の形成方法（詳しくは第1の実施形態の第2変形例を参照）のうち、本実施形態の方法と大きく異なる点は次の通りである。すなわち、メモリセルトランジスタが形成された半導体基板400上に第1の層間絶縁膜412の下層膜412aを形成した後、非メモリセル領域の下層膜412aの上に導電層430を形成し、その後、第1の層間絶縁膜412の上層膜412bを形成する。その後、第1の層間絶縁膜412に、メモリセルトランジスタと接続する第1のプラグ413、及び導電層430と接続する第2のプラグ414を形成する。ここで、導電層430の材料は特に限定されるものではないが、導電層430が容量上部電極419の引き出し配線に使用されることを考慮して、導電層430の材料として低抵抗材料、例えばポリシリコン若しくはそれをシリサイド化したもの又はタンゲステン等を用いることが好ましい。また、導電層430として、強誘電体キャパシタ（容量下部電極415、容量絶縁膜418及び容量上部電極419により構成される容量素子）よりも下側の配線層、例えばビット線に使用される配線層を利用してもよい。或いは、導電層430として、例えば図32に示すように、半導体基板400上に層間絶縁膜を介さずに形成された配線層、例えばメモリセルトランジスタ又は制御トランジスタのゲート電極と同時に形成された配線層を用いてもよい。このとき、該配線層は、素子分離領域401の上に形成されていてもよいし、半導体基板400における素子分離領域401が形成されていない領域の上に形成されていてもよい。

#### 【0247】

また、第4の実施形態において、第2のプラグ414の上面を酸素バリア性を有する接続パッド416により覆ったが、これに代えて、例えば第2のプラグ414が酸素バリア性を有する材料による場合には、接続パッド416を形成しなくてもよい。このようにすると、強誘電体メモリの集積度を向上させることができる。また、このとき、導電性水素バリア膜420の張り出し部420aは、第2のプラグ414の上面の少なくとも一部分を覆うことが好ましい。

#### 【0248】

また、第4の実施形態において、容量下部電極415同士の間の領域又は容量下部電極

10

20

30

40

50

415と接続パッド416との間の領域に、絶縁膜417を埋め込んだが、これに代えて、絶縁膜417を形成しなくてもよい。

#### 【0249】

また、第4の実施形態において、容量絶縁膜418となる強誘電体膜及び容量上部電極419となる導電性膜を同一のマスクパターンを用いてパターン化したが、これに代えて、該導電性膜及び強誘電体膜を互いに異なるマスクパターンを用いてパターン化してもよい。

#### 【0250】

また、第4の実施形態において、導電性水素バリア膜420を形成する前に、容量上部電極419及び容量絶縁膜418のそれぞれの側面にサイドウォールを形成しておくことが好ましい。このようにすると、導電性水素バリア膜420となる導電性膜の段差被覆性が向上して、導電性水素バリア膜420の張り出し部420aに断線が生じる事態を防止できるので、強誘電体メモリの信頼性を向上させることができる。10

#### 【0251】

また、第4の実施形態において、第2の層間絶縁膜421の上に第3のプラグ422と接続するように配線423を形成したが、これに代えて、第2の層間絶縁膜421に第3のプラグ422と接続するように配線423を埋め込んでもよい。

#### 【0252】

##### (第4の実施形態の変形例)

以下、本発明の第4の実施形態の変形例に係る強誘電体メモリ及びその製造方法について図面を参照しながら説明する。20

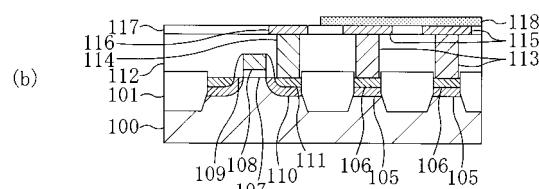

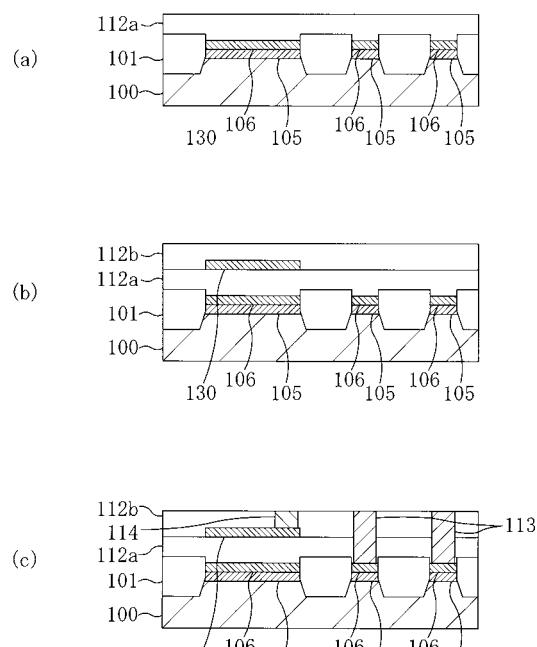

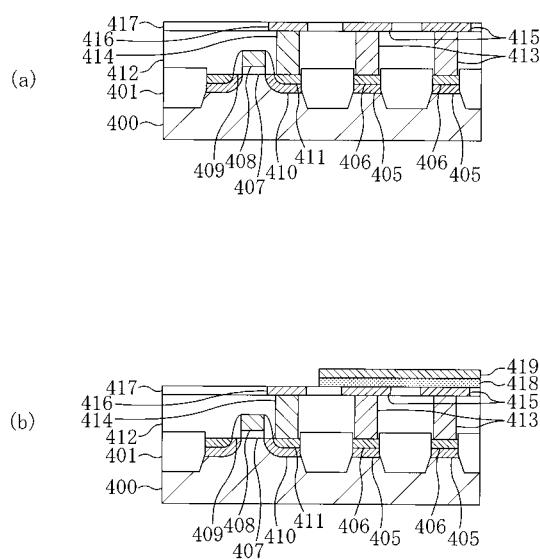

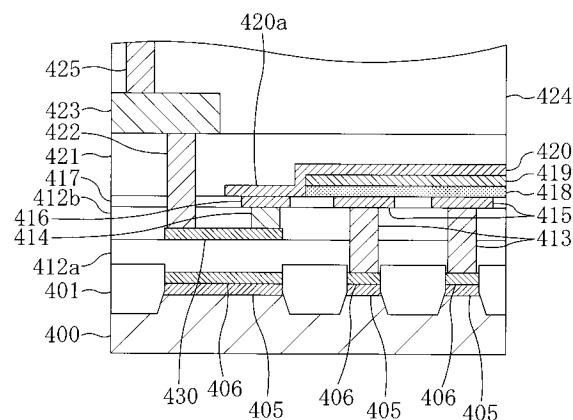

#### 【0253】

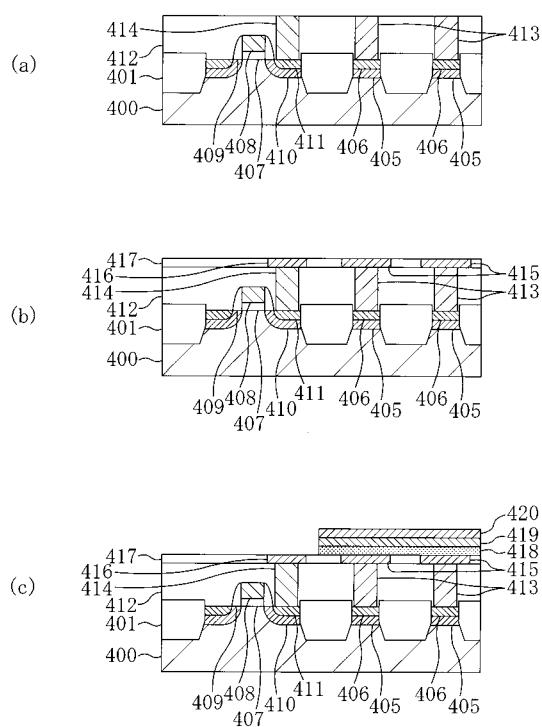

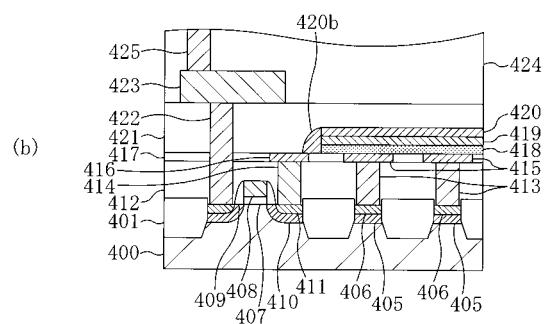

図33(a)～(c)、図34(a)、(b)及び図35(a)、(b)は、第4の実施形態の変形例に係る強誘電体メモリの製造方法の各工程を示す断面図である。

#### 【0254】

まず、図33(a)に示すように、半導体基板400の表面に、STI構造を有する素子分離領域401を形成する。その後、半導体基板400における素子分離領域401により囲まれた領域のうち各メモリセル領域の表面部に、下層となる第1の低濃度不純物拡散層405及び上層となる第1の高濃度不純物拡散層406を形成する。第1の低濃度不純物拡散層405及び第1の高濃度不純物拡散層406は、メモリセルトランジスタ(ゲート電極等の図示省略)のソース領域又はドレイン領域となる。30

#### 【0255】

また、図33(a)に示すように、半導体基板400における非メモリセル領域の上に、第2のゲート絶縁膜407を介して、制御トランジスタを構成する第2のゲート電極408を形成する。その後、第2のゲート電極408の側面に絶縁性の第2のサイドウォール409を形成すると共に、半導体基板400における非メモリセル領域の表面部に、下層となる第2の低濃度不純物拡散層410及び上層となる第2の高濃度不純物拡散層411を形成する。第2の低濃度不純物拡散層410及び第2の高濃度不純物拡散層411は、制御トランジスタのソース領域又はドレイン領域となる。

#### 【0256】

尚、第4の実施形態の変形例において、メモリセルトランジスタ及び制御トランジスタのそれぞれを構成するゲート電極等の各要素を要素毎に同時に形成してもよい。

#### 【0257】

次に、図33(a)に示すように、メモリセルトランジスタ及び制御トランジスタが形成されている半導体基板400上に第1の層間絶縁膜412を形成する。その後、第1の層間絶縁膜412に、第1の高濃度不純物拡散層406(ソース領域となる部分)と接続し且つタングステンよりなる第1のプラグ413、及び、第2の高濃度不純物拡散層411(ソース領域となる部分及びドレイン領域となる部分のうちのいずれか一方)と接続し且つタングステンよりなる第2のプラグ414を形成する。

#### 【0258】

50

20

30

40

50

次に、第1の層間絶縁膜412の上に全面に亘って、酸素バリア性を有する導電性膜（例えばIr膜又はIrO<sub>2</sub>膜等）を全面に成膜した後、該導電性膜をパターン化することによって、図33(b)に示すように、酸素バリア性を有する導電性膜よりなり且つ第1のプラグ413の上面を覆う容量下部電極415、及び酸素バリア性を有する導電性膜よりなり且つ第2のプラグ414の上面を覆う接続パッド416を形成する。これにより、メモリセルトランジスタと容量下部電極415とが第1のプラグ413を介して接続される。その後、容量下部電極415同士の間の領域又は容量下部電極415と接続パッド416との間の領域に、絶縁膜417を、その上面と容量下部電極415及び接続パッド416のそれぞれの上面とが面一になるように埋め込む。

## 【0259】

10

次に、絶縁膜417が形成された第1の層間絶縁膜412の上に全面に亘って、PZT系又はSBT系の材料よりなる強誘電体膜、Pt又はPtを含む合金よりなる第1の導電性膜、及び水素バリア性を有する第2の導電性膜（例えばTi膜若しくはTa膜又はTi若しくはTaを含む合金膜）を順次成膜した後、該第2の導電性膜、第1の導電性膜及び強誘電体膜を同一のマスクパターン（図示省略）を用いてパターン化する。これにより、図33(c)に示すように、容量下部電極415の上面を覆う容量絶縁膜418、容量絶縁膜418の上面を覆う容量上部電極419、及び容量上部電極419の上面を覆う導電性水素バリア膜420を形成する。尚、容量下部電極415、容量絶縁膜418及び容量上部電極419により容量素子が構成されている。

## 【0260】

20

次に、導電性水素バリア膜420が形成された第1の層間絶縁膜412の上に全面に亘って、導電性膜（図示省略）を堆積した後、該導電性膜に対してエッチバックを行なうことによって、図34(a)に示すように、導電性水素バリア膜420の側面に導電性の第3のサイドウォール420bを接続パッド416と接続するように形成する。これにより、導電性水素バリア膜420と第2のプラグ414とが第3のサイドウォール420b及び接続パッド416を介して接続される。

## 【0261】

30

次に、図34(b)に示すように、容量素子が形成された第1の層間絶縁膜412の上に第2の層間絶縁膜421を形成する。その後、第1の層間絶縁膜412、絶縁膜417及び第2の層間絶縁膜421に、タングステンよりなる第3のプラグ422を、第2の高濃度不純物拡散層411（ソース領域となる部分及びドレイン領域となる部分のうち第2のプラグ414が接続されていない方）と接続するように形成する。

## 【0262】

40

次に、図35(a)に示すように、第2の層間絶縁膜421の上に、アルミニウム等よりなる配線423を第3のプラグ422と接続するように形成する。これにより、配線423と第2の高濃度不純物拡散層411とが第3のプラグ422を介して接続される。その後、図35(b)に示すように、配線423を含む第2の層間絶縁膜421の上に第3の層間絶縁膜424を形成した後、第3の層間絶縁膜424に、タングステンよりなる第4のプラグ425を、配線423と接続するように形成する。その後、図示は省略しているが、第3の層間絶縁膜424の上に、さらに上層の層間絶縁膜、配線又は表面保護膜等を形成することによって、強誘電体メモリを完成させる。

## 【0263】

40

以上に説明したように、第4の実施形態の変形例によると、メモリセルトランジスタ、及び第2の高濃度不純物拡散層411を含む制御トランジスタが形成された半導体基板400上に第1の層間絶縁膜412を形成した後、第1の層間絶縁膜412に、メモリセルトランジスタと接続する第1のプラグ413、及び第2の高濃度不純物拡散層411と接続する第2のプラグ414を形成する。その後、第1の層間絶縁膜412の上に第1のプラグ413と接続する容量下部電極415を形成した後、容量絶縁膜418となる強誘電体膜、容量上部電極419となる第1の導電性膜、及び導電性水素バリア膜420となる第2の導電性膜を同一のマスクパターンを用いてパターン化する。これによって、容量下

50

部電極 415 の上面を覆う容量絶縁膜 418、容量絶縁膜 418 の上面を覆う容量上部電極 419、及び容量上部電極 419 の上面を覆う導電性水素バリア膜 420 を形成する。その後、導電性水素バリア膜 420 の側面に導電性の第 3 のサイドウォール 420b を第 2 のプラグ 414 と電気的に接続するように形成する。その後、導電性水素バリア膜 420 を含む第 1 の層間絶縁膜 412 の上に第 2 の層間絶縁膜 421 を形成した後、第 1 の層間絶縁膜 412 及び第 2 の層間絶縁膜 421 に、第 2 の高濃度不純物拡散層 411 と第 2 の層間絶縁膜 421 上の配線 423 とを接続する第 3 のプラグ 422 を形成する。このため、容量上部電極 419 の形成前に、具体的には、メモリセルトランジスタと容量下部電極 415 とを接続する第 1 のプラグ 413 の形成と同時に、第 3 のサイドウォール 420b を介して導電性水素バリア膜 420 と第 2 の高濃度不純物拡散層 411 とを接続する第 2 のプラグ 414 を第 1 の層間絶縁膜 412 に形成できる。これにより、導電性水素バリア膜 420、第 2 のプラグ 414、第 2 の高濃度不純物拡散層 411 及び第 3 のプラグ 422 を介して容量上部電極 419 と配線 423 とを電気的に接続することができる。すなわち、予め容量素子よりも下側に形成されている第 2 のプラグ 414 及び第 2 の高濃度不純物拡散層 411 を用いて、容量上部電極 419 と配線 423 とを電気的に接続することができる。従って、容量上部電極 419 の形成後に、容量上部電極 419 と配線 423 とを直接接続するプラグを形成するためのコンタクトホールを形成する必要がないので、容量上部電極 419 が露出して水素雰囲気又は還元性雰囲気にさらされる事態を回避できる。その結果、容量上部電極 419 として強い触媒作用を有する Pt 膜を用いる場合にも、容量絶縁膜 418 を構成する強誘電体膜の特性の劣化を防止して、強誘電体メモリの信頼性を向上させることができる。10 20

#### 【 0264 】

また、第 4 の実施形態の変形例によると、容量下部電極 415、容量絶縁膜 418 及び容量上部電極 419 より構成される容量素子を導電性水素バリア膜 420 によって常に覆っているため、容量素子の耐還元性を向上させることができる。

#### 【 0265 】

また、第 4 の実施形態の変形例によると、酸素バリア性を有する容量下部電極 415 が第 1 のプラグ 413 の上面を覆っていると共に、酸素バリア性を有する接続パッド 416 が第 2 のプラグ 414 の上面を覆っている。このため、容量絶縁膜 418 を構成する強誘電体膜を酸素雰囲気中で焼結するときに、第 1 のプラグ 413 及び第 2 のプラグ 414 が酸化されることを防止できる。30

#### 【 0266 】

また、第 4 の実施形態の変形例によると、容量下部電極 415 の材料として用いられ且つ酸素バリア性を有する導電性膜を第 2 のプラグ 414 の上面全体を覆うようにパターン化することによって、容量下部電極 415 の形成と同時に接続パッド 416 を形成するため、工程の増加を招くことなく第 2 のプラグ 414 の酸化を防止できる。また、導電性水素バリア膜 420 の側面に導電性の第 3 のサイドウォール 420b を接続パッド 416 と接続するように形成するため、導電性水素バリア膜 420 と第 2 のプラグ 414 とを第 3 のサイドウォール 420b 及び接続パッド 416 を介して接続できる。

#### 【 0267 】

また、第 4 の実施形態の変形例によると、容量絶縁膜 418 となる絶縁性膜及び容量上部電極 419 となる第 1 の導電性膜をパターン化するために用いられたマスクパターンを用いて、導電性水素バリア膜 420 となる第 2 の導電性膜をパターン化するため、製造工程で用いられるマスクパターンの数を低減できる。40

#### 【 0268 】

また、第 4 の実施形態の変形例によると、容量下部電極 415 同士の間の領域又は容量下部電極 415 と接続パッド 416との間の領域に、絶縁膜 417 を、その上面と容量下部電極 415 及び接続パッド 416 のそれぞれの上面とが面一になるように埋め込む。このため、容量絶縁膜 418 等の堆積工程を平坦な下地上で行なえるので、容量素子の信頼性つまり強誘電体メモリの信頼性を向上させることができる。50

## 【0269】

また、第4の実施形態の変形例によると、第2の高濃度不純物拡散層411の表面部をシリサイド化してシリサイド層を形成しておき、該シリサイド層を、第2のプラグ414と第3のプラグ422とを接続する導電層として用いた場合、次のような効果が得られる。すなわち、第2のプラグ414と第3のプラグ422とを接続する導電層として、半導体基板400上に形成されたポリシリコン層等を用いる場合と比べて、該導電層を低抵抗化できる。

## 【0270】

尚、第4の実施形態の変形例において、第3のサイドウォール420bは水素バリア性を有することが好ましい。このようにすると、容量下部電極415、容量絶縁膜418及び容量上部電極419より構成される容量素子の全体を水素バリア膜によって確実に覆うことができるので、容量素子の耐還元性を向上させることができる。また、第3のサイドウォール420bの材料として、導電性水素バリア膜420と同一の材料を用いる場合には、導電性水素バリア膜420となる第2の導電性膜を厚く堆積することが好ましい。

## 【0271】

また、第4の実施形態の変形例において、第1のプラグ413、第2のプラグ414、又は第3のプラグ422等の材料として、タンゲステンを用いたが、これに代えて、ポリシリコン等を用いてもよい。

## 【0272】

また、第4の実施形態の変形例において、容量下部電極415としては、酸素含有率の少ないTiON膜若しくはTiN膜、又はTiを含む合金膜等を下層膜（密着層として機能する）とし、且つ耐酸化性の強いPt膜若しくはPtを含む合金膜、酸化物が酸素バリア性及び導電性を有するRu膜若しくはIr膜、又はRuO<sub>2</sub>膜若しくはIrO<sub>2</sub>膜等を上層膜とする積層膜を用いることが好ましい。

## 【0273】

また、第4の実施形態の変形例において、容量下部電極415同士の間に埋め込まれる絶縁膜417としては、SiO<sub>2</sub>膜、Si<sub>3</sub>N<sub>4</sub>膜、又はSiON膜等を用いることが好ましい。

## 【0274】

また、第4の実施形態の変形例において、容量絶縁膜418を構成する強誘電体膜の材料としては、PZT系の材料又はSBT系の材料等を用いることが好ましい。

## 【0275】

また、第4の実施形態の変形例において、容量上部電極419としては、耐酸化性の強いPt膜若しくはPtを含む合金膜、酸化物が酸素バリア性及び導電性を有するRu膜若しくはIr膜、又はRuO<sub>2</sub>膜若しくはIrO<sub>2</sub>膜等を少なくとも一部分に用いることが好ましい。このようにすると、容量絶縁膜418を構成する強誘電体膜の結晶を十分に成長させることができる。

## 【0276】

また、第4の実施形態の変形例において、導電性水素バリア膜420としては、Ti膜、Ta膜、TiON膜、TiN膜、TaN膜、TiAlN膜、TiAlON膜、又は、Ti、Ta、TiON、TiN、TaN、TiAlN若しくはTiAlONを含む合金膜を用いることが好ましい。このようにすると、TiやTaの水素を吸蔵する性質を利用して、容量上部電極419まで水素が拡散することを防止し、それによって容量素子の耐還元性を確実に向上させることができる。また、導電性水素バリア膜420の導電性が確実に保たれるので、導電性水素バリア膜420を介して容量上部電極419と第2のプラグ414とを電気的に確実に接続することができる。

## 【0277】

また、第4の実施形態の変形例において、半導体基板400上における非メモリセル領域に、第2のゲート電極408等により構成される制御トランジスタを形成したが、回路構成上、制御トランジスタを必要としない強誘電体メモリにおいては、半導体基板400

10

20

30

40

50

上における非メモリセル領域に第2の高濃度不純物拡散層411のみを形成してもよい。この場合、第2の高濃度不純物拡散層411の表面部をシリサイド化してもよい。

#### 【0278】

また、第4の実施形態の変形例において、第2のプラグ414の上面を酸素バリア性を有する接続パッド416により覆ったが、これに代えて、例えば第2のプラグ414が酸素バリア性を有する材料よりなる場合には、接続パッド416を形成しなくてもよい。このようにすると、強誘電体メモリの集積度を向上させることができる。また、このとき、第3のサイドウォール420bは、第2のプラグ414の上面の少なくとも一部分を覆うことが好ましい。

#### 【0279】

また、第4の実施形態の変形例において、容量下部電極415同士の間の領域又は容量下部電極415と接続パッド416との間の領域に、絶縁膜417を埋め込んだが、これに代えて、絶縁膜417を形成しなくてもよい。

#### 【0280】

また、第4の実施形態の変形例において、容量絶縁膜418となる強誘電体膜、容量上部電極419となる第1の導電性膜、及び導電性水素バリア膜420となる第2の導電性膜を同一のマスクパターンを用いてパターン化したが、これに代えて、各導電性膜及び強誘電体膜を互いに異なるマスクパターンを用いてパターン化してもよい。

#### 【0281】

また、第4の実施形態の変形例において、容量絶縁膜418を、容量下部電極415の上面を覆い且つ接続パッド416とは接触しないように形成したが、これに代えて、容量絶縁膜418を、その端部が接続パッド416の上に位置するように形成してもよい。このようにすると、容量絶縁膜418となる絶縁性膜に対して大きなエッチング選択比を有する導電性膜を接続パッド416の材料として用いると共に、該接続パッド416をエッチングストッパーとして前記の絶縁性膜をパターン化することによって、オーバーエッチングに起因する段差形成を防止しながら容量絶縁膜418を形成できる。

#### 【0282】

また、第4の実施形態の変形例において、第2の層間絶縁膜421の上に第3のプラグ422と接続するように配線423を形成したが、これに代えて、第2の層間絶縁膜421に第3のプラグ422と接続するように配線423を埋め込んでもよい。

#### 【産業上の利用可能性】

#### 【0283】

本発明は、強誘電体メモリ及びその製造方法に関し、特に、容量絶縁膜として強誘電体膜が用いられている容量素子を備えた強誘電体メモリに適用した場合、強誘電体膜の特性の劣化を防止して強誘電体メモリの信頼性を向上させることができ、非常に有用である。

#### 【図面の簡単な説明】

#### 【0284】

【図1】(a)は本発明の第1の実施形態に係る強誘電体メモリの製造方法の一工程を示す断面図であり、(b)は(a)におけるI-I線の断面図である。

【図2】(a)及び(b)は本発明の第1の実施形態に係る強誘電体メモリの製造方法の各工程を示す断面図である。

【図3】(a)～(c)は本発明の第1の実施形態に係る強誘電体メモリの製造方法の各工程を示す断面図である。

【図4】(a)は本発明の第1の実施形態に係る強誘電体メモリの製造方法の一工程を示す断面図であり、(b)は(a)におけるIV-IV線の断面図である。

#### 【図5】本発明の第1の実施形態に係る強誘電体メモリの断面図の一例である。

【図6】(a)～(c)は本発明の第1の実施形態の第1変形例に係る強誘電体メモリの製造方法の各工程を示す断面図である。

【図7】(a)及び(b)は本発明の第1の実施形態の第1変形例に係る強誘電体メモリの製造方法の各工程を示す断面図である。

10

20

30

40

50

【図 8】(a) 及び (b) は本発明の第 1 の実施形態の第 1 変形例に係る強誘電体メモリの製造方法の各工程を示す断面図である。

【図 9】(a) ~ (c) は本発明の第 1 の実施形態の第 2 変形例に係る強誘電体メモリの製造方法の各工程を示す断面図である。

【図 10】(a) ~ (c) は本発明の第 1 の実施形態の第 2 変形例に係る強誘電体メモリの製造方法の各工程を示す断面図である。

【図 11】(a) ~ (c) は本発明の第 1 の実施形態の第 2 変形例に係る強誘電体メモリの製造方法の各工程を示す断面図である。

【図 12】本発明の第 1 の実施形態の第 2 変形例に係る強誘電体メモリの断面図の一例である。

10

【図 13】(a) は本発明の第 2 の実施形態に係る強誘電体メモリの製造方法の一工程を示す断面図であり、(b) は(a)におけるXIII-XIII線の断面図である。

【図 14】(a) 及び (b) は本発明の第 2 の実施形態に係る強誘電体メモリの製造方法の各工程を示す断面図である。