(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5723363号

(P5723363)

(45) 発行日 平成27年5月27日(2015.5.27)

(24) 登録日 平成27年4月3日(2015.4.3)

(51) Int.Cl.

H05K 3/46 (2006.01)

F 1

|      |      |   |

|------|------|---|

| H05K | 3/46 | N |

| H05K | 3/46 | B |

| H05K | 3/46 | Z |

| H05K | 3/46 | Q |

請求項の数 23 (全 15 頁)

(21) 出願番号 特願2012-521917 (P2012-521917)

(86) (22) 出願日 平成22年7月28日 (2010.7.28)

(65) 公表番号 特表2013-501345 (P2013-501345A)

(43) 公表日 平成25年1月10日 (2013.1.10)

(86) 國際出願番号 PCT/CA2010/001174

(87) 國際公開番号 WO2011/011880

(87) 國際公開日 平成23年2月3日 (2011.2.3)

審査請求日 平成25年7月5日 (2013.7.5)

(31) 優先権主張番号 12/533,569

(32) 優先日 平成21年7月31日 (2009.7.31)

(33) 優先権主張国 米国(US)

(73) 特許権者 508301087

エーティーアイ・テクノロジーズ・ユーニューアルシー

ATI TECHNOLOGIES ULC

カナダ、オンタリオ エル3ティー 7

エックス6、マーカム、コマース バリー

ドライブ イースト 1

One Commerce Valley

Drive East, Markham, Ontario, L3T 7X6

Canada

(74) 代理人 100108833

弁理士 早川 裕司

最終頁に続く

(54) 【発明の名称】非対称なビルドアップ層を有する基板を製造する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

コアと、前記コアの第1の表面上のm層のビルドアップ層と、前記コアの第2の表面上のn層のビルドアップ層とを有する基板を製造する方法であつて、

前記ビルドアップ層の各々は、同一の材質からなる誘電体層とその上の導電性層とを備え、 $m > n$  であり、

前記方法は、前記第1の表面上に前記m層のビルドアップ層の( $m - n$ )層を形成することと、前記( $m - n$ )層のビルドアップ層の形成後に、さらにn対のビルドアップ層を形成することとを備え、

前記m層のビルドアップ層の前記( $m - n$ )層の各々を形成することは、それぞれの誘電体層を穴開けすると共に、デスマニア溶液を用いてデスマニアすることを備え、前記n対の各々は、前記第2の表面上に形成される前記n層のビルドアップ層の1つと、前記第1の表面上の前記( $m - n$ )層のビルドアップ層に形成される前記m層ビルドアップ層の残りのn層の1つとを備え、前記n対のビルドアップ層の各々を形成することは、誘電体層のそれぞれの対の各1つを穴開けすることと、前記デスマニア溶液を用いて誘電体層の前記それぞれの対を同時にデスマニアすることとを備える方法。

## 【請求項 2】

誘電体層のそれぞれの対の各1つを前記穴開けすることは、レーザ穴開けすることを備える請求項1の方法。

## 【請求項 3】

10

前記 m 層のビルドアップ層及び前記 n 層のビルドアップ層の任意の 1 つにおける任意の誘電体層は 1 回だけデスマニアされる請求項 1 の方法。

【請求項 4】

誘電体層の前記それぞれの対を前記デスマニアすることは、誘電体層のそれぞれの対の各 1 つを前記穴開けすることの後に誘電体層の前記それぞれの対から残渣を除去することを備える請求項 1 の方法。

【請求項 5】

前記 m 層のビルドアップ層の ( m - n ) 層を前記形成することの前に前記コアの前記第 1 及び第 2 の表面の少なくとも 1 つ上に複数の導電性トレースを形成することと、前記コアの前記第 1 及び第 2 の表面上の前記複数の導電性トレースを電気的に接続することとを更に備えた請求項 1 の方法。 10

【請求項 6】

前記電気的に接続することは、前記コア内に少なくとも 1 つの穴を穴開けすることと、前記穴を導電性材質でめっきしてめっきされたスルーホール ( PTH ) を形成することとを備える請求項 5 の方法。

【請求項 7】

前記コア内に前記少なくとも 1 つの穴を前記穴開けすることは、機械穴開けすることを備える請求項 6 の方法。

【請求項 8】

前記 n 層のビルドアップ層の各々は、40  $\mu$ m ~ 60  $\mu$ m の範囲内の高さを有する誘電体層を備え、前記 m 層のビルドアップ層の各々は、25  $\mu$ m より大きく 40  $\mu$ m より小さい 高さを有する誘電体層を備える請求項 1 の方法。 20

【請求項 9】

前記 m 層のビルドアップ層の最も外側の 1 つ上に第 1 の半田マスクを形成することを更に備えた請求項 1 の方法。

【請求項 10】

前記 n 層のビルドアップ層の最も外側の 1 つ上に第 2 の半田マスクを形成することを更に備えた請求項 9 の方法。

【請求項 11】

前記第 1 の半田マスクは 16  $\mu$ m ~ 30  $\mu$ m の排他的範囲内の高さを有し、前記第 2 の半田マスクは 30  $\mu$ m ~ 60  $\mu$ m の範囲内の高さを有する請求項 10 の方法。 30

【請求項 12】

前記基板を強化するために前記コアの前記第 2 の表面上の前記 n 層のビルドアップ層の少なくとも幾つかの内部にリングを形成することを更に備えた請求項 1 の方法。

【請求項 13】

前記リングは銅リングである請求項 12 の方法。

【請求項 14】

$m = 2$  且つ  $n = 1$  である請求項 1 の方法。

【請求項 15】

請求項 1 に従い製造される基板であって、コアと、前記コアの第 1 の表面上の m 層のビルドアップ層と、前記コアの第 2 の表面上の n 層のビルドアップ層とを有し、 $m > n$  であり、前記ビルドアップ層の各々は 1 回だけデスマニアされる誘電体層を備える基板。 40

【請求項 16】

m 層のビルドアップ層の最も外側の 1 つを覆う第 1 の半田マスクと、n 層のビルドアップ層の最も外側の 1 つを覆う第 2 の半田マスクとを更に備えた請求項 15 の基板。

【請求項 17】

前記 m 層のビルドアップ層の各々は 25  $\mu$ m より大きく 40  $\mu$ m より小さい 高さを有する誘電体層を有し、前記 n 層のビルドアップ層の各々は 40  $\mu$ m より大きく 60  $\mu$ m より小さい 高さを有する誘電体層を有する請求項 15 の基板。

【請求項 18】

10

20

30

40

50

前記コアは 15 ppm / より小さい熱膨張係数を有する請求項 15 の基板。

【請求項 19】

請求項 15 の基板と、前記 m 層のビルドアップ層の 1 つを備える前記導電性層の 1 つと相互接続されるダイとを備えた半導体デバイス。

【請求項 20】

前記 m 層のビルドアップ層の最も外側の 1 つ及び前記 n 層のビルドアップ層の最も外側の 1 つをそれぞれ覆う第 1 及び第 2 の半田マスクを更に備え、前記第 2 の半田マスクは前記第 1 の半田マスクの高さより高い高さを有する請求項 19 の半導体デバイス。

【請求項 21】

前記 m 層のビルドアップ層の最も外側の 1 つを覆う半田マスクと、前記 n 層のビルドアップ層の最も外側の 1 つを覆う誘電体材質の層とを更に備え、前記誘電体材質の層は前記半田マスクの高さより高い高さを有する請求項 19 の半導体デバイス。 10

【請求項 22】

前記第 1 の半田マスクは 16  $\mu$ m ~ 30  $\mu$ m の排他的範囲内の高さを有し、前記第 2 の半田マスクは 30  $\mu$ m ~ 60  $\mu$ m の範囲内の高さを有する請求項 19 の半導体デバイス。

【請求項 23】

前記デバイスにおける反りを軽減するために前記ビルドアップ層の少なくとも幾つかの内部に強化リングを更に備えた請求項 19 の半導体デバイス。

【発明の詳細な説明】

【技術分野】

20

【0001】

本発明は概して電子的なパッケージングに関し、より特定的にはそのようなパッケージングにおいて用いられる、同じでない数のビルドアップ層を対向面上に有する基板に関し、基板は、集積回路パッケージ、周辺拡張カード及びプリント配線板又はプリント回路板の一部を形成することができる。

【背景技術】

【0002】

基板は、集積回路パッケージ、周辺拡張カード、マザーボード、及び電子回路パッケージを形成するために用いられる他のプリント回路板において用いられる。基板上に形成される導電性トレース (conductive traces) が、基板に取り付けられる種々の電子部品を電気的に相互接続する。 30

【0003】

例えば集積回路パッケージは、通常、集積回路を含む半導体ダイを取り付けるために用いられるキャリア基板を含む。キャリア基板はまた、集積回路パッケージを周辺拡張カード又はプリント回路板のような外部回路に取り付けるために用いられる半田ボール又はピンを含むであろう。

【0004】

基板は通常コアを含み、コア上には、電気的な信号を経路付けるための 1 つ以上の経路付け層 (routing layers) が形成される。典型的には、導電性トレースの受動回路がコアの一方の面上又は両面上に最初に形成される。これらの導電性トレースは、多くの場合、薄膜金属又は銅箔を用いてエッチングされる。その後に、1 つ以上の追加的な経路付け層がコア上に形成される (いわゆる「ビルドアップ層」)。ビルドアップ層は典型的には誘電体層及び導電性層を含む。誘電体層は、典型的には、形成された経路付け層又はコアを覆うように誘電体材質を積層することによって形成される。導電性層は誘電体層上に形成される。ビルドアップ層内の誘電体材質は、誘電体層の下にある導電性トレースから導電性層を絶縁する。1 つのビルドアップ層の誘電体上の導電性層の一部を誘電体材質の下にあるトレースと相互接続するために、誘電体層内の適切な点に穴が形成されることがある。そのようなビルドアップ層が互いの上に形成されて多重化され得る。 40

【0005】

典型的には、コアの各面 (上面及び下面) 上には同じ数のビルドアップ層が形成される

50

。めっきされたスルーホール(plated through-holes) ( P T H ) と称される、コアを通つての導電性トンネル又は穿孔(perforations)が、上部ビルドアップ層上のトレースを基板コアの下部ビルドアップ層でのトレースと相互接続するためによく用いられる。

【 0 0 0 6 】

コアの各面上に同じ数のビルドアップ層を形成することは、必要とされるであろうよりも多いビルドアップ層の形成をもたらすことがあるので、しばしば非効率的になる。例えば、奇数のビルドアップ層(例えば3層)で十分である場合、コアの上部及び下部に同じ数のビルドアップ層を有すること(例えば各面上に2層)は、概して不要な第4の層を導入してしまう。これはパッケージの材質コスト及び製造コストを付加するので望ましくない。

10

【 0 0 0 7 】

ビルドアップ層の数を減少させるために知られている方法は、コアなし基板を用いることを含む。しかし、これは反りの危険性を高めるので、多くの場合に補強材の使用を必要とし、残念ながら製造コストを上昇させる。

【 0 0 0 8 】

一方の面上にのみビルドアップ層を形成させる片面基板もまた知られている。しかし、そのような基板もまた反りに敏感である。更に、片面基板においては、集積回路ダイのような電子部品は典型的には基板の同じ側(ビルドアップ層を含む側)に取り付けられるので、ダイを取り付けるのに利用可能な面積を制限する。

【 0 0 0 9 】

20

コアの各面に同じでない数のビルドアップ層を有する基板を製造することが知られているが、既知の方法は、多くの場合、ビルドアップ層の幾つかにおける誘電体層の過剰なデスマニア、及び反りのような望ましくない特性をもたらす。

【発明の概要】

【発明が解決しようとする課題】

【 0 0 1 0 】

従って、ビルドアップ層の使用を効率的にする一方で上述した欠点を回避することが集積回路パッケージに対して求められている。

【課題を解決するための手段】

【 0 0 1 1 】

30

非対称なビルドアップ層を伴う基板を製造する方法が開示される。基板は、コアと、コアの1つの表面上に形成されるのm層のビルドアップ層と、コアの反対側の表面上に形成されるn層( $m > n$ )のビルドアップ層とを有する。

【 0 0 1 2 】

本発明の1つの態様によると、コアと、コアの第1の表面上のm層のビルドアップ層と、コアの第2の表面上のn層のビルドアップ層とを有する基板を製造する方法が提供され、ここで $m > n$ である。ビルドアップ層の各々は、誘電体層とその上に形成される導電性層とを備える。方法は、第1の表面上にm層のビルドアップ層の( $m - n$ )層を形成することを含む。m層のビルドアップ層の( $m - n$ )層の各々を形成することは、それぞれの誘電体層を穴開けすると共にデスマニアすることを含む。方法はまたn対のビルドアップ層を形成することを含み、n対の各々は、第2の表面上に形成されるn層のビルドアップ層の1つと、第1の表面上に形成されるm層のビルドアップ層の残りのn層の1つとを有する。n対のビルドアップ層の各々を形成することは、誘電体層のそれぞれの対の各1つを穴開けすることと、誘電体層のそれぞれの対を同時にデスマニアすることとを含む。

40

【 0 0 1 3 】

本発明の他の態様及び特徴は、添付の図面と共に本発明の具体的な実施形態の以下の説明を精査する場合に当業者に明らかになる。

【図面の簡単な説明】

【 0 0 1 4 】

本発明の実施形態を例示的な目的のみで示す図面は以下の通りである。

50

## 【0015】

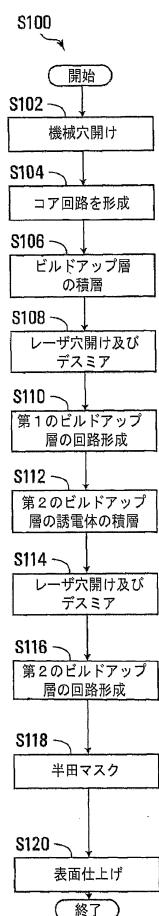

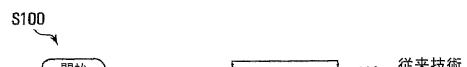

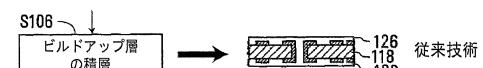

図1はコアの択一的な面上に同じでない数のビルドアップ層を有する従来の基板を製造するために用いられる従来の処理のフローチャートである。

## 【0016】

図2A～2Kは図1に示されるステップに対応する製造の異なる段階での従来の基板の縦断面図である。

## 【0017】

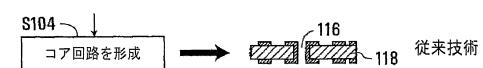

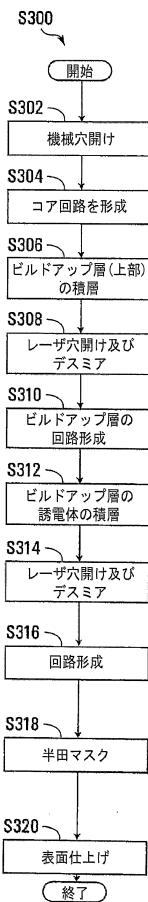

図3は例示的な基板を作製するために用いられる本発明の実施形態の例示的な処理のフローチャートである。

## 【0018】

図4A～4Kは図3に示される例示的なステップに対応する製造の異なる段階での例示的な基板の縦断面図である。

## 【0019】

図5は基板コアの各面上に同じでない数のビルドアップ層を有する例示的な半導体デバイスの縦断面図である。

## 【0020】

図6はそのコアの各面上の同じでない数のビルドアップ層及び銅リングを有する例示的な半導体デバイスの別の実施形態の縦断面図である。

## 【発明を実施するための形態】

## 【0021】

$k$ 層を有するコアと、コアの一方の面上の $m$ 層のビルドアップ層と、コアの他方の面上の $n$ 層のビルドアップ層とを含む基板は、 $m / k / n$ ビルドアップ設計を有すると一般的に言わることがあり、ここで $m$ 及び $n$ は正の整数である。そのような基板は、 $m = n$ である場合に、非対称ビルドアップ層を有していると言われることがある。

## 【0022】

従って $m / k / n$ ビルドアップ設計を有する非対称基板は、コアと、全部で $(m + n)$ 層のビルドアップ層とを含む。各ビルドアップ層は、典型的には、例えばアジノモトビルドアップフィルム(Ajinomoto build-up film)(ABF)のような誘電体層と、誘電体層上に形成される導電性トレースとを含む。

## 【0023】

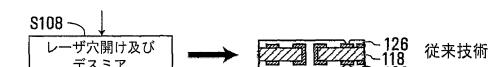

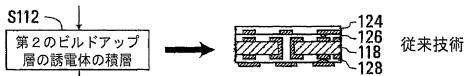

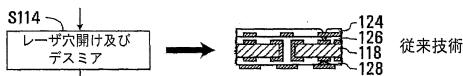

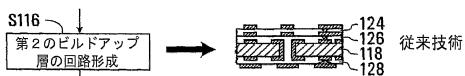

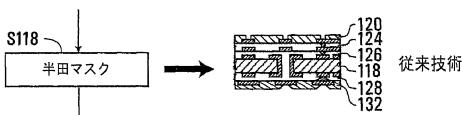

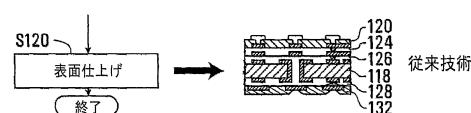

図1におけるフローチャートS100は、コアの対向面上に非対称な、即ち同じでない数のビルドアップ層を有する基板を提供するために基板製造供給元によってしばしば用いられる従来の製造処理を示している。図2A～2Kは、フローチャートS100における複数のステップに適合する種々の段階でのそのような基板の断面図を示している。

## 【0024】

図示されるように、それ自身の複数のサブ層を有していてよい基板コア118は、めっきされたスルーホール(PTH)を形成するためにステップS102において最初に機械穴開けされる。ステップS104では、導電性トレースが用いられて、コア118の択一的な面上に回路又は導電性層を形成する。基板コア118の対向面上の回路トレースを相互接続するために、めっきされたスルーホール116が用いられてよい。ステップS106では、誘電体材質(例えばABF)を用いて第1の上部ビルドアップ層126及び第1の下部ビルドアップ層128が積層される。ステップS108では、第1のビルドアップ誘電体層126, 128(上部及び下部)は、レーザ穴開けされ、そしてステップS104で形成されたコア回路のトレースを露出させるようにデスマニアされる(desmeared)。ステップS110では、導電性トレースが用いられて、第1の上部ビルドアップ層126上及び第1の下部ビルドアップ層128上の両方に導電性層を形成する。

## 【0025】

デスマニア(desmearing)は、一般的には、適切な電気的相互接続を確実にするための残渣の除去のことを言う。残渣は付着した(smeared)エポキシ樹脂の副生成物を含むことがあり、ABF少量又は誘電体少量が、穴開けされた穴(ビア、マイクロビア又はPTH)内

10

20

30

40

50

で露出しているトレース表面に付くことがある。例えば、穴開けの間に、エポキシ樹脂又はA B Fのような誘電体材質がしばしば溶融すると共に導電性トレースの表面にわたって付着してしまうことがある。穴開けされた穴（ピア又はスルーホール）の導電性材質を用いる次のめっきは、異なるビルドアップ層からのトレースを電気的に接続することを目的としている。従って、除去しない限り、残渣はトレース表面と穴開けされた穴の内壁の導電性めっきとの間に誘電体バリアを生成することがあり、しばしば欠陥回路がもたらされることになる。デスマニアは、典型的には、導電性トレースを化学的に洗浄すると共にそのような残渣を導電性トレースから除去するために、過マンガン酸ナトリウム又は過マンガン酸カリウムのような洗浄溶液の使用を伴う。

## 【0026】

10

ステップS112では、A B F層又は同等な誘電体材質を用いて第2のビルドアップ層124の誘電体層が形成される。しかし、付加的な（第2の）下部ビルドアップ層は必要とされていないので形成されない。ステップS114では、上部の第2のビルドアップ層124は、レーザ穴開けされ、そしてステップS110で形成された第1のビルドアップ層の導電性層のトレースを露出させるようにデスマニアされる。

## 【0027】

穴が穴開けされる場合、穴開けされた材質の残渣が形成される。例えばエポキシファイバグラス又は樹脂のような誘電体層が穴開けされる場合、誘電体材質の断片が形成されることがある。機械的な穴開けの間、穴開けされている材質に対するドリルビットの摩擦が、ドリルビットの温度を材質の融点よりも高く上昇させる。レーザ穴開けも同様に穴開けされている材質の融点よりも高く温度を上昇させる。このようにして溶融した穴開けされた材質の断片は、導電性トレースの一部を露出させる穴の内壁のような表面上にしばしば付着する。

20

## 【0028】

このように、残渣（ステップS114における穴開けによって残る）を除去するためにデスマニアが必要であり、残渣の一部は導電性トレース上に付着してしまっているであろう。デスマニアは、典型的には、予め定められた時間での過マンガン酸塩溶液のような洗浄溶液内への基板の種々の浸漬又はディッピングを伴う。デスマニアは当該分野において既知であり、そして例えば米国特許第4,425,380号及び米国特許第4,601,783号に記載されており、それらの内容は参照によってここに組み込まれる。またデスマニアは、基板を化学溶液内に浸漬した後の水洗い流しを伴うことがある。

30

## 【0029】

基板を化学溶液内に浸漬することは、露出されたビルドアップ層に影響を与える。従ってステップS114においては、第1の下部ビルドアップ層128もデスマニアされてしまう。特に、このデスマニアは、層128が既にステップS108でデスマニアされていることから、層128に行われる第2のデスマニアステップとなり、従って本来は不要であろう。

## 【0030】

ステップS116では、付加的な導電性トレースが用いられて、第2の上部ビルドアップ層124の導電性層及び下部ビルドアップ層128の導電性層を形成する。

## 【0031】

40

ステップS118では、ビルドアップ層124, 128上に形成された導電性層にそれぞれ半田マスク(solder masks)120及び132が塗布される。ステップS120では、導電性層の酸化に対する付加的な保護をもたらすと共に、半田ボールの搭載及び/又はダイの取り付けに対する表面を準備するために、表面仕上げが行われる。

## 【0032】

図2Kに示される結果としてもたらされた基板は、2/k/1ビルドアップ設計を有しており、ここでkはコア118におけるサブ層の数である。しかし、残念なことに図2Kの基板は、2回のデスマニアステップ（S108及びS114）の結果として、過剰にデスマニアされた下部ビルドアップ層128を含むであろう。

## 【0033】

50

過剰なデスマニアは、誘電体層を多重のデスマニアステップにさらすことに起因している。例えば図1においては、ビルドアップ層128の誘電体層はS100において2回デスマニアされる(先ずステップS108で、次いでステップS114で)。過剰なデスマニアはビルドアップ層内に多くの好ましくない変化をもたらす。例えば、誘電体層の接着特性に悪影響があるかもしれない。加えて、多重のデスマニアステップが適用される場合、誘電体層で穴を開けられた穴又はビアが拡大されることがある。更に、誘電体層の表面が結果として粗くなることがある。

【0034】

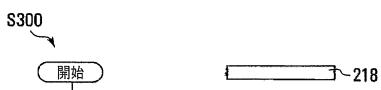

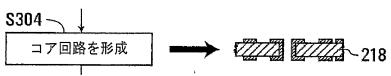

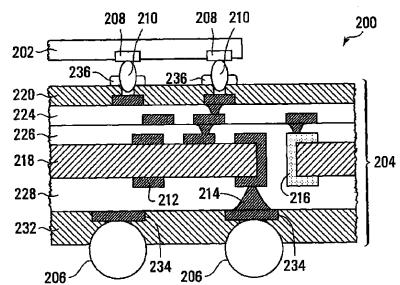

そこで、図3は本発明の実施形態を例示する製造処理を表すフローチャートS300を示しており、その製造処理は、コアの対向面上に異なる(同じでない)数のビルドアップ層を有する基板デバイスを提供するために用いられてよい。コアの第1の表面(例えば上部)はその上に形成されるm層のビルドアップ層を有していてよい一方、第2の表面(例えば下部)はその上に形成されるn層のビルドアップ層を有していてよい(ここではm > n)。図4A~4Kは、フローチャートS300に示される複数のステップに適合する種々の段階での、製造されている最中の基板の断面図を示している。

【0035】

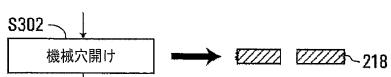

図3に示されるように、それ自身の複数のサブ層(サブ層は図示せず)を有していてよい基板コア(例えばコア218)が、ステップS302において最初に機械穴開けされる。

【0036】

ステップS304では、導電性トレースが用いられて、コア218の折一的な面上に導電性層又は回路を形成する。導電性層は、薄膜金属又は銅箔を用いているコア上の導電性トレースをエッチングすることによって形成されてよい。基板コア218の対向面上のコア回路トレースを相互接続するするために、めっきされたスルーホール(PTH)216が形成されると共に用いられてよい。PTHは、ステップS302で形成された穴の内壁を銅のような導電性材質でめっきすることによって形成される。

【0037】

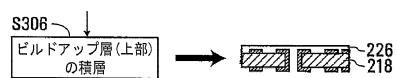

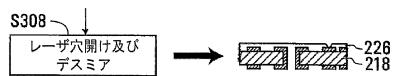

ステップS306では、ABFのような誘電体材質を積層することによって、第1の上部ビルドアップ層226の誘電体層が形成される。しかし、このステップでは、下部ビルドアップ層は形成されない。その代わりに上部ビルドアップ層のみが形成される。尚、この点が、第1の上部ビルドアップ層及び第1の下部ビルドアップ層の両方がこの段階で形成されるであろうフローチャートS100に示される従来の処理と対照的である。

【0038】

ステップS308では、第1のビルドアップ層226は、レーザ穴開けされ、そしてステップS304でコア218の上面上に形成された回路トレースを露出させるようにデスマニアされる。コア218の下面上の回路は、そこには下部の積層がないので露出されたままである。

【0039】

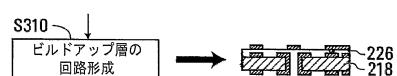

ステップS310では、導電性トレースが用いられて、ビルドアップ層226上に導電性層又は回路を形成する。特に基板の下部にはコア218の下部表面上に形成された回路がある。

【0040】

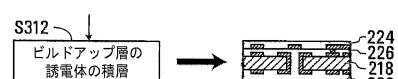

明らかにあるであろうように、概して、m層の上部ビルドアップ層及びn層の下部ビルドアップ層(ここではm > n)に対しては、上部のm層のビルドアップ層の(m-n)層を形成するために、誘電体層を形成し、誘電体層を穴開けすると共にデスマニアし、次いでデスマニアされた誘電体上に導電性層を形成するようにステップS306, S308, S310が連続的に実行されてよい。

【0041】

ステップS312では、ABFのような誘電体材質の層を用いて、第2の上部ビルドアップ層224及び第1の下部ビルドアップ層228が形成される。後で説明されるように

10

20

30

40

50

、反りを軽減するために、層 228 は層 224 よりも実質的に厚くてよい。

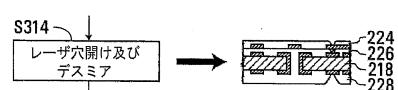

【0042】

ステップ 314 では、第 2 の上部ビルドアップ層 224 及び第 1 の下部ビルドアップ層 228 の誘電体層は、レーザ穴開けされると共に次いでデスマニアされてよい。穴開けされたビアは、上部ビルドアップ層 226 上の導電性層の回路トレース（ステップ S310 で形成されている）の一部を露出させ、また基板 218 の下部に形成されている回路トレース（ステップ S304 で形成されている）の一部を露出させる。

【0043】

ステップ S316 では、付加的な導電性トレースが用いられて、第 2 の上部ビルドアップ層 224 及び第 1 の下部ビルドアップ層 228 の両方の導電性層を形成する。10 穴開けされたビアは、新たに形成された導電性層のトレースをステップ S310 で形成されている既存の導電性層と相互接続するために、導電性材質で充填されてよい。

【0044】

概して、m 層の上部ビルドアップ層及び n 層の下部ビルドアップ層（ここでは  $m > n$ ）に対しては、n 対のビルドアップ層を形成するためにステップ S312、S314 及び S316 が用いられてよく、各対は、コアの第 2 の（下部の）表面上に形成されるべき n 層のビルドアップ層の 1 つと、第 1 の（上部の）表面上に形成される m 層の残りの n 層の 1 つとを有している。各ビルドアップ層は、誘電体層とその上に形成される導電性層とを含む。ビルドアップ層の n 対の各々を形成することは、誘電体層のそれぞれの対の各 1 つを穴開けすることと、誘電体層の当該対を同時にデスマニアすることとを伴う（S314）。20 次いで、デスマニアされた誘電体層上に導電性層が形成されてよい（S316）。理解されるであろうように、m 層のうちの（m - n）層は、ステップ S306、S308、S310 を用いて既に形成されている。

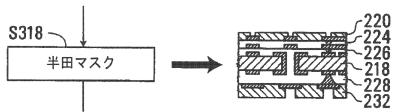

【0045】

ステップ S318 では、ビルドアップ層 224、228 上に形成された回路にそれぞれ半田マスクが塗布される。半田マスクは、言うまでもなく最も外側のビルドアップ層 224、228 上に塗布される。後で論じられるように、より少ないビルド層を有している側（例えば下側）に塗布される半田マスク 232 は、コア 218 の反対側（上側）の半田マスク 220 よりも実質的に厚くてよい。

【0046】

ステップ S320 では、半田ボールの搭載及び / 又はダイの取り付けに対する表面を準備するために、表面仕上げが行われる。30

【0047】

S300 に示される例示的な処理においては、好都合なことに、1 つのデスマニアステップのみが誘電体材質（例えば A B F）の各層に適用される。従って、図 4 K における基板は、2 つ以上のデスマニアステップを受けることに典型的には起因する過剰にデスマニアされたいかなるビルドアップ層を有することもないであろう。

【0048】

S300 に示される方法は、本発明の実施形態の例である基板を製造する一般化された方法を代表することが容易に認識されるであろう。従って、コア（例えばコア 218）と、コアの第 1 の表面（例えば上面）上の m 層のビルドアップ層（例えば 2 つのビルドアップ層 226、224）と、コアの第 2 の表面（例えば下面）上の n 層のビルドアップ層（例えば 1 つのビルドアップ層 228）とを有する基板を製造する一般的な方法（ここで  $m > n$ ）は、第 1 の表面上に m 層のビルドアップ層の（m - n）層を形成することと、n 対のビルドアップ層を形成することとを含み、m 層のビルドアップ層の（m - n）層の各々を形成することは、それぞれの誘電体層を穴開けすると共にデスマニアすることと含み、n 対の各々は、第 2 の表面上に形成される n 層のビルドアップ層の 1 つと、第 1 の表面上に形成される m 層のビルドアップ層の残りの n 層の 1 つとを含む。ビルドアップ層の n 対の各々を形成することは、誘電体層のそれぞれの対の各 1 つを穴開けすることと、誘電体層のそれぞれの対を同時にデスマニアすることとを含む。各ビルドアップ層は、連続的に、誘4050

電体層を形成し、誘電体を穴開けと共にデスマニアし、そしてデスマニアされた誘電体上に導電性層を形成することによって形成されてよい。誘電体層が穴開けされると共にデスマニアされた後に、薄膜金属又は銅箔のような導電性材質をエッティングし又は堆積させることによって、導電性トレースが形成されてよい。図4 A ~ 4 Kは、 $m = 2$ 、 $n = 1$ 、 $(m - n) = 1$ に対する特定の例を示しており、その結果、 $(m - n)$ 層はビルドアップ層226によって表され、そして $n$ 対のビルドアップ層はビルドアップ層224, 228の対を含む。

#### 【0049】

代替的な実施形態では、約 $100\mu m$ より小さい厚み又は高さを有するコア層を穴開けするために、レーザ穴開け及び機械穴開けが交換可能に用いられてよい。より厚いコア(例えば $400\mu m$ 又は $800\mu m$ )は典型的には機械穴開けを用いる。言うまでもなく、誘電体材質又は絶縁体内に穴又はキャビティを形成するための他の既知の方法が用いられてもよい。

#### 【0050】

また、全てのステップは必要でなくてよく、あるいは追加のステップが加えられてよい。例えば、図示されるものに加えて多くの更なるビルドアップ層が形成されてよい。後で更に詳細にされるように、基板を補強し且つ反りを軽減するために、銅リングが埋め込まれてもよい。

#### 【0051】

今や明らかなはずであるように、フローチャートS100に示されるような従来の製造方法は、過剰にデスマニアされたビルドアップ層をもたらし得る。上述したように、過剰なデスマニアは、誘電体層の接着特性に望ましくない変化を引き起こす。更に、特定のビルドアップ層に適用される多重デスマニア動作の結果としての過剰なデスマニアに起因して、レーザ穴開けされたビアは大きくなることがあり、また誘電体表面は粗くなることがある。これらの不利益は、フローチャートS300に示される例示的な製造処理の使用によって都合よく回避される。

#### 【0052】

コアレス基板及び片面基板もまた、反りの影響を大きく受け易い。反りの原因になりまた回路を動作不可能にする可能性のある機械的及び熱的なストレスにコアレス基板又は片面基板が耐え得ることを確実にするために、補強材がしばしば必要になる。

#### 【0053】

本発明の例示的な実施形態は、反りを軽減するために、より少ないビルドアップ層を含むコアの側に、より厚いビルドアップ誘電体層及びより厚い半田マスク層を含んでいてよい。このように、ステップS312においては、下部ビルドアップ層228は、ビルドアップ層224, 226において用いられる誘電体層よりも厚い誘電体層を用いてよい。1つの例示的な実施形態では、ビルドアップ層228は約 $40\mu m$  ~  $60\mu m$ であってよく、一方ビルドアップ層224, 226は各々約 $25\mu m$  ~  $40\mu m$ である。

#### 【0054】

同様に、ステップS318においては、下部半田マスク232は、その対応する上部半田マスク220よりも実質的に厚く作製されてよい。回路パッケージのサイズに応じて種々の相対的な厚み値が用いられてよい。1つの例示的な実施形態では、半田マスク232は $30\mu m$  ~  $60\mu m$ であってよい一方で、半田マスク220は $16\mu m$  ~  $30\mu m$ の高さにすぎないであろう。

#### 【0055】

半田マスク232は、誘電体材質の層によって置換されてよい。加えて、後で説明されるように、例えば銅で作製される複数のリングが、本発明の例示である半導体デバイスを補強するために用いられてよい。

#### 【0056】

それに沿って、図5は両面にビルドアップ層を有する基板204を含む例示的な集積回路パッケージ200の部分的な縦断面図を示している。集積回路パッケージ200は、基

10

20

30

40

50

板 204 に取り付けられるダイ 202 を含む。

【0057】

ダイ 202 は典型的にはシリコンウエハの一片のような半導体材質から作製され、そして集積回路及びその能動表面上に形成されるパッド 208 を含んでいる。パッド 208 は、ダイ 202 上の集積回路への I/O 接続点を提供する。制御されたコラプスチップ接続 (controlled collapse chip connect) (C4) 又はフリップチップ取り付け技術を用いて半田バンプ 210 の取り付けを容易にするために、パッド 208 の各々上には UBM が形成されてよい。パッド 208 上に形成される半田バンプ 210 は、ダイ 202 を基板 204 へ取り付けるために用いられてよい。

【0058】

基板 204 は、基板コア 218 及び複数のビルドアップ層 224, 226, 228 を含む。最も外側のビルドアップ層 224, 228 上にはそれぞれ半田マスク 220, 232 が形成される。基板パッド 234 の各々上には半田あげ (pre-solder) 236 が適用されてよい。

【0059】

基板コア 218 は、複数のそれ自身の多重層又はサブ層 (図示せず) を含んでいてよい。層 224, 226 内のトレースを層 228 内のトレース 212 と電気的に相互接続するために、コア 218 内に形成されるめっきされたスルーホール (PTH) 216 が用いられる。層 224 上のトレースを層 226 上のそれらと相互接続するために、ビア又はマイクロビア 214 がレーザ穴開けにより形成されると共に導電性材質によってめっきされ又は充填されてよい。同様に、層 226 上のトレース 212 をコア 218 の上部表面上のトレースと相互接続するために、又は層 228 上のトレースをコア 218 の下側表面上のトレースと相互接続するために、マイクロビア 214 が用いられてよい。

【0060】

半田あげ 236 は半田ペーストの形態にあってよく、従って半田体積を増大させると共にダイ取り付け処理の間に半田バンプ 210 と基板パッド 234 の間での良好な相互接続を提供することができる。半田あげ 236 はまた、バンプ 210 の有効高さを増大させて毛細管アンダーフィル処理 (capillary underfill processes) に役立つ。

【0061】

図 2K に示される基板とは対照的に、パッケージ 200 においては、ビルドアップ層 228 は、層 224, 226 よりも厚い誘電体材質を含んでいてよい。上述したように、層 228 は  $40 \mu\text{m} \sim 60 \mu\text{m}$  の厚みであってよい一方で、層 224, 226 は各々  $25 \mu\text{m} \sim 40 \mu\text{m}$  の排他的な範囲内の呼び厚み (nominal thickness) を有していてよい。幾つかの実施形態では、より少ないビルドアップ層を含む側 (例えば下部) の任意の層 (例えばビルドアップ層 228) は、反対側 (例えば下部) の各層 (例えば層 224, 226) よりも厚くてよい。同様に、半田マスク 232 は半田マスク 220 よりも厚くてよい。1 つの実施形態においては、半田マスク 220 は  $16 \mu\text{m} \sim 30 \mu\text{m}$  の排他の高さを有していてよく、一方、半田マスク 232 は  $30 \mu\text{m} \sim 60 \mu\text{m}$  の範囲内の厚みを有していてよい。ビルドアップ層及び半田マスクの具体的な高さは、ビルドアップ層の相対的な厚みを強調するために例として提供されているだけである。言うまでもなく、他の実施形態は、特定された範囲の外側の厚み値を用いてよい。好都合なことに、より厚い層及び半田マスクはパッケージ 200 における反りを軽減するのに役立つ。

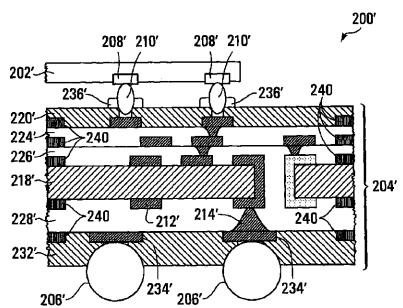

【0062】

反りを防止するために追加的な補強がもたらされてよい。それに沿って図 6 は本発明の別の実施形態を例示する集積回路パッケージ 200' の断面図を示している。パッケージ 200' は、反りを低減するのに役立つように設けられる複数のリング 240 の存在を除き、パッケージ 200 と実質的に類似していてよい。図 5 及び図 6 における同様の部分は構造及び機能において実質的に類似していてよく、そして同様の数字によって表されている。ダッシュ (') 記号は図 6 における部分を図 5 におけるその対応部分から区別しており、そして更には論じられない。

10

20

30

40

50

## 【0063】

また、コア218又はコア218'は小さい熱膨張係数(CTE)を有する材質から形成されてよく、それにより反りを軽減するのに役立つ。材質は紙面に垂直な方向において線熱膨張係数(<sub>1</sub>, <sub>2</sub>で表される)を有しているであろう。例示的な材質は、約15 ppm/(例えば<sub>1</sub>, <sub>2</sub> 5~12 ppm/)より小さい熱膨張係数を伴う材質、約200~240の高いガラス転移温度(Tg)を有するガラス布強化樹脂、等を含んでいてよい。

## 【0064】

リング240は、ビルドアップ層224', 226', 228'又はコア218'の1つ以上の上に、それぞれの導電性層を形成することの一部として(又はその後に)、適切な厚みの金属(例えば銅)を堆積させることによって形成されてよい。半導体パッケージ内に補強材リングを埋め込む種々の方法が当業者によく知られており、リング240を形成するために用いられてよい。1つの実施形態では、リング240は、回路形成段階の間に導電性トレース212と共に形成されてよい。

10

## 【0065】

リング240はパッケージ200'の形状を取ってよい。即ち、リング240の平面視は、上方から見たときのパッケージ200'の外周の輪郭と実質的に同じであってよい。

## 【0066】

リング240は、トレースそれら自身と実質的に類似の材質(例えば銅)で作製されてよい。このことは、好都合にも、ビルドアップ層上に導電性トレースを形成するために用いられるのと同じ製造ステップでリング240が形成されることを可能にする。代替的な実施形態においては、リング240を構成するために、適切な強度の他の材質が用いられてもよい。

20

## 【0067】

より少ないビルドアップ層を含むコアの側でのより厚い誘電体層及び半田マスク層の使用は、コア218'の対向面(即ち上面及び下面)上に非対称な(同じでない数の)ビルドアップ層を有するにもかかわらず、パッケージ200'のバランスを回復する。

## 【0068】

好都合なことに、フローチャートS300に示される処理のような例示的な方法を用いてパッケージ200'を作製することは、そのビルドアップ層(例えば層228')の過剰なデスマニアをうまく回避する一方で、同時にリング240、厚い誘電体層228'及び厚い半田マスク232'は反りを軽減することに役立つ。

30

## 【0069】

理解されるであろうように、本発明の実施形態は、コアの折一的な面上のビルドアップ層の多くの異なる組み合わせを有する例示的な基板を含む。上述した非対称なビルドアップ層を伴う基板は、単に例示的なものであり且つ限定的ではない。本発明の他の実施形態は、一般的には、形態m/k/nのビルドアップ設計を有していてよく、ここでm及びnは正の整数であり、またm n(例えばm>n>0)である。コアは任意の数の層を有していてよく、そして典型的には2層(即ちk=2)及びしばしば4層(即ちk=4)がコア内にあってよく、それぞれ2/2/1及び2/4/1の基板をもたらす。

40

## 【0070】

上述した例示的な方法を用いる半導体デバイス製造は、各ダイに対して又はウエハレベルで実行されてよい。ウエハレベルのパッキングにおいては、個々のダイのための基板に対して上述の方法を適用する代わりに、パッケージング方法は、製造されたウエハ全体のための基板に対して同時に適用される。最後のステップとして、基板及びウエハは、外部配線板上での組み立ての準備が整っている個々のパッケージングされた半導体パッケージへと切り分けられる。

## 【0071】

上述した議論においてコアの対向面又は対向側を参照するために用いられる「上部」及び「下部」(又は「上の」及び「下の」)の用語は、例示的な実施形態の図示に一致して

50

おり、従って図面の方向に応じて交換されてよい。

【0072】

本発明の実施形態は、DRAM、SRAM、EEPROM、フラッシュメモリ、グラフィクスプロセッサ、汎用プロセッサ、DSP、並びに種々の標準的なアナログ、デジタル及び混在の信号の回路パッケージの製造を含む種々の応用において用いられてよい。

【0073】

例示的な方法及び基板は、プリント回路板(PCB)又はプリント配線板(PWB)の他、集積回路パッケージのためのキャリア基板を構成するために適用されてよい。従って本発明の実施形態は、マザーボード、ドーターボード、メモリモジュール、周辺拡張カード(例えばグラフィクスカード、ネットワークインターフェースカード、サウンドカード)等において用いられてよい。

10

【0074】

言うまでもなく、上述の実施形態は例示を目的とするものであり且つ限定を目的とするものではない。本発明を実施する上述の実施形態は、形態、部品の配置、動作の詳細及び順序の多くの修正を許容し得る。むしろ本発明は、特許請求の範囲によって画定されるその範囲内での全てのそのような修正を包含することが意図されている。

【図1】

【図2 A】

【図2 B】

【図2 C】

【図2 D】

【図2 E】

【図2 F】

【図2G】

【図2H】

【図2I】

【図2J】

【図2K】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図4F】

【図3】

【図4G】

【図4H】

【図4I】

【図4J】

【図4K】

【図5】

FIG. 5

【図6】

FIG. 6

---

フロントページの続き

(74)代理人 100111615

弁理士 佐野 良太

(74)代理人 100162156

弁理士 村雨 圭介

(72)発明者 アンドリュー レオン

カナダ、エル3ピー 7エイ1、オンタリオ州、マーカム、エイドリアン クレセント 38

(72)発明者 ローデン トーパシオ

カナダ、エル3アール 4エス8、オンタリオ州、マーカム、カルマ ロード 7

(72)発明者 リアン マルティネス

カナダ、エル3エックス 3ジェイ6、オンタリオ州、ニューマーケット、ケン ビショップ ウエイ 56

(72)発明者 イップ セン ロウ

カナダ、エル3ティー 7エックス4、オンタリオ州、ソーンヒル、サウス パーク ロード 2

24

審査官 吉澤 秀明

(56)参考文献 国際公開第2009/081518 (WO, A1)

特開平11-340610 (JP, A)

特開2008-098570 (JP, A)

特開2005-159201 (JP, A)

特開2000-216289 (JP, A)

特開2002-290031 (JP, A)

特開2007-073766 (JP, A)

特開平11-274731 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H05K 3/46

H01L 23/12