## (19) 대한민국특허청(KR)

### (12) 공개특허공보(A)

(51) Int. Cl.

G11C 11/40 (2006.01)

(11) 공개번호 10-2006-0056249

G11C 11/407 (2006.01)

(43) 공개일자 2006년05월24일

G11C 11/409 (2006.01)

(21) 출원번호 10-2005-0109606

(22) 출원일자 2005년11월16일

|            |                    |             |        |

|------------|--------------------|-------------|--------|

| (30) 우선권주장 | JP-P-2004-00335886 | 2004년11월19일 | 일본(JP) |

|            | JP-P-2005-00172077 | 2005년06월13일 | 일본(JP) |

(71) 출원인

가부시키가이샤 히타치세이사쿠쇼

일본국 도쿄토 치요다쿠 마루노우치 1초메 6반 6고

엘피다 메모리 가부시키가이샤

일본 도쿄도 쥬오꾸 야에스 2쵸메 2방 1고

(72) 발명자

세키구치 토모노리

일본국 도쿄토 치요다쿠 마루노우치 1초메 6반 1고마루노우치 센터비루

12카이 가부시키가이샤 히타치세이사쿠쇼지테키자이산肯hon부나이

아키야마 사토루

일본국 도쿄토 치요다쿠 마루노우치 1초메 6반 1고마루노우치 센터비루

12카이 가부시키가이샤 히타치세이사쿠쇼지테키자이산肯hon부나이

다케무라 리이치로

일본국 도쿄토 치요다쿠 마루노우치 1초메 6반 1고마루노우치 센터비루

12카이 가부시키가이샤 히타치세이사쿠쇼지테키자이산肯hon부나이

한자와 사토루

일본국 도쿄토 치요다쿠 마루노우치 1초메 6반 1고마루노우치 센터비루

12카이 가부시키가이샤 히타치세이사쿠쇼지테키자이산肯hon부나이

가지가야 카즈히코

일본국 도쿄도 쥬오꾸 야에스 2쵸메 2방 1고 엘피다 메모리가부시키가

이사나이

(74) 대리인 특허법인 원전

심사청구 : 없음

(54) 반도체 기억장치

#### 요약

특히 DRAM의 미세화에 유익(有益)하게 되는 반도체 기억장치를 제공한다.

외부로부터 라이트 커맨드(WRT)가 입력되어, 비트선 BLT, BLB의 전압이 VDL, VSS가 되고, 메모리 셀 트랜지스터를 통해서 커패시터의 축적노드(SN)에 그 메모리 셀 트랜지스터의 문턱치전압(LVT: 낮은 문턱치전압, MVT: 중간 문턱치전압,

HVT: 높은 문턱치전압)에 따른 전압이 기록되고, 그 후, 커페시터의 플레이트측에 접속된 플레이트선(PL)이 전압 VPL로부터 전압 VPH로 구동되어, 커플링에 의해 축적노드(SN)의 전압이 상승한 단계에서, 비트선 BLT를 전압 VDL로부터 전압 VDP로 내리고, 축적노드(SN)에 과잉 기록된 전압을 메모리 셀 트랜지스터의 문턱치전압의 크기에 따라 저하시켜, 문턱치전압의 변동에 기인한 축적노드(SN)의 전압의 변동을 저감한다.

## 대표도

도 6

## 색인어

DRAM, 미세화, 비트선, 메모리 셀, 트랜지스터, 문턱치전압, 축적노드, 플레이트선, 커맨드, 커페시터.

## 명세서

### 도면의 간단한 설명

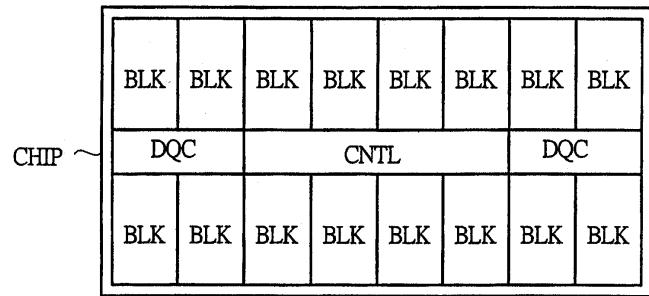

도 1은 본 발명의 일실시형태에 의한 반도체 기억장치에 있어서, 그 침 구성의 일례를 나타내는 평면도이며, (a)는 침 전체의 구성 예, (b)는 (a)에서의 메모리 블록의 구성 예를 나타내는 것이다.

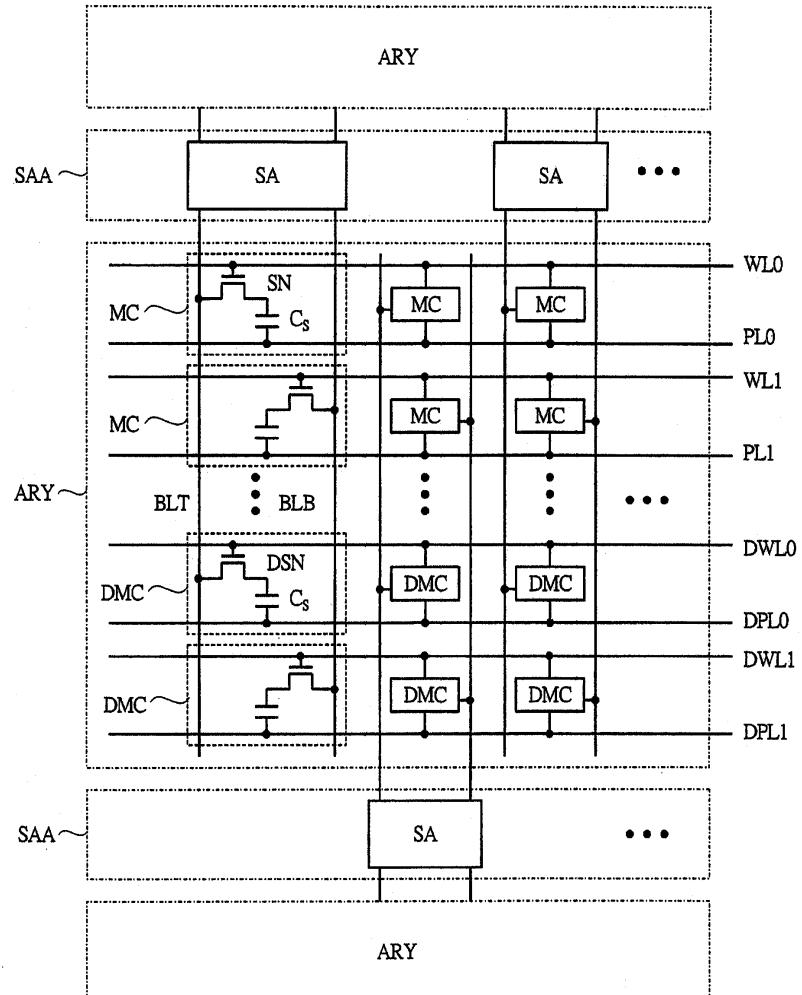

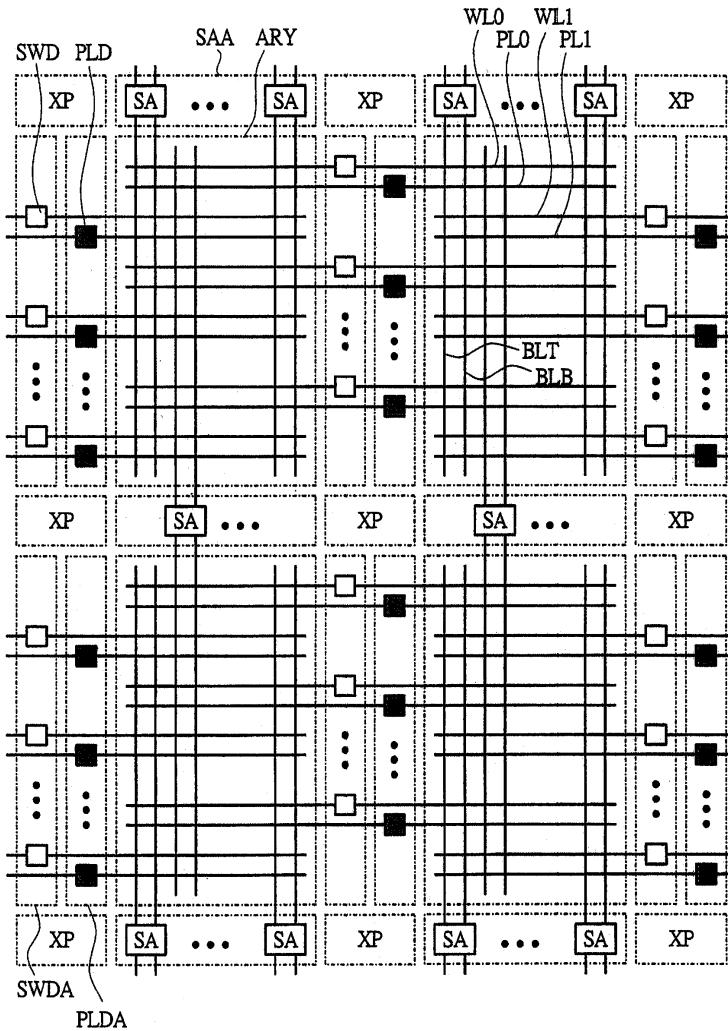

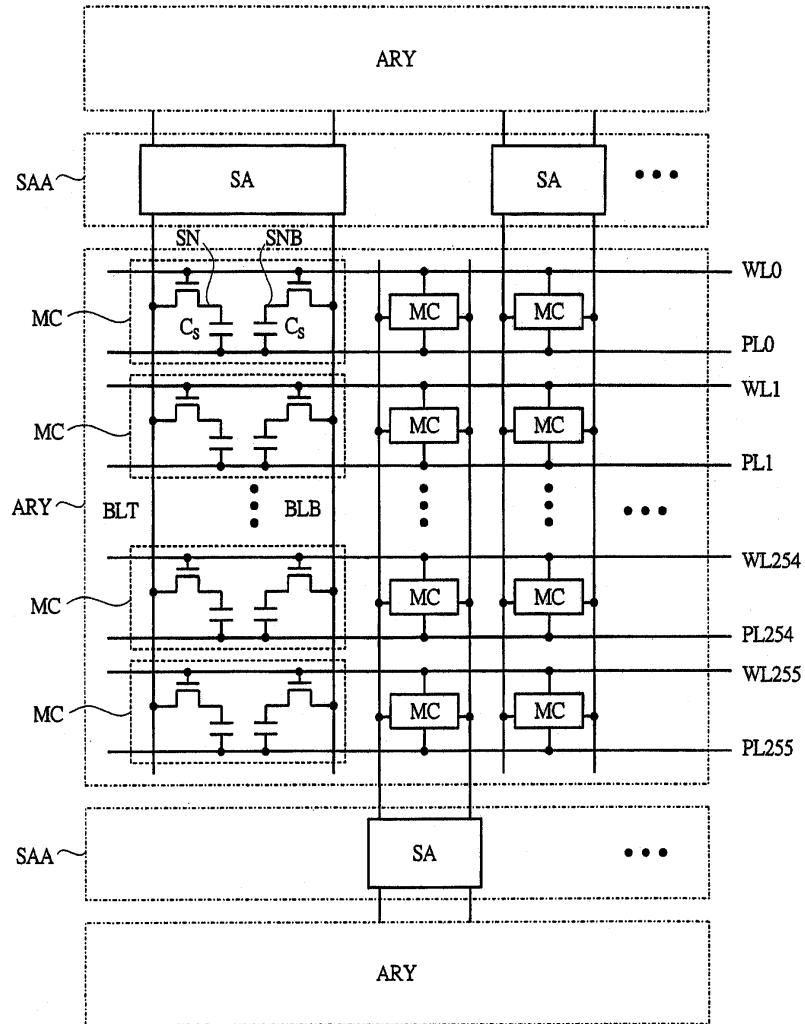

도 2는 도 1의 반도체 기억장치에 있어서, 그 메모리 어레이와 센스 앰프 열(列)의 구성의 일례를 나타내는 회로도이다.

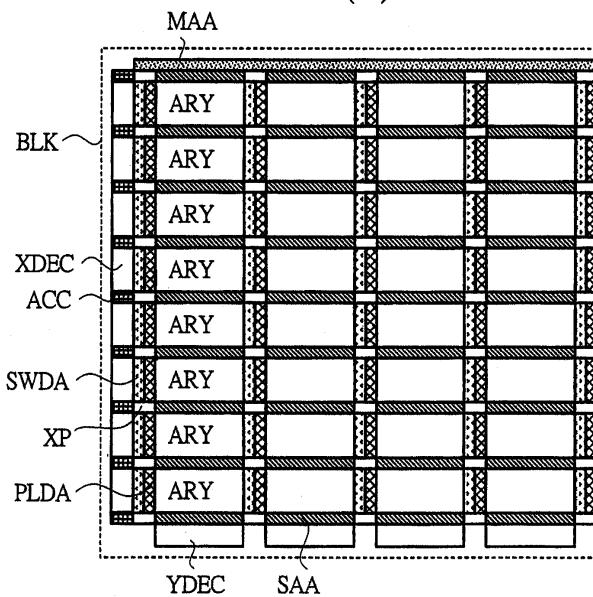

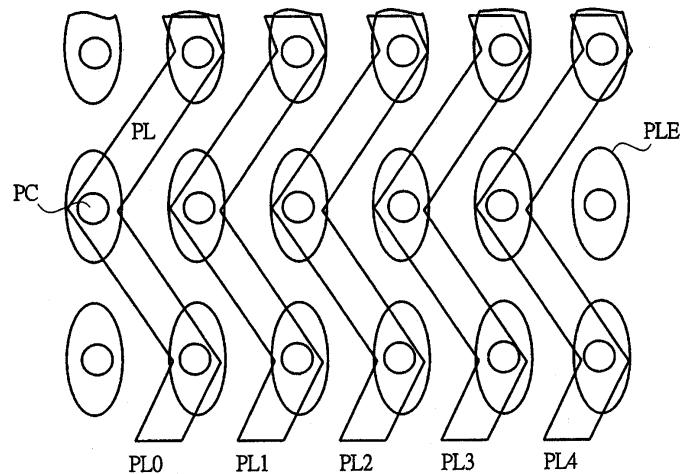

도 3은 도 1의 반도체 기억장치에 있어서, 그 센스 앰프 열과 서브 워드 드라이버 열(列)과 플레이트 드라이버 열(列)의 상세한 배치관계의 일례를 나타내는 평면도이다.

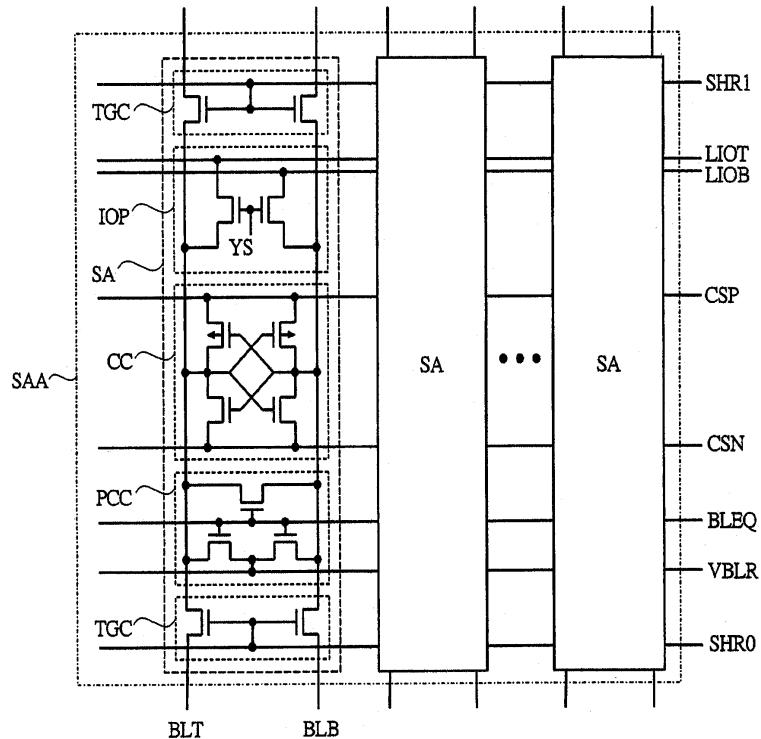

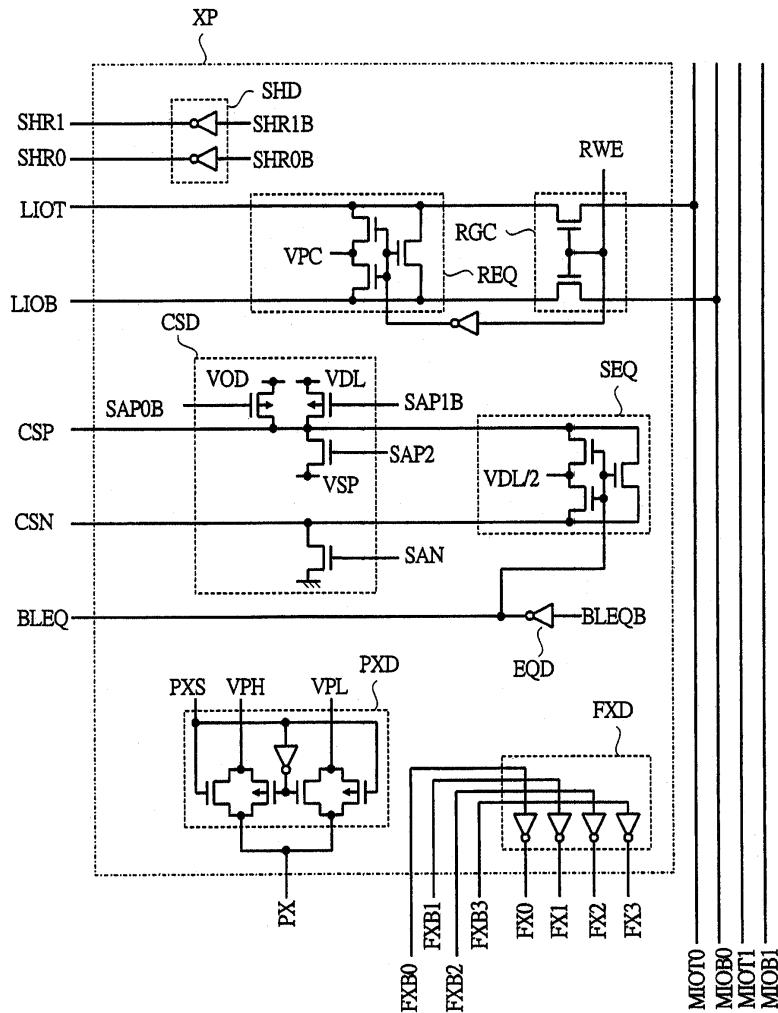

도 4는 도 2의 반도체 기억장치에 있어서, 그 센스 앰프 열의 상세한 구성의 일례를 나타내는 회로도이다.

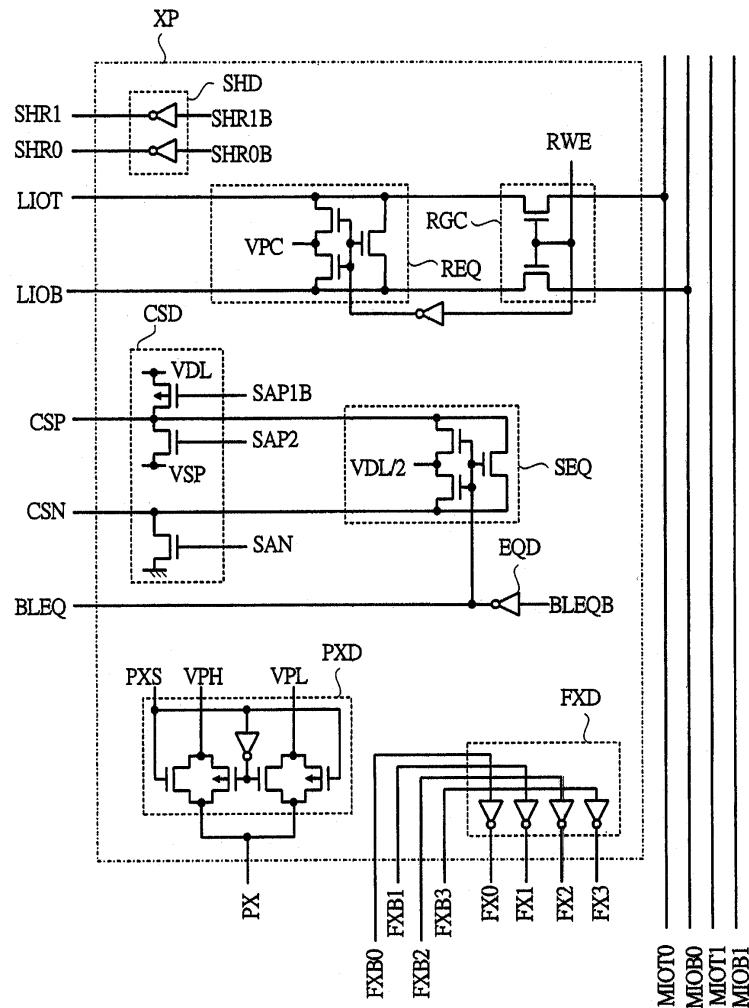

도 5는 도 1의 반도체 기억장치에 있어서, 그 크로스 에리어의 구성의 일례를 나타내는 회로도이다.

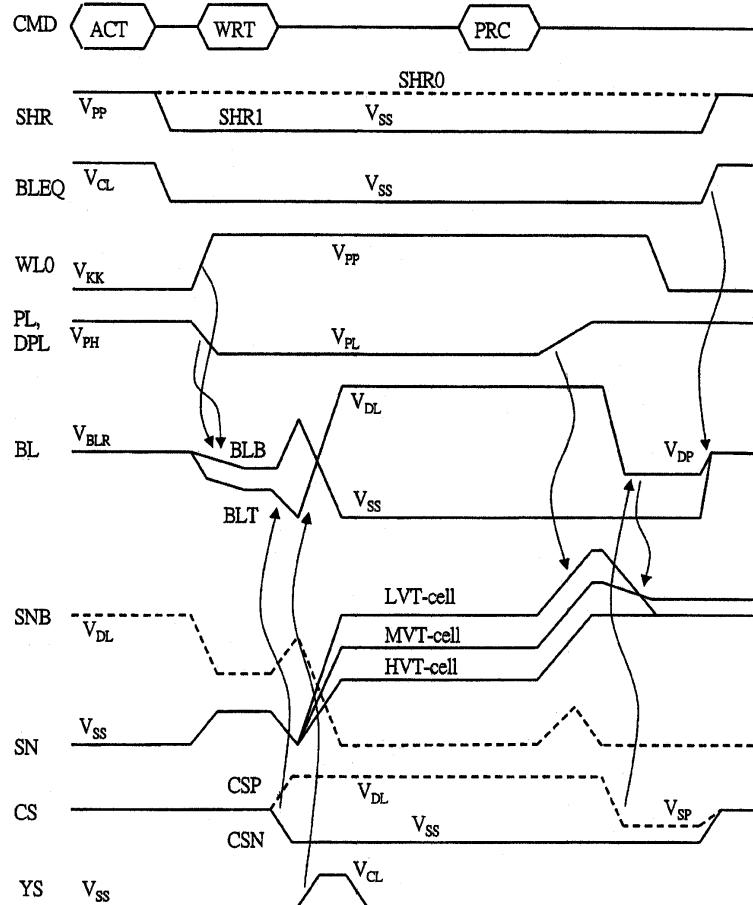

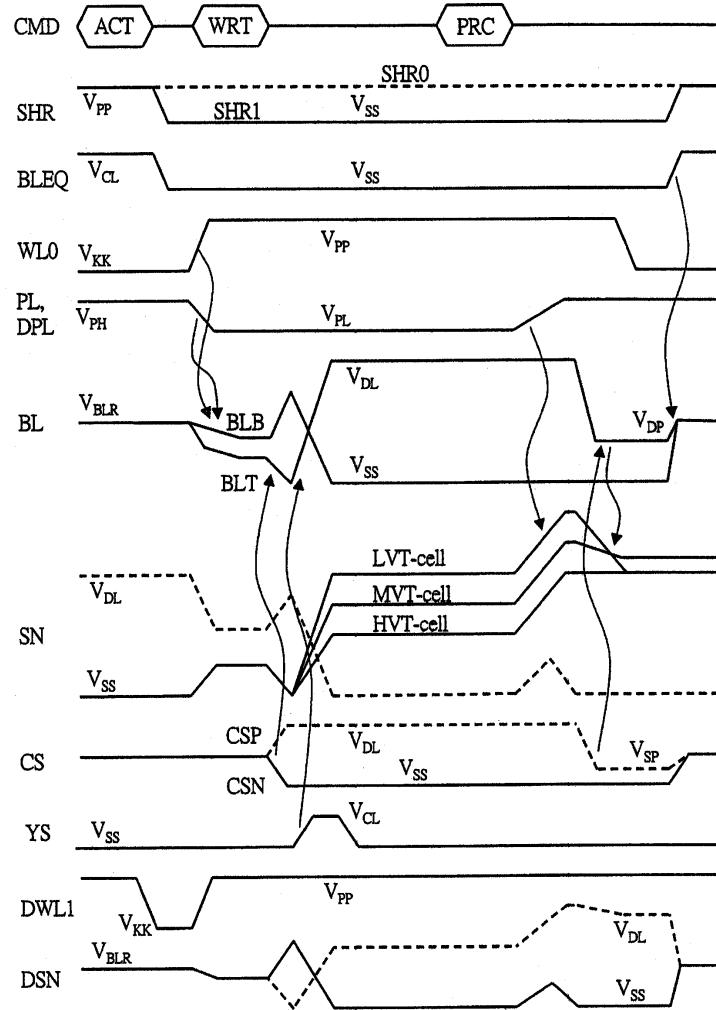

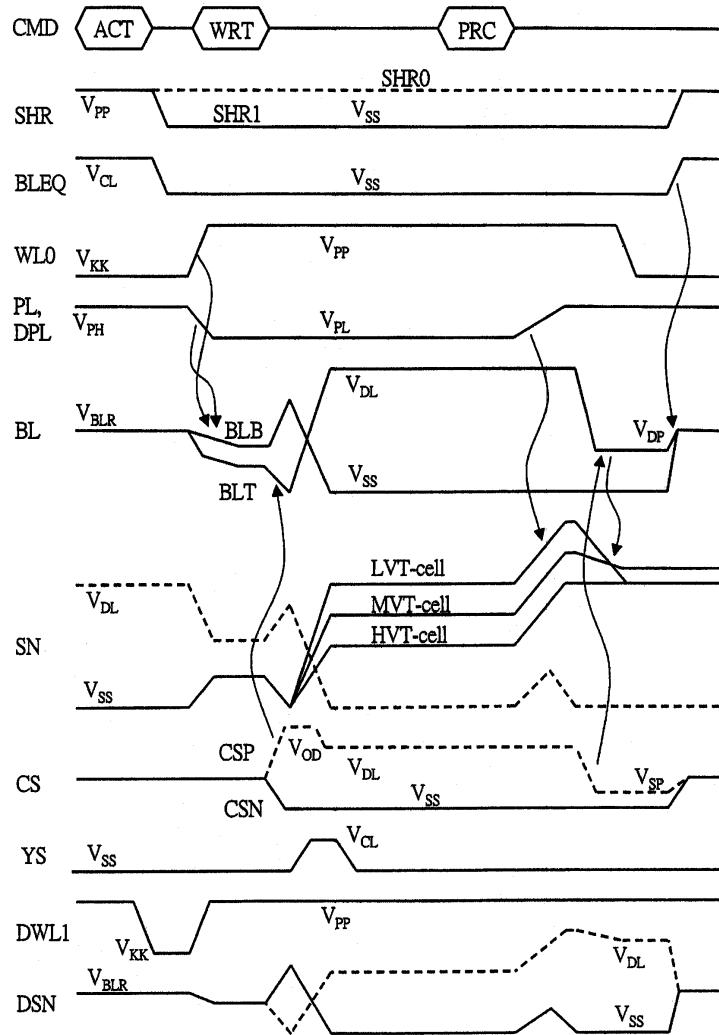

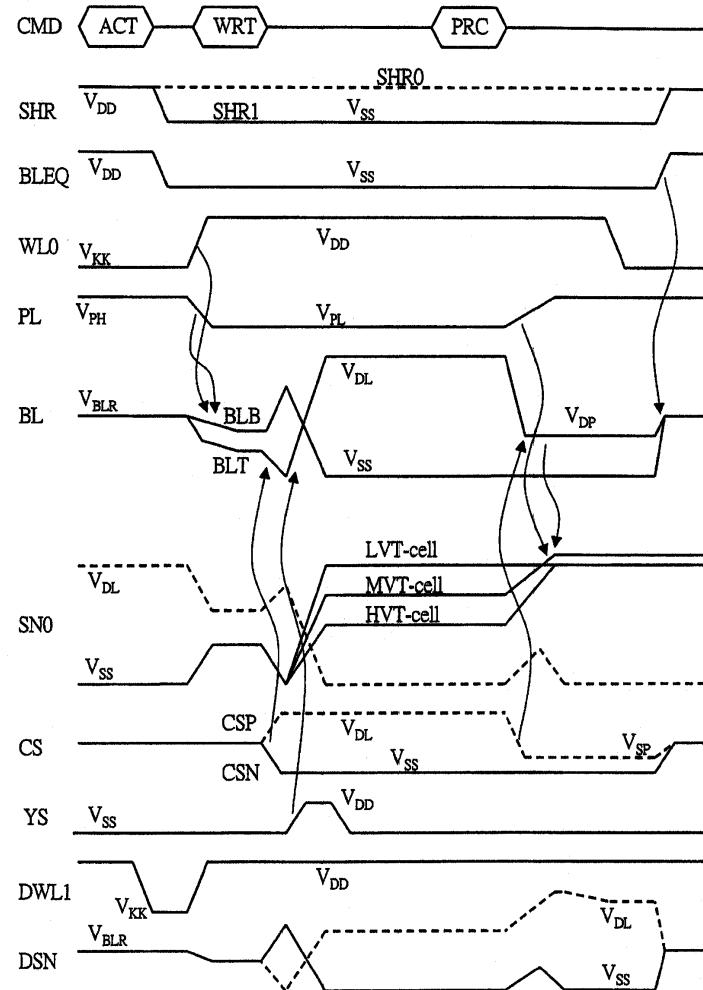

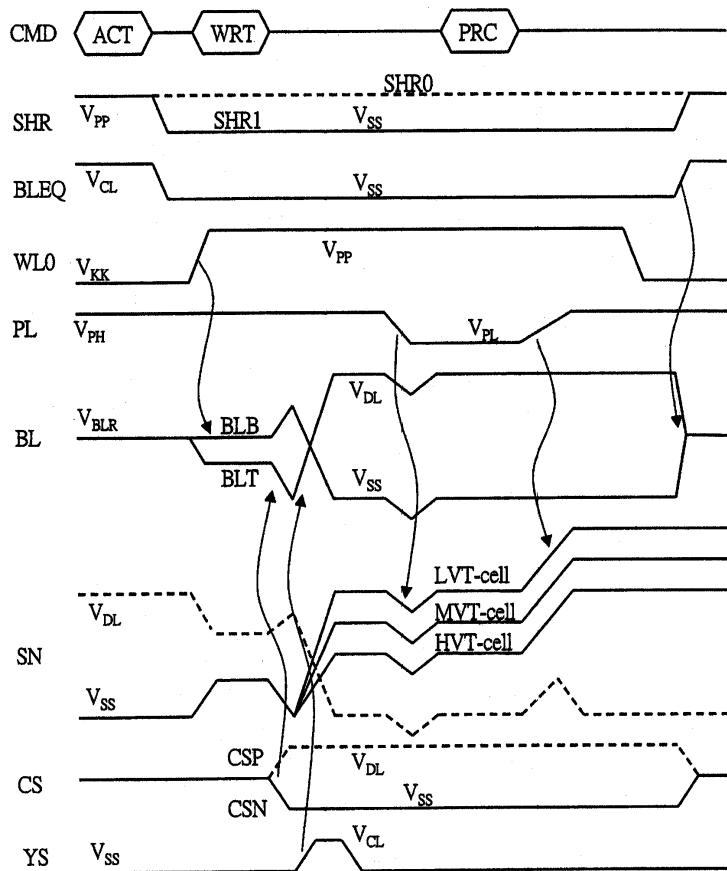

도 6은 도 1의 반도체 기억장치에 있어서, 그 동작의 일례를 나타내는 동작 과정도이다.

도 7은 도 5의 크로스 에리어에 있어서, 그 구성을 변형한 일례를 나타내는 회로도이다.

도 8은 도 7의 크로스 에리어에 있어서, CS선 드라이버에서 사용하는 전압의 발생방식의 일례를 나타내는 개략도이다.

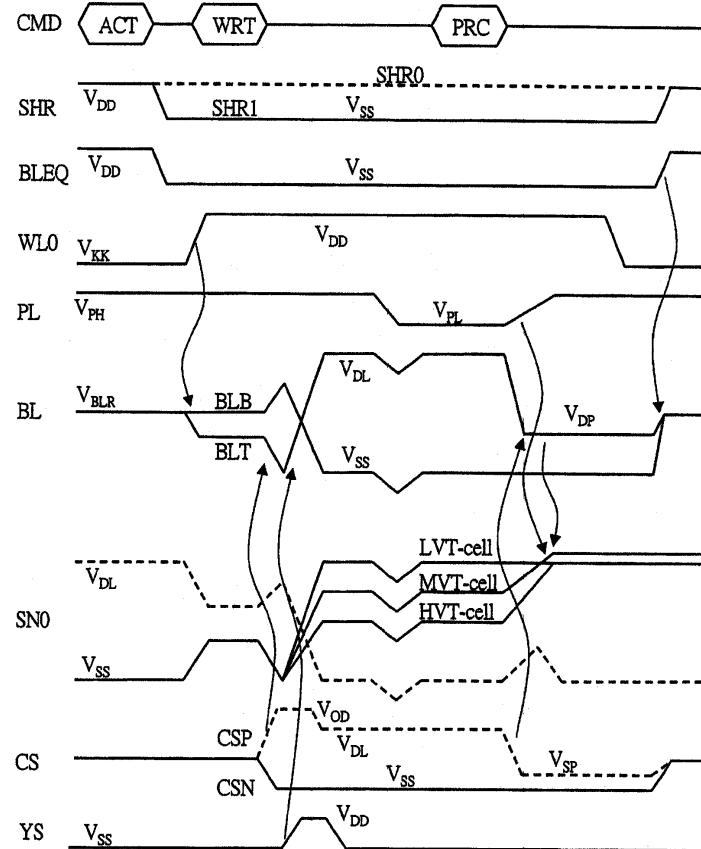

도 9는 도 1의 반도체 기억장치에 있어서, 도 7의 크로스 에리어를 이용한 경우 동작의 일례를 나타내는 과정도이다.

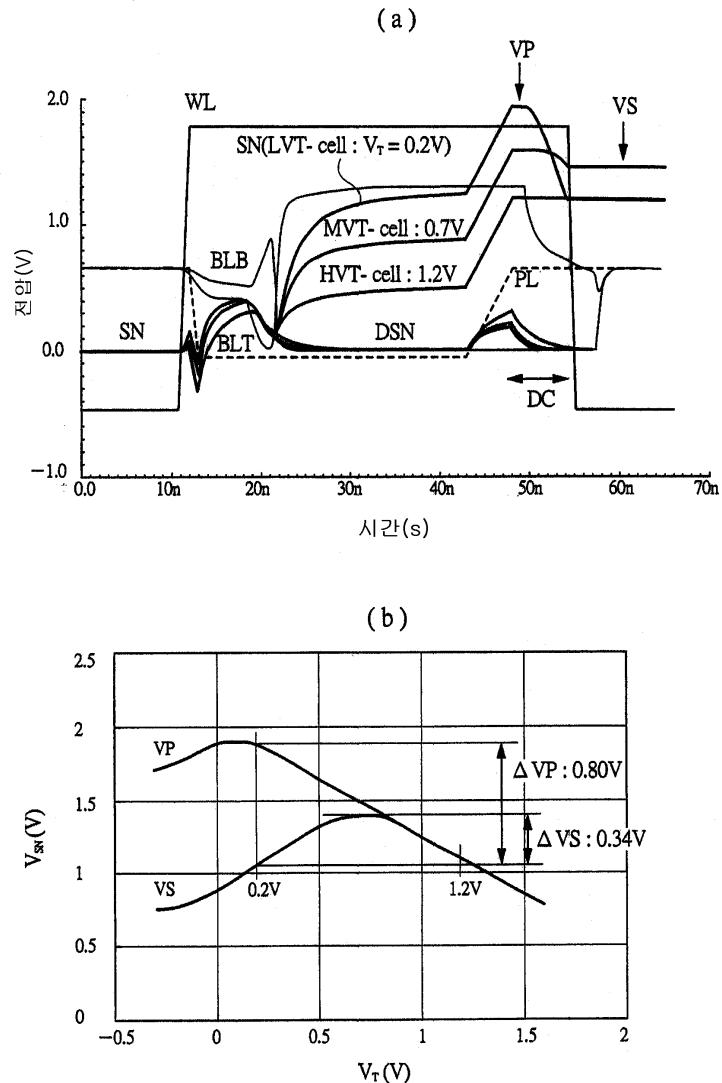

도 10은 도 6에서의 동작을 회로 시뮬레이션으로 재현한 것이며, (a)는 그 동작에서의 주요부의 과정도, (b)는 그 동작에서의 문턱치전압과 기록전압의 관계를 나타내는 그래프이다.

도 11은 도 1의 반도체 기억장치에 있어서, 도 6을 변형한 동작의 일례를 나타내는 동작 과정도이다.

도 12는 도 1의 반도체 기억장치에 있어서, 도 6을 변형한 동작의 일례를 나타내는 동작 과정도이다.

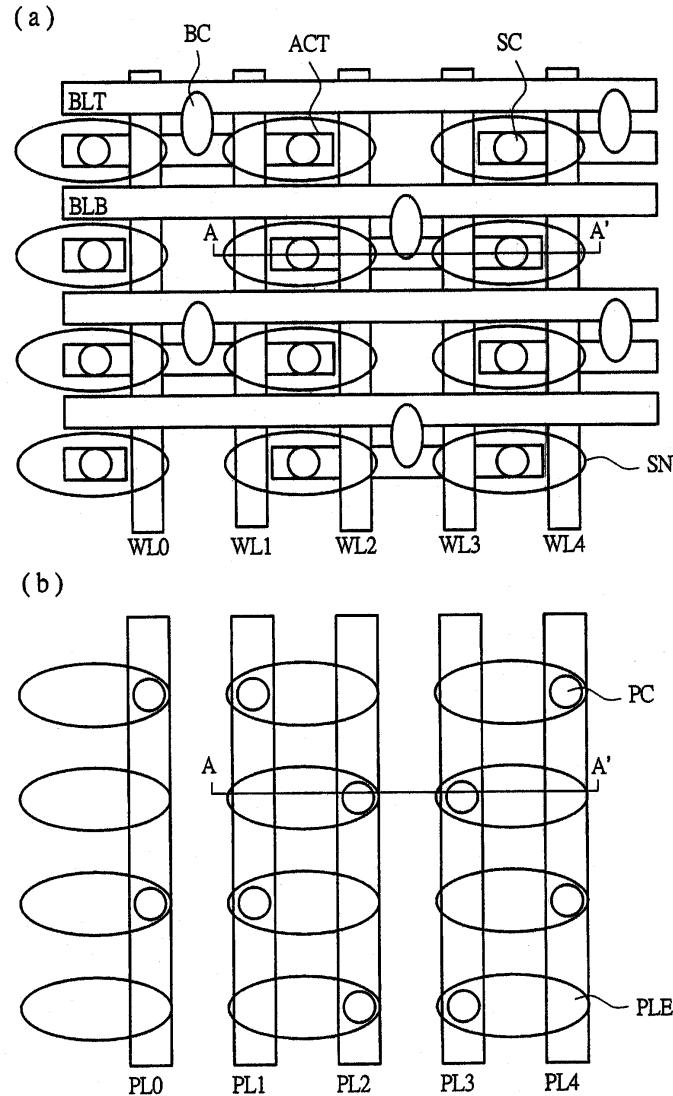

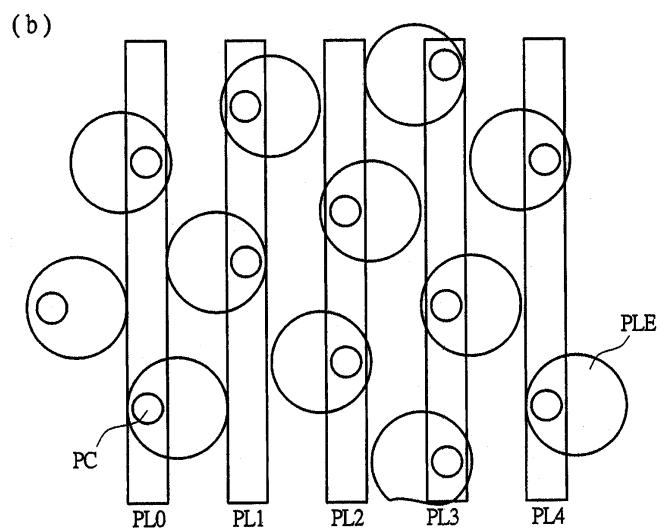

도 13은 도 1의 반도체 기억장치에 있어서, 그 메모리 어레이의 레이아웃의 일례를 나타내는 도면이며, (a)는 트랜지스터의 활성영역으로부터 축적노드까지의 레이아웃, (b)는 플레이트 전극으로부터 플레이트선까지의 레이아웃을 나타내는 것이다.

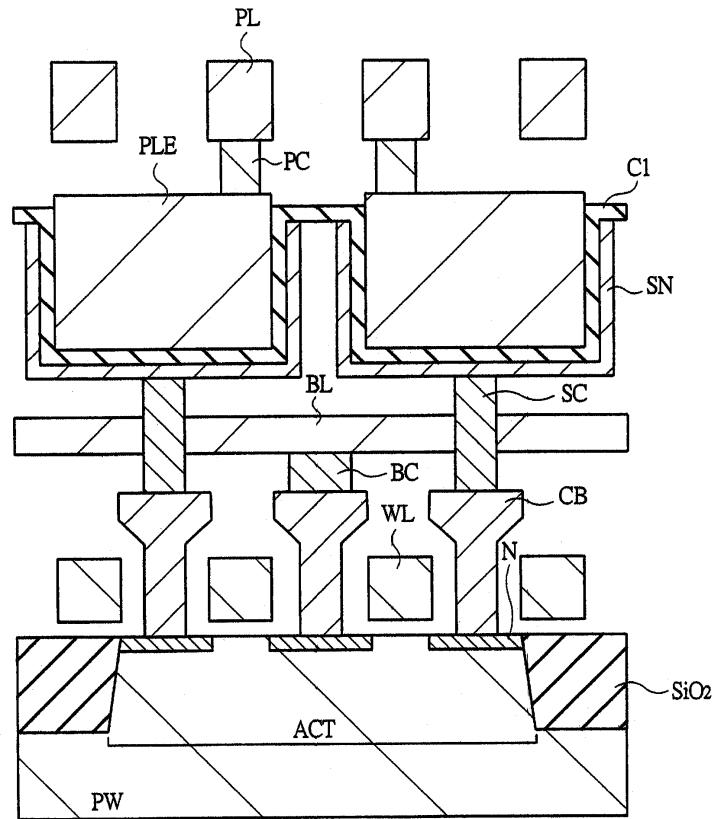

도 14는 도 13의 레이아웃에 있어서, 그 A-A'간의 단면구성의 일례를 나타내는 도면이다.

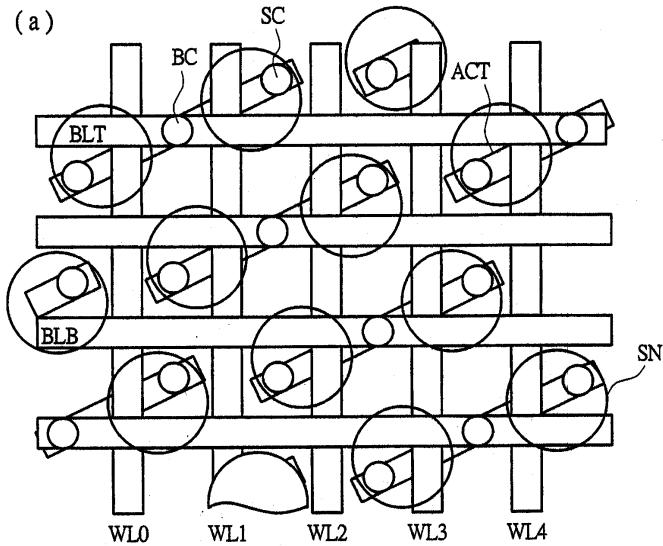

도 15는 도 1의 반도체 기억장치에 있어서, 도 13과는 다른 메모리 어레이의 레이아웃의 일례를 나타내는 도면이며, (a)는 트랜지스터의 활성영역으로부터 축적노드까지의 레이아웃, (b)는 플레이트 전극으로부터 플레이트선까지의 레이아웃을 나타내는 것이다.

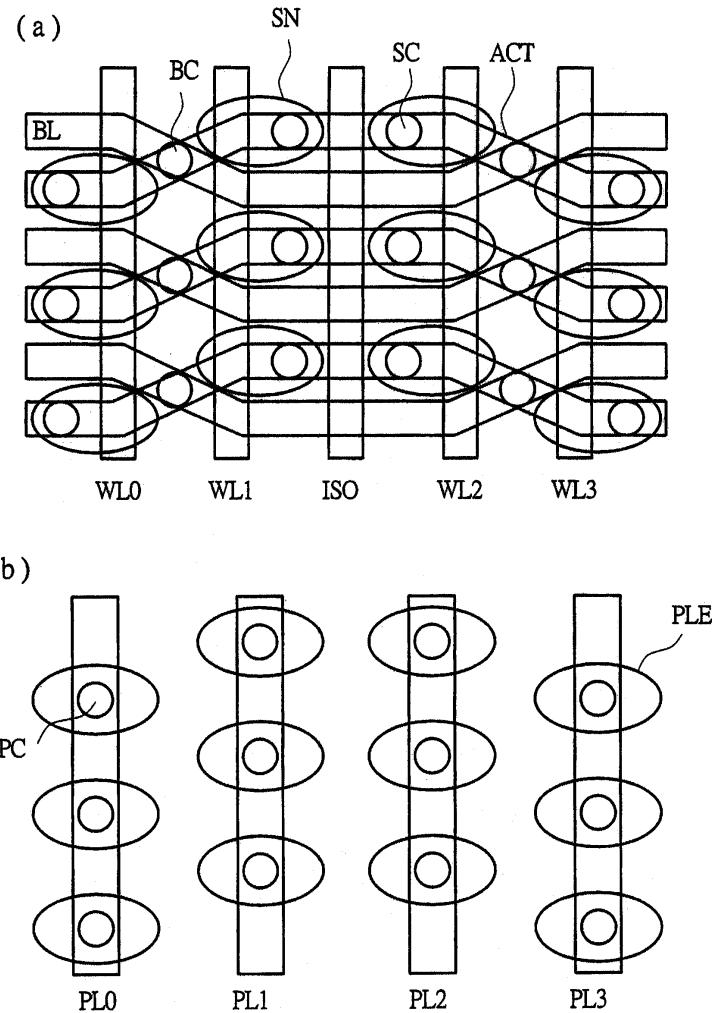

도 16은 도 1의 반도체 기억장치에 있어서, 도 13과는 다른 메모리 어레이의 레이아웃의 일례를 나타내는 도면이며, (a)는 트랜지스터의 활성영역으로부터 축적노드까지의 레이아웃, (b)는 플레이트 전극으로부터 플레이트선까지의 레이아웃을 나타내는 것이다.

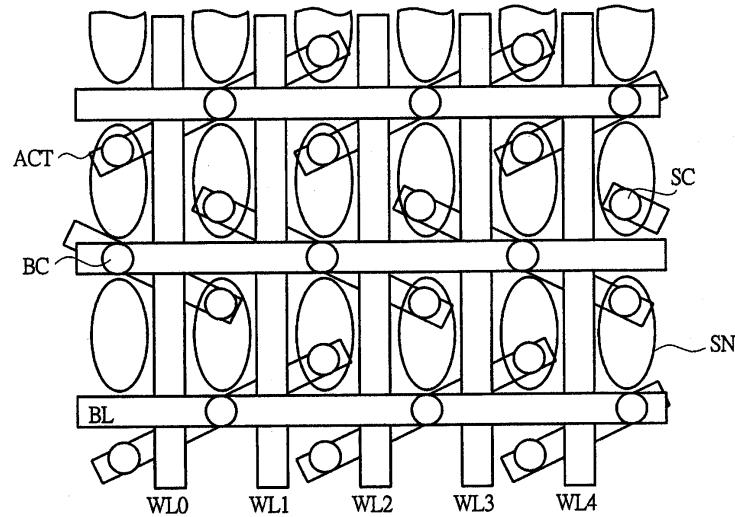

도 17은 도 1의 반도체 기억장치에 있어서, 도 16과는 다른 메모리 어레이의 레이아웃의 일례를 나타내는 도면이며, (a)는 트랜지스터의 활성영역으로부터 축적노드까지의 레이아웃, (b)는 플레이트 전극으로부터 플레이트선까지의 레이아웃을 나타내는 것이다.

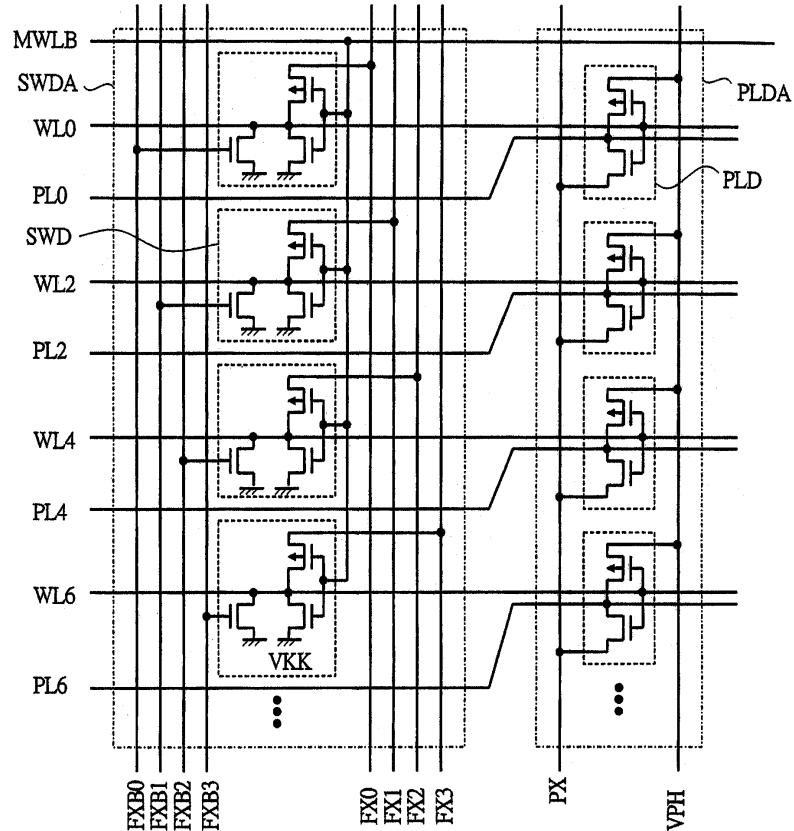

도 18은 도 1의 반도체 기억장치에 있어서, 그 서브 워드 드라이버 열과 플레이트 드라이버 열의 구성의 일례를 나타내는 회로도이다.

도 19는 도 18의 서브 워드 드라이버 열과 플레이트 드라이버 열에 있어서, 그 동작 파형의 일례를 나타내는 파형도이다.

도 20은 본 발명의 전제로서 검토한 기술의 반도체 기억장치에 있어서, 플레이트를 구동하는 DRAM 메모리 어레이의 일부 구성 예를 나타내는 회로도이다.

도 21은 도 20의 반도체 기억장치에 있어서, 그 동작의 일례를 나타내는 동작 파형도이다.

도 22는 도 1의 반도체 기억장치에 있어서, 도 2를 변형한 메모리 어레이와 센스 앤프 열의 구성의 일례를 나타내는 회로도이다.

도 23은 도 1의 반도체 기억장치에 있어서, 도 6을 변형한 동작의 일례를 나타내는 동작 파형도이다.

[도면의 주요 부분에 대한 간단한 부호의 설명]

CHIP 메모리 칩, BLK 메모리 블록,

DQC 입출력 회로, CNTL 제어회로,

ARY 메모리 어레이, MAA 메인 앤프 열,

XDEC 행 디코더, YDEC 열 디코더,

ACC 어레이 제어회로, XP 크로스 애리어,

SWDA 서브 워드 드라이버 열, SWD 서브 워드 드라이버,

PLDA 플레이트 드라이버 열, PLD 플레이트 드라이버,

SAA 센스 앤프 열, SA 센스 앤프,

MC 메모리 셀, DMC 더미 메모리 셀,

SN 축적노드, DSN 더미 축적노드,

CS 커.ForEach,

BL, BLT, BLB 비트선,

WL, WLO~4 워드선,

MWLB 메인 워드선,

FX 서브 워드 드라이버 선택선,

DWL, DWLO, DWL1 더미 워드선

PL, PLO~4 플레이트선,

PX 플레이트 제어선,

PXS 플레이트 타이밍신호,

DPL, DPLO, DPL1 더미 플레이트선,

TGC 트랜스퍼 게이트,

IOP 판독 · 기록포트,

YS 열 선택선,

CC 크로스 커플 · 앰프,

PCC 프리 차지회로,

SHRO, SHR1 센스 앰프 분리신호,

LIOT, LIOB 로컬 IO선,

MIOT, MIOB 메인 IO선,

CSP P측 공통 소스선,

CSN N측 공통 소스선,

BLEQ 비트선 프리 차지신호,

SHD SHR 신호 드라이버,

REQ LIO선 프리 차지회로,

RGC 리드 라이트 게이트,

CSD CS선 드라이버,

SEQ CS선 프리 차지회로,

EQD BLEQ 신호 드라이버,

FXD FX선 드라이버,

PXD PX선 드라이버,

ACT 활성영역,

BC 비트선 콘택트,

SC 축적노드 콘택트,

PC 플레이트 콘택트,

PLE 플레이트 전극,

CI 용량절연막 CI,

CB 콘택트,

NN형 확산층 영역,

PW 반도체 기판,

SiO<sub>2</sub> 절연막,

ISO 소자분리용 게이트.

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은, 다이내믹형 랜덤 액세스 메모리(DRAM) 등의 반도체 기억장치에 관한 것으로서, 특히 플레이트 전극을 구동해서 메모리 셀로의 기록 전하량을 증가하는 반도체 기억장치에 적용하는 유효한 기술에 관한 것이다.

본 발명자가 검토한 바에 의하면, DRAM의 미세화 기술에 관해서는, 이하와 같은 것이 생각된다.

DRAM의 메모리 셀을 미세화해서 고집적화하기 위해서는, 한정된 메모리 셀 바닥면적 중에서 큰 용량을 실현하는 커퍼시터 및 미세 트랜지스터가 필요하다. 메모리 셀 트랜지스터를 미세화할 때 큰 문제가 되는 것이, 게이트 산화막의 박막화이다. MOS 트랜지스터의 게이트 길이를 단축할 때는, 단(短)채널 효과를 억제하기 위해서, 게이트 산화막을 박막화 할 필요가 있다.

그렇지만, DRAM에 있어서는, 메모리 셀에 N채널 트랜지스터를 사용하고 있고, 축적노드의 'H'측의 최대 기록전압이, 메모리 셀 트랜지스터의 게이트에 인가되는 워드선 'H'측의 전압 VPP로부터 문턱치전압 VT만큼 내려간 VPP-VT가 되는 것 및 데이터 유지특성을 유지하기 위해서 문턱치전압 VT를 저감하는 것은 허용되지 않으므로, 워드선 전압을 용이하게 저감할 수 없다. 따라서, 로직 제품에 사용되는 MOS 트랜지스터와 비교하면, 메모리 셀 트랜지스터의 게이트 산화막은 두꺼워지기 때문에, 미세화가 곤란하다.

이러한 문제에 대해서, 예컨대 특허문현1에는, 메모리 셀의 플레이트 전극을 구동하고, 메모리 셀로의 기록전압을 높이는 DRAM이 나타나 있다. 본 방식에서는, 워드선의 'H'측의 전압을 저감하고, 이것에 의해 'H'측 데이터의 기록이 불충분해지는 문제를, 플레이트 전극을 구동하는 것에 의해 보충하고 있다. 이렇게 하면, 메모리 셀 트랜지스터의 게이트 산화막을 박막화할 수 있기 때문에, 메모리 셀을 미세화하는 것이 가능해진다.

[특허문현1] 특개평11-260054호 공보

그런데, 상기와 같은 DRAM의 미세화 기술에 대해서, 본 발명자가 검토한 결과, 이하와 같은 것이 명백해졌다.

예컨대, 전술한 특허문현1의 기술에는, 다음과 같은 문제가 있는 것을 판명하였다. 메모리 셀에 이용하는 미세 트랜지스터는, 문턱치전압(VT)의 변동이 크고, 대용량의 DRAM에 있어서는, 변동의 범위는 1V 가깝게 된다. 이렇게 메모리 셀의 문

문턱치전압 변동이 큰 경우에 플레이트 구동을 행하면, 메모리 셀에 기록되는 전압이 큰 변동을 갖는다. 즉, 문턱치전압이 큰 셀에 대해서 충분히 전압을 기록하고자 하여, 플레이트의 진폭을 크게 하면, 문턱치전압이 작은 셀에서는 과잉으로 높은 전압이 기록되어 버려, 메모리 셀 트랜지스터의 신뢰성이 저하한다.

이 문제를 도 20, 도 21을 이용해서 설명한다. 도 20은, 본 발명의 전제로서 검토한 기술의 반도체 기억장치에 있어서, 플레이트를 구동하는 DRAM 메모리 어레이의 일부 구성 예를 나타내는 회로도이다. 도 21은, 도 20의 반도체 기억장치에 있어서, 그 동작의 일례를 나타내는 동작 과형도이다.

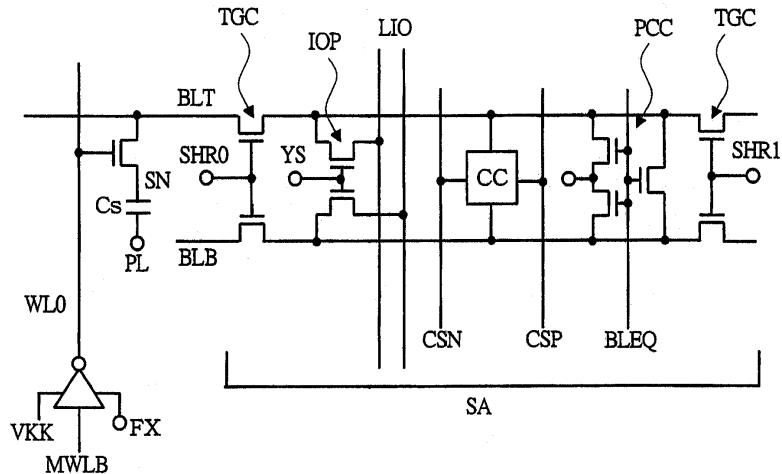

도 20에 나타내는 DRAM 메모리 어레이에는, 예컨대, 메인 워드선(MWLB)이나 서브 워드 드라이버 선택선(FX)에 의해 구동되는 워드선(WLO)과, 비트선 BLT, BLB와, 워드선(WLO)과 비트선 BLT의 교점에 설치된 메모리 셀과, 비트선 BLT, BLB의 사이에 설치된 센스 앰프(SA) 등을 포함하고 있다. 메모리 셀은, 메모리 셀 트랜지스터와 커페시터(Cs)를 포함하고 있고, 커페시터(Cs)의 일단(메모리 셀 트랜지스터측)은 축적노드(SN)이며, 타단은 플레이트선(PL)이다.

센스 앰프(SA)는, 센스 앰프 분리신호(SHRO, SHR1)에 의해 구동되는 트랜스퍼 게이트(TGC)와, 열(列) 선택선(YS)에 의해 비트선 BLT, BLB와 로컬 IO선쌍(LIO선쌍)을 접속하는 판독·기록 포트(IOP)와, 프리 차지신호(BLEQ)의 활성화에 의해 비트선 BLT, BLB의 프리 차지를 행하는 프리 차지회로(PCC)와, P측 공통 소스선(CSP) 및 N측 공통 소스선(CSN)의 구동에 의해 비트선 BLT, BLB의 전압차이를 증폭하는 크로스 커플·앰프(CC)를 포함하고 있다. 또, 여기에서는 일부의 구성을 나타내고 있지만, 실제의 DRAM 메모리 어레이에는, 다수의 메모리 셀이나 센스 앰프(SA) 등이 포함된다.

이러한 구성에 대해서, 예컨대 도 21과 같은 동작이 행하여진다. 우선, 칩 외부로부터 뱅크 활성화 커맨드(ACT)가 입력되면, 어드레스로 지정된 센스 앰프(SA)에 있어서 센스 앰프 분리신호(SHR)의 한쪽 SHR1과 프리 차지신호(BLEQ)가 비활성화된다. 행 디코더에 있어서, 메인 워드선(MWLB)이 VKK로 내려가고, 어레이 제어회로에 있어서 서브 워드 드라이버 선택선(FX)이 활성화되면, 선택된 워드선(WLO)이 VKK로부터 VPP로 활성화된다. 여기에서, VKK는 부(負)전원발생 회로에 의해 발생된 워드선의 저레벨측의 전원전압이며, VPP는 고(高)레벨측의 전원전압이다.

그리고, 워드선(WLO)에 의해 선택된 메모리 셀에 있어서는, 메모리 셀 트랜지스터가 도통하여, 비트선 BLT 상에 신호가 판독된다. 도 21에서는, 메모리 셀에 접지전압 VSS가 기록되고 있고, 'L'의 신호가 발생한 예를 나타내고 있다. 그 후, 센스 앰프(SA)에 있어서 P측 공통 소스선(CSP)이 VDL로, N측 공통 소스선(CSN)이 접지전압 VSS로 구동되어, 비트선 BLT, BLB 상의 신호가 증폭된다. 이 상태에서, 메모리 칩은, 리드 커맨드(RD) 또는 라이트 커맨드(WRT)를 받아들일 수 있다. 도 21에서는, 라이트 커맨드(WRT)가 입력된 경우를 나타내고 있다.

이것에 의해, 선택된 어드레스의 열 선택선(YS)이 활성화되어, LIO선쌍으로 부터, 라이트 데이터가 기록된다. 여기에서는 비트선 BLT가 'H'로 구동되는 반전 기록시의 과형을 나타내고 있다.

그 후, 선택 메모리 셀의 플레이트선(PL)의 전압이 VPH로부터 VPL으로 하강된다. 메모리 셀 트랜지스터는 N채널 MOS 트랜지스터므로, 문턱치전압을 VT라 하면, 축적노드(SN)에 기록할 수 있는 최대의 전압은 VPP-VT가 된다. 이 DRAM 메모리 어레이에서는, 워드선의 'H'레벨 VPP를 전원전압 VDD(예를들면 1.8V) 정도까지 내리고 있다. 또한, 메모리 셀 트랜지스터는, 미세한 트랜지스터를 이용하고 있고, 개수도 많기 때문에, 문턱치전압(VT)의 변동이 1V 가깝게 매우 커진다. 예컨대 설계 중심값을 0.7V라고 한 경우, 문턱치전압(VT)의 최소값은 0.2V, 최대값은 1.2V가 된다.

그렇게 하면, 비트선 전압(VDL)을 예컨대 1.3V라고 한 경우, 문턱치전압이 낮은 메모리 셀(LVT-ce11)에서는, VPP-VT=1.6V이므로 메모리 셀 트랜지스터가 온하고 있고, 축적노드(SN)에 VDL=1.3V가 기록되지만, 문턱치전압이 중간 정도의 메모리 셀(MVT-ce11), 높은 메모리 셀(HVT-ce11)에서는 증폭의 도중에 컷오프(cut off) 상태가 되어, 각각 1.1V, 0.6V까지 밖에 기록되지 않는다. 즉, 기록시에서의 축적노드(SN)의 전압은, 메모리 셀 트랜지스터의 문턱치전압(VT)에 대응해서 0.6V로부터 1.3V까지의 변동을 갖는다.

이 상태에서, 프리 차지 커맨드(PRC)가 입력된 후에, 선택 메모리 셀의 플레이트선(PL)의 전압을 VPL로부터 VPH로 복귀시키면, 축적노드(SN)의 전압은, 커페시터(Cs)로부터의 커플링을 받고,  $\Delta PL = VPH - VPL$  분 만큼 상승한다. 'H'가 기록된 메모리 셀에서는, 메모리 셀 트랜지스터가 컷오프하거나 컨더턴스가 대단히 작은 상태이기 때문에,  $\Delta PL$ 의 전압 상승분이 유지되지만, 'L'이 기록된 메모리 셀에서는, 메모리 셀 트랜지스터가 충분히 온 상태이기 때문에, 곧 접지전압 VSS으로 복귀한다. 따라서, 축적 전하량을  $\Delta PL$  만큼 증가할 수 있다.

$\Delta PL$ 을, 가장 문턱치전압이 높은 메모리 셀(HVT-ce11)의 기록전압이 VDL까지 상승하도록 예컨대 0.7V로 설정하면, 모든 메모리 셀이 1.3V 이상으로 기록되기 때문에, 다음 사이클에서의 판독 신호량이나 리텐션(retention) 시간의 마진을 넓

힐 수 있다. 그렇지만, 문턱치전압이 낮은 셀(LVT-ce11)에서는, 원래 VDL=1.3V까지 기록되어 있었으므로, 더 전압이  $\Delta$ PL분만큼 상승하면 2.0V까지 높아진다. 이대로 워드선을 비활성화하면, 대기시에 메모리 셀 트랜지스터에 높은 전압이 인가된 그대로 되기 때문에, 디바이스의 신뢰성이 저하하고, 메모리 셀 트랜지스터의 미세화가 곤란해진다.

### 발명이 이루고자 하는 기술적 과제

그래서, 본 발명의 목적은, 이러한 문제 등을 감안하여, 특히 DRAM의 미세화에 유익해지는 반도체 기억장치를 제공하는 것이다.

본 발명의 상기 및 그 밖의 목적과 신규인 특징은, 본 명세서의 기술 및 첨부 도면으로부터 명백해질 것이다.

### 발명의 구성 및 작용

본원에 있어서 개시되는 발명 중, 대표적인 것의 개요를 간단히 설명하면, 다음과 같다.

본 발명에 의한 반도체 기억장치는, 각각 MOS 트랜지스터와 커패시터를 포함하고, 이 MOS 트랜지스터의 게이트가 선택 단자로 되며, 소스 및 드레인의 한쪽이 입출력 단자로 되고, 소스 및 드레인의 다른쪽이 커패시터의 축적노드에 접속되는 복수의 메모리 셀과, 복수의 메모리 셀의 선택단자에 각각 접속되는 복수의 워드선과, 복수의 메모리 셀의 입출력 단자에 각각 접속되는 상보 비트선과, 상보 비트선의 일단에 접속되어, 상보 비트선의 전압차이를 증폭해서 래치를 행하는 센스 앰프를 구비하고 있고, 또, 복수의 워드선 중 어느 하나의 워드선이 활성화된 후, 센스 앰프가 활성화되어, 상보 비트선 중 한쪽의 비트선이 제1의 전압으로 증폭되고, 다른쪽의 비트선이 제1의 전압보다도 낮은 제2의 전압으로 증폭된 단계에서, 제1의 전압으로 증폭된 비트선을, 제1의 시간에서 제1의 전압보다도 낮은 제3의 전압으로 내리고, 그 후에 상기 어느 하나의 워드선을 비활성화하는 수단을 갖는 것으로 되어 있다.

즉, DRAM 메모리 셀에 있어서, MOS 트랜지스터(메모리 셀 트랜지스터)의 문턱치전압의 변동 등에 의해, 기록(재기록을 포함한다) 전하량의 변동이 생기는 경우가 있지만, 이 기록 전하량의 변동을, 워드선을 비활성화하기 전의 기록의 종반부분에서, 과잉 기록전하를 방전시키는 것으로 저감한다. 이것에 의해, 과잉 기록전하에 따라 발생하는, 소자의 내구성(耐久性), 내압(耐壓) 및 리크 등의 신뢰성의 문제를 해결 할 수 있고, 반도체 기억장치의 미세화가 가능하게 된다.

여기에서, 상기 센스 앰프는, 소위 크로스 커플형 앰프로 할 수 있고, 이 경우, 전술한 것과 같은 수단은, 이 크로스 커플형 앰프의 P측 공통 소스단자를, 제1의 전압으로부터 이것보다도 낮은 제4의 전압으로 내리는 것으로 실현할 수 있다. 또한, 상기 제1의 시간은, 상기 반도체 기억장치에 끌리 차지 커맨드가 입력된 시간보다도 느린 시간으로 할 수 있다. 즉, 워드선이 비활성화하는 직전의 짧은 시간에, 축적노드로의 과잉 기록전하를 방전하여, 기록전하의 조정을 행한다.

또, 전술한 수단은, 소위 센스 앰프의 오버 드라이브와 조합해서 이용할 수도 있다. 이 경우, 워드가 활성화된 후, P측 공통 소스선을 제1의 전압보다도 높은 제5의 전압으로 구동하고, 그 후, 제1의 전압으로 구동하며, 또 그 후, 제4의 전압으로 구동하게 된다.

또한, 본 발명에 의한 반도체 기억장치는, 각각 MOS 트랜지스터와 커패시터를 포함하고, 이 MOS 트랜지스터의 게이트가 선택 단자로 되며, 소스 및 드레인의 한쪽이 입출력 단자로 되고, 소스 및 드레인의 다른쪽이 커패시터의 축적노드에 접속되는 복수의 메모리 셀과, 복수의 메모리 셀의 선택단자에 각각 접속되는 복수의 워드선과, 복수의 메모리 셀의 입출력 단자에 각각 접속되는 상보 비트선과, 복수의 메모리 셀의 커패시터에서, 축적노드의 반대측의 단자에 각각 접속되는 복수의 플레이트선과, 상보 비트선의 일단에 접속되어, 상보 비트선의 전압차이를 증폭해서 래치를 행하는 센스 앰프를 구비하고 있고, 또, 복수의 워드선 중 어느 하나의 워드선이 활성화된 후, 센스 앰프가 활성화되어, 상보 비트선의 중 한쪽의 비트선이 제1의 전압으로 증폭되고, 다른쪽의 비트선이 제1의 전압보다도 낮은 제2의 전압으로 증폭된 단계에서, 상기 어느 하나의 워드선에 대응하는 플레이트선을, 제2의 시간에서 제6의 전압으로부터 이것보다도 높은 제7의 전압으로 구동하는 수단과, 제1의 전압으로 증폭된 비트선을, 제1의 시간에서 제1의 전압보다도 낮은 제3의 전압으로 내리고, 그 후에 상기 어느 하나의 워드선을 비활성화하는 수단을 갖는 것으로 되어 있다.

즉, 특히, 플레이트선을 구동하는 플레이트 구동방식의 DRAM 메모리 셀의 경우에, 지금까지 기술한 것과 같은 과잉 기록 전하가 발생하기 쉽다. 이러한 과잉 기록전하는, 미세화에 있어서 디바이스의 신뢰성을 손상하는 요인이 되지만, 전술한 것과 같은 수단을 설치하는 것에 의해, 이러한 문제를 해결할 수 있다.

본 발명에 의한 반도체 기억장치는, 각각 MOS 트랜지스터와 커패시터를 포함하고, 이 MOS 트랜지스터의 게이트가 선택 단자로 되며, 소스 및 드레인의 한쪽이 입출력 단자로 되고, 소스 및 드레인의 다른쪽이 커패시터의 축적노드에 접속되는 복수의 메모리 셀과, 복수의 메모리 셀의 상기 선택단자에 각각 접속되는 복수의 워드선과, 복수의 메모리 셀의 입출력 단자에 각각 접속되는 상보 비트선과, 상보 비트선의 일단에 접속되어, 상보 비트선의 전압차이를 증폭해서 래치를 행하는 센스 앰프와, 센스 앰프에 접속되는 P측 공통 소스선 및 N측 공통 소스선과, P측 공통 소스선을 구동하는 제1, 제2 및 제3의 드라이버를 구비하고 있고, 상기 센스 앰프는, 크로스 커플형의 앰프로 되어 있으며, 상기 제1의 드라이버는 제1의 전원 전압에 접속되고, 상기 제2의 드라이버는 제4의 전원전압에 접속되며, 상기 제3의 드라이버는 제5의 전원전압에 접속되는 것으로 되어 있다.

여기에서, 상기 제4의 전원전압은, 상기 제1의 전원전압의 절반보다도 낮은 전압으로 할 수 있다. 즉, 제1의 전원전압은, 예컨대 상보 비트선의 'H'측의 기록전압 VDL이며, 제4의 전원전압은, 전술한 과잉 기록전하의 방전을 행할 때 이용되지만, 실용상, 이 전압을 VDL/2보다도 낮은 값으로 함으로써, 'H'측의 비트선의 전압을 고속으로 내리고, 축적노드에 존재하는 과잉 기록전하를 고속으로 방전하면 좋다. 또, 실제상은, 크로스 커플형 앰프의 P채널형 MOS 트랜지스터의 문턱치전압의 영향으로, 이 문턱치전압 이하로는 비트선의 전압이 내려가지 않기 때문에, 제4의 전원전압은, 접지전압 VSS(OV) 등으로 해도 문제는 없다. 또한, 상기 제5의 전원전압은, 예컨대, 센스 앰프의 오버 드라이브용의 전압으로 되어 있다.

이하, 본 발명의 실시형태를 도면에 의거해서 상세히 설명한다. 또, 실시형태를 설명하기 위해 전체 도면에 있어서, 동일한 부재에는 원칙으로서 동일한 부호를 붙이고, 그 반복의 설명은 생략한다.

도 1은, 본 발명의 일실시형태에 의한 반도체 기억장치에 있어서, 그 칩 구성의 일례를 나타내는 평면도이며, (a)는 칩 전체의 구성 예, (b)는 (a)에서의 메모리 블록의 구성 예를 나타내는 것이다.

도 1에 나타내는 반도체 기억장치는, 플레이트 구동방식의 DRAM으로 되어 있다. 그 메모리 칩(CHIP) 전체의 구성은, 예컨대 도 1의 (a)에 나타내는 바와 같이, 제어회로(CNTL)와, 입출력 회로(DQC)와, 메모리 블록(BLK)으로 크게 나누어진다. 제어회로(CNTL)에는, 클록, 어드레스, 제어신호가 메모리 칩(CHIP) 외부에서 입력되어, 메모리 칩(CHIP)의 동작모드의 결정이나 어드레스의 프리 디코드 등이 행하여진다. 입출력 회로(DQC)는 입출력 버퍼 등을 구비하고, 메모리 칩(CHIP) 외부로부터 라이트 데이터가 입력되어, 메모리 칩(CHIP) 외부로 리드 데이터를 출력한다.

메모리 블록(BLK)에는, 예컨대 도 1의 (b)에 나타내는 바와 같이, 복수의 어레이 모양으로 배치된 메모리 어레이(ARY)가 배치되고, 그 주위에는 센스 앰프 열(SAA), 서브 워드 드라이버 열(SWDA), 플레이트 드라이버 열(PLDA), 크로스 애리어(XP)가 배치된다. 또한, 메모리 블록(BLK)의 외주(外周)에는, 센스 앰프 열(SAA)과 평행하게 열 디코더(YDEC) 및 메인 앰프 열(MAA)이 배치되고, 서브 워드 드라이버 열(SWDA)과 평행하게 행 디코더(XDEC) 및 어레이 제어회로(ACC)가 배치된다.

도 2는, 도 1의 반도체 기억장치에 있어서, 그 메모리 어레이와 센스 앰프 열의 구성의 일례를 나타내는 회로도이다. 도 2에 나타내는 바와 같이, 메모리 어레이(ARY)는, 복수의 메모리 셀(MC)로 구성되어 있다. 메모리 셀(MC)은, DRAM 메모리 셀로 이루어져 있고, 1개의 MOS 트랜지스터(메모리 셀 트랜지스터) 및 1개의 커패시터(Cs)로 구성되며, MOS 트랜지스터의 한쪽의 소스 또는 드레인이, 비트선 BLT 또는 비트선 BLB에 접속되고, 다른쪽의 소스 또는 드레인이 축적노드(SN)에 접속되며, 게이트가 워드선(WL)에 접속되어 있다.

커패시터(Cs)의 한쪽의 단자는 축적노드(SN)에 접속되고, 다른쪽의 단자는 워드선(WL)과 병행하게 배선된 플레이트선(PL)에 접속된다. 또, 비트선 BLT와 비트선 BLB는, 비트선쌍(상보 비트선)(BLT/B)으로서 기능한다.

여기에서, 통상의 DRAM과 달리, 플레이트선(PL)을 1개의 워드선(WL)마다 분할해서 워드선(WL)과 병행하게 배선하고, 워드선(WL)이 활성화된 메모리 셀(MC)의 플레이트선(PL)만을 구동하는 구성으로 하면 좋다. 이것이 의해, 플레이트선(PL)의 구동에 따른 다른 비선택 상태의 메모리 셀(MC)로의 디스터브를 저감하면서, 축적노드(SN)의 전압을 증가할 수 있는 효과가 얻어진다. 또한, 메모리 어레이(ARY)에는, 전술한 메모리 셀(MC)과 같은 구성의 더미 메모리 셀(DMC)이 포함되어 있다. 더미 메모리 셀(DMC)은, 더미 워드선(DWL) 및 더미 플레이트선(DPL)에 접속되어, 판독시의 참조신호 발생에 이용된다.

도 3은, 도 1의 반도체 기억장치에 있어서, 그 센스 앰프 열과 서브 워드 드라이버 열과 플레이트 드라이버 열의 상세한 배치관계의 일례를 나타내는 평면도이다. 도 3에 나타내는 바와 같이, 센스 앰프 열(SAA)내의 센스 앰프(SA)는, 메모리 어레이(ARY)에 대해서 상하로 교대 배치되고, 상하의 메모리 어레이(ARY)내의 비트선쌍(BLT/B)에 공통 접속된다.

마찬가지로, 서브 워드 드라이버 열(SWDA)내의 서브 워드 드라이버(SWD)와 플레이트 드라이버 열(PLDA)내의 플레이트 드라이버(PLD)도, 각각, 메모리 어레이(ARY)에 대해서 좌우로 교대 배치되고, 좌우의 메모리 어레이(ARY)내의 워드선(WL)과 플레이트선(PL)에 공통 접속된다. 이렇게 배치하는 것에 의해, 서브 워드 드라이버 열(SWDA)내 및 플레이트 드라이버 열(PLDA)내에 있어서, 서브 워드 드라이버(SWD) 사이 및 플레이트 드라이버(PLD) 사이의 피치를, 메모리 어레이(ARY)내의 워드선(WL) 사이 및 플레이트선(PL) 사이의 피치의 2배로 넓힐 수 있다. 따라서, 미세화가 용이해진다.

도 4는, 도 2의 반도체 기억장치에 있어서, 그 센스 앰프 열의 상세한 구성의 일례를 나타내는 회로도이다. 도 4에 나타내는 바와 같이, 센스 앰프 열(SAA)에는 복수의 센스 앰프(SA)가 배치되고, 각 센스 앰프(SA)는, 인접하는 양측의 메모리 어레이(ARY)의 비트선쌍(BLT/B)에 공통 접속되어 있다. 그리고, 각 센스 앰프(SA)내에는, 트랜스퍼 게이트(TGC)와, 프리 차지회로(PCC)와, 크로스 커플·앰프(CC)와, 판독·기록포트(IOP)가 포함되어 있다.

트랜스퍼 게이트(TGC)는, 센스 앰프 분리신호(SHR 신호)가 활성화되었을 때 센스 앰프(SA)와 메모리 어레이(ARY) 사이를 접속하는 회로이다. 프리 차지회로(PCC)는, 비트선 프리 차지신호(BLEQ 신호)가 활성화되었을 때 쌍이 되는 비트선 BLT, BLB의 사이를 이퀄라이즈 하고, 비트선 프리 차지레벨(VBLR)로 프리 차지한다. 비트선 프리 차지레벨(VBLR)은, 통상, 비트선 진폭의 전압 VDL(칩 외부로부터의 전원전압(VCC)과 같은 레벨이거나 또는 그것을 강압한 레벨)의 중간점 VDL/2로 설정된다.

크로스 커플·앰프(CC)는, 비트선 BLT, BLB 상에 메모리 셀(MC) 및 더미 메모리 셀(DMC)으로부터의 미소한 판독신호가 발생한 후에, P측 공통 소스선(CSP)을 전압 VDL로 구동하고, N측 공통 소스선(CSN)을 접지전압 VSS로 구동하며, 비트선 BLT와 비트선 BLB 중 전압이 높은 쪽을 전압 VDL로, 낮은 쪽을 접지전압 VSS로 증폭하고, 증폭된 전압을 래치하는 회로이다. 판독·기록포트(IOP)는, 열 선택선(YS)이 활성화되었을 때 로컬 IO선(LIO선)(LIOT/B)과 비트선쌍(BLT/B)을 접속하는 회로이다. 또, LIO선(LIOT/B)은, 비선택 센스 앰프 열(SAA)에서의 전류소비를 방지하기 위해서, 대기시에는 프리 차지레벨로 유지된다.

도 5는, 도 1의 반도체 기억장치에 있어서, 그 크로스 에리어의 구성의 일례를 나타내는 회로도이다. 크로스 에리어(XP)는, SHR신호 드라이버(SHD)와, LIO선 프리 차지회로(REQ)와, 리드 라이트 게이트(RGC)와, CS선 드라이버(CSD)와, CS선 프리 차지회로(SEQ)와, BLEQ신호 드라이버(EQD)와, FX선 드라이버(FXD)와, PX선 드라이버(PXD)를 포함하고 있다.

SHR 신호 드라이버(SHD)는, SHR신호의 상보신호(SHRB)가 입력되어, 그 반전 신호를 출력한다. LIO선 프리 차지회로(REQ)는, 리드 라이트 인에이블 신호(RWE)가 비활성 상태의 VSS레벨일 때에, LIO선(LIOT/B)을 전압 VPC로 프리 차지한다. 리드 라이트 게이트(RGC)는, 리드 라이트 인에이블 신호(RWE)가 활성상태의 전압 VCL(외부 VCC레벨과 동일하거나 또는 그것을 강압한 레벨에서 주변회로용 전원전압으로서 사용된다)일 때에 LIO선(LIOT/B)과 메인 IO선(MIOT/B)을 접속하는 회로이다.

CS선 드라이버(CSD)는, N측 센스 앰프 인에이블 신호(SAN)가 활성상태일 때에, N측 공통 소스선(CSN)을 접지전압 VSS로 구동하고, 제1의 P측 센스 앰프 인에이블 신호(SAP1B)이 활성상태(VSS 레벨)일 때에, P측 공통 소스선(CSP)을 전압 VDL(비트선의 'H'레벨)로 구동하고, 제2의 P측 센스 앰프 인에이블 신호(SAP2)가 활성상태(VCL 레벨)일 때에, P측 공통 소스선(CSP)을 전압 VSP로 구동하는 회로이다.

또, 여기에서는, P측 공통 소스선(CSP)을 전압 VDL로 구동하는 회로로서 P채널 MOS 트랜지스터를, 전압 VSP로 구동하는 회로로서 N채널 MOS 트랜지스터를 사용하고 있다. 전압 VSP로 구동하는 회로는, 후술하지만 기록시의 'H'측의 비트선 전압을 일시 내리는 것이므로 N채널 MOS 트랜지스터로 하고 있다. 이것에 의해, 고속으로 비트선 전압을 내리는 것이 가능해진다. 단, 이것을 P채널 MOS 트랜지스터로 구성하는 것도 가능하다.

이와 같이, 본 발명에서는, CS선 드라이버(CSD) 내에, 센스 앰프(SA)가 활성화 상태에서의 P측 공통 소스선(CSP)의 레벨을, 전압 VDL과 전압 VSP의 2종류로 설정 가능한 기능을 구비한 것을 특징으로 하고 있다. 이때에, CS선 드라이버(CSD)를 크로스 에리어(XP)에 배치하면, 센스 앰프(SA)의 면적이 증가하지 않는다는 이점이 있다.

CS선 프리 차지회로(SEQ)는, BLEQ 신호가 활성화되었을 때에 P측, N측 공통 소스선(CSP, CSN)을 VDL/2로 프리 차지하는 회로이다. BLEQ 신호 드라이버(EQD)는, 프리 차지신호(BLEQ)의 상보신호(BLEQB)가 입력되어, 그 반전 신호를 출력한다. FX 선 드라이버(FXD)는, 신호 FXB가 입력되어, 그 상보신호를 서브 워드 드라이버 선택선 FX(FX선)로 출력한다.

PX선 드라이버(PXD)는, 전압 VCL 진폭의 플레이트 타이밍 신호(PXS)가 입력되어, 플레이트 제어선(PX선)으로 전압을 출력한다. PX선은, 플레이트선(PL)을 구동하기 위한 배선이다. 플레이트 타이밍 신호(PXS)가 비활성의 경우, PX선에는, 통상시의 플레이트 전압 VPH가 출력된다. 한편, 플레이트 타이밍 신호(PXS)가 활성화된 경우, PX선에는, 플레이트 전압 VPL이 출력된다. 또, PX선 드라이버(PXD)를 크로스 에리어(XP)에 배치하는 것에 의해, PX선의 지연을 저감하는 것이 가능하다.

다음에, 지금까지 설명한 것과 같은 반도체 기억장치의 동작에 대해서 설명한다. 도 6은, 도 1의 반도체 기억장치에 있어서, 그 동작의 일례를 나타내는 동작 과정도이다.

도 6에 나타내는 바와 같이, 메모리 칩 외부로부터 뱅크 활성화 커맨드(ACT)가 입력되면, 우선, 어드레스로 지정된 센스 앤프 열(SAA)에 있어서 SHR 신호의 한 쪽과 BLEQ 신호가 비활성화된다. 또한, 활성화 상태에서 VPP 레벨이었던 더미 셀(DMC)의 더미 워드선(DWL1)이 비활성화되어, VKK 레벨로 복귀한다. 여기서 VKK는, 부(負)전원발생 회로에 의해 발생된 워드선의 저레벨측의 전원전압이다. 이렇게, 비활성화시의 워드선 레벨을 접지전압 VSS보다도 낮게 하는 것에 의해, 메모리 셀 트랜지스터의 문턱치전압을 낮게 설정할 수 있고, 워드선의 'H'측의 레벨 VPP를 저감할 수 있다.

그 후, 행 디코더(XDEC)에 있어서 메인 워드선(MWLB)이 전압 VKK로 내려가고, 어레이 제어회로(ACC)에 있어서 FX선이 활성화되면, 선택된 워드선(WLO)이 전압 VPP로 활성화된다. 워드선(WLO)에 의해 선택된 메모리 셀(MC)에 있어서는, 메모리 셀 트랜지스터가 도통하여, 비트선 BLT 상에 신호가 판독된다. 도 6에서는, 메모리 셀(MC)에 미리 접지전압 VSS가 기록되고 있고, 'L'의 신호가 발생한 예를 나타내고 있다. 또한, 워드선(WLO)의 활성화와 동시에 더미 워드선(DWL1)도 활성화되어, 프리 차지전압(VBLR)이 기록되어 있었던 더미 메모리 셀(DMC)로부터 비트선 BLB 상에 참조신호가 발생한다.

또, 이때, 선택된 메모리 셀(MC)의 플레이트선(PLO)과, 그것에 대응하는 더미 메모리 셀(DMC)의 플레이트선(DPL1)이 전압 VPH로부터 전압 VPL로 하강된다. 이렇게, 플레이트선(PLO)을 구동하면, 선택된 메모리 셀(MC)의 축적노드(SN)와 더미 메모리 셀(DMC)의 더미 축적노드(DSN)는, 커패시터(Cs)를 통한 커플링에 의해 전압 레벨이 내려가기 때문에, 각각의 축적전하가 고속으로 비트선 BLT, BLB 상에 판독된다. 여기에서, 전압 VPH는, 전압 VDL과 접지전압 VSS의 거의 중간 전압으로 해 놓으면, 대기시에 메모리 셀의 용량절연막에 인가되는 전압이 작아지므로, 신뢰성이 높아진다.

그 후, 센스 앤프(SA)에 있어서, P측 공통 소스선(CSP)을 전압 VDL로, N측 공통 소스선(CSN)을 접지전압 VSS로 구동하고, 비트선 BLT, BLB 상의 전압차이를 증폭한다. 이 상태에서, 메모리 칩은 리드 커맨드(RD) 또는 라이트 커맨드(WRT)를 받아들일수 있다. 도 6에서는 라이트 커맨드(WRT)가 입력된 경우를 나타내고 있다. 그리고, 선택된 어드레스의 열 선택선(YS)이 활성화되어, LIO선(LIOT/B)으로부터, 라이트 데이터가 기록된다. 여기에서는, 비트선 BLT가 'H'로 구동되는 반전 기록시의 과정을 나타내고 있다.

메모리 셀 트랜지스터는, N채널 트랜지스터이므로, 문턱치전압을 VT라 하면, 축적노드(SN)에 기록할 수 있는 최대의 전압은 VPP-VT가 된다. 본 발명의 메모리 칩에서는, 메모리 셀 트랜지스터의 게이트 산화막을 박막화하기 위해서, 워드선의 'H'레벨 전압 VPP를, 전원전압 VDD(예를들면 1.8V) 정도까지 내리고 있다. 또한, 메모리 셀 트랜지스터는 미세한 트랜지스터를 이용하고 있고, 개수도 많기 때문에, 문턱치전압(VT)의 변동이 1V 가깝게 매우 크고, 예컨대 설계 중심값을 0.7V로 한 경우, 최소값은 0.2V, 최대값은 1.2V가 된다.

그렇게 하면, 비트선 전압 VDL을 일례로서 1.3V로 한 경우, 문턱치전압(VT)이 낮은 메모리 셀(LVT-ce11)에서는 VPP-VT=1.6V이므로 메모리 셀 트랜지스터가 온하고 있고, 축적노드(SN)에 VDL=1.3V를 기록할 수 있다. 한편, 문턱치전압(VT)이 중간 정도의 메모리 셀(MVT-ce11), 문턱치전압(VT)이 높은 메모리 셀(HVT-ce11)에서는, 증폭의 도중에 컷오프(cut off) 상태가 되어, 각각 1.1V, 0.6V까지 밖에 기록되지 않는다. 즉, 기록시의 축적노드(SN)의 전압은, 메모리 셀 트랜지스터의 문턱치전압(VT)에 대응해서 0.6V로부터 1.3V까지의 변동을 갖는다.

이 상태에서, 프리 차지 커맨드(PRC)가 입력되었을 때에, 선택된 메모리 셀(MC)의 플레이트선(PLO)과 더미 메모리 셀(DMC)의 더미 플레이트선(DPL1)을 전압 VPL로부터 전압 VPH로 복귀시키면, 각각의 축적노드(SN, DSN)의 전압은, 커패시터(Cs)로부터의 커플링을 받아,  $\Delta PL = VPH - VPL$  분 만큼 상승한다. 이때에, 'H'이 기록된 메모리 셀(MC)에서는, 메모리 셀 트랜지스터가 컷오프 하거나 컨덕턴스가 높은 상태이기 때문에,  $\Delta PL$ 의 전압상승분이 유지되지만, 'L'이 기록된 메모리 셀(MC)에서는 메모리 셀 트랜지스터가 충분히 온 상태이기 때문에, 곧 접지전압 VSS로 복귀한다. 따라서, 메모리 셀(MC)의 축적노드(SN)의 축적 전하량을  $\Delta PL$  만큼 증가할 수 있다.

여기에서,  $\triangle PL$ 을, 가장 문턱치전압(VT)의 높은 메모리 셀(HVT-ce11)의 기록전압이 VDL까지 상승하도록 예컨대 0.7V로 설정하면, 모든 메모리 셀(MC)이 1.3V 이상으로 기록되기 때문에, 다음 사이클에서의 관독 신호량이나 리텐션 시간의 마진을 넓힐 수 있다. 그렇지만, 문턱치전압(VT)이 낮은 메모리 셀(LVT-ce11)에서는, 원래 VDL=1.3V까지 기록되어 있었으므로, 더 전압이  $\triangle PL$ 분 만큼 상승하면 2.0V까지 높아진다. 이대로 워드선을 비활성화하면, 대기시에 메모리 셀 트랜지스터에 높은 전압이 인가된 그대로 되어, 디바이스의 신뢰성이 저하한다.

그래서, 본 발명에서는 다음과 같은 방법으로 문턱치전압(VT)이 낮은 메모리 셀(MC)만을 선택적으로 방전하여, 워드선 비활성시의 축적노드(SN)로의 기록전압을 일치시키는 것으로 디바이스의 신뢰성을 높인다. 즉, 예컨대 프리 차지 커멘드 (PRC)의 입력에 이어서 플레이트선(PL)을 구동한 후의 타이밍에서, 도 5에서 기술한 CS선 드라이버(CSD)에 의해 P측 공통 소스선(CSP)을 전압 VSP까지 내리는 것에 의해, 'H'측의 비트선 전압을 VDP(예컨대 0.7V)까지 내린다.

그렇게 하면, 문턱치전압(VT)이 낮은 메모리 셀(MC)에서의 메모리 셀 트랜지스터에서는, 실효 게이트 전압 VGS-VT가  $(1.8-0.7)-0.2=0.9V$ 가 되고, 강하게 온하기 때문에, 축적노드(SN)의 전하가 급속히 방전된다. 한편, 문턱치전압(VT)이 중간정도의 메모리 셀에서는, VGS-VT가 0.4V가 되고, 약하게 온하기 때문에 방전은 완만하고, 문턱치전압(VT)이 높은 메모리 셀에서는, VGS-VT가 부(負)이기 때문에 컷오프의 상태가 유지된다.

따라서, 도 6에 나타내는 바와 같이, 문턱치전압(VT)이 낮은 메모리 셀(LVT-ce11)에서는, 과잉으로 기록된 전하의 방전에 의해 지나치게 오른 전압이 내려가고, 문턱치전압의 중간 정도의 메모리 셀(MVT-ce11) 및 높은 메모리 셀(HVT-cell)에서는, 전압이 거의 유지되기 때문에, 문턱치전압(VT)의 변동보다도 기록전압의 변동이 작아진다. 그리고, 이러한 방전 동작의 종료 후는, 워드선(WLO)를 하강해서, BLEQ 신호 및 SHR 신호를 다시 활성화시켜, 비트선쌍(BLT/B)을 프리 차지한다.

이상과 같이, 본 발명의 구성 및 동작을 이용하면, 플레이트 구동에 의해 메모리 셀에 기록되는 전하량을 증가하고, 리텐션 특성이나 동작 속도를 개선하는 동시에, 과잉 기록전하의 방전을 행하는 조정수법에 의해, 문턱치전압의 변동이 큰 경우라도 기록 전하량의 변동을 저감할 수 있다. 이것에 의해, 메모리 셀 트랜지스터에 고전압이 장시간 인가되는 것을 방지하는 것이 가능해지기 때문에, 디바이스의 신뢰성이 향상한다. 또한, 워드선 전압을 저감할 수 있기 때문에, 메모리 셀 트랜지스터의 게이트 산화막을 박막화할 수 있어, 미세화가 가능해진다. 그리고, DRAM 칩의 대용량화 또는 칩 사이즈의 저감에 의한 제조 코스트의 저감을 실현할 수 있다.

그런데, 지금까지의 설명에 있어서는, CS선 드라이버(CSD) 내에, 센스 앰프(SA)가 활성화 상태에서의 P측 공통 소스선 (CSP)의 레벨을, 전압 VDL과 전압 VSP의 2종류로 설정하는 예를 나타냈지만, 부가해서도 7과 같이, 오버 드라이브 센스 방식을 조합하는 것도 가능하다. 도 7은, 도 5의 크로스 에리어에 있어서, 그 구성을 변형한 일례를 나타내는 회로도이다.

도 7에 나타내는 크로스 에리어(XP)는, 전술한 플레이트 구동방식과 오버 드라이브 센스방식을 조합해서 이용할 때의 회로 구성 예로 되어 있고, 도 5에 나타낸 회로와 비교하여, CS선 드라이버(CSD)의 구성이 다르게 되어 있다. 즉, 도 7에 나타내는 CS선 드라이버(CSD)에서는, 초기의 P측 센스 앰프 인에이블 신호(SAPOP)가 활성상태일 때에, P측 공통 소스선 (CSP)을 일시적으로 오버 드라이브 전압 VOD로 구동하기 위한 PMOS 트랜지스터가 추가되어 있다. 전압 VOD는, 최종적인 비트선의 'H'레벨 전압 VDL보다도 높은 전압이며, 센스 앰프(SA)의 증폭동작을 고속화하기 위한 것이다. 또, 이렇게 하여 드라이버의 종류를 증가시켜도, CS선 드라이버(CSD)를 크로스 에리어(XP)에 배치하고 있기 때문에, 센스 앰프의 면적을 증가하지 않고, 미세화가 가능해진다는 이점이 있다.

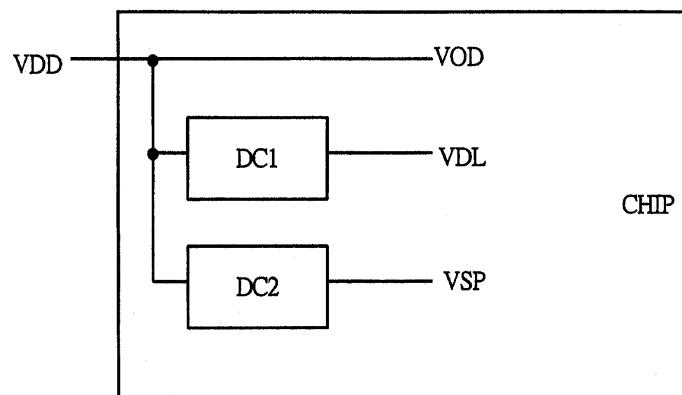

도 8은, 도 7의 크로스 에리어에 있어서, CS선 드라이버에서 사용하는 전압의 발생방식의 일례를 나타내는 개략도이다. 오버 드라이브 전압 VOD는, 최종적인 비트선의 'H'레벨 전압 VDL보다도 높은 전압이기 때문에, 예컨대 도 8에 나타내는 바와 같이, 메모리 칩(CHIP) 외부로부터 공급되는 외부 전원전압 VDD를 그대로 이용할 수 있다. 비트선의 'H'레벨 전압 VDL은, 외부 전원전압 VDD를 강압회로(DC1)에서 강압하여 발생한다. 전압 VSP는, 그 값으로서, 도 6에서 기술한 방전 동작시의 비트선 전압 VDP보다도, 크로스 커플 · 앰프(CC)에서의 PMOS 트랜지스터의 문턱치전압분 만큼 낮게 할 필요가 있다. 이것 때문에, 강압회로(DC2)를 이용해서 비트선 전압의 절반 VDL/2보다도 낮은 값으로 강압하거나 또는 접지전압 VSS를 그대로 이용하는 것이 바람직하다.

이렇게, 플레이트 구동방식과 오버 드라이브 센스방식을 조합시킨 경우는, 예컨대 도 9에 나타내는 것과 같은 동작이 된다. 도 9는, 도 1의 반도체 기억장치에 있어서, 도 7의 크로스 에리어를 이용한 경우의 동작의 일례를 나타내는 과정도이다. 도 9에 나타내는 동작 과정은, 전술한 도 6의 동작 과정과 달리, 센스 앰프(SA)에 의한 증폭의 초기에 P측 공통 소스선

(CSP)을 일시적으로 오버 드라이브 전압 VOD로 구동하고 있다. 그리고, 비트선 쌍(BLT/B)이 충분히 증폭된 후, P측 공통 소스선(CSP)은 전압 VDL로 구동된다. 이러한 구동을 행하면, 판독 동작시 및 재기록 동작시에 비트선의 증폭 동작이 고속화된다. 이것 이후의 동작은 도 6과 같다.

도 10은, 도 6에서의 동작을 회로 시뮬레이션으로 재현한 것이며, (a)는 그 동작에서의 주요부의 파형도, (b)는 그 동작에서의 문턱치전압과 기록전압의 관계를 나타내는 그래프이다. 도 10의 (a)에서는, 도 6에서 설명한 바와 같이, 워드선(WL)을 1.8V로 활성화하고, 플레이트선(PL)을 0.7V 내린 상태에서, 비트선 BLT, BLB 상에 신호가 발생하고 있다. 여기에서, 비트선 BLT, BLB의 신호 증폭을 개시하고, 이어서 반전 기록을 행하면, 문턱치전압(VT)의 차이에 의해 축적노드(SN)로의 기록전압의 변동이 발생한다.

그 후, 플레이트선(PL)의 전압을 상승시키면, 'H'가 기록된 메모리 셀(MC)에 서의 축적노드(SN)의 전압은 상승하지만, 'L' 측의 더미 메모리 셀(DMC)에서의 더미 축적노드(DSN)의 전압은, 일단 상승 후, 바로 접지전압 VSS로 복귀한다. 'H'가 기록된 메모리 셀(MC)에 있어서는, DC로 나타낸 기간, 비트선 BLT의 전압을 내리는 것으로, 과잉으로 기록된 전하를 방전 시킨다. 이것에 의해, 최종적인 기록전압의 변동이 저감되고 있다.

도 10의 (b)에 나타내는 그래프는, 횡축(橫軸)에 메모리 셀 트랜지스터의 문턱치전압(VT)을 나타내고, 종축(縱軸)에, 축적노드(SN)에서의, 플레이트 구동 직후의 기간에서 전압 VP와 방전 동작을 7ns 행하여 워드선을 비활성화한 직후의 기간에서의 전압 VS를 나타내고 있다. 문턱치전압(VT)의 변동 범위를 0.2~1.2V로 가정하면, 도 10의 (b)에 나타내는 바와 같이, 플레이트 구동 직후의 기간에서 축적노드(SN)의 최대전압 VP는 2.0V 가까이 되고, 변동  $\Delta$ VP는 0.80V가 된다. 즉, 방전 동작 없음에서는, 0.80V분의 과잉전압이 메모리 셀 트랜지스터에 인가된다.

한편, 방전 동작을 행한 경우, 최종적인 축적노드(SN)의 전압은, 전압 VS까지 방전되기 때문에, VT=0.7V 부근에서 최대값 1.3V를 취하지만, 변동은  $\Delta$ VS=0.34V가 되어, 메모리 셀 트랜지스터에 인가되는 과잉전압이 43%까지 억제되고 있다. 이것에 의해, 메모리 셀 트랜지스터의 신뢰성이 향상하고, 미세화가 용이해진다.

도 11 및 도 12는, 도 1의 반도체 기억장치에 있어서, 도 6을 변형한 동작의 일례를 나타내는 동작 파형도이다. 도 11에 나타내는 동작은, 도 6에 나타낸 동작에 대해서, 플레이트선(PL)을 전압 VPL로부터 전압 VPH로 상승시키는 동작과, P측 공통 소스선(CSP)의 전압 VSP로의 구동을 동시에 행한 경우를 나타내고 있다. 도 6에 있어서는, 플레이트선(PL)의 전압을 상승시킨 직후에 단시간이면서, 축적노드(SN)의 전압이 상승하고, 메모리 셀 트랜지스터에 고전압이 인가된다.

한편, 도 11에 나타내는 동작에서는, 플레이트선(PL)의 구동에 의한 축적노드(SN)의 전압상승과, 문턱치전압(VT)이 낮은 메모리 셀로부터의 과잉전하의 방전이 동시에 일어나기 때문에, 축적노드(SN)에 피크 전압이 발생하지 않는다. 따라서, 메모리 셀 트랜지스터로의 고전압의 인가를 억제하는 것이 가능해지고, 디바이스의 신뢰성을 더 향상시킬 수 있어, 미세화가 용이해진다.

또한, 도 12에 나타내는 동작은, 도 11의 동작에 대해서, 플레이트선(PL)을 전압 VPH로부터 전압 VPL로 하강시키는 타이밍을, 센스 앰프 활성화 후까지 지연시킨 경우를 나타내고 있다. 이 경우, 비트선 쌍(BLT/B)으로의 신호 판독시에 플레이트선(PL)이 일정 전압 그대로이므로, 워드선 활성화 후의 신호발생은 약간 늦지만, 센스 앰프 증폭시의 참조 전압으로서 비트선 프리 차지전압(VBLR)을 그대로 이용할 수 있다. 이것에 의해, 더미 메모리 셀(DMC)이 불필요해지고, 칩 사이즈를 저감하는 것이 가능해진다. 또한, 도 12에 나타내는 동작은, 전술한 플레이트선(PL)의 타이밍 변경에 부가해서, 센스 앰프 활성화시에 P측 공통 소스선(CSP)을 일시적으로 오버 드라이브 전압 VOD로 구동하여, 센스 동작을 고속화한 경우를 나타내고 있다.

도 13은, 도 1의 반도체 기억장치에 있어서, 그 메모리 어레이의 레이아웃의 일례를 나타내는 도면이며, (a)는 트랜지스터의 활성영역으로부터 축적노드까지의 레이아웃, (b)는 플레이트 전극으로부터 플레이트선까지의 레이아웃을 나타내는 것이다. 도 14는, 도 13의 레이아웃에 있어서, 그 A-A'간의 단면구성의 일례를 나타내는 도면이다. 도 13에 나타내는 레이아웃은, 복수의 워드선(WLO~4)과 복수의 인접한 비트선 쌍(BLT/B)을 포함하고, 이 비트선 쌍(BLT/B)에 의해 상보 동작을 행하는 구성으로 되어 있다. 또, 본 레이아웃은, 비트선 쌍(BLT/B)이 1개의 워드선과 교차하고 있어, 2교점 메모리 어레이라 불리고 있다.

도 13의 (a)에 나타내는 레이아웃에서는, 복수의 활성영역(ACT)이 비트선과 평행하게 형성되고, 각 활성영역(ACT) 상에는, 2개의 워드선이 연신(延伸)하고 있다. 각 활성영역(ACT) 내에서는, 이 2개의 워드선의 각각을 게이트로 하는 2개의 메

모리 셀 트랜지스터가 형성된다. 이 2개의 메모리 셀 트랜지스터의 소스/드레인의 일단은, 공통의 비트선 콘택트(BC)에 의해 비트선에 접속되고, 타단은 각각 다른 축적노드 콘택트(SC)에 의해, 각각 다른 축적노드(SN)에 접속된다. 또, 각 축적노드(SN)의 비트선 방향의 횡폭은, 예컨대 인접하는 워드선 2개분에 겹치는 정도의 크기로 할 수 있다.

도 13의 (b)에 나타내는 레이아웃은, 도 13의 (a)의 복수의 축적노드(SN)와 1대1로 대응하는 형태로 복수의 플레이트 전극(PLE)이 형성되고, 또한, 복수의 워드선(WLO~4)과 1대1로 대응하는 형태로 복수의 플레이트선(PLO~4)이 형성되어 있다. 즉, 복수의 플레이트선(PLO~4)과 복수의 플레이트 전극(PLE)의 레이아웃은, 도 13의 (a)에서의 복수의 워드선(WLO~4)과 복수의 축적노드(SN)의 레이아웃과 거의 동일형상의 레이아웃으로 할 수 있다. 이 경우, 각 플레이트 전극(PLE)의 비트선 방향의 횡폭은, 인접하는 플레이트선 2개분에 겹치는 정도의 크기로 되기 때문에, 각 플레이트 전극(PLE)은, 이 겹치는 어느 하나의 플레이트선에 플레이트 콘택트(PC)를 통해서 접속할 수 있다.

각 DRAM 메모리 셀은, 도 14에 나타내는 바와 같이, 반도체 기판(PW) 상에 형성된 N채널 트랜지스터(메모리 셀 트랜지스터)와, 비트선 BL의 상부에 설치된 스택 커패시터를 갖는 것으로 되어 있다. 도 14에 있어서는, 절연막(SiO<sub>2</sub>)에 의해 분리된 반도체 기판(PW) 내의 활성영역(ACT) 상에, 2개의 워드선(WL)이 배치되고, 이 2개의 워드선(WL)을 메모리 셀 트랜지스터의 게이트로 하며, 그 소스/드레인이 되는 N형 확산층 영역(N)이 반도체 기판(PW) 내에 설치되어 있다.

이 2개의 워드선(WL)간의 N형 확산층 영역(N)상에는, 콘택트(CB)가 배치되고, 그 상부에 비트선 콘택트(BC)가 배치된다. 비트선 콘택트(BC) 상에는, 워드선의 연신(延伸)방향과 직교하는 방향에 형성된 비트선 BL이 배치된다. 한편, 이 2개의 워드선(WL)의 외측의 N형 확산층 영역(N) 상에는, 각각, 콘택트(CB)가 배치되고, 그 상부에 축적노드 콘택트(SC)가 배치된다. 축적노드 콘택트(SC)의 상부에는, 충간 절연막(도시하지 않음)의 구멍의 내벽에 형성된 오목(凹)형(실린더 형상)의 축적노드(SN)가 배치되고, 축적노드(SN)의 내측에는 플레이트 전극(PLE)이 매립되어 있으며, 이것들이 용량절연막(CI1)을 사이에 두고 커패시터(Cs)를 구성한다.

플레이트 전극(PLE)의 상부에는, 플레이트 콘택트(PC)가 배치되고, 워드선 방향에 배선된 플레이트선(PL)과 접속된다. 도 14에서는, 깊은 구멍에 형성된 축적노드(SN) 전극의 내측만을 커패시터로서 이용하는 타입의 스택 커패시터를 나타내고 있다. 본 커패시터를 이용하면, 축적노드(SN)의 상부에서 플레이트 전극(PLE)을 분리할 수 있기 때문에, 분리 프로세스가 용이해지는 이점이 있다. 또한, 축적노드(SN) 전극의 내측뿐만 아니라, 내측과 외측 양쪽을 사용하는 타입의 커패시터로 할 수도 있다. 단, 이 경우는, 용량을 크게 할 수 있지만, 축적노드(SN) 전극의 하부에서 플레이트 전극(PLE)을 분리하지 않으면 안되기 때문에, 분리 프로세스가 복잡해지는 문제가 있다.

또, 도 13의 (b)에서는, 축적노드(SN)를 1개 걸러 콘택트를 취하는 것에 의해, 워드선(WLO~4)에 의해 선택되는 메모리 셀을 각각 대응한 플레이트선(PLO~4)에 접속하고 있다. 또한, 2교점 레이아웃에서는, 전술한 바와 같이, 축적노드(SN) 및 플레이트 전극(PLE)이 장방(長方) 형상으로 되어 있고, 2개분의 워드선(WL)의 영역에 걸쳐 있다.

따라서, 플레이트선(PL)을 거의 직선 모양으로 배치하고, 인접한 플레이트선(PL)에 교대로 콘택트를 배치하는 것으로, 용이하게 워드선(WL)마다 플레이트선(PL)을 분리할 수 있는 이점이 있다. 또한, MOS 트랜지스터의 활성영역(ACT)이 직선 모양의 패턴이 되기 때문에, 제작 프로세스가 용이해지는 이점이 있다. 이러한 것으로부터, 미세화가 용이하게 실현 가능해지고, 또한, 신호가 발생하는 비트선과 참조 비트선이 같은 어레이 내에 존재하므로, 노이즈를 저감할 수 있는 이점이 있다.

도 15는, 도 1의 반도체 기억장치에 있어서, 도 13과는 다른 메모리 어레이의 레이아웃의 일례를 나타내는 도면이며, (a)는 트랜지스터의 활성영역으로부터 축적노드까지의 레이아웃, (b)는 플레이트 전극으로부터 플레이트선까지의 레이아웃을 나타내는 것이다. 도 15에 나타내는 레이아웃은, 의사(疑似) 2교점 메모리 어레이(쿼터 피치 · 메모리 어레이)라 불리고, 복수의 워드선(WLO~4)과 복수의 비트선을 포함하며, 사이에 1개의 비트선을 둔 비트선쌍(BL/BLB)에 의해 상보 동작을 행하는 구성으로 되어 있다.

도 15의 (a), (b)에 나타내는 레이아웃에서는, 전술한 도 13의 활성영역(ACT)이 비트선에 대해서 경사지게 형성되고, 각 활성영역(ACT) 내의 2개의 축적노드 콘택트(SC)가, 비트선을 사이에 두도록 형성된다. 본 레이아웃을 이용하면, 축적노드(SN)의 형상을 거의 원형으로 할 수 있기 때문에, 미세화를 진행해도 커패시터 용량을 확보하는 것이 용이해지는 이점이 있다. 또한, 의사 2교점 메모리 어레이에 있어서도 신호가 발생하는 비트선과 참조 비트선이 같은 메모리 어레이 내에 존재하므로, 노이즈를 저감할 수 있는 이점이 있다.

도 16은, 도 1의 반도체 기억장치에 있어서, 도 13과는 다른 메모리 어레이의 레이아웃의 일례를 나타내는 도면이며, (a)는 트랜지스터의 활성영역으로부터 축적노드까지의 레이아웃, (b)는 플레이트 전극으로부터 플레이트선까지의 레이아웃을 나타내는 것이다. 도 16에 나타내는 레이아웃은, 1개의 워드선에 대해서 비트선쌍(BLT/B)의 내의 한쪽만이 교차하여, 1교점 메모리 어레이라 불린다. 그리고, 본 레이아웃은, 더욱, 비트선 BL의 피치를 좁힌 협(狹)비트선 피치형 1교점 메모리 어레이로 되어 있다.

본 메모리 어레이에서는, 모든 비트선 BL과 워드선(WL)의 교점에 DRAM 메모리 셀이 설치된다. 쌍이 되는 비트선 BLT, BLB는, 서로 센스 앰프를 사이에 두고 반대측의 메모리 어레이 내에 존재한다. 도 16의 (a), (b)에서는, 복수의 활성영역 (ACT)이, 비트선 BL 방향에 연속해서 형성되어 있고, 각 활성영역(ACT) 상에는, 다수의 워드선(WL)이 연신하는 구성으로 되어 있다. 단, 3개의 워드선(WL) 중 1개는, 소자분리용 게이트(ISO)로서 사용되고, 필요시에 'L'레벨로 구동하거나, 'L'레벨의 고정전압에 접속된다.

워드선(WL)을 2F(F: 최소 가공치수) 피치로 배치한 경우, 비트선 BL의 피치는, 2F나 그것 이하로 하는 것이 가능하다. 메모리 셀 사이즈는, 전술한 소자분리용 게이트(ISO)의 존재에 의해 실효적인 워드선(WL)의 피치가 3F로 되기 때문에,  $6F^2$ 가 된다. 따라서, 2교점 메모리 어레이의 메모리 셀 사이즈인  $8F^2$ 보다도 축소 가능하며, 미세화에 유익한 구성이 된다. 또한, 본 메모리 어레이를 이용한 경우, 1개의 워드선(WL)으로 선택되는 메모리 셀의 축적노드(SN)가 직선 모양으로 나열하기 때문에, 플레이트선(PL)을 직선 패턴으로 할 수 있고, 더욱 플레이트선(PL)의 피치도 3F로 넓힐 수 있기 때문에, 제작 프로세스가 용이해지는 이점이 있다.

도 17은, 도 1의 반도체 기억장치에 있어서, 도 16과는 다른 메모리 어레이의 레이아웃의 일례를 나타내는 도면이며, (a)는 트랜지스터의 활성영역으로부터 축적노드까지의 레이아웃, (b)는 플레이트 전극으로부터 플레이트선까지의 레이아웃을 나타내는 것이다. 도 17에 나타내는 레이아웃은, 넓은 비트선 피치형 1교점 메모리 어레이의 레이아웃으로 되어 있다.

본 메모리 어레이에서는, 모든 비트선 BL과 워드선(WL)의 교점에 DRAM 메모리 셀이 설치된다. 쌍이 되는 비트선 BLT, BLB는, 서로 센스 앰프를 사이에 두고 반대측의 메모리 어레이 내에 존재한다. 도 16의 (a), (b)에서는, 복수의 활성영역 (ACT)이 비트선 BL에 대해서 경사지게 형성되고, 각 활성영역(ACT) 상에는, 2개의 워드선(WL)이 연신하는 구성으로 되어 있다.

워드선(WL)을 2F 피치로 배치한 경우, 비트선 BL의 피치는, 예컨대 3F가 된다. 본 메모리 어레이를 이용하면, 어레이 노이즈는, 2교점 메모리 어레이보다도 커지지만 메모리 셀 사이즈는  $6F^2$ 이며, 2교점 메모리 어레이의  $8F^2$ 보다도 축소 가능하다. 또한, 워드선(WL)의 피치에 비해서 비트선 BL의 피치가 넓기 때문에, 미세화에 의해도 비트선간 커플링 노이즈를 작게 할 수 있는 것 및 센스 앰프의 레이아웃이 용이해지는 등의 이점이 있다.

도 18은, 도 1의 반도체 기억장치에 있어서, 그 서브 워드 드라이버 열과 플레이트 드라이버 열의 구성의 일례를 나타내는 회로도이다. 서브 워드 드라이버 열(SWDA)은, 복수의 서브 워드 드라이버(SWD)에 의해 구성되고, 플레이트 드라이버 열(PLDA)은, 복수의 플레이트 드라이버(PLD)에 의해 구성된다. 또한, 도 1의 (b) 등에도 나타낸 바와 같이, 플레이트 드라이버 열(PLDA)과 서브 워드 드라이버 열(SWDA)은, 메모리 어레이(ARY)의 주변에서 서로 인접해서 배치된다.

서브 워드 드라이버(SWD)와 플레이트 드라이버(PLD)는, 각각 함께 양측에 배치되는 메모리 어레이(ARY) 내의 워드선 (WL)과 플레이트선(PL)을 구동한다. 이때, 1개의 워드선(WL)에 1개의 플레이트선(PL)을 대응시켜서 구동한다. 또한, 도 3에서 설명한 바와 같이, 플레이트 드라이버 열(PLDA)과 서브 워드 드라이버 열(SWDA)은, 메모리 어레이(ARY)에 대해서 교대 배치되어 있기 때문에, 메모리 어레이(ARY) 내의 워드선(WL)(서브 워드선) 및 플레이트선(PL)은, 1개 걸러 좌우의 서브 워드 드라이버(SWD) 및 플레이트 드라이버(PLD)에 접속된다.

서브 워드 드라이버(SWD)는, N채널 트랜지스터 2개와 P채널 MOS 트랜지스터 1개로 구성된다. 한쪽의 N채널 MOS 트랜지스터는, 게이트에 메인 워드선(MWLB)이 접속되고, 드레인에 워드선(WL)이 접속되며, 소스에 전압 VKK가 접속된다. 다른쪽의 N채널 트랜지스터는 게이트에 상보 워드 드라이버 선택선(FXB), 드레인에 워드선(WL)이 접속되며, 소스에 전압 VKK가 접속된다.

P채널 MOS 트랜지스터는, 게이트에 메인 워드선(MWLB)이 접속되고, 드레인에 워드선(WL)이 접속되며, 소스에 서브 워드 드라이버 선택선(FX)이 접속된다. 도 18과 같이, 1개의 서브 워드 드라이버 열(SWDA) 상에 4세트(組)의 서브 워드 드라이버 선택선(FXO~4)이 배선되고, 1개의 메인 워드선(MWLB)에서 선택되는 4개의 서브 워드 드라이버(SWD) 중 어느 것인가 1개를 선택해서 1개의 워드선(WL)이 활성화된다.

플레이트 드라이버(PLD)는, N채널 트랜지스터 1개와 P채널 MOS 트랜지스터 1개로 구성된다. N채널 MOS 트랜지스터는, 게이트에 워드선(WL)이 접속되고, 드레인에 플레이트선(PL)이 접속되며, 소스에 플레이트 제어선(PX)이 접속된다. P채널 MOS 트랜지스터는, 게이트에 워드선(WL)이 접속되고, 드레인에 플레이트선(PL)이 접속되며, 소스에 플레이트 전압 VPH의 전원선이 접속된다.

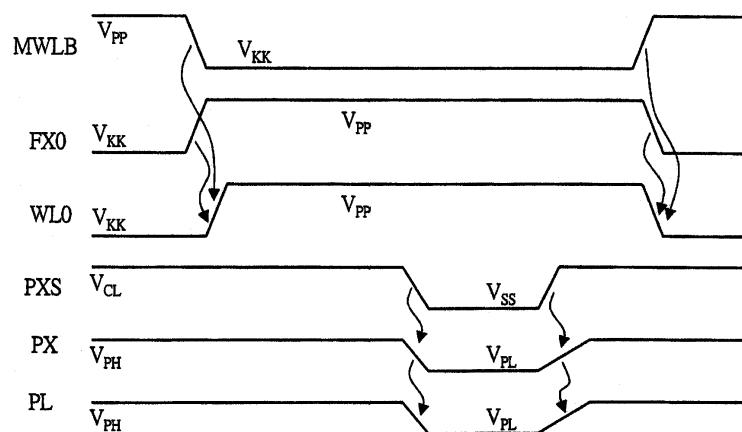

도 19는, 도 18의 서브 워드 드라이버 열과 플레이트 드라이버 열에 있어서, 그 동작 과정의 일례를 나타내는 과정도이다. 행 디코더(XDEC)에 있어서 메인 워드선(MWLB)이 전압 VKK로 내려가고, 어레이 제어회로(ACC)에 있어서 FX선이 활성화되면, 선택된 워드선(WLO)이 전압 VPP로 활성화된다.

워드선(WLO)이 비활성상태의 전압 VKK 레벨에 있을 때에는, 플레이트선(PL)은 전압 VPH로 고정된다. 워드선(WLO)이 전압 VPP로 활성화되면, 플레이트선(PL)과 플레이트 제어선 PX(PX선)가 접속된다. 도 5의 크로스 에리어(XP)에서의 PX 선 드라이버는, 플레이트 타이밍 신호(PXS)가 'H'일 때에는 PX선에 전압 VPH를 출력하고, 플레이트 타이밍 신호(PXS)가 'L'일 때에는 PX선에 전압 VPL을 출력한다. 이렇게 PX선의 전압을 하강 및 상승하는 것에 의해, 플레이트선(PL)의 전압도 같이 하강 및 상승한다.

도 22는 본 발명을 트윈 셀 어레이에 적용한 경우에 대해서, 메모리 어레이와 그 양측의 센스 앰프 열을 나타낸 것이다. 메모리 어레이에는 복수의 메모리 셀(MC)로 이루어진다. 트윈 DRAM 셀은 2개의 MOS 트랜지스터 및 2개의 커패시터로 구성되고, 2세트의 DRAM 셀에 의해 메모리 셀을 구성한다. 제1의 MOS 트랜지스터의 한쪽의 소스 또는 드레인이 비트선 BLT에 접속되고, 다른쪽의 소스 또는 드레인이 축적노드(SN)에 접속되며, 게이트가 워드선(WL)에 접속되어 있다. 제1의 커패시터의 한쪽의 단자는 축적노드(SN)에 접속되고, 커패시터의 다른쪽의 단자는 워드선과 병행하게 배선된 플레이트선(PL)에 접속된다. 제2의 MOS 트랜지스터의 한쪽의 소스 또는 드레인이 상보 비트선 BLB에 접속되고, 다른쪽의 소스 또는 드레인이 축적노드(SNB)에 접속되며, 게이트가 워드선(WL)에 접속되어 있다. 제2의 커패시터의 한쪽의 단자는 축적노드(SNB)에 접속되고, 커패시터의 다른쪽의 단자는 워드선과 병행하게 배선된 플레이트선(PL)에 접속된다.

통상의 DRAM과 달리, 플레이트선을 워드선 1개마다 분할해서 워드선과 평행하게 배선하고, 워드선이 활성화된 메모리 셀의 플레이트선만을 구동하면, 다른 비선택 상태의 메모리 셀로의 디스터브를 저감하면서, 축적전압을 증가할 수 있는 효과가 얻어진다. 이 어레이에서는 플레이트를 구동했을 때, 비트선 BLT와 상보 비트선 BLB가 같은 만큼, 커플링 전압을 받기 때문에, 도 2와 같이 더미 셀을 설치할 필요가 없게 된다는 이점이 있다. 또한, 비트선과 상보 비트선의 양쪽에 신호가 발생하기 때문에, 센스 앰프로 입력되는 신호량이 증가하여, 고속 동작이 가능하게 된다. 또한 센스 앰프의 전원전압을 내린 경우에도, 큰 신호량이 얻어지므로, 데이터 유지시간을 길게 할 수 있어, 저소비 전력화가 가능해진다.

도 23에 도 22에 나타낸 트윈 셀 어레이의 구동방법을 나타낸다. 이 예에서는 도 6의 플레이트 구동방식을 트윈 셀 어레이에 적용한 경우를 나타내고 있다. 도 6과의 차이는, 더미 셀이 불필요해지는 것과, 비트선 BLT, 상보 비트선 BLB에 상보의 신호가 나오는 것이다.

도 23의 동작 과정을 이용하여, 본 발명의 일실시형태에 의한 DRAM 어레이의 동작을 나타낸다. 칩 외부로부터 뱅크 활성화 커맨드(ACT)가 입력되면, 어드레스로 지정된 센스 앰프 열(SAA)에 있어서 센스 앰프 분리신호(SHR)의 한쪽과 프리 차지신호(BLEQ)가 비활성화된다. 행 디코더에 있어서 메인 워드선(MWLB)이 VKK로 내려가고, 어레이 제어회로(ACC)에 있어서 FX가 활성화되면, 선택된 워드선(WLO)이 VPP로 활성화된다. 워드선(WLO)에 의해 선택된 메모리 셀에 있어서는 셀 트랜지스터가 도통하여, 비트선 BLT, 상보 비트선 BLB 상에 신호가 판독된다. 도 23에서는 SN에 VSS, SNB에 VDL이 기록되어져 있어 '0'의 신호가 발생한 예를 나타내고 있다. 또한, 선택 셀의 플레이트선(PL)이 VPH로부터 VPL로 하강된다. 이렇게 플레이트선을 구동하면 선택 셀의 SN, SNB는, 셀 용량을 통한 커플링으로 레벨이 내려가기 때문에, 전하가 고속으로 비트선에 판독된다. 여기에서, VPH는 VDL과 VSS의 거의 중간의 전압으로 해 놓으면, 대기시에 메모리 셀의 용량절연막에 인가되는 전압이 작아지므로, 신뢰성이 높아진다.

센스 앰프에 있어서 P측 공통 소스선(CSP)을 VDL로, N측 공통 소스선(CSN)을 VSS로 구동하면, 비트선 상의 신호가 증폭된다. 이 상태에서, 칩은 리드 커맨드(RD) 또는 라이트 커맨드(WRT)를 받아들일 수 있다. 도면에서는 라이트 커맨드가 입력된 경우를 나타낸다. 선택된 어드레스의 열 선택선(YS)이 활성화되고, LIO선쌍으로부터, 라이트 데이터가 기록된다. 여기에서는 BLT가 'H'로 구동되는 반전 기록시의 파형을 나타내고 있다.

메모리 셀은 N채널이므로, 문턱치를 VT라 하면, SN에 기록할 수 있는 최대의 전압은 VPP-VT가 된다. 본 발명의 일상 형태에 의한 DRAM에서는 메모리 셀 트랜지스터의 게이트 산화막을 박막화하기 위해서, 워드선의 H레벨인 VPP를 전원 전압 VDD (예를들면 1.8V) 정도까지 내리고 있다. 또한, 메모리 셀 트랜지스터는 미세한 트랜지스터를 이용하고 있고, 개수도 많기 때문에, 문턱치 변동이 1V 가깝게 매우 크고, 예컨대 설계 중심값을 0.7V로 한 경우, 최소값은 0.2V, 최대값은 1.2V가 된다. 비트선 전압 VDL을 일례로서 1.3V로 한 경우, 문턱치가 낮은 셀(LVT-ce11)에서는 VPP-VT=1.6V이므로 셀 트랜지스터가 온 하고 있고, SN에 VDL=1.3V가 기록되지만, 문턱치가 중간 정도의 셀(MVT-ce11), 높은 셀(HVT-ce11)에서는 증폭의 도중에 컷오프 상태가 되어, 각각 1.1V, 0.6V까지 밖에 기록되지 않는다. 즉, 기록시의 SN전압은 셀 트랜지스터의 VT에 대응해서 0.6V로부터 1.3V까지의 변동을 갖는다.

이 상태에서, 프리 차지 커맨드(PRC)가 입력되었을 때에, 선택 셀의 플레이트(PL)를 VPL로부터 VPH로 복귀시키면, SN의 전위는 커패시터로부터의 커플링을 받아,  $\Delta PL = VPH - VPL$  분 만큼 상승한다. 상기와 같이 'H'가 기록된 SN측의 셀에서는 셀 트랜지스터가 컷오프 하기 때문에,  $\Delta PL$ 의 전위상승 분이 유지되지만, 'L'이 기록된 SNB측의 셀에서는 셀 트랜지스터가 온 상태이기 때문에, 곧 VSS로 복귀한다. 따라서, 축적 전하량을  $\Delta PL$  만큼 증가할 수 있다.  $\Delta PL$ 을 가장 문턱치가 높은 메모리 셀(HVT-ce11)의 기록전압이 VDL까지 상승하도록 예컨대 0.7V로 설정하면, 모든 메모리 셀이 1.3V 이상으로 기록되기 때문에, 다음 사이클에서 판독 신호량이나 리텐션 시간의 마진을 넓힐 수 있다. 그렇지만, 문턱치가 낮은 셀(LVT-ce11)에서는 원래 VDL=1.3V까지 기록되어 있었으므로, 더 전위가  $\Delta PL$  분 만큼 상승하면 2.0V까지 높아진다. 이대로 워드선을 비활성화하면, 대기시에 메모리 셀 트랜지스터에 높은 전압이 인가된 그대로 되어, 디바이스의 신뢰성이 저하된다.

그래서, 여기에서는 다음과 같은 방법으로 VT의 낮은 셀만을 선택적으로 방전하여, 워드선 비활성시의 SN 기록전압을 일치시켜, 디바이스의 신뢰성을 높인다. 즉, 플레이트 구동 후, P측 공통 소스선(CSP)을 VSP까지 내리는 것에 의해, 'H'측의 비트선 전압을 VDP(예컨대 0.7V)까지 내린다. 그렇게 하면, 문턱치가 낮은 메모리 셀(LVT-ce11)에서는 실효 게이트 전압 VGS-VT가  $(1.8 - 0.7) - 0.2 = 0.9V$ 가 되어, 강하게 온 하기 때문에, SN의 전하가 급속히 방전된다. 한편, 문턱치가 중간 정도의 셀에서는 VGS-VT가 0.4V로 약하게 밖에 온 하지 않기 때문에, 방전은 완만하며, 문턱치가 높은 셀에서는 VGS-VT가 부(負)로 컷오프의 상태가 유지된다. 따라서, 도면에 나타낸 바와 같이, 문턱치가 낮은 셀에서 지나치게 오른 전위가 내려가고, 문턱치가 중간 정도의 셀 및 높은 셀에서는 전위가 거의 유지되기 때문에, 문턱치 변동보다도 기록전압의 변동이 작아진다. 방전동작이 종료 후, 워드선을 하강해서, BLEQ, SHR이 다시 활성화되어, 비트선이 프리 차지된다.

이렇게, 도 22 및 도 23에 나타낸 것과 같은 구성 및 동작을 이용하는 것으로, 셀 트랜지스터에 고전압이 장시간 인가되는 것을 방지할 수 있기 때문에, 메모리 셀 트랜지스터의 게이트 산화막을 박막화할 수 있어, 미세화가 가능해진다.

이상, 본 발명자에 의해 이루어진 발명을 실시형태에 의거해서 구체적으로 설명했지만, 본 발명은 상기 실시형태에 한정되는 것은 아니고, 그 요지를 이탈하지 않는 범위에서 여러 가지 변경 가능한 것은 말할 필요도 없다.

본 발명의 반도체 기억장치는, 플레이트 구동방식을 구비한 DRAM 제품에 적용해서 특히 유익한 기술이며, 이것에 한정하지 않고, 마이크로 프로세서나 DSP(Digital Signal Processor) 등의 로직 칩에 내장되는 온칩(on-chip) 메모리 등에 대해서도 적용 가능하다.

### 발명의 효과

본원에 있어서 개시되는 발명 중, 대표적인 것에 의해 얻어지는 효과를 간단히 설명하면, 반도체 기억장치의 미세화가 실현 가능해진다.

### (57) 청구의 범위

#### 청구항 1.

각각 MOS 트랜지스터와 커패시터를 포함하고, 상기 MOS 트랜지스터의 게이트가 선택단자로 되며, 소스 및 드레인의 한 쪽이 입출력 단자로 되고, 소스 및 드레인의 다른쪽이 상기 커패시터의 축적노드에 접속되는 복수의 메모리 셀과,

상기 복수의 메모리 셀의 상기 선택단자에 각각 접속되는 복수의 워드선과,

상기 복수의 메모리 셀의 상기 입출력 단자에 각각 접속되는 상보 비트선과,

상기 상보 비트선의 일단에 접속되어, 상기 상보 비트선의 전압차이를 증폭해서 래치를 행하는 센스 앰프를 구비한 반도체 기억장치로서,

상기 복수의 워드선 중 어느 하나의 워드선이 활성화된 후, 상기 센스 앰프가 활성화되어, 상기 상보 비트선 중 한쪽의 비트선이 제1의 전압으로 증폭되고, 다른쪽의 비트선이 상기 제1의 전압보다도 낮은 제2의 전압으로 증폭된 단계에서, 상기 제1의 전압으로 증폭된 비트선을, 제1의 시간에서 상기 제1의 전압보다도 낮은 제3의 전압으로 내리고, 그 후에 상기 어느 하나의 워드선을 비활성화하는 수단을 갖는 것을 특징으로 하는 반도체 기억장치.

## 청구항 2.

제 1 항에 있어서,

상기 센스 앰프는, 제1 및 제2의 P채널형 MOS 트랜지스터와, 제1 및 제2의 N채널형 MOS 트랜지스터를 포함하고,

상기 제1의 P채널형 MOS 트랜지스터는, 소스가 P측 공통 소스단자에 접속되고, 게이트가 상기 상보 비트선 중의 제2의 비트선에 접속되며, 드레인이 상기 상보 비트선 중의 제1의 비트선에 접속되어 있고,

상기 제2의 P채널형 MOS 트랜지스터는, 소스가 상기 P측 공통 소스단자에 접속되고, 게이트가 상기 제1의 비트선에 접속되며, 드레인이 상기 제2의 비트선에 접속되어 있으며,

상기 제1의 N채널형 MOS 트랜지스터는, 소스가 N측 공통 소스단자에 접속되고, 게이트가 상기 제2의 비트선에 접속되며, 드레인이 상기 제1의 비트선에 접속되어 있고,

상기 제2의 N채널형 MOS 트랜지스터는, 소스가 상기 N측 공통 소스단자에 접속되고, 게이트가 상기 제1의 비트선에 접속되며, 드레인이 상기 제2의 비트선에 접속되어 있으며,

상기 복수의 워드선 중 어느 하나의 워드선이 활성화된 후, 상기 P측 공통 소스선이 상기 제1의 전압으로 구동되고, 상기 N측 공통 소스선이 상기 제2의 전압으로 구동된 단계에서, 상기 P측 공통 소스선을 상기 제1의 시간에서 상기 제1의 전압보다도 낮은 제4의 전압으로 구동하고, 그 후에 상기 어느 하나의 워드선을 비활성화하는 수단을 갖는 것을 특징으로 하는 반도체 기억장치.

## 청구항 3.

제 2 항에 있어서,

상기 제4의 전압은, 상기 제3의 전압에서 상기 제1 또는 상기 제2의 P채널형 MOS 트랜지스터의 문턱치전압을 뺀 값보다도 낮은 것을 특징으로 하는 반도체 기억장치.

## 청구항 4.

제 2 항에 있어서,

상기 제1의 시간은, 상기 반도체 기억장치에 프리 차지 커맨드가 입력된 시간보다도 느린 것을 특징으로 하는 반도체 기억장치.

### 청구항 5.

제 2 항에 있어서,

상기 어느 하나의 워드선이 활성화된 후, 상기 P측 공통 소스선을, 상기 제1의 전압보다도 높은 제5의 전압으로 구동하며, 그 후, 상기 제1의 전압으로 구동하고, 또 그 후, 상기 제1의 시간에서 상기 제4의 전압으로 구동하는 수단을 갖는 것을 특징으로 하는 반도체 기억장치.

### 청구항 6.

제 2 항에 있어서,

복수의 플레이트선을 구비하고,

상기 복수의 플레이트선은, 상기 복수의 메모리 셀내에서 상기 축적노드와 반대측의 상기 커페시터의 노드가 되는 플레이트 단자에 각각 접속되며,

상기 복수의 플레이트선 중 동일한 플레이트선에는, 상기 복수의 워드선 중 동일한 워드선에 접속되는 상기 복수의 메모리 셀의 상기 플레이트 단자만이 접속되는 것을 특징으로 하는 반도체 기억장치.

### 청구항 7.

제 6 항에 있어서,

상기 커페시터는, 상기 커페시터의 한쪽 전극이 충간 절연막의 구멍의 내벽에 형성된 실린더 형상인 것을 특징으로 하는 반도체 기억장치.

### 청구항 8.

제 6 항에 있어서,

상기 상보 비트선은, 상기 복수의 워드선 중 동일한 워드선과 교차하고, 서로 인접해서 배치되는 것을 특징으로 하는 반도체 기억장치.

### 청구항 9.

제 6 항에 있어서,

상기 상보 비트선은, 상기 복수의 워드선 중 동일한 워드선과 교차하고, 사이에 1개의 비트선을 두고 배치되는 것을 특징으로 하는 반도체 기억장치.

### 청구항 10.

제 6 항에 있어서,

상기 상보 비트선은, 상기 센스 앰프를 중심으로 서로 반대 방향으로 연신(延伸)하고,

상기 센스 앰프가 상기 복수의 워드선의 연신하는 방향에 복수 배치되는 것으로, 상기 상보 비트선을 포함하는 복수의 비트선이 서로 인접해서 배치되며,

상기 복수의 워드선간의 피치는, 상기 복수의 비트선간의 피치와 동일하거나 또는 넓은 것을 특징으로 하는 반도체 기억장치.

### 청구항 11.

제 6 항에 있어서,

상기 상보 비트선은, 상기 센스 앰프를 중심으로 서로 반대 방향으로 연신하고,

상기 센스 앰프가 상기 복수의 워드선의 연신하는 방향에 복수 배치되는 것으로, 상기 상보 비트선을 포함하는 복수의 비트선이 서로 인접해서 배치되며,

상기 복수의 워드선간의 피치는, 상기 복수의 비트선간의 피치보다도 좁은 것을 특징으로 하는 반도체 기억장치.

### 청구항 12.

각각 MOS 트랜지스터와 커패시터를 포함하고, 상기 MOS 트랜지스터의 게이트가 선택단자로 되며, 소스 및 드레인의 한쪽이 입출력 단자로 되고, 소스 및 드레인의 다른쪽이 상기 커패시터의 축적노드에 접속되는 복수의 메모리 셀과,

상기 복수의 메모리 셀의 상기 선택단자에 각각 접속되는 복수의 워드선과,

상기 복수의 메모리 셀의 상기 입출력 단자에 각각 접속되는 상보 비트선과,

상기 복수의 메모리 셀의 커패시터에서, 상기 축적노드의 반대측의 단자에 각각 접속되는 복수의 플레이트선과,

상기 상보 비트선의 일단에 접속되어, 상기 상보 비트선의 전압차이를 증폭해서 래치를 행하는 센스 앰프를 구비한 반도체 기억장치로서,

상기 복수의 워드선 중 어느 하나의 워드선이 활성화된 후, 상기 센스 앰프가 활성화되어, 상기 상보 비트선의 중 한쪽의 비트선이 제1의 전압으로 증폭되고, 다른쪽의 비트선이 상기 제1의 전압보다도 낮은 제2의 전압으로 증폭된 단계에서, 상기 어느 하나의 워드선에 대응하는 플레이트선을, 제2의 시간에서 제6의 전압으로부터 상기 제6의 전압보다도 높은 제7의 전압으로 구동하는 수단과,

상기 제1의 전압으로 증폭된 비트선을, 제1의 시간에서 상기 제1의 전압보다도 낮은 제3의 전압으로 내리고, 그 후에 상기 어느 하나의 워드선을 비활성화하는 수단을 갖는 것을 특징으로 하는 반도체 기억장치.

### 청구항 13.

제 12 항에 있어서,

상기 제1의 시간은, 상기 제2의 시간과 거의 동시인 것을 특징으로 하는 반도체 기억장치

**청구항 14.**

제 12 항에 있어서,

상기 어느 하나의 워드선에 대응하는 플레이트선은, 상기 어느 하나의 워드선이 활성화된 후에 상기 센스 앰프가 활성화되기 전에, 상기 제7의 전압으로부터 상기 제6의 전압으로 구동되는 것을 특징으로 하는 반도체 기억장치.

**청구항 15.**

제 12 항에 있어서,

상기 어느 하나의 워드선에 대응하는 플레이트선은, 상기 센스 앰프가 활성화된 후에 상기 제2의 시간보다도 전에, 상기 제7의 전압으로부터 상기 제6의 전압으로 구동되는 것을 특징으로 하는 반도체 기억장치.

**청구항 16.**

각각 MOS 트랜지스터와 커패시터를 포함하고, 상기 MOS 트랜지스터의 게이트가 선택단자로 되며, 소스 및 드레인의 한 쪽이 입출력 단자로 되고, 소스 및 드레인의 다른쪽이 상기 커패시터의 축적노드에 접속되는 복수의 메모리 셀과,

상기 복수의 메모리 셀의 상기 선택단자에 각각 접속되는 복수의 워드선과,

상기 복수의 메모리 셀의 상기 입출력 단자에 각각 접속되는 상보 비트선과,

상기 상보 비트선의 일단에 접속되어, 상기 상보 비트선의 전압차이를 증폭해서 래치를 행하는 센스 앰프와,

상기 센스 앰프에 접속되는 P측 공통 소스선 및 N측 공통 소스선과,

상기 P측 공통 소스선을 구동하는 제1, 제2 및 제3의 드라이버를 구비하고,

상기 센스 앰프는, 제1 및 제2의 P채널형 MOS 트랜지스터와, 제1 및 제2의 N채널형 MOS 트랜지스터를 포함하며,

상기 제1의 P채널형 MOS 트랜지스터는, 소스가 P측 공통 소스단자에 접속되고, 게이트가 상기 상보 비트선 중의 제2의 비트선에 접속되며, 드레인이 상기 상보 비트선 중의 제1의 비트선에 접속되어 있고,

상기 제2의 P채널형 MOS 트랜지스터는, 소스가 상기 P측 공통 소스단자에 접속되고, 게이트가 상기 제1의 비트선에 접속되며, 드레인이 상기 제2의 비트선에 접속되어 있으며,

상기 제1의 N채널형 MOS 트랜지스터는, 소스가 N측 공통 소스단자에 접속되고, 게이트가 상기 제2의 비트선에 접속되며, 드레인이 상기 제1의 비트선에 접속되어 있고,

상기 제2의 N채널형 MOS 트랜지스터는, 소스가 상기 N측 공통 소스단자에 접속되고, 게이트가 상기 제1의 비트선에 접속되며, 드레인이 상기 제2의 비트선에 접속되어 있으며,

상기 제1의 드라이버는 제1의 전원전압에 접속되고, 상기 제2의 드라이버는 제4의 전원전압에 접속되며, 상기 제3의 드라이버는 제5의 전원전압에 접속되는 것을 특징으로 하는 반도체 기억장치.

**청구항 17.**

제 16 항에 있어서,

상기 제4의 전원전압은, 상기 제1의 전원전압의 절반보다도 낮은 것을 특징으로 하는 반도체 기억장치.

### 청구항 18.

제 16 항에 있어서,

상기 제1 및 상기 제4의 전원전압은, 각각 외부 전원전압을 강압(降壓)회로에서 강압하는 것으로 칩 내부에서 생성되고,

상기 제5의 전원전압은, 상기 외부 전원전압을 그대로 사용하여 생성되는 것을 특징으로 하는 반도체 기억장치.

### 청구항 19.

각각 MOS 트랜지스터와 커패시터를 포함하고, 상기 MOS 트랜지스터의 게이트가 선택단자로 되며, 소스 및 드레인의 한 쪽이 입출력 단자로 되고, 소스 및 드레인의 다른쪽이 상기 커패시터의 축적노드에 접속되는 복수의 메모리 셀과,

상기 복수의 메모리 셀에서의 상기 축적노드와 반대측의 상기 커패시터의 노드에 각각 접속된 복수의 플레이트선과,

상기 복수의 메모리 셀의 상기 선택단자에 각각 접속되는 복수의 워드선과,

상기 복수의 메모리 셀의 상기 입출력 단자에 각각 접속되는 상보 비트선과,

상기 상보 비트선의 일단에 접속되어, 상기 상보 비트선의 전압차이를 증폭해서 래치를 행하는 센스 앰프와,

상기 센스 앰프에 접속되어, 상기 상보 비트선의 고레벨측의 전압을 공급하기 위한 P측 공통 소스선과,

상기 센스 앰프에 접속되어, 상기 상보 비트선의 저레벨측의 전압을 공급하기 위한 N측 공통 소스선과,

소스 및 드레인의 한쪽이 상기 상보 비트선의 고레벨측의 기록전압이 되는 제1의 전원전압에 접속되고, 다른쪽이 상기 P측 공통 소스선에 접속된 제3의 MOS 트랜지스터와,

소스 및 드레인의 한쪽이 상기 제1의 전원전압보다도 낮은 제4의 전원전압에 접속되고, 다른쪽이 상기 P측 공통 소스선에 접속된 제4의 MOS 트랜지스터와,

상기 P측 공통 소스선과 상기 N측 공통 소스선에 접속되고, 상기 P측 공통 소스선과 상기 N측 공통 소스선을 동일한 전압으로 프리 차지하는 프리 차지회로와,

상기 복수의 플레이트선에 접속되어, 기록 및 판독 동작시에 상기 복수의 플레이트선의 전압을 소정의 값으로 변동시키는 플레이트 드라이버를 갖는 것을 특징으로 하는 반도체 기억장치.

### 청구항 20.

제 19 항에 있어서,

상기 제3의 MOS 트랜지스터는 P채널형 MOS 트랜지스터이며,

상기 제4의 MOS 트랜지스터는 N채널형 MOS 트랜지스터인 것을 특징으로 하는 반도체 기억장치.

## 청구항 21.

워드선과,

2개의 비트선으로 이루어지고, 상기 워드선과의 사이에서 2개의 교점을 구비하는 상보 비트선과,

MOS 트랜지스터 및 커패시터를 포함하고, 상기 MOS 트랜지스터의 게이트가 상기 워드선에 접속되며, 소스 또는 드레인의 한쪽이 상기 상보 비트선의 한쪽의 비트선에 접속되고, 소스 또는 드레인의 다른쪽이 상기 커패시터에 접속된 다이내믹형 메모리 셀과,

상기 상보 비트선의 일단측에 배치되어, 상기 상보 비트선의 전압차이를 증폭하는 래치회로 이루어지는 센스 앰프를 구비하고,

상기 워드선과 상기 상보 비트선이 이루는 2개 교점의 어느 것에도, 상기 다이내믹형 메모리 셀이 설치되며,

상기 2개의 교점에 각각 설치된 다이내믹형 메모리 셀에서의 상기 커패시터의 타단은, 동일한 플레이트선에 접속되고,

상기 다이내믹형 메모리 셀로부터 데이터를 판독할 때, 상기 워드선이 활성화되어, 상기 상보 비트선에 상보의 신호가 발생하고, 상기 플레이트선의 레벨이, 제7의 전압으로부터, 상기 제7의 전압보다도 낮은 제6의 전압으로 구동되는 것을 특징으로 하는 반도체 기억장치.

## 청구항 22.

제 21 항에 있어서,

상기 상보 비트선 중 한쪽의 비트선이 제1의 전압으로 증폭되고, 다른쪽의 비트선이 상기 제1의 전압보다도 낮은 제2의 전압으로 증폭된 후, 제2의 시간에 상기 플레이트선의 레벨이 상기 제6의 전압으로부터, 상기 제7의 전압으로 구동되고, 제1의 시간에 있어서 상기 제1의 전압으로 증폭된 비트선이, 상기 제1의 전압보다도 낮은 제3의 전압으로 내려진 후, 상기 워드선이 비활성화되는 것을 특징으로 하는 반도체 기억장치.

## 청구항 23.

제 22 항에 있어서,

상기 제1의 시간과 상기 제2의 시간이 거의 동시인 것을 특징으로 하는 반도체 기억장치.

**도면**

## 도면1

(a)

(b)

## 도면2

## 도면3

도면4

## 도면5

## 도면6

도면7

도면8

## 도면9

## 도면10

## 도면11

## 도면12

## 도면13

도면14

도면15

도면16

## 도면17

(a)

(b)

도면18

도면19

도면20

도면21

## 도면22

## 도면23