Republik

Österreich

Patentamt

(11) Nummer: AT 401 117 B

(12)

# PATENTSCHRIFT

(21) Anmeldenummer: 666/93

(51) Int.Cl.<sup>6</sup> : G06F 3/00

(22) Anmeldetag: 1. 4.1993

(42) Beginn der Patentdauer: 15.10.1995

(45) Ausgabetag: 25. 6.1996

### (5c) Entzesschaltungen:

FB 132384 FB 384621A DE 37358284

(73) Patentinhaber:

ELIN ENERGIEANWENDUNG GESELLSCHAFT M.B.H.

A-1141 WIEN (AT).

(72) Erfinder:

HASENBERGER RONALD DIPLO. ING.

WIEN (AT).

(54) EINRICHTUNG FÜR EINE DIGITAL-SIGNALPROZESSORPLATINE ZUR ANPASSUNG EINES SCHNELLEN PROZESSORS AN LANGSAME BAUTEILE

(57) In der Mikroprozessortechnik bzw. in der elektronischen Datenverarbeitung kommt es häufig vor, daß in einer Anlage sowohl ein schneller Bus, auf den oft zugegriffen wird, als auch ein langsamer Bus, an welchem langsame Peripherie angeschlossen ist, enthalten sind. Dabei ergibt sich sehr oft das Problem, daß aus Kostengründen lediglich ein Prozessor für beide Busse eingesetzt werden soll.

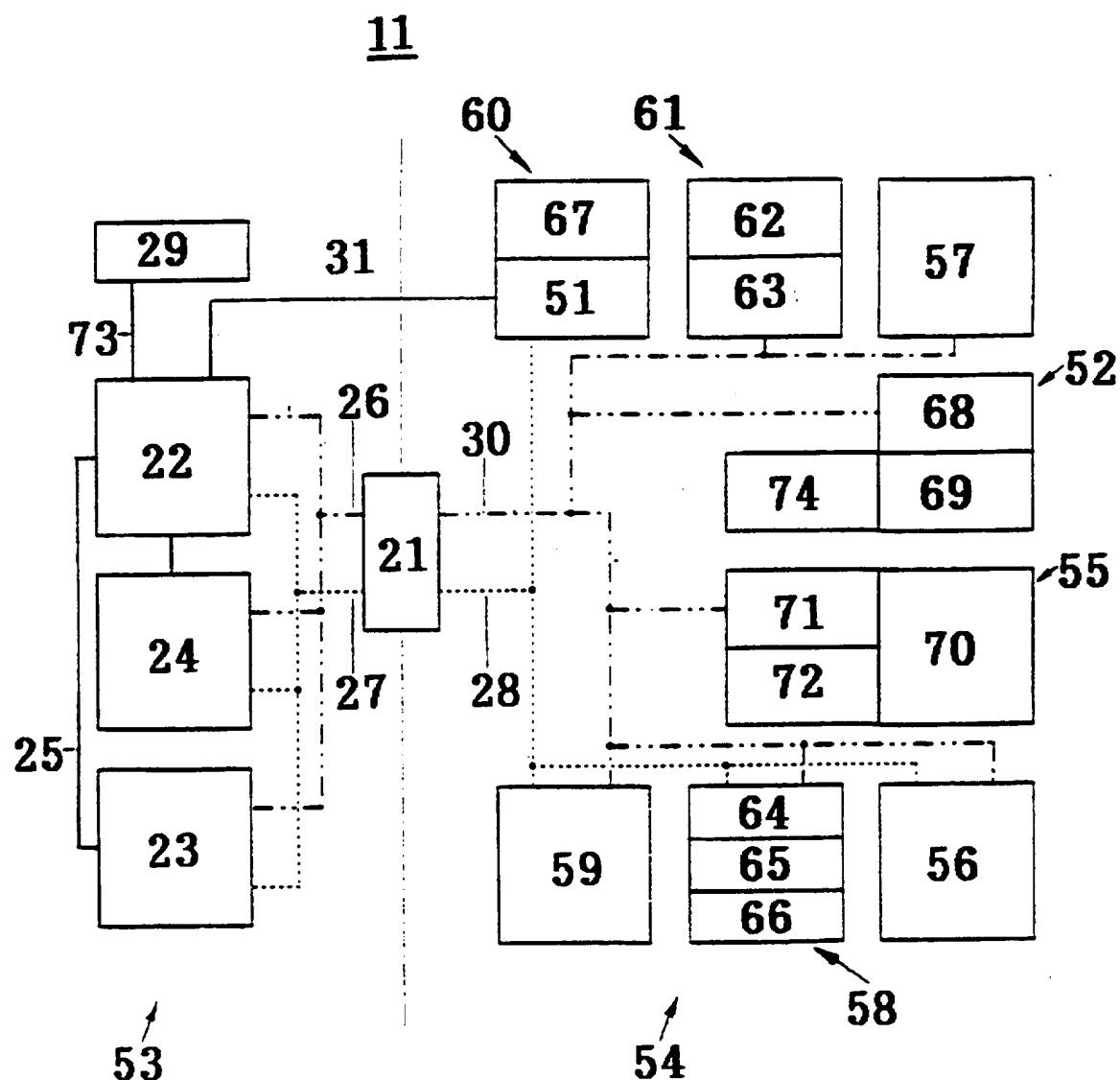

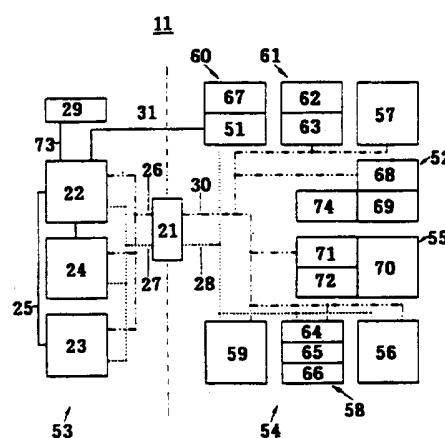

ein Prozessor für beide Busse eingesetzt werden soll. Erfindungsgemäß ist zur Trennung in zwei Busbereiche (53, 54) eine Übernahmezeit-Verlängerungseinheit (21) eingesetzt, welche über Datenbusse (26, 27 bzw. 28, 30) mit dem Hochgeschwindigkeits-Busbereich (53) sowie dem Niedriggeschwindigkeits-Busbereich (54) verbunden ist.

Die Erfindung ist vorteilhaft, weil es durch die Trennung mittels einer Übernahmezeit-Verlängerungseinheit möglich ist, unter Verwendung nur eines Prozessors zwei Busbereiche mit jeweils genau definiertem Verwendungszweck zu erstellen.

AT 401 117 B

Die Erfindung betrifft eine Einrichtung für eine Digital-Signalprozessor-Platine zur Anpassung eines schnellen Prozessors an langsame Bauteile, wobei eine Trennung dieser Platine in einen Hochgeschwindigkeits-Busbereich und einen Niedergeschwindigkeits-Busbereich durchgeführt ist.

In der Mikroprozessortechnik bzw. in der elektronischen Datenverarbeitung kommt es häufig vor, daß 5 eine Anlage sowohl einen schnellen Bus, auf den oft zugegriffen wird, als auch einen langsamen Bus, an welchem langsame Peripherie angeschlossen ist, enthält. Dabei ergibt sich sehr oft das Problem, daß aus Kostengründen lediglich ein Prozessor für beide Busse eingesetzt werden soll.

Es ist eine Schaltung bekannt, bei welcher zur Lösung dieses Problems die Auftrennung des Busses in 10 einen lokalen Bus und in einen Systembus vorgeschlagen wird. Die Schnittstelle zwischen lokalem Bus und Systembus wird dabei von einem Bus-Steuermodul gesteuert. Dabei ist der lokale Bus als Multimaster-Bus ausgeführt, in welchem der Prozessor mit einem Arithmetik-Koprozessor eng gekoppelt, aber entkoppelt vom restlichen Bus, zusammenarbeitet.

Der Nachteil dieser Schaltung besteht darin, daß der lokale Bus, welcher einem Hochgeschwindigkeitsbus entsprechen soll, für die meisten Anwendungen unbrauchbar ist, da an ihn ausschließlich der Prozessor 15 angeschlossen ist; aus diesem Grund kann keine Anpassung der Signale an die Erfordernisse der am Systembus angeschlossenen Komponenten erfolgen. Zudem ist die elektromagnetische Verträglichkeit (EMV) äußerst ungünstig.

Eine andere bekannte Schaltungsanordnung bedient sich des Pufferspeicher-Systems. In diesem Fall 20 erfolgt die Aufteilung des Busses in einen schnellen und einen langsamen Bus derart, daß sich am langsamen Bus die gesamte Peripherie und der (große) Hauptspeicher befinden. Am schnellen Bus befindet sich ein schnelles RAM, in welchem ein Teil des Hauptspeichers abgebildet ist. Diese Aufteilung erfolgt im wesentlichen aus Kostengründen, da die Ausführung des gesamten Hauptspeichers mit schnellen RAMs die 25 Kosten explodieren lassen würde. Bei einem Zugriff auf den Speicher wird von der Pufferspeicher-Steuereinheit zunächst festgestellt, ob sich das vom Prozessor angeforderte Datum im Pufferspeicher befindet. Ist das der Fall, wird ein Zugriff auf den Pufferspeicher durchgeführt und das entsprechende Datum schnell zur Verfügung gestellt.

Nachteilig ist diese Schaltungsanordnung, weil das Datum, wenn es sich nicht im Pufferspeicher befindet, aus dem langsamen Hauptspeicher geholt werden muß, wofür eine erhebliche Wartezeit des Prozessors erforderlich ist. Die Verwendung eines Pufferspeicher-Systems für den vorerwähnten Zweck 30 ergibt somit eine Verringerung der Anzahl der Zugriffe am langsamen Bus. Weiters ergibt sich eine Verlängerung der Impulse beim Zugriff auf den langsamen Bus, weil langsame Bausteine angesteuert werden müssen. Für die Erkennung des jeweiligen Ladezustandes des Pufferspeichers ist ein sehr hoher Bauteilaufwand erforderlich, da sich der Inhalt des Pufferspeicher je nach der Art der jeweils vorangegangenen Aktionen ändert. Daraus ergibt sich ein sehr komplexer, somit störungsanfälliger und teurer Aufbau.

35 Die Patentpublikation EP-A-13 739 stellt eine Datenfernverarbeitungs-Steuereinheit in einem Datenverarbeitungssystem vor. Diese Datenfernverarbeitungs-Steuereinheit ist in ein Datenverarbeitungssystem integriert, welches aus einer Zentraleinheit mit einem Hauptsteuerspeicher und einem lokalen Speicher besteht. Weiters sind in dem System mehrere Hochgeschwindigkeitsanschlüsse vorgesehen, welche mittels einer Hochgeschwindigkeits-Busleitung mit der Zentraleinheit in Verbindung stehen. Dabei versorgen die Hochgeschwindigkeitsanschlüsse mehrere Eingabe-/Ausgabebauelemente. Mindestens einer der Hochgeschwindigkeitsanschlüsse ist als Hochgeschwindigkeits-Busleitungsanschluß ausgebildet und steuert über eine Niedergeschwindigkeits-Busleitung mehrere Niedergeschwindigkeits-Informationsleitungsanschlüsse. Sämtliche Mikroprogramme für die Steuerung der Funktionen und der Diagnose der verschiedenen Informationsleitungen befinden sich innerhalb eines Informationssteuerspeichers im Hauptsteuerspeicher. Weiters findet ein 40 standardisierter (vorzugsweise ein ICA-) Busleitungsanschluß Verwendung, welcher an der Niedergeschwindigkeits-Busleitung einen eigenen Buskontroller darstellt, der zahlreiche Anforderungen unabhängig von der Zentraleinheit abarbeiten kann.

Nachteilig an der in der Patentpublikation EP-A-13 739 dargestellte Struktur ist, daß der Hochgeschwindigkeits-Busleitungsanschluß durch eigene Mikroprogramme in der Zentraleinheit unterstützt werden muß. 50 Zudem läßt bei höheren Anforderungen die Qualität der elektromagnetische Verträglichkeit zu wünschen übrig.

Die Druckschrift DE-A-3 735 828 befaßt sich mit einem Verfahren zur Restaurierung bei Unterbrechung von umfangreichen Mikroprogrammen in einer mikroprogrammgesteuerten Datenverarbeitungsvorrichtung. Zur Durchführung des Verfahrens wird beim Wiederanlauf einer Anweisung nach einem Aussetzen die 55 interne Information einer Verarbeitungsvorrichtung zum Zeitpunkt des Anweisungs-Aussetzens in einem Speicher sichergestellt. Die auf diese Weise sichergestellte interne Information wird nach Durchführung eines Prozesses wiedergewonnen, bei dem die Ursache für das Aussetzen beseitigt wird. Eine der Adresse eines momentan ausgeführten Mikroprogramms zugeordnete Adresse (Fixpunkt) wird entsprechend einer

Bestimmung durch das Mikroprogramm gespeichert. Nach dem Prozeß, in welchem die Ursachen für das Aussetzen beseitigt wurden, läuft die Ausführung der Anweisung unter Verwendung der Fixpunkt-Adresse wieder an. Ist nach dem Prozeß zum Beseitigen der Aussetz-Ursachen keine Fixpunkt-Adresse gespeichert, läuft die Ausführung der Anweisung von einer Leseoperation der Aussetz-Anweisung vom Hauptspeicher 5 aus wieder an. Es wird also mit dem jeweils aktuellen Mikroprogramm nicht vollständig neu begonnen, sondern das alte Mikroprogramm - unter Beachtung verschiedener Erfordernisse - fortgesetzt.

Eine Anpassung eines schnellen Prozessors an langsame Bauteile ist mit der Erfindung lt. Druckschrift DE-A-3 735 828 nicht möglich.

In der Patentpublikation EP-A-384 621 geht es um die Datenübertragung zwischen zwei asynchronen 10 Busleitungen. Dieses System erlaubt eine Datenübertragung zwischen einer Hochgeschwindigkeits-Busleitung und einer Niedergeschwindigkeits-Busleitung, wobei diese beiden Busleitungen unabhängig voneinander und asynchron arbeiten. Wenn die Niedergeschwindigkeits-Busleitung einen Zugriff auf die Hochgeschwindigkeits-Busleitung benötigt, so ist der Besetztzustand der Hochgeschwindigkeits-Busleitung festgelegt und Übertragungen zur Hochgeschwindigkeits-Busleitung werden mit hoher Geschwindigkeit durchgeführt, wenn diese Busleitung unbelegt ist.

Wenn von der Hochgeschwindigkeits-Busleitung ein Zugriff auf die Niedergeschwindigkeits-Busleitung eingeleitet ist, dann wird für den Fall, daß die Niedergeschwindigkeits-Busleitung belegt ist, der abfragende Kontroller an der Hochgeschwindigkeits-Busleitung in einen zeitweilig anstehenden Anforderungszustand versetzt und gibt die Hochgeschwindigkeits-Busleitung frei; dadurch ist also die Hochgeschwindigkeits- 20 Busleitung frei für die Durchführung anderer Anforderungen. Wenn die Niedergeschwindigkeits-Busleitung wieder frei ist, wird dem anstehenden Anforderer mit dem höchsten Vorrang Zugriff auf die Niedergeschwindigkeits-Busleitung eingeräumt, und zwar auf Grundlage eines Vorrangprinzips gegenüber allen niederrangigeren anstehenden Anforderern. Es können beide Busleitungen Zugriff auf die jeweils andere Busleitung beanspruchen. Damit wird eine Minimierung der Leerlaufzeiten auf den Busleitungen, insbesondere auf der Hochgeschwindigkeits-Busleitung, erreicht.

Bei der in der Publikation EP-A-384 621 vorgestellten Erfindung muß auf jede Busleitung eine eigene aktive Einheit plaziert werden. Ein weiterer Nachteil besteht darin, daß die elektromagnetische Verträglichkeit des Systems für höhere Anforderungen nicht genügt.

Aufgabe der Erfindung ist es, eine universelle Lösung zu konzipieren, welche es ermöglicht, die 30 Steuerung schneller und langsamer Prozessabläufe mit nur einem (schnellen) Prozessor durchzuführen und dabei, unter Ausschaltung der Nachteile der bekannten Systeme, große Betriebssicherheit zu gewährleisten.

Die Aufgabe wird durch die Erfindung gelöst. Diese ist dadurch gekennzeichnet, daß zur Trennung in zwei Busbereiche eine Übernahmezeit-Verlängerungseinheit eingesetzt ist, welche über Datenbusse mit dem Hochgeschwindigkeits-Busbereich sowie dem Niedergeschwindigkeits-Busbereich verbunden ist.

35 Die Erfindung ist vorteilhaft, weil es durch die Trennung mittels einer Übernahmezeit-Verlängerungseinheit möglich ist, unter Verwendung nur eines Prozessors zwei Busbereiche mit jeweils genau definiertem Verwendungszweck zu erstellen. Dabei entspricht der Hochgeschwindigkeits-Busbereich zur Gänze den vom Prozessor angebotenen Bus-Zeitbedingungen.

Eine Weiterbildung der Erfindung ist dadurch gekennzeichnet, daß in der Übernahmezeit-Verlängerungseinheit für die Datenübertragung vom Niedergeschwindigkeits-Busbereich zu einem Prozessor ein Treiber vorgesehen ist, der bei einem Lesezugriff auf die am Niedergeschwindigkeits-Busbereich angeschlossene Peripherie niederohmig und in allen anderen Fällen hochohmig schaltet, und daß die Speicherung der Daten im Hochgeschwindigkeits-Busbereich mittels eines Signalspeichers, welcher im Transparenzmodus geschaltet ist, sobald ein Schreibzugriff auf eine der Einheiten am Niedergeschwindigkeits- 40 Busbereich erfolgt, durchführbar ist, und daß der Signalspeicher mittels einer zugeordneten Steuerung, die den Treiberteil des Signalspeichers einen oder mehrere Prozessorzyklen lang niederohmig geschaltet hält, danach hochohmig schaltet, und daß alle Signale vom Prozessor zum Niedergeschwindigkeits-Busbereich unmittelbar nach dem Treiber des Signalspeichers über Widerstände geführt sind und als vorgegebener Zustand am Niedergeschwindigkeits-Busbereich hochohmig gewählt ist, und daß eine Verzögerung von 45 50 Steuerleitungen mittels D-Flipflops vorgesehen ist, und daß diese Verzögerung synchron bis zur jeweils nächsten steigenden Flanke eines Prozessortaktes durchgeführt ist.

Durch diese erfindungsgemäße Weiterbildung werden die Treiber des Prozessors entlastet, so daß im Hochgeschwindigkeits-Busbereich die Einhaltung der Datenblatt-Zeitbedingungen gewährleistet ist. Da für den Niedergeschwindigkeits-Busbereich die gesamten Signalzeitbedingungen neu erzeugt werden, ergibt 55 sich eine große Unabhängigkeit dieses Niedergeschwindigkeits-Busbereiches vom eingesetzten Prozessor; dadurch ist ein Umstieg auf einen anderen (beispielsweise schnelleren) Prozessor problemlos durchführbar. Bei einer mechanisch entsprechend modularen Ausführung kann jener Schaltungsteil (selbstverständlich exklusive der Übernahmezeit-Verlängerungseinheit), der den Niedergeschwindigkeits-Busbereich enthält,

unverändert belassen werden.

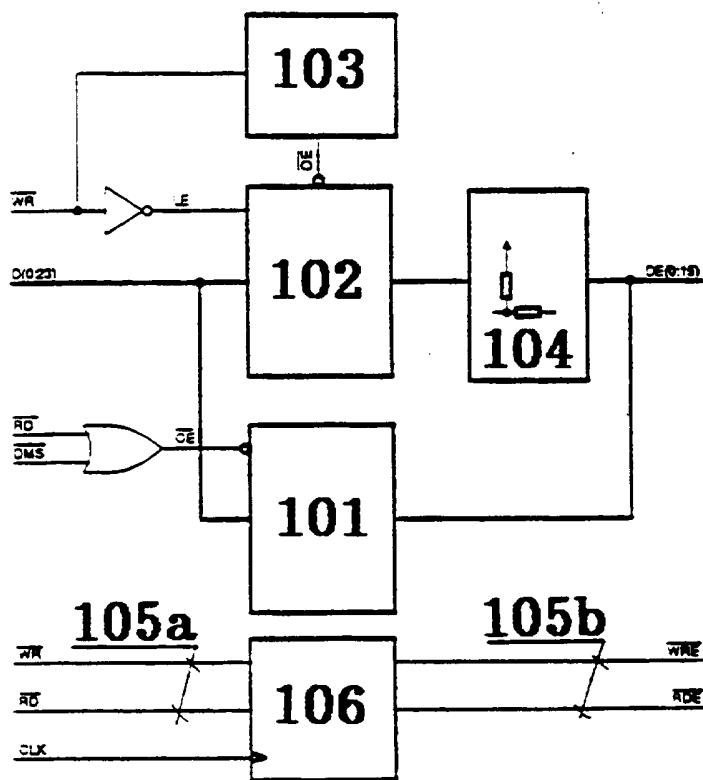

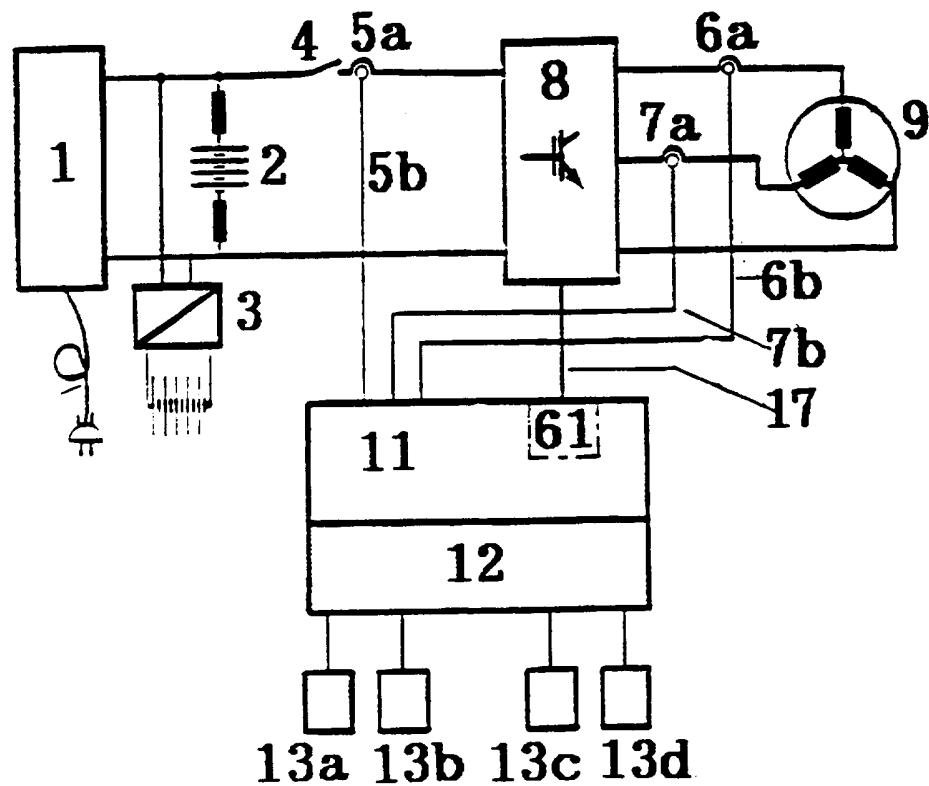

Anhand eines konkreten Ausführungsbeispiels soll die Erfindung näher erläutert werden. Dabei zeigt Fig. 1. die Schaltung der eingesetzten Übernahmezeit-Verlängerungseinheit. In Fig. 2 ist, in Form eines Blockschaltbildes, der Antrieb eines Elektroautos dargestellt. Die dabei eingezeichnete Digital-Signalprozessor-Platine benutzt, wie danach umfassend in Fig. 3 dargestellt, die erfundungsgemäße Einrichtung.

Lt. Fig. 1 ist in der Übernahmezeit-Verlängerungseinheit 21 für den Datentransfer vom Niedergeschwindigkeits-Busbereich 54 zum Prozessor 22 ein Treiber 101 eingesetzt, der bei einem Lesezugriff die am Niedergeschwindigkeits-Busbereich angeschlossene Peripherie aktiviert und in allen anderen Fällen hochohmig schaltet. Die Speicherung der Daten im Hochgeschwindigkeits-Busbereich erfolgt mittels eines Signalspeichers 102, welcher im Transparentmodus schaltbar ist, sobald ein Schreibzugriff auf eine der Einheiten am Niedergeschwindigkeits-Busbereich erfolgt. Der Treiber 101 ist mittels einer zugeordneten Steuerung 103, die den Treiberteil 29 einen oder mehrere Prozessorzyklen lang eingeschaltet hält, danach hochohmig geschaltet. Alle Signale vom Prozessor 22 zum Niedergeschwindigkeits-Busbereich, unmittelbar nach dem als Treiber fungierenden Signalspeicher 102, sind über Längswiderstände 104 geführt; zwischen einem Schreib- und Lesezugriff auf die am Niedergeschwindigkeits-Busbereich angeschlossene Peripherie liegt mindestens ein Prozessorzyklus, und als Standard-Zustand am Niedergeschwindigkeits-Busbereich ist hochohmig gewählt.

Aufgrund der in der Übernahmezeit-Verlängerungseinheit 21 auftretenden Verzögerung der Adreßsignale (über die Datenbusse 27, 28 lt. Fig. 3) ist eine Verzögerung der Steuerleitungen 105a, 105b mittels eines D-Flipflops 106 bis zur nächsten steigenden Flanke des Prozessortaktes notwendig.

Wie aus Fig. 2 ersichtlich, speist ein erstes Ladegerät 1a eine Fahrbatterie 2 höherer Spannung, sowie ein zweites Ladegerät 3a niedrigerer Spannung. Die Spannung von der Fahrbatterie 2 wird, über einen Schalter 4 und eine Gleichstrom-Meßvorrichtung 5a, einem als Wechselrichter 8 ausgeführten Leistungsteil zugeführt. Der Wechselrichter 8 speist über zwei Strommeßeinrichtungen 6a, 7a eine Asynchronmaschine 9 an. Sowohl von der Gleichstrom-Meßvorrichtung 5a als auch von den Strommeßeinrichtungen 6a, 7a führt je eine Meßleitung 6b, 7b zur Digital-Signalprozessor-Platine 11. Eine weitere Meßleitung 5b verbindet die Gleichstrom-Meßeinrichtung 5a mit der Digital-Signalprozessor-Platine 11. Der Wechselrichter 8 ist über eine Steuerleitung 17 mit einem Umrichter-Ansteuerungsmodul 61 der Digital-Signalprozessor-Platine 11 verbunden. Über eine Schnittstellenplatine 12, welche den Übergang zum Bereich niedrigerer Spannung bildet, sind externe Geber 13a, 13b, 13c und 13d angeschlossen.

Wie Fig. 3 zeigt, werden im Hochgeschwindigkeits-Busbereich 53 von einem Urlader-ROM 23 mit Hilfe einer Urladerspeicher-Selektierungsleitung 25 einem Analog-Digital-Signalprozessor 22 die Daten für dessen internes Programm-ROM zugeführt. Auf ein Programm-ROM 24 für den Analog-Digital-Signalprozessor 22 kann über den ersten und den zweiten Datenbus 26, 27 zugegriffen werden. Das Urlader-ROM 23 ist an den ersten und den zweiten Datenbus 26, 27 angeschlossen; als serielle Schnittstelle ist ein Treiber 29 vorgesehen ist, der über einen seriellen Datenbus 73 mit dem Analog-Digital-Signalprozessor 22 verbunden ist. Die Daten vom Analog-Digital-Signalprozessor 22 im Hochgeschwindigkeits-Busbereich 53 sind über eine Datenspeicher-Selektleitung 31 einem ersten Modul 60, welches einen Adreßdekkoder 51 und ein Überwachungsmodul 67 enthält, im Niedergeschwindigkeits-Busbereich 54 zuführbar.

Die zur Berechnung der zeitlichen Änderungen des Stromraumzeigerbetrages der Asynchronmaschine 9 notwendigen Stromänderungen werden von den zwei zwischen dem Stromrichter 8 und der Synchronmaschine 9 angeordneten Strommeßeinrichtungen 6a, 7a, - ersichtlich aus Fig. 2 - abgenommen und einem im Niedergeschwindigkeits-Busbereich (54) vorgesehenen, aus zwei Analog-Digital-Konvertern 68, 69 und einem Analog-Digital-Konverter-Zeitgeber 74 bestehendem ersten Modul 52 zugeführt, welches mit dem vierten Datenbus 30 verbunden ist. Die Regelungsparameter der Asynchronmaschine 9 sind über den dritten und vierten Datenbus 28, 30 einem EEPROM 59 zuführbar, welches über den dritten Datenbus 28 mit dem Adreßdekkoder 51 verbunden ist. Weiters ist ein aus drei Totzeitgeneratoren 62 und einem Umrichterschutz 63 bestehendes Umrichteransteuerungsmodul 61 vorgesehen, welches über den vierten Datenbus 30 mit dem EEPROM 59 sowie einem Inkrementaleingang 57 zur konventionellen Flußlagebestimmung verbunden ist. Alle im Zeitverhalten unkritischen Signale werden über den vierten Datenbus 30 einem Analog-Digital-Konverter 70 mit Mehrfachmultiplexer sowie ein sogenanntes „FIFO-Modul“ 71, welches die zuerst an den Speicher übernommene Information zuerst wieder ausgibt, und einem Analog-Digital-Konverter-Steuerungsmodul 72 bestehenden zweiten Modul 55 zugeführt. Weiters ist ein aus einem externen Zeitgeber 64 sowie einer Echtzeituhr 65 und einem batteriegepufferten RAM 66 bestehendes drittes Modul 58 vorgesehen, welches mit dem dritten und dem vierten Leitungsbus 28, 30 verbunden ist. Zur Übermittlung von Ansteuerungssignalen an Meßinstrumente des Elektroautos während des Fahrbetriebes ist ein Analog-Digital-Konverter 56 eingesetzt, welcher mit dem dritten und dem vierten Datenbus 28, 30 verbunden ist.

Durch die Zweiteilung der Digital-Signalprozessor-Platine wird also der Systembus zweigeteilt, nämlich in einen schnellen Teil (Hochgeschwindigkeits-Busbereich), auf den oft zugegriffen werden kann, und einen langsamen Teil (Niedergeschwindigkeits-Busbereich), auf den selten zugegriffen wird. Der Hochgeschwindigkeits-Busbereich entspricht dabei zur Gänze dem vom Prozessor angebotenen Bus-Zeitbedingungen.

- 5 5 Im Niedergeschwindigkeits-Busbereich werden folgende Eigenschaften realisiert: eine längere Haltezeit, um langsame Bausteine anschließen zu können; längere Impulszeiten, wodurch die erste Eckfrequenz des Leistungsdichtespektrums zu niedriger Frequenz gelegt wird; seltener Signalwechsel, wodurch die Wahrscheinlichkeit einer Störung von analogen Schaltungsteilen durch die (schnellen) Flanken der Bussignale reduziert wird.

- 10 10 Durch die Trennung des Prozessors von den langen Leitungen des Niedergeschwindigkeits-Busbereiches wird außerdem ein zusätzlicher Schutz des Prozessors vor auf langen Leitungen des Niedergeschwindigkeits-Busbereiches eingefangenen Störungen erzielt.

#### Patentansprüche

- 15 1. Einrichtung für eine Digital-Signalprozessor-Platine zur Anpassung eines schnellen Prozessors an langsame Bauteile, wobei eine Trennung dieser Platine in einen Hochgeschwindigkeits-Busbereich und einen Niedergeschwindigkeits-Busbereich durchgeführt ist, **dadurch gekennzeichnet**, daß zur Trennung in zwei Busbereiche (53, 54) eine Übernahmezeit-Verlängerungseinheit (21) eingesetzt ist, welche 20 über Datenbusse (26, 27 bzw. 28, 30) mit dem Hochgeschwindigkeits-Busbereich (53) sowie dem Niedergeschwindigkeits-Busbereich (54) verbunden ist.

- 25 2. Einrichtung nach Anspruch 1, **dadurch gekennzeichnet**, daß in der Übernahmezeit-Verlängerungseinheit (21) für die Datenübertragung vom Niedergeschwindigkeits-Busbereich (54) zu einem Prozessor (22) ein Treiber (101) vorgesehen ist, der bei einem Lesezugriff auf die am Niedergeschwindigkeits-Busbereich (54) angeschlossene Peripherie niederohmig und in allen anderen Fällen hochohmig geschaltet ist, und daß die Speicherung der Daten im Hochgeschwindigkeits-Busbereich (53) mittels 30 eines Signalspeichers (102), welcher im Transparenzmodus geschaltet ist, sobald ein Schreibzugriff auf eine der Einheiten am Niedergeschwindigkeits-Busbereich (54) erfolgt, durchführbar ist, und daß der Signalspeicher (102) mittels einer zugeordneten Steuerung (103), die den Treiberteil des Signalspeichers (102) einen oder mehrere Prozessorzyklen lang niederohmig geschaltet hält, danach hochohmig schaltet, und daß alle Signale vom Prozessor (22) zum Niedergeschwindigkeits-Busbereich (54) unmittelbar nach dem Treiber des Signalspeichers (102) über Widerstände (104) geführt sind und als 35 vorgegebener Zustand am Niedergeschwindigkeits-Busbereich (54) hochohmig gewählt ist, und daß diese Verzögerung von Steuerleitungen (105a) mittels D-Flipflops (106) vorgesehen ist, und daß diese Verzögerung synchron bis zur jeweils nächsten steigenden Flanke eines Prozessortaktes durchgeführt ist.

Hiezu 3 Blatt Zeichnungen

40

45

50

55

21

Fig. 1

Fig. 2