(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5224784号

(P5224784)

(45) 発行日 平成25年7月3日(2013.7.3)

(24) 登録日 平成25年3月22日(2013.3.22)

(51) Int.CI.

H01L 23/12 (2006.01)

F 1

H01L 23/12 501B

請求項の数 10 (全 39 頁)

(21) 出願番号 特願2007-290789 (P2007-290789)

(22) 出願日 平成19年11月8日 (2007.11.8)

(65) 公開番号 特開2009-117703 (P2009-117703A)

(43) 公開日 平成21年5月28日 (2009.5.28)

審査請求日 平成22年9月13日 (2010.9.13)

前置審査

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100107766

弁理士 伊東 忠重

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 堀内 章夫

長野県長野市小島田町80番地 新光電気

工業株式会社内

(72) 発明者 横田 泰志

長野県長野市小島田町80番地 新光電気

工業株式会社内

審査官 田代 吉成

最終頁に続く

(54) 【発明の名称】配線基板及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体素子が搭載される半導体素子搭載用パッドと、前記半導体素子搭載用パッドが設けられる絶縁層と、前記半導体素子が搭載される半導体素子搭載領域とを有する配線基板本体と、

前記半導体素子搭載用パッドが形成された側の前記絶縁層の面に接着され、前記半導体素子搭載領域を露出する半導体素子搭載用貫通部を有するスティフナーと、を備えた配線基板であって、

前記スティフナーに前記半導体素子搭載領域よりも外側に位置する部分の前記絶縁層の面を露出する貫通部が設けられ、

前記貫通部は、前記スティフナーの前記配線基板本体の各辺に対応する部分ごとに、複数設けられ、かつ、

前記貫通部の平面視における形状は、長方形において短辺が略半円となる形状であり、前記形状の長辺は、前記半導体素子搭載領域の1つの辺と対向するように設けられることを特徴とする配線基板。

## 【請求項 2】

前記配線基板本体は、前記絶縁層に設けられ、電子部品が搭載される電子部品搭載用パッドを有し、

前記スティフナーに、前記電子部品が搭載される領域に対応する部分の前記絶縁層の面を露出する電子部品搭載用貫通部を設けたことを特徴とする請求項1記載の配線基板。

**【請求項 3】**

前記貫通部と前記電子部品搭載用貫通部とを一体的に構成したことを特徴とする請求項2記載の配線基板。

**【請求項 4】**

前記半導体素子搭載用貫通部は、前記半導体素子を収容する収容部と、前記収容部の側壁に対応する部分のスティフナーに設けられ、前記絶縁層の面を露出する他の切り欠き部とを有することを特徴とする請求項1ないし3のうち、いずれか一項記載の配線基板。

**【請求項 5】**

半導体素子が搭載される半導体素子搭載用パッドと、前記半導体素子搭載用パッドが設けられる絶縁層と、前記半導体素子が搭載される半導体素子搭載領域とを有する配線基板本体と。10

前記半導体素子搭載用パッドが形成された側の前記絶縁層の面に接着され、前記半導体素子搭載領域を露出する半導体素子搭載用貫通部を有するスティフナーと、を備えた配線基板の製造方法であって、

複数の前記配線基板本体が隣接するように配置され、前記複数の配線基板本体が一体的に構成された基板を形成する基板形成工程と、

前記半導体素子搭載領域に対応する部分の前記基板を露出する前記半導体素子搭載用貫通部と、前記半導体素子搭載領域よりも外側に位置する部分の前記絶縁層の面を露出する貫通部とを備え、複数の前記スティフナーの母材となるスティフナー母材を形成するスティフナー母材形成工程と。20

接着剤により、前記基板に設けられた前記絶縁層の面に前記スティフナー母材を接着する接着工程と、

前記接着工程後に、前記基板及び前記スティフナー母材を切断して、前記複数の配線基板本体及び前記複数のスティフナーを個片化する切断工程と、を含むことを特徴とする配線基板の製造方法。

**【請求項 6】**

前記貫通部は、前記配線基板本体の外周部に対応する部分の前記絶縁層の面から隣り合う他の前記配線基板本体の外周部に対応する部分の前記絶縁層の面に亘る領域の前記絶縁層の面を露出するように形成することを特徴とする請求項5記載の配線基板の製造方法。

**【請求項 7】**

前記スティフナー母材形成工程では、前記半導体素子搭載用貫通部及び前記貫通部を同時に形成することを特徴とする請求項5又は6に記載の配線基板の製造方法。

**【請求項 8】**

前記基板は、前記絶縁層に設けられ、電子部品が搭載される電子部品搭載用パッドを有し、

前記スティフナー母材は、前記電子部品搭載用パッドが形成される領域に対応する部分の前記絶縁層の面を露出する電子部品搭載用貫通部を備え、

前記スティフナー母材形成工程では、前記電子部品搭載用貫通部と前記半導体素子搭載用貫通部及び前記貫通部とを同時に形成することを特徴とする請求項5又は6記載の配線基板の製造方法。40

**【請求項 9】**

前記接着工程の前に、前記電子部品を前記電子部品搭載用パッドに搭載する電子部品搭載工程を設けたことを特徴とする請求項8記載の配線基板の製造方法。

**【請求項 10】**

絶縁層と、該絶縁層上に設けられた、半導体素子が搭載される半導体素子搭載用パッドと、前記半導体素子が搭載される半導体素子搭載領域よりも外側に形成された、電子部品が搭載される電子部品搭載用パッドとを有する配線基板本体と、

前記半導体素子搭載用パッドが形成された側の前記絶縁層の面に接着され、前記半導体素子搭載領域を露出する半導体素子搭載用貫通部と前記電子部品搭載用パッドを露出する電子部品搭載用貫通部とを有するスティフナーと、を備えた配線基板の製造方法であって50

、前記電子部品搭載用パッドに前記電子部品を搭載する電子部品搭載工程と、該電子部品搭載工程の後に、接着剤を介して前記スティフナーを前記半導体素子搭載用パッドが形成された側の前記絶縁層の面に密着させて、余分な接着剤を前記電子部品搭載用貫通部内にはみ出させる接着工程と、を含むことを特徴とする配線基板の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スティフナーを備えた配線基板に関する。

【背景技術】

10

【0002】

従来の配線基板には、配線基板本体の反りを低減するためのスティフナーを備えた配線基板(図1参照)がある。

【0003】

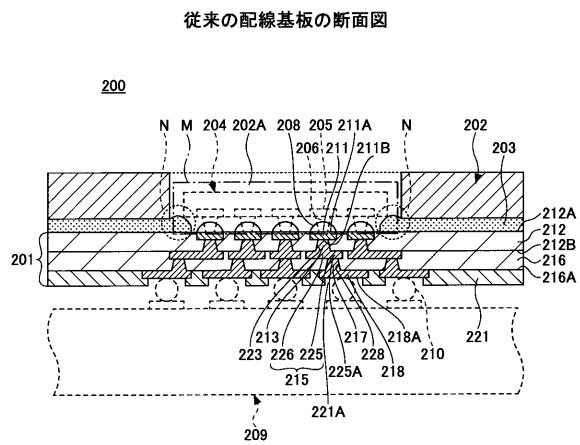

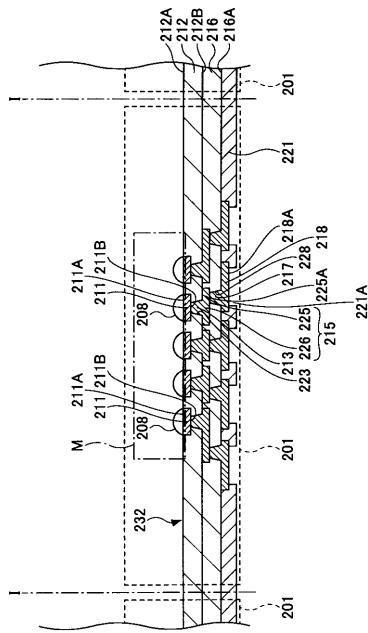

図1は、従来の配線基板の断面図である。

【0004】

図1を参照するに、従来の配線基板200は、配線基板本体201と、スティフナー202とを有する。

【0005】

20

配線基板本体201は、コアレス基板であり、半導体素子搭載用パッド211と、樹脂材からなる絶縁層212, 216と、ビア213, 217と、配線パターン215と、外部接続用パッド218と、ソルダーレジスト層221とを有する。

【0006】

半導体素子搭載用パッド211は、半導体素子204が搭載される搭載面211Aを有する。半導体素子搭載用パッド211は、搭載面211Aと絶縁層212の面212Aとが略面一となるように、絶縁層212に内設されている。搭載面211Aには、半導体素子204の電極パッド205に設けられた内部接続端子206を半導体素子搭載用パッド211上に固定するためのはんだ208が設けられている。

【0007】

30

絶縁層212は、半導体素子搭載用パッド211、ビア213、及び配線パターン215を形成するための絶縁層である。絶縁層212は、半導体素子搭載用パッド211の面211B(搭載面211Aとは反対側に位置する半導体素子搭載用パッド211の面)を露出する開口部223を有する。

【0008】

ビア213は、開口部223に設けられている。ビア213の一方の端部は、半導体素子搭載用パッド211と電気的に接続されており、ビア213の他方の端部は、配線パターン215と一体的に構成されている。

【0009】

40

配線パターン215は、パッド225と、配線226とを有する。パッド225は、絶縁層212の面212Bに設けられている。パッド225は、配線226と一体的に構成されている。パッド225は、配線226を介して、ビア213と電気的に接続されている。配線226は、絶縁層212の面212Bに設けられている。配線226は、ビア213及びパッド225と一体的に構成されている。配線226は、ビア213とパッド225とを電気的に接続している。

【0010】

絶縁層216は、配線226を覆うように、絶縁層212の面212Bに設けられている。絶縁層216は、パッド225の面225Aを露出する開口部228を有する。

【0011】

ビア217は、開口部228に設けられている。ビア217の一方の端部は、パッド225と接続されており、ビア217の他方の端部は、外部接続用パッド218と一体的に

50

構成されている。

【0012】

外部接続用パッド218は、ビア217の他方の端部及び絶縁層216の面216Aに設けられている。外部接続用パッド218は、ビア217を介して、パッド225と電気的に接続されている。外部接続用パッド218は、外部接続端子210が配設される端子配設面218Aを有する。外部接続用パッド218は、外部接続端子210を介して、マザーボード等の実装基板209と電気的に接続されるパッドである。

【0013】

ソルダーレジスト層221は、絶縁層216の面216Aに設けられている。ソルダーレジスト層221は、端子配設面218Aを露出する開口部221Aを有する。

10

【0014】

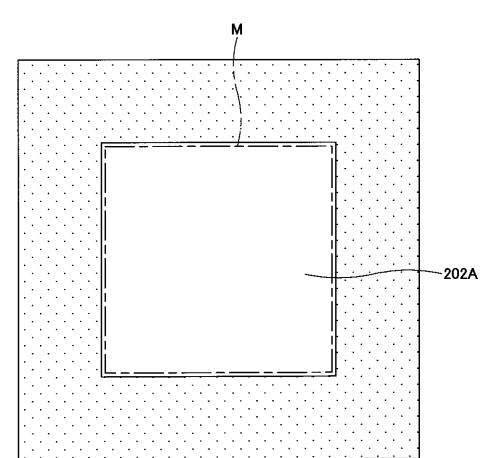

図2は、図1に示すスティフナーの平面図である。

【0015】

図1及び図2を参照するに、スティフナー202は、平面視額縁形状とされており、接着剤203により、絶縁層212の面212Aに接着されている。スティフナー202は、半導体素子搭載領域Mを露出する開口部202Aを有する。開口部202Aは、配線基板本体201に搭載される半導体素子204を収容するための開口部である。スティフナー202の母材としては、例えば、金属板やガラスエポキシ基板等を用いることができる。また、接着剤203としては、例えば、絶縁層212, 216に用いる樹脂と同様な組成からなる液状やシート状のエポキシ樹脂を用いることができる。

20

【0016】

このように、反りの発生しやすい配線基板本体201にスティフナー202を設けることにより、配線基板本体201の反りを低減することができる。

【0017】

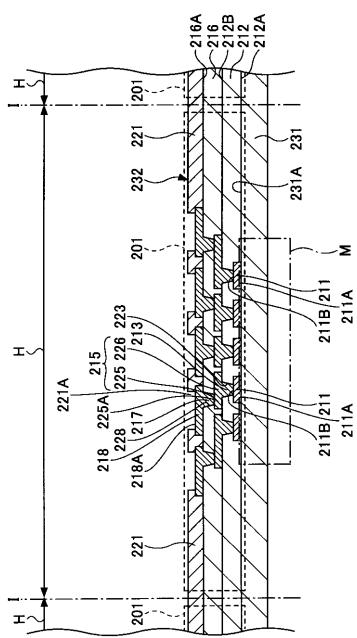

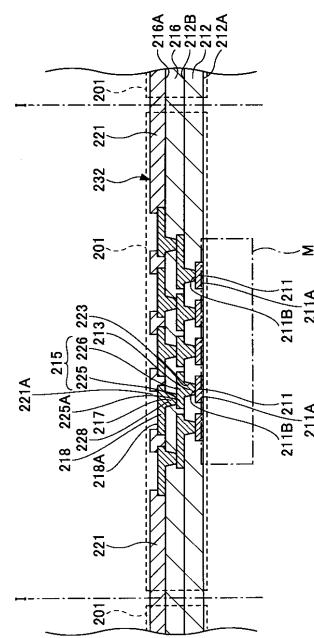

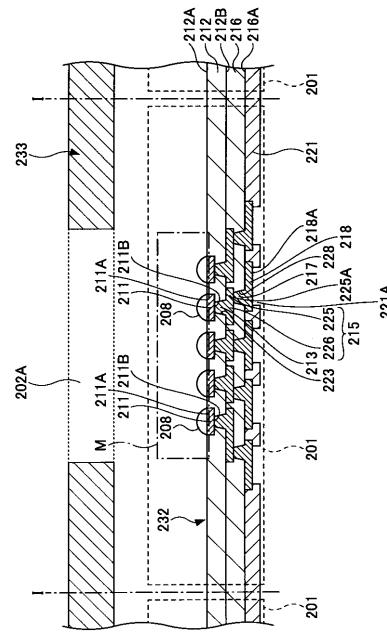

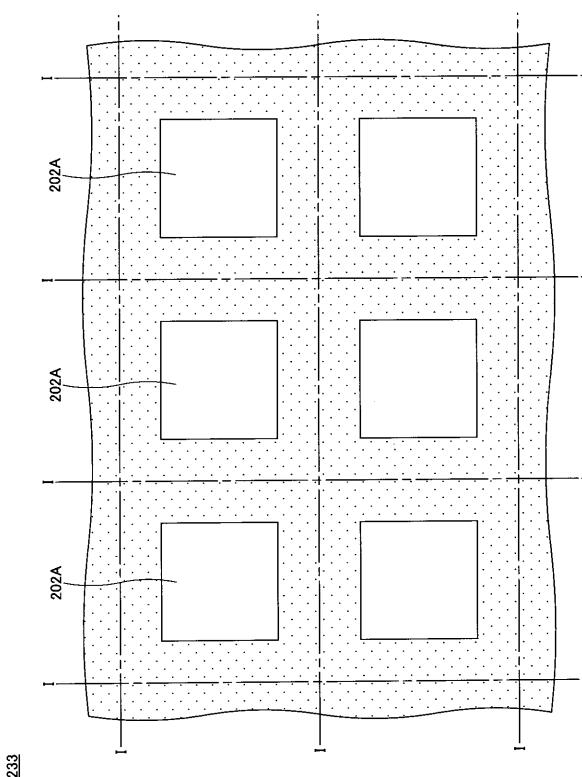

図3～図8は、従来の配線基板の製造工程を示す図であり、図9は、従来のスティフナー母材の平面図である。図3～図9において、従来の配線基板200と同一構成部分には同一符号を付す。

【0018】

図3～図9を参照して、従来の配線基板200の製造方法について説明する。始めに、図3に示す工程では、周知の手法により、導電性を有すると共に、配線基板本体201が形成される配線基板本体形成領域Hを複数有した支持体231の上面231Aに複数の配線基板本体201が一体的に構成された基板232を形成する。

30

【0019】

次いで、図4に示す工程では、図3に示す支持体231を除去する。次いで、図5に示す工程では、図4に示す基板232を上下反転させた後、基板232に設けられた半導体素子搭載用パッド211の搭載面211Aにはんだ208を形成する。

【0020】

次いで、図6に示す工程では、金属板或いはガラスエポキシ基板を加工して、複数の開口部202Aを有したスティフナー母材233(図9参照)を形成し、その後、半導体素子搭載領域Mと開口部202Aが対向するように、基板232とスティフナー母材233とを対向配置させる。スティフナー母材233は、切断位置Iにおいて切断されることで、複数のスティフナー202(図1及び図2参照)となる部材である。

40

【0021】

次いで、図7に示す工程では、接着剤203により、スティフナー母材233を絶縁層212の面212Aに接着させる。これにより、複数の配線基板200に相当する構造体が形成される。

【0022】

次いで、図8に示す工程では、切断位置Iに対応する部分の基板232及びスティフナー母材233を切断することにより、複数の配線基板200が個片化される。基板232及びスティフナー母材233の切断には、例えば、ダイサーやスライサー等を用いること

50

ができる（例えば、特許文献1参照。）。

【特許文献1】特開2000-323613号公報

【発明の開示】

【発明が解決しようとする課題】

【0023】

しかしながら、従来の半導体装置200の製造方法では、スティフナー母材233を絶縁層212の面212Aに接着させた際、半導体素子搭載領域Mに対応する部分の絶縁層212の面212Aに余分な接着剤203がはみ出してしまう（以下、半導体素子搭載領域Mに対応する部分の絶縁層212の面212Aにはみ出した部分の接着剤203を「はみ出し部分N」とする）。

10

【0024】

このため、接着剤203のはみ出し部分Nの高さが内部接続端子206の高さよりも高い場合、半導体素子204と接着剤203のはみ出し部分Nとが接触して、内部接続端子206と半導体素子搭載用パッド211との間で電気的な接続不良が発生するという問題があった。言い換えれば、配線基板本体201に設けられた半導体素子搭載用パッド211と半導体素子204との間の電気的な接続信頼性が低下してしまうという問題があった。

【0025】

そこで本発明は、上述した問題点に鑑みなされたものであり、配線基板本体に設けられた半導体素子搭載用パッドと半導体素子との間の電気的な接続信頼性を向上させることのできる配線基板及びその製造方法を提供することを目的とする。

20

【課題を解決するための手段】

【0026】

本発明の一観点によれば、半導体素子が搭載される半導体素子搭載用パッドと、前記半導体素子搭載用パッドが設けられる絶縁層と、前記半導体素子が搭載される半導体素子搭載領域とを有する配線基板本体と、前記半導体素子搭載用パッドが形成された側の前記絶縁層の面に接着され、前記半導体素子搭載領域を露出する半導体素子搭載用貫通部を有するスティフナーと、を備えた配線基板であって、前記スティフナーに前記半導体素子搭載領域よりも外側に位置する部分の前記絶縁層の面を露出する貫通部が設けられ、前記貫通部は、前記スティフナーの前記配線基板本体の各辺に対応する部分ごとに、複数設けられ、かつ、前記貫通部の平面視における形状は、長方形において短辺が略半円となる形状であり、前記形状の長辺は、前記半導体素子搭載領域の1つの辺と対向するように設けられることを特徴とする配線基板が提供される。

30

【0027】

本発明によれば、半導体素子搭載用パッドが形成された側の絶縁層の面に接着されるスティフナーの外周部に半導体素子搭載領域よりも外側に位置する部分の絶縁層の面を露出する貫通部を設けることにより、スティフナーと絶縁層とを接着する際に用いられる接着剤のうち、余分な接着剤を貫通部に露出された部分の絶縁層の面にはみ出させ、半導体素子搭載領域に対応する部分の絶縁層の面にはみ出る余分な接着剤の量を少なくして、半導体素子搭載領域に対応する部分の絶縁層の面にはみ出る余分な接着剤の高さを低くすることが可能となる。

40

【0028】

これにより、半導体素子搭載領域に対応する部分の絶縁層の面にはみ出た余分な接着剤と半導体素子搭載用パッドに搭載される半導体素子とが接触することがなくなるため、半導体素子搭載用パッドと半導体素子とを精度良く電気的に接続することが可能となるので、配線基板本体に設けられた半導体素子搭載用パッドと半導体素子との間の電気的な接続信頼性を向上させることができる。

【0030】

本発明によれば、半導体素子搭載用パッドが形成された側の絶縁層の面に接着されるスティフナーに半導体素子搭載領域よりも外側に位置する部分の絶縁層の面を露出する切り

50

欠き部を設けることにより、スティフナーと絶縁層とを接着する際に用いられる接着剤のうち、余分な接着剤を切り欠き部に露出された部分の絶縁層の面にはみ出させ、半導体素子搭載領域に対応する部分の絶縁層の面にはみ出る余分な接着剤の量を少なくして、半導体素子搭載領域に対応する部分の絶縁層の面にはみ出る余分な接着剤の高さを低くすることが可能となる。

【0031】

これにより、半導体素子搭載領域に対応する部分の絶縁層の面にはみ出た余分な接着剤と半導体素子搭載用パッドに搭載される半導体素子とが接触することがなくなるため、半導体素子搭載用パッドと半導体素子とを精度良く電気的に接続することが可能となるので、配線基板本体に設けられた半導体素子搭載用パッドと半導体素子との間の電気的な接続信頼性を向上させることができる。

10

【0032】

本発明のその他の観点によれば、半導体素子が搭載される半導体素子搭載用パッドと、前記半導体素子搭載用パッドが設けられる絶縁層と、前記半導体素子が搭載される半導体素子搭載領域とを有する配線基板本体と、前記半導体素子搭載用パッドが形成された側の前記絶縁層の面に接着され、前記半導体素子搭載領域を露出する半導体素子搭載用貫通部を有するスティフナーと、を備えた配線基板の製造方法であって、複数の前記配線基板本体が隣接するように配置され、前記複数の配線基板本体が一体的に構成された基板を形成する基板形成工程と、前記半導体素子搭載領域に対応する部分の前記基板を露出する前記半導体素子搭載用貫通部と、前記半導体素子搭載領域よりも外側に位置する部分の前記絶縁層の面を露出する貫通部とを備え、複数の前記スティフナーの母材となるスティフナー母材を形成するスティフナー母材形成工程と、接着剤により、前記基板に設けられた前記絶縁層の面に前記スティフナー母材を接着する接着工程と、前記接着工程後に、前記基板及び前記スティフナー母材を切断して、前記複数の配線基板本体及び前記複数のスティフナーを個片化する切断工程と、を含むことを特徴とする配線基板の製造方法が提供される。

20

【0033】

本発明によれば、複数の配線基板本体が隣接するように配置され、複数の配線基板本体が一体的に構成された基板を形成し、半導体素子搭載領域に対応する部分の基板を露出する半導体素子搭載用貫通部と、半導体素子搭載領域よりも外側に位置する部分の絶縁層の面を露出する貫通部とを備え、複数のスティフナーの母材となるスティフナー母材を形成し、接着剤により、基板に設けられた絶縁層の面にスティフナー母材を接着し、その後、基板及びスティフナー母材を切断して、複数の配線基板本体及び複数のスティフナーを個片化することにより、スティフナー母材と絶縁層とを接着する接着剤のうち、余分な接着剤を貫通部に露出された部分の絶縁層の面にはみ出させ、半導体素子搭載領域に対応する部分の絶縁層の面にはみ出る余分な接着剤の量を少なくして、半導体素子搭載領域に対応する部分の絶縁層の面にはみ出る余分な接着剤の高さを低くすることが可能となる。これにより、半導体素子搭載領域に対応する部分の絶縁層の面にはみ出た余分な接着剤と半導体素子搭載用パッドに搭載される半導体素子とが接触することがなくなるため、半導体素子搭載用パッドと半導体素子とを精度良く電気的に接続することが可能となるので、配線基板本体に設けられた半導体素子搭載用パッドと半導体素子との間の電気的な接続信頼性を向上させることができる。

30

【0034】

また、配線基板本体の外周部に対応する部分の絶縁層の面から隣り合う他の配線基板本体の外周部に対応する部分の絶縁層の面に亘る領域の絶縁層の面を露出する貫通部を形成してもよい。

40

【0035】

これにより、切断工程において、貫通部を通過するようにスティフナー母材が切断されるため、切断工程に要する時間を従来よりも短縮することができる。また、スティフナー母材を切断する際に使用する切断

50

用工具（例えば、ダイサーヤやスライサー等）の磨耗量を少なくすることが可能となるため、配線基板の製造コストを低減することができる。

本発明のその他の観点によれば、絶縁層と、該絶縁層上に設けられた、半導体素子が搭載される半導体素子搭載用パッドと、前記半導体素子が搭載される半導体素子搭載領域よりも外側に形成された、電子部品が搭載される電子部品搭載用パッドとを有する配線基板本体と、前記半導体素子搭載用パッドが形成された側の前記絶縁層の面に接着され、前記半導体素子搭載領域を露出する半導体素子搭載用貫通部と前記電子部品搭載用パッドを露出する電子部品搭載用貫通部とを有するスティフナーと、を備えた配線基板の製造方法であって、前記電子部品搭載用パッドに前記電子部品を搭載する電子部品搭載工程と、該電子部品搭載工程の後に、接着剤を介して前記スティフナーを前記半導体素子搭載用パッドが形成された側の前記絶縁層の面に密着させて、余分な接着剤を前記電子部品搭載用貫通部内にはみ出させる接着工程と、を含むことを特徴とする配線基板の製造方法が提供される。10

#### 【発明の効果】

##### 【0036】

本発明によれば、配線基板本体に設けられた半導体素子搭載用パッドと半導体素子との間の電気的な接続信頼性を向上させることができる。

#### 【発明を実施するための最良の形態】

##### 【0037】

次に、図面に基づいて本発明の実施の形態について説明する。20

##### 【0038】

###### （第1の実施の形態）

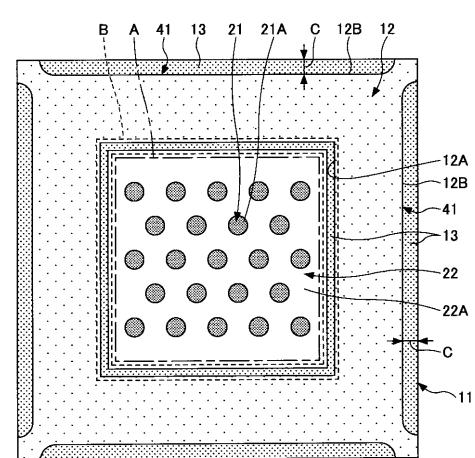

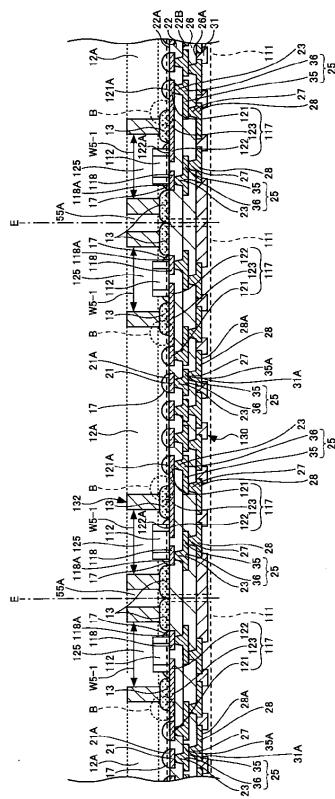

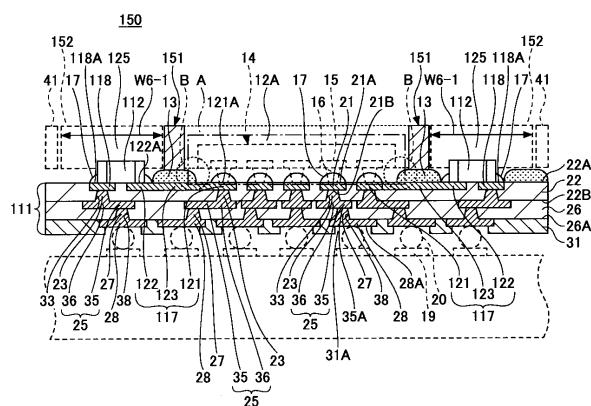

図10は、本発明の第1の実施の形態に係る配線基板の断面図であり、図11は、図10に示す配線基板の平面図である。図11では、図10に示すはんだ17の図示を省略する。

##### 【0039】

図10及び図11を参照するに、第1の実施の形態の配線基板10は、配線基板本体11と、スティフナー12とを有する。配線基板本体11は、平面視四角形とされたコアレス基板であり、半導体素子14が搭載される領域に対応する部分の半導体素子搭載用パッド21及び絶縁層22により構成された半導体素子搭載領域Aと、半導体素子搭載用パッド21と、絶縁層22, 26と、ビア23, 27と、配線パターン25と、外部接続用パッド28と、ソルダーレジスト層31とを有する。30

##### 【0040】

半導体素子搭載用パッド21は、半導体素子14が搭載される搭載面21Aを有する。半導体素子搭載用パッド21は、搭載面21Aと絶縁層22の面22Aとが略面一となるように、絶縁層22に内設されている。搭載面21Aには、半導体素子14の電極パッド15に設けられた内部接続端子16を半導体素子搭載用パッド21上に固定するためのはんだ17が設けられている。

##### 【0041】

半導体素子搭載用パッド21としては、例えば、絶縁層22の面22A側からAu層（例えば、厚さ0.5μm）と、Ni層（例えば、厚さ5.0μm）とを順次積層させたAu/Ni積層膜、絶縁層22の面22A側からAu層、Pd層、Ni層の順に積層したAu/Pd/Ni積層膜、絶縁層22の面22A側からAu層、Pd層の順に積層したAu/Pd積層膜等を用いることができる。内部接続端子16としては、例えば、バンプ（例えば、はんだバンプやAuバンプ）を用いることができる。内部接続端子16の高さは、例えば、20μm～50μmとすることができます。

##### 【0042】

絶縁層22は、半導体素子搭載用パッド21、ビア23、及び配線パターン25を形成するための絶縁層である。絶縁層22は、半導体素子搭載用パッド21の面21B（搭載

10

20

30

40

50

面 2 1 A の反対側に位置する半導体素子搭載用パッド 2 1 の面 ) を露出する開口部 3 3 を有する。絶縁層 2 2 としては、例えば、絶縁樹脂層を用いることができる。絶縁層 2 2 となる絶縁樹脂層の材料としては、例えば、エポキシ系樹脂やポリイミド樹脂等を用いることができる。また、開口部 3 3 は、例えば、レーザ加工法により形成することができる。

【 0 0 4 3 】

ビア 2 3 は、開口部 3 3 に設けられている。ビア 2 3 の一方の端部は、半導体素子搭載用パッド 2 1 と接続されており、ビア 2 3 の他方の端部は、配線パターン 2 5 と一体的に構成されている。

【 0 0 4 4 】

配線パターン 2 5 は、パッド 3 5 と、配線 3 6 とを有する。パッド 3 5 は、絶縁層 2 2 の面 2 2 B に設けられている。パッド 3 5 は、配線 3 6 と一体的に構成されている。パッド 3 5 は、配線 3 6 を介して、ビア 2 3 と電気的に接続されている。配線 3 6 は、絶縁層 2 2 の面 2 2 B ( 半導体素子搭載用パッド 2 1 が設けられた側とは反対側の絶縁層 2 2 の面 ) に設けられている。配線 3 6 は、ビア 2 3 及びパッド 3 5 と一体的に構成されている。配線 3 6 は、ビア 2 3 とパッド 3 5 とを電気的に接続している。上記構成とされたビア 2 3 及び配線パターン 2 5 の材料としては、例えば、Cu を用いることができる。また、配線 3 6 の厚さは、例えば、15 μm とすることができます。

【 0 0 4 5 】

絶縁層 2 6 は、配線 3 6 を覆うように、絶縁層 2 2 の面 2 2 B に設けられている。絶縁層 2 6 は、パッド 3 5 の面 3 5 A を露出する開口部 3 8 を有する。絶縁層 2 6 としては、例えば、絶縁樹脂層を用いることができる。絶縁層 2 6 となる絶縁樹脂層の材料としては、例えば、エポキシ系樹脂やポリイミド樹脂等を用いることができる。また、開口部 3 8 は、例えば、レーザ加工法により形成することができる。

【 0 0 4 6 】

ビア 2 7 は、開口部 3 8 に設けられている。ビア 2 7 の一方の端部は、パッド 3 5 と接続されており、ビア 2 7 の他方の端部は、外部接続用パッド 2 8 と一体的に構成されている。

【 0 0 4 7 】

外部接続用パッド 2 8 は、ビア 2 7 の他方の端部及び絶縁層 2 6 の面 2 6 A に設けられている。外部接続用パッド 2 8 は、ビア 2 7 を介して、パッド 3 5 と電気的に接続されている。外部接続用パッド 2 8 は、外部接続端子 2 0 が配設される端子配設面 2 8 A を有する。外部接続用パッド 2 8 は、外部接続端子 2 0 を介して、マザーボード等の実装基板 1 8 に設けられたパッド 1 9 と電気的に接続されるパッドである。

【 0 0 4 8 】

上記構成とされたビア 2 7 及び外部接続用パッド 2 8 の材料としては、例えば、Cu を用いることができる。また、外部接続用パッド 2 8 の厚さは、例えば、15 μm とすることができます。

【 0 0 4 9 】

ソルダーレジスト層 3 1 は、絶縁層 2 6 の面 2 6 A に設けられている。ソルダーレジスト層 3 1 は、端子配設面 2 8 A を露出する開口部 3 1 A を有する。

【 0 0 5 0 】

スティフナー 1 2 は、平面視略額縁形状とされており、半導体素子搭載用貫通部 1 2 A と、切り欠き部 4 1 を有する。スティフナー 1 2 は、半導体素子搭載用貫通部 1 2 A が半導体素子搭載領域 A を露出するように、接着剤 1 3 により、絶縁層 2 2 の面 2 2 A に接着されている。半導体素子搭載用貫通部 1 2 A は、配線基板本体 1 1 の半導体素子搭載領域 A に搭載される半導体素子 1 4 を収容するための空間である。

【 0 0 5 1 】

切り欠き部 4 1 は、スティフナー 1 2 の外周部に複数 ( この場合 4 つ ) 設けられており、平面視四角形とされた配線基板本体 1 1 の各辺にそれぞれ 1 つの切り欠き部 4 1 が対応するように配置されている。切り欠き部 4 1 は、配線基板本体 1 1 に設けられた絶縁層 2

10

20

30

40

50

2の面22Aにスティフナー12を配置した状態において、半導体素子搭載領域Aよりも外側に位置する部分の絶縁層22の面22Aを露出するように構成されている。

【0052】

このように、半導体素子搭載領域Aよりも外側に位置する部分の絶縁層22の面22Aを露出する切り欠き部41をスティフナー12に設けることにより、スティフナー12と絶縁層22とを接着する接着剤13のうち、余分な接着剤13を切り欠き部41に露出された部分の絶縁層22の面22Aにはみ出させて、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出る余分な接着剤13(図10及び図11に示す領域Bに対応する部分の接着剤13)の量を少なくして、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出る余分な接着剤13の高さを従来よりも低くすることが可能となる。

10

【0053】

これにより、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出た余分な接着剤13と半導体素子搭載用パッド21に搭載される半導体素子14との接触を防止することが可能となるため、半導体素子搭載用パッド21と半導体素子14とを精度良く電気的に接続することが可能となり、配線基板本体11に設けられた半導体素子搭載用パッド21と半導体素子14との間の電気的な接続信頼性を向上させることができる。

【0054】

切り欠き部41が形成された部分のスティフナー12の側壁12Bから配線基板本体11の外周縁までの配線基板10の面方向の距離Cは、例えば、100μm～500μmとすることができる。

20

【0055】

上記構成とされたスティフナー12の母材としては、金属板(例えば、Cu板、Cu合金板、Al板、ステンレス板等)やガラスエポキシ基板等の樹脂板を用いることができる。スティフナー12の母材としてCu板を用いた場合、スティフナー12の厚さは、例えば、1～2mmとすることができる。また、接着剤13としては、例えば、絶縁層22、26に用いる樹脂と同様な組成からなる液状やシート状のエポキシ樹脂を用いることができる。

【0056】

本実施の形態の配線基板によれば、半導体素子搭載領域Aよりも外側に位置する部分の絶縁層22の面22Aを露出する切り欠き部41をスティフナー12に設けることにより、スティフナー12と絶縁層22とを接着する接着剤13のうち、余分な接着剤13を切り欠き部41に露出された部分の絶縁層22の面22Aにはみ出させて、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出る余分な接着剤13の高さを従来よりも低くすることが可能となる。

30

【0057】

これにより、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出た余分な接着剤13と半導体素子搭載用パッド21に搭載される半導体素子14との接触を防止することが可能となるため、半導体素子搭載用パッド21と半導体素子14とを精度良く電気的に接続することが可能となり、配線基板本体11に設けられた半導体素子搭載用パッド21と半導体素子14との間の電気的な接続信頼性を向上させることができる。

40

【0058】

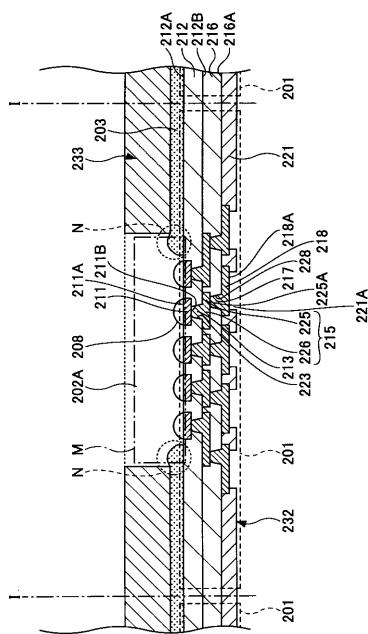

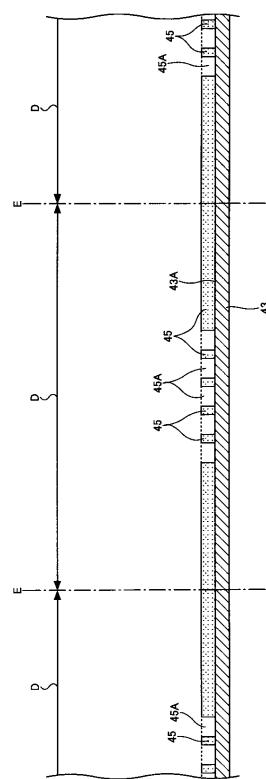

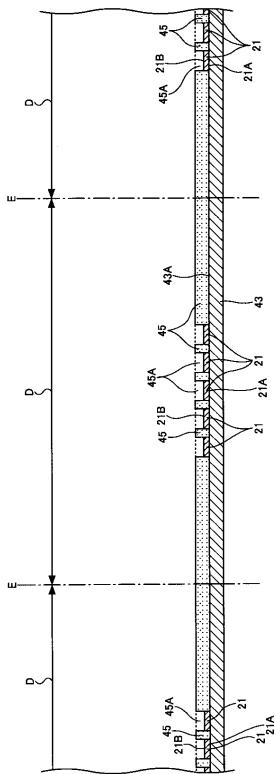

図12～図23は、本発明の第1の実施の形態に係る配線基板の製造工程を示す図であり、図24は、図21に示すスティフナー母材の平面図である。図12～図24において、第1の実施の形態の配線基板10と同一構成部分には同一符号を付す。

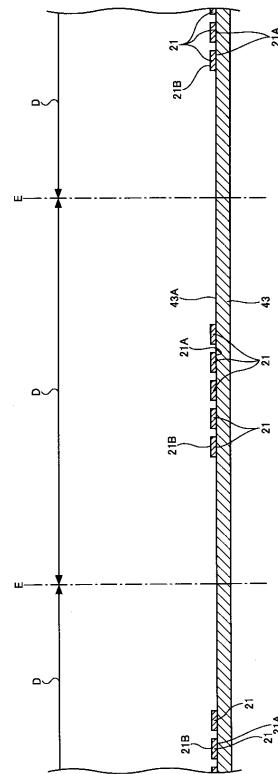

【0059】

図12～図24を参照して、第1の実施の形態の配線基板10の製造方法について説明する。始めに、図12に示す工程では、導電性を有すると共に、配線基板本体11が形成される配線基板本体形成領域Dを複数有した支持体43の上面43Aに、開口部45Aを有しためっき用レジストパターン45を形成する。開口部45Aは、半導体素子搭載用パ

50

ツド 2 1 の形成領域に対応する部分の支持体 4 3 の上面 4 3 A を露出するように形成する。支持体 4 3 としては、例えば、金属箔や金属板等を用いることができる。支持体 4 3 となる金属箔及び金属板の材料としては、例えば、Cu、Al、ステンレスや他の金属を用いることができる。

#### 【 0 0 6 0 】

次いで、図 1 3 に示す工程では、導電性を有した支持体 4 3 を給電層とする電解めっき法により、開口部 4 5 A に露出された部分の支持体 4 3 の上面 4 3 A に半導体素子搭載用パッド 2 1 を形成する。半導体素子搭載用パッド 2 1 は、支持体 4 3 をエッティングで除去する際のエッティング液に溶解しない金属膜により構成するとよい。具体的には、支持体 4 3 の材料が Cu の場合、半導体素子搭載用パッド 2 1 としては、例えば、支持体 4 3 の上面 4 3 A に Au 層（例えば、厚さ 0.5 μm）と、Ni 層（例えば、厚さ 5.0 μm）とを順次積層させた Au / Ni 積層膜、支持体 4 3 の上面 4 3 A に Au 層、Pd 層、Ni 層の順に積層した Au / Pd / Ni 積層膜、支持体 4 3 の上面 4 3 A に Au 層、Pd 層の順に積層した Au / Pd 積層膜等を用いることができる。

#### 【 0 0 6 1 】

次いで、図 1 4 に示す工程では、図 1 3 に示すめっき用レジストパターン 4 5 を除去する。次いで、図 1 5 に示す工程では、支持体 4 3 の上面 4 3 A に、開口部 3 3 を有した絶縁層 2 2 を形成する。絶縁層 2 2 としては、例えば、絶縁樹脂層を用いることができる。絶縁層 2 2 は、例えば、シート状の絶縁樹脂層を半導体素子搭載用パッド 2 1 が形成された支持体 4 3 の上面 4 3 A に貼り付け、その後、シート状の絶縁樹脂層にレーザを照射して開口部 3 3 を加工することで形成する。絶縁層 2 2 となる絶縁樹脂層の材料としては、例えば、エポキシ系樹脂やポリイミド樹脂等を用いることができる。

#### 【 0 0 6 2 】

次いで、図 1 6 に示す工程では、例えば、セミアディティブ法により、ビア 2 3 及び配線パターン 2 5 を同時に形成する。具体的には、開口部 3 3 に露出された部分の半導体素子搭載用パッド 2 1 の面 2 1 B、開口部 3 3 の側面に対応する部分の絶縁層 2 2 の面、及び絶縁層 2 2 の面 2 2 B を覆うようにシード層（図示せず）を形成し、次いで、シード層上に、配線パターン 2 5 の形成領域に対応する部分のシード層を露出する開口部（図示せず）を有しためっき用レジストパターン（図示せず）を形成し、次いで、シード層を給電層とする電解めっき法により、開口部に露出された部分のシード層上にめっき膜（図示せず）を析出成長させ、その後、めっき用レジストパターンを除去し、次いで、めっき膜が形成されていない部分の不要なシード層を除去することでビア 2 3 及び配線パターン 2 5 を同時に形成する。シード層としては、例えば、スパッタ法、蒸着法、無電解めっき法等の方法により形成された金属層（例えば、Cu 層）を用いることができる。また、めっき膜としては、例えば、Cu めっき膜を用いることができる。配線 3 6 の厚さは、例えば、15 μm とすることができます。

#### 【 0 0 6 3 】

次いで、図 1 7 に示す工程では、図 1 5 に示す工程と同様な処理を行うことにより、図 1 6 に示す構造体の上面にパッド 3 5 を露出する開口部 3 8 を有した絶縁層 2 6 を形成し、その後、図 1 6 に示す工程と同様な処理を行うことにより、絶縁層 2 6 にビア 2 7 及び外部接続用パッド 2 8 を同時に形成する。絶縁層 2 6 としては、例えば、絶縁樹脂層を用いることができる。絶縁層 2 6 となる絶縁樹脂層の材料としては、例えば、エポキシ系樹脂やポリイミド樹脂等を用いることができる。ビア 2 7 及び外部接続用パッド 2 8 は、例えば、Cu 層（シード層）及び Cu めっき膜から構成することができる。

#### 【 0 0 6 4 】

次いで、図 1 8 に示す工程では、周知の手法により、絶縁層 2 6 の面 2 6 A に、外部接続用パッド 2 8 の端子配設面 2 8 A を露出する開口部 3 1 A を有したソルダーレジスト層 3 1 を形成する。これにより、支持体 4 3 の上面 4 3 A に、複数の配線基板本体 1 1（図 1 0 参照）が隣接するように配置され、複数の配線基板本体 1 1 が一体的に構成された基板 5 0 が製造される。次いで、図 1 9 に示す工程では、図 1 8 に示す基板 5 0 から支持体

10

20

30

40

50

43を除去する。支持体43としてCu板又はCu箔を用いた場合、支持体43は、例えば、エッチングにより除去することができる。なお、図12～図19に示す工程が基板形成工程に相当する工程である。

#### 【0065】

次いで、図20に示す工程では、図19に示す基板50を上下反転させ、その後、基板50に設けられた複数の半導体素子搭載用パッド21の搭載面21Aにはんだ17を形成する。

#### 【0066】

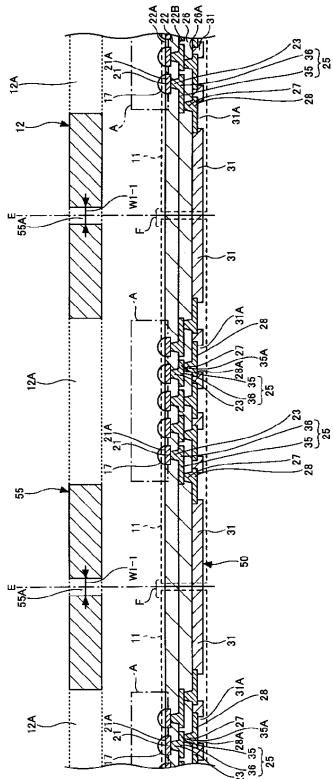

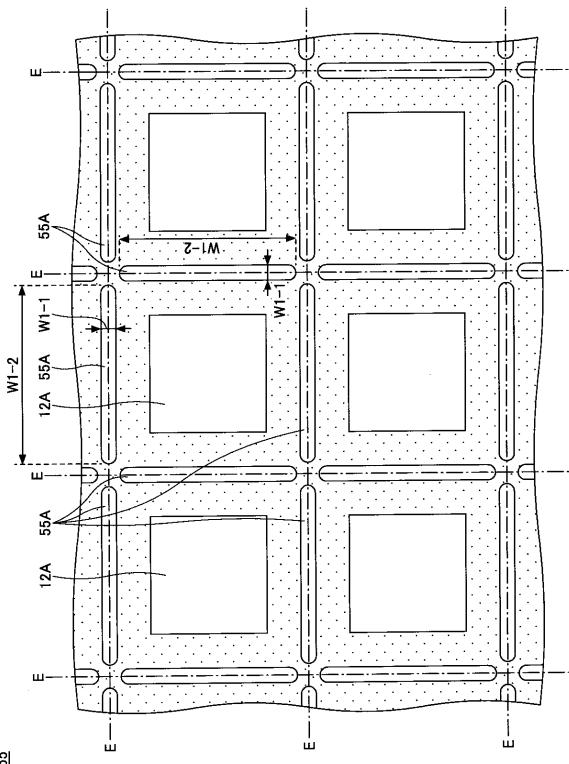

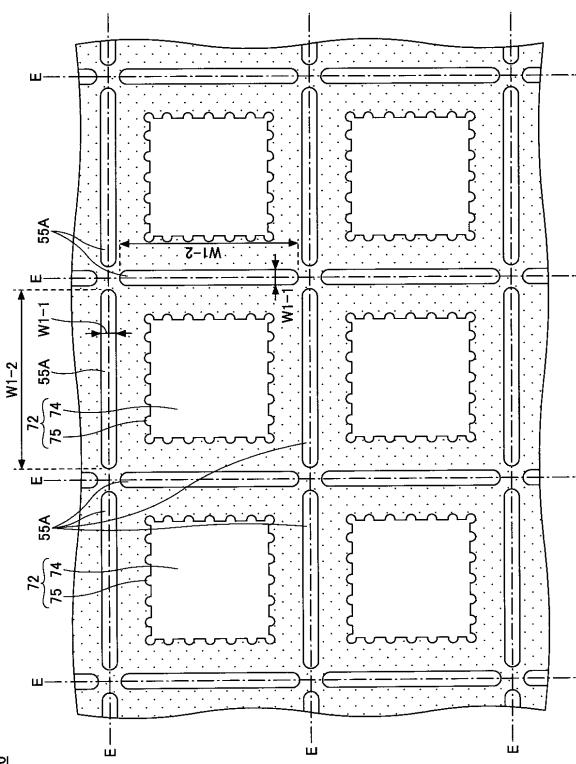

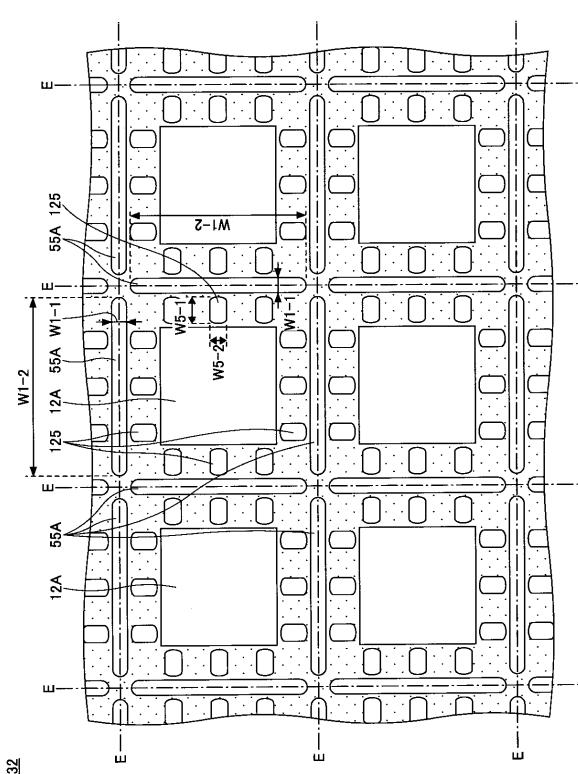

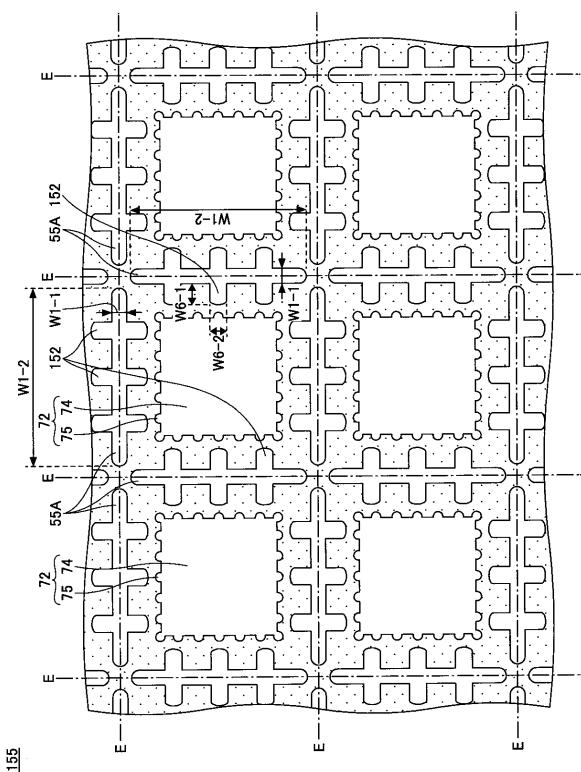

次いで、図21に示す工程では、基板50の半導体素子搭載領域Aを露出する半導体素子搭載用貫通部12Aと、基板50に設けられた配線基板本体11の外周部に対応する部分の絶縁層の面を露出する貫通部55Aとを備え、複数のスティフナー12(図10及び図11参照)の母材となるスティフナー母材55(図24参照)を形成(スティフナー母材形成工程)し、その後、半導体素子搭載用貫通部12Aと半導体素子搭載領域Aとが対向するように、基板50の上方にスティフナー母材55を配置する。貫通部55Aは、切断位置Eに対応する部分のスティフナー母材55を貫通するように形成する。基板50上にスティフナー母材55を載置した際、貫通部55Aは、配線基板本体11の外周部に対応する部分の絶縁層22の面22Aから隣り合う他の配線基板本体11の外周部に対応する部分の絶縁層22の面22Aに亘る領域Fに対応する絶縁層22の面22Aを露出するように形成する。貫通部55Aは、後述する図23に示す工程においてスティフナー母材55が切断されることにより、図10及び図11に示す切り欠き部41となる部分である。

10

#### 【0067】

上記構成とされたスティフナー母材55は、例えば、金属板(例えば、Cu板やCu合金板)やガラスエポキシ基板等の板体に半導体素子搭載用貫通部12A及び貫通部55Aを加工することで形成する。スティフナー12の材料としてCu板を用いた場合、スティフナー12の厚さは、例えば、1mm～2mmとすることができます。また、接着剤13としては、例えば、エポキシ樹脂を用いることができる。半導体素子搭載用貫通部12A及び貫通部55Aは、例えば、エッチング法やプレス加工法等の方法を用いて同時に形成する。

#### 【0068】

20

このように、半導体素子搭載用貫通部12A及び貫通部55Aを同時に形成することで、配線基板10の製造工程を増加させることなく、貫通部55Aを形成することができる。貫通部55Aの一方の幅W1-1は、例えば、100μm～1000μmとすることができます。また、貫通部55Aの他方の幅W1-2は、例えば、10mm～100mmとすることができる。

#### 【0069】

このように、切断位置Eに対応する部分のスティフナー母材55を貫通する貫通部55Aを設けることにより、後述する切断工程(図23参照)においてスティフナー母材55を切断する際、貫通部55Aを通過するようにスティフナー母材55が切断されるため、切断工程に要する時間を従来よりも短縮することができる。また、スティフナー母材55を切断する際に使用する切断用工具(例えば、ダイサーラやスライサー等)の磨耗量を少なくすることが可能となるため、配線基板10の製造コストを低減することができる。

40

#### 【0070】

次いで、図22に示す工程では、接着剤13により、基板50に設けられた絶縁層22の面22Aにスティフナー母材55を接着して、複数の配線基板10に相当する構造体を形成する(接着工程)。

#### 【0071】

このように、接着剤13を用いて、切断位置Eに対応する部分のスティフナー母材55を貫通する貫通部55Aを有したスティフナー母材55を基板50に設けられた絶縁層2

50

2の面22Aに接着することにより、接着剤13のうち、余分な接着剤13を貫通部55Aに露出された部分の絶縁層22の面22Aにはみ出させ、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出る余分な接着剤13(図22に示す領域Bに対応する部分の接着剤13)の量を従来よりも少なくして、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出る余分な接着剤13の高さを低くすることが可能となる。

#### 【0072】

これにより、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出た余分な接着剤13と半導体素子搭載用パッド21に搭載される半導体素子14との接触を防止することが可能となるため、半導体素子搭載用パッド21と半導体素子14とを精度良く電気的に接続することが可能となり、配線基板本体11に設けられた半導体素子搭載用パッド21と半導体素子14との間の電気的な接続信頼性を向上させることができる。10

#### 【0073】

次いで、図23に示す工程では、切断位置Eに対応する部分の基板50及びスティフナー母材55を切断することで、複数の配線基板本体11及び複数のスティフナー12を個片化する(切断工程)。これにより、複数の配線基板10が製造される。基板50及びスティフナー母材55の切断するときに使用する切断用工具としては、例えば、ダイサーやスライサー等を用いることができる。

#### 【0074】

本実施の形態の配線基板の製造方法によれば、接着剤13を用いて、切断位置Eに対応する部分のスティフナー母材55を貫通する貫通部55Aを有したスティフナー母材55を基板50に設けられた絶縁層22の面22Aに接着することにより、接着剤13のうち、余分な接着剤13を貫通部55Aに露出された部分の絶縁層22の面22Aにはみ出させ、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出る余分な接着剤13(図22に示す領域Bに対応する部分の接着剤13)の量を従来よりも少なくして、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出る余分な接着剤13の高さを低くすることが可能となる。これにより、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出た余分な接着剤13と半導体素子搭載用パッド21に搭載される半導体素子14との接触を防止することが可能となるため、半導体素子搭載用パッド21と半導体素子14とを精度良く電気的に接続することが可能となり、配線基板本体11に設けられた半導体素子搭載用パッド21と半導体素子14との間の電気的な接続信頼性を向上させることができる。20

#### 【0075】

また、スティフナー母材55に、切断位置Eに対応する部分のスティフナー母材55を貫通する貫通部55Aを設けることにより、スティフナー母材55を切断する際、貫通部55Aを通過するようにスティフナー母材55が切断されるため、切断工程に要する時間を従来よりも短縮することが可能となり、配線基板10の生産性を向上させることができる。また、スティフナー母材55を切断する際に使用する切断用工具(例えば、ダイサーやスライサー等)の磨耗量を従来よりも少なくすることが可能となるため、配線基板10のコストを低減することができる。30

#### 【0076】

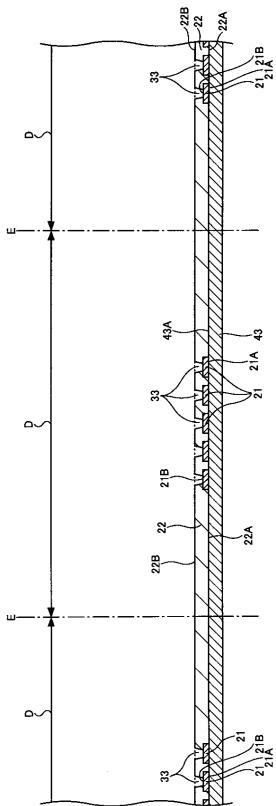

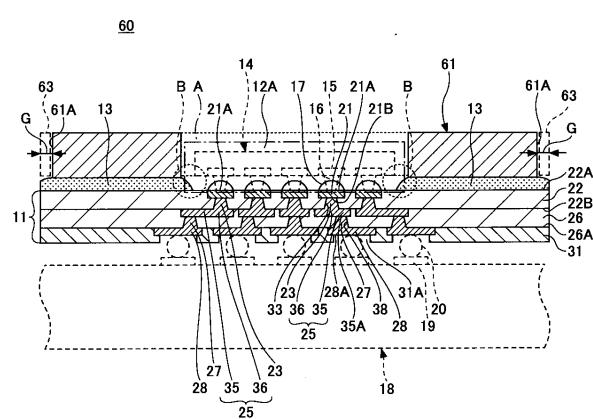

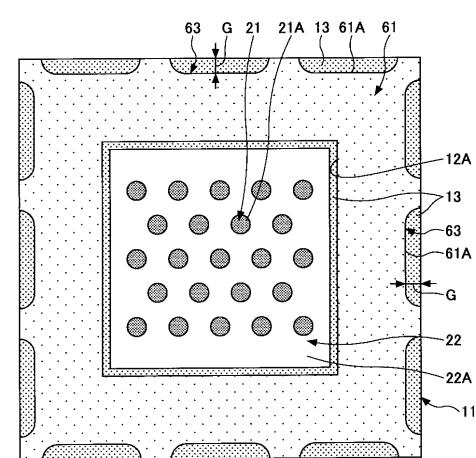

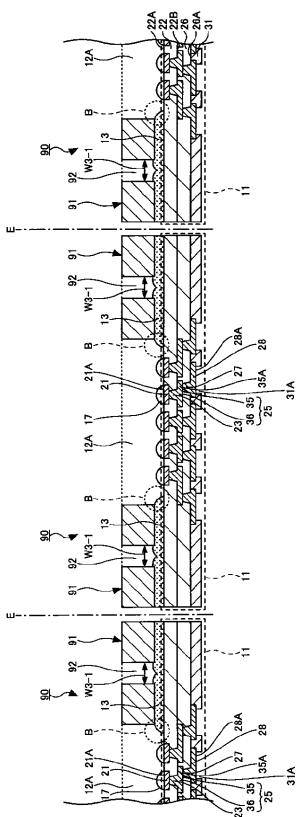

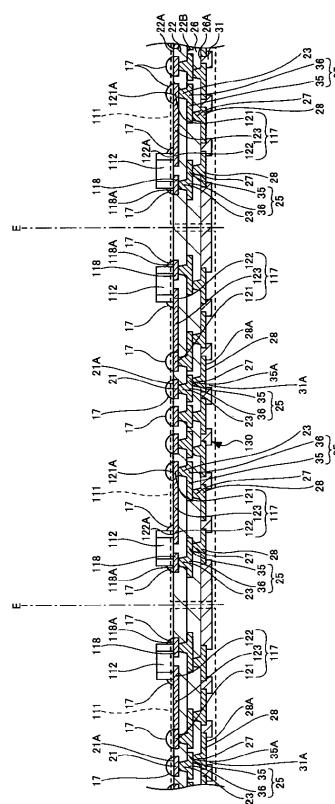

図25は、本発明の第1の実施の形態の第1変形例に係る配線基板の断面図であり、図26は、図25に示す配線基板の平面図である。図25及び図26において、第1の実施の形態の配線基板10と同一構成部分には同一符号を付す。図26では、図25に示すはんだ17の図示を省略する。

#### 【0077】

図25及び図26を参照するに、第1の実施の形態の第1変形例の配線基板60は、第1の実施の形態の配線基板10に設けられたスティフナー12の代わりにスティフナー61を設けた以外は配線基板10と同様に構成される。

#### 【0078】

50

20

30

40

50

スティフナー 6 1 は、第 1 の実施の形態で説明したスティフナー 1 2 (図 1 0 及び図 1 1 参照) に設けられた切り欠き部 4 1 の代わりに、切り欠き部 6 3 を設けた以外はスティフナー 1 2 と同様に構成される。

【 0 0 7 9 】

切り欠き部 6 3 は、スティフナー 6 1 の外周部に設けられている。切り欠き部 6 3 は、平面視四角形とされた配線基板本体 1 1 の各辺に複数 (この場合 3 つ) の切り欠き部 6 3 が対応するように配置されている。切り欠き部 6 3 は、配線基板本体 1 1 上にスティフナー 6 1 を配置した状態において、半導体素子搭載領域 A よりも外側に位置する部分の絶縁層 2 2 の面 2 2 A を露出するように構成されている。

【 0 0 8 0 】

このように、平面視四角形とされた配線基板本体 1 1 の各辺にそれぞれ複数の切り欠き部 6 3 が対応するように、スティフナー 6 1 の外周部に切り欠き部 6 3 を設けてもよい。このような構成とされたスティフナー 6 1 を備えた配線基板 6 0 は、第 1 の実施の形態の配線基板 1 0 と同様な効果を得ることができる。

【 0 0 8 1 】

切り欠き部 6 3 が形成された部分のスティフナー 6 1 の側壁 6 1 A から配線基板本体 1 1 の外周縁までの配線基板 6 0 の面方向の距離 G は、例えば、 $100 \mu m \sim 500 \mu m$  とすることができます。スティフナー 6 1 の材料としては、金属板 (例えば、Cu 板や Cu 合金板) やガラスエポキシ基板等を用いることができる。スティフナー 6 1 の材料として Cu 板を用いた場合、スティフナー 6 1 の厚さは、例えば、 $1 mm \sim 2 mm$  とすることができます。

【 0 0 8 2 】

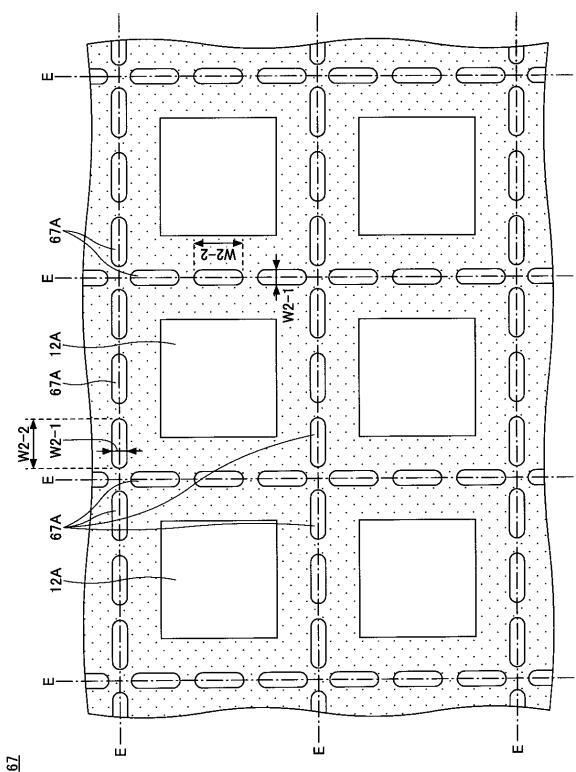

図 2 7 は、本発明の第 1 の実施の形態の第 1 変形例に係る配線基板を製造するときに使用するスティフナー母材の平面図である。

【 0 0 8 3 】

上記構成とされた配線基板 6 0 は、第 1 の実施の形態の配線基板 1 0 を製造する際に使用するスティフナー母材 5 5 の代わりに、図 2 7 に示すスティフナー母材 6 7 を用いて、先に説明した図 1 2 ~ 図 2 3 に示す工程と同様な処理を行うことで製造できる。

【 0 0 8 4 】

ここで、図 2 7 を参照して、第 1 の実施の形態の第 1 変形例の配線基板 6 0 を製造する際に使用するスティフナー母材 6 7 について説明する。

【 0 0 8 5 】

スティフナー母材 6 7 は、第 1 の実施の形態で説明したスティフナー母材 5 5 (図 2 4 参照) に設けられた貫通部 5 5 A の代わりに、貫通部 6 7 A を設けた以外はスティフナー母材 5 5 と同様に構成される。貫通部 6 7 A は、基板 5 0 (図 2 1 参照) に設けられた配線基板本体 1 1 の外周部に対応する部分の絶縁層 2 2 の面 2 2 A を露出するように形成されている。貫通部 6 7 A は、切断位置 E に対応する部分のスティフナー母材 6 7 を貫通している。基板 5 0 上にスティフナー母材 6 7 を載置した際、貫通部 6 7 A は、配線基板本体 1 1 の外周部に対応する部分の絶縁層 2 2 の面 2 2 A から隣り合う他の配線基板本体 1 1 の外周部に対応する部分の絶縁層 2 2 の面 2 2 A に亘る領域 F に対応する絶縁層 2 2 の面 2 2 A を露出するように形成する。貫通部 6 7 A は、スティフナー母材 6 7 が切断位置 E において切断されることにより、図 2 5 に示す切り欠き部 6 3 となる部分である。貫通部 6 7 A の一方の幅 W 2 - 1 は、例えば、 $200 \mu m \sim 1000 \mu m$  とすることができます。また、貫通部 6 7 A の他方の幅 W 2 - 2 は、例えば、 $10 mm \sim 20 mm$  とすることができます。

【 0 0 8 6 】

このように、切断位置 E に対応する部分のスティフナー母材 6 7 を貫通する貫通部 6 7 A を設けることにより、スティフナー母材 6 7 を切断する際、貫通部 6 7 A を通過するようにスティフナー母材 6 7 が切断されるため、スティフナー母材 6 7 の切断に要する時間を従来よりも短縮することが可能となるので、配線基板 6 0 の生産性を向上させることができ

10

20

40

50

できる。また、スティフナー母材 6 7 を切断する際に使用する切断用工具（例えば、ダイサーやスライサー等）の磨耗量を少なくすることが可能となるため、配線基板 6 0 のコストを低減することができる。

【0087】

上記構成とされたスティフナー母材 6 7 の材料としては、例えば、金属板（例えば、Cu 板や Cu 合金板）やガラスエポキシ基板等を用いることができる。スティフナー 6 7 の材料として Cu 板を用いた場合、スティフナー母材 6 7 の厚さは、例えば、1 mm ~ 2 mm とすることができます。

【0088】

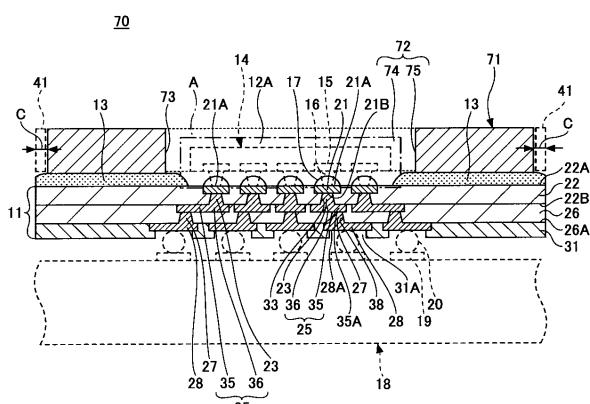

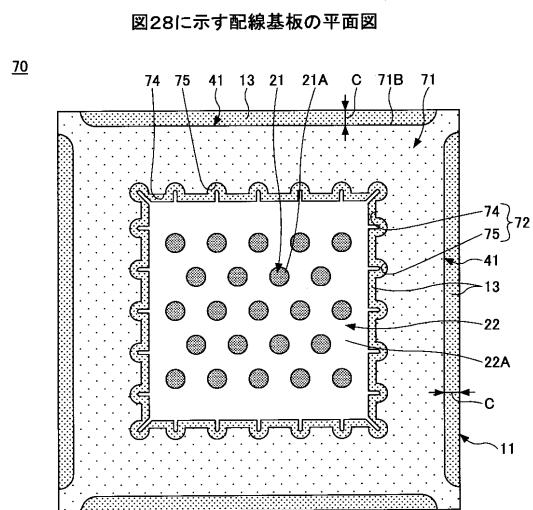

図 28 は、本発明の第 1 の実施の形態の第 2 变形例に係る配線基板の断面図であり、図 29 は、図 28 に示す配線基板の平面図である。図 28 及び図 29 において、第 1 の実施の形態の配線基板 10 と同一構成部分には同一符号を付す。また、図 29 では、図 28 に示すはんだ 17 の図示を省略する。

【0089】

図 28 及び図 29 を参照するに、第 1 の実施の形態の第 2 变形例の配線基板 70 は、第 1 の実施の形態の配線基板 10 に設けられたスティフナー 12（図 10 及び図 11 参照）の代わりにスティフナー 71 を設けた以外は配線基板 10 と同様に構成される。

【0090】

スティフナー 71 は、スティフナー 12 に設けられた半導体素子搭載用貫通部 12A の代わりに、半導体素子搭載用貫通部 72 を設けた以外はスティフナー 12 と同様に構成される。

【0091】

半導体素子搭載用貫通部 72 は、半導体素子 14 を収容するための収容部 74 と、収容部 74 の側壁 73 に対応する部分のスティフナー 71 に形成された複数の切り欠き部 75（他の切り欠き部）とを有した構成とされている。切り欠き部 75 は、スティフナー 71 を貫通するように形成されている。切り欠き部 75 の形状は、例えば、平面視円弧形状とすることができます。

【0092】

このように、半導体素子 14 を収容するための収容部 74 と、収容部 74 の側壁に対応する部分のスティフナー 71 に形成された複数の切り欠き部 75 とをスティフナー 71 に設けることで、接着剤 13 により、スティフナー 71 を配線基板 11 に設けられた絶縁層 22 の面 22A に接着させた際、切り欠き部 75 に露出された部分の絶縁層 22 の面 22A に余分な絶縁剤 13 をはみ出させて、半導体素子搭載領域 A に対応する部分の絶縁層 22 の面 22A にはみ出る余分な接着剤 13 の高さを低くすることが可能となる。

【0093】

これにより、半導体素子搭載領域 A に対応する部分の絶縁層 22 の面 22A にはみ出た余分な接着剤 13 と半導体素子搭載用パッド 21 に搭載される半導体素子 14 との接触を防止することができるため、半導体素子搭載用パッド 21 と半導体素子 14 とを精度良く電気的に接続することができる。配線基板本体 11 に設けられた半導体素子搭載用パッド 21 と半導体素子 14 との間の電気的な接続信頼性を向上させることができる。

【0094】

図 30 は、本発明の第 1 の実施の形態の第 2 变形例に係る配線基板を製造するときに使用するスティフナー母材の平面図である。図 30 において、図 28 及び図 29 に示すスティフナー 71 と同一構成部分には同一符号を付す。

【0095】

ここで、図 30 を参照して、第 1 の実施の形態の第 2 变形例の配線基板 70 を製造する際に使用するスティフナー母材 80 について説明する。

【0096】

スティフナー母材 80 は、第 1 の実施の形態で説明したスティフナー母材 55（図 24 参照）に設けられた半導体素子搭載用貫通部 12A の代わりに、図 28 及び図 29 で説明

10

20

30

40

50

した半導体素子搭載用貫通部 7 2 を設けた以外はスティフナー母材 5 5 と同様に構成される。スティフナー母材 8 0 の材料としては、例えば、金属板（例えば、Cu 板や Cu 合金板）やガラスエポキシ基板等を用いることができる。スティフナー 8 0 の材料として Cu 板を用いた場合、スティフナー母材 8 0 の厚さは、例えば、1 mm ~ 2 mm とすることができる。

【0097】

本実施の形態の配線基板 7 0 は、第 1 の実施の形態の配線基板 1 0 を製造する際に使用するスティフナー母材 5 5 の代わりに、図 3 0 に示すスティフナー母材 8 0 を用いて、第 1 の実施の形態で説明した図 1 2 ~ 図 2 3 に示す工程と同様な処理を行うことで製造できる。

10

【0098】

本実施の形態の配線基板の製造方法によれば、半導体素子 1 4 を収容するための収容部 7 4 と、収容部 7 4 の側壁 7 3 に対応する部分のスティフナー 7 1 に形成された複数の切り欠き部 7 5 とを有した半導体素子搭載用貫通部 7 2 を備えたスティフナー母材 8 0 を用いて、複数の配線基板 7 0 を製造することにより、基板 5 0 とスティフナー母材 8 0 とを接着する接着剤 1 3 のうち、余分な絶縁剤 1 3 を切り欠き部 7 5 に露出された部分の絶縁層 2 2 の面 2 2 A にはみ出させて、半導体素子搭載領域 A に対応する部分の絶縁層 2 2 の面 2 2 A にはみ出る余分な接着剤 1 3 の高さを低くすることが可能となる。

【0099】

これにより、半導体素子搭載領域 A に対応する部分の絶縁層 2 2 の面 2 2 A にはみ出た余分な接着剤 1 3 と半導体素子搭載用パッド 2 1 に搭載される半導体素子 1 4 との接触を防止することが可能となるため、半導体素子搭載用パッド 2 1 と半導体素子 1 4 とを精度良く電気的に接続することが可能となり、配線基板本体 1 1 に設けられた半導体素子搭載用パッド 2 1 と半導体素子 1 4 との間の電気的な接続信頼性を向上させることができる。

20

【0100】

また、スティフナー母材 8 0 を用いて、複数の配線基板 7 0 を製造した場合、第 1 の実施の形態の配線基板 1 0 の製造方法と同様な効果を得ることができる。

【0101】

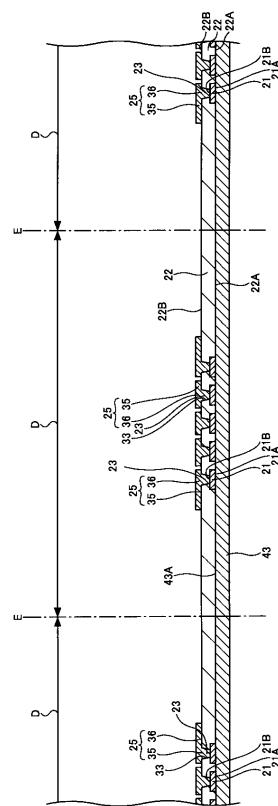

（第 2 の実施の形態）

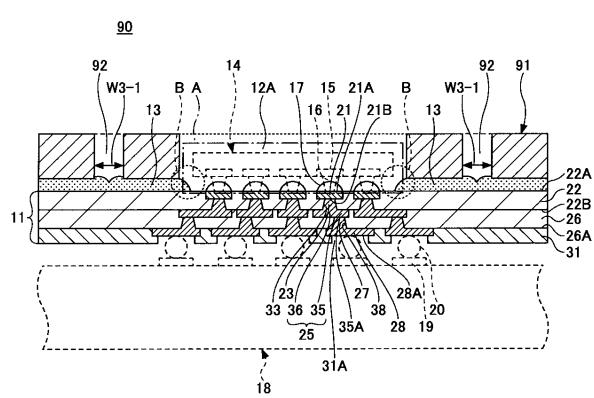

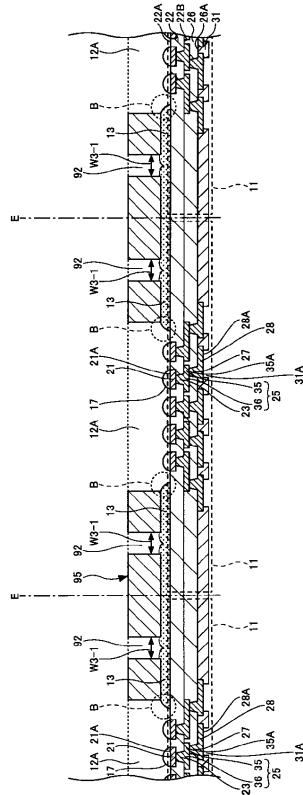

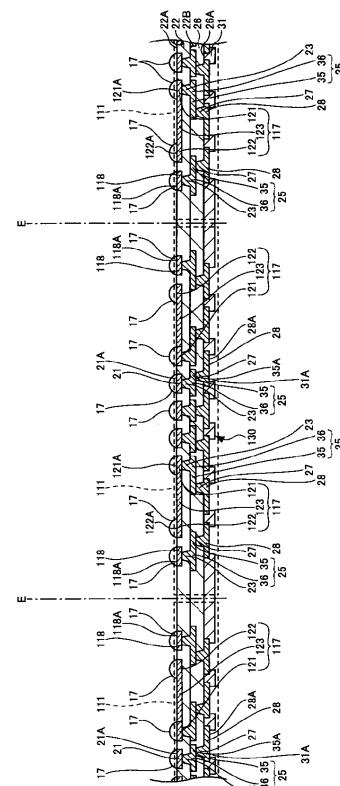

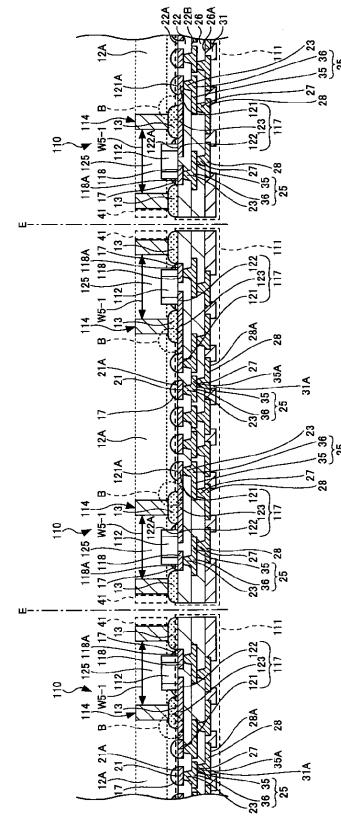

図 3 1 は、本発明の第 2 の実施の形態に係る配線基板の断面図であり、図 3 2 は、図 3 1 に示す配線基板の平面図である。図 3 1 及び図 3 2 において、第 1 の実施の形態の配線基板 1 0 と同一構成部分には同一符号を付す。また、図 3 2 では、図 3 1 に示すはんだ 1 7 の図示を省略する。

30

【0102】

図 3 1 及び図 3 2 を参照するに、第 2 の実施の形態の配線基板 9 0 は、第 1 の実施の形態の配線基板 1 0 に設けられたスティフナー 1 2 （図 1 0 及び図 1 1 参照）の代わりにスティフナー 9 1 を設けた以外は配線基板 1 0 と同様に構成される。

【0103】

スティフナー 9 1 は、スティフナー 1 2 に設けられた切り欠き部 4 1 の代わりに貫通部 9 2 を設けた以外はスティフナー 1 2 と同様に構成される。貫通部 9 2 は、平面視四角形とされた半導体素子搭載領域 A の各辺と対向すると共に、半導体素子搭載用貫通部 1 2 A とスティフナー 9 1 の外周縁との間に位置する部分のスティフナー 9 1 を貫通するように形成されている。配線基板本体 1 1 に設けられた絶縁層 2 2 の面 2 2 A にスティフナー 9 1 を配置した際、貫通部 9 2 は、半導体素子搭載領域 A よりも外側に配置された部分の絶縁層 2 2 の面 2 2 A を露出するように構成されている。貫通部 9 2 の一方の幅 W 3 - 1 は、例えば、2 mm ~ 5 mm とすることができます。また、貫通部 9 2 の他方の幅 W 3 - 2 は、例えば、10 mm ~ 40 mm とすることができます。

40

【0104】

上記構成とされたスティフナー 9 1 は、接着剤 1 3 により、配線基板 1 1 に設けられた絶縁層 2 2 の面 2 2 A に接着されている。スティフナー 9 1 の材料としては、金属板（例

50

えば、Cu板やCu合金板)やガラスエポキシ基板等を用いることができる。スティフナー91の材料としてCu板を用いた場合、スティフナー91の厚さは、例えば、1mm~2mmとすることができます。

#### 【0105】

本実施の形態の配線基板によれば、半導体素子搭載領域Aよりも外側に配置された部分の絶縁層22の面22Aを露出する貫通部92を有したスティフナー91と配線基板11に設けられた絶縁層22の面22Aとを接着剤13を用いて接着することにより、余分な接着剤13を貫通部92に露出された部分の絶縁層22の面22Aにはみ出させ、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出る接着剤13(図31及び図32に示す領域Bに対応する部分の接着剤13)の量を従来よりも少なくして、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出る余分な接着剤13の高さを低くすることが可能となる。10

#### 【0106】

これにより、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出た余分な接着剤13と半導体素子搭載用パッド21に搭載される半導体素子14との接触を防止することが可能となるため、半導体素子搭載用パッド21と半導体素子14とを精度良く電気的に接続することが可能となり、配線基板本体11に設けられた半導体素子搭載用パッド21と半導体素子14との間の電気的な接続信頼性を向上させることができる。

#### 【0107】

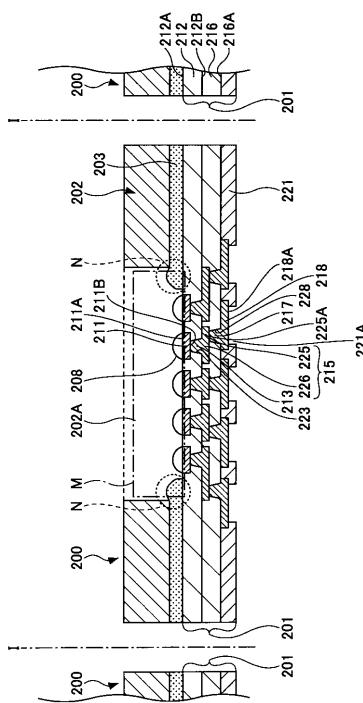

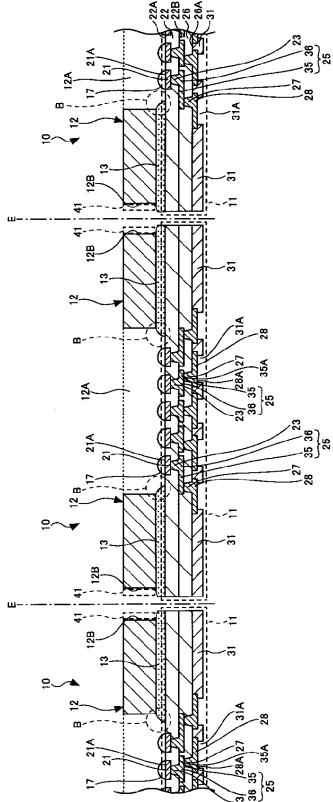

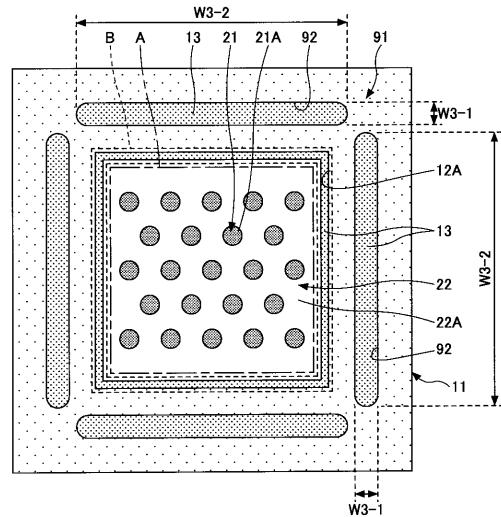

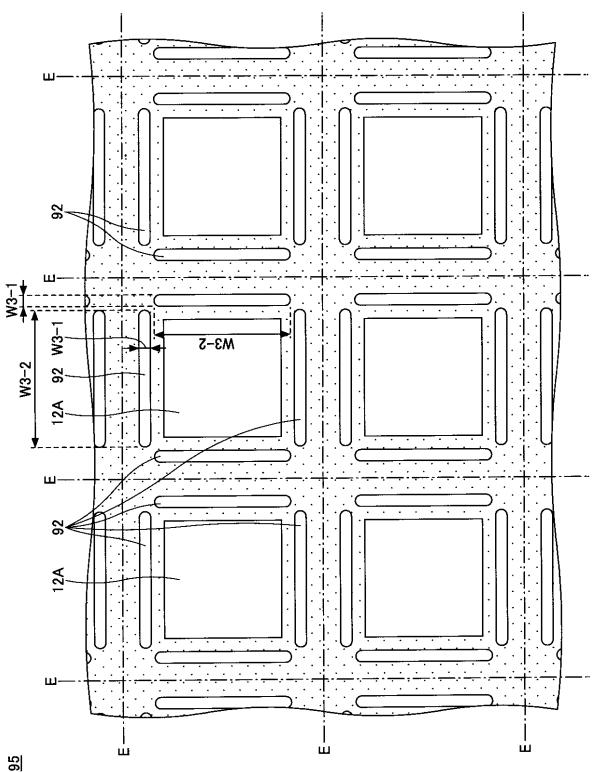

図33~図35は、本発明の第2の実施の形態の配線基板の製造工程を示す図であり、20図36は、図33に示すスティフナーの平面図である。図33~図36において、第2の実施の形態の配線基板90と同一構成部分には同一符号を付す。

#### 【0108】

図33~図36を参照して、第2の実施の形態の配線基板90の製造方法について説明する。始めに、図33に示す工程では、第1の実施の形態で説明した図12~図19に示す工程と同様な処理を行うことで基板50を形成する(基板形成工程)。次いで、基板50の半導体素子搭載領域Aを露出する半導体素子搭載用貫通部12Aと、半導体素子搭載領域Aの外側に位置する部分の絶縁層22の面22Aを露出する貫通部92を有すると共に、複数のスティフナー91(図31及び図32参照)の母材となるスティフナー母材95(図36参照)を形成(スティフナー母材形成工程)する。その後、半導体素子搭載用貫通部12Aと半導体素子搭載領域Aとが対向するように、基板50の上方にスティフナー母材95を配置する。スティフナー母材95は、切断位置Eにおいて切断されにより、複数のスティフナー91(図31及び図32参照)となる部材である。30

#### 【0109】

上記構成とされたスティフナー母材95は、例えば、金属板(例えば、Cu板やCu合金板)やガラスエポキシ基板等の板体に半導体素子搭載用貫通部12A及び貫通部92を加工することで形成する。半導体素子搭載用貫通部12A及び貫通部92は、例えば、エッチング法やプレス加工法等の方法を用いて同時に形成する。

#### 【0110】

このように、半導体素子搭載用貫通部12A及び貫通部92を同時に形成することで、40配線基板90の製造工程を増加させることなく、貫通部92を形成することができる。貫通部92の一方の幅W3-1は、例えば、2mm~5mmとすることができます、貫通部92の他方の幅W3-2は、例えば、20mm~40mmとすることができます。

#### 【0111】

次いで、図34に示す工程では、接着剤13を用いて、基板50に設けられた絶縁層22の面22Aにスティフナー母材95を接着して、複数の配線基板90に相当する構造体を形成する(接着工程)。

#### 【0112】

このように、接着剤13を用いて、半導体素子搭載領域Aの外側に位置する部分の絶縁層22の面22Aを露出する貫通部92を有したスティフナー母材95と基板50に設け50

られた絶縁層 22 の面 22 A とを接着することにより、接着剤 13 のうち、余分な接着剤 13 を貫通部 92 に露出された部分の絶縁層 22 の面 22 A にはみ出させ、半導体素子搭載領域 A に対応する部分の絶縁層 22 の面 22 A にはみ出る余分な接着剤 13 (図 31 に示す領域 B に対応する部分の接着剤 13 ) の量を減らして、半導体素子搭載領域 A に対応する部分の絶縁層 22 の面 22 A にはみ出る余分な接着剤 13 の高さを従来よりも低くすることが可能となる。

【0113】

これにより、半導体素子搭載領域 A に対応する部分の絶縁層 22 の面 22 A にはみ出た余分な接着剤 13 と半導体素子搭載用パッド 21 に搭載される半導体素子 14 との接触を防止することが可能となるため、半導体素子搭載用パッド 21 と半導体素子 14 とを精度良く電気的に接続することが可能となり、配線基板本体 11 に設けられた半導体素子搭載用パッド 21 と半導体素子 14 との間の電気的な接続信頼性を向上させることができる。

10

【0114】

次いで、図 35 に示す工程では、図 34 に示す切断位置 E に対応する部分の基板 50 及びスティフナー母材 95 を切断することで、複数の配線基板本体 11 及び複数のスティフナー 91 を個片化する (切断工程)。これにより、複数の配線基板 90 が製造される。基板 50 及びスティフナー母材 95 の切断する際の切断用工具としては、例えば、ダイサー やスライサー等を用いることができる。

【0115】

本実施の形態の配線基板の製造方法によれば、接着剤 13 を用いて、半導体素子搭載領域 A の外側に位置する部分の絶縁層 22 の面 22 A を露出する貫通部 92 を有したスティフナー母材 95 と基板 50 に設けられた絶縁層 22 の面 22 A とを接着することにより、接着剤 13 のうち、余分な接着剤 13 を貫通部 92 に露出された部分の絶縁層 22 の面 22 A にはみ出させ、半導体素子搭載領域 A に対応する部分の絶縁層 22 の面 22 A にはみ出る余分な接着剤 13 (図 31 に示す領域 B に対応する部分の接着剤 13 ) の量を減らして、半導体素子搭載領域 A に対応する部分の絶縁層 22 の面 22 A にはみ出る余分な接着剤 13 の高さを従来よりも低くすることが可能となる。

20

【0116】

これにより、半導体素子搭載領域 A に対応する部分の絶縁層 22 の面 22 A にはみ出た余分な接着剤 13 と半導体素子搭載用パッド 21 に搭載される半導体素子 14 との接触を防止することが可能となるため、配線基板本体 11 に設けられた半導体素子搭載用パッド 21 と半導体素子 14 との間の電気的な接続信頼性を向上させることができる。

30

【0117】

図 37 は、本発明の第 2 の実施の形態の変形例に係る配線基板の断面図であり、図 38 は、図 37 に示す配線基板の平面図である。図 37 及び図 38 において、第 2 の実施の形態の配線基板 90 と同一構成部分には同一符号を付す。また、図 38 では、図 37 に示すはんだ 17 の図示を省略する。

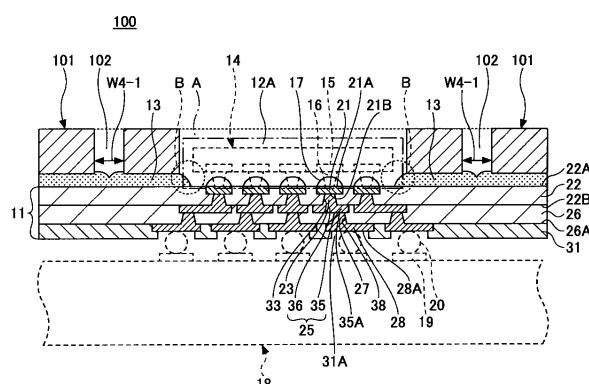

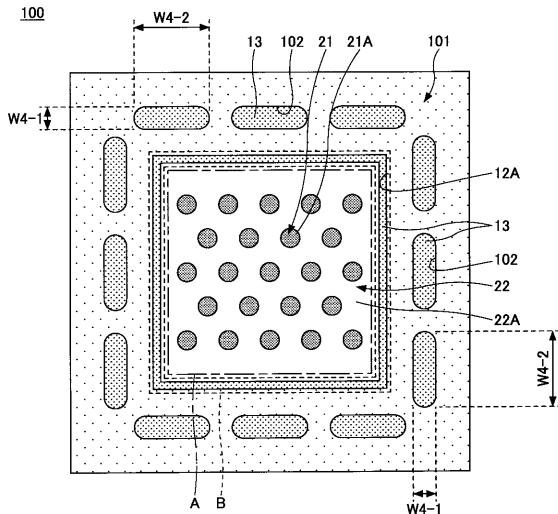

【0118】

図 37 及び図 38 を参照するに、第 2 の実施の形態の変形例の配線基板 100 は、第 2 の実施の形態の配線基板 90 に設けられたスティフナー 91 の代わりにスティフナー 101 を設けた以外は配線基板 90 と同様に構成される。

40

【0119】

スティフナー 101 は、スティフナー 91 (図 31 及び図 32 参照) に設けられた貫通部 92 の代わりに、貫通部 102 を設けた以外はスティフナー 91 と同様に構成される。

【0120】

貫通部 102 は、平面視四角形とされた配線基板本体 11 の各辺に複数 (この場合 3 つ) の貫通部 102 が対応するように配置されている。貫通部 102 の一方の幅 W4-1 は、例えば、2 mm ~ 5 mm とすることができる、貫通部 102 の他方の幅 W4-2 は、例えば、10 mm ~ 40 mm とすることができる。

【0121】

50

このような貫通部 102 を備えた配線基板 100 は、第 2 の実施の形態の配線基板 90 と同様な効果を得ることができる。また、配線基板 100 は、第 2 の実施の形態の配線基板 90 と同様な手法により製造することができ、第 2 の実施の形態の配線基板 90 の製造方法と同様な効果を得ることができる。

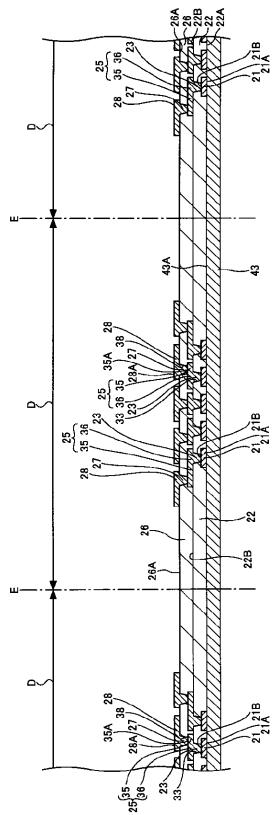

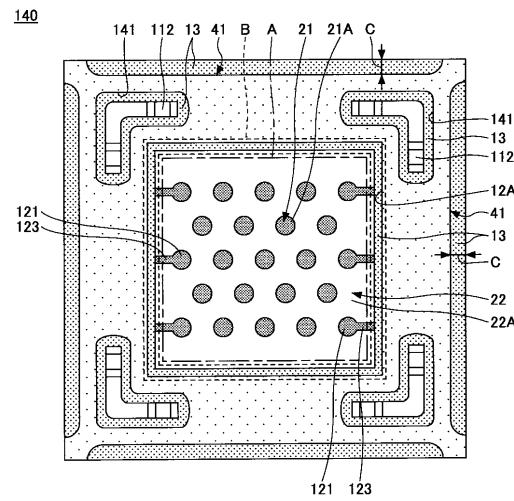

【0122】

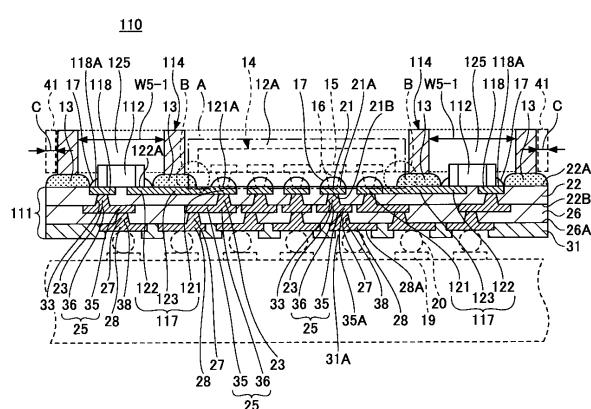

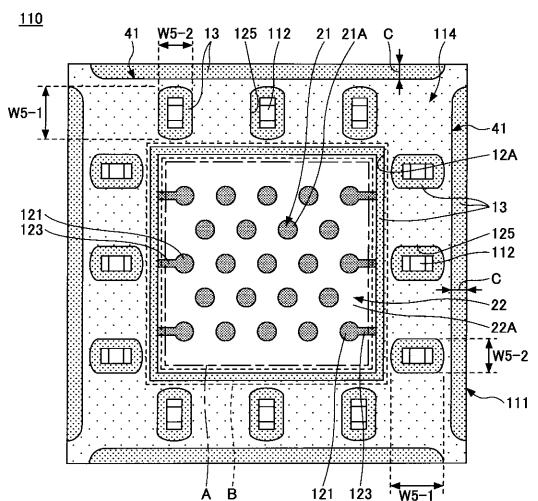

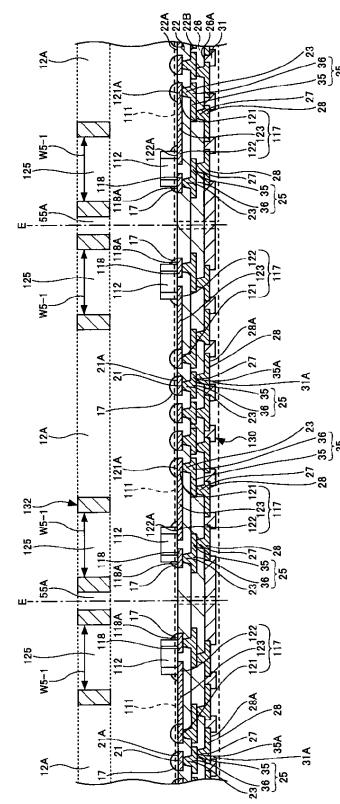

(第 3 の実施の形態)

図 39 は、本発明の第 3 の実施の形態に係る配線基板の断面図であり、図 40 は、図 39 に示す配線基板の平面図である。図 39 及び図 40 において、第 1 の実施の形態の配線基板 10 と同一構成部分には同一符号を付す。また、図 40 では、図 39 に示すはんだ 17 の図示を省略する。

10

【0123】

図 39 及び図 40 を参照するに、第 3 の実施の形態の配線基板 110 は、配線基板本体 111 と、電子部品 112 と、スティフナー 114 とを有する。配線基板本体 111 は、第 1 の実施の形態で説明した配線基板本体 11 の構成に、さらに配線パターン 117 及び電子部品搭載用パッド 118 を設けた以外は配線基板本体 11 と同様に構成される。

【0124】

配線パターン 117 は、その一方の面が絶縁層 22 の面 22A と略面一となるように、絶縁層 22 に内設されている。配線パターン 117 は、半導体素子搭載用パッド 121 と、電子部品搭載用パッド 122 と、配線 123 とを有する。半導体素子搭載用パッド 121 は、半導体素子 14 が搭載される搭載面 121A を有する。搭載面 121A は、絶縁層 22 の面 22A と略面一とされている。搭載面 121A には、半導体素子 14 の電極パッド 15 と電気的に接続された内部接続端子 16 を半導体素子搭載用パッド 121 に固定するためのはんだ 17 が配設されている。半導体素子搭載用パッド 121 は、配線 123 と一体的に構成されている。搭載面 121A の反対側に位置する部分の半導体素子搭載用パッド 121 は、ビア 23 と接続されている。

20

【0125】

電子部品搭載用パッド 122 は、電子部品 112 が搭載される領域に対応する部分の絶縁層 22 に内設されている。電子部品搭載用パッド 122 は、電子部品 112 が搭載される搭載面 122A を有する。搭載面 122A は、絶縁層 22 の面 22A と略面一とされている。搭載面 122A には、電子部品 112 を電子部品搭載用パッド 122 に固定するためのはんだ 17 が設けられている。電子部品搭載用パッド 122 は、はんだ 17 を介して、電子部品 112 と電気的に接続されている。電子部品搭載用パッド 122 は、配線 123 と一体的に構成されており、配線 123 を介して、半導体素子搭載用パッド 121 と電気的に接続されている。

30

【0126】

配線 123 は、その一方の面が絶縁層 22 の面 22A と略面一となるように、絶縁層 22 に内設されている。配線 123 は、その一方の端部が半導体素子搭載用パッド 121 と一体的に構成されており、他方の端部が電子部品搭載用パッド 122 と一体的に構成されている。これにより、配線 123 は、半導体素子搭載用パッド 121 と電子部品搭載用パッド 122 とを電気的に接続している。

40

【0127】

上記構成とされた配線パターン 117 としては、例えば、絶縁層 22 の面 22A 側から Au 層（例えば、厚さ 0.5 μm）と、Ni 層（例えば、厚さ 5.0 μm）とを順次積層させた Au / Ni 積層膜、絶縁層 22 の面 22A 側から Au 層、Pd 層、Ni 層の順に積層した Au / Pd / Ni 積層膜、絶縁層 22 の面 22A 側から Au 層、Pd 層の順に積層した Au / Pd 積層膜等を用いることができる。

【0128】

電子部品搭載用パッド 118 は、電子部品 112 の搭載領域に対応する部分の絶縁層 22 に内設されている。電子部品搭載用パッド 118 は、電子部品 112 が搭載される搭載面 118A を有する。搭載面 118A には、電子部品 112 を電子部品搭載用パッド 11

50

8に固定するためのはんだ17が設けられている。電子部品搭載用パッド118は、はんだ17を介して、電子部品112と電気的に接続されている。はんだ17が設けられた側の反対側に位置する部分の電子部品搭載用パッド118は、ビア23と電気的に接続されている。

【0129】

上記構成とされた電子部品搭載用パッド118としては、例えば、絶縁層22の面22A側からAu層(例えば、厚さ0.5μm)と、Ni層(例えば、厚さ5.0μm)とを順次積層させたAu/Ni積層膜、絶縁層22の面22A側からAu層、Pd層、Ni層の順に積層したAu/Pd/Ni積層膜、絶縁層22の面22A側からAu層、Pd層の順に積層したAu/Pd積層膜等を用いることができる。

10

【0130】

電子部品112は、はんだ17を介して、電子部品搭載用パッド118, 122に搭載されている。電子部品112は、電子部品搭載用パッド118を介して、外部接続用パッド28と電気的に接続されると共に、配線パターン117を介して、半導体素子14と電気的に接続されている。電子部品112は、半導体素子14の特性を調整するための部品である。電子部品112としては、例えば、チップ抵抗、チップインダクタ、チップキャパシタ等を用いることができる。

【0131】

スティフナー114は、第1の実施の形態で説明した図10及び図11に示すスティフナー12に電子部品112を収容するための電子部品搭載用貫通部125を設けた以外はスティフナー12と同様に構成される。電子部品搭載用貫通部125は、配線基板本体111に搭載された電子部品112を収容するための空間である。電子部品搭載用貫通部125は、配線基板本体111の電子部品112が搭載される領域に対応する部分のスティフナー114を貫通するように形成されている。電子部品112が搭載される領域は、半導体素子搭載領域Aよりも外側に位置する部分の配線基板本体111に配置されている。電子部品搭載用貫通部125の一方の幅W5-1は、例えば、2mm~10mmとすることで、電子部品搭載用貫通部125の他方の幅W5-2は、例えば、2mm~5mmとすることができます。

20

【0132】

本実施の形態の配線基板によれば、配線基板本体111に電子部品112が搭載される配線パターン117及び電子部品搭載用パッド118を設け、電子部品112を配線パターン117及び電子部品搭載用パッド118に搭載すると共に、スティフナー114に電子部品112を収容する電子部品搭載用貫通部125を設けることにより、配線基板110のサイズを大型化させることなく、配線基板110の実装密度を向上させることができる。

30

【0133】

また、接着剤13を用いて、切り欠き部41及び電子部品搭載用貫通部125を備えたスティフナー114を配線基板本体111の絶縁層22の面22Aに接着させた際、切り欠き部41及び電子部品搭載用貫通部125に露出された部分の絶縁層22の面22Aに余分な接着剤13をはみ出させ、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出る余分な接着剤13の量を減らして、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出る余分な接着剤13の高さを従来よりも低くすることが可能となる。

40

【0134】

これにより、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出た余分な接着剤13と半導体素子搭載用パッド21に搭載される半導体素子14との接触を防止することが可能となるため、配線基板本体11に設けられた半導体素子搭載用パッド21と半導体素子14との間の電気的な接続信頼性を向上させることができる。

【0135】

図41~図46は、本発明の第3の実施の形態に係る配線基板の製造工程を示す図であ

50

り、図47は、図44に示すスティフナーの平面図である。図41～図46において、第3の実施の形態の配線基板110と同一構成部分には同一符号を付す。

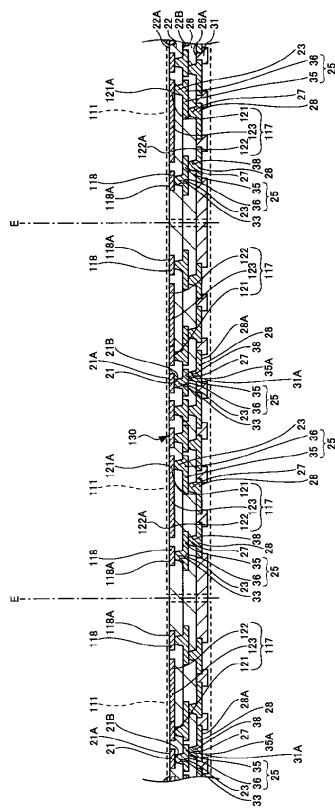

【0136】

図41～図46を参照して、第3の実施の形態の配線基板110の製造方法について説明する。始めに、図41に示す工程では、第1の実施の形態で説明した図12～図19に示す工程と同様な処理を行って、複数の配線基板本体111(図39参照)が隣接するよう配置され、複数の配線基板本体111が一体的に構成された基板130を形成する(基板形成工程)。

【0137】

次いで、図42に示す工程では、半導体素子搭載用パッド21, 121の搭載面21A, 121A及び電子部品搭載用パッド118, 122の搭載面118A, 122Aにはんだ17を形成する。

【0138】

次いで、図43に示す工程では、はんだ17が設けられた電子部品搭載用パッド118, 122に電子部品112を搭載する(電子部品搭載工程)。電子部品112としては、例えば、チップ抵抗、チップインダクタ、チップキャパシタ等を用いることができる。

【0139】

次いで、図44に示す工程では、基板130の半導体素子搭載領域Aを露出する半導体素子搭載用貫通部12Aと、基板130に設けられた配線基板本体111の外周部に対応する部分の絶縁層の面を露出する貫通部55Aと、電子部品搭載用パッド118, 122の形成領域に対応する部分の絶縁層22の面22Aを露出する電子部品搭載用貫通部125とを備え、複数のスティフナー114(図39参照)の母材となるスティフナー母材132(図47参照)を形成(スティフナー母材形成工程)し、その後、半導体素子搭載用貫通部12Aと半導体素子搭載領域Aとが対向するように、基板130の上方にスティフナー母材132を配置する。スティフナー母材132は、図24に示すスティフナー母材55に電子部品搭載用貫通部125が形成された構成とされている。

【0140】

上記構成とされたスティフナー母材132は、例えば、金属板(例えば、Cu板やCu合金板)やガラスエポキシ基板等の板体に半導体素子搭載用貫通部12A、貫通部55A、及び電子部品搭載用貫通部125を加工することで形成する。半導体素子搭載用貫通部12A、貫通部55A、及び電子部品搭載用貫通部125は、例えば、エッチング法やプレス加工法等の方法を用いて同時に形成する。

【0141】

このように、半導体素子搭載用貫通部12A、貫通部55A、及び電子部品搭載用貫通部125を同時に形成することで、配線基板110の製造工程を増加させることなく、貫通部55A及び電子部品搭載用貫通部125を形成することができる。電子部品搭載用貫通部125の一方の幅W5-1は、例えば、2mm～10mmとすることができる。また、電子部品搭載用貫通部125の他方の幅W5-2は、例えば、2mm～5mmとすることができる。

【0142】

貫通部55Aは、切断位置Eに対応する部分のスティフナー母材132を貫通するように形成する。

【0143】

このように、切断位置Eに対応する部分のスティフナー母材132を貫通するように貫通部55Aを形成することにより、貫通部55Aを通過するようにスティフナー母材132が切断されるため、スティフナー母材132の切断に要する時間を従来よりも短縮することができるため、配線基板110の生産性を向上させることができる。また、基板130及びスティフナー母材132を切断する際に使用する切断用工具(例えば、ダイサーやスライサー等)の磨耗量を少なくすることが可能となるため、配線基板110のコストを低減することができる。

10

20

30

40

50

## 【0144】

上記構成とされたスティフナー母材132の材料としては、例えば、金属板（例えば、Cu板やCu合金板）やガラスエポキシ基板等を用いることができる。スティフナー母材132の材料としてCu板を用いた場合、スティフナー母材132の厚さは、例えば、1mm～2mmとすることができます。

## 【0145】

次いで、図45に示す工程では、接着剤13により、基板130に設けられた絶縁層22の面22Aにスティフナー母材132を接着して、複数の配線基板110に相当する構造体を形成する（接着工程）。

## 【0146】

このように、接着剤13を用いて、スティフナー母材132を基板130に設けられた絶縁層22の面22Aに接着することにより、接着剤13のうち、余分な接着剤13を貫通部55A及び電子部品搭載用貫通部125に露出された部分の絶縁層22の面22Aにはみ出させ、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出る余分な接着剤13（図45に示す領域Bに対応する部分の接着剤13）の量を少なくして、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出る余分な接着剤13の高さを低くすることが可能となる。

## 【0147】

これにより、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出た余分な接着剤13と半導体素子搭載用パッド21, 121に搭載される半導体素子14とが接触することがなくなるため、配線基板本体111に設けられた半導体素子搭載用パッド21, 121と半導体素子14との間の電気的な接続信頼性を向上させることができる。

## 【0148】

次いで、図46に示す工程では、切断位置Eに対応する部分の基板130及びスティフナー母材132を切断することで、複数の配線基板本体111及び複数のスティフナー114を個片化する（切断工程）。これにより、複数の配線基板110が製造される。基板130及びスティフナー母材132の切断に用いる切断用工具としては、例えば、ダイサーやスライサー等を用いることができる。

## 【0149】

本実施の形態の配線基板の製造方法によれば、接着剤13を用いて、スティフナー母材132を基板130に設けられた絶縁層22の面22Aに接着することにより、接着剤13のうち、余分な接着剤13を貫通部55A及び電子部品搭載用貫通部125に露出された部分の絶縁層22の面22Aにはみ出させ、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出る余分な接着剤13（図45に示す領域Bに対応する部分の接着剤13）の量を少なくして、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出る余分な接着剤13の高さを低くすることが可能となる。

## 【0150】

これにより、半導体素子搭載領域Aに対応する部分の絶縁層22の面22Aにはみ出た余分な接着剤13と半導体素子搭載用パッド21, 121に搭載される半導体素子14とが接触することがなくなるため、配線基板本体111に設けられた半導体素子搭載用パッド21, 121と半導体素子14との間の電気的な接続信頼性を向上させることができる。

## 【0151】

また、切断位置Eに対応する部分のスティフナー母材132を貫通するように貫通部55Aを形成することにより、貫通部55Aを通過するようにスティフナー母材132が切断されるため、スティフナー母材132の切断に要する時間を従来よりも短縮することができるため、配線基板110の生産性を向上させることができる。

## 【0152】

さらに、基板130及びスティフナー母材132を切断する際に使用する切断用工具（

10

20

30

40

50

例えば、ダイサーやスライサー等)の磨耗量を少なくすることが可能となるため、配線基板110のコストを低減することができる。

【0153】

図48は、本発明の第3の実施の形態の変形例に係る配線基板の平面図である。図48において、第3の実施の形態の配線基板110と同一構成部分には同一符号を付す。

【0154】

なお、配線パターン117及び電子部品搭載用パッド118の形成位置、及び電子部品搭載用貫通部125の形成位置及び形状は、本実施の形態に限定されない。例えば、図48に示す第3の実施の形態の変形例の配線基板140のように、電子部品搭載用貫通部125の代わりに、平面視四角形とされた半導体素子搭載領域Aの角部を囲むように、平面視L字型とされた電子部品搭載用貫通部141を設け、電子部品搭載用貫通部141の形成位置に対応するように、配線パターン117及び電子部品搭載用パッド118を配置してもよい。このような構成とされた配線基板140は、第3の実施の形態の配線基板110と同様な手法により形成することができる。

【0155】

(第4の実施の形態)

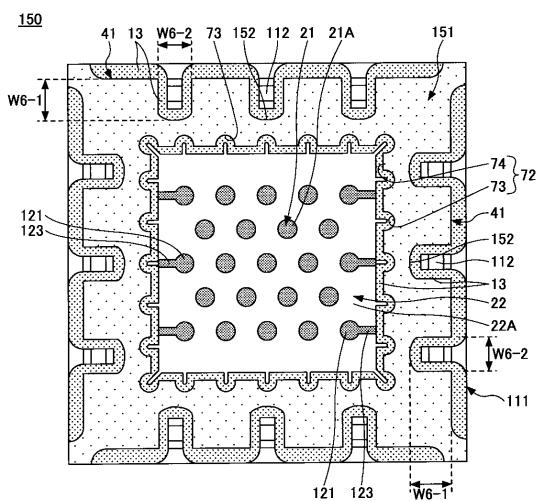

図49は、本発明の第4の実施の形態に係る配線基板の断面図であり、図50は、図49に示す配線基板の平面図である。図49及び図50において、第3の実施の形態の配線基板110と同一構成部分には同一符号を付す。また、図50では、図49に示すはんだ17の図示を省略する。

10

20

【0156】

図49及び図50を参照するに、第4の実施の形態の配線基板150は、第3の実施の形態の配線基板110に設けられたスティフナー114の代わりに、スティフナー151を設けた以外は配線基板110と同様に構成される。

【0157】

スティフナー151は、第2の実施の形態で説明したスティフナー71(図28及び図29参照)に切り欠き部41と一体的に構成された電子部品搭載用貫通部152を設けた以外はスティフナー71と同様に構成される。

【0158】

電子部品搭載用貫通部152は、電子部品112が搭載される領域に対応する部分の配線基板本体111(具体的には、電子部品搭載用パッド118, 122及び電子部品112が搭載される領域に対応する部分の絶縁層22の面22A)を露出するように形成されている。電子部品搭載用貫通部152の一方の幅W6-1は、例えば、2mm~10mmとすることができます。また、電子部品搭載用貫通部152の他方の幅W6-2は、例えば、2mm~5mmとすることができます。

30

【0159】

本実施の形態の配線基板によれば、第1の実施の形態の第2変形例の配線基板70及び第3の実施の形態の配線基板110と同様な効果を得ることができる。

【0160】

図51は、本発明の第4の実施の形態に係る配線基板を製造するときに使用するスティフナー母材の平面図である。図51において、先に説明した図30に示すスティフナー母材80と同一構成部分には同一符号を付す。

40

【0161】

ここで、図51を参照して、第4の実施の形態の配線基板150を製造する際に使用するスティフナー母材155について説明する。

【0162】

スティフナー母材155は、先に説明した図30に示すスティフナー母材80に、貫通部55Aと一体的に構成された電子部品搭載用貫通部152を設けた以外はスティフナー母材80と同様に構成される。電子部品搭載用貫通部152は、貫通部55A及び半導体素子搭載用貫通部72と同時に形成される。

50

**【0163】**

このように、貫通部 55A、半導体素子搭載用貫通部 72、及び電子部品搭載用貫通部 152 を同時に形成することで、配線基板 150 の製造工程を増加させることなく、電子部品搭載用貫通部 152 を形成することができる。

**【0164】**

上記構成とされた第4の実施の形態の配線基板 150 は、図51に示すスティフナー母材 155 を用いて、第3の実施の形態で説明した図41～図46に示す工程と同様な処理を行うことで製造できる。

**【0165】**

以上、本発明の好ましい実施の形態について詳述したが、本発明はかかる特定の実施の形態に限定されるものではなく、特許請求の範囲内に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

10

**【0166】**

例えば、第4の実施の形態の配線基板 150 に設けられた切り欠き部 41 の代わりに、図31及び図32に示す貫通部 92 をスティフナー 151 に設けて、貫通部 92 と電子部品搭載用貫通部 152 と一体的に構成してもよい。

**【0167】**

また、第1～第4の実施の形態で説明したスティフナー 12, 61, 71, 91, 101, 114, 151 を、コア基板を備えたコア付きビルドアップ基板に設けてもよい。

**【産業上の利用可能性】**

20

**【0168】**

本発明は、スティフナーを備えた配線基板及びその製造方法に適用できる。

**【図面の簡単な説明】****【0169】**

【図1】従来の配線基板の断面図である。

【図2】図1に示すスティフナーの平面図である。

【図3】従来の配線基板の製造工程を示す図(その1)である。

【図4】従来の配線基板の製造工程を示す図(その2)である。

【図5】従来の配線基板の製造工程を示す図(その3)である。

30

【図6】従来の配線基板の製造工程を示す図(その4)である。

【図7】従来の配線基板の製造工程を示す図(その5)である。

【図8】従来の配線基板の製造工程を示す図(その6)である。

【図9】従来のスティフナー母材の平面図である。

【図10】本発明の第1の実施の形態に係る配線基板の断面図である。

【図11】図10に示す配線基板の平面図である。

【図12】本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その1)である。

【図13】本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その2)である。

【図14】本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その3)である。

40

【図15】本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その4)である。

【図16】本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その5)である。

【図17】本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その6)である。

【図18】本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その7)である。

【図19】本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その8)である。

50

る。

【図20】本発明の第1の実施の形態に係る配線基板の製造工程を示す図（その9）である。

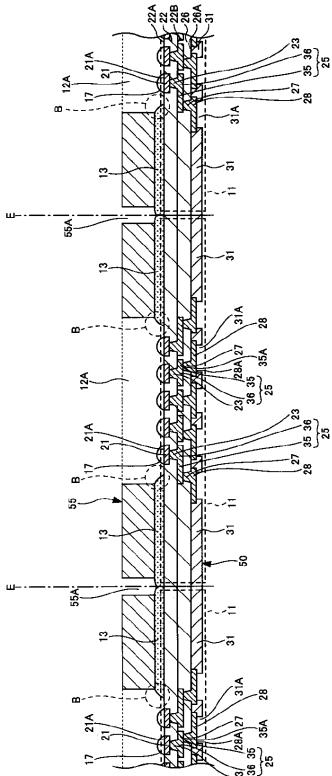

【図21】本発明の第1の実施の形態に係る配線基板の製造工程を示す図（その10）である。

【図22】本発明の第1の実施の形態に係る配線基板の製造工程を示す図（その11）である。

【図23】本発明の第1の実施の形態に係る配線基板の製造工程を示す図（その12）である。

【図24】図21に示すスティフナー母材の平面図である。

10

【図25】本発明の第1の実施の形態の第1変形例に係る配線基板の断面図である。

【図26】図25に示す配線基板の平面図である。

【図27】本発明の第1の実施の形態の第1変形例に係る配線基板を製造するときに使用するスティフナー母材の平面図である。

【図28】本発明の第1の実施の形態の第2変形例に係る配線基板の断面図である。

【図29】図28に示す配線基板の平面図である。

【図30】本発明の第1の実施の形態の第2変形例に係る配線基板を製造するときに使用するスティフナー母材の平面図である。

【図31】本発明の第2の実施の形態に係る配線基板の断面図である。

【図32】図31に示す配線基板の平面図である。

20

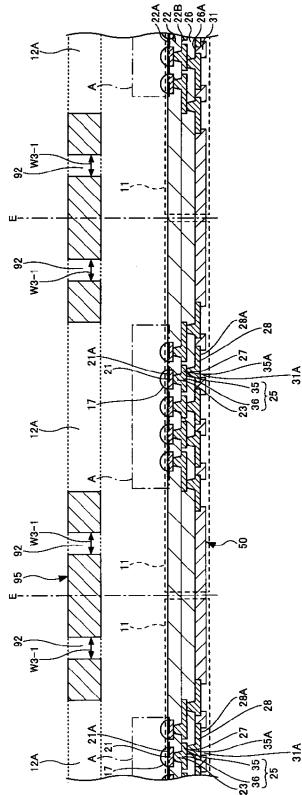

【図33】本発明の第2の実施の形態の配線基板の製造工程を示す図（その1）である。

【図34】本発明の第2の実施の形態の配線基板の製造工程を示す図（その2）である。

【図35】本発明の第2の実施の形態の配線基板の製造工程を示す図（その3）である。

【図36】図33に示すスティフナーの平面図である。

【図37】本発明の第2の実施の形態の変形例に係る配線基板の断面図である。

【図38】図37に示す配線基板の平面図である。

【図39】本発明の第3の実施の形態に係る配線基板の断面図である。

【図40】図39に示す配線基板の平面図である。

【図41】本発明の第3の実施の形態に係る配線基板の製造工程を示す図（その1）である。

30

【図42】本発明の第3の実施の形態に係る配線基板の製造工程を示す図（その2）である。

【図43】本発明の第3の実施の形態に係る配線基板の製造工程を示す図（その3）である。

【図44】本発明の第3の実施の形態に係る配線基板の製造工程を示す図（その4）である。

【図45】本発明の第3の実施の形態に係る配線基板の製造工程を示す図（その5）である。

【図46】本発明の第3の実施の形態に係る配線基板の製造工程を示す図（その6）である。

40

【図47】図44に示すスティフナーの平面図である。

【図48】本発明の第3の実施の形態の変形例に係る配線基板の平面図である。

【図49】本発明の第4の実施の形態に係る配線基板の断面図である。

【図50】図49に示す配線基板の平面図である。

【図51】本発明の第4の実施の形態に係る配線基板を製造するときに使用するスティフナー本体の平面図である。

【符号の説明】

【0170】

10, 60, 70, 90, 100, 110, 140, 150 配線基板

11, 111 配線基板本体

50

|                                                                                                                          |              |    |

|--------------------------------------------------------------------------------------------------------------------------|--------------|----|

| 1 2 , 6 1 , 7 1 , 9 1 , 1 0 1 , 1 1 4 , 1 5 1                                                                            | スティフナー       |    |

| 1 2 A , 7 2                                                                                                              | 半導体素子搭載用貫通部  |    |

| 1 2 B , 6 1 A                                                                                                            | 側壁           |    |

| 1 3                                                                                                                      | 接着剤          |    |

| 1 4                                                                                                                      | 半導体素子        |    |

| 1 5                                                                                                                      | 電極パッド        |    |

| 1 6                                                                                                                      | 内部接続端子       |    |

| 1 7                                                                                                                      | はんだ          |    |

| 1 8                                                                                                                      | 実装基板         |    |

| 1 9 , 3 5                                                                                                                | パッド          | 10 |

| 2 0                                                                                                                      | 外部接続端子       |    |

| 2 1 , 1 2 1                                                                                                              | 半導体素子搭載用パッド  |    |

| 2 1 A , 1 1 8 A , 1 2 1 A , 1 2 2 A                                                                                      | 搭載面          |    |

| 2 1 B , 2 2 A , 2 2 B , 2 6 A , 3 5 A                                                                                    | 面            |    |

| 2 2 , 2 6                                                                                                                | 絶縁層          |    |

| 2 3 , 2 7                                                                                                                | ビア           |    |

| 2 5 , 1 1 7                                                                                                              | 配線パターン       |    |

| 2 8                                                                                                                      | 外部接続用パッド     |    |

| 2 8 A                                                                                                                    | 端子配設面        |    |

| 3 1                                                                                                                      | ソルダーレジスト層    | 20 |

| 3 1 A , 3 3 , 3 8 , 4 5 A                                                                                                | 開口部          |    |

| 3 6 , 1 2 3                                                                                                              | 配線           |    |

| 4 1 , 6 3 , 7 5                                                                                                          | 切り欠き部        |    |

| 4 3                                                                                                                      | 支持体          |    |

| 4 3 A                                                                                                                    | 上面           |    |

| 4 5                                                                                                                      | めっき用レジストパターン |    |

| 5 0 , 1 3 0                                                                                                              | 基板           |    |

| 5 5 , 6 7 , 8 0 , 9 5 , 1 3 2 , 1 5 5                                                                                    | スティフナー母材     |    |

| 5 5 A , 6 7 A , 9 2 , 1 0 2                                                                                              | 貫通部          |    |

| 7 4                                                                                                                      | 収容部          | 30 |

| 1 1 2                                                                                                                    | 電子部品         |    |

| 1 1 8 , 1 2 2                                                                                                            | 電子部品搭載用パッド   |    |

| 1 2 5 , 1 4 1 , 1 5 2                                                                                                    | 電子部品搭載用貫通部   |    |

| A                                                                                                                        | 半導体素子搭載領域    |    |

| B , F                                                                                                                    | 領域           |    |

| C , G                                                                                                                    | 距離           |    |

| D                                                                                                                        | 配線基板本体形成領域   |    |

| E                                                                                                                        | 切断位置         |    |

| W 1 - 1 , W 1 - 2 , W 2 - 1 , W 2 - 2 , W 3 - 1 , W 3 - 2 , W 4 - 1 , W 4 - 2<br>, W 5 - 1 , W 5 - 2 , W 6 - 1 , W 6 - 2 | 幅            | 40 |

【図1】

【図2】

図1に示すスティフナーの平面図

【図3】

従来の配線基板の製造工程を示す図(その1)

【図4】

従来の配線基板の製造工程を示す図(その2)

【図5】

### 従来の配線基板の製造工程を示す図(その3)

【 四 6 】

#### 従来の配線基板の製造工程を示す図(その4)

【図7】

### 従来の配線基板の製造工程を示す図(その5)

【 四 8 】

### 従来の配線基板の製造工程を示す図(その6)

【図9】

【 図 1 0 】

### 従来のスティフナー母材の平面図

【図 1 1 】

【 図 1 2 】

図10に示す配線基板の平面図

## 本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その1)

【図13】

本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その2)

【図14】

本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その3)

【図15】

本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その4)

【図16】

本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その5)

【図17】

本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その6)

### 【図21】

【図22】

#### 本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その10)

### 本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その11)

### 【図23】

### 【図24】

### 本発明の第1の実施の形態に係る配線基板の製造工程を示す図(その12)

図21に示すスティフナー母材の平面図

【図25】

本発明の第1の実施の形態の第1変形例に係る配線基板の断面図

【図26】

図25に示す配線基板の平面図

【図27】

本発明の第1の実施の形態の第1変形例に係る

配線基板を製造するときに使用するスティフナー母材の平面図

【図28】

本発明の第1の実施の形態の第2変形例に係る配線基板の断面図

【図29】

【図30】

本発明の第1の実施の形態の第2変形例に係る

配線基板を製造するときに使用するスティーナー母材の平面図

【図31】

本発明の第2の実施の形態に係る配線基板の断面図

【図32】

図31に示す配線基板の平面図

### 【図33】

## 本発明の第2の実施の形態の配線基板の製造工程を示す図(その1)

### 【図34】

## 本発明の第2の実施の形態の配線基板の製造工程を示す図(その2)

### 【図35】

### 本発明の第2の実施の形態の配線基板の製造工程を示す図(その3)

【図36】

図33に示すスティフナーの平面図

【図37】

## 本発明の第2の実施の形態の変形例に係る配線基板の断面図

【 図 3 8 】

図37に示す配線基板の平面図

〔 四 3 9 〕

### 本発明の第3の実施の形態に係る配線基板の断面図

〔 四〇 〕

図39に示す配線基板の平面図

【図41】

### 本発明の第3の実施の形態に係る配線基板の製造工程を示す図(その1)

【図42】

### 本発明の第3の実施の形態に係る配線基板の製造工程を示す図(その2)

【図4-3】

本発明の第3の実施の形態に係る配線基板の製造工程を示す図(その3)

### 【図4-4】

本発明の第3の実施の形態に係る配線基板の製造工程を示す図(その4)

### 【図45】

### 本発明の第3の実施の形態に係る配線基板の製造工程を示す図(その5)

【図47】

図44に示すスティフナーの平面図

【図46】

### 本発明の第3の実施の形態に係る配線基板の製造工程を示す図(その6)

【図48】

### 本発明の第3の実施の形態の変形例に係る配線基板の平面図

【図49】

本発明の第4の実施の形態に係る配線基板の断面図

【図50】

図39に示す配線基板の平面図

【図51】

本発明の第4の実施の形態に係る

配線基板を製造するときに使用する

スティフナー本体の平面図

---

フロントページの続き

(56)参考文献 特開平10-50877(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12