(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-256867

(P2012-256867A)

(43) 公開日 平成24年12月27日(2012.12.27)

(51) Int.Cl.

H01S 5/343 (2006.01)

F 1

H01S 5/343

テーマコード(参考)

5 F 173

審査請求 未請求 請求項の数 14 O L (全 14 頁)

(21) 出願番号 特願2012-106528 (P2012-106528)

(22) 出願日 平成24年5月8日 (2012.5.8)

(31) 優先権主張番号 特願2011-110887 (P2011-110887)

(32) 優先日 平成23年5月17日 (2011.5.17)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100086483

弁理士 加藤 一男

(72) 発明者 小山 泰史

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

F ターム(参考) 5F173 AA21 AB13 AF04 AF07 AF12

AG03 AH02 AR13 AR81 AR96

(54) 【発明の名称】導波路、該導波路を用いた装置及び導波路の製造方法

## (57) 【要約】

【課題】製造プロセスなどに起因する歪や欠陥や、初期又は動作中に半導体に生じる歪や欠陥を抑制して、特性の向上や安定化が期待される導波路及びその製造方法を提供する。

【解決手段】導波路107は、導波モードの電磁波に対する誘電率実部が負の負誘電率媒質の第一の導体層103と第二の導体層104と、2つの導体層103、104に接し且つ2つの導体層103、104の間に配置された半導体部101を含むコア層108と、を有する。半導体部101を含むコア層108は、面内方向に広がった特定の凹凸構造を有する。

【選択図】図1

図1、本発明の発振素子の実施形態を説明する図

## 【特許請求の範囲】

## 【請求項 1】

導波モードの電磁波に対する誘電率実部が負の負誘電率媒質の第一の導体層と第二の導体層と、前記 2 つの導体層に接し且つ前記 2 つの導体層の間に配置された半導体部を含むコア層と、を有する導波路であって、

前記半導体部を含むコア層は、面内方向に広がった凹凸構造を有し、

前記導波モードの電磁波の伝播方向に対して垂直方向に前記凹凸構造を有し、凸部を複数有することを特徴とする導波路。

## 【請求項 2】

導波モードの電磁波に対する誘電率実部が負の負誘電率媒質の第一の導体層と第二の導体層と、前記 2 つの導体層に接し且つ前記 2 つの導体層の間に配置された半導体部を含むコア層と、を有する導波路であって、

前記半導体部を含むコア層は、面内方向に広がった凹凸構造を有し、

前記電磁波の波長を  $\lambda$  、前記導波路の等価屈折率を  $n_e$  として、 $g = \lambda / n_e$  と表すとき、前記凹凸構造のピッチ長が  $g / 2$  未満であることを特徴とする導波路。

## 【請求項 3】

導波モードの電磁波に対する誘電率実部が負の負誘電率媒質の第一の導体層と第二の導体層と、前記 2 つの導体層に接し且つ前記 2 つの導体層の間に配置された半導体部を含むコア層と、を有する導波路であって、

前記半導体部を含むコア層は、面内方向に広がった凹凸構造を有し、

前記凹凸構造のピッチ長が  $100 \mu m$  未満であることを特徴とする導波路。

## 【請求項 4】

前記凹凸構造の凹部は、前記コア層を厚さ方向に貫通して前記半導体部を島状に分離する溝で構成されていることを特徴とする請求項 1 から 3 の何れか 1 項に記載の導波路。

導波路。

## 【請求項 5】

前記凹部は、誘電体又は絶縁体のスペーサとして構成されていることを特徴とする請求項 1 から 4 の何れか 1 項に記載の導波路。

## 【請求項 6】

前記電磁波の波長を  $\lambda$  、当該導波路の等価屈折率を  $n_e$  として、 $g = \lambda / n_e$  と表すとき、前記スペーサは、当該導波路の長手方向および短手方向の幅が  $g / 2$  以下であることを特徴とする請求項 1 から 5 の何れか 1 項に記載の導波路。

## 【請求項 7】

前記電磁波の波長を  $\lambda$  、当該導波路の等価屈折率を  $n_e$  として、 $g = \lambda / n_e$  と表すとき、前記半導体部は、当該導波路の長手方向および短手方向の幅が  $g / 2$  以下、或いは  $g / 10$  以下であることを特徴とする請求項 1 から 6 の何れか 1 項に記載の導波路。

## 【請求項 8】

前記半導体部は、少なくとも、前記発振モードにおける共振電界の腹となる位置に配置されることを特徴とする請求項 1 から 7 の何れか 1 項に記載の導波路。

## 【請求項 9】

前記スペーサは、少なくとも、前記発振モードにおける共振電界の節となる位置に配置されることを特徴とする請求項 1 から 8 の何れか 1 項に記載の導波路。

## 【請求項 10】

前記半導体部は、キャリアのサブバンド間遷移によりテラヘルツ波を発生する多重量子井戸構造を含み構成されることを特徴とする請求項 1 から 9 の何れか 1 項に記載の導波路。

## 【請求項 11】

前記凹凸構造の粗密が前記導波路の端面近傍で段階的に変化することを特徴とする請求項 1 から 10 の何れか 1 項に記載の導波路。

## 【請求項 12】

電磁波を用いる装置であって、

10

20

30

40

50

請求項 1 から 11 の何れか 1 項に記載の導波路と、

検体と相互作用した前記電磁波を検出し、検出した信号から検体の状態を算出する演算部

と、を有することを特徴とする装置。

【請求項 13】

請求項 1 から 11 の何れか 1 項に記載の導波路の製造方法であって、

半導体層に凹部を形成するステップと、

前記凹部に物質を充填してスペーサを配置するステップと、を含むことを特徴とする導波

路の製造方法。

【請求項 14】

上面に前記半導体層を備えた第一の基板を準備するステップと、

第二の基板を準備するステップと、

前記第一の基板の前記半導体層を前記第二の基板の上面に第一の導体層を介して転写する

ステップと、

前記スペーサが配置された前記半導体層の上面に第二の導体層を形成するステップと、を

含むことを特徴とする請求項 13 に記載の導波路の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、導波路、該導波路を用いた装置及び導波路の製造方法に関する。特に、ミリ波

帯からテラヘルツ波帯 (30 GHz ~ 30 THz) までの周波数領域の電磁波（以下、テ

ラヘルツ波とも記す）に係る導波路に関する。

【背景技術】

【0002】

テラヘルツ波の周波数領域には、生体材料・医薬品・電子材料などの多くの有機分子につ

いて、構造や状態に由來した吸収ピークが存在する。また、テラヘルツ波は、紙・セラミ

ック・樹脂・布といった材料に対して高い透過性を有する。近年、この様なテラヘルツ波

の特徴を活かしたイメージング技術やセンシング技術の研究開発が行われている。例え

ば、X線装置に代わる安全な透視検査装置や、製造工程におけるインラインの非破壊検査

装置などへの応用が期待されている。

【0003】

電流注入型のテラヘルツ波光源として、半導体量子井戸構造における電子のサブバンド間

遷移に基づいた電磁波利得を利用する構造が検討されている。非特許文献 1 には、低損失

の導波路として知られる Double-side Metal Waveguide (以下、DMW とも記す) を共振器として集積したテラヘルツ波帯の量子カスケードレーザ (Quantum Cascade Laser : QCL、以下、QCL とも記す) が提案

されている。本素子は、10 μm 程度の薄さの半導体薄膜からなる利得媒質の上下に金属

を配置した共振器構造に、誘導放出されたテラヘルツ波を表面プラズモンモードで導波さ

ることで、高い光閉じ込めと低損失伝搬により 3 THz 近傍のレーザ発振を達成してい

る。

【0004】

一方、多重量子井戸構造は、歪による特性変化が知られており、非特許文献 2 には、歪に

による共鳴トンネルダイオード (Resonant Tunnel Diode : RTD、

以下、RTD とも記す) の特性変化が報告されている。この非特許文献 2 では、100 M

Pa 弱の応力で、約 2 倍の微分負性抵抗変化が観測されている。また、特許文献 1 に示す

ような導波路を伴ったレーザ素子について開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献 1】米国特許 7 693 198 号

【非特許文献】

10

20

30

40

50

## 【0006】

【非特許文献1】Appl. Phys. Lett. 83, 2124 (2003)

【非特許文献2】Sensors and Actuators, A, 143, (2008), 230-236

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0007】

非特許文献1に開示されたDMWは、 $10\text{ }\mu\text{m}$ 程度の半導体層を2枚の金属層で挟んだ構造であり、金属接合技術などを用いて半導体薄膜を異なる基板に転写することで作製される。一方、格子定数や熱膨張係数の異なる薄膜材料を積層した構造は、製造プロセスに起因した残留応力が生じ易いことが一般的に知られている。従って、従来の構造は、製造プロセスなどに起因した歪や欠陥で利得媒質である半導体薄膜の特性が変化し、発振特性の劣化や不安定化が生じる可能性があった。

10

## 【課題を解決するための手段】

## 【0008】

上記課題に鑑み、本発明の導波路は、導波モードの電磁波に対する誘電率実部が負の負誘電率媒質の第一の導体層と第二の導体層と、前記2つの導体層に接し且つ前記2つの導体層の間に配置された半導体部を含むコア層と、を有する。そして、前記半導体部を含むコア層は、面内方向に広がった凹凸構造を有し、さらに次の構成要件のいずれか一つを少なくとも有する。

20

(1) 前記導波モードの電磁波の伝播方向に対して垂直方向に前記凹凸構造を有し、凸部を複数有する。

(2) 前記電磁波の波長を $\lambda$ 、前記導波路の等価屈折率を $n_e$ として、 $g = \lambda / n_e$ と表すときに、前記凹凸構造のピッチ長が $g/2$ 未満である。

(3) 前記凹凸構造のピッチ長が $100\text{ }\mu\text{m}$ 未満である。

## 【発明の効果】

## 【0009】

本発明による導波路では、半導体部を含むコア層が面内方向に広がった凹凸構造を有する。よって、負誘電率媒質の第一の導体層/半導体部を含むコア層/負誘電率媒質の第二の導体層といった異種材料の積層構造でも、微細な凹凸構造による歪緩和の影響で、格子定数や熱膨張係数の差によって生じる歪が緩和される。具体的には、3つの場合がある。

30

(1) 前記導波モードの電磁波の伝播方向に対して垂直方向に前記凹凸構造凹凸構造を有し、凸部を複数有する場合がある。(2) 前記電磁波の波長を $\lambda$ 、前記導波路の等価屈折率を $n_e$ として、 $g = \lambda / n_e$ と表すときに、前記凹凸構造のピッチ長が $g/2$ 未満である場合がある。(3) 前記凹凸構造のピッチ長が $100\text{ }\mu\text{m}$ 未満である場合がある。従って、製造プロセスなどに起因する歪や欠陥、初期又は動作中に半導体に生じる歪や欠陥が抑制されるので、発振特性などの特性の向上や安定化が期待される。例えば、寸法的に作製が容易で、テラヘルツ波帯の周波数領域で安定して動作する半導体素子やその製造方法を提供することができる。

40

## 【図面の簡単な説明】

## 【0010】

【図1】本発明の素子の実施形態及び実施例1を説明する図。

【図2】本発明の素子の実施例2を説明する図。

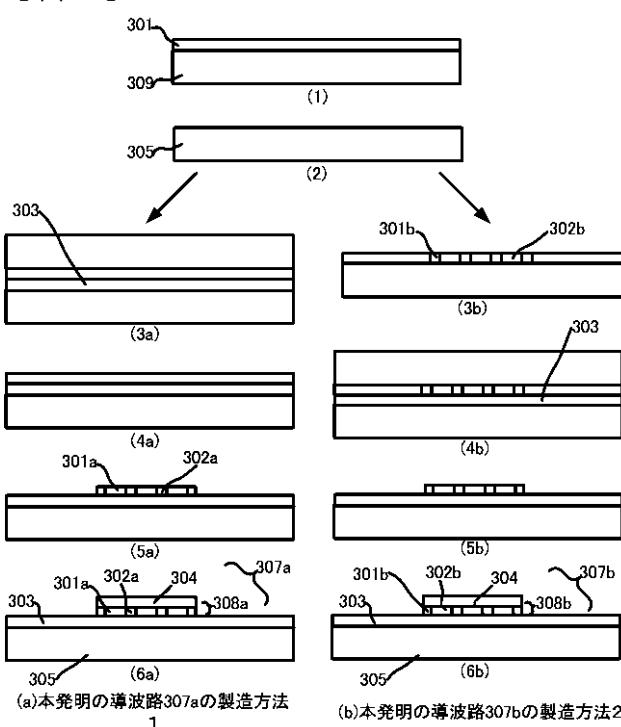

【図3】本発明の導波路の製造方法の例を説明する図。

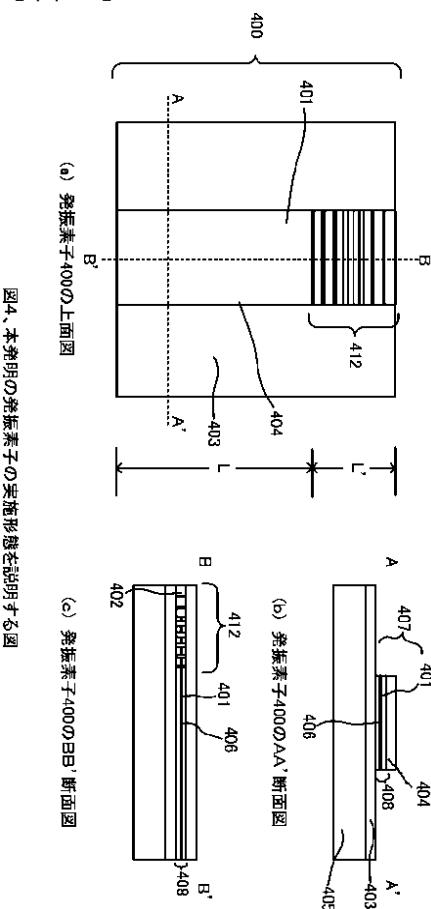

【図4】本発明の素子の実施例3を説明する図。

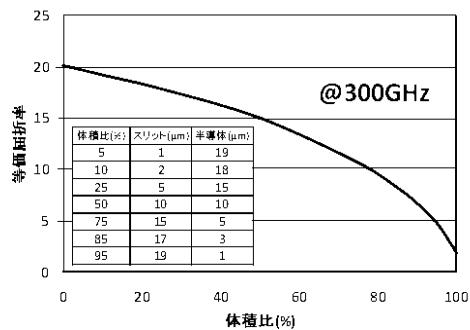

【図5】本発明の素子の実施例3の構造における解析結果を説明する図。

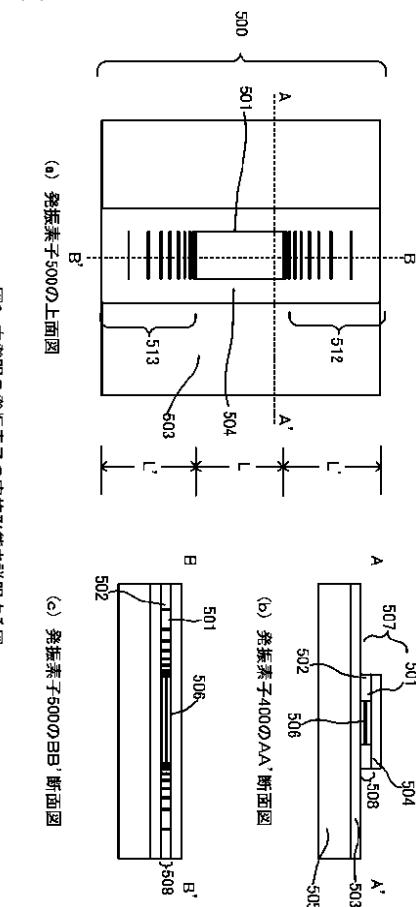

【図6】本発明の素子の実施例3の変形例を説明する図。

【図7】本発明の素子を用いた応用例を示す図。

## 【発明を実施するための形態】

50

## 【0011】

本発明の特徴は、導波路を規定する負誘電率媒質の2つの導体層に接してこれらの間に配置された半導体部を含むコア層が、面内方向に広がった凹凸構造を有することである。さらに、凹凸構造は次のいずれか一つの要件を少なくとも有することを特徴としている。(1)前記導波モードの電磁波の伝播方向に対して垂直方向に前記凹凸構造を有し、凸部を複数有する。(2)前記電磁波の波長を $\lambda$ 、前記導波路の等価屈折率を $n_e$ として、 $g = \lambda / n_e$ と表すときに、前記凹凸構造のピッチ長が $g / 2$ 未満である。(3)前記凹凸構造のピッチ長が $100 \mu m$ 未満である。凹凸構造は、コア層を厚さ方向に貫通する分離溝、厚さ方向にコア層の途中まで掘り下げられた中途溝、コア層中に設けられた中空部などで構成することができる。半導体部が、後述する様な電磁波利得を有する活性層を含む場合、中途溝は、効果に鑑み、好ましくは活性層を貫いて掘り下げられるのがよいが、活性層の手前までしか掘り下げられなくても、一定の効果がある。また、溝や中空部で形成された凹部は、そのまま空間であってもよいが、そこに誘電体や絶縁体が充填されてスペーサとして構成されると、強度、その上に配置される導体層の形状安定性などの点で好ましい。本発明は、凹凸構造の端部におけるミスフィット転位などによる歪緩和の影響を利用するものであるので、こうした歪緩和を起こすのであれば、どの様な形態の凹凸構造をコア層に形成してもよい。本発明による導波路は、単純な電磁波の導波路として用いることもできるが、後述の実施形態や実施例で説明する様に、半導体部に電磁波利得部を持たせて、発振素子、電磁波検出素子、電磁波增幅素子などを構成することもできる。

10

## 【0012】

以下、図を用いて、本発明による導波路、それを含む素子、その製造方法の実施形態及び実施例を説明する。

## (実施形態)

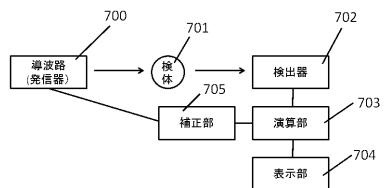

導波路を含む発振素子100の一実施形態について、図1を用いて説明する。図1(a)は上面図、図1(b)は図1(a)のA-A'断面図、図1(c)は図1(a)のB-B'断面図である。

20

## 【0013】

発振素子100は、電磁波利得を有し複数の島状に形成された半導体部101、スペーサ102、導波モードの電磁波に対する誘電率実部が負の負誘電率媒質の導体層である第一の金属層103と第二の金属層104から構成され、基板105上に集積される。本実施形態では、後述の活性層106とその上下の半導体とで半導体部101を構成し、該半導体部とスペーサ102とでコア層108を構成し、クラッドをなす2つの金属層103、104とコア層108とでDMWと呼ばれる導波路107を構成する。厚さ方向の貫通溝で分離された半導体部101は複数の島状に形成されており、その大きさは、 $10 \mu m$ からサブ $\mu m$ のオーダーの範囲が好適である。こうした寸法を持つミリ波からテラヘルツ波の周波数領域用の素子では、半導体部101の大きさは、導波路107の長手方向及び短手方向の幅が $g / 2$ 以下、好ましくは $g / 10$ 以下となる。ここで、 $g$ は導波路107の発振モードにおける管内波長であり、電磁波の波長を $\lambda$ 、導波路の等価屈折率を $n_e$ とすると、 $g = \lambda / n_e$ で表される。2つの金属層103、104は、例えば $g$ 以下の距離に近接して設けられる。

30

## 【0014】

半導体部101は、キャリアのサブバンド間遷移によりテラヘルツ波を発生する多重量子井戸構造からなる活性層106を含み、電磁波利得を有している。活性層106は、例えば、共鳴トンネル構造や、数百から数千層の半導体多層構造を持つ量子カスケードレーザ構造が好適である。本実施形態は、活性層106として、共鳴トンネルダイオード(RTD)を用いた場合で説明する。RTDは、微分負性抵抗領域において、フォトンアシストトンネル現象に基づくミリ波からテラヘルツ波の周波数領域の電磁波利得を有する。半導体部101は、RTDに電流注入するためのエミッタ/コレクタとして、活性層106の上下に、高濃度にドーピングされた層を備えることが好ましい。電磁波利得を有し活性層106を含む半導体部101は、2つの金属層103、104に接し且つ2つの金属層の

40

50

間に配置される。

#### 【0015】

本実施形態では、凹凸構造に特に特徴を有している。具体的には、次の3つになる。(1)前記導波モードの電磁波の伝播方向に対して垂直方向に前記凹凸構造を有し、凸部を複数有する。(2)前記電磁波の波長を $g$ 、前記導波路の等価屈折率を $n_e$ として、 $g = 1/n_e$ と表すときに、前記凹凸構造のピッチ長が $g/2$ 未満である。(3)前記凹凸構造のピッチ長が $100\mu m$ 未満である。このような構成を設けることにより、導波モードの電磁波に対して反射、散乱、屈折などの影響が無視できる凹凸構造であるとみなされるからである。隣接する半導体部101の間には、面内方向に広がった凹凸構造をコア層108に持たせるスペーサ102が半導体部101と接して配置される。面内方向において、半導体部101が凹凸構造の凸部をなし、スペーサ102が凹凸構造の凹部をなす。スペーサ102は、半導体部101とは異なる誘電体や絶縁体などの材料が好適であり、好ましくは、発振する電磁波に対して低損失な材料であると良い。スペーサ102は、半導体部101と異なる格子定数の材料や、多結晶材料、非晶質材料であってもよく、半導体部101が島状、すなわち不連続膜となるような材料であることが好ましい。スペーサ102の大きさは、導波路107の長手方向及び短手方向の幅が $g/2$ 以下、好ましくは $g/10$ 以下であると良い。これは、波長の $1/10$ 以下のサイズの構造体は、一般的にその波長の電磁波に対して反射、散乱、屈折などの影響が無視できるとみなされるからである。

10

#### 【0016】

上述した様に、半導体部101及びスペーサ102の上下には、第二の金属層104と第一の金属層103とが配置されている。半導体部101と第一の金属層103及び第二の金属層104とは機械的かつ電気的に互いに接している。これにより、金属層103、104の間に電圧を印加して、活性層106であるRTDを駆動する。また、スペーサ102は、金属層103、104と少なくとも機械的に接していることが好ましい。スペーサ102は、近接する第一の金属層103と第二の金属層104との間の距離を固定する役割があり、導波路107をリジッドで安定した構造にしている。

20

#### 【0017】

以上の様に、本実施形態の発振素子100は、電磁波利得を有する半導体部101を含むコア層108と、近接した第一の金属層103と第二の金属層104から構成されるクラッドとよりなるDMW導波路107を備える。ここで、発振素子100の発振モードの管内波長を $g$ とした時、第一の金属層103と第二の金属層104の距離は、 $g/2$ 以下、好ましくは $g/10$ 以下まで近接される。この時、ミリ波からテラヘルツ波の周波数領域の電磁波は、導波路107を、回折限界が存在しない表面プラズモンモードで伝搬する。管内波長が $g$ の発振モードを得るには、半導体レーザ技術で知られるように、伝搬方向である導波路107の長手方向の長さ $L$ を $g/2$ の整数倍となるように設定すればよい。

30

#### 【0018】

本実施形態の発振素子は、上記の如き導波路107を有する。金属/半導体部/金属のような格子定数や熱膨張係数が異なる薄膜材料を積層した構造は、製造プロセスなどに起因した歪が半導体部に生じる可能性がある。一般的に、半導体の成膜工程や素子の製造プロセスの熱履歴等で薄膜に生じる内部応力は、略 $\pm 1\text{ GPa}$ の範囲であり、半導体部101や活性層106は、プロセスにより $\pm 0.1\% \sim \pm 1\%$ の歪が生じる可能性がある。ここで、+は引張応力、-は圧縮応力を表す。また、従来のように異種基板を接合してDMW構造を製造する場合、熱膨張係数差による熱応力や、接合界面近傍の応力集中などにより半導体部に歪が生じる可能性がある。

40

#### 【0019】

これに対して、本素子は、導波路107の幅方向の大きさが $g/2$ から $g/10$ 以下(テラヘルツ波の周波数領域では $10\mu m$ からサブ $\mu m$ )の島状に形成した活性層106を含む半導体部101と、その間に配置されたスペーサ102を備える。このように、利得

50

媒質である半導体部を、従来の連続膜から、波長以下のサイズに微細化した島状構造にすることで、島構造の端におけるミスフィット転位に起因した歪緩和の影響で、半導体部に生じる歪を緩和することができる。本実施形態の素子は、テラヘルツ波の周波数領域における発振モードの管内波長  $g$  の大きさから、半導体部の厚さが数十  $\mu\text{m}$  ~ 0 . 1  $\mu\text{m}$ 、幅が数十  $\mu\text{m}$  ~ 0 . 1  $\mu\text{m}$  となり、歪緩和には好適な構造となる。

#### 【0020】

また、本実施形態の素子は、誘電体や絶縁体のスペーサ 102 を隣り合う半導体部 101 の間に配置することで、DMW 構造をより安定化している。スペーサ 102 として、ミリ波からテラヘルツ波で低損失な材料を用いることで、自由電子吸収又は導体損失などによる導波ロスが低減される。さらに、導波路 107 における定在波を効率良く增幅するには、利得媒質である活性層 106 を含む半導体部 101 を、少なくとも、発振モードにおける共振電界の腹となる位置に配置することが望ましい。電磁波利得の増幅に寄与しないスペーサ 102 を、共振電界の節に配置するような構成であってもよい。

10

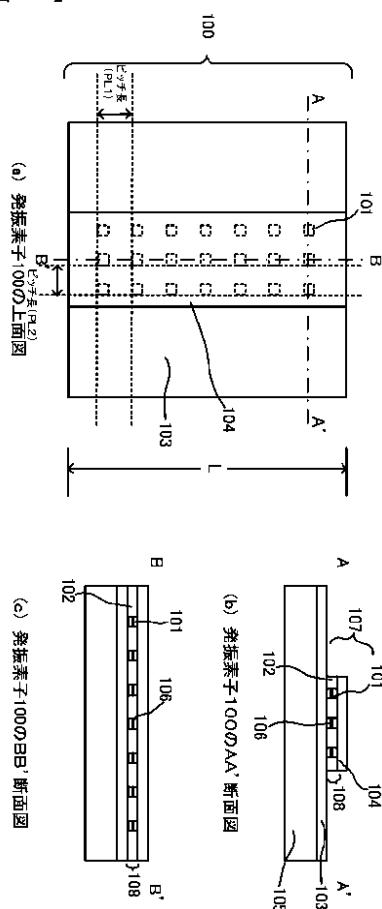

#### 【0021】

図 3 を参照して導波路の製造方法の一例を説明する。この製造方法は、半導体層に凹部を形成するステップと、凹部に物質を充填してスペーサを配置するステップを含む。より具体的には、本実施形態で述べた素子及び素子の共振器である導波路 307 は、次のような工程で製造することで、製造工程などに起因して初期又は動作中に半導体に生じる歪や欠陥を低減することが出来る。導波路 307 は、管内波長  $g$  以下の距離に近接した第一の導体層 303 と第二の導体層 304 からなるクラッドと、導体層 303、304 の間に配置されたコア層 308 とから構成される。コア層 308 は、複数の島状に形成された半導体部 301 とスペーサ 302 とから構成される。導波路 307 は次の (A) ~ (F) のステップを含む工程で製造される。

20

(A) 上面に半導体部 301 を備えた第一の基板 309 を準備するステップ

(B) 第二の基板 305 を準備するステップ

(C) 第一の基板 309 上の半導体部 301 を第二の基板 305 の上面に第一の導体層 303 を介して転写するステップ

(D) 半導体部 301 を島状に分割するステップ

(E) 島状に分割した半導体部 301 の間にスペーサ 302 を配置するステップ

(F) 半導体部 301 の上面に第二の導体層 304 を形成するステップ

30

#### 【0022】

図 3 (a)との対応関係では、図 3 (1) がステップ (A) に対応し、図 3 (2) がステップ (B) に対応し、図 3 (3a)、(4a) がステップ (C) に対応し、図 3 (5a) がステップ (D) と (E) に対応し、図 3 (6a) がステップ (F) に対応する。ここで、(A) ~ (F) は必ずしもこの順 (図 3 (a)) で実施される必要はない。例えば、図 3 の右側 (図 3 (b)) の部分に示したように、(A) (B) (D) (E) (C) (F) の順であっても、転写時の応力を低減可能であり、歪低減の効果が期待される。また、半導体部 301 が電磁波利得を持つ活性層を含めば、導波路 307 を共振器として備えた発振素子 100 が製造される。(D) と (E) のステップを含む製造方法であれば、初期や動作中に半導体が歪む可能性がある構造において、歪を抑制することが出来る。第一の導体層 303 と第二の導体層 304 が金属であれば、低損失で閉じ込め効率が高いダブルプラスモン導波路が実現される。第二の導体層 304 が半導体であれば、低損失なシングルプラスモン導波路を実現することができる。

40

#### 【0023】

以上に述べた如く、本実施形態は、金属 (導体層) / 半導体部 / 金属 (導体層) といった異種薄膜材料の積層構造であっても、製造プロセスなどに起因して半導体に生じる歪や欠陥が抑制される構成の素子及びその製造方法を提供する。従って、本実施形態により、テラヘルツ波帯の周波数領域で安定して動作する発振素子などが実現される。

#### 【0024】

以下、より具体的な実施例を説明する。

50

## (実施例 1 )

本発明の素子の具体的な実施例 1 について、図 1 及び図 3 を用いて説明する。実施例 1 では、サブバンド間遷移によりテラヘルツ波を発生する多重量子井戸構造からなる活性層 106 として、InP 基板に格子整合する InGaAs / InAlAs 系の共鳴トンネルダイオード構造のものを用いた。活性層 106 は、上から順に、n-InGaAs (50 nm,  $1 \times 10^{18} \text{ cm}^{-3}$ )、InGaAs (5 nm)、AlAs (1.3 nm)、InGaAs (7.6 nm, )、InAlAs (2.6 nm)、InGaAs (5.6 nm, )、AlAs (1.3 nm)、InGaAs (5 nm)、n-InGaAs (50 nm,  $1 \times 10^{18} \text{ cm}^{-3}$ ) の順に積層された半導体多層構造である。ここで、厚さの後に 10 を付した InGaAs 層が量子井戸層、 を付していない InAlAs 系の材料がポテンシャル障壁層となり、3重障壁共鳴トンネル構造を構成している。また、InP に格子整合していない AlAs は、臨界薄膜よりは薄く、エネルギーの高い障壁となっている。また、上下の高濃度キャリアでドーピングされた n-InGaAs 層は、共鳴トンネル構造への電子の注入と抽出を行うエミッタ / コレクタ層である。エミッタ / コレクタ層とポテンシャル障壁層の間に配置された InGaAs (5 nm) は、ドーピング材料である Si の拡散防止層である。

## 【0025】

半導体部 101 は、上述の活性層 106 と、活性層 106 の上下に配置された高濃度にキャリアドープされた n-InGaAs (500 nm,  $1 \times 10^{19} \text{ cm}^{-3}$ ) から構成される。このドーピング層により、半導体部 101 と、半導体部 101 の上下に配置した第一の金属層 103 及び第二の金属層 104 とを低抵抗で接続する。第一の金属層 103 と第二の金属層 104 は、Ti / Pd / Au の積層膜で構成される。発振素子 100 は、第一の金属層 103 と第二の金属層 104 を介して電源に接続され、駆動用のバイアス電圧が供給される。これらの構成により、発振素子 100 は、微分負性抵抗領域で、フォトニアリストトンネル現象に基づいてミリ波からテラヘルツ波の周波数領域の電磁波を発生する。

## 【0026】

導波路 107 は、ファブリペロー型の共振器構造であり、電磁波の伝搬方向において少なくとも二つの端面を備えており、この端面からの反射を利用して電磁波を定在化する。こうして、伝搬方向（導波路 107 の長手方向）の長さ L が発振波長を決める要素となる。本実施例では、導波路 107 の長さ L が g の 5 倍となる 1 mm、幅を 0.02 mm としている。従って、第二の金属層 104 は 1 mm × 0.02 mm の矩形パターンである。

## 【0027】

島状に分離して形成した半導体部 101 は、導波モードの電磁波の伝播方向に対して垂直方向に凹凸構造を有し、凸部を複数有する。半導体部は、幅が 2 μm の正方形で、導波路 107 の長手方向にはピッチ長が 100 μm ピッチ (g / 2) で 9 個、導波路 107 の短手方向にはピッチ長が 5 μm ピッチで 3 個配置される。このように、導波モードの電磁波の伝播方向に垂直な短手方向に凹凸構造が伸びるように設けられている。なお、図 1において、ピッチ長とは、凹部と凸部とで一つのピッチ長としている。導波モードの電磁波の伝播方向と平行なピッチ長が PL1 で、伝播方向と面内において垂直方向のピッチ長が PL2 になる。半導体部 101 の数は構造の特徴を分かり易くする示すために省略して記載している。半導体部 101 は、導波路 107 の発振モードの共振電界の腹の位置に配置されている。本実施例の場合、導波路 107 の端面が開放端となり、少なくとも、端面から g / 2 の位置が共振電界の腹の位置となる。また、隣接する半導体部 101 の間にはスペーサ 102 として、テラヘルツ波帯で低損失な BCB (ベンゾシクロブテン) を、半導体部 101 と接するように配置した。スペーサ 102 として、ミリ波からテラヘルツ波で低損失な材料を用いることで、自由電子吸収又は導体損失などによる導波ロスが低減される。第一の金属層 103 と第二の金属層 104 との距離は、半導体部 101 の層厚から分かる様に、約 1 μm であり、スペーサ 102 も同じ厚さに設定した。本実施例では、導波路 107 のコア層 108 は、9割以上が、スペーサ 102 である BCB となるので、発

振周波数 1 T H z における等価屈折率を約 1 . 5 として、発振モードの管内波長  $g$  は 2 0 0  $\mu m$  となる。従って、半導体部 1 0 1 の大きさは  $g / 1 0 0$  程度、ピッチは  $g / 2$  、スペーサ 1 0 2 の大きさは  $g / 2$  程度に対応している。なお、導波路 1 0 7 のコア層 1 0 8 において半導体部 1 0 1 の比率が多くなる場合は、後述の実施例 2 に説明する様に等価屈折率が増大し、比率が半々であれば、実施例 1 と実施例 2 の中間程度になると考えればよい。

#### 【 0 0 2 8 】

本実施例の素子の導波路 3 0 7 a の製造方法について図 3 の左側の部分を用いて説明する。第一の基板として、半導体部 3 0 1 を構成する多重量子井戸構造をエピタキシャル成長した I n P 基板 3 0 9 を準備する(図 3 ( 1 ) )。第二の基板として、G a A s 基板 3 0 5 を準備する(図 3 ( 2 ) )。I n P 基板 3 0 9 の上面(半導体部 3 0 1 が配置された面)に真空蒸着法で T i / P d / A u ( 2 0 n m / 2 0 n m / 2 0 0 n m ) を成膜する。G a A s 基板 3 0 5 の上面に真空蒸着法で T i / P d / A u ( 2 0 n m / 2 0 n m / 2 0 0 n m ) を成膜する。I n P 基板 3 0 9 と G a A s 基板 3 0 5 の上面を対向させて A u の熱圧着により両基板を接合する(図 3 ( 3 a ) )。ここで、熱圧着により形成した T i / P d / A u / P d / T i ( 2 0 n m / 2 0 n m / 4 0 0 n m / 2 0 n m / 2 0 n m ) が第一の金属層 3 0 3 となる。研磨及び塩酸エッティングにより、一体化した基板から、I n P 基板 3 0 9 を除去し、半導体部 3 0 1 を G a A s 基板 3 0 5 に転写する(図 3 ( 4 a ) )。フォトリソグラフィーとドライエッティング法により、半導体部 3 0 1 を島状の半導体部 3 0 1 a に分割する。スピニコート法及びドライエッティング法により、隣接する半導体部 3 0 1 a の間に B C B を埋め込んで、スペーサ 3 0 2 a を形成し、コア層 3 0 8 a を形成する(図 3 ( 5 a ) )。真空蒸着法とリフトオフ法を用いて、T i / P d / A u ( 2 0 n m / 2 0 n m / 2 0 0 n m ) からなる第二の金属層 3 0 4 を形成する(図 3 ( 6 a ) )。

#### 【 0 0 2 9 】

本実施例の素子では、金属 / 半導体 / 金属といった異種薄膜材料の積層構造であっても、格子定数や熱膨張係数の差によって生じる歪が緩和される。従って、製造プロセスなどに起因して初期又は動作中に半導体に生じる歪や欠陥が抑制されるので、発振特性などの特性の向上や安定化が実現される。この際、スペーサ 1 0 2 を配置することでリジッドな構造のプラズモン導波路となり、より安定な素子が実現される。また、電磁波利得を持つ半導体部 1 0 1 を、少なくとも導波路の発振モードにおける腹の位置に配置し、テラヘルツ波で低損失な材料のスペーサ 1 0 2 を発振モードの節の位置に配置しているので、低損失で高効率なプラズモン導波路が実現される。さらに、本発明の半導体素子は、電流が流れる半導体部 1 0 1 が凹凸構造や島状構造といった不連続の膜で構成される。このため、従来に比べて半導体の面積が低減されることで、素子に流れる電流が抑制される。具体的には、本実施例の場合、半導体層の構造と面積から概算した素子抵抗は、従来の約 0 . 1 に対し本実施例は 1 0 0 倍の 1 0 程度となる。このため、素子や周辺回路及び外部電源を含むシステム全体の低電流化が図れるので、微小な抵抗や容量などの寄生成分の影響が低減され、発振素子の歩留まり向上が期待される。また、大電流が不要となれば電源や周辺回路に標準的な電子部品や装置を使用することが出来るので、コスト削減といったより実用的な効果も期待される。

#### 【 0 0 3 0 】

本発明は上記構成に限定されるものではなく、以下に示す様な変形例も可能である。例えば、本実施例では、活性層 1 0 6 として、I n P 基板上に成長した I n G a A s / I n A l A s 、I n G a A s / A l A s からなる 3 重障壁共鳴トンネルダイオードについて説明してきた。しかし、これらの構造や材料系に限られることなく、他の構造や材料の組み合わせであっても半導体素子を提供することができる。例えば、2 重障壁量子井戸構造を有する共鳴トンネルダイオードや、4 重以上の多重障壁量子井戸構造を有する共鳴トンネルダイオード、量子カスケードレーザで知られるようなカスケード接続された多重量子井戸構造などを用いても良い。また材料系としては、G a A s 基板上に形成した G a A s / A l G a A s / 、G a A s / A l A s 、I n G a A s / G a A s / A l A s 、I n P 基板上の

10

20

30

40

50

InGaAs / AlGaAsSb、InAs 基板上の InAs / AlAsSb、InAs / AlSb、Si 基板上に形成した SiGe / SiGe の組み合わせ等であっても良い。これら構造と材料は、所望される周波数などに応じて適宜選定すれば良い。

### 【0031】

また、本実施例では、キャリアが電子である場合を想定して説明をしているが、本発明はこれに限定されるものではなく、正孔（ホール）を用いたものであっても良い。また、基板の材料は用途に応じて選定すればよく、シリコン基板、ガリウムヒ素基板、インジウムヒ素基板、ガリウムリン基板などの半導体基板や、ガラス基板、セラミック基板、樹脂基板などを用いても良い。また、第一の金属層 103 及び第二の金属層 104 には、金属（Ag、Au、Cu、Al、AuIn 合金など）及び半金属（Bi、Sb、ITO、ErAs など）を好適に用いることが出来る。もちろん、高濃度にドーピングされた半導体を導電体として用いても良い。また、スペーサ 102 には、SiO<sub>2</sub>、TEOS、ポリシリコン、SiN<sub>x</sub>、AlN、TiO<sub>2</sub>などの無機材料や、BCB、SU-8、ポリイミドなどの有機材料が好適に用いられる。また、低導電性の真性半導体を再成長したものを用いても良い。これらの変形例は、他の実施形態や実施例でも同様に適用可能である。10

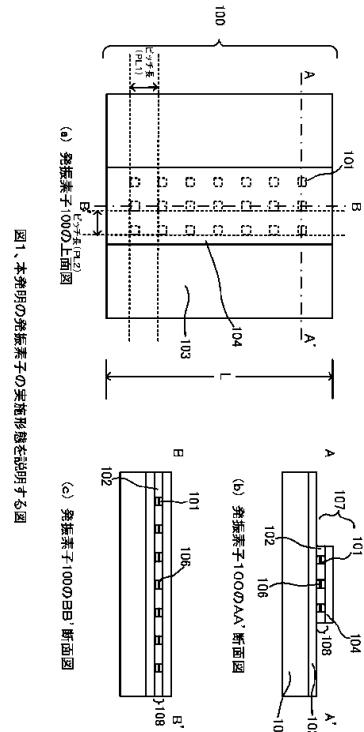

### 【0032】

#### （実施例 2）

本発明の素子の実施例 2 について、図 2 及び図 3 を用いて説明する。活性層 206 は、実施例 1 と同じ共鳴トンネルダイオード構造を用いており、半導体部 201 の層構成も同じである。導波路 207 も、実施例 1 と同様、長さ  $l$  が  $g$  の 20 倍となる 1 mm、幅が 0.05 mm で、第二の金属層 204 は 1 mm × 0.05 mm の矩形パターンとなるように形成される。その他、実施例 1 と同じ構造については説明を省略する。20

### 【0033】

本実施例における島状に形成した半導体部 201 は、幅が 24 μm の正方形で、導波路 207 の端から、長手方向及び短手方向にそれぞれ一ピッチ長が 25 μm ピッチで、 $g/8$  で配置した。図 2 において、ピッチ長とは、凹部と凸部とを一つの周期（一ピッチ長）としている。導波モードの電磁波の伝播方向と平行なピッチ長が PL1 で、伝播方向と面内において垂直方向のピッチ長が PL2 になる。半導体部 201 の数は構造体を分かりやすく示すため省略して記載している。隣接する半導体部 201 の間には、幅 1 μm のスペーサ 202 が、導波路 207 の発振モードにおける共振電界の節にライン状に配置される。本実施例の場合、導波路 207 の端面が開放端となり、少なくとも端面から  $g/4$  の位置が共振電界の節の位置となる。增幅に寄与しない電界の節に、利得媒質でないスペーサ 202 を配置することで、そこに半導体部 201 がある構造よりも、発振素子の利得低下を防止している。本実施例では、スペーサ 202 として、テラヘルツ波帯で低損失な SiO<sub>2</sub> を半導体部 201 と接するように配置した。30

### 【0034】

第一の金属層 203 と第二の金属層 204 との距離は、半導体部 201 の層厚から、約 1 μm であり、スペーサ 202 も同じ厚さに設定した。本実施例では、導波路 207 のコア層 208 は、9 割以上が半導体部 201 であり、電磁波は活性層 206 の薄い真性半導体層を表面プラズモンモードで伝搬する。本実施例では、発振周波数 0.3 THz における導波路 207 の等価屈折率を約 2.0 として、発振モードの管内波長  $g$  は 50 μm となる。従って、半導体部 201 の大きさは  $g/2$  程度、ピッチは  $g/2$  程度、スペーサ 202 の大きさは  $g/50$  程度に対応している。40

### 【0035】

本実施例の素子の導波路 307b の製造方法について図 3 の右側の部分を用いて説明する。本実施例の導波路 307b は、次のように製造される。第一の基板として、分子線エピタキシーなどで半導体部 301 を構成する多重量子井戸構造をエピタキシャル成長した InP 基板 309 を準備する（図 3（1））。第二の基板として、GaAs 基板 305 を準備する（図 3（2））。フォトリソグラフィーとドライエッチング法により、半導体部 301 を島状の半導体部 301b に分割する。プラズマ CVD 法と CMP 法を用いて、隣接

10

20

30

40

50

する半導体 30b の間に  $\text{SiO}_2$  を埋め込みスペーサ 302b を形成する(図3(3b))。InP基板309の上面(半導体部301bが配置された面)に真空蒸着法でTi/Pd/Au(20nm/20nm/200nm)を成膜する。GaAs基板305の上面に真空蒸着法でTi/Pd/Au(20nm/20nm/200nm)を成膜する。InP基板309とGaAs基板305の上面を対向させてAuの熱圧着により基板を接合する(図3(4b))。ここで、熱圧着により形成したTi/Pd/Au/Pd/Ti(20nm/20nm/400nm/20nm/20nm)が第一の金属層303となる。研磨及び塩酸エッティングにより、一体化した基板から、InP基板309を除去し、半導体部301bをGaAs基板305に転写する。フォトリソグラフィーとドライエッティング法によりスペーサ302bを成形する(図3(5b))。真空蒸着法とリフトオフ法を用いて、Ti/Pd/Au(20nm/20nm/200nm)からなる第二の金属層304を形成する(図3(6b))。

10

## 【0036】

本実施例の素子においても、製造プロセスなどに起因して初期又は動作中に半導体に生じる歪や欠陥が抑制されるので、発振特性などの特性の向上や安定化が実現される。

## 【0037】

## (実施例3)

本発明の実施例3について、図4から図6を用いて説明する。なお、図において、凹凸構造の数は省略して記載している。活性層406は、実施例1と同じ共鳴トンネルダイオード構造を用いており、半導体部401の層構成も同じである。導波路407は、長さLがgの20倍となる1mm、幅が0.005mmで、第二の金属層404は1mm×0.005mmの矩形パターンとなるように形成される。その他、実施例1と同じ構造については説明を省略する。

20

## 【0038】

本実施例の発振素子400は、導波路407の片側の端面付近に、面内方向に広がる凹凸構造である島状に形成された半導体部401とスペーサ402が配置された領域412を備える。ここで、スペーサ402は、実施例1と同様にBCBで構成される。本実施例では、導波路407のコア408における半導体部401とスペーサ402の体積比が面内方向に分布している。言い換えると、導波路407のコア408の凹凸構造の粗密が導波路の端面近傍で段階的に変化する構成となっている。より具体的には、図5に示した表の通り、端面方向に向かって $20\mu\text{m}$ ピッチで、半導体部401の体積比が段階的に減少(従って、スペーサ402の体積比が段階的に増加)するように配置されており、領域412の長さL'は0.14mmである。

30

## 【0039】

図5には、本実施例で示した導波路407の構造について、スペーサの体積比と300GHzにおける等価屈折率との相関を高周波電磁界シミュレータ(アンシス社製HFSS)を用いて解析した結果を示した。導波路407を伝搬する電磁波の等価屈折率は、スリット402と半導体401の体積比に対して約2から20の間で段階的に変化する。従って、本実施例にて開示した構造は、導波路400の端部の領域412において、等価屈折率が端面方向に向かってグレーデッドに減少しながら約2に近づくので、導波路外部とのインピーダンスマッチングを比較的容易に達成することが可能となる。ここで、導波路の外部とは、自由空間、伝送線路、低誘電率の誘電体などが挙げられる。

40

## 【0040】

図6は、本実施例の変形例となる導波路500の説明図である。なお、図において、凹凸構造の数は構造の特徴を分かり易く示すために省略して記載している。また、図4に開示した発振素子400と基本的な構造や材料は同じであるためそれらの説明は省略する。この変形例の発振素子500のように、導波路507の両側の端面付近に、面内方向に広がる凹凸構造である島状に形成された半導体部501とスペーサ502が配置された領域512と領域513を備えるような構成であっても良い。導波路507の領域512と領域513には、 $2\mu\text{m}$ 幅の半導体部501が、単位長さあたりの個数が端面方向に向かって

50

段階的に減少するように配置されている。具体的には、 $2 \mu m$ 幅の半導体部 501 の長さ  $50 \mu m$ における個数を 25 個、10 個、5 個、2 個、1 個と  $50 \mu m$ ピッチで段階的に減少するように配置される。この場合、 $L' = 250 \mu m$ である。このような方法で、端面付近の等価屈折率をグレーデッドに変化させる構成も外部とのインピーダンスマッチングに好適である。

#### 【0041】

また、本実施例の別の変形例として、導波路 407 のコア 408 の凹凸構造の粗密を部分的に変化することで、導波路の有効屈折率を部分的に変化させることも可能である。

#### 【0042】

本実施例の素子においても、製造プロセスなどに起因して初期又は動作中に半導体に生じる歪や欠陥が抑制されるので、発振特性などの特性の向上や安定化が実現される。また、DMW は、導波路と空間とのモードミスマッチに起因した端面反射の増加やビームパターンの発散が生じるため、応用の観点からビームの効率的な利用を取り回しが課題となっている。本実施例の構成であれば、導波路と外部とのインピーダンスマッチングが容易な高効率の導波路を提供することが可能となる。10

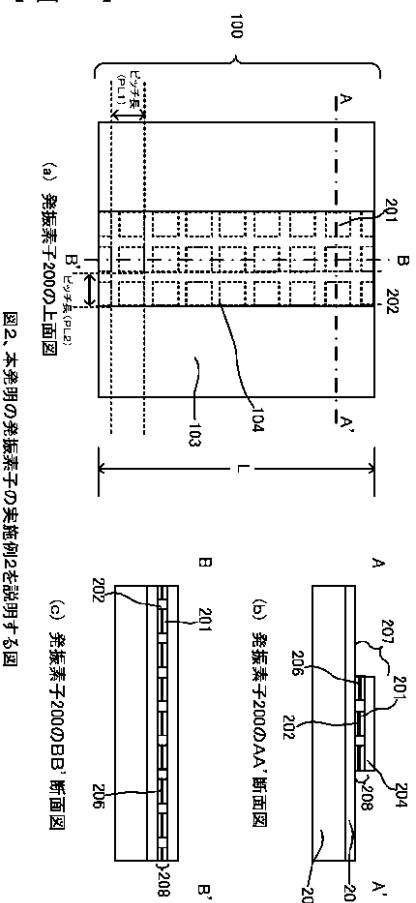

#### 【0043】

また、これまで説明してきた導波路を用い、検体の状態などを算出する演算部などと組合せた図 7 に示す装置を提供することができる。例えば、導波路を発信器 700 として用い、導波路の端部に検体 701 を配置する。検体 701 は導波路から発信される電磁波と相互作用するため、発信された電磁波は何らかの影響をうける。検体に照射された電磁波は反射や透過するため、それを検出器 702 で検出する。その後、パソコン等の演算部 703 で、検出した信号から検体 701 の状態を算出する。具体的には、薬の状態などを検査する産業用検査装置などの応用が想定される。演算部 703 で得られた検体 701 の状態は表示部 704 で表示することもできる。また、発信器 700 からの情報を用いて、補正部により、演算部 703 で得られる検体 701 の状態に補正をかけてもよい。20

#### 【0044】

以上、本発明の実施形態と実施例について説明したが、本発明はこれらの実施形態と実施例に限定されず、その要旨の範囲内で種々の変形及び変更が可能である。

#### 【符号の説明】

#### 【0045】

101 … 半導体部、103 … 第一の導体層（第一の金属層）、104 … 第二の導体層（第二の金属層）、107 … 導波路、108 … コア層30

【図1】

図1、本発明の発振素子の実施形態を説明する図

【図2】

図2、本発明の発振素子の実施例2を説明する図

【図3】

図3、本発明の導波路の製造方法を説明する図

【図4】

図4、本発明の発振素子の実施形態を説明する図

【図5】

図5、本発明の素子の実施例3の構造における解析結果を説明する図

【図6】

図6、本発明の発振素子の実施形態を説明する図

【図7】