(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5815578号

(P5815578)

(45) 発行日 平成27年11月17日(2015.11.17)

(24) 登録日 平成27年10月2日(2015.10.2)

|                             |            |

|-----------------------------|------------|

| (51) Int.Cl.                | F 1        |

| <b>H04B 1/16 (2006.01)</b>  | H04B 1/16  |

| <b>H03F 1/32 (2006.01)</b>  | H03F 1/32  |

| <b>H03F 3/189 (2006.01)</b> | H03F 3/189 |

請求項の数 37 外国語出願 (全 28 頁)

|              |                                                                   |

|--------------|-------------------------------------------------------------------|

| (21) 出願番号    | 特願2013-19131 (P2013-19131)                                        |

| (22) 出願日     | 平成25年2月4日(2013.2.4)                                               |

| (62) 分割の表示   | 特願2011-523944 (P2011-523944)<br>の分割<br>原出願日 平成21年8月18日(2009.8.18) |

| (65) 公開番号    | 特開2013-138458 (P2013-138458A)                                     |

| (43) 公開日     | 平成25年7月11日(2013.7.11)                                             |

| 審査請求日        | 平成25年3月5日(2013.3.5)                                               |

| (31) 優先権主張番号 | 12/193,695                                                        |

| (32) 優先日     | 平成20年8月18日(2008.8.18)                                             |

| (33) 優先権主張国  | 米国(US)                                                            |

|           |                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595020643<br>クアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92<br>121-1714、サン・ディエゴ、モア<br>ハウス・ドライブ 5775 |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                                                                |

| (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                                                                |

| (74) 代理人  | 100088683<br>弁理士 中村 誠                                                                                                 |

| (74) 代理人  | 100103034<br>弁理士 野河 信久                                                                                                |

最終頁に続く

(54) 【発明の名称】負荷切換を用いた高線形性低ノイズ受信器

## (57) 【特許請求の範囲】

## 【請求項 1】

低ノイズ・アンプ(LNA)入力信号を受信し、少なくとも1つのLNA出力信号を提供するように構成されている低ノイズ・アンプ(LNA)であって、並列接続された複数のNチャネル金属酸化膜半導体(NMOS)トランジスタ、および別個の複数のNMOSトランジスタならびに複数のPチャネル金属酸化膜半導体(PMOS)トランジスタを具備する、低ノイズ・アンプと、

前記LNAに結合されている複数のミキサ対であって、各ミキサ対はイネーブルにされていると1つのLNA出力信号をダウンコンバートするように構成されており、各ミキサ対は選択的にイネーブルまたはディセーブルにされる、複数のミキサ対と、

を具備し、

前記複数のミキサ対は可変のミキサ入力インピーダンスを有し、各ミキサ対の選択的なイネーブル化およびディセーブル化は変化するミキサ入力インピーダンスによって装置線形性を増加させる、装置。

## 【請求項 2】

前記複数のミキサ対が、相違するサイズのトランジスタを用いて実現されている第1および第2ミキサ対を具備する、

請求項1の装置。

## 【請求項 3】

前記複数のミキサ対が、相違する量の電流または相違するバイアス電圧によってバイア

10

20

スされる第1および第2ミキサ対を具備する、

請求項1の装置。

【請求項4】

前記複数のミキサ対が、相違する信号レベルの局部発振器(LO)信号によって駆動される第1および第2ミキサ対を具備する、

請求項1の装置。

【請求項5】

前記複数のミキサ対が、相互に結合されかつ被ダウンコンバート信号を提供する出力を有する、

請求項1の装置。

10

【請求項6】

各ミキサ対が複数のモードの中から選択されたモードに基づいてイネーブルまたはディセーブルにされ、

各モードは、少なくとも1つのミキサ対の相違する組と関連付けられており、

前記選択されたモードと関連付けられている前記少なくとも1つのミキサ対はイネーブルにされ、存在する場合は残りのミキサ対は全てディセーブルにされる、

請求項1の装置。

【請求項7】

高線形性モードについては第1および第2ミキサ対がイネーブルにされ、

低線形性モードについては前記第1ミキサ対がイネーブルにされるとともに前記第2ミキサ対がディセーブルにされる、

20

請求項1の装置。

【請求項8】

大きな妨害信号が検出される場合に高線形性モードが選択され、

大きな妨害信号が検出されない場合に低線形性モードが選択される、

請求項7の装置。

【請求項9】

前記LNAが1つのLNA出力信号を提供するように構成されており、

各ミキサ対が、イネーブルにされていると前記LNA出力信号をダウンコンバートするように、構成されている、

30

請求項1の装置。

【請求項10】

前記LNAが、複数のLNA出力信号を提供するように構成されており、

1つのLNA出力信号が各ミキサ対用であり、

各ミキサ対が、イネーブルにされていると、それぞれのLNA出力信号をダウンコンバートするように構成されている、

請求項1の装置。

【請求項11】

前記LNAが第1および第2LNA出力信号を提供するように構成されており、

第1ミキサ対が、イネーブルにされていると前記第1LNA出力信号をダウンコンバートするように構成されており、

40

第2ミキサ対が、イネーブルにされていると前記第2LNA出力信号をダウンコンバートするように構成されている、

請求項1の装置。

【請求項12】

入力段および出力段を具備する低ノイズ・アンプ(LNA)であって、前記入力段はLNA入力信号を受信するとともに被增幅信号を提供し、前記出力段は前記被增幅信号をバッファするとともに少なくとも1つのLNA出力信号を提供し、前記出力段は並列結合されている複数の負荷部を具備し、各負荷部は選択的にイネーブルまたはディセーブルにされるように構成されている、低ノイズ・アンプ

50

を具備する装置であって、

前記装置は、各負荷部を選択的にイネーブルおよびディセーブルにすることによって前記LNAの内部負荷を変化するように構成されており、

前記入力段は並列接続された複数のNチャネル金属酸化膜半導体(NMOS)トランジスタを具備し、各負荷部は複数のNMOSトランジスタおよび複数のPチャネル金属酸化物半導体(PMOS)トランジスタを具備する、

装置。

【請求項13】

前記複数の負荷部の各々が1組のNチャネル金属酸化膜半導体(NMOS)トランジスタに結合されている1組のPチャネル金属酸化膜半導体(PMOS)トランジスタを具備する、

請求項12の装置。

【請求項14】

前記複数の負荷部が、相違するサイズのトランジスタを用いて実現されている、

請求項12の装置。

【請求項15】

前記複数の負荷部が、相違する量の電流または相違するバイアス電圧によってバイアスされる、

請求項12の装置。

【請求項16】

前記複数の負荷部が、複数のLNA出力信号を提供するように構成されており、

1つのLNA出力信号が各負荷部用である、

請求項12の装置。

【請求項17】

前記複数の負荷部が第1および第2負荷部を具備し、

高線形性モードについては前記第1および第2負荷部がイネーブルにされ、

低線形性モードについては前記第1負荷部がイネーブルにされるとともに前記第2負荷部がディセーブルにされる、

請求項12の装置。

【請求項18】

低ノイズ・アンプ(LNA)入力信号を受信し、複数のLNA出力信号を提供するように構成されている低ノイズ・アンプ(LNA)であって、並列接続された複数のNチャネル金属酸化膜半導体(NMOS)トランジスタ、および別個の複数のNMOSトランジスタならびに複数のPチャネル金属酸化膜半導体(PMOS)トランジスタを具備する、低ノイズ・アンプと、

前記LNAに結合されている複数のミキサ対であって、各ミキサ対はイネーブルにされていると前記複数のLNA出力信号のうちの相違する1つをダウンコンバートするように構成されている、複数のミキサ対と、

を具備し、

前記複数のミキサ対は可変のミキサ入力インピーダンスを有し、各ミキサ対の選択的なイネーブル化およびディセーブル化は変化するミキサ入力インピーダンスによって装置線形性を増加させる、装置。

【請求項19】

各ミキサ対が、複数のモードの中から選択されたモードに基づいてイネーブルまたはディセーブルにされる、

請求項18の装置。

【請求項20】

前記LNAが、前記複数のLNA出力信号を提供するように構成されている複数の負荷部を具備し、

各負荷部が、選択されたモードに基づいてイネーブルまたはディセーブルにされる、

10

20

30

40

50

請求項 1 9 の装置。

【請求項 2 1】

前記 L N A が、第 1 および第 2 ミキサ対のための第 1 および第 2 L N A 出力信号を提供するように構成されている第 1 および第 2 負荷部をそれぞれ具備する、

請求項 1 8 の装置。

【請求項 2 2】

高線形性モードについては前記第 1 および第 2 負荷部ならびに前記第 1 および第 2 ミキサ対がイネーブルにされ、

低線形性モードについては前記第 1 負荷部および前記第 1 ミキサ対がイネーブルにされるとともに前記第 2 負荷部および前記第 2 ミキサ対がディセーブルにされる、

請求項 2 1 の装置。

【請求項 2 3】

低ノイズ・アンプ ( L N A ) 入力信号を受信し、少なくとも 1 つの L N A 出力信号を提供するように構成されている低ノイズ・アンプ ( L N A ) であって、並列接続された複数の N チャネル金属酸化膜半導体 ( N M O S ) トランジスタ、および別個の複数の N M O S トランジスタならびに複数の P チャネル金属酸化膜半導体 ( P M O S ) トランジスタを具備する、低ノイズ・アンプと、

前記 L N A に結合されている複数のミキサ対であって、各ミキサ対はイネーブルにされていると少なくとも 1 つの L N A 出力信号のうちの 1 つをダウンコンバートするように構成されており、各ミキサ対は選択的にイネーブルまたはディセーブルにされる、複数のミキサ対と、

を具備し、

前記複数のミキサ対は可変のミキサ入力インピーダンスを有し、各ミキサ対の選択的なイネーブル化およびディセーブル化は変化するミキサ入力インピーダンスによって集積回路線形性を増加させる、集積回路。

【請求項 2 4】

高線形性モードについては第 1 および第 2 ミキサ対がイネーブルにされ、

低線形性モードについては前記第 1 ミキサ対がイネーブルにされるとともに前記第 2 ミキサ対がディセーブルにされる、

請求項 2 3 の集積回路。

30

【請求項 2 5】

前記 L N A が並列結合されている複数の負荷部を具備し、

各負荷部が選択的にイネーブルまたはディセーブルにされる、

請求項 2 3 の集積回路。

【請求項 2 6】

前記複数の負荷部が第 1 および第 2 負荷部を具備し、

高線形性モードについては前記第 1 および第 2 負荷部がイネーブルにされ、

低線形性モードについては前記第 1 負荷部がイネーブルにされるとともに前記第 2 負荷部がディセーブルにされる、

請求項 2 5 の集積回路。

40

【請求項 2 7】

前記複数の負荷部が第 1 および第 2 負荷部を具備し、

高線形性モードについては前記第 1 および第 2 負荷部ならびに第 1 および第 2 ミキサ対がイネーブルにされ、

低線形性モードについては前記第 1 負荷部および前記第 1 ミキサ対がイネーブルにされるとともに前記第 2 負荷部および前記第 2 ミキサ対がディセーブルにされる、

請求項 2 5 の集積回路。

【請求項 2 8】

検出された動作条件に基づいて複数のモードの中からモードを選択することと、

前記選択されたモードに基づいて、複数のミキサ対のうちの少なくとも 1 つのミキサ対

50

をイネーブルにすることと、

前記選択されたモードに基づいて、存在する場合に前記複数のミキサ対のうちの残りのミキサ対をディセーブルにすることと、

前記選択されたモードに基づいて、低ノイズ・アンプ (LNA) の複数の負荷部のうちの少なくとも1つの負荷部をイネーブルにすることであって、前記LNAは並列接続された複数のNチャネル金属酸化膜半導体 (NMOS) トランジスタ、および別個の複数のPMOSトランジスタならびに複数のPチャネル金属酸化膜半導体 (PMOS) トランジスタを具備する、イネーブルにすることと、

前記選択されたモードに基づいて、存在する場合に前記複数の負荷部のうちの残りの負荷部をディセーブルにすることと、

10

を具備し、

前記複数のミキサ対は可変のミキサ入力インピーダンスを有し、ミキサ対をイネーブルおよびディセーブルにすることは変化するミキサ入力インピーダンスによって受信器線形性を増加させる、受信器を操作する方法。

【請求項29】

前記複数のミキサ対のうちの少なくとも1つのミキサ対をイネーブルにすることおよび残りのミキサ対をディセーブルにすることが、高線形性モードが選択されている場合に第1および第2ミキサ対をイネーブルにすることと、低線形性モードが選択されている場合に前記第1ミキサ対をイネーブルにするとともに前記第2ミキサ対をディセーブルにすることと、を具備する、

20

請求項28の方法。

【請求項30】

前記複数の負荷部が第1および第2負荷部を具備し、

前記複数の負荷部のうちの少なくとも1つの負荷部をイネーブルにすることおよび残りの負荷部をディセーブルにすることが、高線形性モードが選択されている場合に前記第1および第2負荷部をイネーブルにすることと、低線形性モードが選択されている場合に前記第1負荷部をイネーブルにするとともに前記第2負荷部をディセーブルにすることと、を具備する、

請求項28の方法。

【請求項31】

30

前記モードを選択することが、

大きな妨害信号を検出することと、

大きな妨害信号が検出される場合に高線形性モードを選択することと、

大きな妨害信号が検出されない場合に低線形性モードを選択することと、

を具備する、

請求項28の方法。

【請求項32】

検出された動作条件に基づいて複数のモードの中からモードを選択するための手段と、

前記選択されたモードに基づいて、複数のミキサ対のうちの少なくとも1つのミキサ対をイネーブルにするための手段と、

40

前記選択されたモードに基づいて、存在する場合に前記複数のミキサ対のうちの残りのミキサ対をディセーブルにするための手段と、

前記選択されたモードに基づいて、低ノイズ・アンプ (LNA) の複数の負荷部のうちの少なくとも1つの負荷部をイネーブルにするための手段であって、前記LNAは並列接続された複数のNチャネル金属酸化膜半導体 (NMOS) トランジスタ、および別個の複数のNMOSトランジスタならびに複数のPチャネル金属酸化膜半導体 (PMOS) トランジスタを具備する、イネーブルにするための手段と、

前記選択されたモードに基づいて、存在する場合に前記複数の負荷部のうちの残りの負荷部をディセーブルにするための手段と、

を具備する装置。

50

## 【請求項 3 3】

前記複数のミキサ対のうちの少なくとも 1 つのミキサ対をイネーブルにするための手段および残りのミキサ対をディセーブルにするための手段が、

高線形性モードが選択されている場合に第 1 および第 2 ミキサ対をイネーブルにするための手段と、

低線形性モードが選択されている場合に前記第 1 ミキサ対をイネーブルにするとともに前記第 2 ミキサ対をディセーブルにするための手段と、

を具備する、

請求項 3 2 の装置。

## 【請求項 3 4】

10

前記複数の負荷部が第 1 および第 2 負荷部を具備し、

前記複数の負荷部のうちの少なくとも 1 つの負荷部をイネーブルにするための手段および残りの負荷部をディセーブルにするための手段が、

高線形性モードが選択されている場合に前記第 1 および第 2 負荷部をイネーブルにするための手段と、

低線形性モードが選択されている場合に前記第 1 負荷部をイネーブルにするとともに前記第 2 負荷部をディセーブルにするための手段と、

を具備する、

請求項 3 2 の装置。

## 【請求項 3 5】

20

前記モードを選択するための手段が、

大きな妨害信号を検出するための手段と、

大きな妨害信号が検出される場合に高線形性モードを選択するための手段と、

大きな妨害信号が検出されない場合に低線形性モードを選択するための手段と、

を具備する、

請求項 3 2 の装置。

## 【請求項 3 6】

少なくとも 1 つのコンピュータに、検出された動作条件に基づいて複数のモードの中からモードを選択させるためのコードと、

前記少なくとも 1 つのコンピュータに、前記選択されたモードに基づいて、複数のミキサ対のうちの少なくとも 1 つのミキサ対をイネーブルにさせるためのコードと、

前記少なくとも 1 つのコンピュータに、前記選択されたモードに基づいて、存在する場合に前記複数のミキサ対のうちの残りのミキサ対をディセーブルにさせるためのコードと、

前記選択されたモードに基づいて、低ノイズ・アンプ ( L N A ) の複数の負荷部のうちの少なくとも 1 つの負荷部をイネーブルにするためのコードであって、前記 L N A は並列接続された複数の N チャネル金属酸化膜半導体 ( N M O S ) トランジスタ、および別個の複数の N M O S トランジスタならびに複数の P チャネル金属酸化膜半導体 ( P M O S ) トランジスタを具備する、イネーブルにするためのコードと、

前記選択されたモードに基づいて、存在する場合に前記複数の負荷部のうちの残りの負荷部をディセーブルにするためのコードと、

を具備するコンピュータ可読記憶媒体。

## 【請求項 3 7】

40

前記少なくとも 1 つのミキサ対をイネーブルにするためのコードおよび前記複数のミキサ対のうちの残りのミキサ対をディセーブルにするためのコードが、

高線形性モードが選択されている場合に第 1 および第 2 ミキサ対をイネーブルにするためのコードと、

低線形性モードが選択されている場合に前記第 1 ミキサ対をイネーブルにするとともに前記第 2 ミキサ対をディセーブルにするためのコードと、

を具備する、

50

請求項 3 6 のコンピュータ可読記憶媒体。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、概して電子回路に関し、より具体的には無線通信用受信器に関する。

【背景技術】

【0002】

受信器は、無線周波数 (RF) 被受信 (受信された) 信号を調整し (例えば、増幅し、濾波し、ダウンコンバートし)、かつベースバンド信号を提供するために、様々な無線通信システム中で広く使用されている。受信器は、典型的には、様々な線形性要件およびノイズ要件を満たすことを要求されている。これらの要件はいくつかの無線通信システムについて厳格であり得る。受信器は、最悪の動作条件の下でその厳格な線形性要件およびノイズ要件を満たすことを目的として、多くの無効成分 (例えばインダクタ) および高バイアス電流とともに設計され得る。無効成分は受信器のサイズおよびコストを上げ得、高バイアス電流は電力消費を上げ得る。これらはいずれも望ましくない。

10

【発明の概要】

【0003】

良好な線形性およびノイズ性能を有する受信器が本明細書において記述されている。一デザインでは、受信器は、低ノイズ・アンプ (LNA) および相互に結合されている出力を有する複数のミキサ対を含んでいる。LNAはLNA入力信号を受信および増幅し、少なくとも1つのLNA出力信号を提供する。各ミキサ対は、同相 (I) 成分用のミキサおよび直交位相 (Q) 成分用の別のミキサを含んでいる。複数のミキサ対は同じまたは相違するサイズのトランジスタを用いて (によって) 実現され、同じまたは相違する量の電流によってバイアスされ、同じまたは相違するバイアス電圧によってバイアスされ、同じまたは相違する信号レベルの局部発振器 (LO) 信号によって駆動され得る。各ミキサ対は、イネーブルにされると、少なくとも1つのLNA出力信号のうちの1つをダウンコンバートする。各ミキサ対は、例えば複数のモードの中から選択されたモードに基づいて、選択的にイネーブルまたはディセーブルにされ得る。

20

【0004】

一デザインでは、複数のモードは、大きな妨害信号が検出される場合に選択され得る高線形性モード、および大きな妨害信号が検出されない場合に選択され得る低線形性モードを含んでいる。高線形性モードについては、第1および第2ミキサ対がイネーブルにされ得る。低線形性モードについては、第1ミキサ対がイネーブルにされ得、第2ミキサ対がディセーブルにされ得る。

30

【0005】

一デザインでは、LNAは入力段および出力段を含んでおり、シングルエンド型または差動型デザインによって実現され得る。入力段はLNA入力信号を受信および増幅し、被増幅 (増幅された) 信号を提供する。被増幅信号は電圧または電流のいずれかであり得る。出力段は被増幅信号をバッファし、また少なくとも1つのLNA出力信号を提供する。出力段は、並列接続された複数の負荷部を含んでいる。各負荷部は、例えば選択されたモードに基づいて選択的にイネーブルまたはディセーブルにされ得る。各負荷部は1組のN型金属酸化膜半導体 (NMOS) トランジスタに結合されている1組のP型金属酸化膜半導体 (PMOS) トランジスタを具備し、また (または) 抵抗を具備し得る。複数の負荷部は、同じまたは相違するサイズのトランジスタによって実現され、同じまたは相違する量の電流によってバイアスされ得る。

40

【0006】

一デザインでは、LNAは複数のLNA出力信号を提供し、各ミキサ対は、イネーブルにされていると相違するLNA出力信号をダウンコンバートする。一デザインでは、LNAは、(i) 第1ミキサ対のための第1LNA出力信号を提供する第1負荷部、および(ii) 第2ミキサ対のための第2LNA出力信号を提供する第2負荷部、を含んでいる。

50

高線形性モードについては、両方の負荷部および両方のミキサ対がイネーブルにされ得る。低線形性モードについては、第1負荷部および第1ミキサ対がイネーブルにされ得、第2負荷部および第2ミキサ対がディセーブルにされ得る。

**【0007】**

概説的には、LNAは任意の数の負荷部を含み得、直交ダウンコンバータは任意の数のミキサ対を含み得る。高線形性が望まれる場合、より多くの負荷部、より多くのミキサ対、および／またはより大きなトランジスタを有する負荷部ならびにミキサが選択され得る。ノイズ性能を改善することを目的として線形性が必要でない場合、より少ない負荷部、より少ないミキサ対、および／またはより小さなトランジスタを有する負荷部ならびにミキサが選択され得る。

10

**【0008】**

本開示の様々な側面および特徴は、以下に、より詳細に記述されている。

**【図面の簡単な説明】**

**【0009】**

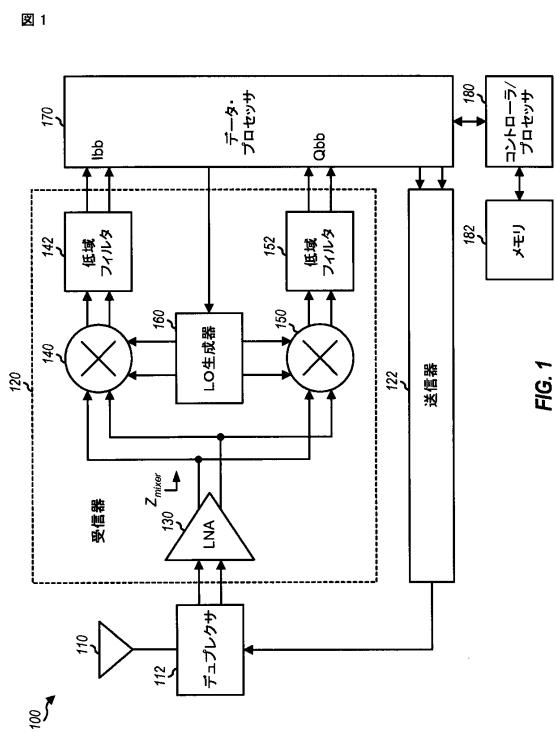

**【図1】**無線装置のブロック図を示している。

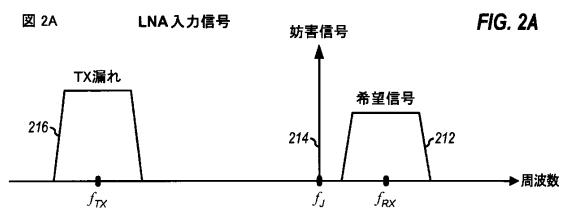

**【図2A】**LNA入力信号スペクトルを示している。

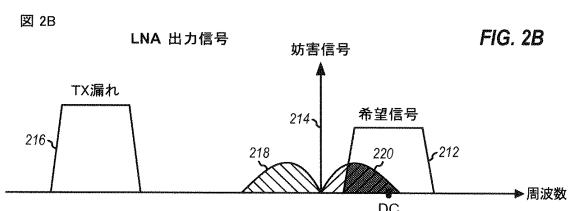

**【図2B】**LNA出力信号スペクトルを示している。

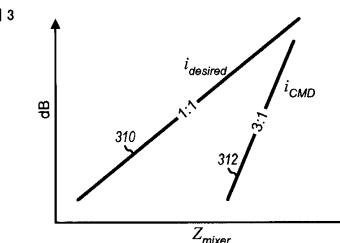

**【図3】**ミキサによってもたらされる負荷に対する希望信号電流およびLNAの歪み電流のプロットを示している。

**【図4】**LNAおよび複数のミキサ対のブロック図を示している。

20

**【図5】**LNAのデザインの概略図を示している。

**【図6】**LNAおよび複数のミキサ対の別のブロック図を示している。

**【図7】**LNAの別のデザインの概略図を示している。

**【図8A】**ミキサのデザインの概略図を示している。

**【図8B】**ミキサのデザインの概略図を示している。

**【図9】**受信器を動作させるための工程を示している。

**【詳細な説明】**

**【0010】**

本明細書において記述されている受信器は、符号分割多元接続(CDMA)システム、時分割多元接続(TDMA)システム、周波数分割多元接続(FDMA)システム、直交FDMA(OFDMA)システム、シングル・キャリアFDMA(SC-FDMA)システム、無線ローカル・エリア・ネットワーク(WLAN)、放送システム、衛星測位システムなどの様々な通信システムに対して使用され得る。簡潔化のために、以下において、受信器の一部の側面はCDMAシステムについて記述されている。

30

**【0011】**

図1は、無線装置100のデザインのブロック図を示している。無線装置100は、受信器120および送信器122を含んでいる。概して、無線装置100は、任意の数の通信システムおよび任意の数の周波数帯用の任意の数の送信器ならびに任意の数の受信器を含み得る。

**【0012】**

40

送信器または受信器はスーパー・ヘテロダイン・アーキテクチャまたは直接変換アーキテクチャによって実現され得る。スーパー・ヘテロダイン・アーキテクチャでは、信号は複数段においてRFとベースバンドとの間で、例えば受信器のための1段においてRFから中間周波数(IF)へ、次いで別の段においてIFからベースバンドへ周波数変換される。直接変換アーキテクチャ(これは、ゼロIFアーキテクチャとも称される)では、信号は1段においてRFとベースバンドの間で周波数変換される。スーパー・ヘテロダインおよび直接変換アーキテクチャは、相違する回路ブロックを使用し得、また／または相違する要件を有し得る。図1に示されているデザインでは、受信器120は直接変換アーキテクチャによって実現されている。

**【0013】**

50

受信経路上で、アンテナ 110 は、基地局、衛星、および / または他の送信器局からダウンリンク信号を受信し、またデュプレクサ 112 に RF 被受信（受信された）信号（受信信号）を提供する。図 1 に示されているデザインでは、デュプレクサ 112 は、シングルエンド型 RF 被受信信号を差動型に変換し、また LNA 130 に差動 LNA 入力信号を提供する。LNA 130 は、差動 LNA 入力信号を増幅し、差動 LNA 出力信号を I ダウンコンバータ 140 および Q ダウンコンバータ 150 に提供する。ダウンコンバータ 140 は、差動 LNA 出力信号を差動 I LO 生成器 160 からの LO 信号によってダウンコンバートし、差動 I 被ダウンコンバート（ダウンコンバートされた）信号を提供する。低域通過フィルタ 142 は、差動 I 被ダウンコンバート信号を濾波し、またデータ・プロセッサ 170 に差動 I ベースバンド信号（I b b）を提供する。同様に、ダウンコンバータ 150 は、差動 LNA 出力信号を LO 生成器 160 からの差動 Q LO 信号によってダウンコンバートし、差動 Q 被ダウンコンバート信号を提供する。低域通過フィルタ 152 は、差動 Q 被ダウンコンバート信号を濾波し、またデータ・プロセッサ 170 に差動 Q ベースバンド信号（Q b b）を提供する。

#### 【0014】

LO 生成器 160 は、ダウンコンバータ 140 用の I LO 信号およびダウンコンバータ 150 用の Q LO 信号を生成する。LO 生成器 160 は、1 または複数の電圧制御発振器（VCO）、位相ロック・ループ（PLL）、基準発振器、分周器、バッファなどを含み得る。

#### 【0015】

図 1 は例示的な受信器デザインを示している。概して、受信器中の信号の調整は 1 または複数のアンプ、フィルタ、ダウンコンバータなどによって実行され得る。これらの回路ブロックはシングルエンド型信号または差動信号に対して動作し得る。これらの回路ブロックは、図 1 に示されている構成とは異なって配置されていてもよい。さらに、図 1 において示されていない他の回路ブロックが、受信器中の信号を調整するために使用され得る。受信器の全体または一部は、1 または複数の RF 集積回路（RFIC）、アナログ IC、混合信号 IC 等上で実現され得る。例えば、LNA 130 およびダウンコンバータ 140 ならびに 150 は、RFIC 上で実現され得る。

#### 【0016】

送信経路上で、データ・プロセッサ 170 は、送信されるデータを処理し、送信器 122 にアナログ I 信号および Q 信号を提供する。送信器 122 は、アナログ I 信号および Q 信号を処理し（例えば、増幅し、濾波し、アップコンバートし）て RF 送信信号を生成する。RF 送信信号は、デュプレクサ 112 によってルーティングされ、アンテナ 110 によって送信される。

#### 【0017】

データ・プロセッサ 170 は、データ送受信および他の機能のための各種処理ユニットを含み得る。例えば、データ・プロセッサ 170 は、アナログ・デジタル変換器（ADC）、デジタル・アナログ変換器（DAC）、デジタル信号プロセッサ（DSP）、縮小命令セット型コンピュータ（RISC）プロセッサ、中央処理装置（CPU）などを含み得る。コントローラ/プロセッサ 180 は、無線装置 100 における動作を制御し得る。メモリ 182 は、無線装置 100 のためのプログラム・コードおよびデータを格納し得る。データ・プロセッサ 170、コントローラ/プロセッサ 180、および / またはメモリ 182 は、1 または複数の特定用途向け集積回路（ASIC）ならびに / あるいは他の IC 上で実現され得る。

#### 【0018】

図 2A は、LNA 130 に提供される LNA 入力信号のスペクトルを示している。図 2A に示されているように、LNA 入力信号は、受信周波数  $f_{RX}$  における希望信号 212、周波数  $f_J$  における妨害信号 214、および送信周波数  $f_{TX}$  における TX 漏れ信号 216 を含み得る。妨害信号は、希望信号に周波数において接近している、大きい振幅の不要信号である。妨害信号は、同じ領域内で動作する別の通信システムに由来し得る。希望

10

20

30

40

50

信号および妨害信号は、アンテナ 110 によって提供される R F 被受信信号に含まれており得る。T X 漏れ信号は、送信器 122 からデュプレクサ 112 を介して L N A 130 に結合または漏れています。T X 漏れの量は、デュプレクサ 112 の送信ポートと受信ポートとの間の分離の量に依存する。R F 送信信号は R F 被受信信号よりもはるかに大きいものであり得る。したがって、T X 漏れ信号は、デュプレクサ 112 の送信ポートと受信ポートとの間の良好な分離があったとしても希望信号よりもはるかに大きいものであり得る。

#### 【 0 0 1 9 】

図 2 B は、L N A 130 によって提供される L N A 出力信号のスペクトルを示している。L N A 130 の非線形性は、T X 漏れ信号 216 に対する変調を狭帯域妨害信号 214 に移す可能性がある。このことは、妨害信号のまわりの広げられたスペクトル 218 につながる。スペクトルが広くなることは相互変調または混変調と称される。図 2 B に示されているように、広げられたスペクトル 218 の一部 220 は希望信号帯域内にある。部分 220 (これは陰影によって示されている) は、無線装置の性能を悪化させる余計なノイズとして作用する。このノイズはまた、受信器感度を悪化させ、その結果、受信器によって確実に検出されることが可能な最小希望信号がより大きな振幅を有さなければならぬだろう。

#### 【 0 0 2 0 】

良好な受信器の性能は相互変調 ( I M ) 歪みを低く維持することによって得られ得る。線形性の高い受信器は、多くのオンチップ・インダクタを使用することによって低い I M 歪を達成することが可能である。しかしながら、オンチップ・インダクタは大きなシリコン領域を占領し、このことはダイのコストを上げる。したがって、オンチップ・インダクタの使用を最小化することが望ましい。L N A 130 は、負荷としてオンチップ・インダクタの代わりにトランジスタを使用することができる。しかしながら、負荷トランジスタは過度の I M 歪を生成し得、このことは、C D M A および他の高性能システムの厳格な線形性要件を満たすことを困難にし得る。

#### 【 0 0 2 1 】

一側面では、L N A 130 に提供されている外部負荷は、良好な性能を達成するために、動作条件に基づいて変えられ得る。L N A 130 は、内部負荷として P M O S トランジスタを使用し、また低電源電圧 ( 例えは 1 . 3 ボルト ) で動作し得る。P M O S トランジスタは、より小さなダイ領域ゆえにオンチップ・インダクタよりも好ましいものであり得、低い供給 ( supply ) ヘッドルームゆえに抵抗よりも好ましいものであり得る。P M O S トランジスタに起因する歪みは、厳格な線形性要件を満たすために外部負荷を変化させることによって対抗され得る。

#### 【 0 0 2 2 】

歪みは、L N A 130 の負荷とも L N A 130 の入力段とも関係し得る。L N A 負荷によって生成された歪みは例えは P M O S トランジスタに起因し得、L N A 130 からの出力電流は出力電圧の関数として以下のように表現され得る。

#### 【 数 1 】

$$i_{out} = g_1 \cdot V_{out} + g_2 \cdot V_{out}^2 + g_3 \cdot V_{out}^3 + \dots \quad \text{式(1)}$$

#### 【 0 0 2 3 】

ここで、

$V_{out}$  は L N A 130 によって提供される出力電圧であり、

$i_{out}$  は L N A 130 によって提供される出力電流であり、

$g_1$ 、 $g_2$ 、および  $g_3$  は L N A 130 の線形性を定義する係数である。

#### 【 0 0 2 4 】

等式 ( 1 ) は、 $g_1$ 、 $g_2$ 、および  $g_3$  とは異なる係数を使用して、L N A 130 についての入力電圧  $V_{in}$  の関数として書き直され得る。

10

20

30

40

50

## 【0025】

LNA出力電圧は次のように表現され得る。

## 【数2】

$$V_{out} = V_{desired} \cdot \cos(\omega_{desired}t) + V_{TX} \cdot (\cos(\omega_{TX1}t) + \cos(\omega_{TX2}t)) + V_J \cdot \cos(\omega_Jt) \quad 式(2)$$

## 【0026】

ここで、

$V_{desired}$  は周波数  $\omega_{desired}$  (ラジアン / 秒) での希望信号電圧であり、

$V_{TX}$  は周波数  $\omega_{TX1}$  および  $\omega_{TX2}$  での TX漏れ信号電圧であり、

$V_J$  は周波数  $\omega_J$  での妨害信号電圧である。

## 【0027】

$\omega_{TX1}$  および  $\omega_{TX2}$  での TX漏れ成分は被変調 (変調された) TX漏れを表わし得る。

## 【0028】

LNA出力電流は、周波数  $\omega_{TX1} - \omega_{TX2} + \omega_J$  において、希望電流および相互変調または混変調歪 (CMD) の電流を含んでいる。混変調歪 (CMD) が主要な興味対象 (main interest) である。なぜなら、被変調 TX漏れが考慮される場合、混変調歪が図 2B 中の広げられたスペクトル 218 を含んでいるからである。CMDについての電流 (これは、トリプル・ビート電流 (triple beat current) とも称される) は、次のように表現され得る。

## 【数3】

$$i_{CMD} = \frac{3}{2} g_3 \cdot V_{TX}^2 \cdot V_J = \frac{3}{2} g_3 \cdot (i_{TX} \cdot Z_{mixer})^2 \cdot (i_J \cdot Z_{mixer}) = \frac{3}{2} g_3 \cdot \alpha^2 \cdot i_J^3 \cdot Z_{mixer}^3 \quad 式(3)$$

## 【0029】

ここで、

$i_{TX}$  は TX漏れ信号電流であり、 $i_J$  は妨害信号電流であり、 $i_{CMD}$  は CMD電流であり、 $\alpha = i_{TX} / i_J$  は LNA 130 についての無線通信規格によって規定されている不变の比率であり、 $Z_{mixer}$  は LNA 130 の出力によって観察される外部負荷である。

## 【0030】

図 1 に示されているデザインでは、LNA 130 の外部負荷はダウンコンバータ 140 および 150 の入力インピーダンスと等しい。したがって、「外部負荷」および「ミキサ入力インピーダンス」という用語は、本明細書において可換的に使用されている。

## 【0031】

等式 (3) は、外部負荷が LNA 130 の内部負荷を支配するとしている。これは、力スケード構成の場合に多い。例えば、ミキサ入力インピーダンスは 100 オーム未満であり得、他方、LNA 内部負荷は 1 キロ・オーム以上であり得る。

## 【0032】

等式 (3) に示されているように、CMD電流の量は、妨害信号電流の量およびミキサ入力インピーダンス  $Z_{mixer}$  に依存する。さらに、CMD電流は  $Z_{mixer}$  の 3 乗に比例する。したがって、 $Z_{mixer}$  が因数 2 だけ減じられると、CMD電流は因数 8 だけ減じられる。したがって、CMD電流の量は、 $Z_{mixer}$  を変化させることによって制御され得る。

## 【0033】

図 3 は、ミキサ入力インピーダンス  $Z_{mixer}$  に対する希望信号電流  $i_{desired}$

10

20

30

40

50

<sub>d</sub> のプロット 310 および CMD 電流  $i_{CMD}$  のプロット 312 を示している。垂直軸は電流を対数目盛で示しており、水平軸は  $Z_{mixer}$  を均等目盛で示している。希望信号電流は 1 : 1 スロープを有しており、 $Z_{mixer}$  が因数 2 だけ減じられると 6 dB だけ減少する。CMD 電流は 3 : 1 スロープを有しており、 $Z_{mixer}$  が因数 2 だけ減じられると 18 dB だけ減少する。したがって、 $Z_{mixer}$  が減じられると、CMD 電流は希望信号電流よりはるかに速い速さで低下する。

#### 【0034】

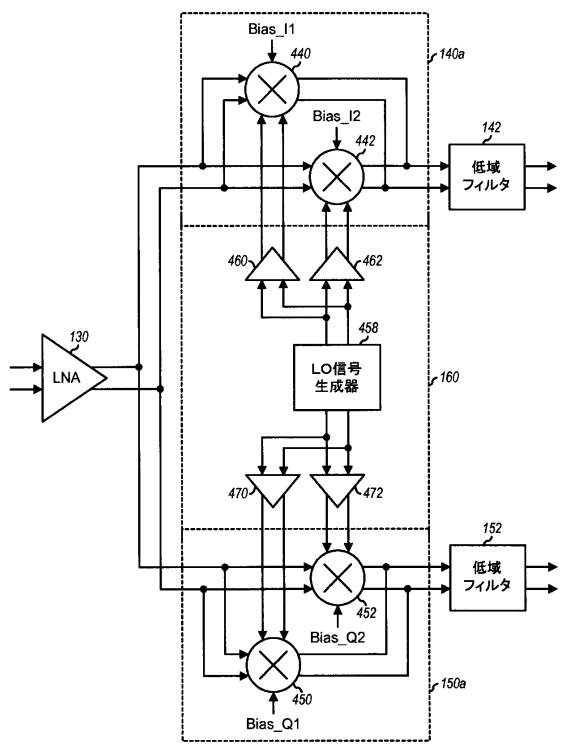

図 4 は、ダウンコンバータ 140a および 150a ならびに LO 生成器 160 のデザインのブロック図を示している。ダウンコンバータ 140a および 150a は、可変の入力インピーダンスを有し、それぞれ図 1 中のダウンコンバータ 140 および 150 の一デザインである。

#### 【0035】

図 4 に示されているデザインにおいて、ダウンコンバータ 140a は、第 2 I ミキサ 442 と並列結合（接続）されている第 1 I ミキサ 440 を含んでいる。ダウンコンバータ 150a は、第 2 Q ミキサ 452 と並列結合されている第 1 Q ミキサ 450 を含んでいる。LO 生成器 160 は、LO 信号生成器 458 および 4 つのバッファ 460、462、470、および 472 を含んでいる。生成器 458 は I LO 信号および Q LO 信号を生成する。バッファ 460 および 462 は、I LO 信号を受信およびバッファし、第 1 および第 2 I LO 信号をミキサ 440 および 442 にそれぞれ提供する。バッファ 470 および 472 は、Q LO 信号を受信およびバッファし、第 1 および第 2 Q LO 信号をミキサ 450 および 452 にそれぞれ提供する。

#### 【0036】

ミキサ 440 は、イネーブルにされていると、LNA 出力信号をバッファ 460 からの第 1 I LO 信号でダウンコンバートし、第 1 I 被ダウンコンバート信号を提供する。ミキサ 442 は、イネーブルにされていると、LNA 出力信号をバッファ 462 からの第 2 I LO 信号でダウンコンバートし、第 2 I 被ダウンコンバート信号を提供する。第 1 および第 2 I 被ダウンコンバート信号は合算され、フィルタ 142 に提供される。ミキサ 450 は、イネーブルにされていると、LNA 出力信号をバッファ 470 からの第 1 Q LO 信号でダウンコンバートし、第 1 Q 被ダウンコンバート信号を提供する。ミキサ 452 は、イネーブルにされていると、LNA 出力信号をバッファ 472 からの第 2 Q LO 信号でダウンコンバートし、第 2 Q 被ダウンコンバート信号を提供する。第 1 および第 2

Q 被ダウンコンバート信号は合算され、フィルタ 152 に提供される。ミキサ 440 および 442 は、それぞれ、それらのバイアス電流  $Bias\_I1$  および  $Bias\_I2$  を制御することによってイネーブルまたはディセーブルにされ得る。ミキサ 450 および 452 は、それぞれ、それらのバイアス電流  $Bias\_Q1$  および  $Bias\_Q2$  を制御することによってイネーブルまたはディセーブルにされ得る。

#### 【0037】

一デザインでは、ミキサ 440 および 442 は同じサイズのトランジスタによって実現される。別デザインでは、ミキサ 440 および 442 は相違するサイズのトランジスタによって実現される。例えば、ミキサ 440 はより小さなトランジスタによって実現され得、ミキサ 442 はより大きなトランジスタによって実現され得る。一デザインでは、ミキサ 440 および 442 は、イネーブルにされている際、同じ量の電流および / または同じバイアス電圧によってバイアスされる。別デザインでは、ミキサ 440 および 442 は、イネーブルにされている際、相違する量の電流および / または相違するバイアス電圧によってバイアスされる。例えば、ミキサ 440 は、イネーブルにされている際、より少ない電流またはより低いバイアス電圧によってバイアスされ得、ミキサ 442 は、イネーブルにされている際、より多い電流またはより高いバイアス電圧によってバイアスされ得る。一デザインでは、ミキサ 440 および 442 は同様の信号レベルの LO 信号によって駆動される。別デザインでは、ミキサ 440 および 442 は相違する信号レベルの LO 信号によって駆動される。例えば、ミキサ 440 はより小さな LO 信号によって駆動され得、ミ

10

20

30

40

50

キサ442はより大きなL0信号によって駆動され得る。同様に、ミキサ450および452は同じまたは相違するサイズのトランジスタによって実現され得、イネーブルにされている際に同じまたは相違する量の電流および同じまたは相違するバイアス電圧によってバイアスされ得、同様または相違する信号レベルのL0信号によって駆動され得る。L0バッファ460、462、470、および472は、それぞれ、ミキサ440、442、450、および452のトランジスタ・サイズに従ってスケールされ得る。

#### 【0038】

ミキサ入力インピーダンス $Z_{mixer}$ は複数のやり方で変えられ得る。一デザインでは、 $Z_{mixer}$ は、I経路については、ミキサ440、ミキサ442、または両方のミキサ440および442を選択することによって変えられ得る。より低い $Z_{mixer}$ は、より大きなトランジスタを有する1または複数のミキサを選択すること等によってより多くのミキサをイネーブルにすることによって得られ得る。別デザインでは、 $Z_{mixer}$ は、選択されたミキサのバイアス条件を調整することによって変えられ得る。より低い $Z_{mixer}$ は、より高いバイアス電圧によって得られ得る。さらなる別デザインでは、 $Z_{mixer}$ はL0信号の信号レベルを調整することによって変えられ得る。これは、バッファ460および462のための $V_{DD}$ 電源電圧を変えること等によってL0バッファ460および462を変化させることによって(例えばバッファ460および462中のより多くの段をイネーブルにすることによって)達成され得る。より低い $Z_{mixer}$ は、より大きなL0信号レベルによって得られ得る。

#### 【0039】

一デザインでは、高線形性モードと低線形性モードがサポートされ得る。高線形性モードは大きな妨害信号および/または高いTX漏れが検出される場合に選択され得る。ダウンコンバータ140および150は、高線形性モードにおいてLNA130にとっての低い $Z_{mixer}$ を得るために、表1に示されているように動作させられ得る。このことは、PMOSトランジスタ負荷の歪みが減じられるように、LNA出力での信号スイングを減じ得る。低線形性モードは大きな妨害信号および/または高いTX漏れが検出されない場合に選択され得る。ダウンコンバータ140および150は、低線形性モードにおいてLNA130にとってのより高い $Z_{mixer}$ を得るために、表1に示されているように動作させられ得る。このことは、LNA130によって示される寄生容量を減じ得る。このことは、受信器の全体的なノイズ指数を改善し得る。

#### 【表1】

表1

| モード     | 説明                                                                                                                                                                     |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 高線形性モード | <ul style="list-style-type: none"> <li>両方のミキサまたはより大きなトランジスタを有するミキサをイネーブルにする、</li> <li>イネーブルにされているミキサに対してより大きなバイアス電圧を使用する、および/または</li> <li>より大きなL0信号レベルを使用する</li> </ul> |

| 低線形性モード | <ul style="list-style-type: none"> <li>より小さなトランジスタを有するミキサをイネーブルにする、</li> <li>イネーブルにされているミキサに対してより小さなバイアス電圧を使用する、および/または</li> <li>より小さなL0信号レベルを使用する</li> </ul>          |

#### 【0040】

別の側面では、LNA130の内部負荷は、良好な性能を達成するために、動作条件に

10

20

30

40

50

よって変えられ得る。LNA130の内部負荷は複数の部分に分割され得る。これらの部分は、大きな妨害信号および/または高いTX漏れが検出されているかに基づいて、選択的にイネーブルにされ得る。

#### 【0041】

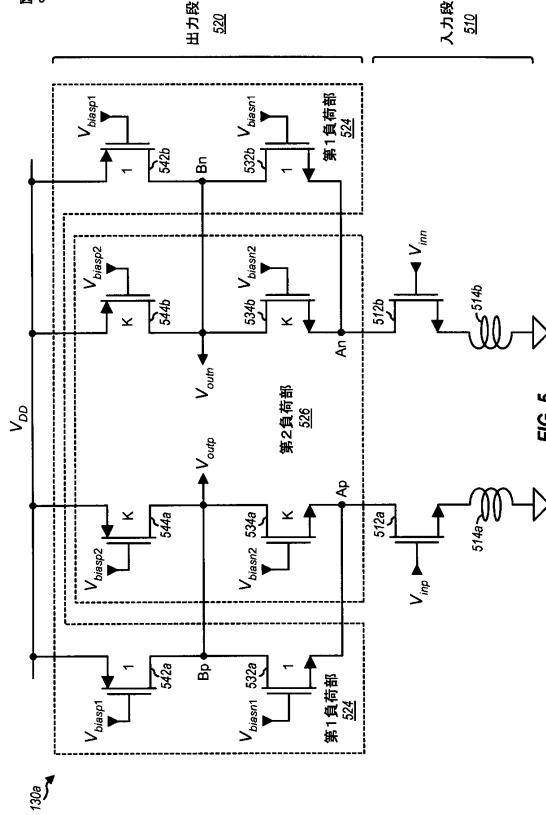

図5は、LNA130aの概略図を示している。これは、図1および図4中のLNA130の一デザインである。LNA130aは、信号増幅をもたらす入力段510と、入力段510のための能動負荷をもたらす出力段520と、を含んでいる。入力段510において、NMOSトランジスタ512aは、ソースをインダクタ514aの一端に結合されており、ゲートがLNA入力信号 $V_{in_p}$ を受信し、ドレインをノードApに結合されている。NMOSトランジスタ512bは、ソースをインダクタ514bの一端に結合されており、ゲートが相補LNA入力信号 $V_{in_n}$ を受信し、ドレインをノードAnに結合されている。インダクタ514aおよび514bの他端は回路グランドに結合されている。NMOSトランジスタ512aおよび512bは差動LNA入力信号 $V_{in_p}$ および $V_{in_n}$ に対する信号増幅をもたらす。NMOSトランジスタ512aおよび512bのバイアス電圧、バイアス電流、およびサイズは、入力段510について所望の利得および線形性を得るように選択され得る。インダクタ514aおよび514bは、NMOSトランジスタ512aおよび512bのためのソース・デジネレーションをもたらし、またNMOSトランジスタ512aおよび512bのゲートを見た(looking into)際のインピーダンス整合をもたらし得る。

#### 【0042】

出力段520は第1負荷部524および第2負荷部526を含んでいる。出力段520において、NMOSトランジスタ532aおよび534aは、並列結合されており、ソースをノードApに結合されており、ゲートが $V_{bias_{n1}}$ および $V_{bias_{n2}}$ バイアス電圧をそれぞれ受け取り、およびドレインをノードBpに結合されている。PMOSトランジスタ542aおよび544aも、並列結合されており、ソースを $V_{DD}$ 電源電圧に結合されており、ゲートが $V_{bias_{p1}}$ および $V_{bias_{p2}}$ バイアス電圧をそれぞれ受け取り、ドレインをノードBpに結合されている。NMOSトランジスタ532bおよび534bは並列結合されており、ソースをノードAnに結合されており、ゲートが $V_{bias_{n1}}$ および $V_{bias_{n2}}$ バイアス電圧をそれぞれ受け取り、ドレインをノードBnに結合されている。PMOSトランジスタ542bおよび544bも、並列結合されており、ソースを $V_{DD}$ 電源電圧に結合されており、ゲートが $V_{bias_{p1}}$ および $V_{bias_{p2}}$ バイアス電圧をそれぞれ受け取り、ドレインをノードBnに結合されている。NMOSトランジスタ532a、532b、534a、および534bは、NMOSトランジスタ512aおよび512bのための負荷分離をもたらす。PMOSトランジスタ542a、542b、544a、および544bは、入力段510のための能動負荷を提供する。 $V_{bias_{n1}}$ および $V_{bias_{n2}}$ バイアス電圧は、NMOSトランジスタ532a、534a、532b、および534bを所望の動作点でバイアスするように選択され得る。 $V_{bias_{p1}}$ および $V_{bias_{p2}}$ バイアス電圧は、PMOSトランジスタ542a、544a、542b、および544bを所望の動作点でバイアスするように選択され得る。

#### 【0043】

LNA130aは1つの差動LNA出力信号 $V_{out_p}$ および $V_{out_n}$ を生成する。MOSトランジスタ532a、534a、542a、および544aのドレインが、 $V_{out_p}$ 信号を提供する。MOSトランジスタ532b、534b、542b、および544bのドレインが、 $V_{out_n}$ 信号を提供する。

#### 【0044】

図5に示されているデザインでは、MOSトランジスタ532a、532b、542a、および542bは1のサイズを有し、MOSトランジスタ534a、534b、544a、および544bはKのサイズを有する。図5に示されていない別のデザインでは、MOSトランジスタは全て同じサイズを有する。

10

20

30

40

50

## 【0045】

出力段520の第1負荷部524は、MOSトランジスタ532a、532b、542a、および542bを含んでいる。出力段520の第2負荷部526はMOSトランジスタ534a、534b、544a、および544bを含んでいる。第1負荷部524は、MOSトランジスタ532a、532b、542a、および542bのための適切な $V_{b_{i\text{asn}1}}$ および $V_{b_{i\text{asp}1}}$ バイアス電圧を提供することによってイネーブルにされ得る。第2負荷部526は、MOSトランジスタ534a、534b、544a、および544bのための適切な $V_{b_{i\text{asn}2}}$ および $V_{b_{i\text{asp}2}}$ バイアス電圧を提供することによってイネーブルにされ得る。

## 【0046】

10

高線形性モードでは、より大きなMOSトランジスタを有する第2負荷部526が、または第1負荷部524および第2負荷部526の両方が、低い歪みを達成するためにイネーブルにされ得る。低線形性モードでは、より小さなMOSトランジスタを有する第1負荷部524のみが、低ノイズ指数を達成するためにイネーブルにされ得る。

## 【0047】

図5は、LNA130の例示的デザインを示している。LNAは他のデザインによって実現されてもよい。

## 【0048】

20

さらに別の側面では、LNA130の内部および外部負荷の両方が、良好な性能を達成するために、動作条件に基づいて変えられ得る。これは、内部負荷を複数の部分に分割することによって、および外部負荷を複数の部分に分割することによっても達成され得る。内部および外部負荷の複数の部分は、大きい妨害信号および/または高いTX漏れが検出されるかに基づいて選択的にイネーブルにされ得る。

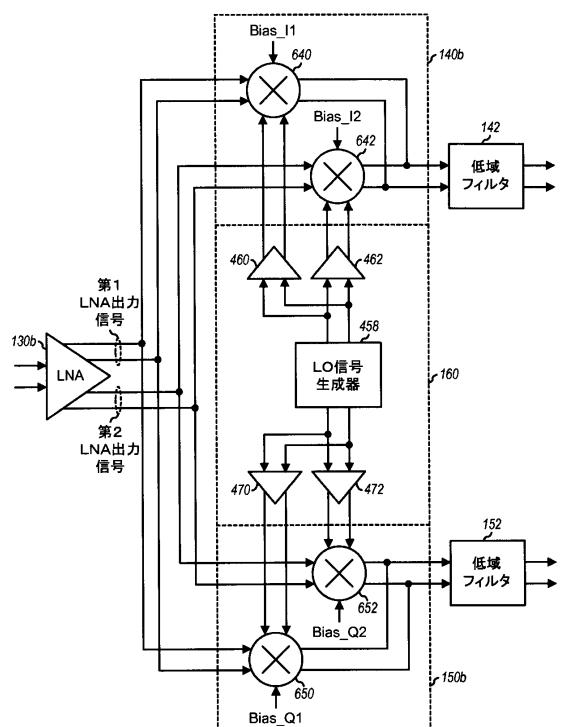

## 【0049】

図6は、LNA130b、および可変入力インピーダンスを有するダウンコンバータ140bならびに150bのデザインのブロック図を示している。LNA130bは図1中のLNA130の別のデザインである。ダウンコンバータ140bおよび150bは、それぞれ、図1中のダウンコンバータ140および150の別のデザインである。

## 【0050】

30

図6に示されているデザインにおいて、LNA130bはLNA入力信号を受信し、第1および第2LNA出力信号を提供する。ダウンコンバータ140bは、第2IMIKSA642と並列結合されている第1IMIKSA640を含んでいる。ダウンコンバータ150bは、第2QMIKSA652と並列接続されている第1QMIKSA650を含んでいる。MIKSA640は、イネーブルにされていると、第1LNA出力信号をバッファ460からの第1ILO信号でダウンコンバートし、第1I被ダウンコンバート信号を提供する。MIKSA642は、イネーブルにされていると、第2LNA出力信号をバッファ462からの第2ILO信号でダウンコンバートし、第2I被ダウンコンバート信号を提供する。第1および第2I被ダウンコンバート信号は合算され、フィルタ142に提供される。MIKSA650は、イネーブルにされていると、第1LNA出力信号をバッファ470からの第1QLO信号でダウンコンバートし、第1Q被ダウンコンバート信号を提供する。MIKSA652は、イネーブルにされていると、第2LNA出力信号をバッファ472からの第2QLO信号でダウンコンバートし、第2Q被ダウンコンバート信号を提供する。第1および第2Q被ダウンコンバート信号は合算され、フィルタ152に提供される。

40

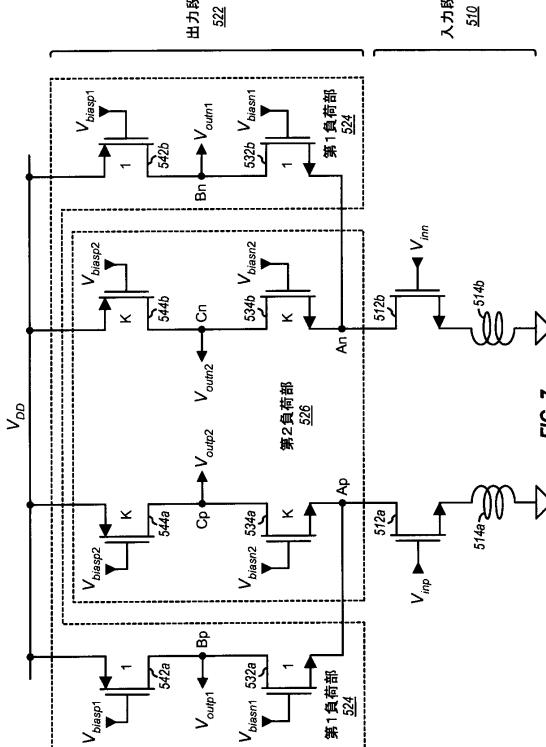

## 【0051】

図7は、図6中のLNA130bのデザインの概略図を示している。LNA130bは、図5中のLNA130aに回路部品を全て含んでおり、以下が異なる。出力段522は第1負荷部524および第2負荷部526を含んでいる。第1負荷部524において、MOSトランジスタ532aおよび542aのドレインは、ノードBpに結合されており、 $V_{outp1}$ 信号を提供する。MOSトランジスタ532bおよび542bのドレインは、ノードBnに結合されており、 $V_{outn1}$ 信号を提供する。第2負荷部526において

50

て、MOSトランジスタ534aおよび544aのドレインは、ノードCpに結合されており、 $V_{outp2}$ 信号を提供する。MOSトランジスタ534bおよび544bのドレインは、ノードCnに結合されており、 $V_{outn2}$ 信号を提供する。第1LNA出力信号は $V_{outp1}$ と $V_{outn1}$ とからなる。第2LNA出力信号は $V_{outp2}$ と $V_{outn2}$ とからなる。

#### 【0052】

図6および図7に示されているデザインでは、出力段中の負荷部は各々1つのLNA出力信号を生成し、1つのLNA出力信号は1つのミキサ対を駆動する。具体的には、第1負荷部524からの第1LNA出力信号 $V_{outp1}$ および $V_{outn1}$ は第1ミキサ対640および650を駆動する。第2負荷部526からの第2LNA出力信号 $V_{outp2}$ および $V_{outn2}$ は第2ミキサ対642および652を駆動する。

10

#### 【0053】

一デザインでは、LNA130bの第1および第2負荷部および第1および第2ミキサ対は、高線形性モードにおいてイネーブルにされる。別デザインでは、高線形性モードにおいて、より大きなMOSトランジスタを有するLNA130bの第2負荷部、およびより大きなMOSトランジスタを有する第2ミキサ対642ならびに652のみがイネーブルにされる。どちらのデザインについても、より低い負荷インピーダンスがLNA130bのために提供され得る。このことは、LNA出力での信号スイングを減じ、また、PMOSトランジスタの歪みを減じ得る。

#### 【0054】

20

一デザインでは、低線形性モードにおいて、LNA130bのより小さなMOSトランジスタを有する第1負荷部、およびより小さなMOSトランジスタを有する第1ミキサ対640および650のみがイネーブルにされる。イネーブルにされているミキサは、LNA130bによって与えられる、より高い入力インピーダンスおよびより少ない寄生容量を観察し、このことは、全体的なノイズ指数を改善し得る。さらに、LNA130bの内部負荷の一部がディセーブルにされているので、LNAによって寄与されるノイズが減じられる。

#### 【0055】

コンピュータ・シミュレーションは、同じLNA利得を有する出力段の一部についてPMOSトランジスタをディセーブルにすることによって、ノイズ指数における改善を示す。出力段の一部をディセーブルにすることは、低線形性モードにおいて実現可能であり得る。なぜなら、より低いバイアス電流が使用されており、イネーブルにされているPMOSトランジスタが、低い供給電圧の場合でさえ適切な飽和電圧 $V_{dsat}$ で動作可能だからである。

30

#### 【0056】

低線形性モードでは、LNA130bの寄生容量はより小さい。なぜなら、出力段の1つの負荷部のみがイネーブルにされているからである。相応して、LNA130bとミキサ640および650との間の交流結合キャパシタがスケールされ得る。また、1つのミキサ対640および650のみがイネーブルにされているので、ミキサ入力での全体的な入力容量 $C_{par}$ が減じられ得る。このより低いミキサ入力容量は全体的な受信器ノイズ指数を改善し得る。

40

#### 【0057】

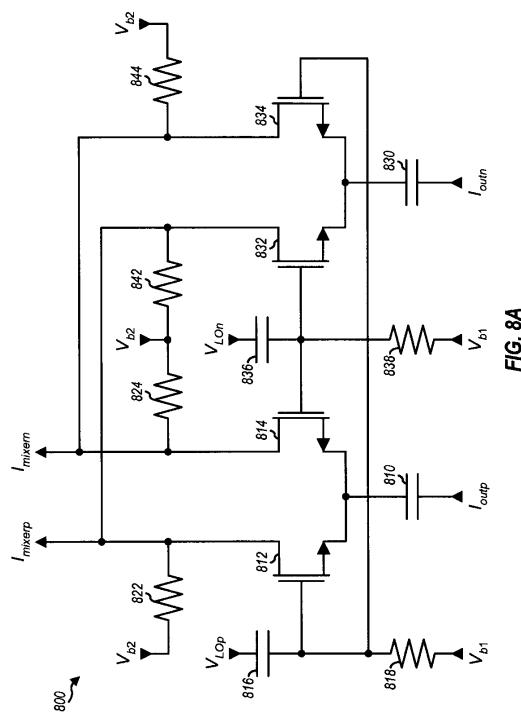

図8Aは、ミキサ800のデザインの概略図を示している。これは、図4中の各ミキサ440、442、450、および452、ならびに図6中の各ミキサ640、642、650、および652のために使用され得る。

#### 【0058】

ミキサ800において、NMOSトランジスタ812および814は、第1差動対を形成し、ソース同士を結合されており、ゲートがキャパシタ816および836を介してLO信号 $V_{Lop}$ および $V_{Lon}$ をそれぞれ受け取り、ドレインが差動ミキサ出力信号 $I_{mixer_p}$ および $I_{mixer_n}$ を提供する。NMOSトランジスタ832および834

50

は、第2差動対を形成し、ソース同士を結合されており、ゲートがキャパシタ836および816を介してLO信号 $V_{L_{0n}}$ および $V_{L_{0p}}$ をそれぞれ受け取り、ドレインが $I_{mixer_p}$ および $I_{mixer_n}$ 信号をそれぞれ提供する。キャパシタ810は、LNA130から $I_{out_p}$ 信号を受け取る一端、およびNMOSトランジスタ812および814のソースに結合されている他端を有する。キャパシタ830は、LNA130から $I_{out_n}$ 信号を受け取る一端、およびNMOSトランジスタ832および834のソースに結合されている他端を有する。 $I_{out_p}$ および $I_{out_n}$ 信号は、図4中の $V_{out_p}$ および $V_{out_n}$ 信号、図6中の $V_{out_{p1}}$ および $V_{out_{n1}}$ 信号、または図6中の $V_{out_{p2}}$ と $V_{out_{n2}}$ 信号に相当し得る。

【0059】

10

キャパシタ816は、 $V_{L_{0p}}$ LO信号を受け取る一端、およびNMOSトランジスタ812および834のゲートに結合されている他端を有する。キャパシタ836は、 $V_{L_{0n}}$ LO信号を受け取る一端、およびNMOSトランジスタ814および832のゲートに結合されている他端を有する。 $V_{L_{0p}}$ および $V_{L_{0n}}$ LO信号は図4中のバッファ460、462、470、または472、あるいは図6中のバッファ660、662、670、または672からの差動LO信号に相当し得る。

【0060】

20

抵抗818および838は、 $V_{b_1}$ バイアス電圧に結合されている一端、およびNMOSトランジスタ812および814のゲートにそれぞれ結合されている他端を有する。抵抗822および824は、 $V_{b_2}$ バイアス電圧に結合されている一端、およびNMOSトランジスタ812および814のドレインにそれぞれ結合されている他端を有する。抵抗842および844は、 $V_{b_2}$ バイアス電圧に結合されている一端、およびNMOSトランジスタ832および834のドレインにそれぞれ結合されている他端を有する。

【0061】

30

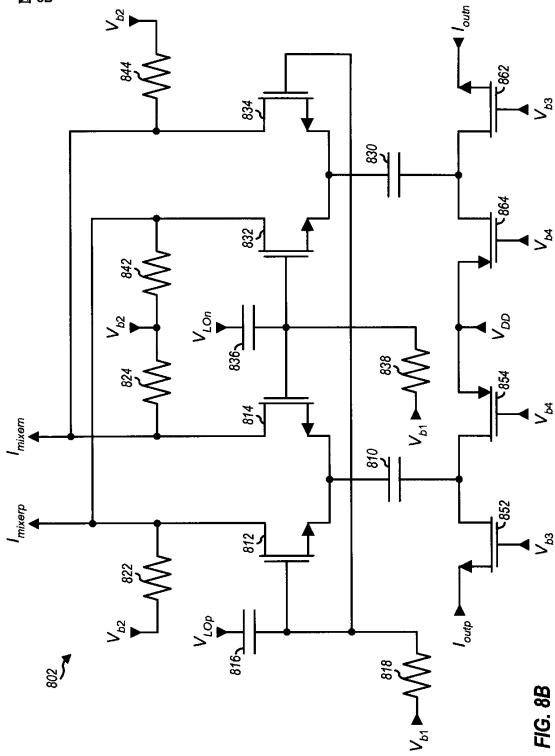

図8Bは、ミキサ802のデザインの概略図を示している。これも、図4中の各ミキサ440、442、450、および452、ならびに図6中の各ミキサ640、642、650、および652のために使用され得る。ミキサ802は、図8A中のミキサ800中の回路素子を全て含んでいる。ミキサ802は、さらに $I_{out_p}$ および $I_{out_n}$ 信号の各々のための入力電流バッファを含んでいる。 $I_{out_p}$ 信号のための入力電流バッファは、PMOSトランジスタ854から構成されているPMOS負荷と直列結合されているNMOSトランジスタ852から構成されている入力段を含んでいる。 $I_{out_n}$ 信号のための入力電流バッファは、PMOSトランジスタ864から構成されているPMOS負荷と直列結合されているNMOSトランジスタ862から構成されている入力段を含んでいる。入力電流バッファは、PMOS入力段およびNMOS負荷によって実現されてもよい。 $V_{b_3}$ バイアス電圧は、NMOSトランジスタ852および862のバイアス電流および入力インピーダンスを調整するために使用され得る。 $V_{b_4}$ バイアス電圧は、PMOSトランジスタ854および864のためのバイアス電圧を調整するために使用され得る。

【0062】

40

図8Aおよび図8Bは、ミキサ800および802の2つの例示的なデザインをそれぞれ示している。ミキサは他のデザインによって実現されてもよい。

【0063】

図1、図4、および図6に示されているように、低域フィルタ142および152は、それぞれダウンコンバータ140および150からのIおよびQ被ダウンコンバート信号を濾波し得る。一デザインでは、各低域フィルタは、送信低域フィルタを含んでおり、ベースバンド・フィルタが続く。送信低域フィルタは希望信号を通過させたりTX漏れ信号を減じたりし得る。送信低域フィルタの帯域幅は、通過帯域応答に影響することを避けるために希望信号帯域幅よりはるかに広いものであります。ベースバンド・フィルタは希望信号の帯域幅に一致し得る。

【0064】

50

上記のデザインにおいては、LNAの内部負荷は2つの負荷部に分割され、2つのI-Qミキサ対が直交ダウンコンバータのために使用されている。概括的には、LNAの内部負荷は任意の数の負荷部に分割され得る。これらの複数の負荷部は同じまたは相違するトランジスタ・サイズによって実現され、同じまたは相違する量の電流によってバイアスされ、同じまたは相違するバイアス電圧によってバイアスされ得る。直交ダウンコンバータも、任意の数のI-Qミキサ対によって実現され得る。これらの複数のI-Qミキサ対は同じまたは相違するトランジスタ・サイズによって実現され、同じまたは相違する量の電流によってバイアスされ、同じまたは相違するバイアス電圧によってバイアスされ、同じまたは相違する信号レベルのLO信号によって駆動され得る。

## 【0065】

10

概括的には、どのような数のモードがサポートされてもよい。各モードはある動作条件を目的として選択され得る。動作条件は、妨害信号強度、TX漏れ信号強度、および/または他のパラメータによって定量化され得る。各モードは、1または複数の負荷部および1または複数のI-Qミキサ対にも関連付けられ得る。適切なモードは、検出された動作条件に基づいて選択され得る。選択されたモードについての1または複数の負荷部および1または複数のI-Qミキサ対は、良好な性能を達成するようにイネーブルにされるとともに使用され得る。したがって、LNA負荷は、動作条件に従って（例えば妨害信号強度、TX漏れ信号強度などに従って）切り替えられ得る。

## 【0066】

20

妨害信号は様々な方法で検出され得る。一デザインでは、被ダウンコンバート信号の電力は、ベースバンド・フィルタの前で、またベースバンド・フィルタの後で測定され得る。妨害信号の存在および強度は、ベースバンド・フィルタの後で測定された電力に対するベースバンド・フィルタの前で測定された電力の比率に基づいて割り出され得る。妨害信号は、ベースバンド・フィルタの前で被ダウンコンバート信号に対して高速フーリエ変換（FFT）を実行するとともにFFTからのスペクトル反応を検査して妨害信号の存在および強度を割り出すことによって検出され得る。妨害信号は他の方法で検出されてもよい。

## 【0067】

30

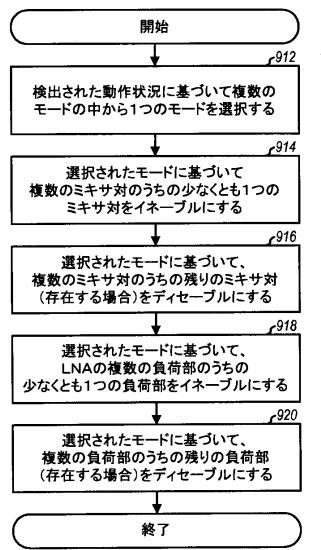

図9は、受信器を動作させるための工程900のデザインを示している。検出された動作条件に基づいて、複数のモードの中から1つのモードが選択され得る（ブロック912）。一デザインでは、大きな妨害信号が検出される場合、高線形性モードが選択され得、また、大きな妨害信号が検出されない場合、低線形性モードが選択され得る。他のモードもサポートされ得る。妨害信号、TX漏れ信号、および/または他のパラメータに基づいて、適切なモードが選択され得る。

## 【0068】

選択されたモードに基づいて、複数のミキサ対のうちの少なくとも1つのミキサ対がイネーブルにされ得る（ブロック914）。複数のミキサ対のうちのミキサ対（存在する場合）が、選択されたモードに基づいてディセーブルにされ得る（ブロック916）。LNAの複数の負荷部のうちの少なくとも1つの負荷部が、選択されたモードに基づいてイネーブルにされ得る（ブロック918）。複数の負荷部のうちの残りのミキサ対（存在する場合）が、選択されたモードに基づいてディセーブルにされ得る（ブロック920）。一デザインでは、複数のミキサ対は第1および第2ミキサ対を含み得、複数の負荷部は第1および第2負荷部を含み得る。高線形性モードが選択されている場合、両方のミキサ対および両方の負荷部がイネーブルにされ得る。低線形性モードが選択されている場合、第1ミキサ対および第1負荷部がイネーブルにされ得、第2ミキサ対および第2負荷部がディセーブルにされ得る。概括的には、任意の数のミキサ対および任意の数の負荷部が利用可能であり得、任意の数のモードもサポートされ得る。各モードは、そのモードについてイネーブルにされるべき少なくとも1つのミキサ対および少なくとも1つの負荷部に関連付けられ得る。

## 【0069】

50

本明細書において記述されている LNA およびミキサは、いくつかの利点をもたらし得る。第 1 に、高線形性が、オンチップ・インダクタを LNA 負荷として使用することなく達成され得る。このことは、著しいコスト削減を、特に複数のシステムおよび / または複数の周波数帯をサポートする無線装置に対して、もたらし得る。第 2 に、本技術は、LNA とミキサとの間の表面弾性波 (SAW) フィルタの除去を可能にし得る。このこと、コスト削減および他の利点を提供し得る。SAW フィルタは、TX 漏れ信号を減じるために、CDMA 用の無線装置中で LNA とミキサとの間で一般に使用されている。本明細書において記述されている技術を有する改善された線形性は、図 1、図 4、および図 6 に示されているように、LNA がミキサに直接結合されることを可能にし得る。第 3 に、本技術は、LNA 負荷用のオンチップ・インダクタの除去に起因して LO 再放射を減じ得る。

10

#### 【0070】

本明細書において記述されている LNA およびミキサは、IC、アナログ IC、RF IC、混合信号 IC、ASIC、プリント回路基板 (PCB)、エレクトロニクス装置等上で実現され得る。LNA およびミキサは、相補型金属酸化膜半導体 (CMOS)、NMOS、PMOS、バイポーラ接合トランジスタ (BJT)、バイポーラ CMOS (BiCMOS)、シリコン・ゲルマニウム (SiGe)、砒化ガリウム (GaAs) のような様々な IC プロセス技術によって製造されてもよい。

#### 【0071】

本明細書において記述されている LNA およびミキサを実現する装置はスタンド・アロン型装置であってもよいし大型装置の一部であってもよい。装置は (i) スタンド・アロン型 IC、(ii) データおよび / または命令を格納するためのメモリ IC を含み得る 1 または複数の IC の組、(iii) RF 受信器 (RFR) または RF 送信器 / 受信器 (RTT) のような RF IC、(iv) 移動局モデル (MSM) のような ASIC、(v) 他の装置内に埋め込まれ得るモジュール、(vi) 受信器、携帯電話、無線装置、ハンドセット、あるいはモバイル・ユニット、(vii) その他、であり得る。

20

#### 【0072】

1 つまたは複数の例示的デザインにおいて、記述されている機能は、ハードウェア、ソフトウェア、ファームウェア、またはそれらのあらゆる組合せにおいて実現され得る。ソフトウェアにおいて実現される場合、関数は 1 つまたは複数の指示またはコードとして、コンピュータ可読媒体上で格納または送信され得る。コンピュータ可読媒体は、コンピュータ記憶装置媒体、およびコンピュータ・プログラムのある位置から別の位置への移動を容易にするあらゆる媒体を含む通信媒体、の両方を含んでいる。記憶媒体は、コンピュータによってアクセスされることが可能なあらゆる利用可能な物理的媒体であり得る。限定ではなく例として、そのようなコンピュータ可読媒体は、RAM、ROM、EEPROM、CD-ROM または他の光学ディスク記憶装置、磁気ディスク記憶装置または他の磁気記憶装置、または命令またはデータ構造の形態の所望のプログラム・コードを運ぶか格納するために使用されることが可能で且つコンピュータによってアクセスされることが可能な他のあらゆる媒体を具備し得る。また、あらゆる接続も当然、コンピュータ可読媒体と称される。例えば、ソフトウェアが、同軸ケーブル、光ファイバーケーブル、撲線対、デイジタル加入者線 (DSL)、または赤外線、無線およびマイクロ波のような無線技術を使用して、ウェブサイト、サーバ、または他の遠隔ソースから送信される場合、この同軸ケーブル、光ファイバーケーブル、撲線対、DSL、または赤外線、無線およびマイクロ波のような無線技術は、媒体の定義に含まれている。本明細書において使用されているディスク (disk) とディスク (disc) は、コンパクト・ディスク (CD)、レーザーディスク (登録商標)、光ディスク、デジタル多用途ディスク (DVD)、フロッピー (登録商標)・ディスクおよびブルーレイ・ディスクを含んでいる。ここで、ディスク (disk) は通常磁気的にデータを再生し、他方、ディスク (disc) はレーザーでデータを光学的に再生する。上記のものの組合せもコンピュータ可読媒体の範囲内に含まれるべきである。

30

#### 【0073】

40

50

本開示のここまで記述は、あらゆる当業者が本開示を実行または使用することを可能にするために提供されている。本開示に対する様々な修正は当業者にとって容易に明らかになり、また、本明細書において定義されている包括的な原理は、本開示の範囲から逸脱することなく他の変形体に適用され得る。したがって、本開示は、本明細書において記述されている例およびデザインに制限されることを意図されておらず、本明細書において開示されている原理および新規な特徴と一貫している最も広い範囲と一致するべきである。

以下に、本願出願時の特許請求の範囲に記載された発明を付記する。

[ 1 ] 低ノイズ・アンプ ( L N A ) 入力信号を受信し、少なくとも 1 つの L N A 出力信号を提供するように構成されている低ノイズ・アンプ ( L N A ) と、

前記 L N A に結合されている複数のミキサ対であって、各ミキサ対はイネーブルにされると少なくとも 1 つの L N A 出力信号のうちの 1 つをダウンコンバートするように構成されており、各ミキサ対は選択的にイネーブルまたはディセーブルにされる、複数のミキサ対と、

10

を具備する装置。

[ 2 ] 前記複数のミキサ対が、相違するサイズのトランジスタを用いて実現されている第 1 および第 2 ミキサ対を具備する、

[ 1 ] の装置。

[ 3 ] 前記複数のミキサ対が、相違する量の電流または相違するバイアス電圧によってバイアスされる第 1 および第 2 ミキサ対を具備する、

[ 1 ] の装置。

[ 4 ] 前記複数のミキサ対が、相違する信号レベルの局部発振器 ( L O ) 信号によって駆動される第 1 および第 2 ミキサ対を具備する、

[ 1 ] の装置。

[ 5 ] 前記複数のミキサ対が、相互に結合されかつ被ダウンコンバート信号を提供する出力を有する、

[ 1 ] の装置。

[ 6 ] 各ミキサ対が複数のモードの中から選択されたモードに基づいてイネーブルまたはディセーブルにされ、

各モードは、少なくとも 1 つのミキサ対の相違する組と関連付けられており、

前記選択されたモードと関連付けられている前記少なくとも 1 つのミキサ対はイネーブルにされ、存在する場合は残りのミキサ対は全てディセーブルにされる、

30

[ 1 ] の装置。

[ 7 ] 前記複数のミキサ対が第 1 および第 2 ミキサ対を具備し、

高線形性モードについては前記第 1 および第 2 ミキサ対がイネーブルにされ、

低線形性モードについては前記第 1 ミキサ対がイネーブルにされるとともに前記第 2 ミキサ対がディセーブルにされる、

[ 1 ] の装置。

[ 8 ] 大きな妨害信号が検出される場合に高線形性モードが選択され、

大きな妨害信号が検出されない場合に低線形性モードが選択される、

[ 7 ] の装置。

[ 9 ] 前記 L N A が 1 つの L N A 出力信号を提供するように構成されており、

各ミキサ対が、イネーブルにされていると前記 L N A 出力信号をダウンコンバートするように、構成されている、

[ 1 ] の装置。

[ 10 ] 前記 L N A が、複数の L N A 出力信号を提供するように構成されており、

1 つの L N A 出力信号が各ミキサ対用であり、

各ミキサ対が、イネーブルにされていると、それぞれの L N A 出力信号をダウンコンバートするように構成されている、

[ 1 ] の装置。

[ 11 ] 前記複数のミキサ対が第 1 および第 2 ミキサ対を具備し、

10

20

30

40

50

前記 LNA が第 1 および第 2 LNA 出力信号を提供するように構成されており、

前記第 1 ミキサ対が、イネーブルにされていると前記第 1 LNA 出力信号をダウンコンバートするように構成されており、

前記第 2 ミキサ対が、イネーブルにされていると前記第 2 LNA 出力信号をダウンコンバートするように構成されている、

[ 1 ] の装置。

[ 12 ] 入力段および出力段を具備する低ノイズ・アンプ (LNA) であって、前記入力段は LNA 入力信号を受信するとともに被増幅信号を提供し、前記出力段は前記被増幅信号をバッファするとともに少なくとも 1 つの LNA 出力信号を提供し、前記出力段は並列結合されている複数の負荷部を具備し、各負荷部は選択的にイネーブルまたはディセーブルにされる、低ノイズ・アンプ

を具備する装置。

[ 13 ] 前記複数の負荷部の各々が 1 組の N 型金属酸化膜半導体 (NMOS) トランジスタに結合されている 1 組の P 型金属酸化膜半導体 (PMOS) トランジスタを具備する、

[ 12 ] の装置。

[ 14 ] 前記複数の負荷部が、相違するサイズのトランジスタを用いて実現されている、

[ 12 ] の装置。

[ 15 ] 前記複数の負荷部が、相違する量の電流または相違するバイアス電圧によってバイアスされる、

[ 12 ] の装置。

[ 16 ] 前記複数の負荷部が、複数の LNA 出力信号を提供するように構成されており、

1 つの LNA 出力信号が各負荷部用である、

[ 12 ] の装置。

[ 17 ] 前記複数の負荷部が第 1 および第 2 負荷部を具備し、

高線形性モードについては前記第 1 および第 2 負荷部がイネーブルにされ、

低線形性モードについては前記第 1 負荷部がイネーブルにされるとともに前記第 2 負荷部がディセーブルにされる、

[ 12 ] の装置。

[ 18 ] 低ノイズ・アンプ (LNA) 入力信号を受信し、複数の LNA 出力信号を提供するように構成されている低ノイズ・アンプ (LNA) と、

前記 LNA に結合されている複数のミキサ対であって、各ミキサ対はイネーブルにされていると前記複数の LNA 出力信号のうちの相違する 1 つをダウンコンバートするように構成されている、複数のミキサ対と、

を具備する装置。

[ 19 ] 各ミキサ対が、複数のモードの中から選択されたモードに基づいてイネーブルまたはディセーブルにされる、

[ 18 ] の装置。

[ 20 ] 前記 LNA が、前記複数の LNA 出力信号を提供するように構成されている複数の負荷部を具備し、

各負荷部が、選択されたモードに基づいてイネーブルまたはディセーブルにされる、

[ 19 ] の装置。

[ 21 ] 前記複数のミキサ対が第 1 および第 2 ミキサ対を具備し、

前記 LNA が、前記第 1 および第 2 ミキサ対のための第 1 および第 2 LNA 出力信号を提供するように構成されている第 1 および第 2 負荷部をそれぞれ具備する、

[ 18 ] の装置。

[ 22 ] 高線形性モードについては前記第 1 および第 2 負荷部ならびに前記第 1 および第 2 ミキサ対がイネーブルにされ、

低線形性モードについては前記第 1 負荷部および前記第 1 ミキサ対がイネーブルにされるとともに前記第 2 負荷部および前記第 2 ミキサ対がディセーブルにされる、

[ 21 ] の装置。

10

20

30

40

50

[ 2 3 ] 低ノイズ・アンプ ( L N A ) 入力信号を受信し、少なくとも 1 つの L N A 出力信号を提供するように構成されている低ノイズ・アンプ ( L N A ) と、

前記 L N A に結合されている複数のミキサ対であって、各ミキサ対はイネーブルにされていると少なくとも 1 つの L N A 出力信号のうちの 1 つをダウンコンバートするように構成されており、各ミキサ対は選択的にイネーブルまたはディセーブルにされる、複数のミキサ対と、

を具備する集積回路。

[ 2 4 ] 前記複数のミキサ対が第 1 および第 2 ミキサ対を具備し、

高線形性モードについては前記第 1 および第 2 ミキサ対がイネーブルにされ、

低線形性モードについては前記第 1 ミキサ対がイネーブルにされるとともに前記第 2 ミキサ対がディセーブルにされる、

10

[ 2 3 ] の集積回路。

[ 2 5 ] 前記 L N A が並列結合されている複数の負荷部を具備し、

各負荷部が選択的にイネーブルまたはディセーブルにされる、

[ 2 3 ] の集積回路。

[ 2 6 ] 前記複数の負荷部が第 1 および第 2 負荷部を具備し、

高線形性モードについては前記第 1 および第 2 負荷部がイネーブルにされ、

低線形性モードについては前記第 1 負荷部がイネーブルにされるとともに前記第 2 負荷部がディセーブルにされる、

[ 2 5 ] の集積回路。

20

[ 2 7 ] 前記複数のミキサ対が第 1 および第 2 ミキサ対を具備し、

前記複数の負荷部が第 1 および第 2 負荷部を具備し、

高線形性モードについては前記第 1 および第 2 負荷部ならびに前記第 1 および第 2 ミキサ対がイネーブルにされ、

低線形性モードについては前記第 1 負荷部および前記第 1 ミキサ対がイネーブルにされるとともに前記第 2 負荷部および前記第 2 ミキサ対がディセーブルにされる、

[ 2 5 ] の集積回路。

[ 2 8 ] 検出された動作条件に基づいて複数のモードの中からモードを選択することと、

前記選択されたモードに基づいて、複数のミキサ対のうちの少なくとも 1 つのミキサ対をイネーブルにすることと、

30

前記選択されたモードに基づいて、存在する場合に前記複数のミキサ対のうちの残りのミキサ対をディセーブルにすることと、

を具備する、受信器を操作する方法。

[ 2 9 ] 前記複数のミキサ対が第 1 および第 2 ミキサ対を具備し、

前記複数のミキサ対のうちの少なくとも 1 つのミキサ対をイネーブルにすることおよび残りのミキサ対をディセーブルにすることが、高線形性モードが選択されている場合に前記第 1 および第 2 ミキサ対をイネーブルにすることと、低線形性モードが選択されている場合に前記第 1 ミキサをイネーブルにするとともに前記第 2 ミキサ対をディセーブルにすることと、を具備する、

[ 2 8 ] の方法。

40

[ 3 0 ] 前記選択されたモードに基づいて、低ノイズ・アンプ ( L N A ) の複数の負荷部のうちの少なくとも 1 つの負荷部をイネーブルにすることと、

前記選択されたモードに基づいて、存在する場合に前記複数の負荷部のうちの残りの負荷部をディセーブルにすることと、

をさらに具備する、

[ 2 8 ] の方法。

[ 3 1 ] 前記複数の負荷部が第 1 および第 2 負荷部を具備し、

前記複数の負荷部のうちの少なくとも 1 つの負荷部をイネーブルにすることおよび残りの負荷部をディセーブルにすることが、高線形性モードが選択されている場合に前記第 1 および第 2 負荷部をイネーブルにすることと、低線形性モードが選択されている場合に前

50

記第1負荷部をイネーブルにするとともに前記第2負荷部をディセーブルにすることと、

を具備する、

[ 3 0 ] の方法。

[ 3 2 ] 前記モードを選択することが、

大きな妨害信号を検出することと、

大きな妨害信号が検出される場合に高線形性モードを選択することと、

大きな妨害信号が検出されない場合に低線形性モードを選択することと、

を具備する、

[ 2 8 ] の方法。

[ 3 3 ] 検出された動作条件に基づいて複数のモードの中からモードを選択するための手段と、 10

前記選択されたモードに基づいて、複数のミキサ対のうちの少なくとも1つのミキサ対をイネーブルにするための手段と、

前記選択されたモードに基づいて、存在する場合に前記複数のミキサ対のうちの残りのミキサ対をディセーブルにするための手段と、

を具備する装置。

[ 3 4 ] 前記複数のミキサ対が第1および第2ミキサ対を具備し、

前記複数のミキサ対のうちの少なくとも1つのミキサ対をイネーブルにするための手段および残りのミキサ対をディセーブルにするための手段が、

高線形性モードが選択されている場合に前記第1および第2ミキサ対をイネーブルにするための手段と、 20

低線形性モードが選択されている場合に前記第1ミキサをイネーブルにするとともに前記第2ミキサ対をディセーブルにするための手段と、

を具備する、

[ 3 3 ] の装置。

[ 3 5 ] 前記選択されたモードに基づいて、低ノイズ・アンプ ( L N A ) の複数の負荷部のうちの少なくとも1つの負荷部をイネーブルにするための手段と、

前記選択されたモードに基づいて、存在する場合に前記複数の負荷部のうちの残りの負荷部をディセーブルにするための手段と、

をさらに具備する、 30

[ 3 3 ] の装置。

[ 3 6 ] 前記複数の負荷部が第1および第2負荷部を具備し、

前記複数の負荷部のうちの少なくとも1つの負荷部をイネーブルにするための手段および残りの負荷部をディセーブルにするための手段が、

高線形性モードが選択されている場合に前記第1および第2負荷部をイネーブルにするための手段と、

低線形性モードが選択されている場合に前記第1負荷部をイネーブルにするとともに前記第2負荷部をディセーブルにするための手段と、

を具備する、

[ 3 5 ] の装置。

[ 3 7 ] 前記モードを選択するための手段が、 40

大きな妨害信号を検出するための手段と、

大きな妨害信号が検出される場合に高線形性モードを選択するための手段と、

大きな妨害信号が検出されない場合に低線形性モードを選択するための手段と、

を具備する、

[ 3 3 ] の装置。

[ 3 8 ] 少なくとも1つのコンピュータに、検出された動作条件に基づいて複数のモードの中からモードを選択させるためのコードと、

前記少なくとも1つのコンピュータに、前記選択されたモードに基づいて、複数のミキサ対のうちの少なくとも1つのミキサ対をイネーブルにさせるためのコードと、

前記少なくとも1つのコンピュータに、前記選択されたモードに基づいて、存在する場合に前記複数のミキサ対のうちの残りのミキサ対をディセーブルにさせるためのコードと

を具備するコンピュータ可読媒体を具備するコンピュータ・プログラム製品。

[ 39 ] 前記コンピュータ可読媒体が、

前記少なくとも 1 つのコンピュータに、前記選択されたモードに基づいて、低ノイズ・アンプ (LNA) の複数の負荷部のうちの少なくとも 1 つの負荷部をイネーブルにさせるためのコードと、

前記少なくとも1つのコンピュータに、前記選択されたモードに基づいて、存在する場合に前記複数の負荷部のうちの残りの負荷部をディセーブルにさせるためのコードと、

をさらに具備する、

[ 38 ] のコンピュータ・プログラム製品。

(  1 )

FIG. 1

〔 囮 2 A 〕

〔図2B〕

【 义 3 】

FIG. 3

【図4】

図4

FIG. 4

【図5】

図5

FIG. 5

【図6】

図6

FIG. 6

【図7】

図7

FIG. 7

【図 8 A】

図 8A

【図 8 B】

図 8B

【図 9】

図 9

## フロントページの続き

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100158805

弁理士 井関 守三

(74)代理人 100172580

弁理士 赤穂 隆雄

(74)代理人 100179062

弁理士 井上 正

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(72)発明者 リ・リウ

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 プラサド・エス・・グデム

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 石川 雄太郎

(56)参考文献 特開平04-346523 (JP, A)

特開2005-295348 (JP, A)

特開2001-127658 (JP, A)

特開2006-066714 (JP, A)

特開2006-311623 (JP, A)

特開2003-298441 (JP, A)

特表2001-511321 (JP, A)

国際公開第2007/046303 (WO, A1)

特開2007-300437 (JP, A)

特開平10-173563 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |                  |

|--------|------------------|

| H 04 B | 1 / 16           |

| H 04 B | 7 / 24 - 7 / 26  |

| H 04 W | 4 / 00 - 99 / 00 |

H 0 3 F 1 / 3 2

H 0 3 F 3 / 1 8 9