(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-158366

(P2007-158366A)

(43) 公開日 平成19年6月21日(2007.6.21)

(51) Int.C1.

HO1L 21/822 (2006.01)

HO1L 27/04 (2006.01)

HO1G 4/33 (2006.01)

F 1

HO1L 27/04

HO1G 4/06

C

102

テーマコード(参考)

5E082

5F038

審査請求 有 請求項の数 2 O.L. (全 9 頁)

(21) 出願番号

特願2007-11924 (P2007-11924)

(22) 出願日

平成19年1月22日(2007.1.22)

(62) 分割の表示

特願平7-172142の分割

原出願日

平成7年7月7日(1995.7.7)

(71) 出願人 000116024

ローム株式会社

京都府京都市右京区西院溝崎町21番地

(74) 代理人 100105647

弁理士 小栗 昌平

(74) 代理人 100105474

弁理士 本多 弘徳

(74) 代理人 100108589

弁理士 市川 利光

(72) 発明者 中村 孝

京都市右京区西院溝崎町21番地 ローム

株式会社内F ターム(参考) 5E082 AB01 BB01 BB07 EE05 FG03

5F038 AC02 AC05 AC15 DF05 EZ16

EZ17 EZ20

(54) 【発明の名称】誘電体キャパシタ

## (57) 【要約】

【課題】経年劣化および分極反転の繰り返しによる劣化の少ない強誘電体キャパシタまたは高誘電率を有する誘電体キャパシタを提供する。

【解決手段】下部電極と、前記下部電極の上に形成され、強誘電体または高誘電率を有する誘電体によって構成される誘電体層と、前記誘電体層の上に形成された上部電極と、を備え、前記下部電極はパラジウムの柱状結晶間にその酸化物である酸化パラジウムを有し、その上層に白金層を具備したことを特徴とする。

【選択図】図1

2 : シリコン基板

4 : 酸化シリコン層

8 : 強誘電体層

12 : 下部電極

15 : 上部電極

**【特許請求の範囲】****【請求項 1】**

下部電極と、前記下部電極の上に形成され、強誘電体または高誘電率を有する誘電体によって構成される誘電体層と、前記誘電体層の上に形成された上部電極と、を備え、前記下部電極はパラジウムの柱状結晶間にその酸化物である酸化パラジウムを有し、その上層に白金層を具備した誘電体キャパシタ。

**【請求項 2】**

下部電極を形成するステップと、前記下部電極の上に強誘電体または高誘電率を有する誘電体によって構成される誘電体層を形成するステップと、前記誘電体層の上に上部電極を形成するステップとを備える誘電体キャパシタの製造方法であって、前記下部電極を形成するステップは、柱状結晶構造を有するパラジウムの薄膜を形成する工程と、前記パラジウムの薄膜上に白金の薄膜を形成する工程と、前記パラジウムは酸化する一方前記白金は酸化しない条件の酸化雰囲気中で熱処理を行い、前記パラジウムの薄膜の柱状結晶間にのみ酸化パラジウムを形成する工程とからなることを特徴とする誘電体キャパシタの製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

この発明は誘電体キャパシタに関するものであり、特にその強誘電性等の向上に関するものである。

**【背景技術】****【0002】**

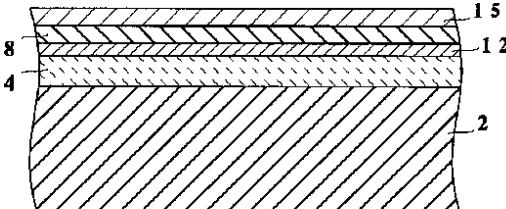

従来の強誘電体キャパシタを、図10に示す。シリコン基板2の上に、酸化シリコン層4が形成されている。その上に、白金からなる下部電極6が設けられている。下部電極6の上には、強誘電体層であるPZT( $PbZr_xTi_{1-x}O_3$ )膜8が設けられ、さらにその上には、白金からなる上部電極10が設けられている。このようにして、下部電極6、PZT膜8、上部電極10により、強誘電体キャパシタが形成される。

**【0003】**

なお、ここで、下部電極6として白金を用いているのは、次のような理由によるものである。PZT膜8は、配向膜の上に形成しなければならない。アモルファス膜の上に形成すると、配向しないため強誘電性が損なわれてしまうからである。一方、下部電極6は、シリコン基板2から絶縁した状態で形成しなければならない。このため、シリコン基板2上に酸化シリコン層4を形成している。この酸化シリコン層4はアモルファスである。一般に、アモルファスの上に形成した膜は無配向膜となるが、白金はアモルファスの上においても、配向膜となる性質を有している。このような理由から、下部電極として白金が用いられている。

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

しかしながら、上記のような従来の強誘電体キャパシタには、次のような問題点があった。

**【0005】**

白金は酸素やPbを透過しやすいため、強誘電体(PZT)内の酸素の抜け出し、経年変化および分極反転の繰り返しによって強誘電性が低下するという問題があった。つまり、図11に示すように、白金の柱状結晶の間から、強誘電体中の酸素やPbが抜け出すおそれがあった。

**【0006】**

また、このような問題は高誘電率を有する誘電体を用いたキャパシタにおいても同様に生じていた。

**【0007】**

10

20

20

30

40

50

この発明は、上記の問題点を解決して、経年劣化および分極反転の繰り返しによる劣化の少ない強誘電体キャパシタまたは高誘電率を有する誘電体キャパシタを提供することを目的とする。

【課題を解決するための手段】

【0008】

なお、この発明において、「キャパシタ」とは絶縁体の両側に電極が設けられた構造を指すものであり、電気の蓄積に用いられると否とにかかわらず、この構造を有するものを含む概念である。

【0009】

本発明は、下部電極と、前記下部電極の上に形成され、強誘電体または高誘電率を有する誘電体によって構成される誘電体層と、前記誘電体層の上に形成された上部電極と、を備え、前記下部電極はパラジウムの柱状結晶間にその酸化物である酸化パラジウムを有し、その上層に白金層を具備したことを特徴とする。

【0010】

また本発明は、下部電極を形成するステップと、前記下部電極の上に強誘電体または高誘電率を有する誘電体によって構成される誘電体層を形成するステップと、前記誘電体層の上に上部電極を形成するステップとを備える誘電体キャパシタの製造方法であって、前記下部電極を形成するステップは、柱状結晶構造を有するパラジウムの薄膜を形成する工程と、前記パラジウムの薄膜上に白金の薄膜を形成する工程と、前記パラジウムは酸化する一方前記白金は酸化しない条件の酸化雰囲気中で熱処理を行い、前記パラジウムの薄膜の柱状結晶間に酸化パラジウムを形成する工程とからなることを特徴とする。

【0011】

また以下のような構成もある。

この誘電体キャパシタは、少なくとも柱状結晶の酸化層である $W_{0x}$ 層、 $Ti_{0x}$ 層、 $Ta_{0x}$ 層、 $Ir_{02}$ 層、 $Pt_{02}$ 層、 $Ru_{0x}$ 層、 $Re_{0x}$ 層、 $Pd_{0x}$ 層、 $Os_{0x}$ 層のいずれか1つの酸化層を有する下部電極、下部電極の上に形成され、強誘電体または高誘電率を有する誘電体によって構成される誘電体層、誘電体層の上に形成された上部電極、を備え、前記酸化層は前記誘電体層からの酸素の抜け出しを防止するように構成されている。

【0012】

また、この誘電体キャパシタは、酸化層の上に、 $W$ 層、 $Ti$ 層、 $Ta$ 層、 $Ir$ 層、 $Pt$ 層、 $Ru$ 層、 $Re$ 層、 $Pd$ 層、 $Os$ 層のいずれか1つの導電体層が形成されて下部電極が構成されており、当該導電体層の上に強誘電体層が形成されている。

【0013】

また、この誘電体キャパシタは、下部電極は、基板の上に形成された酸化シリコン層の上に形成されており、また、酸化シリコン層に接する接合層を有している。

【0014】

また、この誘電体キャパシタは、下部電極、下部電極の上に形成され、強誘電体または高誘電率を有する誘電体によって構成される誘電体層、誘電体層の上に形成され、少なくとも柱状結晶の酸化層である $W_{0x}$ 層、 $Ti_{0x}$ 層、 $Ta_{0x}$ 層、 $Ir_{02}$ 層、 $Pt_{02}$ 層、 $Ru_{0x}$ 層、 $Re_{0x}$ 層、 $Pd_{0x}$ 層、 $Os_{0x}$ 層のいずれか1つの酸化層を有する上部電極、を備え、酸化層は誘電体層からの酸素の抜け出しを防止するように構成されている。

【0015】

また、この誘電体キャパシタは、下部電極は、基板の上に形成された酸化シリコン層の上に形成されており、また、酸化シリコン層に接する接合層を有している。

【0016】

また、この誘電体キャパシタは、少なくとも柱状結晶の酸化層である $W_{0x}$ 層、 $Ti_{0x}$ 層、 $Ta_{0x}$ 層、 $Ir_{02}$ 層、 $Pt_{02}$ 層、 $Ru_{0x}$ 層、 $Re_{0x}$ 層、 $Pd_{0x}$ 層、 $Os_{0x}$ 層のいずれか1つの酸化層を有する下部電極、下部電極の上に形成され、強誘電体または高誘電率を有する誘電体によって構成される誘電体層、誘電体層の上に形成され、少なくとも柱状結晶の酸化層である $W_{0x}$ 層、 $Ti_{0x}$ 層、 $Ta_{0x}$ 層、 $Ir_{02}$ 層、 $Pt_{02}$ 層、 $Ru_{0x}$ 層、 $Re_{0x}$ 層、 $Pd_{0x}$ 層、 $Os_{0x}$ 層のいずれか1

10

20

30

40

50

つの酸化層を有する上部電極を備え、酸化層は誘電体層からの酸素の抜け出しを防止するように構成されている。

【0017】

また、この誘電体キャパシタは、酸化層の上に、W層、Ti層、Ta層、Ir層、Pt層、Ru層、Re層、Pd層、Os層のいずれか1つの導電体層が形成されて下部電極が構成されており、当該導電体層の上に強誘電体層が形成されている。

【0018】

また、この誘電体キャパシタは、下部電極は、基板の上に形成された酸化シリコン層の上に形成されており、また、酸化シリコン層に接する接合層を有している。

【0019】

また、この誘電体キャパシタの製造方法は、基板上に、スパッタリングによって、柱状結晶の酸化層である $W_{0x}$ 層、 $Ti_{0x}$ 層、 $Ta_{0x}$ 層、 $Ir_{02}$ 層、 $Pt_{02}$ 層、 $Ru_{0x}$ 層、 $Re_{0x}$ 層、 $Pd_{0x}$ 層、 $Os_{0x}$ 層のいずれか1つの酸化層を下部電極として形成するステップ、下部電極の上に強誘電体膜または高誘電率を有する誘電体膜を誘電体層として形成するステップ、誘電体層の上に上部電極を形成するステップ、を備え、酸化層は誘電体層からの酸素の抜け出しを防止するように構成されている。

【0020】

また、この誘電体キャパシタの製造方法は、基板上にスパッタリングによってW層、Ti層、Ta層、Ir層、Pt層、Ru層、Re層、Pd層、Os層のいずれか1つの柱状結晶材料のベース層を形成するステップ、柱状結晶材料のベース層の表面を酸化するステップ、表面が酸化された柱状結晶材料のベース層の上に強誘電体膜または高誘電率を有する誘電体膜を誘電体層として形成するステップ、誘電体層の上に上部電極を形成するステップ、を備え、酸化層は前記誘電体層からの酸素の抜け出しを防止するように構成されている。

【0021】

また、この誘電体キャパシタの製造方法は、基板上に下部電極を形成するステップ、下部電極の上に強誘電体膜または高誘電率を有する誘電体膜を誘電体層として形成するステップ、誘電体層の上に、スパッタリングによって、柱状結晶の酸化層である $W_{0x}$ 層、 $Ti_{0x}$ 層、 $Ta_{0x}$ 層、 $Ir_{02}$ 層、 $Pt_{02}$ 層、 $Ru_{0x}$ 層、 $Re_{0x}$ 層、 $Pd_{0x}$ 層、 $Os_{0x}$ 層のいずれか1つの酸化層を上部電極として形成するステップ、を備え、酸化層は誘電体層からの酸素の抜け出しを防止するように構成されている。

【0022】

また、この誘電体キャパシタの製造方法は、基板上に下部電極を形成するステップ、下部電極の上に強誘電体膜または高誘電率を有する誘電体膜を誘電体層として形成するステップ、誘電体層の上にスパッタリングによってW層、Ti層、Ta層、Ir層、Pt層、Ru層、Re層、Pd層、Os層のいずれか1つの柱状結晶材料のベース層を形成するステップ、柱状結晶材料のベース層の表面を酸化して誘電体層からの酸素の抜け出しを防止する酸化層を形成するステップ、を備えている。

【0023】

また、この誘電体キャパシタの製造方法は、基板上にスパッタリングによってW層、Ti層、Ta層、Ir層、Pt層、Ru層、Re層、Pd層、Os層のいずれか1つの柱状結晶材料のベース層を層を形成するステップ、ベース層の表面に、W層、Ti層、Ta層、Ir層、Pt層、Ru層、Re層、Pd層、Os層のいずれか1つの薄膜導電体層を形成するステップ、表面に薄膜導電体が形成された柱状結晶材料のベース層を酸化して誘電体層からの酸素の抜け出しを防止する柱状結晶材料の酸化層を形成するステップ、酸化処理された柱状結晶材料のベース層の上に薄膜導電体層を介して強誘電体膜または高誘電率を有する誘電体膜を誘電体層として形成するステップ、誘電体層の上に上部電極を形成するステップ、を備えている。

【0024】

また、この誘電体キャパシタの製造方法は、酸化処理を、誘電体層を形成する際の熱処理と併用したことを特徴としている。

【0025】

10

20

30

40

50

また、この誘電体キャパシタは、少なくとも $W_{0x}$ 層、 $Ti_{0x}$ 層、 $Ta_{0x}$ 層、 $IrO_2$ 層、 $PtO_2$ 層、 $RuO_x$ 層、 $ReO_x$ 層、 $PdO_x$ 層、 $OsO_x$ 層のいずれか1つの酸化層を下部電極に有している。したがって、誘電体層からの酸素の抜け出しを防止することができ、誘電特性の経年変化を抑えることができる。

## 【0026】

また、この誘電体キャパシタは、酸化層の上に $W$ 層、 $Ti$ 層、 $Ta$ 層、 $Ir$ 層、 $Pt$ 層、 $Ru$ 層、 $Re$ 層、 $Pd$ 層、 $Os$ 層のいずれか1つの導電層を設け、この導電層の上に誘電体層を設けている。したがって、リーク電流の減少をはかることができる。

## 【0027】

また、この誘電体キャパシタは、少なくとも $W_{0x}$ 層、 $Ti_{0x}$ 層、 $Ta_{0x}$ 層、 $IrO_2$ 層、 $PtO_2$ 層、 $RuO_x$ 層、 $ReO_x$ 層、 $PdO_x$ 層、 $OsO_x$ 層のいずれか1つの酸化層を上部電極に有している。したがって、誘電体層からの酸素の抜け出しを防止することができ、誘電特性の経年変化を抑えることができる。 10

## 【0028】

また、この誘電体キャパシタは、少なくとも $W_{0x}$ 層、 $Ti_{0x}$ 層、 $Ta_{0x}$ 層、 $IrO_2$ 層、 $PtO_2$ 層、 $RuO_x$ 層、 $ReO_x$ 層、 $PdO_x$ 層、 $OsO_x$ 層のいずれか1つの酸化層を上部電極および下部電極に有している。したがって、誘電体層からの酸素の抜け出しを防止することができ、誘電特性の経年変化を抑えることができる。

## 【0029】

また、この誘電体キャパシタは、酸化層の上に $W$ 層、 $Ti$ 層、 $Ta$ 層、 $Ir$ 層、 $Pt$ 層、 $Ru$ 層、 $Re$ 層、 $Pd$ 層、 $Os$ 層のいずれか1つの導電層を設け、この導電層の上に誘電体層を設けている。したがって、リーク電流の減少をはかることができる。 20

## 【0030】

すなわち、強誘電性、高誘電性の良好な誘電体キャパシタを提供することができる。

## 【発明を実施するための最良の形態】

## 【0031】

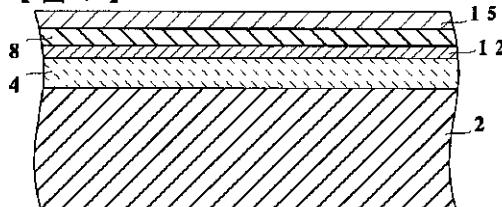

図1に、この発明の一実施例による強誘電体キャパシタの構造を示す。シリコン基板2の上に、酸化シリコン層4、下部電極12、強誘電体膜(強誘電体層)8、上部電極15が設けられている。下部電極12は酸化パラジウム( $PdO_x$ )によって形成されており、上部電極15も酸化パラジウム( $PdO_x$ )によって形成されている。 30

## 【0032】

従来例の図11に示すように、白金は柱状の結晶であるため、強誘電体膜8中の酸素を透過してしまう。この実施例では、酸化パラジウムを下部電極12として用いている。この酸化パラジウム層12は、柱状結晶でないため酸素を透過しにくい。したがって、強誘電体膜8の酸素の欠乏を防ぐことができる。上部電極15についても同様である。これにより、強誘電体膜8の強誘電性が向上した。つまり、上部電極15または下部電極12のいずれかを酸化パラジウムで構成すると、白金で構成した場合に比べて残留分極Prの使用による劣化がかなり改善されたなお、上記実施例では、下部電極12、上部電極15の双方を酸化パラジウムによって形成しているので、酸素やPbの透過を確実に防止することができる。しかし、何れか一方だけでも、ある程度の効果を得ることができる。 40

## 【0033】

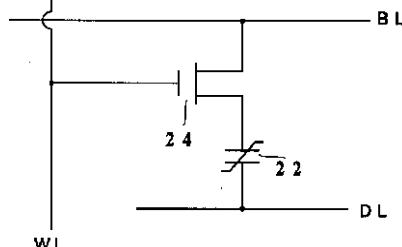

上記のような強誘電体キャパシタは、たとえば、図2に示すように、トランジスタ24と組み合わせて、不揮発性メモリとして用いることができる。

## 【0034】

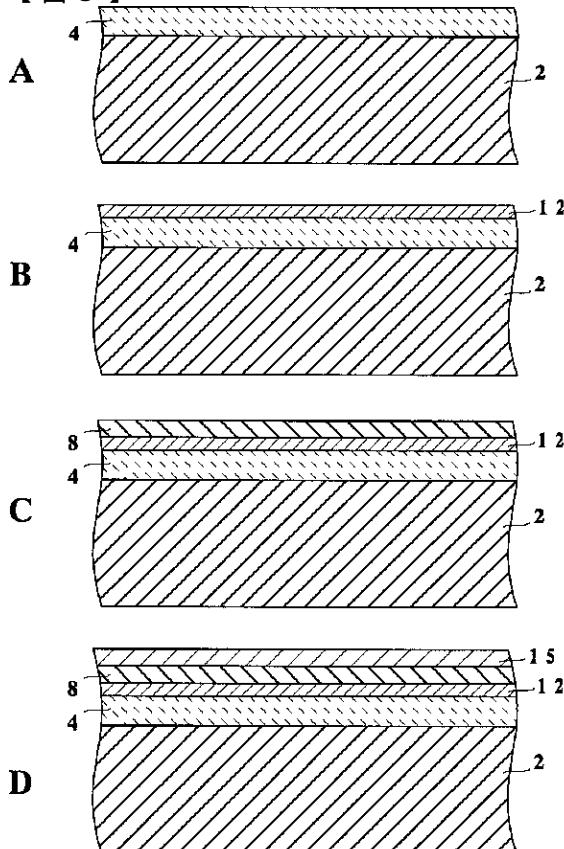

図3に、この発明の一実施例による強誘電体キャパシタの製造工程を示す。シリコン基板2の表面を熱酸化し、酸化シリコン層4を形成する(図3A)。ここでは、酸化シリコン層4の厚さを600nmとした。次に、パラジウムをターゲットとして用いて、反応性スパッタリングにより酸化パラジウムを、酸化シリコン層4の上に形成し、これを下部電極12とする(図3B)。ここでは、200nmの厚さに形成した。

## 【0035】

次に、この下部電極12の上に、ゾルゲル法によって、強誘電体層8としてPZT膜を形成する(図3C)。出発原料として、 $Pb(CH_3COO)_2 \cdot 3H_2O$ 、 $Zr(t-OC_4H_9)_4$ 、 $Ti(i-OC_3H_7)_4$ の混合溶液を用いた。この混合溶液をスピンドルコートした後、150度(摂氏、以下同じ)で乾燥させ、ドライエアー雰囲気において400度で30秒の仮焼成を行った。これを5回繰り返した後、 $O_2$ 雰囲気中で、700度以上の熱処理を施した。このようにして、250nmの強誘電体層8を形成した。なお、ここでは、 $PbZr_xTi_{1-x}O_3$ において、 $x$ を0.52として(以下PZT(52·48)と表わす)、PZT膜を形成している。

## 【0036】

さらに、強誘電体層8の上に、反応性スパッタリングにより酸化パラジウムを形成し、上部電極15とする(図3D)。ここでは、200nmの厚さに形成した。このようにして、強誘電体キャパシタを得ることができる。

## 【0037】

なお、酸化パラジウムに代えて、 $W_0_x, Ti_0_x, Ta_0_x, Ir_0_2, Pt_0_2, Re_0_x, Ru_0_x, Os_0_x$ を用いてよい。

## 【0038】

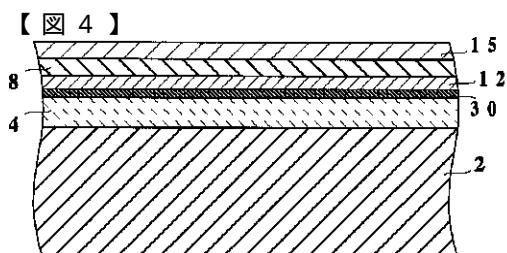

また、これら酸化層の上に強誘電体を形成すると、強誘電体の配向性が損なわれる。そこで、酸化層の上にW層、Ti層、Ta層、Ir層、Pt層、Ru層、Re層、Pd層、Os層等の導電体層を設け、その上に強誘電体を形成してもよい。さらに、このような導電体層を設けることにより、強誘電体のリークを減少させることができた、図4に、この発明の他の実施例による強誘電体キャパシタの構造を示す。この実施例では、下部電極12と酸化シリコン層4との間に、チタン層(5nm)を接合層30として設けている。一般に、酸化パラジウムと酸化シリコンとの密着性はあまり良くない。このため、部分的に合金層がはがれ、強誘電特性を劣化させるおそれがある。そこで、この実施例では、酸化シリコン層4と密着性のよいチタン層を接合層30として設けている。これにより、強誘電特性を改善している。なお、チタン層は、スパッタリングによって形成すればよい。

## 【0039】

なお、上記実施例では、接合層30としてチタン層を用いたが、接合性を改善する材料であれば、どのようなものでもよい。例えば、白金層を用いてよい。

## 【0040】

上記各実施例では、強誘電体膜8としてPZTを用いているが、酸化物強誘電体であれば、どのようなものを用いてよい。たとえば、 $Ba_4Ti_3O_{12}$ を用いてよい。

## 【0041】

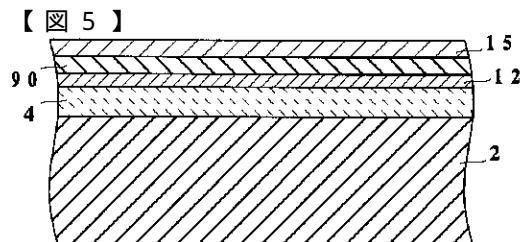

この発明の他の実施例によるキャパシタを図5に示す。この実施例では、強誘電体層8に代えて、高誘電率を有する誘電体層90を用いている。酸化シリコン層4の上に、酸化パラジウムの下部電極12を設け、その上に $SrTiO_3$ 、 $(Sr, Ba)TiO_3$ のペロブスカイト構造を有する高誘電率薄膜を誘電体層90として形成した。この場合も、強誘電体の場合と同様、誘電性の改善が図られた。つまり、強誘電体層について述べたことが、高誘電率を有する誘電体層にも適用できることが明らかとなった。

## 【0042】

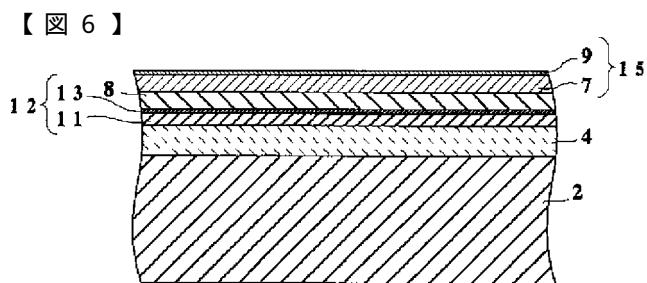

図5に、この発明の他の実施例による強誘電体キャパシタの構造を示す。シリコン基板2の上に、酸化シリコン層4、下部電極12、強誘電体膜(強誘電体層)8、上部電極15が設けられている。下部電極12は、パラジウム層11とその上に形成された酸化パラジウム層によって形成されている。また、上部電極15は、パラジウム層7とその上に形成された酸化パラジウム層9によって形成されている。

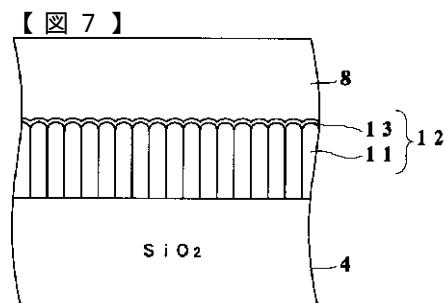

## 【0043】

下部電極12近傍の拡大図を、図7に示す。パラジウム層11は、柱状の結晶であるため、強誘電体膜8中の酸素を透過してしまう。この実施例では、パラジウム層11の上部表面に酸化パラジウム層13を形成している。前述のように、この酸化パラジウム層13によって強誘電体膜8の酸素の欠乏を防ぐことができる。上部電極15についても同様である。

10

20

30

40

50

## 【0044】

上記実施例では、下部電極12、上部電極15の双方に酸化パラジウム層を形成しているので、経年変化の少ない優れた特性の強誘電体キャパシタを得ることができる。なお、下部電極12、上部電極15の何れか一方を、上記の構造にしても、ある程度の効果は得られる。

## 【0045】

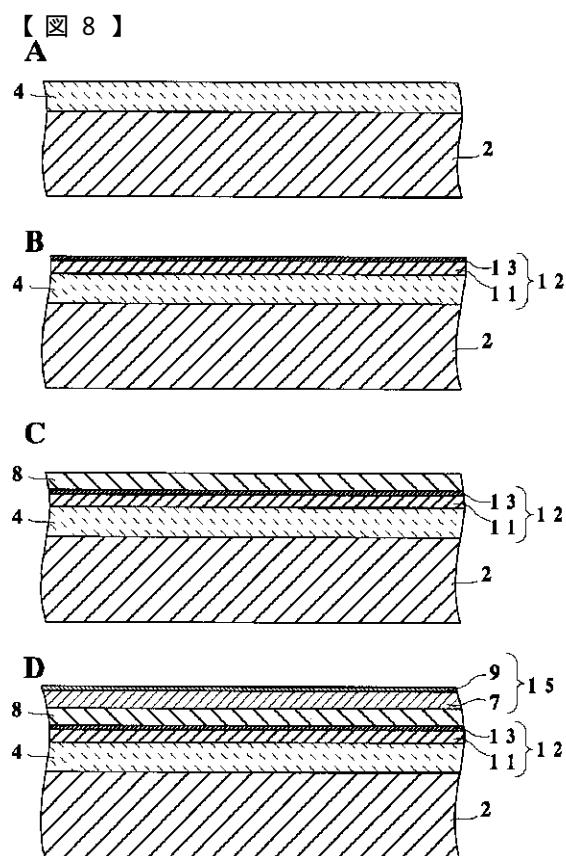

図8に、この強誘電体キャパシタの製造工程を示す。シリコン基板2の表面を熱酸化し、酸化シリコン層4を形成する(図8A)。ここでは、酸化シリコン層4の厚さを600nmとした。次に、パラジウムをターゲットとして用いて、パラジウム層11を、酸化シリコン層4の上に形成する(図8B)。次に、O<sub>2</sub>雰囲気中で800度、1分の熱処理を行い、パラジウム層11の表面に酸化パラジウム層13を形成する。このパラジウム層11と酸化パラジウム層13を、下部電極12とする。ここでは、下部電極を、200nmの厚さに形成した。

## 【0046】

次に、この下部電極12の上に、ゾルゲル法によって、強誘電体層8としてPZT膜を形成する(図8C)。出発原料として、Pb(CH<sub>3</sub>COO)<sub>2</sub>·3H<sub>2</sub>O、Zr(t-OC<sub>4</sub>H<sub>9</sub>)<sub>4</sub>、Ti(i-OC<sub>3</sub>H<sub>7</sub>)<sub>4</sub>の混合溶液を用いた。この混合溶液をスピンドルコートした後、150度(摂氏、以下同じ)で乾燥させ、ドライエアー雰囲気において400度で30秒の仮焼成を行った。これを5回繰り返した後、O<sub>2</sub>雰囲気中で、700度以上の熱処理を施した。このようにして、250nmの強誘電体層8を形成した。なお、ここでは、PbZr<sub>x</sub>Ti<sub>1-x</sub>O<sub>3</sub>において、xを0.52として(以下PZT(52·48)と表わす)、PZT膜を形成している。

## 【0047】

さらに、強誘電体層8の上に、スパッタリングによりパラジウム層7を形成する。次に、O<sub>2</sub>雰囲気中で800度、1分の熱処理を行い、パラジウム層7の表面に酸化パラジウム層9を形成する(図8D)。このパラジウム層7と酸化パラジウム層9を、上部電極15とする。ここでは、上部電極15を、200nmの厚さに形成した。このようにして、強誘電体キャパシタを得ることができる。

## 【0048】

なお、この実施例についても、図4で説明したような接合層30を設けることが好ましい。

## 【0049】

また、ここで説明したパラジウムの表面を酸化するという実施例は、強誘電体膜だけではなく前述の高誘電率を有する誘電体膜にも適用でき、同様の効果を得ることができる。

## 【0050】

上記のように、パラジウム層の表面を酸化することにより強誘電体膜の酸素の抜け出しを防止できるが、表面に酸化パラジウムが形成されて、強誘電体膜の配向性が悪くなる。これは、既に述べたように、酸化パラジウム層13の上に、W層、Ti層、Ta層、Ir層、Pt層、Ru層、Re層、Pd層、Os層等の導電体層を設けることにより解決できる。しかし、次のようにして、下部電極を形成しても解決できる。

## 【0051】

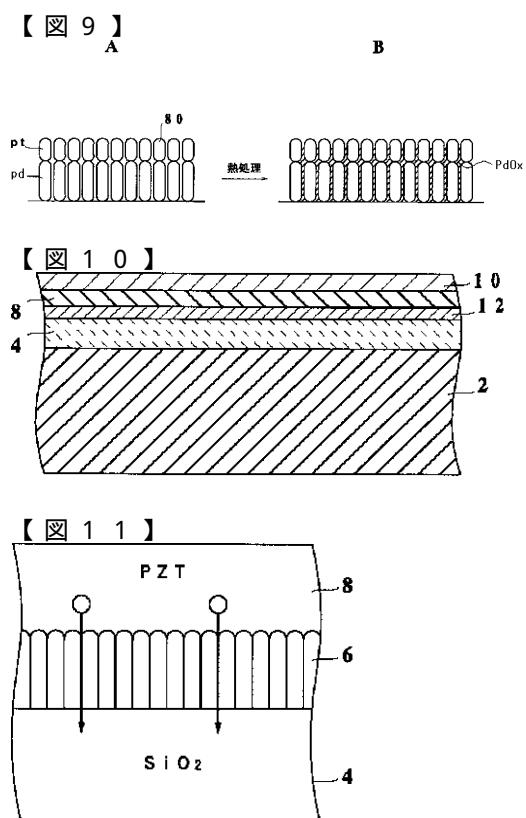

まず、図9に示すように、パラジウム層11の上に白金層80(薄膜導電体)をごく薄く設ける。ここでは、30nmとした。次に、この状態で熱処理を行う。表面の白金層80は酸素と反応しないので、酸化されない。また、白金層80は、薄く形成されているので、その下のパラジウム層11の結晶間が酸化され、酸化パラジウムが形成されて酸素の透過を防ぐ。したがって、表面は配向性に優れたままでありながら、酸素の透過を防ぐことのできる下部電極12を形成することができる。

## 【0052】

なお、このような薄膜白金層80を形成したのち酸化したパラジウム層11は、単独で下部電極12として使用できる。しかし、スパッタリングで形成した酸化パラジウム層の上に配向性の良い導電層(パラジウム層、白金層等)を設けて配向性を改善した実施例に

10

20

30

40

50

おいての、配向性の良い導電層として用いることもできる。

【0053】

また、ここで説明した実施例は、強誘電体膜だけでなく前述の高誘電率を有する誘電体膜にも適用でき、同様の効果を得ることができる。

【図面の簡単な説明】

【0054】

【図1】この発明の一実施例による強誘電体キャパシタの構図を示す図である。

【図2】強誘電体キャパシタ22を用いた不揮発性メモリを示す図である。

【図3】強誘電体キャパシタの製造工程を示す図である。

【図4】接合層30を設けた実施例を示す図である。

【図5】高誘電率を有する誘電体90を用いた場合の実施例を示す図である。

【図6】他の実施例による強誘電体キャパシタの構造を示す図である。

【図7】酸化パラジウム層が酸素の抜け出しを防止するメカニズムを示す図である。

【図8】図22の強誘電体キャパシタの製造工程を示す図である。

【図9】パラジウムの表面に薄膜白金を設けて酸化を行う実施例を示す図である。

【図10】従来の強誘電体キャパシタの構造を示す図である。

【図11】白金による下部電極6から酸素が抜け出す状態を示す図である。

【符号の説明】

【0055】

2 . . . シリコン基板

4 . . . 酸化シリコン層

8 . . . 強誘電体層

12 . . . 下部電極

15 . . . 上部電極

90 . . . 高誘電率を有する誘電体層

【図1】

2 : シリコン基板

4 : 酸化シリコン層

8 : 強誘電体層

12 : 下部電極

15 : 上部電極

【図2】

【図3】

10

20

2 : シリコン基板

4 : 酸化シリコン層

12 : 下部電極

15 : 上部電極