**Erfindungspatent für die Schweiz und Liechtenstein**

Schweizerisch-liechtensteinischer Patentschutzvertrag vom 22. Dezember 1978

**⑬ PATENTSCHRIFT A5**

⑭ Gesuchsnummer: 6954/82

⑮ Inhaber:

Schrack Elektronik Aktiengesellschaft, Wien (AT)

⑯ Anmeldungsdatum: 30.11.1982

⑰ Erfinder:

Leopold, Gerhard, Wiener Neudorf/Niederösterr.

(AT)

Listopad, Manfred, Wien (AT)

⑲ Patent erteilt: 31.10.1986

⑳ Vertreter:

Bovard AG, Bern 25

**㉑ Datenübertragungseinrichtung mit zwei getrennten Uebertragungswegen.**

㉒ Um serielle, aus mehreren Worten hoher Bitzahl bestehende Datenströme über Übertragungskanäle begrenzter Bandbreite übertragen zu können, wird der serielle Datenstrom mittels eines Multiplexers (3) in zwei Teildatenströme mit halber Übertragungsgeschwindigkeit umgesetzt, diese über eigene Kanäle voneinander getrennt übertragen und empfangsseitig mittels eines Multiplexers (12) wieder zum ursprünglichen Datenstrom zusammenge setzt. Um dabei Laufzeitunterschiede in den beiden Kanälen (5, 8) zu erkennen und zu berücksichtigen, sind quellenseitig ein an die Datenquelle (1) angeschlossener Modulator (2), senkenseitig ein mit der Datensenke (14) verbundener Demodulator (13) und sowohl quellenseitig als auch senkenseitig je ein Bitfolgenumsetzer (15, 16) vorgesehen, dessen Ausgang mit einem Eingang des Modulators (2) bzw. des Demodulators (13) und dessen Eingang an den Ausgang des Modulators (2) bzw. des Multiplexers (12) angeschlossen ist. An den Ausgang des Demodulators (13) ist eine dem Erkennen von Laufzeitunterschieden zwischen den beiden Übertragungswegen dienende Prüfvorrichtung (17) angeschlossen, mit der ein Laufzeitglied (11)

gesteuert wird, das in einem der beiden Übertragungswege angeordnet ist.

### PATENTANSPRÜCHE

1. Datenübertragungseinrichtung mit einer Datenquelle, die über einen quellenseitigen Demultiplexer, zwei getrennte Übertragungswege und einen Multiplexer mit einer Datensenke in Verbindung steht, wobei über jeden der beiden Übertragungswege Daten mit einer Bitrate übertragen werden, die die Hälfte der Bitrate der von der Datenquelle gelieferten und von der Datensenke empfangenen Daten beträgt, und wobei der Datenfluss in Worte einer bestimmten gleichbleibenden Bitanzahl unterteilt und in jedem Wort an der gleichen Stelle ein Prüfbit angeordnet ist, das mit jedem Wort alternierend eine logische «0» oder eine logische «1» ist, dadurch gekennzeichnet, dass quellenseitig ein Modulator (2) vorgesehen ist, an dessen einen Eingang die Datenquelle (1) und an dessen anderen Eingang der Ausgang eines ersten Bitfolgenumsetzers (15) angeschlossen ist, dessen Eingang mit dem Ausgang des Modulators (2) und dem Eingang des Demultiplexers (3) verbunden ist, und dass senkenseitig ein Demodulator (13) vorgesehen ist, dessen erster Eingang einerseits mit dem Ausgang des Multiplexers (12) und anderseits mit dem Eingang eines zweiten Bitfolgenumsetzers (16) verbunden ist, dessen Ausgang mit dem zweiten Eingang des Demodulators (13) in Verbindung steht, dessen Ausgang einerseits an die Datensenke (14), anderseits an den Eingang einer dem Erkennen von Laufzeitunterschieden zwischen den beiden Übertragungswegen dienenden Prüfvorrichtung (17) angeschlossen ist, durch die mindestens ein Laufzeitglied (11) gesteuert ist, das in einem der beiden Übertragungswege angeordnet ist.

2. Datenübertragungseinrichtung nach Anspruch 1, dadurch gekennzeichnet, dass als Modulator (2) und als Demodulator (13) je ein Exklusiv-Oder-Gatter (18, 19) und als Bitfolgenumsetzer (15, 16) je ein Schieberegister (20, 22) vorgesehen sind, wobei quellenseitig der eine Eingang des den Modulator (2) bildenden Exklusiv-Oder-Gatters (18) mit der Datenquelle (1), der Ausgang des den Modulator (2) bildenden Exklusiv-Oder-Gatters (18) einerseits mit dem Eingang des Demultiplexers (3), anderseits mit dem Dateneingang des Schieberegisters (20), ein Ausgang des Schieberegisters (20) unmittelbar bzw. zwei oder mehrere Ausgänge desselben über ein, bzw. mehrere in Kaskade geschaltete, Exklusiv-Oder-Gatter (21, 24, 25) mit dem zweiten Eingang des den Modulator (2) bildenden Exklusiv-Oder-Gatters (18) in Verbindung stehen, und dass senkenseitig der Ausgang des Multiplexers (12) einerseits mit dem einen Eingang des den Demodulator (13) bildenden Exklusiv-Oder-Gatters (19), anderseits mit dem Dateneingang des senkenseitigen Schieberegisters (22), ein Ausgang des Schieberegisters (22) unmittelbar bzw. zwei oder mehrere Ausgänge desselben über ein, bzw. mehrere in Kaskade geschaltete, Exklusiv-Oder-Gatter (23) mit dem zweiten Eingang des den Demodulator (13) bildenden Exklusiv-Oder-Gatters (19) und dessen Ausgang mit der Datensenke (14) in Verbindung stehen.

3. Datenübertragungseinrichtung nach Anspruch 1 oder 2, dadurch gekennzeichnet, dass die Prüfvorrichtung (17) ein weiteres Schieberegister (26) aufweist, dessen Speicherkapazität gleich oder grösser als die doppelte übertragene Wortlänge ist und dessen Dateneingang mit dem Ausgang des Demodulators (13) verbunden ist, wobei halb so viele invertierende Exklusiv-Oder-Gatter (27) vorgesehen sind als der Speicherkapazität des Schieberegisters (26) entspricht, deren beide Eingänge jeweils an zwei im Abstand der Wortlänge voneinander distanzierte Ausgänge des Schieberegisters (26), jeweils um einen Speicherplatz verschoben, angeschlossen sind, und dass die Ausgänge der invertierenden Exklusiv-Oder-Gatter (27) mit den einen Eingängen von den invertierenden Exklusiv-Oder-Gattern (27) zugeordneten UND-Gattern (28) verbunden sind, deren andere Eingänge gemeinsam

an den Ausgang eines Frequenzteilers (36) angeschlossen sind, dessen Teilverhältnis gleich der Anzahl der Speicherplätze des Schieberegisters (26) für ein Wort ist, und dessen Eingang mit dem Takteingang des Schieberegisters (26) verbunden ist, wobei bei den Ausgängen der UND-Gatter (28) mit den einen Eingängen von in gleicher Anzahl vorhandenen R/S-Flip-Flops (29), deren andere Eingänge zu ihrem Setzen gemeinsam mit einem Ausgang einer Steuereinheit (30), die Ausgänge der R/S-Flip-Flops (29) mit den Eingängen eines Binärdecoders (31), ein Ausgang des Binärdecoders (31) mit einem Eingang der Steuereinheit (30), die anderen Ausgänge des Binärdecoders (31) mit den Eingängen eines ODER-Gatters (32), dessen Ausgang mit einem zweiten Eingang der Steuereinheit (30) und der Ausgang der Steuereinheit (30) mit mindestens einem Laufzeitglied (11) in Verbindung stehen.

Die Erfindung betrifft eine Datenübertragungseinrichtung mit einer Datenquelle, die über einen quellenseitigen Demultiplexer, zwei getrennte Übertragungswege und einen Multiplexer mit einer Datensenke in Verbindung steht, wobei über jeden der beiden Übertragungswege Daten mit einer Bitrate übertragen werden, die die Hälfte der Bitrate der von der Datenquelle gelieferten und von der Datensenke empfangenen Daten beträgt, und wobei der Datenfluss in Worte einer bestimmten gleichbleibenden Bitanzahl unterteilt und in jedem Wort an der gleichen Stelle ein Prüfbit angeordnet ist, das mit jedem Wort alternierend eine logische «0» oder eine logische «1» ist.

Bei der Übertragung eines seriellen, aus mehreren Worten hoher Bitzahl bestehenden Datenstromes ergeben sich zufolge der begrenzten Bandbreite des Übertragungskanals und einer Obergrenze der Übertragungsgeschwindigkeit der Sender und Empfänger Schwierigkeiten.

Zur Behebung dieser Schwierigkeit ist es bereits bekannt geworden, den seriellen Datenstrom in zwei Teildatenströme mit halber Übertragungsgeschwindigkeit umzusetzen, wobei diese Teildatenströme über eigene Kanäle voneinander getrennt übertragen und empfangsseitig wieder zum ursprünglichen Datenstrom zusammengesetzt werden. Hierfür kann quellenseitig ein Demultiplexer und senkenseitig ein Multiplexer vorgesehen werden, wobei vom quellenseitigen Demultiplexer die ungeradzahligen Bits des von der Datenquelle gelieferten Datenstroms der Bitfolge entsprechend dem ersten Übertragungsweg, die geradzahligen Bits dem zweiten Übertragungsweg zugeordnet werden und der Multiplexer die Bits des zweiten Übertragungsweges in Übereinstimmung mit der von der Datenquelle gesendeten Bitfolge in die Bitfolge des ersten Übertragungsweges einfügt. Es ist ersichtlich, dass ein ordnungsgemässes Ineinanderfügen der Bitfolgen der beiden Übertragungswege nur dann möglich ist, wenn die Laufzeiten auf beiden Übertragungswegen gleich sind. Da die Laufzeitunterschiede in den beiden Kanälen die Werte von mehreren Bit- oder Wortlängen annehmen können, können die beiden Teildatenströme empfangsseitig nicht mehr zum ursprünglichen Datenstrom zusammengesetzt werden.

Um das zu vermeiden, müssen in einen oder in beide Übertragungskanäle Laufzeitglieder eingeschaltet werden, mit denen Laufzeitdifferenzen ausgeglichen werden können. Das Erkennen solcher Laufzeitunterschiede ist jedoch mit Schwierigkeiten verbunden. Hiezu ist es bekannt geworden, von Zeit zu Zeit Prüfworte zu senden, deren ordnungsgemässer Empfang senkenseitig überprüft wird. Wird das Prüfwort nicht ordnungsgemäss empfangen, so liegen Laufzeit-

unterschiede vor. Dies erfordert jedoch umfangreiche Massnahmen, ist sehr zeitraubend und weist dennoch den Nachteil auf, dass Laufzeitänderungen zwischen der Übertragung des Prüfwortes senkenseitig nicht erkannt werden, so dass trotz scheinbar gleicher Laufzeit Wortverfälschungen auftreten können.

Das Ziel der Erfindung besteht nun darin, eine Datenübertragungseinrichtung zu schaffen, bei der Laufzeitänderungen sofort erkannt werden können.

Erfindungsgemäß ist bei einer Datenübertragungseinrichtung der eingangs genannten Art quellenseitig ein Modulator vorgesehen, an dessen einen Eingang die Datenquelle und an dessen anderen Eingang der Ausgang eines ersten Bitfolgenumsetzers angeschlossen ist, dessen Eingang mit dem Ausgang des Modulators und dem Eingang des Demultiplexers verbunden ist, wobei senkenseitig ein Demodulator vorgesehen ist, dessen erster Eingang einerseits mit dem Ausgang des Multiplexers und anderseits mit dem Eingang eines zweiten Bitfolgenumsetzers verbunden ist, dessen Ausgang mit dem zweiten Eingang des Demodulators in Verbindung steht, dessen Ausgang einerseits an die Datensenke, anderseits an den Eingang einer dem Erkennen von Laufzeitunterschieden zwischen den beiden Übertragungswegen dienenden Prüfvorrichtung angeschlossen ist, durch die mindestens ein Laufzeitglied gesteuert ist, das in einem der beiden Übertragungswege angeordnet ist.

Hiebei ist im quellenseitigen Datenstrom ein Kontrollbit enthalten, das nach jedem Wort wiederkehrt. Von einem Kontrollbit zum nächsten ändert sich der logische Zustand, für den sich abwechselnd eine logische «1» und eine logische «0» für das Kontrollblit in einer ununterbrochenen Kontrollbitfolge ergeben. Diese Kontrollbitfolge tritt senkenseitig nur dann auf, wenn die Laufzeiten auf beiden Übertragungswegen gleich sind. Ist das nicht der Fall, so ist senkenseitig der im Abstand einer Wortlänge erforderliche Wechsel des Kontrollbits zwischen einer logischen «1» und einer logischen «0» nicht feststellbar, so dass aus dem Fehlen einer solchen Kontrollbitfolge sofort auf eine Laufzeitdifferenz geschlossen werden kann. Hiezu ist die Prüfvorrichtung vorgesehen, die einen Alarm abgibt, wenn die richtige Kontrollbitfolge fehlt bzw. kein Kontrollbit im senkenseitigen Datenstrom vorhanden ist.

Das von der Prüfvorrichtung gelieferte Alarmsignal kann zur manuellen oder automatischen Nachstellung der Laufzeitglieder bzw. des Laufzeitgliedes zwecks Ausgleich der Laufzeitdifferenzen herangezogen werden, wobei die Laufzeitglieder so lange verstellt werden, bis die Prüfvorrichtung das Vorhandensein der Kontrollbitfolge anzeigt bzw. den Alarm ausschaltet. Dabei ist gewährleistet, dass bei Vorhandensein der Kontrollbitfolge auch die restlichen Daten auf beiden Übertragungswegen korrekt übertragen werden.

Vorteilhafterweise sind als Modulator und als Demodulator je ein Exklusiv-Oder-Gatter und als Bitfolgenumsetzer je ein Schieberegister vorgesehen, wobei quellenseitig der eine Eingang des den Modulator bildenden Exklusiv-Oder-Gatters mit der Datenquelle, der Ausgang des den Modulator bildenden Exklusiv-Oder-Gatters einerseits mit dem Eingang des Demultiplexers, anderseits mit dem Dateneingang des Schieberegisters, ein Ausgang des Schieberegisters unmittelbar bzw. zwei oder mehrere Ausgänge desselben über ein, bzw. mehrere in Kaskade geschaltete, Exklusiv-Oder-Gatter mit dem zweiten Eingang des den Modulator bildenden Exklusiv-Oder-Gatters in Verbindung stehen, und wobei senkenseitig der Ausgang des Multiplexers einerseits mit dem einen Eingang des den Demodulator bildenden Exklusiv-Oder-Gatters, anderseits mit dem Dateneingang des senkenseitigen Schieberegisters, ein Ausgang des Schieberegisters unmittelbar bzw. zwei oder mehrere Ausgänge desselben

über ein, bzw. mehrere in Kaskade geschaltete, Exklusiv-Oder-Gatter mit dem zweiten Eingang des den Demodulator bildenden Exklusiv-Oder-Gatters und dessen Ausgang mit der Datensenke in Verbindung stehen. Durch diese Massnahme ist ein besonders einfacher Aufbau des Modulators, des Demodulators und der Bitfolgenumsetzer erreichbar.

Zweckmässigerweise weist die Prüfvorrichtung ein weiteres Schieberegister auf, dessen Speicherkapazität gleich oder grösser als die doppelte übertragene Wortlänge ist und dessen Dateneingang mit dem Ausgang des Demodulators verbunden ist, wobei halb so viele invertierende Exklusiv-Oder-Gatter vorgesehen sind als der Speicherkapazität des Schieberegisters entspricht, deren beide Eingänge jeweils an zwei im Abstand der Wortlänge voneinander distanzierte Ausgänge des Schieberegisters, jeweils um einen Speicherplatz verschoben, angeschlossen sind, und wobei die Ausgänge der invertierenden Exklusiv-Oder-Gatter mit den einen Eingängen von den invertierenden Exklusiv-Oder-Gattern zugeordneten UND-Gattern verbunden sind, deren andere Eingänge gemeinsam an den Ausgang eines Frequenzteilers angeschlossen sind, dessen Teilverhältnis gleich der Anzahl der Speicherplätze des Schieberegisters für ein Wort ist und dessen Eingang mit dem Takteingang des Schieberegisters verbunden ist, wobei die Ausgänge der UND-Gatter mit den einen Eingängen von in gleicher Anzahl vorhandenen R/S-Flip-Flops, deren andere Eingänge zu ihrem Setzen gemeinsam mit einem Ausgang einer Steuereinheit, die Ausgänge der R/S-Flip-Flops mit den Eingängen eines Binärdecoders, ein Ausgang des Binärdecoders mit einem Eingang der Steuereinheit, die anderen Ausgänge des Binärdecoders mit den Eingängen eines ODER-Gatters, dessen Ausgang mit einem zweiten Eingang der Steuereinheit und der Ausgang der Steuereinheit mit mindestens einem Laufzeitglied in Verbindung stehen, womit eine Prüfvorrichtung erzielt wird, mit der in einfachster Weise Laufzeitunterschiede erkannt werden, die von Hand oder automatisch ausgeglichen werden können.

Die Erfindung ist anhand der Zeichnung, in der u.a. ein Ausführungsbeispiel dargestellt ist, näher erläutert.

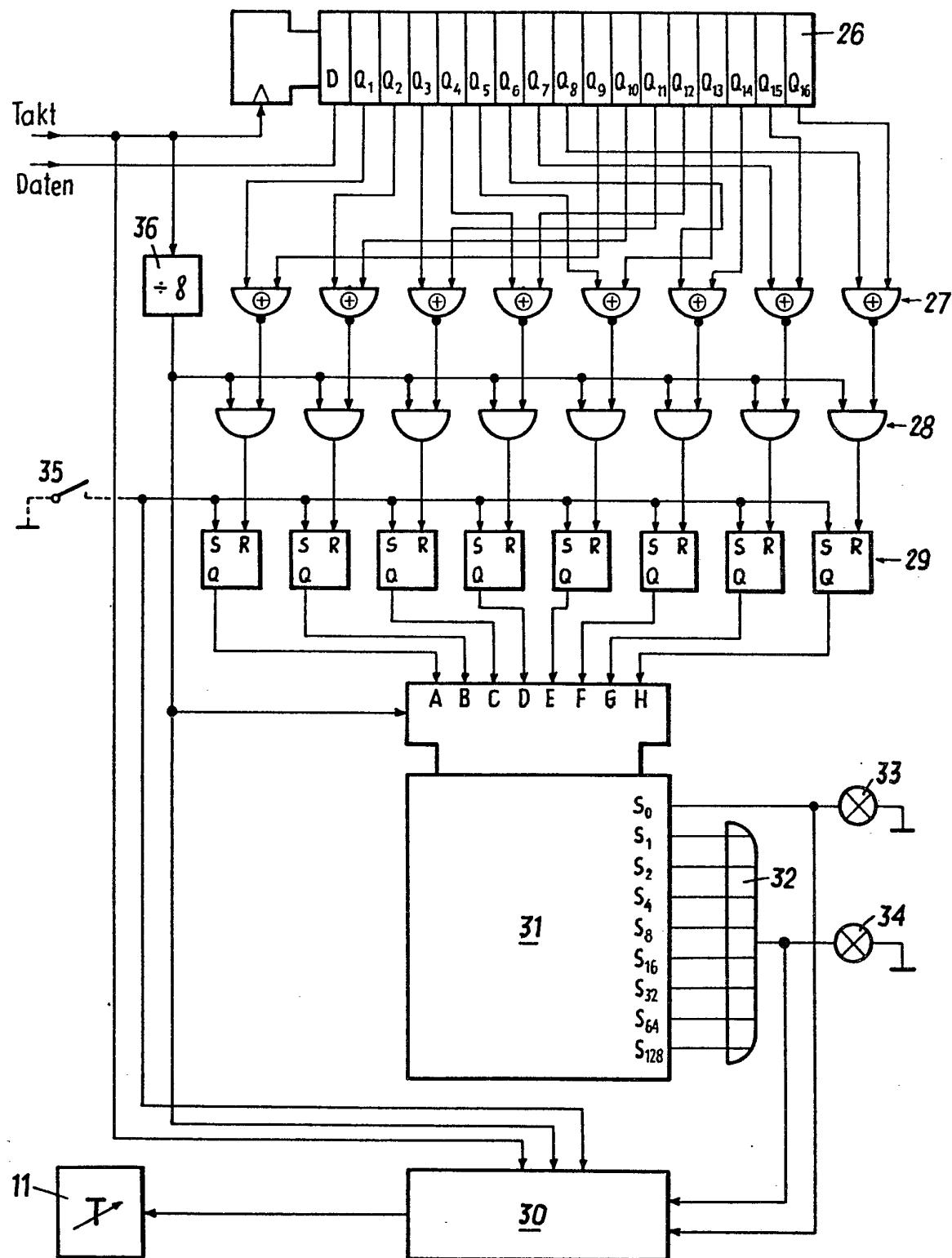

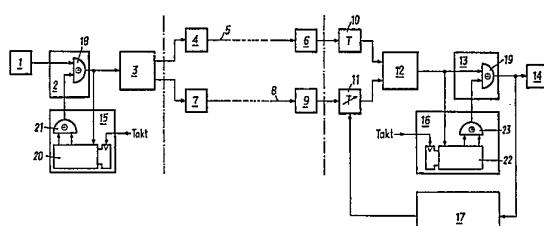

Fig. 1 zeigt schematisch das Prinzipschaltbild einer erfindungsgemässen Datenübertragungseinrichtung,

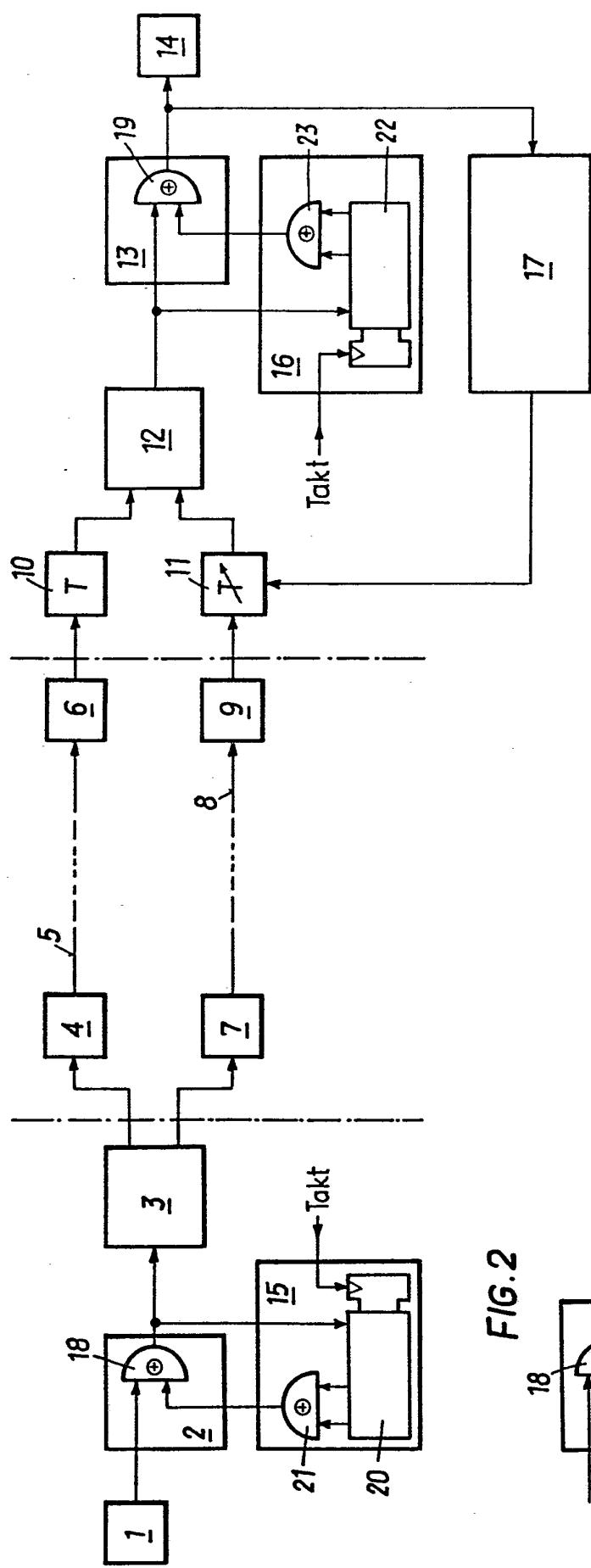

Fig. 2 einen Bitfolgenumsetzer mit in Kaskade geschalteten Exklusiv-Oder-Gattern und

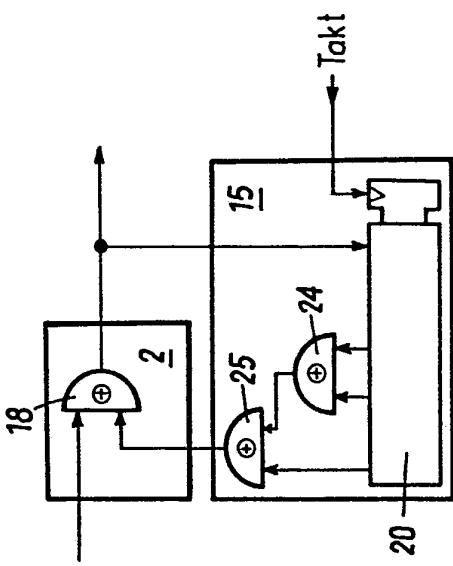

Fig. 3 das Prinzipschaltbild einer Prüfvorrichtung.

Bei dem in Fig. 1 dargestellten Ausführungsbeispiel steht quellenseitig eine Datenquelle 1 über einen Modulator 2 und einen Demultiplexer 3 mit zwei Übertragungswegen in Verbindung, wobei der eine Übertragungsweg in bekannter MODEM-Technik einen Sender 4, einen Übertragungskanal 5 und einen Empfänger 6, der zweite Übertragungsweg einen Sender 7, einen Übertragungskanal 8 und einen Empfänger 9 aufweist.

Senkenseitig sind die Ausgänge der Empfänger 6, 9 über je ein Laufzeitglied 10, 11 mit zwei Eingängen eines Multiplexers 12 verbunden, dessen Ausgang über einen Demodulator 13 mit einer Datensenke 14 in Verbindung steht. Sowohl quellenseitig als auch senkenseitig ist je ein Bitfolgenumsetzer 15, 16 vorgesehen, dessen Ausgang mit einem Eingang des Modulators 2 bzw. des Demodulators 13 und dessen Eingang an den Ausgang des Modulators 2 bzw. des Multiplexers 12 angeschlossen ist. An den Ausgang des Demodulators 13 ist senkenseitig eine Prüfvorrichtung 17 anschlossen, deren Ausgang mit dem Laufzeitglied 11 in Verbindung steht. Dabei ist das Laufzeitglied 10 auf einen festen Wert eingestellt, wohingegen das Laufzeitglied 11 von Hand aus oder durch eine Steuereinheit der Prüfvorrichtung automatisch verstellbar ist.

Es ist ersichtlich, dass die von der Datenquelle 1 gelieferte, Prüfbits enthaltende Datenfolge über den Modulator 2 durch den Bitfolgenumsetzer 15 moduliert dem Demultiplexer 3 zugeführt und erst die modulierte Bitfolge durch den Demultiplexer 3 in die über die beiden Übertragungswege zu übertragenden Teilfolgen aufgeteilt wird. Diese beiden Teilfolgen werden im Multiplexer 12 zu einer einzigen Bitfolge zusammengesetzt und über den Demodulator 13 durch den senkenseitigen Bitfolgenumsetzer 16 demoduliert der Datensenke 14 zugeführt.

Bei dem in Fig. 1 dargestellten Ausführungsbeispiel besteht der Modulator 2 und der Demodulator 13 aus je einem Exklusiv-Oder-Gatter 18, 19. Der eine Eingang des quellenseitigen Exklusiv-Oder-Gatters 18 ist an die Datenquelle 1, der Ausgang des Exklusiv-Oder-Gatters 18 einerseits an den Eingang des Demultiplexers 3, anderseits an den Dateneingang eines Schieberegisters 20 angeschlossen. Zwei Ausgänge des Schieberegisters 20 sind mit den Eingängen eines Exklusiv-Oder-Gatters 21 und dessen Ausgang mit dem zweiten Eingang des Modulator 2 bildenden Exklusiv-Oder-Gatters 18 verbunden. Das Schieberegister 20 und das Exklusiv-Oder-Gatter 21 bilden zusammen den Bitfolgenumsetzer 15. Ebenso ist senkenseitig der eine Eingang des dem Demodulator 13 bildenden Exklusiv-Oder-Gatters 19 an den Ausgang des Multiplexers 12 angeschlossen, an dem auch der Dateneingang eines Schieberegisters 22 liegt. Zwei Ausgänge des Schieberegisters 22 führen zu den beiden Eingängen eines Exklusiv-Oder-Gatters 23, dessen Ausgang an den zweiten Eingang des demodulator 13 bildenden Exklusiv-Oder-Gatters 19 angeschlossen ist, dessen Ausgang mit der Datensenke 14 verbunden ist. Das Schieberegister 22 und das Exklusiv-Oder-Gatter 23 bilden den senkenseitigen Bitfolgenumsetzer 16.

Es ist ersichtlich, dass die am Ausgang des Exklusiv-Oder-Gatters 18 auftretende Bitfolge nicht nur den Demultiplexer 3 und über diesen den beiden Übertragungswegen zugeführt wird, sondern auch dem Schieberegister 20. In diesem ist somit jeweils eine dem Ausgang des Exklusiv-Oder-Gatters 18 entnommene Bitfolge gespeichert, die mit jedem am Ausgang des Exklusiv-Oder-Gatters 18 auftretenden Bit um einen Speicherplatz verschoben wird. Der Inhalt zweier Speicherplätze des Schieberegisters 20, beispielsweise des letzten und vorletzten Speicherplatzes, wird den Eingängen des Exklusiv-Oder-Gatters 21 zugeführt. Befindet sich an diesen beiden Speicherplätzen eine logische «0» oder eine logische «1», so liegt am Ausgang des Exklusiv-Oder-Gatters 21 eine logische «0». Weist der eine Speicherplatz eine logische «0» und der andere Speicherplatz eine logische «1» auf, so liegt am Ausgang des Exklusiv-Oder-Gatters 21 eine logische «1».

Liefert die Datenquelle 1 an den einen Eingang des Exklusiv-Oder-Gatters 18 eine logische «0» und das Exklusiv-Oder-Gatter 21 an den anderen Eingang des Exklusiv-Oder-Gatters 18 eine logische «1», so liegt am Ausgang des Exklusiv-Oder-Gatters 18 eine logische «1». Die von der Datenquelle 1 gelieferte logische «0» wird somit in eine am Eingang des Demultiplexers 3 und damit auch am Dateneingang des Schieberegisters 20 liegende logische «1» umgewandelt. Eine logische «0» bzw. eine logische «1» der von der Datenquelle 1 gelieferten Bitfolge wird nur dann an den Eingängen des Demultiplexers 3 und des Schieberegisters 20 beibehalten, wenn am Ausgang des Exklusiv-Oder-Gatters 21 eine logische «0» liegt, was aber vom Inhalt der Speicherplätze des Schieberegisters 20 abhängt. Die von der Datenquelle 1 gelieferte Bitfolge tritt somit aus dem Modulator 2 durch den Bitfolgenumsetzer 15 moduliert aus. Von der Modulation wird dabei selbstverständlich nicht nur die

Bitfolge der zu übertragenden Worte, sondern auch die Folge der Prüfbits erfasst. Erst diese veränderte Bitfolge wird durch den Demultiplexer 3 bitweise abwechselnd den beiden Übertragungskanälen 5, 8 zugeführt.

- 5 Die senkenseitige Demodulation erfolgt in analoger Weise, so dass bei gleichen Laufzeiten der Datensenke 14 die gleiche Bitfolge mit den in ihr enthaltenen Prüfbits zugeführt wird, die quellenseitig von der Datenquelle 1 geliefert worden ist. Die an die Datensenke 14 gelieferten Daten ergeben sich aus 10 den dem Multiplexer 12 entnommenen Daten, die in die erste Stufe des Schieberegisters 22 eingeschoben werden, durch eine Exklusiv-Oder-Verknüpfung verknüpft mit den zwischengespeicherten, zeitlich vorher eingetroffenen, dem Multiplexer 12 entnommenen Daten, die ebenfalls durch 15 eine Exklusiv-Oder-Verknüpfung verknüpft sind. Sind die Generatorpolynome des Modulators und des Demodulators gleichartig, so werden zuerst die Übertragungsdaten quellenseitig durch das Generatorpolynom dividiert. Senkenseitig werden diese modulierten Daten wieder mit dem Generatorpolynom multipliziert. Treten keine Laufzeitunterschiede 20 auf, so sind die von der Datenquelle 1 gelieferten Daten mit den von der Datensenke 14 empfangenen Daten identisch. Das gilt selbstverständlich auch für die Folge der Prüfbits, die in jedem Wort an der gleichen Stelle, beispielsweise am 25 Anfang jedes Wortes angeordnet sind und die mit jedem Wort alternierend eine logische «1» oder eine logische «0» sind. Diese Bitfolge der Prüfbits ist bei ungleichen Laufzeiten auf den beiden Übertragungswegen nicht vorhanden. Die Prüfvorrichtung 17 prüft, ob die Bitfolge der Prüfbits vorhanden ist oder nicht. Ist sie vorhanden, so ist auch die Übertragung der Worte korrekt. Ist sie nicht vorhanden, so zeigt dies die Prüfvorrichtung 17 an bzw. es verändert die Prüfvorrichtung das Laufzeitglied 11 so lange, bis die Bitfolge der Prüfbits vorhanden ist.

- 30 35 Die Modulation der von der Datenquelle 1 bzw. die Demodulation der von dem Multiplexer 12 gelieferten Bitfolge muss selbstverständlich nicht durch Abgriff zweier Speicherplätze der Schieberegister 20, 22 erfolgen. Es können auch die Exklusiv-Oder-Gatter 21, 23 fortgelassen und ein Ausgang 40 der Schieberegister 20, 22 unmittelbar den einen Eingängen der Exklusiv-Oder-Gatter 18, 19 zugeführt werden.

- 45 Es können auch mehrere Speicherplätze des Schieberegisters 20 und in analoger Weise auch das Schieberegister 22 herangezogen werden, wie dies Fig. 2 zeigt. Bei dem in Fig. 2 dargestellten Ausführungsbeispiel des Bitfolgenumsetzers 15 sind zwei Ausgänge des Schieberegisters 20 an die beiden Eingänge eines Exklusiv-Oder-Gatters 24 geführt, dessen Ausgang an dem einen Eingang eines Exklusiv-Oder-Gatters 25 liegt, an dessen zweiten Eingang ein dritter Ausgang 50 des Schieberegisters 20 angeschlossen ist. Der Ausgang des Exklusiv-Oder-Gatters 25 bildet den Ausgang des Bitfolgenumsetzers 15, der an dem einen Eingang des Exklusiv-Oder-Gatters 18 des Modulators 2 liegt. Die Exklusiv-Oder-Gatter 24, 25 sind in Kaskade geschaltet. Durch eine solche 55 Kaskadenschaltung von Exklusiv-Oder-Gattern können auch mehrere Abgriffe am Schieberegister 20 herangezogen werden. Analoges gilt auch für den senkenseitigen Bitfolgenumsetzer 16.

Als Prüfvorrichtung kann an sich jede bekannte elektronische Anordnung herangezogen werden. In Fig. 3 ist eine besonders vorteilhafte Schaltung einer Prüfvorrichtung dargestellt. Bei dieser in Fig. 3 dargestellten Prüfvorrichtung ist ein Schieberegister 26 vorgesehen, dessen Speicherkapazität gleich oder grösser ist als die doppelt übertragene Wortlänge. 60 Der Dateneingang D ist dabei mit dem Ausgang des Demodulators 13 (Fig. 1) verbunden. Ferner sind halb so viele invertierende Exklusiv-Oder-Gatter 27 als der Speicherkapazität des Schieberegisters 26 entspricht, vorgesehen. Im dar-

gestellten Ausführungsbeispiel sind sechzehn Speicherplätze und somit acht invertierende Exklusiv-Oder-Gatter 27 vorgesehen. Die beiden Eingänge der invertierenden Exklusiv-Oder-Gatter 27 sind jeweils an zwei im Abstand der Wortlänge voneinander distanzierte Ausgänge des Schieberegisters 26 jeweils um einen Speicherplatz verschoben angegeschlossen. Das erste invertierende Exklusiv-Oder-Gatter 27 liegt an den Ausgängen Q<sub>1</sub> und Q<sub>2</sub> des Schieberegisters 26, das nächste an den Ausgängen Q<sub>2</sub> und Q<sub>10</sub> und so fort. Das letzte Exklusiv-Oder-Gatter 27 liegt an den Ausgängen Q<sub>8</sub> und Q<sub>16</sub> des Schieberegisters 26.

Die Ausgänge der invertierenden Exklusiv-Oder-Gatter 27 sind mit den einen Eingängen von UND-Gattern 28 verbunden, deren Zahl gleich der Zahl der invertierenden Exklusiv-Oder-Gatter 27 ist. Die anderen Eingänge der UND-Gatter 28 sind an den Ausgang eines Frequenzteilers 36 angeschlossen, dessen Eingang mit dem Takteingang des Schieberegisters 26 verbunden ist. Das Teilverhältnis des Frequenzteilers 36 ist gleich der Anzahl der Speicherplätze des Schieberegisters 26 für ein Wort, also bei dem dargestellten Ausführungsbeispiel gleich 1:8. Die Ausgänge der UND-Gatter 28 sind mit den R-Eingängen von in gleicher Anzahl vorhandenen R/S-Flip-Flops 29 verbunden, deren S-Eingänge gemeinsam mit einem Ausgang einer Steuereinheit 30 verbunden sind, durch die die R/S-Flip-Flops 29 gesetzt werden können. Die Q-Ausgänge der R/S-Flip-Flops 29 liegen an den Eingängen eines 8 zu 128 Binärdecoders 31, der durch zwei 4 zu 16 Binärdecoder bei entsprechender Ausbildung der Ausgangsschaltung realisiert sein kann. Die Ausgänge S<sub>1</sub> bis S<sub>128</sub> des Binärdecoders 31 führen an die Eingänge einer ODER-Schaltung 32, deren Ausgang an einem Eingang der Steuereinheit 30 liegt. Der erste Ausgang S<sub>0</sub> des Binärdecoders 31 ist unmittelbar an einen Eingang der Steuereinheit 30 geführt, deren Ausgang mit dem verstellbaren Laufzeitglied 11 (Fig. 1) in Verbindung steht. Darüber hinaus ist die Steuereinheit 30 an den Takteingang des Schieberegisters 26 und an den Frequenzteiler 36 angeschlossen. Bei dem in Fig. 3 dargestellten Ausführungsbeispiel der Prüfvorrichtung ist der Ausgang S<sub>0</sub> des Binärdecoders 31 und der Ausgang des ODER-Gatters 32 mit je einer Alarmeinrichtung verbunden, die als Glühlämpchen 33, 34 symbolisiert sind.

Soll durch Tastenbetätigung nur von Zeit zu Zeit eine Überprüfung erfolgen, ob gleiche Laufzeiten in den beiden Übertragungswegen vorliegen, so erübrigt sich die Steuereinheit 30. An deren Stelle kann eine Taste 35 treten, wie dies in Fig. 3 strichliert gezeichnet ist. Die Einregelung der Laufzeitübereinstimmung kann in diesem Falle durch händische Betätigung des Laufzeitgliedes 11 erfolgen. Die Taste 35 kann natürlich auch bei Vorhandensein einer Steuereinheit 30 vorgesehen werden. Die Steuereinheit 30 kann beliebiger

bekannter Art sein. Gesteuert durch den am Takteingang des Schieberegisters 26, an den ein Eingang der Steuereinheit 30 angeschlossen ist, liegenden Takt und das Ausgangssignal des Frequenzteilers 36 hat die Steuereinheit 30 die Aufgabe, das Laufzeitglied 11 zu verändern, wenn durch sie über die beiden mit dem Binärdecoder 31 in Verbindung stehenden Eingänge das Fehlen des Prüfbits in der am Eingang der Datensenke 14 (Fig. 1) auftretenden Bitfolge festgestellt wird.

In das Schieberegister 26 werden laufend die am Eingang 10 der Datensenke 14, also am Ausgang des Exklusiv-Oder-Gatters 19 des Demodulators 13 auftretenden Bitfolgen eingeschrieben. Die Länge des Schieberegisters 26 ist gleich zwei Wortlängen, so dass bei vollgeschriebenem Schieberegister 26 und ordnungsgemässem Empfang im Schieberegister 15 26 zu jedem Zeitpunkt zwei Prüfbits enthalten sind.

Werden nun durch die Steuereinheit 30 bzw. durch Betätigen der Taste 35 die R/S-Flip-Flops 29 gesetzt, so werden über die invertierenden Exklusiv-Oder-Gatter 27 und die UND-Gatter 28 mit dem Takt, der dem Teilverhältnis des Frequenzteilers 36 entspricht, jene R/S-Flip-Flops 29 rückgesetzt, bei denen im Abstand eines Wortes Gleichheit der Bits im Schieberegister 26 vorliegt. Solange kein Prüfbit gefunden ist, liegt am Ausgang S<sub>0</sub> des Binärdecoders 31 eine logische «1», was die Signaleinrichtung 33 beispielsweise durch Aufleuchten anzeigen. Wird ein Prüfbit gefunden, so liegt am Ausgang des ODER-Gatters 32 eine logische «1», so dass das Lämpchen 34 aufleuchtet, weil dasjenige R/S-Flip-Flop 29, das mit zwei Speicherplätzen ungleicher Belegung des Schieberegisters 26 in Verbindung steht, nicht rückgesetzt wird.

Dies hat seinen Grund darin, dass der logische Zustand eines Prüfbits immer eine Folge 1-0-1-0-1 einnimmt. Solange mehr als ein R/S-Flip-Flop 29 nicht rückgesetzt ist, wird durch das Lämpchen 33 angezeigt und der Steuereinheit 30 gemeldet, dass noch kein Prüfbit gefunden ist, demzufolge 35 das Laufzeitglied 11 durch die Steuereinheit 30 verstellt wird bzw. von Hand aus zu verstellen ist. Ist zu einem bestimmten Zeitpunkt nur mehr ein einziges R/S-Flip-Flop 29 gesetzt, also das Prüfbit gefunden, so wird dies über den Binärdecoder 31 und das zugehörige ODER-Gatter 32 erkannt, der 40 Steuereinheit 30 mitgeteilt und das Lämpchen 34 zum Leuchten gebracht, worauf von Hand aus oder automatisch durch die Steuereinheit 30 die Tätigkeit des Laufzeitgliedes 11 beendet wird.

Ist das Prüfbit fehlerhaft bzw. nicht vorhanden, so wird 45 dies durch Aufleuchten des Lämpchens 33 angezeigt und der mit dem Laufzeitglied 11 in Verbindung stehende Ausgang der Steuereinheit 30 aktiviert.

Die Erfindung ist nicht auf das dargestellte Ausführungsbeispiel beschränkt; so können als Modulator, Demodulator und Bitfolgenumsetzer auch andere bekannte Anordnungen gewählt werden.

FIG. 1

FIG. 2

FIG. 3