(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5004791号

(P5004791)

(45) 発行日 平成24年8月22日(2012.8.22)

(24) 登録日 平成24年6月1日(2012.6.1)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 21/76  | (2006.01) | HO1L 21/76 | L    |

| HO1L 21/762 | (2006.01) | HO1L 21/76 | D    |

| HO1L 27/12  | (2006.01) | HO1L 27/12 | F    |

| HO1L 29/786 | (2006.01) | HO1L 27/12 | L    |

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 613A |

請求項の数 9 (全 9 頁) 最終頁に続く

(21) 出願番号 特願2007-516538 (P2007-516538)

(86) (22) 出願日 平成17年6月6日 (2005.6.6)

(65) 公表番号 特表2008-503872 (P2008-503872A)

(43) 公表日 平成20年2月7日 (2008.2.7)

(86) 國際出願番号 PCT/US2005/019815

(87) 國際公開番号 WO2006/009613

(87) 國際公開日 平成18年1月26日 (2006.1.26)

審査請求日 平成20年4月24日 (2008.4.24)

(31) 優先権主張番号 10/710,060

(32) 優先日 平成16年6月16日 (2004.6.16)

(33) 優先権主張国 米国(US)

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100108501

弁理士 上野 剛史

(74) 代理人 100112690

弁理士 太佐 種一

(74) 代理人 100091568

弁理士 市位 嘉宏

最終頁に続く

(54) 【発明の名称】 SOI およびバルク・シリコン領域を含む半導体デバイス内のSTI形成

## (57) 【特許請求の範囲】

## 【請求項1】

シリコン・オン・インシユレータ(SOI)領域およびバルク・シリコン領域を含むデバイス内にシリコン・トレンチ分離部(STI)を形成する方法であって、

STIマスクを使用して最上のシリコン層の上面で停止するように、前記最上のシリコン層の上層をエッチングするステップと、

バルク・シリコン領域において当該バルク・シリコン領域に形成されるSTIに必要な深さまでエッチングし且つSOI領域の埋め込み絶縁体で停止する時限エッチングを実行するステップと、

SOI領域の前記埋め込み絶縁体を貫通してエッチングするステップと、

STIを形成するためにSTI材料を堆積するステップと、

を含む方法。

## 【請求項2】

前記バルク・シリコン領域に形成されるSTIに必要な深さが、前記SOI領域のシリコン層および前記埋め込み絶縁体の厚さと少なくとも同じ厚さである、請求項1に記載の方法。

## 【請求項3】

さらに、ハードマスク層を堆積し、パターン化し、エッチングして前記STIマスクを形成することによって、前記STIマスクを形成するステップを含む、請求項1に記載の方法。

10

20

**【請求項 4】**

前記 S T I マスクのエッチング・ステップが、前記ハードマスク層と、任意の反射防止コーティング( A R C )およびパッド層のうち少なくとも 1 つとを貫通してエッチングすることを含む、請求項 3 に記載の方法。

**【請求項 5】**

前記時限エッ칭のステップが、前記埋め込み絶縁体の材料に対して選択的であるエッチングレシピを使用することを含む、請求項 1 に記載の方法。

**【請求項 6】**

前記埋め込み絶縁体のエッチング・ステップが、前記 S T I マスクを除去することを含む、請求項 1 に記載の方法。

10

**【請求項 7】**

さらに、最上面の上の前記 S T I 材料を除去するために研磨するステップと、パッド層を除去するステップとを含む、請求項 1 に記載の方法。

**【請求項 8】**

シリコン・オン・インシュレータ( S O I )領域とバルク・シリコン領域が混合したデバイスのシリコン・トレンチ分離部( S T I )をエッチングする方法であって、

S T I マスクを使用して最上のシリコン層の上面で停止するように、前記最上のシリコン層の上層をエッチングするステップと、

バルク・シリコン領域において当該バルク・シリコン領域に形成される S T I に必要な深さまでエッチングし且つ S O I 領域の埋め込み絶縁体で停止する時限エッチングを実行するステップと、

20

S O I 領域の前記埋め込み絶縁体を貫通してエッチングするステップと、

を含む方法。

**【請求項 9】**

シリコン・オン・インシュレータ( S O I )領域およびバルク・シリコン領域を含むデバイス内にシリコン・トレンチ分離部( S T I )を形成する方法であって、

S T I マスクを準備するステップと、

前記 S O I 領域および前記バルク・シリコン領域内に前記 S T I を同時に形成するステップと、

を含み、前記形成ステップが、

30

前記 S T I マスクを使用して最上のシリコン層の上面で停止するように、前記最上のシリコン層の上層をエッチングするステップと、

前記バルク・シリコン領域において当該バルク・シリコン領域に形成される S T I に必要な深さまでエッチングし、前記 S O I 領域の埋め込み絶縁体上で停止する時限エッチングを実行するステップと、

前記 S O I 領域の前記埋め込み絶縁体を貫通してエッチングするステップと、

前記 S T I を形成するために S T I 材料を堆積させるステップと

を含む、方法。

**【発明の詳細な説明】****【技術分野】**

40

**【0 0 0 1】**

本発明は一般に浅いトレンチ分離部( shallow trench isolations、 S T I )に関し、特にシリコン・オン・インシュレータ( S O I )およびバルク・シリコン領域を含む半導体デバイス内に S T I を形成する方法に関する。

**【背景技術】****【0 0 0 2】**

技術がますます複雑になるにつれ、より多くの機能を有する集積回路( I C )カスタマ(customer)に対する需要が増大している。最適設計を有する I C を提供するために、エンハンスト・ダイナミック・ランダム・アクセス・メモリ( e D R A M )または無線周波数( R F )用途のような追加の特徴がある高性能相補型金属酸化膜半導体( C M O S )デバ

50

イスが必要である。これらの特徴全てを提供することに関して生じる問題は、各特徴が異なる条件で最適化されることである。例えば、高性能CMOSはシリコン・オン・インシユレータ(SOI)ウェハ上で完成することができるが、RFおよびeDRAMはバルク・シリコンで構築することができる。

#### 【0003】

最良の「バルク技術」を最良の「SOI技術」と統合する目的でパターン化されたSOI(一部がバルクで一部がSOI)を形成する従来の技術がある。このアプローチを使用するこのような技術の一つは、SOIにeDRAMを統合することである。この場合、eDRAMアレイ・ブロックがバルク・シリコン内に構築され、ロジックがSOI内に構築される。このアプローチを使用可能な別の技術は、新興の65nmプロセスSOI技術である。65nmプロセスのステージにある基板は、SOI上のNfetsとバルク・シリコン内のPfetsとから構成される。このプロセス技術は、ハイブリッド・オリエンテーション・テクノロジーつまり「HOT」と呼ばれる。10

#### 【0004】

上述した両例で直面する問題の一つは、製造者がSOI領域とバルク領域の両方の能動的(アクティブ)拡散の分離を行わなければならないことである。この分離を提供する従来の技術は、2つの別個の浅いトレンチ・プロセスを必要とする。バルク・シリコンのためのプロセスとSOIのためのプロセスである。上述したプロセスは非常に複雑で、費用効果が低い。特に、パターン化したSOI対バルク・シリコンに関して浅いトレンチ分離(STI)処理には幾つかの問題がある。20

#### 【0005】

第一の問題は、STIのエッティングの深さに関連する。SOI領域では、STIエッティングの深さはシリコンの厚さであり、エッティングは埋め込み絶縁体の頂部で停止し、これは通常深さ1000未満である。しかし、バルク・プロセスでは、STIの深さが現状のSOIの厚さよりもはるかに深く、例えば通常3500以上である。SOIをパターン化する場合は、バルク・シリコンに対してSTIエッティング深さを選択する幾つかの選択肢がある。第一の選択肢は、SOI STIエッティング深さを使用することであり、これはバルク領域内に十分な分離部を与えない。第二の選択肢はバルクSTIエッティング深さを使用することであり、これはSOI領域で実行するには非常に困難なエッティングである。第三の選択肢は、SOI領域のSTIエッティング深さをSOI STIプロセスの通常の深さと等しくし、バルク・シリコン領域の深さを通常のバルクSTI深さと等しくすることである。しかし、このプロセスは余分なフォトレジスト層を必要とし、STI平坦化に伴う問題を引き起こす可能性がある。30

#### 【0006】

パターン化したSOIのSTI処理に伴う第二の問題は、酸素注入分離(Separation by Implantation of Oxygen、SIMOX)プロセスを使用して生成したウェハに固有の特定のプロセス欠陥から生じる。パターン化したSIMOXプロセスでは、最初にバルク・ウェハに酸化物のハードマスク・アイランドを生成し、ウェハ領域を高い線量(ドーズ量)で高エネルギーの酸素注入(implant)から保護する。埋め込み酸化物(buried oxide、BOX)の形成中に、高温酸化手順を通してBOXの縁部(つまりSOIバルク境界にあるBOX)がSOIフィールド領域のBOXより厚くなる。多くの場合、SOIバルク領域の境界に沿って、埋め込み酸化物が実際にウェハの表面を破損させる。SIMOXウェハ上に成長した酸化物を除去するために酸化物のエッティングが必要であるので、埋め込み酸化物が表面を破損させたこれらの領域もエッティングされ、ウェハ表面に小さいディボット(divot)が残る。次に、ウェハにはパッド酸化物およびパッド・シリコン窒化物(SiN)の堆積が行われる。SiN堆積プロセスでは、これらの穴が窒化物で充填され、それらがSTIエッティング・プロセス中にエッティングされない場合には、STI処理の大部分を通してパターン化されたウェハ上に残ることになる。一旦STIが充填され且つ平坦化されたら、パッドSiNはウェハ表面から剥ぎ取られる必要がある。表面付近に形成されてSiNが詰め込まれたディボットは、エッティング後にSiNがなくなり、次の堆積プロセ4050

スまで材料、つまりゲート・ポリシリコンがない。ポリシリコンは、ドーピングまたはシリサイドへの変換によって電気的に活性化することができるので、ポリシリコンで充填されたディボットがデバイスの短絡を引き起こすことがある。この問題は、初期のS O I e D R A M ハードウェアで観察されている。したがって、パターン化されたS I M O X ウエハは、表面下のディボットにある残留窒化物を完全に除去するプロセスを組み込まねばならない。

【発明の開示】

【発明が解決しようとする課題】

【0007】

以上に鑑みて、当技術分野では関連技術の問題に対し対処するプロセスが必要となつて10

いる。

【課題を解決するための手段】

【0008】

本発明は、シリコン・オン・インシュレータ(SOI)領域およびバルク・シリコン領域にシリコン・トレンチ分離部(silicon trench isolation)を形成またはエッティングする方法、および該方法により形成された半導体デバイスを含む。STIマスクを使用して最上のシリコン層をエッティングし、バルク・シリコン領域を所望の深さまでエッティングし且つSOI領域の埋め込み絶縁体で停止する時限エッティングを実行し、SOI領域の埋め込み絶縁体を貫通してエッティングすることにより、STIは、SOI領域およびバルク・シリコン領域にて同時にエッティングされ得る。このプロセスの埋め込み絶縁体エッティングは20

、ハードマスク除去ステップの一部として、それほど複雑でなく実行することができる。さらに、バルク領域とSOI領域の両方に同じ深さを選択することにより、その後のCMPプロセスでの問題が回避される。本発明は、シリコン窒化物の残留物が存在し得るSOI領域とバルク領域との境界において不要なものを取り除く。

【0009】

本発明の第一の態様は、シリコン・オン・インシュレータ(SOI)領域およびバルク・シリコン領域を含むデバイス内にシリコン・トレンチ分離部(STI)を形成する方法を含む。この方法は、STIマスクを使用して最上のシリコン層をエッティングするステップと、バルク・シリコン領域を所望の深さまでエッティングし且つSOI領域の埋め込み絶縁体で停止する時限エッティング(timed etch)を実行するステップと、SOI領域の埋め込み絶縁体を貫通してエッティングするステップと、STIを形成するためにSTI材料を堆積するステップとを含む。30

【0010】

本発明の第二の態様は、シリコン・オン・インシュレータ(SOI)領域とバルク・シリコン領域が混合したデバイス内でシリコン・トレンチ分離部(STI)をエッティングする方法を含む。この方法は、STIマスクを使用して最上のシリコン層をエッティングするステップと、バルク・シリコン領域を所望の深さまでエッティングし且つSOI領域の埋め込み絶縁体で停止する時限エッティングを実行するステップと、SOI領域の埋め込み絶縁体を貫通してエッティングするステップとを含む。

【0011】

本発明の第三の態様は、シリコン・オン・インシュレータ(SOI)領域およびバルク・シリコン領域を含む半導体デバイスを含む。この半導体デバイスは、SOI領域のシリコン層および埋め込み絶縁体の厚さと実質的に等しい深さまで延在するシリコン・トレンチ分離部(STI)を含む。40

【0012】

本発明の第四の態様は、シリコン・オン・インシュレータ(SOI)領域およびバルク・シリコン領域を含むデバイス内にシリコン・トレンチ分離部(STI)を形成する方法を含む。この方法は、STIマスクを準備するステップと、SOI領域およびバルク・シリコン領域内にSTIを同時に形成するステップと、を含む。

【0013】

10

20

30

40

50

本発明の以上およびその他の特徴は、本発明の実施形態に関する以下のさらに特定の説明から明白になるであろう。

【0014】

本発明の実施形態を、図面を参照しながら詳細に説明し、ここで同様の参照番号は同様の要素を指す。

【発明を実施するための最良の形態】

【0015】

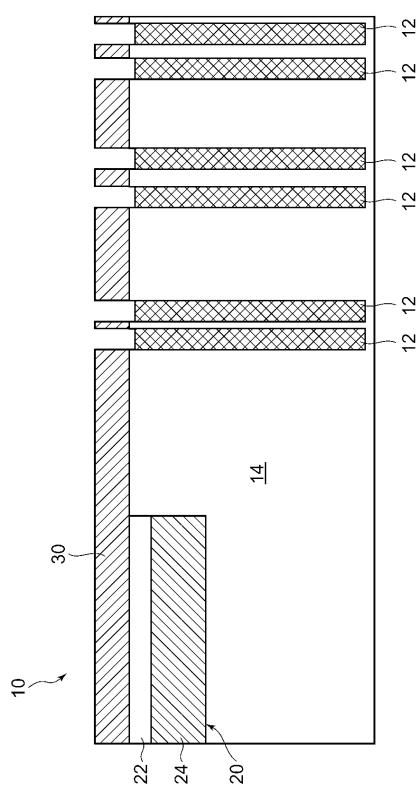

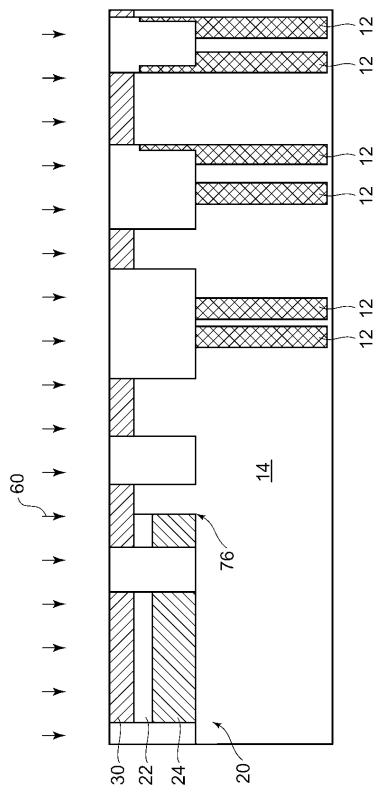

添付図面を参照すると、図1は、バルク・シリコン領域14内に深いトレンチ12を形成した後で、シリコン・トレンチ分離部(STI)ハードマスクを堆積する前の、典型的なウェハ10を示す断面図である。ウェハ10は、埋め込み絶縁体24上にシリコン層22を含むシリコン・オン・インシュレータ(SOI)領域20を含む。

10

【0016】

一実施形態では、埋め込み絶縁体24の材料は二酸化シリコンであるが、他の材料も使用することができる。例示のためにのみ、SOI領域20のシリコン層22は、約700の厚さを有してよく、STI領域20の埋め込み絶縁体24は約1350の厚さを有してよい。パッド層30は、約80の二酸化シリコン(一律の縮尺で図示されていない)および約1200の窒化シリコンを含む厚さを有してよい。しかし、認識されるべきは、本発明の教示は図1の特定の深さまたは初期の構造的開始ポイントに制限されないことである。

20

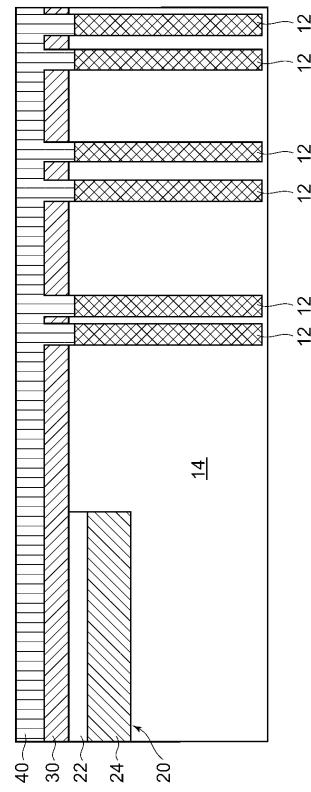

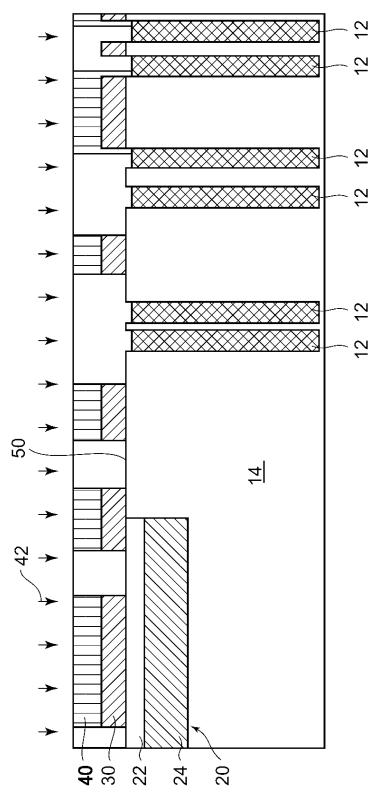

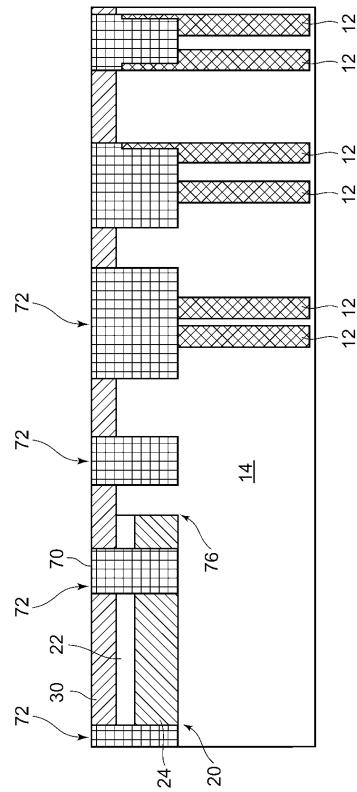

【0017】

図2及び図3に示すように、STIマスクを設ける。特に、図2に示すように、ハードマスク層40をパッド層30の上に、および任意の開口内に堆積する。ハードマスク層40の材料は、埋め込み絶縁体24とほぼ同じエッティングの特徴を有する。一実施形態では、ハードマスク層40は、約1000のテトラエチルオルトシリケート(TEOS)またはホウ素をドーピングしたシリケート・ガラス(BSG)を含む。次に図3に示すように、ハードマスク層40をパターン化し、エッティング42を実行して、STIマスク46を形成する。エッティング42は、ハードマスク層40と、反射防止コーティング層(anti reflective coating、ARC)(図示せず)およびパッド層30のうち少なくとも一方とを貫通して延在し、最上のシリコン層50、つまりバルク・シリコン領域14の上面およびSOI領域20のシリコン層22で停止する。

30

【0018】

次のステップでは、図4に示すように、バルク・シリコン領域14の所望の深さ(D)までエッティングし、且つSOI領域20の埋め込み絶縁体22の最上の表面52で停止する時限(timing)エッティング50を実行する。一実施形態では、バルク・シリコン領域14の所望の深さD(したがってその後に形成されるSTI)は、SOI領域20の厚さと少なくとも同じ深さまで、つまりシリコン層22および埋め込み絶縁体24の深さと少なくとも同じ深さまで延在する。以上の例示的深さに基づき、所望の深さは、例えば約2050、つまりシリコン層22の700に埋め込み絶縁体24の1350を加えた値でよい。一実施形態では、時限エッティング50は反応性イオン・エッティング・プロセスでよいが、他のエッティング・プロセスを実行してもよい。いかなる場合も、時限エッティング50は、埋め込み絶縁体24の材料、例えば二酸化シリコン、に対して選択的であり、シリコン層22と、シリコン層22の下にあり得る任意の窒化シリコンの両方をエッティングし、埋め込み絶縁体24がSOI形成プロセス中に表面に出るようにする。このステップは、シリコン窒化物の残留物が存在し得るSOI領域20とバルク・シリコン領域14の境界76において不要なものを取り除く(clean)。

40

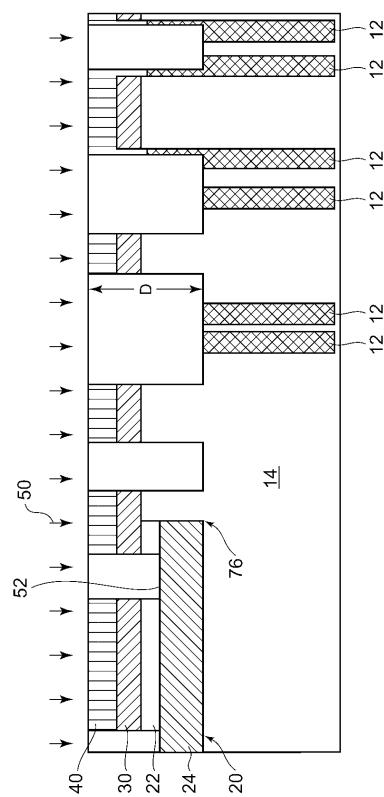

【0019】

図5を参照すると、次のステップは、SOI領域20の埋め込み絶縁体24を貫通してエッティング60を実行することを含む。好ましい実施形態では、エッティング60はハードマスク層40(図3)の除去エッティングの一部として行われる。エッティング60は、ハードマスク層40と露出した埋め込み絶縁体24の材料の両方をエッティングする。しかし、

50

エッティング 60 は、露出したシリコン、ポリシリコンまたは窒化シリコンのいずれもエッティングしない。つまり、エッティングレシピ (recipe) は、露出したシリコン、ポリシリコンおよび窒化シリコンのいずれもエッティングすることができない。

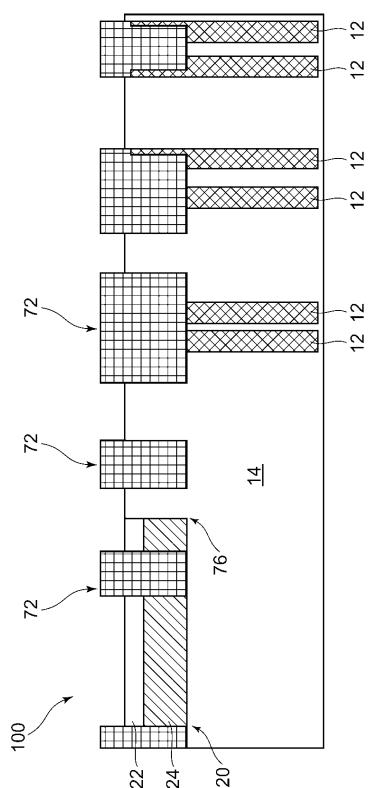

#### 【0020】

図 6 を参照すると、次のステップは、STI 72 を形成するために STI 材料 70 を堆積することを含む。図 6 及び図 7 に示すように、最終処理は、最上面の上にある STI 材料 70 を除去するために従来の高性能 CMOS または DRAM 技術の研磨 (図 6) を実行することと、図 7 に示すように、半導体デバイス 100 に到達するためにパッド層 30 (図 6) を剥離することとを含む。半導体デバイス 100 は、SOI 領域 20 のシリコン層 22 および埋め込み絶縁体 24 の厚さに実質的に等しい深さまで延在する STI 72 を含む。所望の深さ D (図 4) が SOI 領域 20 のシリコン層 22 および埋め込み絶縁体 24 の厚さに実質的に等しい場合、STI 72 は SOI 領域 20 およびバルク・シリコン領域 14 と実質的に等しい深さまで延在する。エッティング深さは、バルク・シリコン領域 14 に、ちょうど SOI 領域 20 のシリコン層 22 で停止する場合よりさらに優れた分離を提供する。

#### 【0021】

本発明を上記で概説した特定の実施形態に関して説明してきたが、当業者には多くの代替物、変更および変形が認識できることが明白である。したがって、上述のような本発明の実施形態は例示的であり、本発明を制限するものではない。請求の範囲で定義されるような本発明の精神および範囲から逸脱することなく、様々に変更することができる。

#### 【図面の簡単な説明】

#### 【0022】

【図 1】本発明を適用する前のウェハを示す断面図である。

【図 2】本発明の STI 形成または STI エッティング方法を示す断面図である。

【図 3】本発明の STI 形成または STI エッティング方法を示す断面図である。

【図 4】本発明の STI 形成または STI エッティング方法を示す断面図である。

【図 5】本発明の STI 形成または STI エッティング方法を示す断面図である。

【図 6】本発明の STI 形成または STI エッティング方法を示す断面図である。

【図 7】本発明の半導体デバイスを示す断面図である。

#### 【符号の説明】

#### 【0023】

10 ウェハ

12 トレンチ

14 バルク・シリコン領域

20 シリコン・オン・インシュレータ (SOI) 領域

22 シリコン層

24 埋め込み絶縁体

30 パッド層

40 ハードマスク層

42 エッティング

50 時限エッティング

60 エッティング

70 STI 材料

72 STI

100 半導体デバイス

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(51)Int.Cl.

F I

H 0 1 L 29/78 6 1 3 B

H 0 1 L 29/78 6 2 1

H 0 1 L 29/78 6 2 6 C

(74)代理人 100086243

弁理士 坂口 博

(72)発明者 スタイゲルワルド、マイケル

アメリカ合衆国12550 ニューヨーク州ニューバーグ ファイヴ・コーチ・レーン

(72)発明者 クマール、マヘンダー

アメリカ合衆国12524 ニューヨーク州フィッシュキル テン・チェイス・ドライヴ アパートメント ナンバー47ディー

(72)発明者 ホー、ハーバート、エル

アメリカ合衆国12553 ニューヨーク州ニュー・ウィンザー ルディ・ロード12

(72)発明者 ドブジンスキー、デイヴィッド

アメリカ合衆国12553 ニューヨーク州ニュー・ウィンザー カリークロス・ロード320

(72)発明者 ファルターメイヤー、ジョナサン

アメリカ合衆国12540 ニューヨーク州ラグランジュヴィル セヴァン・ストラトフォード・コード

審査官 三浦 尊裕

(56)参考文献 特開2005-244020(JP,A)

特開2003-203967(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/76

H01L 21/762

H01L 27/12

H01L 29/786