## (12) 发明专利

(10) 授权公告号 CN 107592114 B

(45) 授权公告日 2023.11.07

(21) 申请号 201710485286.0

(51) Int.CI.

(22) 申请日 2017.06.23

H03M 1/46 (2006.01)

(65) 同一申请的已公布的文献号

申请公布号 CN 107592114 A

(56) 对比文件

(43) 申请公布日 2018.01.16

JP 2013211611 A, 2013.10.10

(30) 优先权数据

JP 2012119767 A, 2012.06.21

2016-133925 2016.07.06 JP

JP 2003283336 A, 2003.10.03

(73) 专利权人 精工爱普生株式会社

CN 101674086 A, 2010.03.17

地址 日本东京都

CN 104954021 A, 2015.09.30

(72) 发明人 羽田秀生

审查员 张慧敏

(74) 专利代理机构 北京三友知识产权代理有限公司 11127

专利代理人 李辉 邓毅

权利要求书3页 说明书20页 附图17页

## (54) 发明名称

电路装置、物理量检测装置、电子设备和移动体

## (57) 摘要

本发明提供电路装置、物理量检测装置、电子设备和移动体。提供实现A/D转换的高速化以及转换错误的抑制的电路装置、物理量检测装置、电子设备和移动体等。电路装置(40)包含：控制电路(50)，其具有逐次比较寄存器(52)；D/A转换电路(DAC)，其对来自逐次比较寄存器(52)的输出数据进行D/A转换；以及比较电路(CP)，其比较模拟输入信号(VIN)与来自D/A转换电路(DAC)的输出信号(DQ)，控制电路(50)具有上限值寄存器(53)、下限值寄存器(54)，它们保持转换范围的上限值、下限值，在逐次比较处理中，在比较电路(CP)输出相同的比较结果达到规定次数以上的情况下，增大上限值或减小下限值。

1. 一种电路装置，其对模拟输入信号进行A/D转换，其特征在于，所述电路装置包含：

控制电路，其具有保持逐次比较数据的逐次比较寄存器；

D/A转换电路，其对来自所述逐次比较寄存器的输出数据进行D/A转换；以及

比较电路，其进行所述模拟输入信号与来自所述D/A转换电路的输出信号的比较处理，

所述控制电路具有：上限值寄存器，其保持通过所述模拟输入信号的A/D转换而得到的

A/D转换结果数据的转换范围的上限值；以及下限值寄存器，其保持所述转换范围的下限

值，

在逐次比较处理中，在所述比较电路输出相同的比较结果达到规定次数以上的情况

下，所述控制电路进行增大所述上限值的更新和减小所述下限值的更新中的至少一方，

所述控制电路进行如下的冗余范围附加处理：

在所述比较电路输出所述模拟输入信号的电压电平为来自所述D/A转换电路的所述输

出信号的电压电平以上的比较结果的情况下，将所述下限值更新为更新前的所述下限值与

所述逐次比较数据之间的值，

在所述比较电路输出所述模拟输入信号的电压电平小于来自所述D/A转换电路的所述

输出信号的电压电平的比较结果的情况下，将所述上限值更新为更新前的所述上限值与所

述逐次比较数据之间的值，

在所述逐次比较处理中，所述控制电路在所述比较电路输出相同的比较结果达到所述

规定次数以上的情况下跳过所述冗余范围附加处理。

2. 根据权利要求1所述的电路装置，其特征在于，

在所述逐次比较处理中，在所述比较电路从第一次的比较起输出相同的比较结果达到

所述规定次数以上的情况下，所述控制电路进行增大所述上限值的更新和减小所述下限值

的更新中的至少一方。

3. 根据权利要求1或2所述的电路装置，其特征在于，

在所述比较电路输出所述模拟输入信号的电压电平为来自所述D/A转换电路的所述输

出信号的电压电平以上的比较结果达到所述规定次数以上的情况下，所述控制电路进行增

大所述上限值的更新，

在所述比较电路输出所述模拟输入信号的电压电平小于来自所述D/A转换电路的所述

输出信号的电压电平的比较结果达到所述规定次数以上的情况下，所述控制电路进行减小

所述下限值的更新。

4. 根据权利要求1或2所述的电路装置，其特征在于，

所述控制电路在所述上限值达到所述逐次比较数据的满量程的上限的情况下将所述

上限值更新为所述满量程的上限，

在所述下限值达到所述逐次比较数据的所述满量程的下限的情况下，将所述下限值更

新为所述满量程的下限。

5. 根据权利要求1或2所述的电路装置，其特征在于，

所述逐次比较处理开始时的所述转换范围是包含上次的A/D转换结果数据的规定范

围，

所述控制电路将所述规定范围的上限值设定为所述上限值寄存器的值，将所述规定范

围的下限值设定为所述下限值寄存器的值。

6. 根据权利要求1或2所述的电路装置，其特征在于，

在所述比较电路输出所述模拟输入信号的电压电平为来自所述D/A转换电路的所述输出信号的电压电平以上的比较结果的情况下，所述控制电路进行增大所述下限值的更新，

在所述比较电路输出所述模拟输入信号的电压电平小于来自所述D/A转换电路的所述输出信号的电压电平的比较结果的情况下，所述控制电路进行减小所述上限值的更新。

7. 根据权利要求1或2所述的电路装置，其特征在于，

所述控制电路将所述逐次比较数据更新为与更新后的所述上限值以及所述下限值的平均值对应的值。

8. 一种电路装置，其对模拟输入信号进行A/D转换，其特征在于，所述电路装置包含：

控制电路，其具有保持逐次比较数据的逐次比较寄存器；

D/A转换电路，其对来自所述逐次比较寄存器的输出数据进行D/A转换；以及

比较电路，其进行所述模拟输入信号与来自所述D/A转换电路的输出信号的比较处理，

所述控制电路具有：上限值寄存器，其保持通过所述模拟输入信号的A/D转换而得到的A/D转换结果数据的转换范围的上限值；以及下限值寄存器，其保持所述转换范围的下限值，

在逐次比较处理中，在所述比较电路输出相同的比较结果达到规定次数以上的情况下，所述控制电路进行增大所述上限值的更新和减小所述下限值的更新中的至少一方，

所述控制电路进行如下的冗余范围附加处理：

在所述比较电路输出所述模拟输入信号的电压电平为来自所述D/A转换电路的所述输出信号的电压电平以上的比较结果的情况下，将所述下限值更新为更新前的所述下限值与所述逐次比较数据之间的值，

在所述比较电路输出所述模拟输入信号的电压电平小于来自所述D/A转换电路的所述输出信号的电压电平的比较结果的情况下，将所述上限值更新为更新前的所述上限值与所述逐次比较数据之间的值，

所述控制电路在由所述上限值和所述下限值设定的所述转换范围的大小变得小于规定范围幅度的情况下跳过所述冗余范围附加处理。

9. 根据权利要求8所述的电路装置，其特征在于，

所述控制电路在由所述上限值和所述下限值设定的所述转换范围变得小于所述范围幅度的情况下，进行多次比较处理，该多次比较处理是使所述比较电路执行多次所述模拟输入信号与来自所述D/A转换电路的所述输出信号的比较处理。

10. 根据权利要求9所述的电路装置，其特征在于，

所述电路装置包含微小信号判定电路，该微小信号判定电路判定所述模拟输入信号的电压电平与来自所述D/A转换电路的所述输出信号的电压电平之差的大小，

所述控制电路在由所述微小信号判定电路判定为微小信号的情况下进行所述冗余范围附加处理或所述多次比较处理，

在由所述微小信号判定电路判定为非微小信号的情况下跳过所述冗余范围附加处理和所述多次比较处理。

11. 根据权利要求8所述的电路装置，其特征在于，

所述逐次比较处理开始时的所述转换范围是包含上次的A/D转换结果数据的规定范

围，

所述控制电路将所述规定范围的上限值设定为所述上限值寄存器的值,将所述规定范围的下限值设定为所述下限值寄存器的值。

12.根据权利要求8所述的电路装置,其特征在于,

在所述比较电路输出所述模拟输入信号的电压电平为来自所述D/A转换电路的所述输出信号的电压电平以上的比较结果的情况下,所述控制电路进行增大所述下限值的更新,

在所述比较电路输出所述模拟输入信号的电压电平小于来自所述D/A转换电路的所述输出信号的电压电平的比较结果的情况下,所述控制电路进行减小所述上限值的更新。

13.根据权利要求8所述的电路装置,其特征在于,

所述控制电路将所述逐次比较数据更新为与更新后的所述上限值以及所述下限值的平均值对应的值。

14.一种物理量检测装置,其特征在于,所述物理量检测装置包含:

物理量换能器;和

权利要求1至13中的任意一项所述的电路装置,其进行A/D转换,该A/D转换用于检测基于来自所述物理量换能器的检测信号的物理量。

15.一种电子设备,其特征在于,

所述电子设备包含权利要求1~13中的任意一项所述的电路装置。

16.一种移动体,其特征在于,

所述移动体包含权利要求1~13中的任意一项所述的电路装置。

## 电路装置、物理量检测装置、电子设备和移动体

### 技术领域

[0001] 本发明涉及电路装置、物理量检测装置、电子设备和移动体等。

### 背景技术

[0002] 以往,作为将模拟信号转换为数字数据的A/D转换电路,已知有逐次比较型A/D转换电路。该逐次比较型A/D转换电路具有比较电路、逐次比较寄存器和D/A转换电路,利用逐次比较动作将对输入信号进行采样/保持后的信号进行A/D转换从而输出数字数据。

[0003] 在将输入信号转换为n位的数字数据的逐次比较型A/D转换电路中、使用从MSB侧逐位地确定位数据的一般方法的情况下,转换周期为n周期。由于周期数会对功耗及转换速度产生影响,因此,提出了通过减少转换周期来实现低功耗且高速的A/D转换的方法。

[0004] 例如,在专利文献1中公开了对每个模拟信号限定转换范围从而实现高速化的逐次比较A/D转换电路。在专利文献2中公开了使用上次的转换码的高位、仅进行低位的转换从而实现高速化的逐次比较A/D转换电路。在专利文献3中公开了在进行伪过采样(pseudo oversampling)动作时限定进行逐次比较的数据范围从而实现高速化的A/D转换电路。

[0005] 专利文献1:日本特开2006-140819号公报

[0006] 专利文献2:日本特开2006-108893号公报

[0007] 专利文献3:日本特开2013-211611号公报

[0008] 专利文献1~专利文献3都是通过限定转换范围来削减转换周期,从而实现高速化。但是,存在这样的课题:在输入了远远偏离预期的信号的情况下,与输入信号对应的数字数据处于转换范围外而无法适当地转换输入信号。

### 发明内容

[0009] 根据本发明的几个方式,能够提供实现A/D转换的高速化以及转换错误的抑制的电路装置、物理量检测装置、电子设备和移动体等。

[0010] 本发明是为了解决上述课题中的至少一部分而完成的,能够作为以下的形态或方式来实现。

[0011] 本发明的一个方式涉及电路装置,该电路装置对模拟输入信号进行A/D转换,其中,所述电路装置包含:控制电路,其具有保持逐次比较数据的逐次比较寄存器;D/A转换电路,其对来自所述逐次比较寄存器的输出数据进行D/A转换;以及比较电路,其进行所述模拟输入信号与来自所述D/A转换电路的输出信号的比较处理,所述控制电路具有:上限值寄存器,其保持通过所述模拟输入信号的A/D转换而得到的A/D转换结果数据的转换范围的上限值;以及下限值寄存器,其保持所述转换范围的下限值,在逐次比较处理中,在所述比较电路输出相同的比较结果达到规定次数以上的情况下,所述控制电路进行增大所述上限值的更新和减小所述下限值的更新中的至少一方。

[0012] 在本发明的一个方式中,在作为逐次比较型A/D转换电路的电路装置中,在从比较电路输出相同的比较结果达到规定次数以上的情况下,进行转换范围的上限值的增大和下

限值的减小中的至少一方。这样,能够将在更新前不包含在转换范围中的范围重新包含到转换范围中。即,通过设定转换范围能够实现转换的高速化,并通过转换范围的适当更新,输出没有错误的转换结果。

[0013] 此外,在本发明的一个方式中,也可以是,在所述逐次比较处理中,在所述比较电路从第一次的比较起输出相同的比较结果达到所述规定次数以上的情况下,所述控制电路进行增大所述上限值的更新和减小所述下限值的更新中的至少一方。

[0014] 这样,能够将从逐次比较处理的第一次起输出相同的比较结果作为增大上限值或减小下限值的条件,因此能够抑制过度地扩大转换范围的情况。

[0015] 此外,在本发明的一个方式中,也可以是,在所述比较电路输出所述模拟输入信号的电压电平为来自所述D/A转换电路的所述输出信号的电压电平以上的比较结果达到所述规定次数以上的情况下,所述控制电路进行增大所述上限值的更新,在所述比较电路输出所述模拟输入信号的电压电平小于来自所述D/A转换电路的所述输出信号的电压电平的比较结果达到所述规定次数以上的情况下,所述控制电路进行减小所述下限值的更新。

[0016] 这样,能够根据比较结果更新上限值或下限值。

[0017] 此外,在本发明的一个方式中,也可以是,所述控制电路在所述上限值达到所述逐次比较数据的满量程的上限的情况下将所述上限值更新为所述满量程的上限,在所述下限值达到所述逐次比较数据的所述满量程的下限的情况下,将所述下限值更新为所述满量程的下限。

[0018] 这样,由于考虑了满量程的上限、下限,因此能够抑制过度地扩大转换范围的情况等。

[0019] 此外,在本发明的一个方式中,也可以是,所述控制电路进行如下的冗余范围附加处理:在所述比较电路输出所述模拟输入信号的电压电平为来自所述D/A转换电路的所述输出信号的电压电平以上的比较结果的情况下,将所述下限值更新为更新前的所述下限值与所述逐次比较数据之间的值,在所述比较电路输出所述模拟输入信号的电压电平小于来自所述D/A转换电路的所述输出信号的电压电平的比较结果的情况下,将所述上限值更新为更新前的所述上限值与所述逐次比较数据之间的值。

[0020] 这样,能够在上限值、下限值的更新时附加冗余范围,从而在比较结果中存在错误的情况下也能够进行适当的转换等。

[0021] 此外,在本发明的一个方式中,也可以是,在所述逐次比较处理中,所述控制电路在所述比较电路输出相同的比较结果达到所述规定次数以上的情况下跳过所述冗余范围附加处理。

[0022] 这样,在必要性较小的情况下,能够跳过冗余范围附加处理,因此能够实现转换处理的高速化。

[0023] 此外,在本发明的一个方式中,也可以是,所述控制电路在由所述上限值和所述下限值设定的所述转换范围的大小变得小于规定范围幅度的情况下跳过所述冗余范围附加处理。

[0024] 这样,能够跳过A/D转换结果不收敛的过度的冗余范围附加处理。

[0025] 此外,在本发明的一个方式中,也可以是,所述控制电路在由所述上限值和所述下限值设定的所述转换范围变得小于所述范围幅度的情况下,进行多次比较处理,该多次比

较处理是使所述比较电路执行多次所述模拟输入信号与来自所述D/A转换电路的所述输出信号的比较处理。

[0026] 这样,由于执行多次比较处理,因此,能够提高比较处理的精度。

[0027] 此外,在本发明的一个方式中,也可以是,所述电路装置包含微小信号判定电路,该微小信号判定电路判定所述模拟输入信号的电压电平与来自所述D/A转换电路的所述输出信号的电压电平之差的大小,所述控制电路在由所述微小信号判定电路判定为微小信号的情况下进行所述冗余范围附加处理或所述多次比较处理,在由所述微小信号判定电路判定为非微小信号的情况下跳过所述冗余范围附加处理和所述多次比较处理。

[0028] 这样,通过进行微小信号判定,从而能够在必要性较大的情况下执行冗余范围附加处理或多次比较处理。

[0029] 此外,在本发明的一个方式中,也可以是,所述逐次比较处理开始时的所述转换范围是包含上次的A/D转换结果数据的规定范围,所述控制电路将所述规定范围的上限值设定为所述上限值寄存器的值,将所述规定范围的下限值设定为所述下限值寄存器的值。

[0030] 这样,能够根据上次的A/D转换结果数据设定比较处理开始时的转换范围。

[0031] 此外,在本发明的一个方式中,也可以是,在所述比较电路输出所述模拟输入信号的电压电平为来自所述D/A转换电路的所述输出信号的电压电平以上的比较结果的情况下,所述控制电路进行增大所述下限值的更新,在所述比较电路输出所述模拟输入信号的电压电平小于来自所述D/A转换电路的所述输出信号的电压电平的比较结果的情况下,所述控制电路进行减小所述上限值的更新。

[0032] 这样,通过根据比较结果缩小转换范围,能够求出A/D转换结果数据。

[0033] 此外,在本发明的一个方式中,也可以是,所述控制电路将所述逐次比较数据更新为与更新后的所述上限值以及所述下限值的平均值对应的值。

[0034] 这样,能够与上限值、下限值的更新对应地适当更新逐次比较数据。

[0035] 此外,本发明的另一方式涉及物理量检测装置,所述物理量检测装置包含:物理量换能器;和所述电路装置,其进行A/D转换,该A/D转换用于检测基于来自所述物理量换能器的检测信号的物理量。

[0036] 此外,本发明的另一方式涉及电子设备,所述电子设备包含所述电路装置。

[0037] 此外,本发明的另一方式涉及移动体,所述移动体包含所述电路装置。

## 附图说明

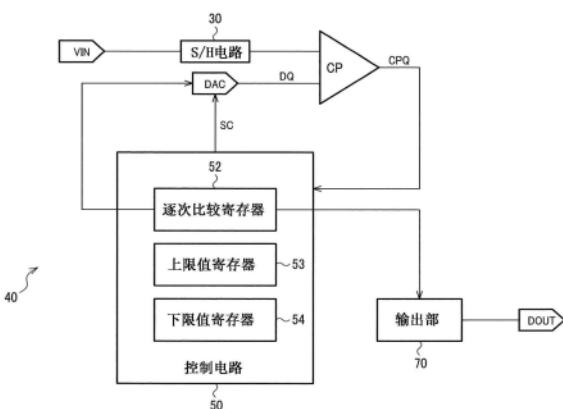

[0038] 图1是作为本实施方式的电路装置的A/D转换电路的结构例。

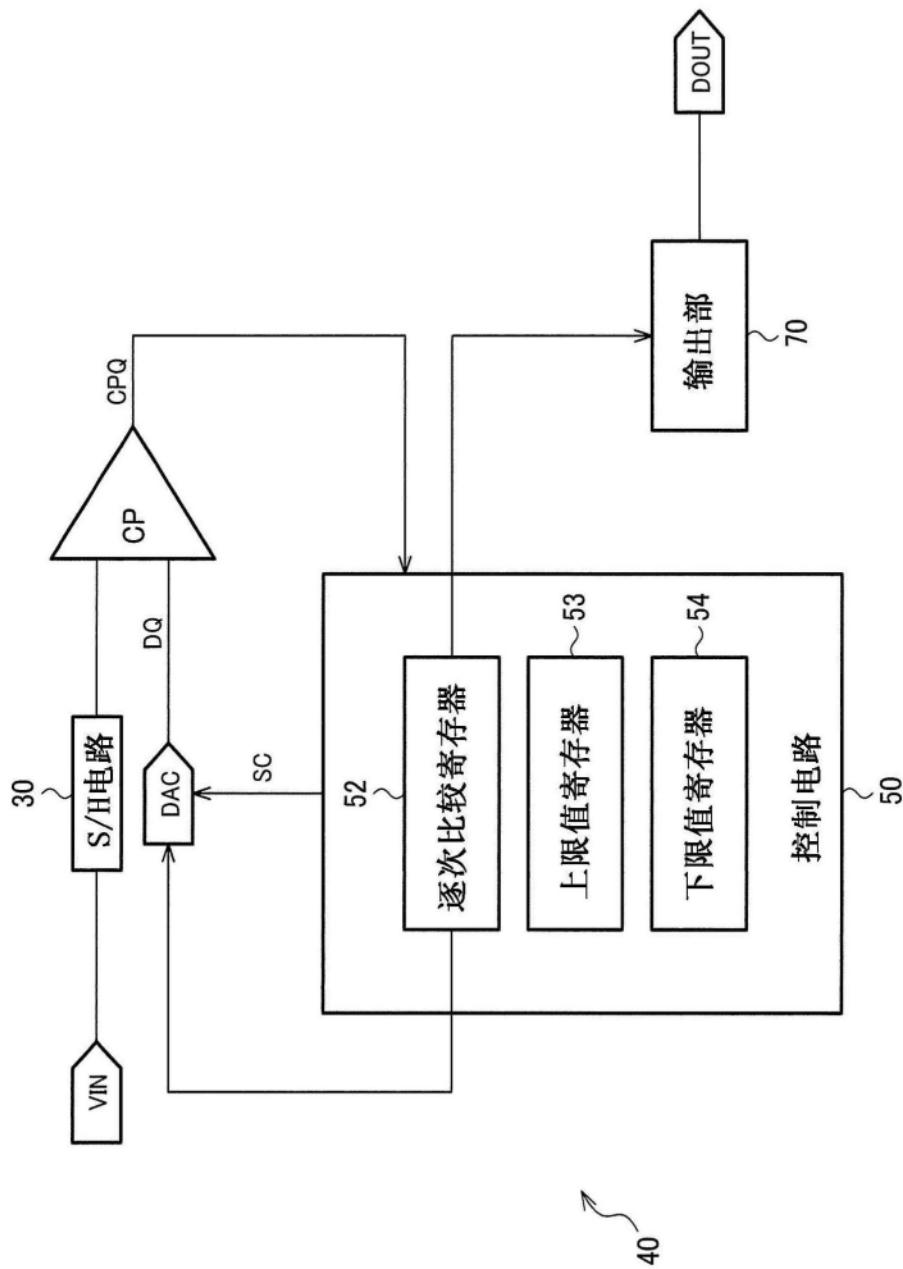

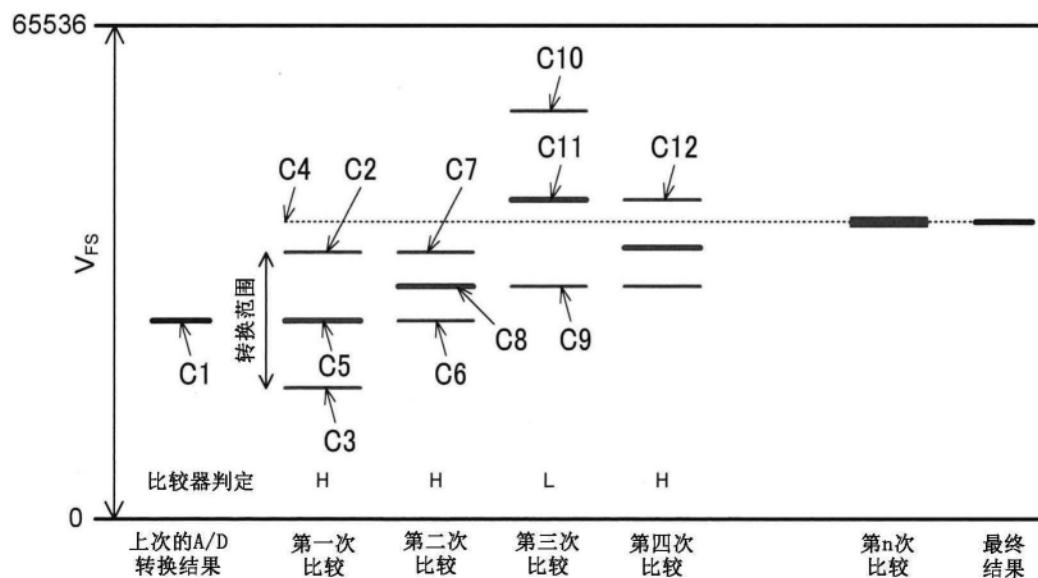

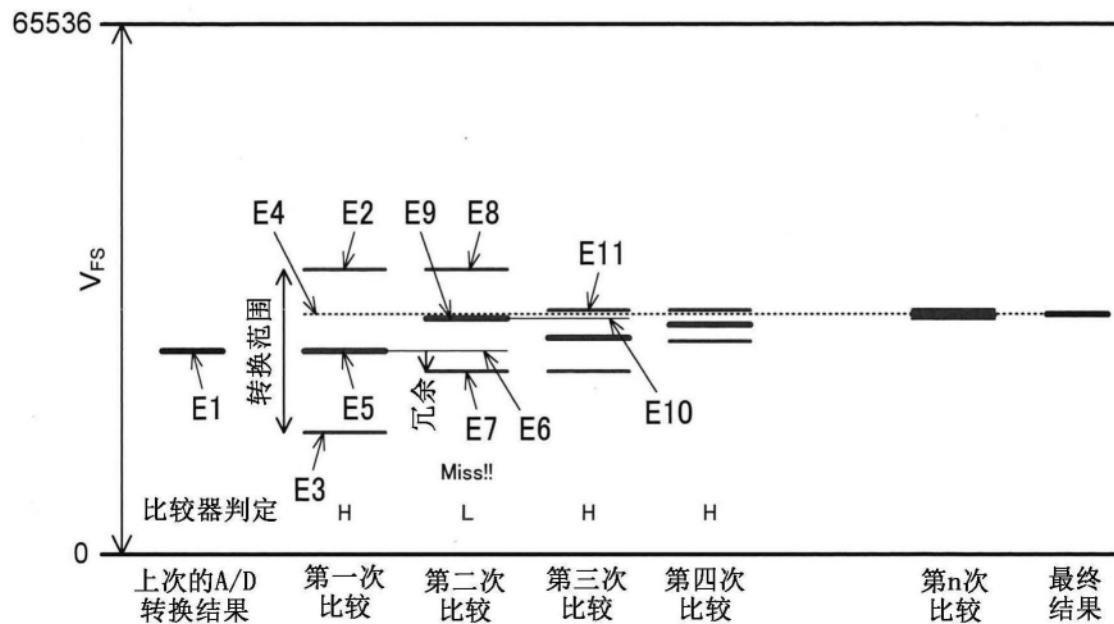

[0039] 图2是表示转换范围的转变的仿真图。

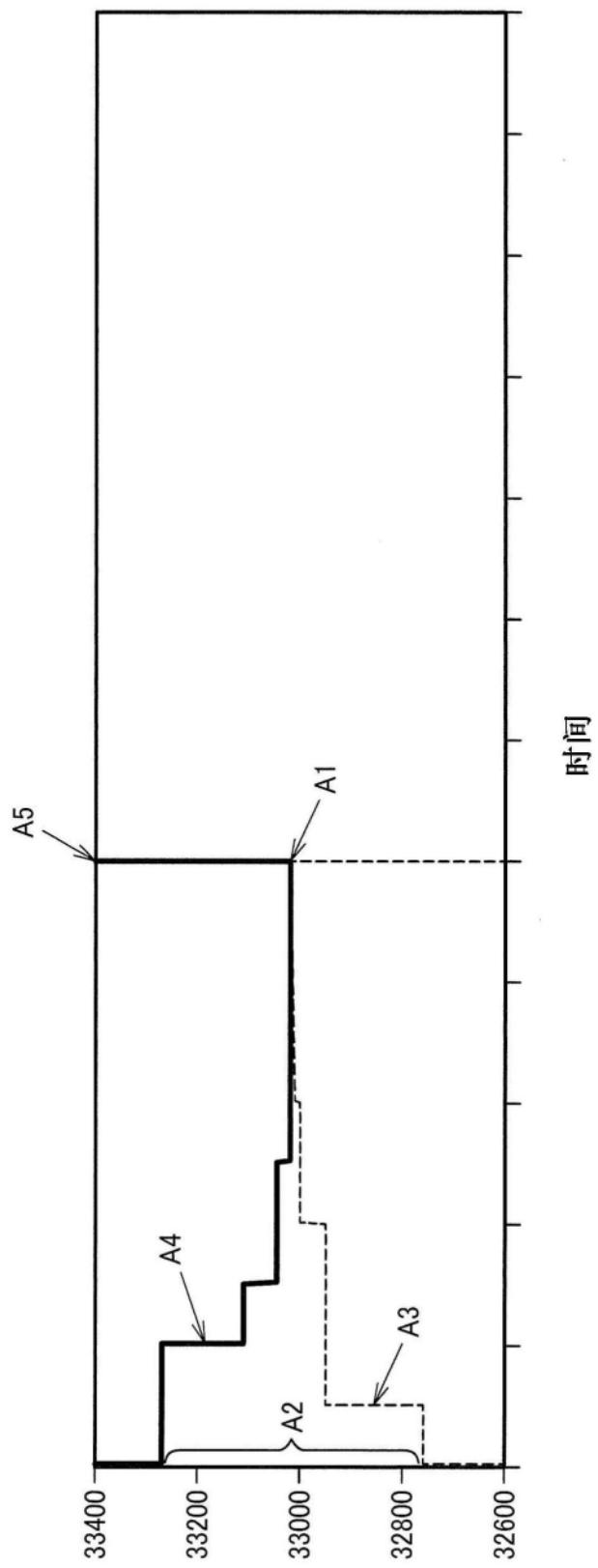

[0040] 图3是表示转换范围的转变的仿真图。

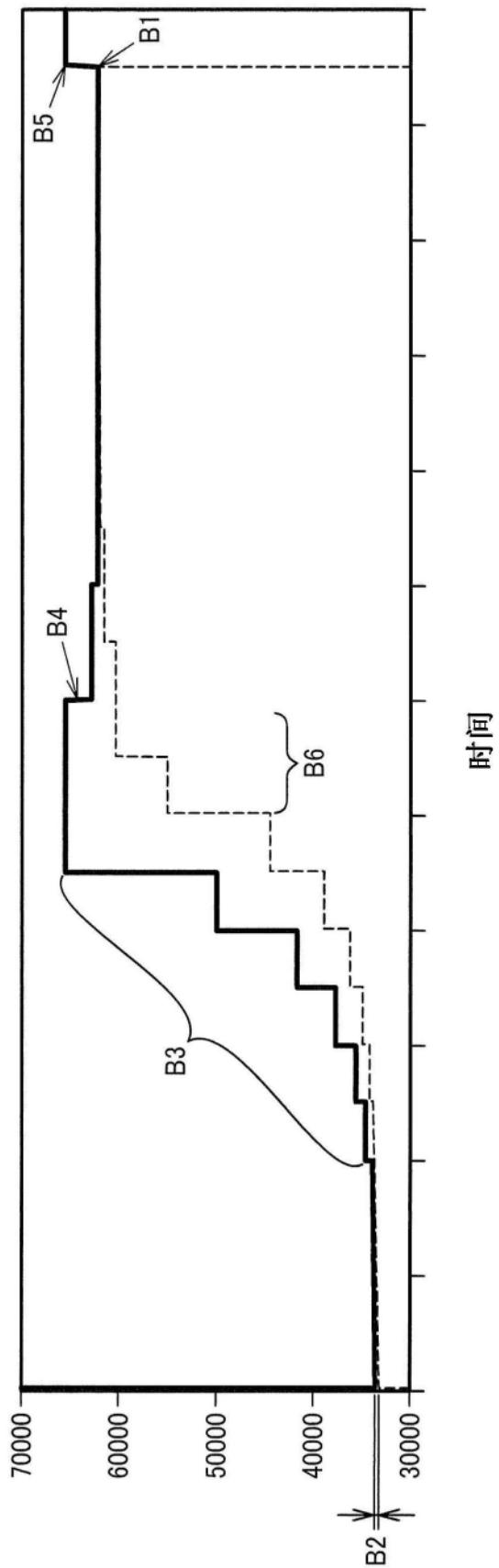

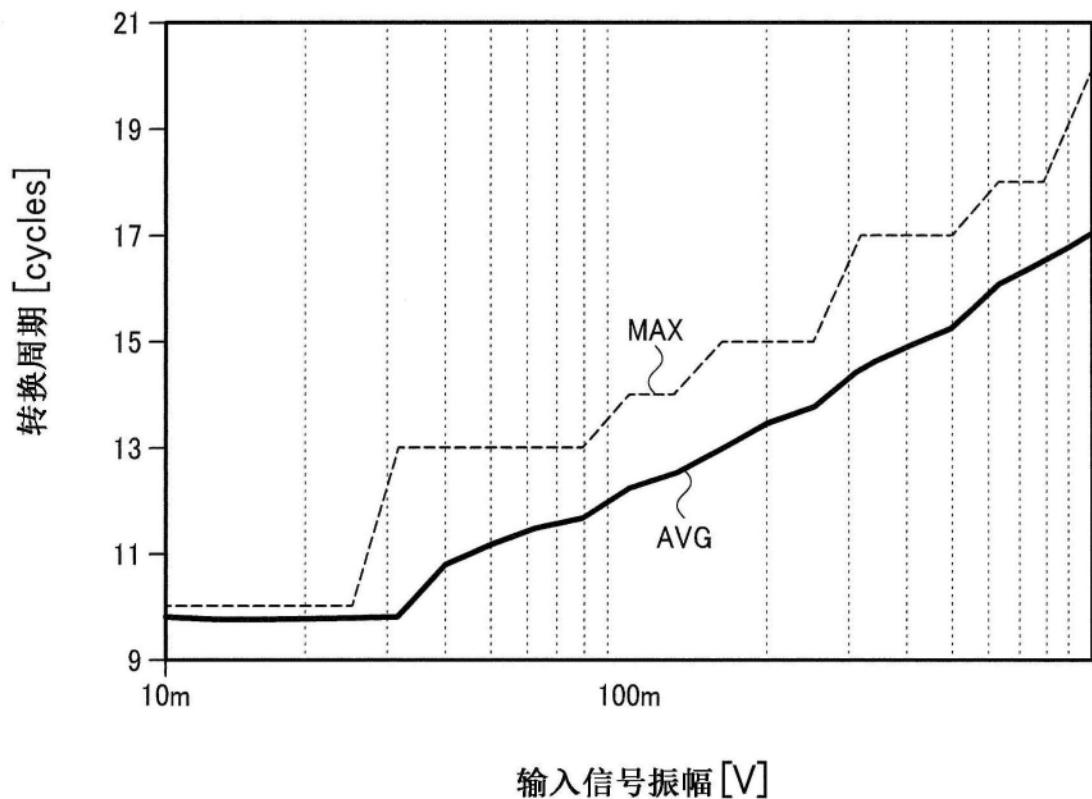

[0041] 图4是输入信号振幅与周期数的关系图。

[0042] 图5是作为本实施方式的电路装置的A/D转换电路的结构例。

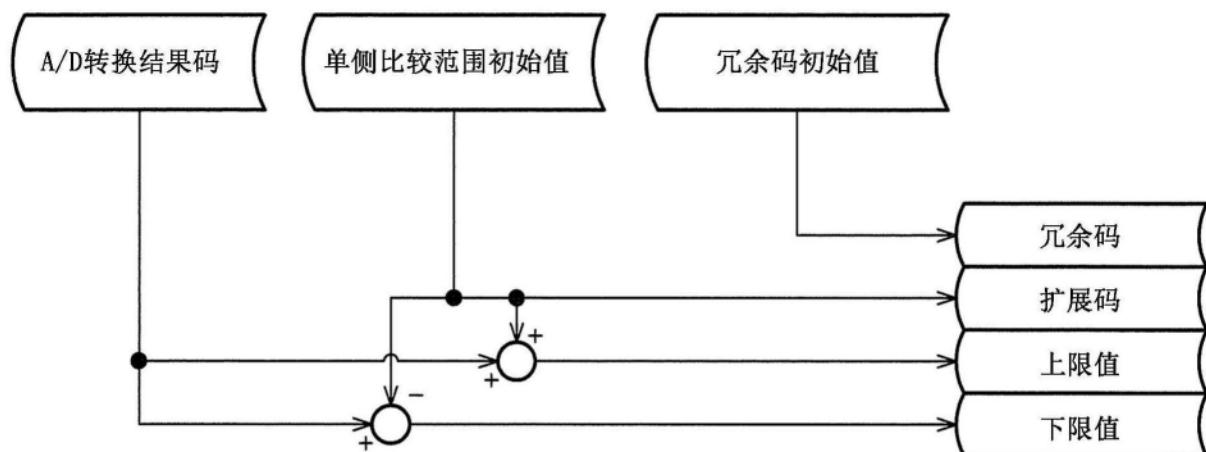

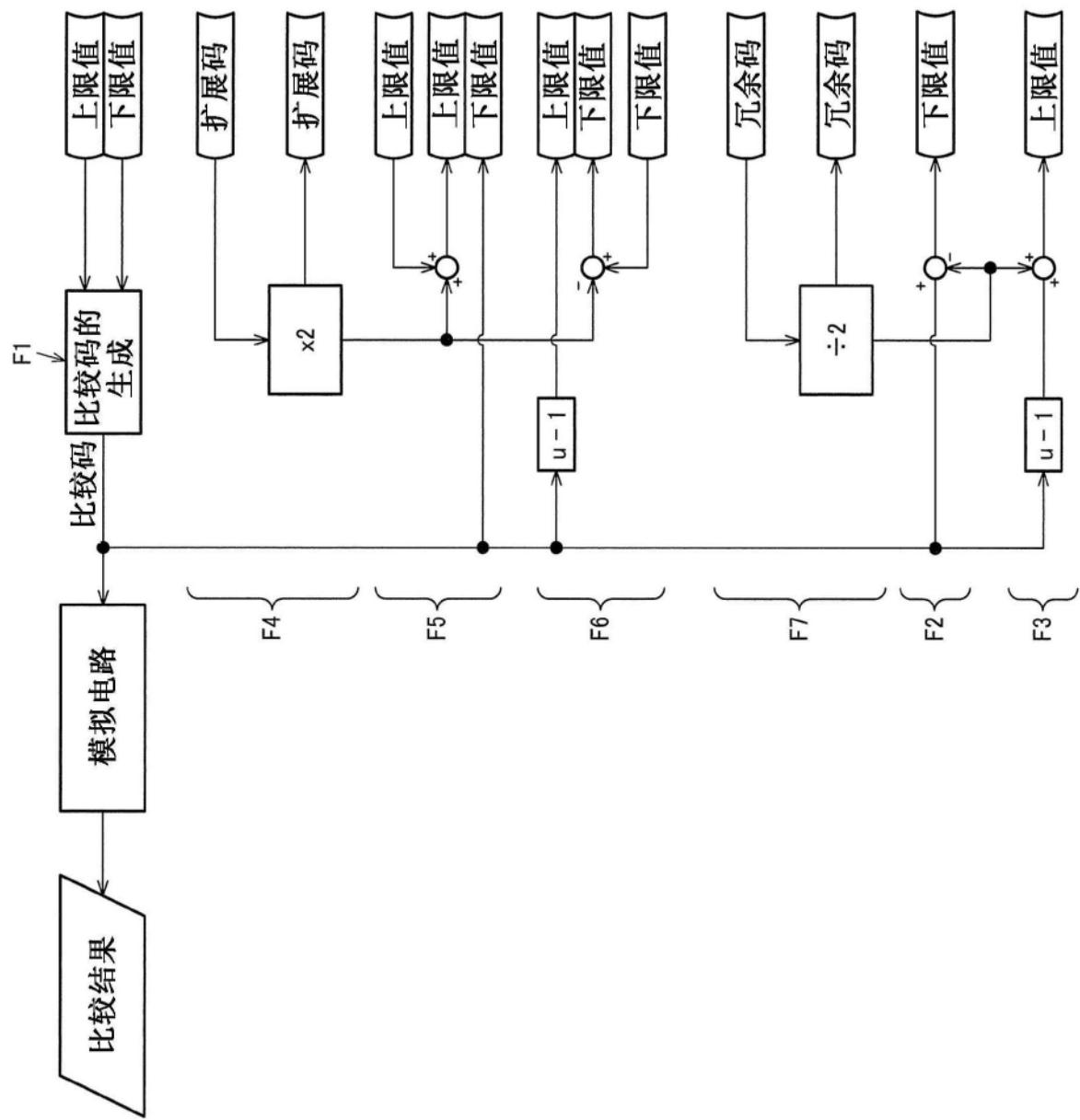

[0043] 图6是A/D转换电路的详细结构例。

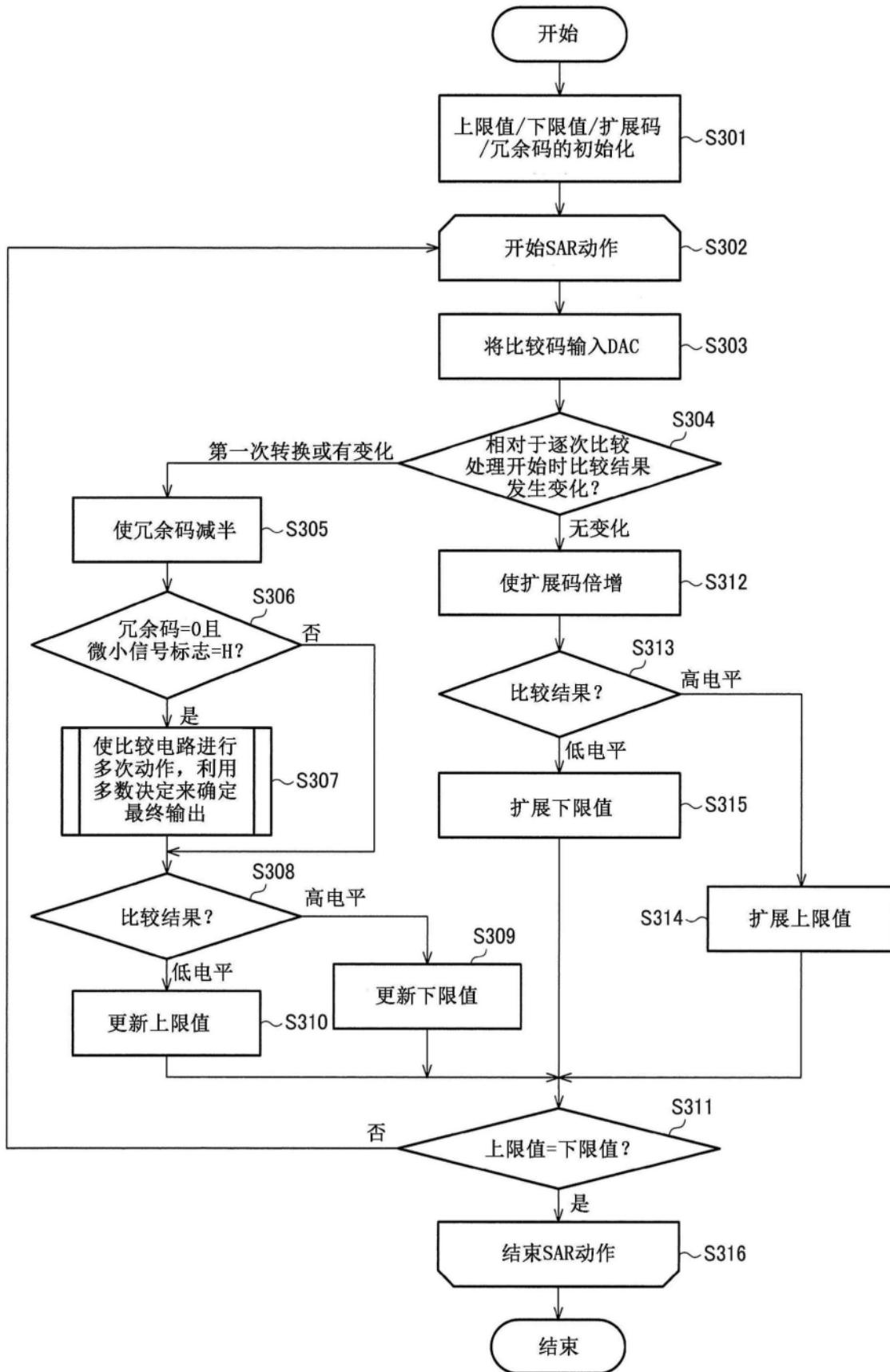

[0044] 图7是说明本实施方式的逐次比较处理的流程图。

[0045] 图8是上限值、下限值、逐次比较数据的更新例。

[0046] 图9是本实施方式的寄存器动作的说明图。

- [0047] 图10是本实施方式的寄存器动作的说明图。

- [0048] 图11是说明进行冗余范围附加处理时的逐次比较处理的流程图。

- [0049] 图12是进行冗余范围附加处理时的上限值、下限值、逐次比较数据的更新例。

- [0050] 图13是进行冗余范围附加处理时的寄存器动作的说明图。

- [0051] 图14是进行冗余范围附加处理时的寄存器动作的说明图。

- [0052] 图15是说明进行微小信号判定时的逐次比较处理的流程图。

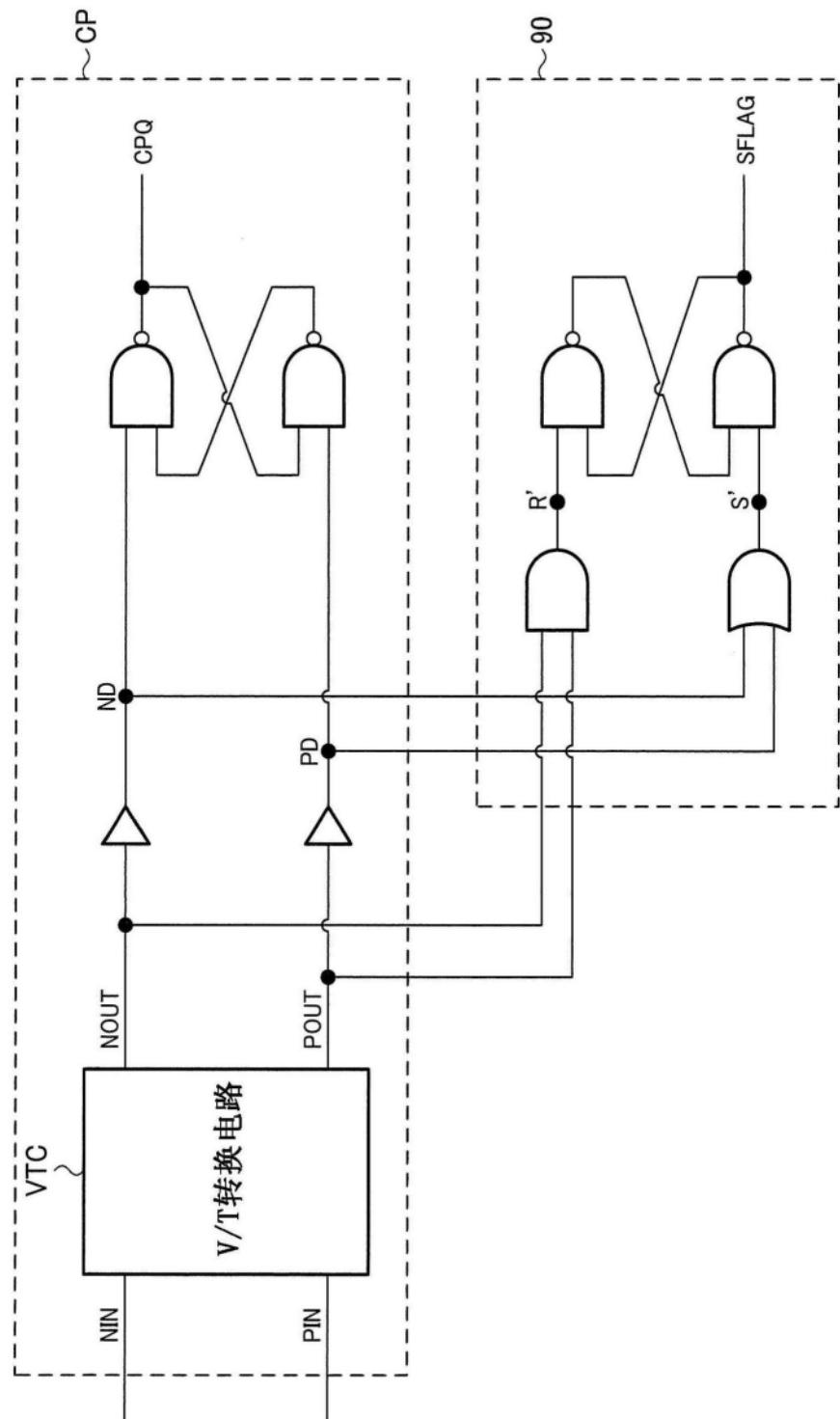

- [0053] 图16是比较电路和微小信号判定电路的结构例。

- [0054] 图17是说明比较电路、微小信号判定电路的动作的波形图。

- [0055] 图18是说明比较电路、微小信号判定电路的动作的波形图。

- [0056] 图19是包含本实施方式的电路装置的物理量检测装置的结构例。

- [0057] 图20是包含本实施方式的电路装置的电子设备的例子。

- [0058] 图21是包含本实施方式的电路装置的移动体的例子。

- [0059] 标号说明

- [0060] DAC、DAC1、DAC2:D/A转换电路;CA1～CA128;CB1～CB9:电容器;CAR1、CAR2:电容器阵列;SA1～SA128、SB1～SB9:开关电路;SAR1、SAR2:开关阵列;SDAC:子D/A转换电路;SCAR:电容器阵列;SSAR:开关阵列;SFLAG:微小信号标志;DOUT:输出数据;VDD、GND:基准电压;VFS:满量程电压;VIN:模拟输入信号;CP:比较电路;VTC:V/T转换电路;ANT:天线;30:S/H电路;40:电路装置;42:D/A转换电路;50:控制电路;52:逐次比较寄存器;53:上限值寄存器;54:下限值寄存器;60:电压生成电路;70:输出部;80:检测电路;82:A/D转换电路;84:处理部;90:微小信号判定电路;200:电子设备;206:汽车;207:车体;208:车体姿势控制装置;209:车轮;210:通信部;220:处理部;230:操作部;240:显示部;250:存储部;300:物理量检测装置;310:物理量换能器。

## 具体实施方式

[0061] 以下,对本发明的优选实施方式详细地进行说明。另外,以下说明的本实施方式并非不当地限定权利要求书所述的本发明的内容,本实施方式中说明的全部结构作为本发明的解决手段并非都是必须的。

### 1. 本实施方式的方法

[0063] 首先,对本实施方式的方法进行说明。在逐次比较型A/D转换电路中,速度和功耗根据转换周期数而确定。这里的转换周期表示如下的1个周期的动作:进行逐次比较数据的D/A转换,进行D/A转换结果与进行采样/保持处理后的输入信号的比较处理,输出比较结果。例如,在n位的A/D转换电路中、进行从MSB侧逐位地确定数据的一般A/D转换处理的情况下,转换周期为n周期。

[0064] 上述一般A/D转换处理是指,将与满量程电压VFS对应的数字数据的满量程 $0 \sim 2^n - 1$ 整体作为转换范围,进行模拟输入信号(输入电压)的转换。对此,如果能够将转换范围限定为比满量程小的范围,则能够减少转换周期,从而能够实现A/D转换的高速化和省电化。

[0065] 例如,如专利文献2那样,固定高位,仅将低位作为转换范围。如果能够固定n位中的高k位,则能够将转换范围限定为与低n-k位相当的 $2^{n-k}$ 的范围,转换周期成为n-k周期。此外,由于只要能够将转换范围限定为较小的范围即可,因此,即使如专利文献3那样,设定转

换范围的上限值和下限值,将由该上限值和下限值设定的转换范围作为对象进行A/D转换,也能够实现高速化和省电化。

[0066] 但是,这些方法是通过不将转换范围外的部分作为探索对象来实现高速化等的方法,因此,正确数据(与模拟输入信号对应的数字数据)需要处于限定得较小的转换范围内。因此,存在这样的课题:即使输入远远偏离预期的信号、正确数据处于转换范围外,输入的数字数据的候选也被限定在转换范围内,无法进行适当的转换。

[0067] 换言之,可以说,现有方法是能够在某种程度上预料输入信号的范围的情况下有用的方法。例如,在专利文献3的方法中,为了进行伪过采样,将相同的输入信号作为对象进行多次逐次比较处理。在对给定的输入信号进行第二次之后的逐次比较处理时,可以期待A/D转换结果数据与上次的A/D转换结果数据相等,因此,即使缩小转换范围,也不易产生问题。与此相对,在必须考虑输入信号的变动的情况下,可能像上述那样无法进行适当的转换。

[0068] 对此,还考虑了如下方法:判定正确数据是否偏离了转换范围,在偏离的情况下变更转换范围。这样,在输入了远远偏离预期的信号的情况下,也能够取得适当的转换结果。但是,在该情况下,会产生用于判定是否偏离转换范围的判定周期,导致转换周期数增大。本来,限定转换范围的方法是为了削减转换周期数,实现高速化、省电化,然而,由判定周期导致的周期数的增大损害了这些效果。

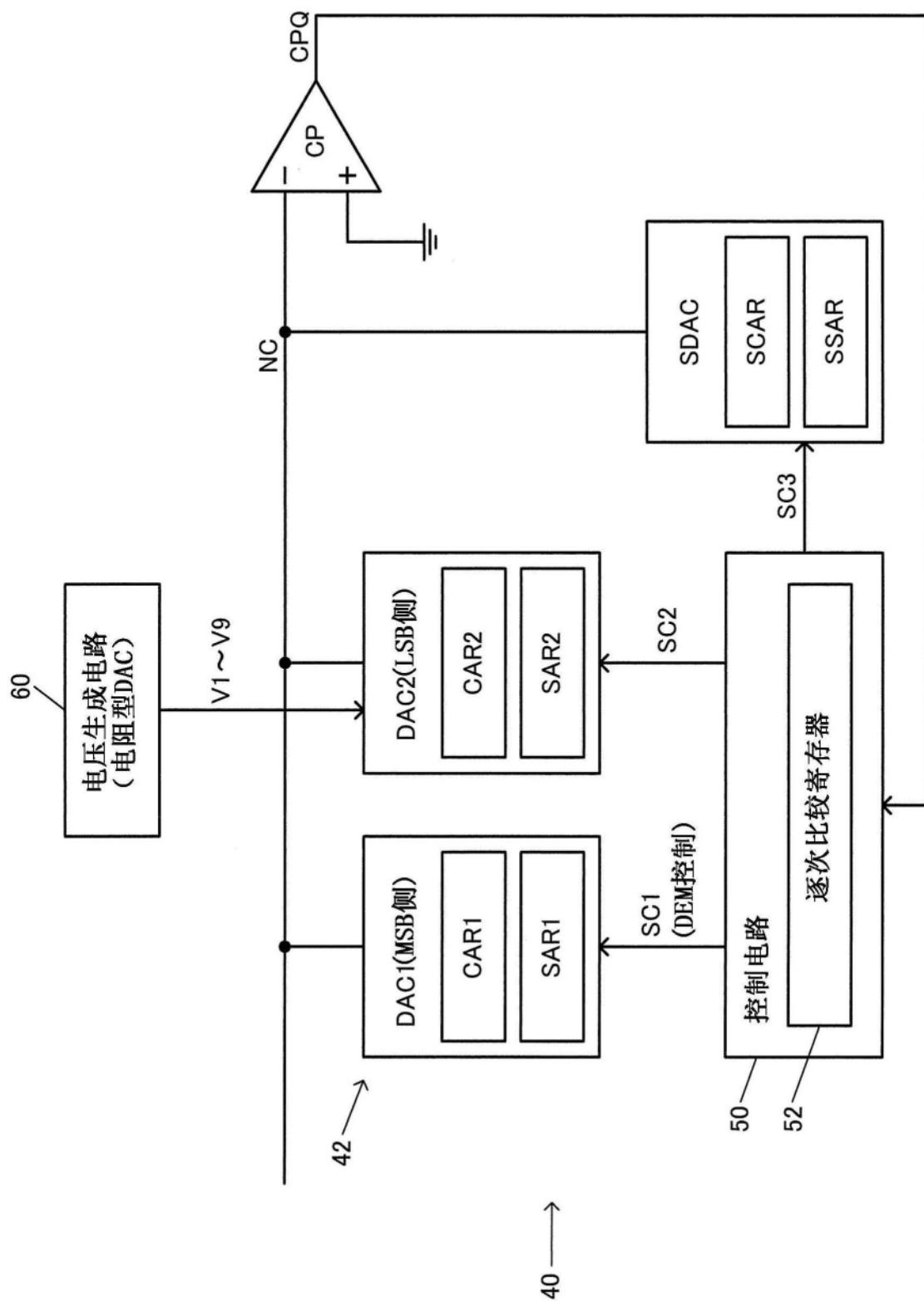

[0069] 由此,本申请人提出同时实现高速化和获得没有错误的转换结果的方法。本实施方式的电路装置40是对模拟输入信号进行A/D转换的电路装置,如图1所示,电路装置40包含:控制电路50,其具有保持逐次比较数据的逐次比较寄存器52;D/A转换电路DAC,其对来自逐次比较寄存器52的输出数据(逐次比较数据)进行D/A转换;以及比较电路CP,其进行模拟输入信号VIN与来自D/A转换电路DAC的输出信号DQ之间的比较处理。并且,控制电路50具有:上限值寄存器53,其保持通过模拟输入信号的A/D转换而得到的A/D转换结果数据的转换范围的上限值;和下限值寄存器54,其保持转换范围的下限值,在逐次比较处理中,在比较电路CP输出相同的比较结果达到规定次数以上的情况下,进行增大上限值的更新和减小下限值的更新中的至少一方。

[0070] 另外,如图1所示,电路装置40还可以包含:S/H电路30,其对作为A/D转换对象的模拟输入信号VIN进行采样/保持;和输出部70,其根据通过逐次比较动作而得到的A/D转换结果数据,输出输出数据DOUT。但是,电路装置40不限于图1的结构,也可以实施省略上述部件中的一部分构成要素、或追加其它构成要素等各种变形。例如,在如使用图5、图6后述的那样使用电荷再分配型D/A转换电路DAC的情况下,能够通过D/A转换电路DAC实现S/H电路30的功能。

[0071] 在此,逐次比较处理表示在求出1次与模拟输入信号VIN对应的A/D转换结果数据的期间内进行的处理。具体而言,相当于多次重复上述转换周期的处理,相当于后述的图7的流程图整体的处理。此外,在本实施方式中,将直到与模拟输入信号VIN对应的A/D转换结果数据得以确定而作为输出数据DOUT输出的处理称作A/D转换处理。一般将通过一次的逐次比较处理得到的A/D转换结果数据作为输出数据DOUT即可,一次A/D转换处理通过一次逐次比较处理来进行。但是,也可以如专利文献3的伪过采样那样使用多个A/D转换结果数据取得一个输出数据DOUT,该情况下,在一次A/D转换处理中,执行多次逐次比较处理。

[0072] 此外,如果是双输入的比较电路,则来自比较电路CP的比较结果(比较结果信号CPQ)是表示第1输入 $\geq$ 第2输入或第1输入 $<$ 第2输入中的任意一个的信息。更具体来说,是表示模拟输入信号VIN与作为逐次比较数据的D/A转换结果的来自D/A转换电路DAC的输出信号DQ是VIN $<$ DQ还是VIN $\geq$ DQ的信息。

[0073] 根据本实施方式的方法,在输出相同的比较结果达到规定次数的情况下,进行增大上限值和减小下限值中的至少一个的更新。如后述那样,在逐次比较处理中,通过减小上限值或增大下限值来缩小转换范围,由此取得A/D转换结果数据。因此,如果是现有的方法,则如果正确数据不在转换范围的初始值(初始范围)内,无论怎样缩小转换范围,也无法取得适当的A/D转换结果数据。在这方面,在本实施方式的方法中,进行增大上限值、减小下限值这种逆向的更新处理。因此,能够将偏离转换范围初始值的范围重新包含到转换范围内,从而能够得到没有错误的转换结果。

[0074] 进而,在本实施方式中,将输出相同的比较结果达到规定次数的情况作为进行增大上限值和减小下限值中的至少一个的更新的触发。由比较电路CP进行的比较只是逐次比较数据的D/A转换结果与模拟输入信号VIN之间的比较处理,因此,转换范围扩展专用的比较处理不是必须的。因此,能够抑制转换周期数的过度增大。

[0075] 图2和图3是说明转换范围的转变的仿真图。纵轴表示数字数据的值,横轴表示时间。此外,实线表示上限值的转变,虚线表示下限值的转变。另外,在图2、图3中,示出了进行使用图11等后述的冗余范围附加的例子,但是,该结构不是必须的。

[0076] 图2是模拟输入信号VIN的变化较小、正确数据A1包含在转换范围A2内的情况的例子。在该情况下,通过增大下限值(A3等)和减小上限值(A4等)来缩小转换范围,在A5所示的时刻,取得A/D转换结果数据。即,图2是转换范围的初始值没有问题的情况,通过将转换范围设定得比满量程小,实现高速化。

[0077] 图3是模拟输入信号VIN的变化较大、正确数据B1处于转换范围B2的范围外的例子。在图3的例子中,模拟输入信号VIN比逐次比较数据(转换范围内的任意一个数字数据)的D/A转换结果(DQ)大,VIN $\geq$ DQ这一比较结果是连续的。由此,在本实施方式的控制电路50中,如B3所示那样使转换范围的上限值增大。由此,正确数据处于转换范围内,VIN $<$ DQ这一比较结果也被输出。其结果是,如B4所示那样,上限值也开始减小,在B5所示的时刻取得A/D转换结果数据。

[0078] 通过增大上限值或减小下限值,将不是转换范围对象的区域重新包含到转换范围内。即,正确数据的探索对象增加,转换周期数增大。当其增大幅度过大时,会损害高速化、低功耗化的效果,因此,本申请人对于这方面也进行了验证。

[0079] 图4是示出模拟输入信号VIN的振幅与转换周期数的关系的图。横轴是模拟输入信号VIN的振幅,表示模拟输入信号VIN是否容易变化。纵轴表示转换周期数。AVG表示转换周期数的平均值,MAX表示转换周期数的最大值。此外,在图4中示出还考虑了后述的冗余范围附加后的结果。

[0080] 在此,由于考虑进行16位的A/D转换,因此,如果是以满量程作为对象的A/D转换,则转换周期为16周期。如图4所示,在本实施方式的方法中,模拟输入信号VIN的振幅越大,则转换周期数的平均值、最大值都越大。在振幅较小的范围内,转换周期数是10周期,相比于原本的16周期,能够实现高速化。此外,即使振幅大到500mV左右,转换周期数也停留在17

周期,相对于原本的16周期的增大幅度不大。

[0081] 根据图4可知:如果是本实施方式中假定的输入信号振幅的范围,则即使增大上限值或减小下限值,高速化、省电化的效果也是显著的。即,本实施方式的方法能够实现取得了速度与转换精度的平衡的适当的A/D转换。

[0082] 以下,对本实施方式的电路装置40的具体结构例进行说明之后,对逐次比较处理的具体处理流程进行说明。最后,对包含本实施方式的电路装置的各种装置的例子进行说明。

### [0083] 2. 电路装置的结构例

[0084] 接下来,对本实施方式的电路装置40的例子进行说明。另外,以下,对作为A/D转换电路的电路装置40中包含的D/A转换电路DAC是电荷再分配型D/A转换电路、且在其MSB侧应用DEM(Dynamic Element Matching:动态单元匹配)的例子进行说明。但是,本实施方式的电路装置40不限于使用图5、图6后述的结构,还可以实施各种变形。

[0085] 图5是作为本实施方式的电路装置40的逐次比较型A/D转换电路的结构例。该电路装置40包含电容电路(CAR1、SAR1、CAR2、SAR2)、以及输出开关控制信号(SC1、SC2)的控制电路50(处理部、逻辑部)。例如,电路装置40(A/D转换电路)包含:比较电路CP(比较器),其比较节点NC(采样节点)与电容器阵列(CAR1、CAR2)连接;D/A转换电路42(DAC1、DAC2),其具有电容器阵列(CAR1、CAR2)和开关阵列(SAR1、SAR2),进行电荷再分配型的D/A转换;以及控制电路50。并且,控制电路50根据比较电路CP的比较结果(CPQ),生成开关控制信号(SC1、SC2),输出至开关阵列(SAR1、SAR2)。

[0086] 具体而言,D/A转换电路42(与图1的DAC对应)包含MSB侧(高位侧)的D/A转换电路DAC1、LSB侧(低位侧)的D/A转换电路DAC2以及子D/A转换电路SDAC。MSB侧的D/A转换电路DAC1具有电容器阵列CAR1和开关阵列SAR1。LSB侧的D/A转换电路DAC2具有电容器阵列CAR2和开关阵列SAR2。例如,电容器阵列CAR1、CAR2的另一端与比较节点NC连接。比较节点NC与比较电路CP的反相输入端子(第1端子)连接,比较电路CP的同相输入端子(第2端子)被设定为GND(基准电压)。电容器阵列CAR1、CAR2的一端分别与开关阵列SAR1、SAR2连接。并且,开关阵列SAR1、SAR2分别由来自控制电路50的开关控制信号SC1、SC2进行开关控制。

[0087] 另外,子D/A转换电路SDAC是各种调节用的D/A转换电路,具有电容器阵列SCAR和开关阵列SSAR。电容器阵列SCAR的另一端与比较节点NC连接,电容器阵列SCAR的一端与开关阵列SSAR连接。开关阵列SSAR由来自控制电路50的开关控制信号SC3进行开关控制。利用子D/A转换电路SDAC能够实现电容偏差的微调、码移位等处理。

[0088] 控制电路50进行逐次比较的A/D转换用的各种处理。并且,将开关控制信号SC1、SC2输出至D/A转换电路DAC1、DAC2。例如,控制电路50具有逐次比较寄存器52,生成逐次比较用数据,该逐次比较寄存器52的寄存器值根据来自比较电路CP的比较结果信号CPQ来设定。D/A转换电路42为对该逐次比较用数据进行D/A转换的电路。具体而言,从控制电路50输出与逐次比较用数据对应的开关控制信号SC1、SC2。并且,D/A转换电路42的D/A转换电路DAC1、DAC2根据开关控制信号SC1、SC2进行电荷再分配型的D/A转换。

[0089] 在该情况下,控制电路50对MSB侧的D/A转换电路DAC1输出基于DEM(Dynamic Element Matching)控制的开关控制信号SC1。作为DEM控制,例如可以采用循环方式的方法。通过进行这样的DEM控制,能够使电容器阵列中的、根据开关控制信号(逐次比较用数

据)选择出的电容器的组合模式具有随机性,从而能够提高电容器的外观上的电容的比精度。

[0090] 此外,在图5的电路装置40中还设有电压生成电路60。作为电压生成电路60,可以使用电阻型DAC(电阻梯型DAC、R2-R梯型DAC)。该电压生成电路60生成用二进制数进行加权得到的电压V1~V9,提供给LSB侧的D/A转换电路DAC2。例如,生成 $V9=VDD/2$ 、 $V8=VDD/4$ 、 $V7=VDD/8$ 、 $V6=VDD/16 \dots V1=VDD/512$ 这样的电压,提供给D/A转换电路DAC2。D/A转换电路DAC2使用这些电压V1~V9进行电荷再分配型的D/A转换。

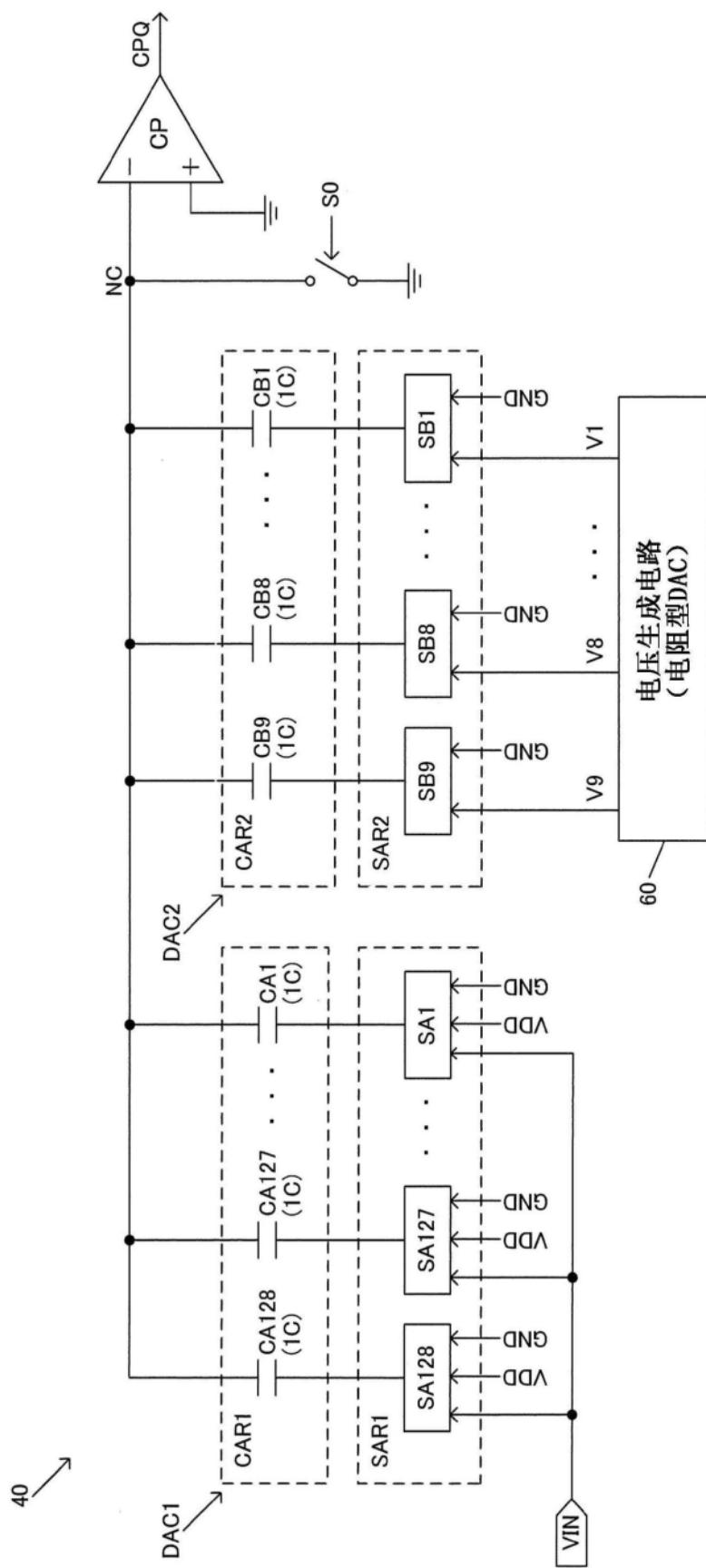

[0091] 图6是作为本实施方式的电路装置40的A/D转换电路的详细结构例。该A/D转换电路进行16位的逐次比较的A/D转换。该16位的A/D转换例如是通过基于MSB侧的D/A转换电路DAC1的7位电荷再分配型的D/A转换以及基于LSB侧的D/A转换电路DAC2的9位电荷再分配型的D/A转换实现的。

[0092] MSB侧的D/A转换电路DAC1的电容器阵列CAR1具有另一端与比较节点NC连接的电容器CA1~CA128。上述电容器CA1~CA128是电容值为1C的单元电容(单位电容)。开关阵列SAR1具有开关电路SA1~SA128,电容器CA1~CA128的一端与开关电路SA1~SA128的一端连接。开关电路SA1~SA128的另一端被提供输入电压(模拟输入信号VIN)、高电位侧的基准电压VDD以及低电位侧的基准电压GND。开关电路SA1~SA128由DEM控制的开关控制信号SC1进行开关控制。此外,比较节点NC与用于控制低电位侧的基准电压GND的提供/不提供的开关电路S0连接。

[0093] LSB侧的D/A转换电路DAC2的电容器阵列CAR2具有另一端与比较节点NC连接的电容器CB1~CB9。上述电容器CB1~CB9是电容值为1C的单元电容。开关阵列SAR2具有开关电路SB1~SB9,电容器CB1~CB9的一端与开关电路SB1~SB9的一端连接。开关电路SB1~SB9的另一端被提供来自电压生成电路60(电阻型DAC)的电压V1~V9和低电位侧的基准电压GND。例如开关电路SB1被提供电压V1和GND,开关电路SB2被提供电压V2和GND。其它开关电路SB3~SB9也同样。

[0094] 对图6的电路装置40的动作简单地进行说明。在模拟输入信号VIN的采样期间内,通过开关电路S0的接通而使比较节点NC与GND连接,MSB侧的D/A转换电路DAC1的开关电路SA1~SA128选择VIN。这时,LSB侧的开关电路SB1~SB9例如选择GND。由此,VIN被提供给电容器CA1~CA128的一端,与VIN对应的电荷蓄积在电容器中。然后,在采样期间结束后,进行基于逐次比较的A/D转换动作。

[0095] 该情况下,开关电路S0断开,比较节点NC的电位与开关电路SA1~SA128、开关电路SB1~SB9的控制状态对应地发生变化。D/A转换电路DAC1的开关电路SA1~SA128例如由循环方式的DEM控制进行开关控制。例如,首先,DEM的指针被设定在电容器CA1的位置(例如P=0)。然后,从该指针的位置起由与逐次比较数据(特别是其中的高7位)对应的开关控制信号SC1确定的n个开关电路SA1~SAn选择VDD,其余的128-n个开关电路SAn+1~SA128选择GND。由此,对电容器CA1~CAn的一端提供VDD,对电容器CAn+1~CA128的一端提供GND。例如,如果逐次比较数据的高7位是“1000000”,则n=64。

[0096] 然后,根据比较电路CP的比较结果信号CPQ是高电平(有效电平)还是低电平(非有效电平)来更新转换范围的上限值和下限值中的至少一方,根据更新后的上限值和下限值来进行逐次比较数据的更新。关于更新的具体方法将在后面叙述。在D/A转换电路DAC1中,

只要根据DEM指针P和更新后的逐次比较数据来确定开关电路SA1～SA128中的、选择VDD的开关电路以及选择GND的开关电路即可。

[0097] 这样,进行针对模拟输入信号VIN的逐次比较处理。并且,在下一个逐次比较处理中使用逐次比较处理结束时最后的选择电容器位置的下一个电容器位置。例如,在逐次比较处理结束时、开关电路SA1～SA40选择VDD(P=0)、开关电路SA41～SA128选择GND的情况下,在下一个逐次比较处理的周期中,使用表示电容器CA40的下一个电容器CA41的值(P=40)作为DEM指针P来进行DEM控制。

[0098] 另一方面,在LSB侧的D/A转换电路DAC2中,不进行这样的DEM控制。然后,D/A转换电路DAC2使用输入到开关电路SB1～SB9中的以二进制数进行加权而得到的电压V1～V9,进行电荷再分配的D/A转换。通过设为这样的结构,即使不采用在D/A转换电路DAC1与D/A转换电路DAC2之间设置串联电容器的结构,也能够实现高分辨率/高精度的A/D转换。

[0099] 3.逐次比较处理的细节

[0100] 接下来,对本实施方式中的逐次比较处理的细节进行说明。首先,说明在输出相同的比较结果达到规定次数的情况下扩展转换范围的方法的详细流程。然后,对通过附加冗余范围来提高比较处理的精度的方法进行说明。进而,说明在难以附加冗余范围时也通过进行微小信号判定来进行应对的方法。

[0101] 3.1转换范围的扩展

[0102] 首先,对扩展转换范围的方法进行说明。另外,这里的“扩展”狭义上是指通过转换范围的更新而使转换范围的大小(幅度,上限值-下限值的值)变大,但不限于此。转换范围的扩展也可以包含通过转换范围的更新将此前不包含在转换范围内的范围重新追加到转换范围中的情况。例如,在增大上限值并以其以上的增大幅度增大下限值的情况下,在此,也认为是“转换范围的扩展”。

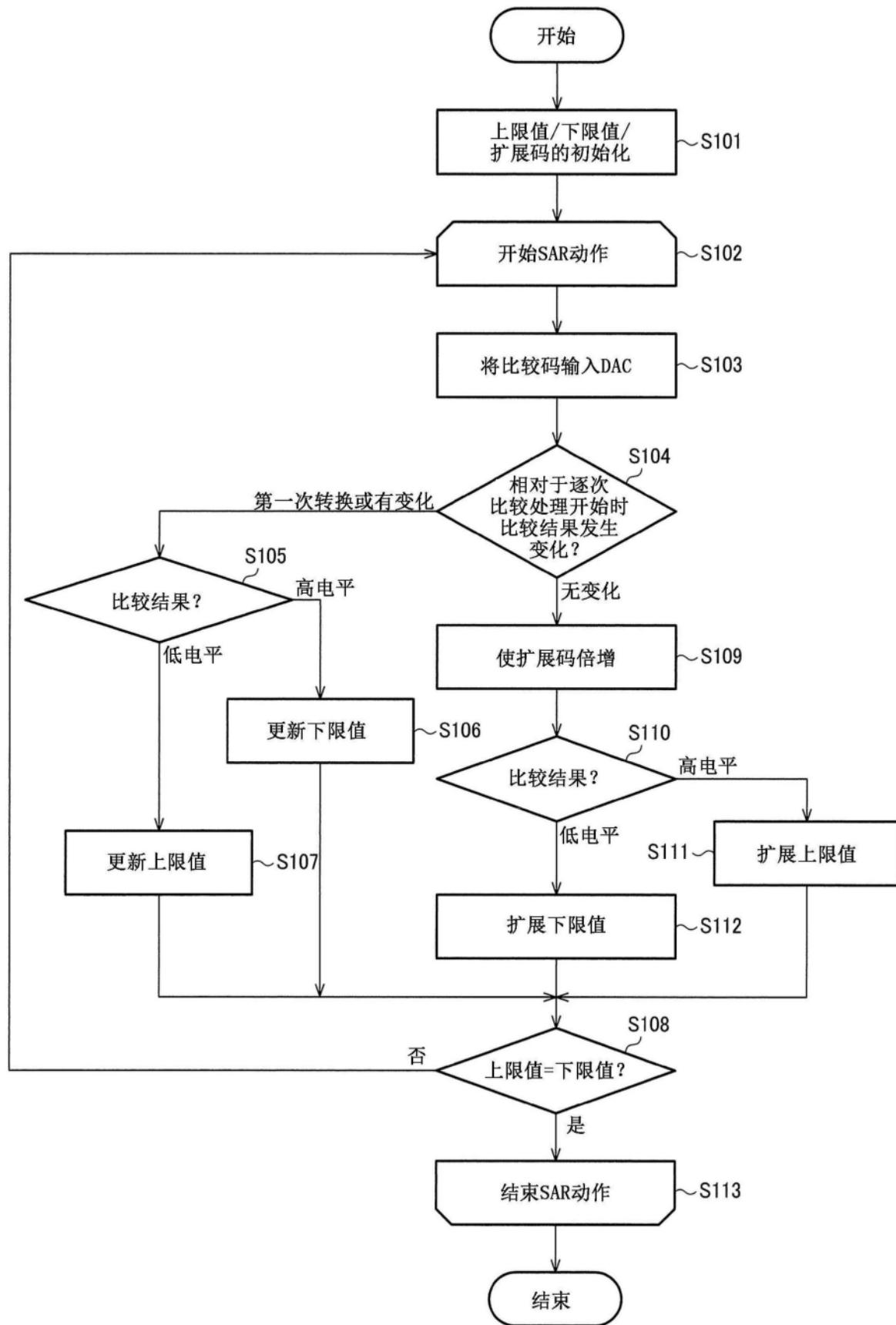

[0103] 图7是说明由控制电路50进行的逐次比较处理的流程图。图8是上限值、下限值和比较码(逐次比较数据)的更新例。此外,图9和图10是进行寄存器动作的说明图。以下,沿图7的流程图说明由控制电路50进行的处理的流程,并且,适当参照图8～图10对各步骤的详细情况和具体例进行说明。另外,在图8中,由于考虑进行16位的A/D转换,因此,与满量程电压VFS对应的数字数据的满量程为0以上且小于65536。

[0104] 当逐次比较处理开始时,首先,控制电路50进行转换范围的上限值、下限值、扩展码的初始化处理(步骤S101)。可以将逐次比较处理开始时的转换范围设为包含上次的A/D转换结果数据的规定范围。然后,控制电路50将该规定范围的上限值设定为上限值寄存器的值,将该规定范围的下限值设定为下限值寄存器的值。

[0105] 这样,能够以上次的A/D转换结果数据为基准来设定转换范围的初始值。可以认为:虽然还取决于A/D转换结果数据的取得率(逐次比较处理的执行率)以及模拟输入信号VIN的特性,但是,从上次的逐次比较处理到本次的逐次比较处理的期间内,模拟输入信号VIN往往变化不大。由此,通过设定包含上次的A/D转换结果数据的转换范围,能够提高正确数据存在于转换范围内的可能性,从而能够实现转换处理的高速化等。

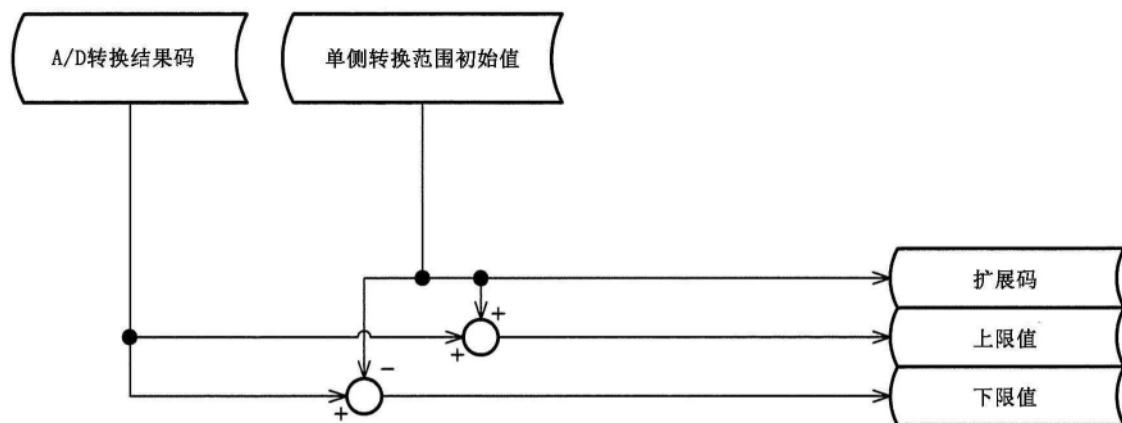

[0106] 图9是说明上限值寄存器53、下限值寄存器54、扩展码寄存器的动作的图。如图9所示,控制电路50将对上次的A/D转换结果数据加上单侧转换范围初始值后的数据作为上限值保存在上限值寄存器53中,将从上次的A/D转换结果数据中减去单侧转换范围初始值后

的数据作为下限值保存在下限值寄存器54中。这里的单侧转换范围初始值是与上述规定范围的幅度的1/2的大小对应的值。即,可以利用图9所示的初始化使转换范围的初始值成为以上次的A/D转换结果数据为中心的规定范围。

[0107] 此外,这里的扩展码是表示增大上限值时的增大幅度或减小下限值时的减小幅度的数字数据。关于扩展码的初始值可以进行各种设定,但是,在图9的例子中,控制电路50将单侧转换范围初始值作为扩展码的初始值保存在扩展码寄存器中。

[0108] 图8的C1~C3与步骤S101对应。将上限值设定得比上次的A/D转换结果数据(C1)高单侧转换范围初始值(C2),将下限值设定得比上次的A/D转换结果数据(C1)低单侧转换范围初始值(C3)。以由C2、C3确定的转换范围为对象,执行比较电路CP中的第一次比较处理。

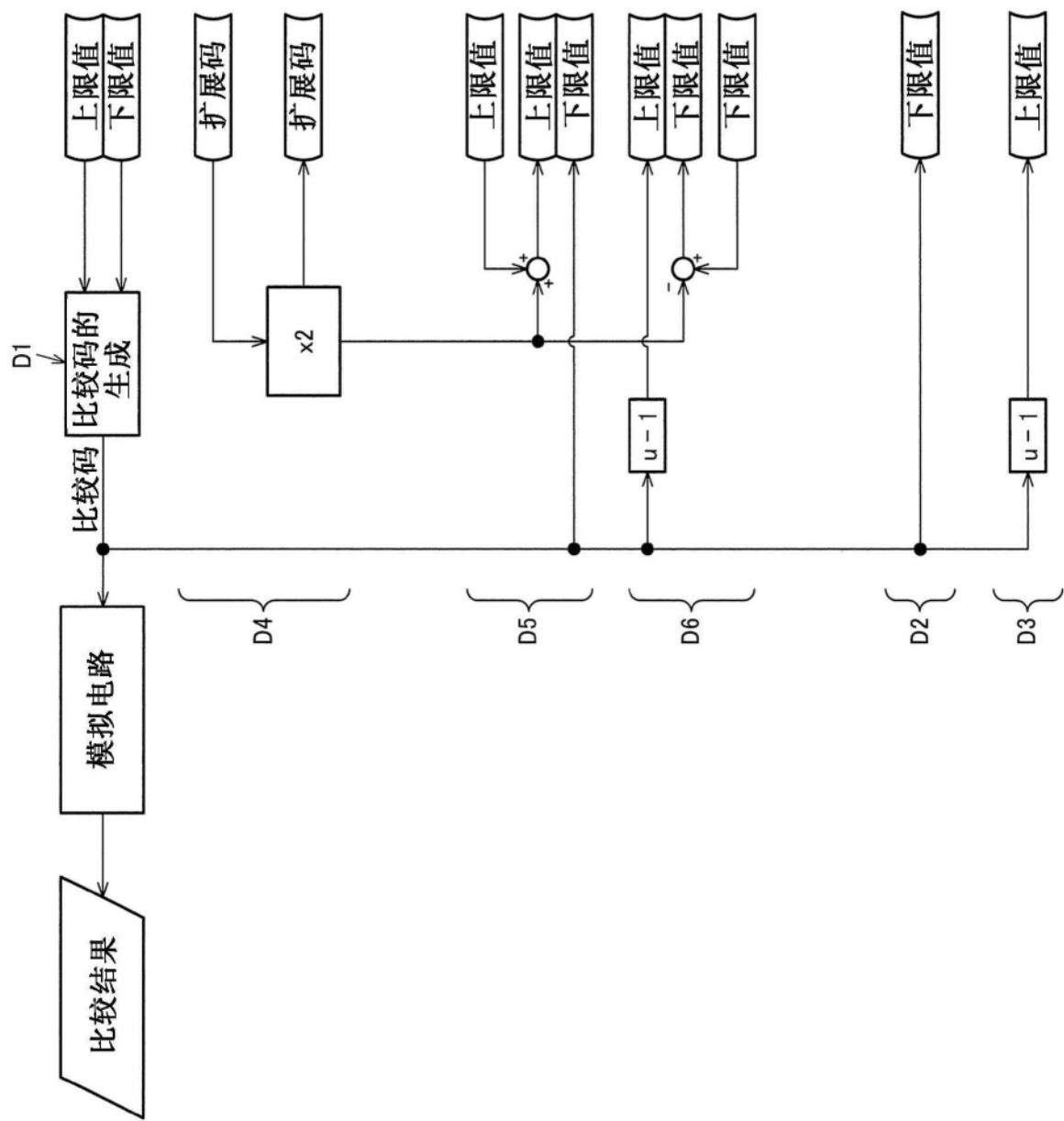

[0109] 在设定初始值之后,控制电路50开始逐次比较的循环处理(步骤S102)。首先,控制电路50生成比较码,将比较码输入到D/A转换电路DAC中(步骤S103)。如图10的D1所示,根据上限值和下限值生成比较码。将比较码设为小于上限值且大于下限值的值即可。例如,控制电路50可以将上限值与下限值的平均值或接近平均值的值作为比较码。

[0110] 接下来,控制电路50根据作为比较电路CP的输出的比较结果(比较结果信号CPQ),判定比较结果是否相对于逐次比较处理开始时发生了变化(步骤S104)。在第一次比较的情况下、或比较结果发生了变化的情况下,转移至步骤S105。

[0111] 控制电路50判定比较结果(步骤S105),根据比较结果更新上限值或下限值。具体而言,在比较电路CP输出了模拟输入信号VIN的电压电平为来自D/A转换电路DAC的输出信号DQ(比较码的D/A转换结果)的电压电平以上的比较结果的情况下,控制电路50使下限值增大。此外,在比较电路CP输出了模拟输入信号VIN的电压电平小于来自D/A转换电路DAC的输出信号DQ的电压电平的比较结果的情况下,控制电路50进行使上限值减小的更新。以下,将模拟输入信号的电压电平为来自D/A转换电路DAC的输出信号DQ的电压电平以上的比较结果表述为“高电平”,将模拟输入信号的电压电平小于来自D/A转换电路DAC的输出信号DQ的电压电平的比较结果表述为“低电平”。

[0112] 如图7所示,控制电路50在比较电路CP的输出为高电平的情况下更新下限值(步骤S106),在比较电路CP的输出为低电平的情况下更新上限值(步骤S107)。具体而言,在比较结果为高电平的情况下,可以认为正确数据处于比较码以上的范围内。由此,如图10的D2所示,控制电路50进行以比较码的值为下限值的更新即可。此外,在比较结果为低电平的情况下,可以认为正确数据处于小于比较码的范围内。由此,如图10的D3所示,控制电路50进行以从比较码减1后的值为上限值的更新即可。

[0113] 在图8中,正确数据与C4的虚线对应。由此,在使用根据转换范围的初始值(C2,C3)设定的比较码(C5)的比较处理中,输出高电平的结果。由此,控制电路50将下限值更新为比较码的值(C6)。在该情况下,上限值维持上次的值(C7)。

[0114] 在上限值、下限值的更新之后,控制电路50判定是否上限值=下限值(步骤S108)。在步骤S108中为“是”的情况下,结束循环处理(步骤S113),1次的逐次比较处理也结束。

[0115] 在步骤S108中为“否”的情况下,继续从步骤S102开始的循环处理。具体而言,控制电路50将逐次比较数据更新为与更新后的上限值以及下限值的平均值对应的值(步骤S103),对比较结果进行判定。这样,能够生成与上限值、下限值的更新结果对应的逐次比较数据,因此,能够通过反复进行比较处理,求出A/D转换结果数据。

[0116] 在图8的例中,根据下限值C6和上限值C7生成比较码C8。在此,C4>C8,因此,第二次的比较结果也为高电平。即,比较结果相对于逐次比较处理开始时没有发生变化,即,输出相同的比较结果达到规定次数(在此为两次)。由此,控制电路50在步骤S104中判定为“无变化”,进行扩展转换范围的处理。

[0117] 首先,控制电路50进行增加扩展码的更新(步骤S109)。例如,如图10的D4所示,进行使扩展码成为此前的值的2倍的处理即可,能够通过移位运算等实现。如上所述,扩展码与上限值的增大幅度或下限值的减小幅度对应。如果扩展码的值过大,则转换范围的幅度容易变大,因此,直到收敛为止的周期数(直到上限值=下限值且求出A/D转换结果数据为止的周期数)增多,可能损害高速化的效果。另一方面,如果扩展码的值过小,则所需的扩展次数增加,直到收敛为止的周期数还是会增多。由此,在本实施方式中,将扩展码的初始值抑制为某种程度的值,然后,在每次执行扩展时增加扩展码来取得平衡。由此,如果正确数据相对于转换范围的偏离程度较小,则不用过度扩大转换范围,在正确数据相对于转换范围的脱离程度较大的情况下,也能够以较少的扩展次数将正确数据适当地包含在转换范围内。另外,还可以实施在后级进行步骤S109的处理、或者不进行扩展码的更新等各种变形。

[0118] 然后,控制电路50进行比较结果的判定(步骤S110),在比较电路CP输出模拟输入信号VIN的电压电平为来自D/A转换电路DAC的输出信号DQ的电压电平以上的比较结果(高电平)达到规定次数以上的情况下,进行增大上限值的更新,在比较电路CP输出模拟输入信号VIN的电压电平小于来自D/A转换电路DAC的输出信号DQ的电压电平的比较结果(低电平)达到规定次数以上的情况下,进行减小下限值的更新。

[0119] 即,在步骤S110中为高电平的情况下,增大上限值(步骤S111)。具体而言,如图10的D5所示,以当前的上限值与扩展码相加后的值为新的上限值。此外,如D5所示,在步骤S111中,也可以一并进行与步骤S106同样地将比较码设为下限值的更新处理。

[0120] 此外,在步骤S110中为低电平的情况下,减小下限值(步骤S112)。具体而言,如图10的D6所示,以从当前的下限值减去扩展码后的值为新的下限值。此外,如D6所示,在步骤S112中,也可以一并进行与步骤S107同样地将从比较码减1后的值设为上限值的更新处理。另外,根据以上说明可知:在一次的更新处理中,进行图10的D2、D3、D5、D6中的某一个。

[0121] 在图8的例子中,第二次的比较结果也为高电平。因此,执行步骤S111、图10的D5的处理。具体而言,控制电路50将下限值更新为比较码的值(C9),使上限值增大与扩展码相应的大小(C10)。

[0122] 根据本实施方式的方法,能够根据比较结果的历史来扩展转换范围。根据图8的C2与C4的比较可知:在正确数据处于转换范围外的情况下,高电平或低电平的比较结果是连续的。由此,在本实施方式中,以输出相同的比较结果达到规定次数为触发而扩展转换范围。这样,无需进行专用的比较处理即可扩展转换范围,从而能够抑制高速化的效果被损害。例如,如果是本实施方式的方法,则上限值的D/A转换结果与模拟输入信号VIN的比较、或下限值的D/A转换结果与模拟输入信号VIN的比较不是必须的。

[0123] 之后的处理也同样,执行步骤S102~步骤S112所示的循环处理直到在步骤S108中判定为“是”为止即可。如果是图8的例,则第三次的比较中使用的比较码(C11)的D/A转换结果大于模拟输入信号VIN,因此,判定为低电平,从而通过步骤S107的处理更新上限值(C12)。此后,不需要转换范围的扩展,利用步骤S106或步骤S107的处理缩小转换范围,在上

限值=下限值时,将此时的下限值(或上限值)的值作为A/D转换结果数据即可。

[0124] 另外,如图7的步骤S104所示,在逐次比较处理中,在比较电路CP从第一次的比较起输出相同的比较结果达到规定次数以上的情况下,控制电路50进行增大上限值的更新和减小下限值的更新中的至少一方。

[0125] 因此,例如,在上述规定次数为两次且第一次至第三次的比较结果为低电平→高电平→高电平的情况下,输出了两次高电平,但是,无需进行增大上限值的更新。同样地,在第一次至第三次的比较结果为高电平→低电平→低电平的情况下,无需进行减小下限值的更新。

[0126] 如果已经至少进行了一次低电平的输出,则正确数据小于此时的比较码。即,可以认为:在现在的上限值的设定中,已将正确数据包含在转换范围内。由此,即使之后高电平的判定是连续的,通过增大上限值而扩展转换范围的意义也不大。在至少进行一次高电平的输出之后输出低电平达到规定次数的情况下也是同样。考虑到以上情况,在本实施方式中,将“从第一次的比较起输出相同的比较结果达到规定次数以上”用作转换范围扩展的条件。由此,能够抑制必要性小的扩展处理,因此,能够实现适当的高速化。

[0127] 如后述那样,虽然可能有时在比较电路CP中发生误判定,但是,该情况下,模拟输入信号VIN与比较码的D/A转换结果也接近(后述的“微小信号”)到发生误判定的程度。由此,通过后述的冗余范围附加或多次判定即可应对,可以不进行转换范围的扩展。

[0128] 此外,控制电路50在上限值达到逐次比较数据的满量程的上限的情况下将上限值更新为满量程的上限,在下限值达到逐次比较数据的满量程的下限的情况下,将下限值更新为满量程的下限。

[0129] 如上所述,上限值、下限值增大或减小与扩展码相应的大小。因此,根据更新前的上限值、下限值和扩展码的状态,可能存在上限值+扩展码超过满量程的上限值(如果是16位,则为65536以上)的情况或下限值-扩展码超过满量程的下限值(小于0)的情况。该情况下,即使超过满量程的范围包含在转换范围内也意义不大。此外,由于由上限值和下限值确定的逐次比较数据过于接近满量程的上限值下限值,可能还存在成为低效的搜索,在极端的例子中,还可能逐次比较数据超过满量程的上限值下限值而无法适当的比较。

[0130] 在这方面,通过将上限值和下限值保持在满量程的上限、下限,能够实现适当的逐次比较处理。如果是上述图3的例子,在B6所示的范围内,高电平的输出是连续的,但是,由于上限值到达了满量程的上限,因此不会进一步增大。

### [0131] 3.2冗余范围附加

[0132] 接下来,对用于提高转换精度的冗余范围附加处理进行说明。可以认为:根据使用了图7~图10的处理,在模拟输入信号VIN的变化较大的情况下也能够执行适当的转换。但是,在实际的电路装置40中,必须考虑产生误差的可能性。具体而言,存在如下可能性:尽管模拟输入信号VIN为比较码的D/A转换结果以上(小于),比较电路CP还是错误地输出低电平(高电平)。该情况下,由于进行图10的D2或D3的更新而导致正确数据处于转换范围外,从而无法进行适当的转换。如果是上述图7的处理流程,则还限定了扩展转换范围的机会,根据误判定的产生时刻的不同,难以进行之后的补救。

[0133] 由此,控制电路50可以进行如下冗余范围附加处理:在比较电路CP输出模拟输入信号VIN的电压电平为来自D/A转换电路DAC的输出信号DQ的电压电平以上的比较结果的情

况下,将下限值更新为更新前的下限值与逐次比较数据之间的值,在比较电路CP输出模拟输入信号VIN的电压电平小于来自D/A转换电路DAC的输出信号DQ的电压电平的比较结果的情况下,将上限值更新为更新前的上限值与逐次比较数据之间的值。

[0134] 这样,与图10的D2或D3的更新相比,能够扩大转换范围。具体而言,在利用D2的更新增大了下限值的情况下处于转换范围外的区域的一部分、或者在通过D3的更新减小了上限值的情况下处于转换范围外的区域的一部分留在转换范围内。由此,即使在发生了误判定的情况下,也能够提高正确数据处于转换范围内的可能性,从而能够实现适当的转换。

[0135] 图11是说明进行冗余范围附加处理时的逐次比较处理的流程图。图12是上限值、下限值和比较码的更新例。图13和图14是说明寄存器动作的图。

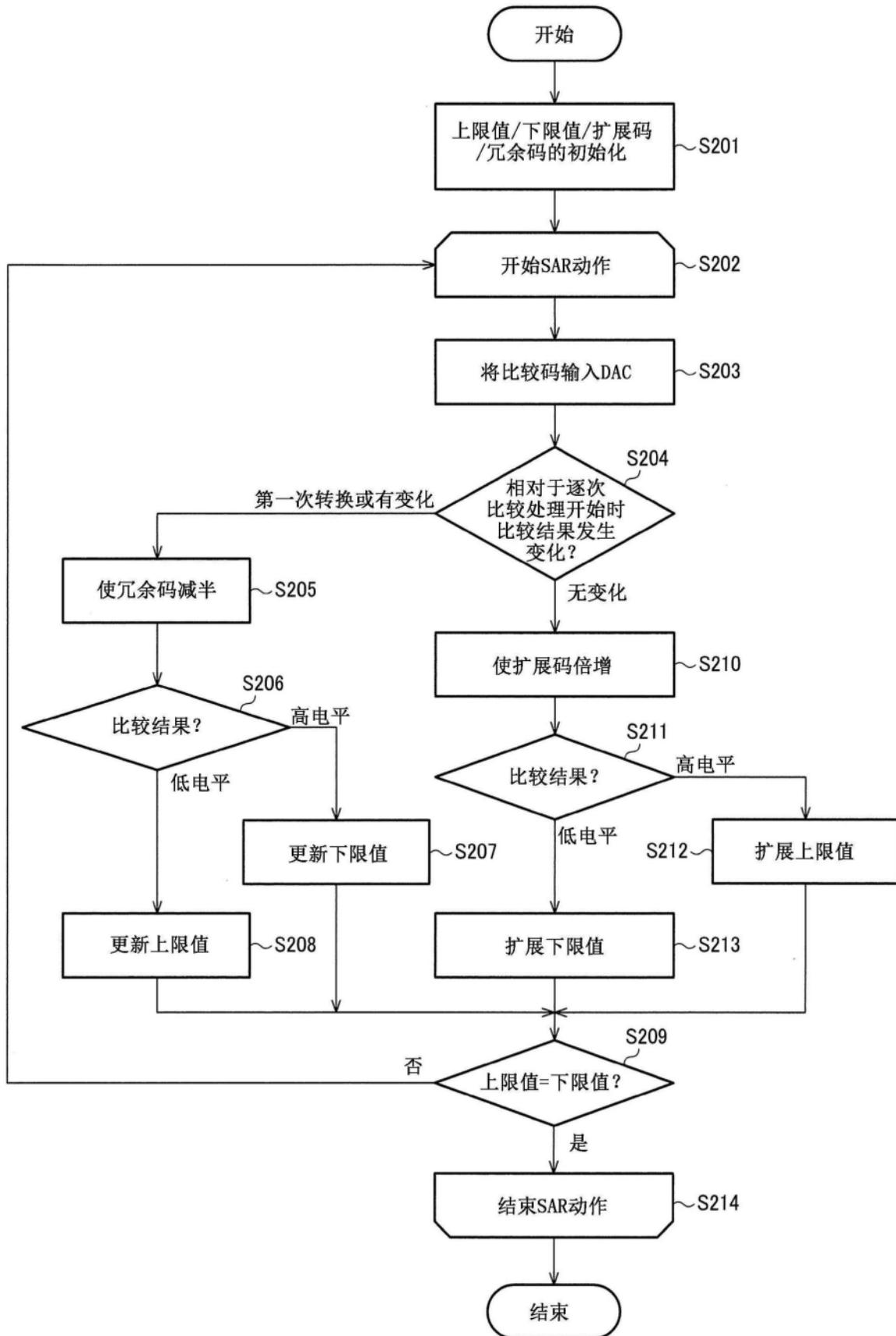

[0136] 当逐次比较处理开始时,首先,控制电路50进行转换范围的上限值、下限值、扩展码、冗余码的初始化处理(步骤S201)。关于上限值、下限值、扩展码,与图7的步骤S101相同。此外,冗余码是表示冗余范围的幅度(相比于图10的D2、D3扩大转换范围的幅度)的信息。

[0137] 图13是说明上限值寄存器、下限值寄存器、扩展码寄存器、冗余码寄存器的动作的图。如图13所示,关于冗余码设定某个初始值,在步骤S201的处理中,控制电路50将该冗余码初始值作为冗余码存储在冗余码寄存器中。

[0138] 关于图11的步骤S202~S204、步骤S209~S214,与图7的步骤S102~S104、步骤S108~S113同样,因此,省略详细的说明。同样地,图14的F1、F4~F6与图10的D1、D4~D6同样,因此,省略详细的说明。

[0139] 在进行冗余范围附加处理时,控制电路50使用冗余码来进行上限值或下限值的更新处理。具体而言,在步骤S204中,在第一次比较的情况下、或者在比较结果发生了变化的情况下,首先,控制电路50进行冗余码的更新处理(步骤S205)。具体而言,如图14的F7所示那样进行使冗余码成为此前的值的1/2的处理即可。

[0140] 然后,控制电路50判定来自比较电路CP的比较结果(步骤S206),在高电平的情况下更新下限值(步骤S207),在低电平的情况下更新上限值(步骤S208)。步骤S207中的寄存器动作与图14的F2对应,步骤S208中的寄存器动作与F3对应。

[0141] 如F2所示,在判定为高电平的情况下,控制电路50不将比较码本身作为下限值,而是将比较码-冗余码的值作为新的下限值。此外,如F3所示,在判定为低电平的情况下,控制电路50不将比较码-1作为上限值,而是将比较码-1+冗余码的值作为新的上限值。

[0142] 图12示出上限值、下限值和比较码的更新例。E1与上次的A/D转换结果数据对应,E4的虚线表示与本次的模拟输入信号VIN对应的正确数据。利用步骤S201和图13的处理来确定上限值的初始值(E2)和下限值的初始值(E3),利用步骤S203和图14的F1的处理来设定比较码的初始值E5。

[0143] 作为第一次的比较结果,输出高电平,因此,进行基于步骤S207的下限值更新处理。这时,如果是图10的D2的例子,则新的下限值与E5所示的逐次比较数据相等(E6),但是,利用冗余范围的附加而将新的下限值更新为比E6小与冗余码相应的大小的值(E7)。这样,可以将E7以上且小于E6的范围作为转换范围,从而能够抑制误判定造成的影响。

[0144] 此外,根据下限值(E7)和上限值(E8=E2),将E9所示的值设定为新的比较码。并且,在图12所示的例子中,正确数据E4>比较码E9,但是,由于E9和E4非常接近,因此,在第二次的比较处理中发生误判定,原本应该输出高电平,但输出了低电平。

[0145] 如果是图10的D3的例子，则新的上限值是从比较码E9减1后的值(E10)，正确数据E4偏离转换范围。但是，如果是F3所示的更新，则上限值被更新为比E10大与冗余码相应的大小的值(E11)。在图12中，可以是E11>E4，因此，正确数据处于转换范围内，能够抑制由误判定造成的影响。这样，通过进行冗余范围附加处理，能够提高转换精度。

[0146] 但是，在附加了冗余范围的情况下，与不附加的情况相比，转换范围的幅度变大(转换范围的缩小幅度变小)，因此，直到收敛成上限值=下限值的状态为止的周期数增加。特别是，如果尽管转换范围本身已经缩小还继续附加冗余范围，则由于所附加的冗余范围的影响，可能永远不收敛。

[0147] 由此，控制电路50在由上限值和下限值设定的转换范围的大小小于规定范围幅度的情况下跳过冗余范围附加处理即可。这样，由于在转换范围小于规定范围幅度的情况下不附加冗余范围，因此，能够适当地收敛成上限值=下限值的状态。此外，反过来说，在转换范围较大的情况下能够进行冗余范围的附加，在该条件下，能够抑制由误判定造成的影响。即，能够进行与情况对应的冗余范围附加。

[0148] 另外，可以考虑各种用于判定转换范围的大小是否小于规定范围幅度的方法。例如，也可以从寄存器取得上限值和下限值，将其差分值作为转换范围的大小。并且，将规定范围幅度的值预先另行存储在寄存器中，控制电路50进行上述差分值与规定范围幅度的比较处理即可。

[0149] 或者，鉴于由于减小上限值的更新或增大下限值的更新而使转换范围的大小缩小，也可以不是求出转换范围的大小本身，而是进行考虑了步骤S207或步骤S208的处理的执行次数的处理。具体而言，如图11的步骤S205所示，在步骤S207或步骤S208的前级，进行使冗余码成为1/2的处理。这样，每当缩小转换范围时，冗余码被更新得更小，由此，利用规定次数的更新而使冗余码成为0。如果冗余码成为0，则F2、F3的处理与D2、D3同样，跳过冗余范围附加处理。即，在步骤S205所示的处理中，也可以根据转换范围的大小对是否进行冗余范围附加进行切换。另外，还可以在步骤S207或S208的后级进行步骤S205的处理、或者使冗余码的更新处理成为与图14的F7不同的处理等实施各种变形。

[0150] 此外，在逐次比较处理中，控制电路50也可以在比较电路CP输出相同的比较结果达到规定次数以上的情况下跳过冗余范围附加处理。这里的“冗余范围附加处理的跳过”表示不进行冗余范围附加处理，更具体来说，表示在不附加冗余范围的情况下进行上限值或下限值的更新处理。例如，如果是图11的流程图，则在步骤S204中判定为无变化的情况下进行步骤S212或S213的处理，可以通过图14的F5实现步骤S212，可以通过图14的F6实现步骤S213。并且，F5、F6与图10的D5、D6同样，在F5中，下限值被更新为比较码的值，在F6中，上限值被更新为比较码-1的值，不使用冗余码。

[0151] 如上所述，扩展转换范围的情况是怀疑正确数据位于转换范围外的情况。例如，高电平连续的情况是存在正确数据大于转换范围的上限值的可能性的情况。该情况下，不太需要考虑正确数据朝小于下限值的方向偏离的可能性，将冗余码用于下限值的更新的意义不大。同样地，在低电平连续的情况下，考虑正确数据小于下限值即可，不太需要考虑大于上限值的可能性。

[0152] 因此，通过排他地进行转换范围扩展和冗余范围附加，能够抑制过度地扩大转换范围的情况，能够抑制高速化的效果被损害的情况。该情况下，不是如图13、图14那样分别

设置冗余码寄存器和扩展码寄存器，而是共同利用一个寄存器。此外，与F4～F6所示的扩展码相关的更新处理和与F2、F3、F7所示的冗余码相关的更新处理的处理内容相似。由此，执行该处理的电路的结构也相似，因此，也可以不分别设置两个电路，而是在双方的处理中利用一个电路。

[0153] 3.3微小信号判定

[0154] 如上所述，在转换范围的大小缩小的情况下，难以附加冗余范围。如果在不附加冗余范围的情况下发生误判定，则无法进行适当的转换。并且，比较电路CP中的误判定在模拟输入信号VIN与比较码的D/A转换结果之差较小的情况下发生的可能性大。

[0155] 由此，本实施方式的电路装置40也可以包含用于判定模拟输入信号VIN的电压电平与来自D/A转换电路DAC的输出信号DQ的电压电平之差的大小的微小信号判定电路90。并且，以利用微小信号判定电路90判定出微小信号为条件，进行多次比较处理，在微小信号判定电路判定为非微小信号的情况下，跳过多次比较处理。

[0156] 这样，在误判定的可能性大的情况下执行多次比较处理，可以根据该多次的比较处理来确定最终的比较结果。即，能够提高比较处理的精度，能够抑制误判定的发生。但是，如果执行多次比较处理，则相对应地周期数增大，损害高速化的效果。由此，在能够通过冗余范围附加处理来应对的情况下，优选利用冗余范围附加来应对，而不利用多次比较处理。

[0157] 由此，作为一例，控制电路50在由微小信号判定电路90判定为微小信号且不进行冗余范围附加处理的情况下进行多次比较处理，在由微小信号判定电路判定为非微小信号的情况下或进行冗余范围附加处理的情况下跳过多次比较处理。这样，能够抑制多次比较处理的执行次数，因此，能够抑制周期数的增大。

[0158] 图15是说明使用来自微小信号判定电路90的输出的逐次比较处理的流程图。除了图15的步骤S306和S307外的步骤与图12相同，因此，省略详细的说明。

[0159] 控制电路50判定在步骤S305的冗余码更新之后是否冗余码=0、且来自微小信号判定电路90的微小信号标志SFLAG是高电平(步骤S306)。另外，微小信号标志SFLAG是这样的标志：表示微小信号判定电路90是否判定为模拟输入信号VIN与来自D/A转换电路DAC的输出信号DQ之差小于给定的阈值、即、是微小信号。在此，示出了在判定为微小信号时SFLAG=H的例子，但是，关于这方面，可以实施各种变形。

[0160] 在步骤S306中为“否”的情况下，转移至步骤S308～S310的处理。在步骤S306中为“否”的情况对应于冗余码不是0而进行冗余范围附加处理的情况、或冗余码=0但是由于SFLAG=L因此发生误判定的可能性较小的情况。无论是哪种情况，根据一次的比较结果更新上限值或下限值都不会带来大问题。

[0161] 另一方面，在步骤S306中为“是”的情况下，则对应于尽管发生误判定的可能性大但无法进行冗余范围附加处理的情况。由此，该情况下，通过使比较电路CP进行多次动作而取得多个比较结果，根据该多个比较结果确定最终的比较结果(步骤S307)。作为一例，可以进行多个比较结果的多数决定，在高电平的次数>低电平的次数的情况下判定为高电平，在低电平的次数>高电平的次数的情况下判定为低电平。

[0162] 在进行了步骤S307的处理的情况下，在步骤S308中使用多数决定的结果进行判定，执行步骤S309或步骤S310的更新处理。

[0163] 另外，如上所述，不进行冗余范围附加处理的情况与转换范围小于规定范围幅度

的情况相当。由此,控制电路50在由上限值和下限值设定的转换范围小于上述范围幅度的情况下,对比较电路CP进行多次比较处理,执行多次模拟输入信号VIN与来自D/A转换电路DAC的输出信号DQ的比较处理。

[0164] 图16是本实施方式的比较电路CP和微小信号判定电路90的结构例。比较电路CP包含根据输入信号PIN、NIN而输出输出信号POUT、NOUT的V/T转换电路VTC。如使用图17、图18后述的那样,V/T转换电路VTC的输出信号POUT、NOUT是在给定的时刻产生从低电平到高电平的上升的步进信号,该上升时刻(相对于给定的基准时刻的延迟时间)是由输入信号(输入电压)PIN、NIN的大小来确定的。在此,对输入信号越大则延迟时间越短(较快地上升)的例子进行说明。

[0165] 在PIN>NIN的情况下,POUT先上升,之后NOUT上升。在NIN>PIN的情况下,NOUT先上升,之后POUT上升。由此,在比较电路CP中,只要将表示POUT和NOUT中的哪个的上升更快的信号作为比较结果信号CPQ输出即可。

[0166] 作为一例,如图16所示,使用两个NAND电路输出CPQ。设ND、PD分别为图16所示的端子处的信号。如图16所示,ND是通过延迟元件使NOUT延迟规定的延迟时间 $\tau$ 而得到的信号,PD是通过延迟元件使POUT延迟规定的延迟时间 $\tau$ 而得到的信号。

[0167] 输出CPQ的结构的动作以RS型触发器为基准。即,当 $(PD, ND) = (1, 0)$ 时 $CPQ = 1$ ,当 $(PD, ND) = (0, 1)$ 时 $CPQ = 0$ 。此外,如果 $(PD, ND) = (1, 1)$ ,则CPQ保持之前的状态。

[0168] 即,在PD比ND先上升的情况下 $CPQ = 1$ ,在ND比PD先上升的情况下 $CPQ = 0$ 。即,CPQ是根据PD和ND中的哪一个上升快而变化为高电平或低电平的信号,在高电平的情况下表示PIN>NIN,在低电平的情况下表示NIN>PIN。

[0169] 此外,微小信号判定电路90还包含AND电路、OR电路以及两个NAND电路。AND电路输入NOUT和POUT。OR电路输入PD和ND。

[0170] 在设AND电路的输出为 $R'$ 的情况下, $R'$ 是在与POUT和NOUT双方的上升完成的时刻对应的时刻成为高电平的步进信号。在设OR电路的输出为 $S'$ 的情况下, $S'$ 是在与PD和ND中的任意一个上升的时刻、即POUT和NOUT中的任意一方上升起经过延迟元件的延迟时间 $\tau$ 后的时刻对应的时刻成为高电平的步进信号。

[0171] 输出SFLAG的两个NAND电路的动作也以RS型触发器为基准。即,当 $(S', R') = (1, 0)$ 时SFLAG=0,当 $(S', R') = (0, 1)$ 时SFLAG=1。此外,如果 $(S', R') = (1, 1)$ 则SFLAG保持之前的状态。

[0172]  $(S', R') = (1, 0)$ 的情况对应于在从POUT和NOUT中的一方上升起经过延迟时间 $\tau$ 后的时刻也没有发生POUT和NOUT中的另一方的信号上升的情况。这相当于POUT和NOUT上升的时间差大于 $\tau$ 的情况,PIN与NIN的电压差较大。即,SFLAG=0表示非微小信号。

[0173]  $(S', R') = (0, 1)$ 的情况对应于从POUT和NOUT中的一方上升起经过延迟时间 $\tau$ 之前、也发生了POUT和NOUT中的另一方的信号上升的情况。这相当于POUT和NOUT上升的时间差小于 $\tau$ 的情况,PIN与NIN的电压差较小。即,SFLAG=1表示微小信号。

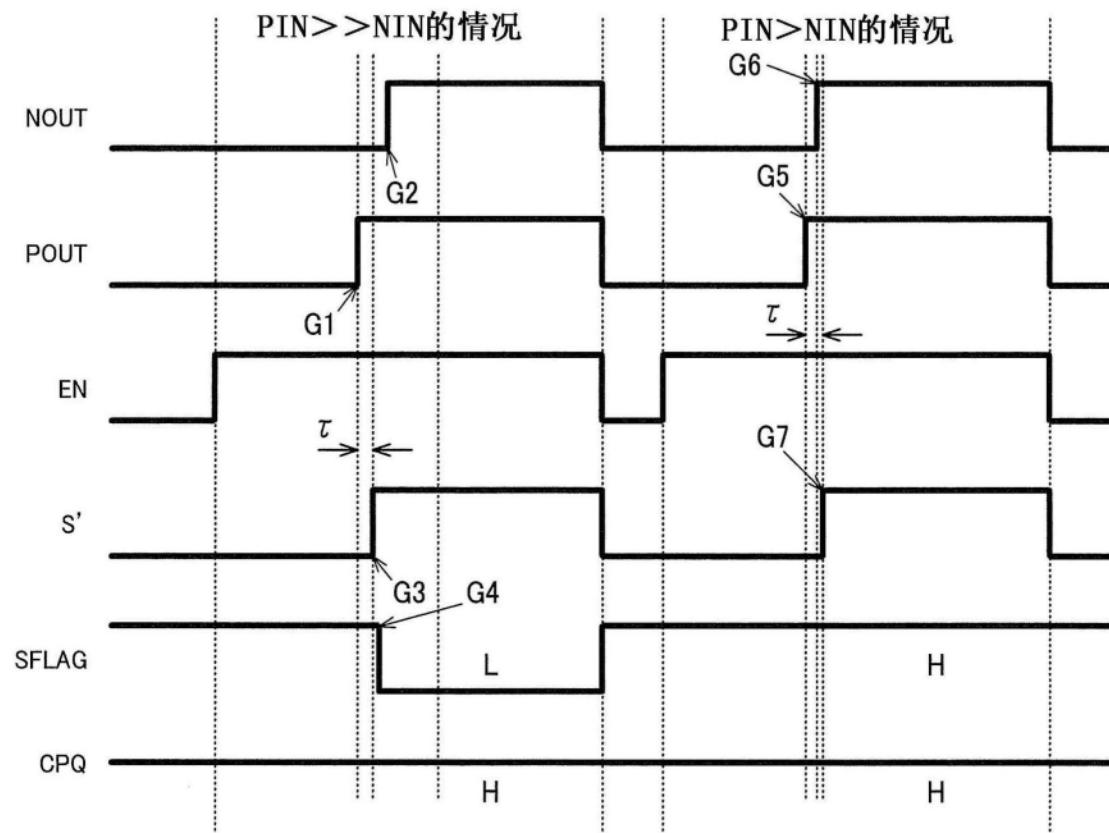

[0174] 图17是PIN>NIN时的、表示各信号的波形图。在PIN远远大于NIN的情况下,POUT先上升(G1),然后,在经过比延迟时间 $\tau$ 长的时间之后,NOUT上升(G2)。该情况下, $S'$ 在从G1经过 $\tau$ 后的时刻(G3)上升, $R'$ 在与G2对应的时刻上升。其结果是,SFLAG在与G3对应的时刻G4变化为低电平,控制电路50能够判定为非微小信号。

[0175] 另一方面,在PIN与NIN之差较小的情况下,POUT先上升(G5),然后,在经过比延迟时间 $\tau$ 短的时间之后,NOUT上升(G6)。该情况下,S' 在从G5经过 $\tau$ 后的时刻(G7)上升,R' 在与G6对应的时刻上升。其结果是,SFLAG保持为高电平,控制电路50能够判定为微小信号。此外,无论在哪种情况下,都是POUT先上升,NOUT后上升,因此,CPQ保持为高电平。

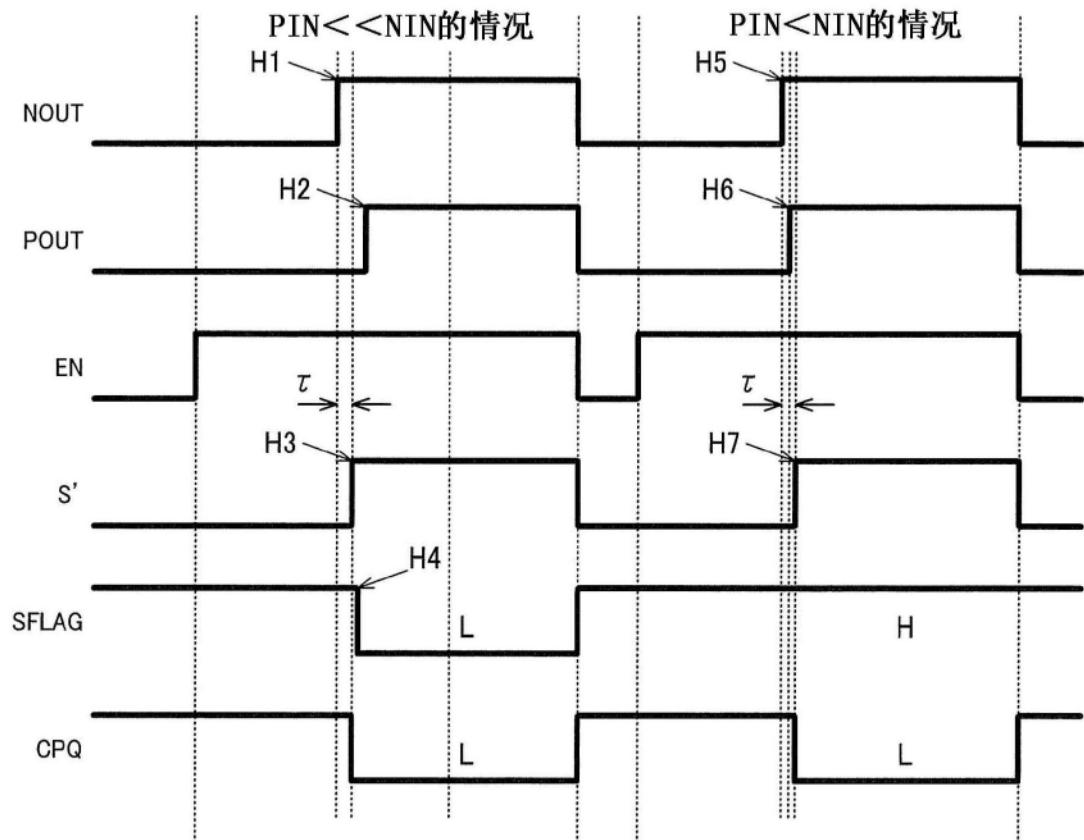

[0176] 图18是NIN>PIN时的、表示各信号的波形图。在NIN远远大于PIN的情况下,NOUT先上升(H1),然后,在经过比延迟时间 $\tau$ 长的时间之后,POUT上升(H2)。该情况下,S' 在从H1经过 $\tau$ 后的时刻(H3)上升,R' 在与H2对应的时刻上升。其结果,SFLAG在与H3对应的时刻H4变化为低电平,控制电路50能够判定为非微小信号。

[0177] 另一方面,在PIN与NIN之差较小的情况下,NOUT先上升(H5),然后,在经过比延迟时间 $\tau$ 短的时间之后,POUT上升(H6)。该情况下,S' 在从H5经过 $\tau$ 后的时刻(H7)上升,R' 在与H6对应的时刻上升。其结果是,SFLAG保持为高电平,控制电路50能够判定为微小信号。此外,无论在哪种情况下,都是NOUT先上升,POUT后上升,因此,CPQ在与从NOUT的上升时刻H1起经过延迟时间 $\tau$ 后对应的时刻变化为低电平。

[0178] 另外,微小信号判定电路90的结构不限于图16。例如,比较电路CP也可以由多个比较器构成。具体而言,使用比较电路CP,该比较电路CP除了包含比较PIN和NIN的第1比较器外,还包含比较PIN+OFFSET和NIN的第2比较器以及比较PIN和NIN+OFFSET的第3比较器。在全部比较器的比较结果相同的情况下,PIN与NIN之间存在偏置电压以上的差,因此,判定为非微小信号。另一方面,在全部比较器的比较结果不相同的情况下,PIN与NIN的电压差小于偏置电压,因此判定为微小信号。此外,关于微小信号判定电路90的结构,可以实施各种变形。

[0179] 3.4变形例

[0180] 以下,对几个变形例进行说明。

[0181] 本实施方式的电路装置40也可以以时间分割的方式对多个输入信号进行处理。例如,在将电路装置40应用于使用图19后述的物理量检测装置300的情况下,存在从物理量换能器310输出多个信号的可能性。例如,在物理量换能器310是3轴陀螺传感器元件的情况下,输入表示x轴的角速度的信号、表示y轴的角速度的信号以及表示z轴的角速度的信号。在电路装置40中,以时间分割的方式对这三个输入信号进行处理。

[0182] 该情况下,上述“上次的A/D转换结果数据”成为问题。例如,考虑在进行x轴的信号XIN的A/D转换之后再进行y轴的信号YIN的A/D转换的情况。这时,根据XIN的A/D转换结果来设定用于求YIN的A/D转换结果数据的转换范围的初始值是不合理的。使用上次的A/D转换结果数据是因为假定如果是相同种类的信号则A/D转换结果数据不会很大程度地变化,在以不同种类的信号为对象的情况下,该假定不成立。

[0183] 由此,本实施方式中的“上次的A/D转换结果数据”使用“针对相同种类的输入信号的上次的A/D转换结果数据”即可。具体而言,预先准备与数据数量对应的用于保持A/D转换结果数据的寄存器,当读出上次的A/D转换结果数据时,以所对应的寄存器为读出对象。如果是上述例,则可以预先设置保持XIN的A/D转换结果的第1寄存器、保持YIN的A/D转换结果的第2寄存器以及保持ZIN的A/D转换结果的第3寄存器,当输入了XIN(YIN,ZIN)时,从第1(第2,第3)的寄存器读出“上次的A/D转换结果数据”。

[0184] 此外,在使用图15叙述的例子中,在冗余码不是0的情况下执行冗余范围附加处

理,微小信号标志SFLAG与是否执行没有关系。但是,在微小信号标志SFLAG=L的情况下,比较电路CP中的误判定的可能性较小,因此,也可以不进行冗余范围附加处理。

[0185] 由此,也可以是,控制电路50在由微小信号判定电路90判定为微小信号的情况下进行冗余范围附加处理或多次比较处理,在由微小信号判定电路判定为非微小信号的情况下跳过冗余范围附加处理和多次比较处理。这里的冗余范围附加处理的跳过表示不附加冗余范围的上限值或下限值的更新处理。此外,多次比较处理的跳过表示在求给定的输入信号和逐次比较数据的D/A转换结果的比较处理结果时不进行多次的比较处理,具体而言,与利用一次的比较处理求给定的输入信号和逐次比较数据的D/A转换结果的比较处理结果的处理相当。如果是图15的例子,则跳过多次比较处理相当于省略步骤S307的处理(从步骤S306直接转变到步骤S308)。

[0186] 这样,在非微小信号的情况下,能够与冗余码的值无关地跳过冗余范围附加处理,从而能够抑制周期数的增大。

[0187] 4. 物理量检测装置、电子设备和移动体

[0188] 此外,本实施方式的方法还可以应用于包含上述电路装置40的各种装置。例如,本实施方式的方法可以应用于物理量检测装置,该物理量检测装置包含物理量换能器、以及进行用于检测基于来自物理量换能器的检测信号的物理量的A/D转换的电路装置。此外,本实施方式的方法还可以应用于包含电路装置40电子设备或移动体。

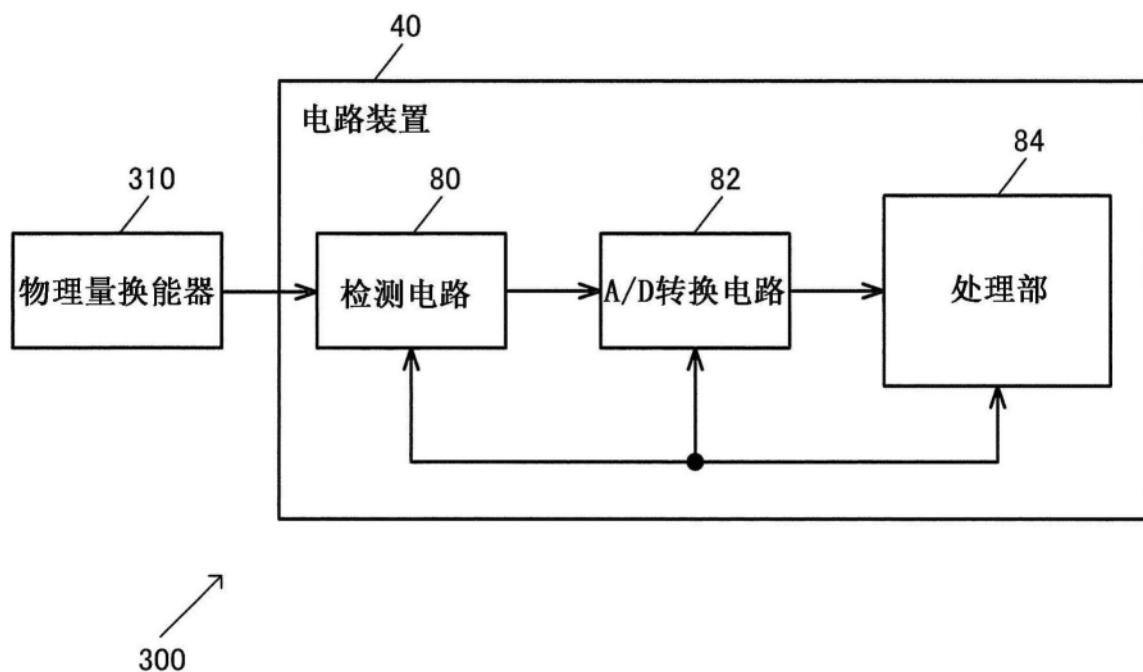

[0189] 图19示出本实施方式的物理量检测装置300的结构例。物理量检测装置300包含物理量换能器310和本实施方式的电路装置40(IC)。本实施方式的电路装置40至少包含进行逐次比较型A/D转换的A/D转换电路82,A/D转换电路82进行基于物理量换能器310的输出信号的信号的A/D转换。另外,电路装置40(A/D转换电路82)也可以是进行与基于物理量换能器310的输出信号的信号不同的信号的A/D转换的电路。物理量换能器310和电路装置40例如安装于物理量检测装置300的封装件内。另外,本实施方式的物理量检测装置300不限于图19的结构,可以实施省略其构成要素的一部分、或追加其它构成要素等各种变形。

[0190] 物理量换能器310是用于检测例如角速度、加速度等物理量的元件(传感器)。物理量换能器310例如是角速度传感器(陀螺传感器),用于检测绕一个或多个轴旋转时的角速度。该角速度传感器也可以是压电型振动陀螺仪,也可以是由硅基板等形成的静电电容检测方式的振动陀螺仪。例如可以使用双T型振动片等作为压电型振动陀螺仪。或者,物理量换能器310例如是加速度传感器,检测一个或多个轴向上的加速度。另外,物理量换能器310也可以是用于检测角速度或加速度以外的物理量(例如速度、移动距离、角加速度或压力等)的转换器。或者,物理量换能器310也可以是振荡器的振子。

[0191] 电路装置40包含检测电路80、A/D转换电路82和处理部84。检测电路80根据来自物理量换能器310的检测信号来检测与角速度或加速度等物理量对应的物理量信号。以角速度传感器为例,检测电路80可以包含放大来自物理量换能器310的检测信号的放大电路(电荷/电压转换电路)及同步检波电路等。该情况下,电路装置40也可以包含驱动物理量换能器310(振子)的驱动电路。A/D转换电路82进行由检测电路80检测出的模拟电压(期望信号的电压)的A/D转换。例如可以使用在图1等中说明的结构的电路作为A/D转换电路82。处理部84根据由A/D转换电路82进行A/D转换后的检测数据进行各种处理。例如进行各种校正处理及滤波处理(数字滤波处理)等。另外,处理部84也可以作为图1的控制电路50动作。

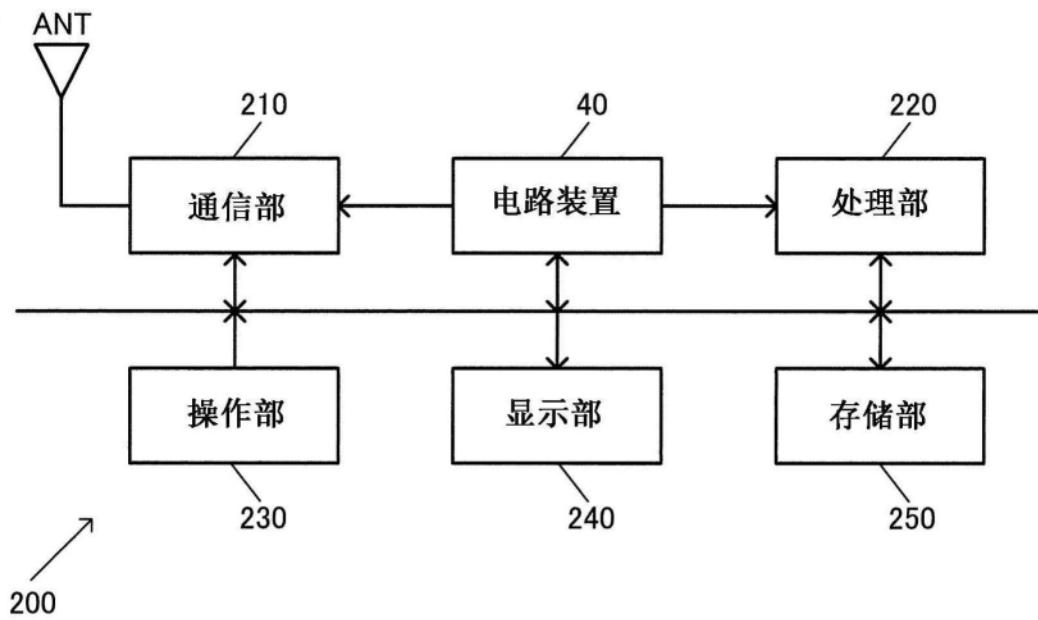

[0192] 图20示出本实施方式的电子设备200的结构例。电子设备200包含本实施方式的电路装置40、处理部220和存储部250。此外，还可以包含天线ANT、通信部210、操作部230和显示部240。另外，本实施方式的电子设备200不限于图20的结构，可以实施省略其构成要素的一部分、或追加其它构成要素等各种变形。

[0193] 作为本实施方式的电子设备200，例如可以假定如下各种设备：数字照相机（数字静态照相机、摄像机）、生物体信息检测装置（脉搏计、活动量计、测步计、健康手表等）、头戴式显示装置、机器人、GPS内置钟表、汽车导航装置、游戏装置、各种可穿戴设备、便携信息终端（智能手机、手机、便携式游戏装置、平板PC等）、发布内容的内容提供终端、视频设备、音频设备或网络相关设备（基站、路由器等）等。例如，通过在数字照相机中使用本实施方式的电路装置，能够实现利用陀螺传感器或加速度传感器实现的手抖校正等。此外，通过在生物体信息检测装置中使用本实施方式的电路装置，能够实现利用陀螺传感器或加速度传感器实现的用户体动检测以及运动状态检测。可以在机器人的可动部（臂、关节）以及主体部使用本实施方式的电路装置。可以假定机器人为移动体（跑步/行走机器人）、电子设备（非跑步/行走机器人）中的任何一个。在跑步/行走机器人的情况下，例如可以在自身行走中使用本实施方式的电路装置。在网络相关设备中，例如可以将本实施方式的电路装置用作对时间（绝对时间等）、时刻进行计时的装置。

[0194] 在图20中，通信部210（无线电路）进行经由天线ANT接收来自外部的数据、或向外部发送数据的处理。通过CPU、MPU等实现的处理部220（处理器）根据存储于存储部250（存储器）中的信息进行各种运算处理以及电子设备200的控制处理等。操作部230是用于供用户进行输入操作的部分，可以通过操作按钮或触摸面板显示器等实现。显示部240是用于显示各种信息的部分，可以通过液晶或有机EL等的显示器实现。存储部250是存储各种信息的部分，可以通过RAM、ROM等半导体存储器或HDD（硬盘驱动器）等实现其功能。

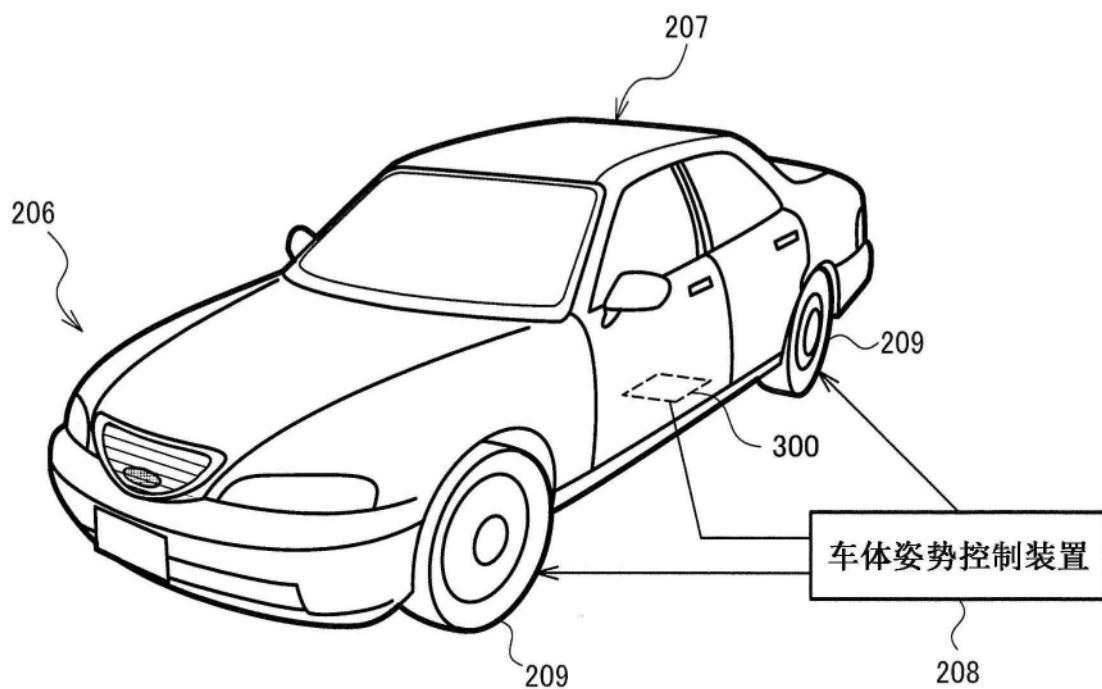

[0195] 此外，本实施方式的电路装置例如可以组装至汽车、飞机、摩托车、自行车或船舶等各种移动体中。移动体例如是具有发动机、马达等驱动机构、方向盘或舵等转向机构以及各种电子设备并在地上、天空或海上移动的设备/装置。

[0196] 图21是概要地示出作为移动体的具体例的汽车206的图。汽车206中组装有具有物理量换能器和电路装置的物理量检测装置300。物理量检测装置300（例如陀螺传感器、以及检测角速度和加速度的复合传感器等）能够检测车体207的姿势。物理量检测装置300的检测信号被提供给车体姿势控制装置208。车体姿势控制装置208例如可以根据车体207的姿势，控制悬架的软硬、或控制各个车轮209的制动。此外，还可以将这样的姿势控制用于双足行走机器人或飞机、直升机等各种移动体。在实现姿势控制时，将物理量检测装置300（电路装置）组装至移动体中。

[0197] 以上，对应用本发明的实施方式及其变形例进行了说明，但是，本发明不限于各实施方式及其变形例，可以在实施阶段在不脱离发明的宗旨的范围内将构成要素变形并具体化。此外，通过对上述各实施方式及变形例中公开的多个构成要素的适当组合能够形成各种发明。例如，也可以从各实施方式及变形例中记述的全部构成要素中删除几个构成要素。而且还可以将不同的实施方式及变形例中的构成要素适当地组合。此外，可以将至少一次与更广义或同义的不同的术语一同记述在说明书或附图中的术语在说明书或附图的任何一个位置替换为该不同的术语。这样，可以在不脱离发明的宗旨的范围内进行各种变形和

应用。

图1

图2

图3

图4

图5

图7

图8

图9

图10

图11

图12

图13

图14

图15

图16

图17

图18

图19

图20

图21