(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

6 March 2003 (06.03.2003)

PCT

(10) International Publication Number

WO 03/019566 A1

(51) International Patent Classification<sup>7</sup>: G11C 5/02, 15/00, 7/00, 8/00

(21) International Application Number: PCT/US02/27343

(22) International Filing Date: 27 August 2002 (27.08.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

09/940,832 27 August 2001 (27.08.2001) US

(71) Applicant: NETLOGIC MICROSYSTEMS, INC. [US/US]; 450 National Avenue, Mountain View, CA 94043 (US).

(72) Inventors: PEREIRA, Jose, P.; 10235 Vicksburg Drive, Cupertino, CA 95014 (US). SRINIVASAN, Varadarajan; 27835 Lupine Road, Los Altos Hills, CA 94022 (US).

(74) Agent: SHEMWELL, Charles, E.; Shemwell Gregory & Courtney LLP, Suite 201, 4880 Stevens Creek Blvd., San Jose, CA 95129 (US).

(81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZM, ZW.

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

[Continued on next page]

(54) Title: CONTENT ADDRESSABLE MEMORY WITH CONFIGURABLE CLASS-BASED STORAGE PARTITION

(57) Abstract: A content addressable memory (CAM) device having a plurality of CAM blocks and a block selection circuit. Each of the CAM blocks includes an array of CAM cells to store data words having a width determined according to a configuration value. The block selection circuit includes an input to receive a class code and circuitry to output a plurality of select signals to the plurality of CAM blocks. Each of the select signals selectively disables a respective one of the plurality of CAM blocks from participating in a compare operation according to whether the class code matches a class assignment of the CAM block.

WO 03/019566 A1

**Published:**

- with international search report

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

**CONTENT ADDRESSABLE MEMORY WITH

CONFIGURABLE CLASS-BASED STORAGE PARTITION**

**CROSS-REFERENCE TO RELATED APPLICATIONS**

This application is a continuation-in-part of each of the following U.S. patent applications:

5 application no. 09/590,642, filed June 8, 2000; application no. 09/590,428 filed June 8, 2000; application no. 09/590,775 filed June 8, 2000; application no. 09/594,206, filed June 14, 2000; application no. 09/594,209, filed June 14, 2000; application no. 09/594,201, filed June 14, 2000; application no. 09/594,194, filed June 14, 2000; and application no. 09/594,202, filed June 14, 2000. Each of the above-identified applications are hereby incorporated by reference in their 10 entirety.

**FIELD OF INVENTION**

This invention relates generally to semiconductor memories and more particularly to content addressable memories.

**BACKGROUND**

15 Content addressable memories (CAMs) are frequently used for address look-up functions in Internet data routing. For example, routers used by local Internet Service Providers (ISPs) typically include one or more CAMs for storing a plurality of Internet addresses and associated data such as, for instance, corresponding address routing information. When data is routed to a destination address, the destination address is compared with all CAM words, e.g., Internet 20 addresses, stored in the CAM array. If there is a match, routing information corresponding to the matching CAM word is output and thereafter used to route the data.

A CAM device includes a CAM array having a plurality of memory cells arranged in an array of rows and columns. Each memory cell stores a single bit of digital information, i.e., either logic zero or logic one. The bits stored within a row of memory cells constitute a CAM word. 25 During compare operations, a comparand word is received at appropriate input terminals of a CAM device and driven into the CAM array using comparand lines to be compared with all the CAM words in the device. For each CAM word that matches the comparand word, a corresponding match line signal is asserted to indicate a match condition. If the comparand word matches more than one of the CAM words, the match line corresponding to each of the matching 30 CAM words is asserted, and a "multiple match" flag is also asserted to indicate the multiple match condition. The match line signals from each CAM block are combined in a priority encoder to determine the address of the highest-priority matching CAM word, i.e., the CAM index.

Associative information corresponding to the CAM index stored in, for instance, an associated RAM, may also be provided.

A single CAM device can be used to store multiple tables each storing and maintaining different classes of data. All entries, however, typically participate in a compare operation. This 5 can cause an undesirable amount of power to be drawn during the compare operation. It would be desirable to limit a search to only those entries associated with a particular class of data to reduce power consumption during the operation.

In a typical CAM device, the width of the data word is fixed according to the number of 10 memory cells per row of the CAM array. U.S. Patent No. 5,440,715 describes a technique for expanding the width of the data words beyond that of a single row of CAM cells. This inter-row 15 configurability provides flexibility in the use of the single CAM array to store data words larger than that available in a single addressable row of CAM cells.

It would be desirable to have a CAM system that includes intra-row configurability to 15 provide additional flexibility in the use of a single CAM array to be used in multiple array 20 configurations. Intra-row configurability is the ability to access and operate upon one or more segments of rows of CAM cells.

#### SUMMARY

A method and apparatus are disclosed that may be used to partition a CAM device having 20 a plurality of CAM blocks into a number of individually searchable partitions, where each partition may include one or more CAM blocks of the CAM device. In accordance with one embodiment of the present invention, each CAM block is connected to a block select circuit that stores a class code indicating what class or type of data is stored in the block. The same class code may be stored in any number of the block select circuits to define a partition as including the 25 corresponding number of CAM blocks. During compare operations between a comparand word and data stored in the CAM device, a search code is provided to the block select circuits. Each block select circuit compares the search code with its class code and, in response thereto, selectively enables or disables the corresponding CAM block for the compare operation. In some 30 embodiments, the block select circuit enables the corresponding CAM block if the search class matches the class code and, conversely, disables the corresponding CAM block if the search code does not match the class code.

In one embodiment, the block select circuit disables a corresponding CAM block by driving the comparand lines of the CAM block to a predetermined state to preclude the comparand word from being driven onto the comparand lines during the compare operation. By

driving the comparand word only on the comparand lines of the selected (i.e., enabled) CAM blocks during the compare operation, present embodiments not only allow for selective searching across CAM blocks according to class codes, but also reduce power consumption in un-selected (i.e., disabled) CAM blocks during such selective compare operations.

5        A CAM system having intra-row configurability is also disclosed. For one embodiment, the CAM system includes a CAM array having a number of rows of CAM cells each segmented into row segments. Each row segment includes a number of CAM cells coupled to a corresponding match line segment. Individual row segments or groups of row segments are uniquely addressable by address logic in response to configuration information that indicates a 10 width and depth configuration of the CAM array. The configuration information may be stored in a configuration register. Data may be communicated with an addressed row segment or group of row segments using data access circuitry. Priority encoding circuitry may be included to generate the address of a row segment or group of row segments that stores data matching comparand data in response to the configuration information. Match flag logic may also be included to determine 15 when comparand data matches data stored in one of the row segments or one of the groups of row segments in response to the configuration information. Additionally, multiple match flag logic may be included to determine when comparand data matches data stored in each of a plurality of row segments and to determine when comparand data matches data stored in each of a plurality of groups of row segments in response to the configuration information.

20        In one embodiment, a CAM system includes multiple CAM blocks each having an associated block select circuit. Each of the CAM blocks is configurable to store data words having a width determined according to a configuration value and is responsive to a block select signal from the associated block select circuit to either participate or not participate in a compare operation. Each select block select circuit compares an input class code with a stored value and 25 either asserts or deasserts the block select signal for the associated CAM block according to the comparison result.

These and other embodiments, features and advantages of the present invention will be apparent from the accompanying drawings and from the detailed description that follows below.

#### BRIEF DESCRIPTION OF THE DRAWINGS

30        The features and advantages of the present invention are illustrated by way of example and are by no means intended to limit the scope of the present invention to the particular embodiments shown, and in which:

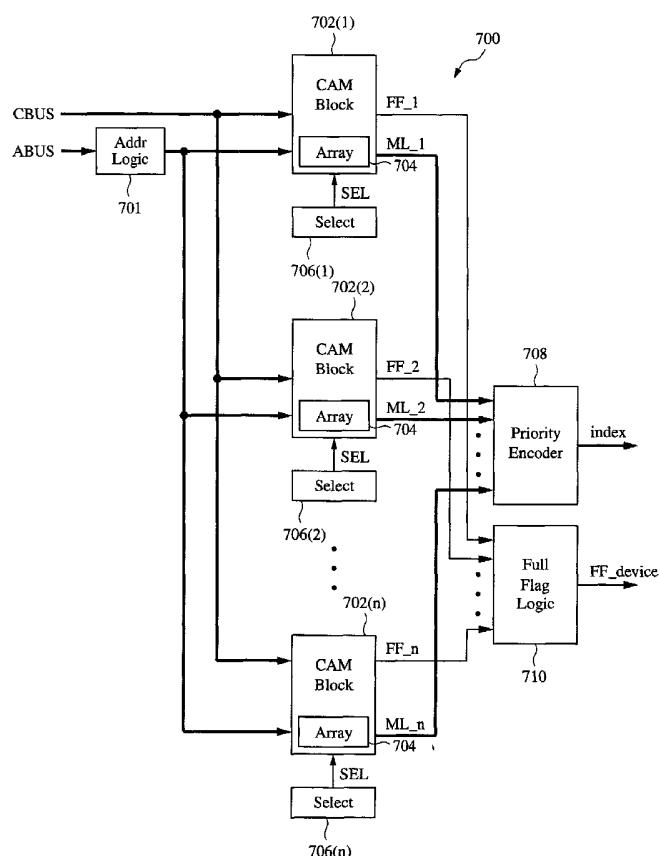

Figure 1 is a block diagram of a CAM device including a plurality of CAM blocks in accordance with one embodiment of the present invention;

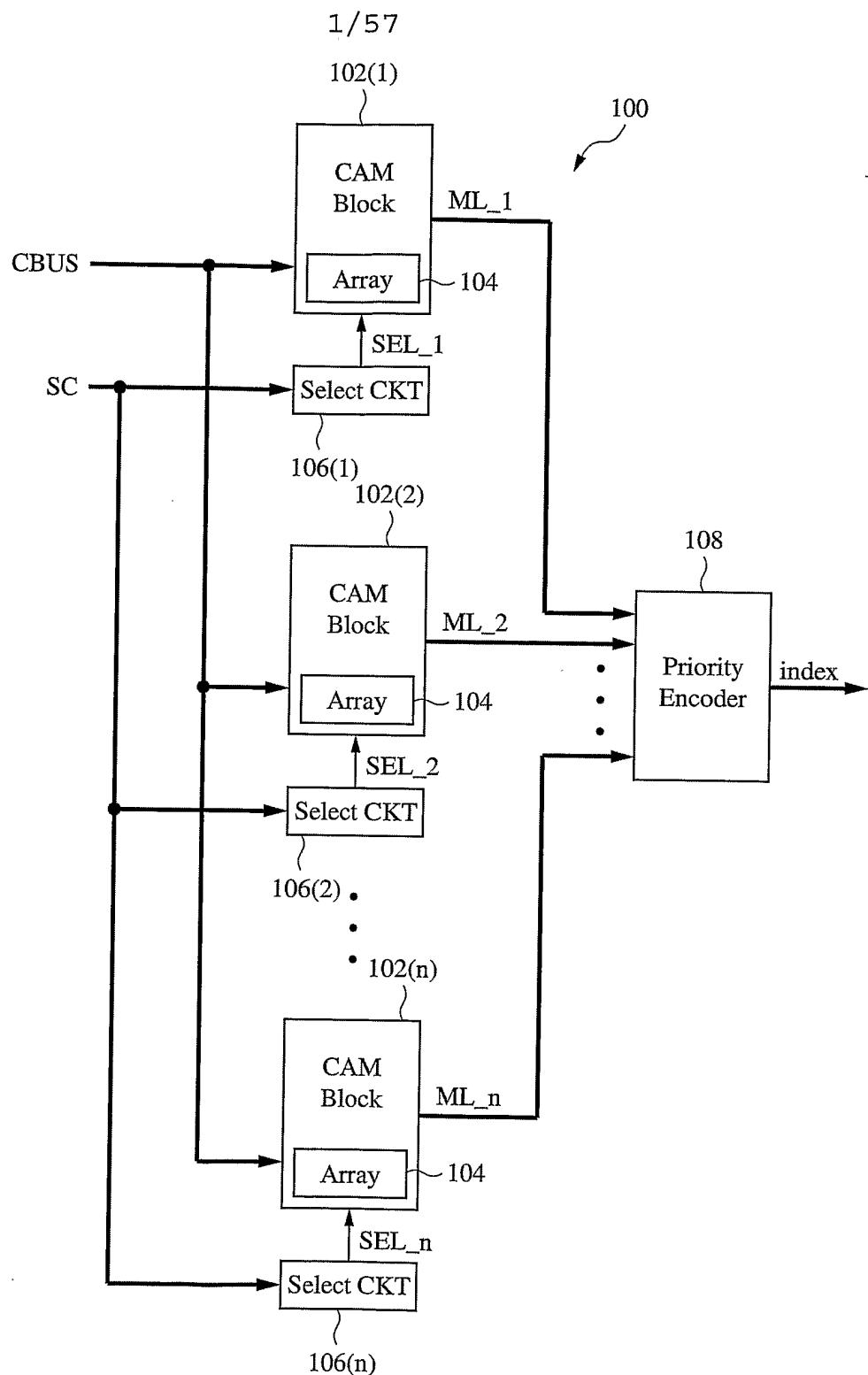

Figure 2 is a block diagram of a CAM block in one embodiment of the array of Figure 1;

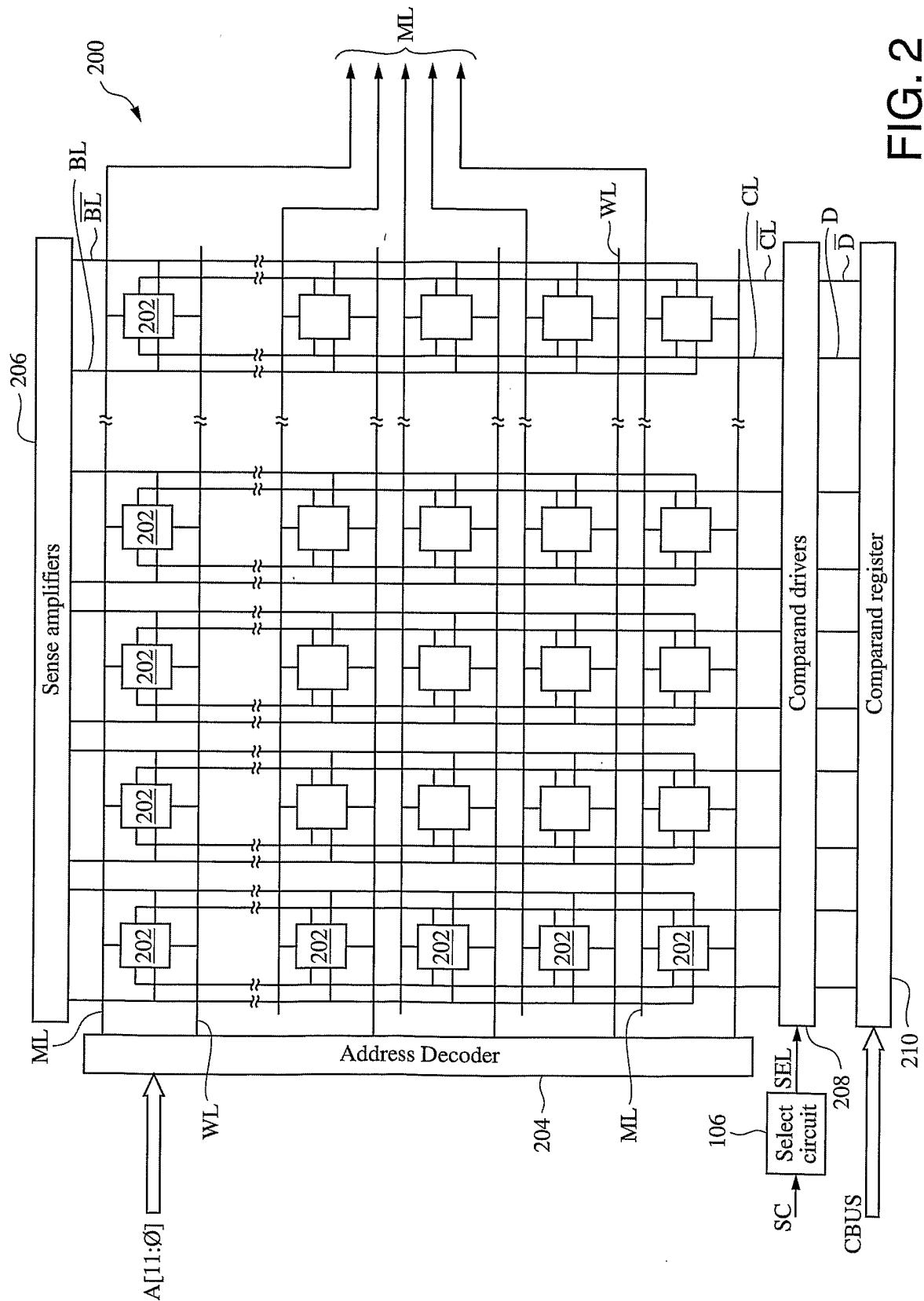

5 Figure 3 is a block diagram of a block select circuit in one embodiment of the CAM block of Figure 2;

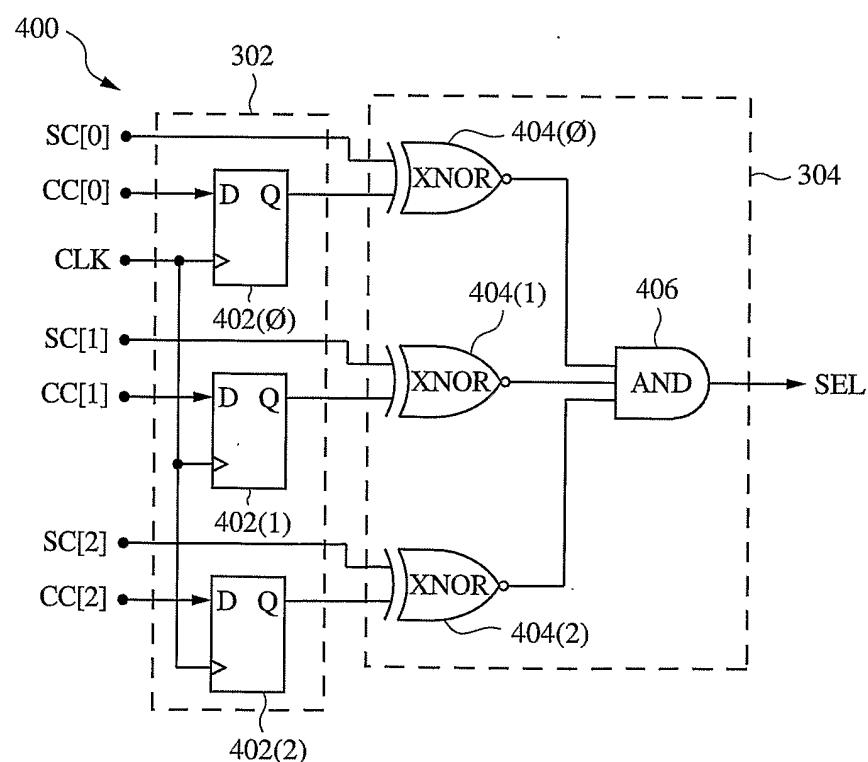

Figure 4 is a logic diagram of one embodiment of the block select circuit of Figure 3;

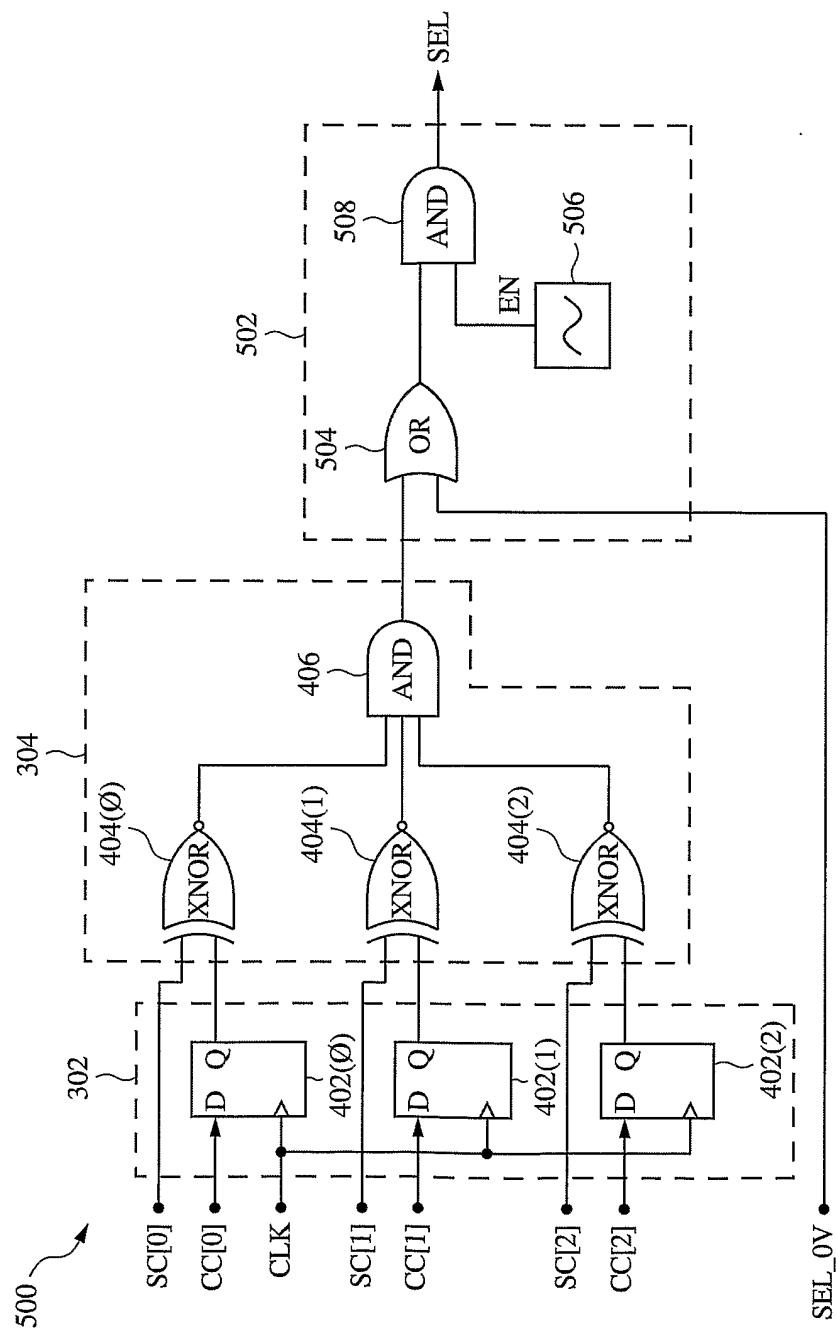

Figure 5 is a logic diagram of another embodiment of the block select circuit of Figure 3;

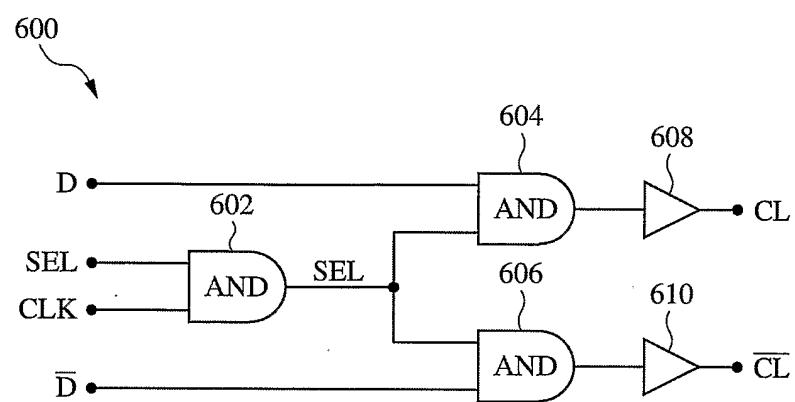

Figure 6 is a logic diagram of one embodiment of a comparand driver of the CAM block of Figure 2;

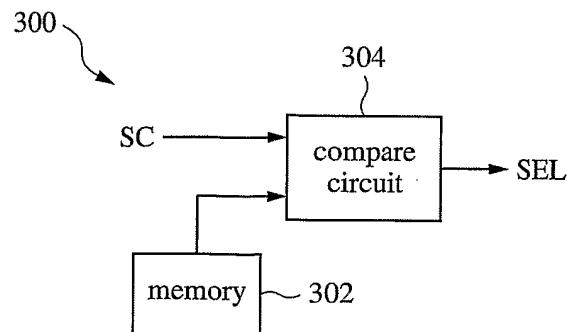

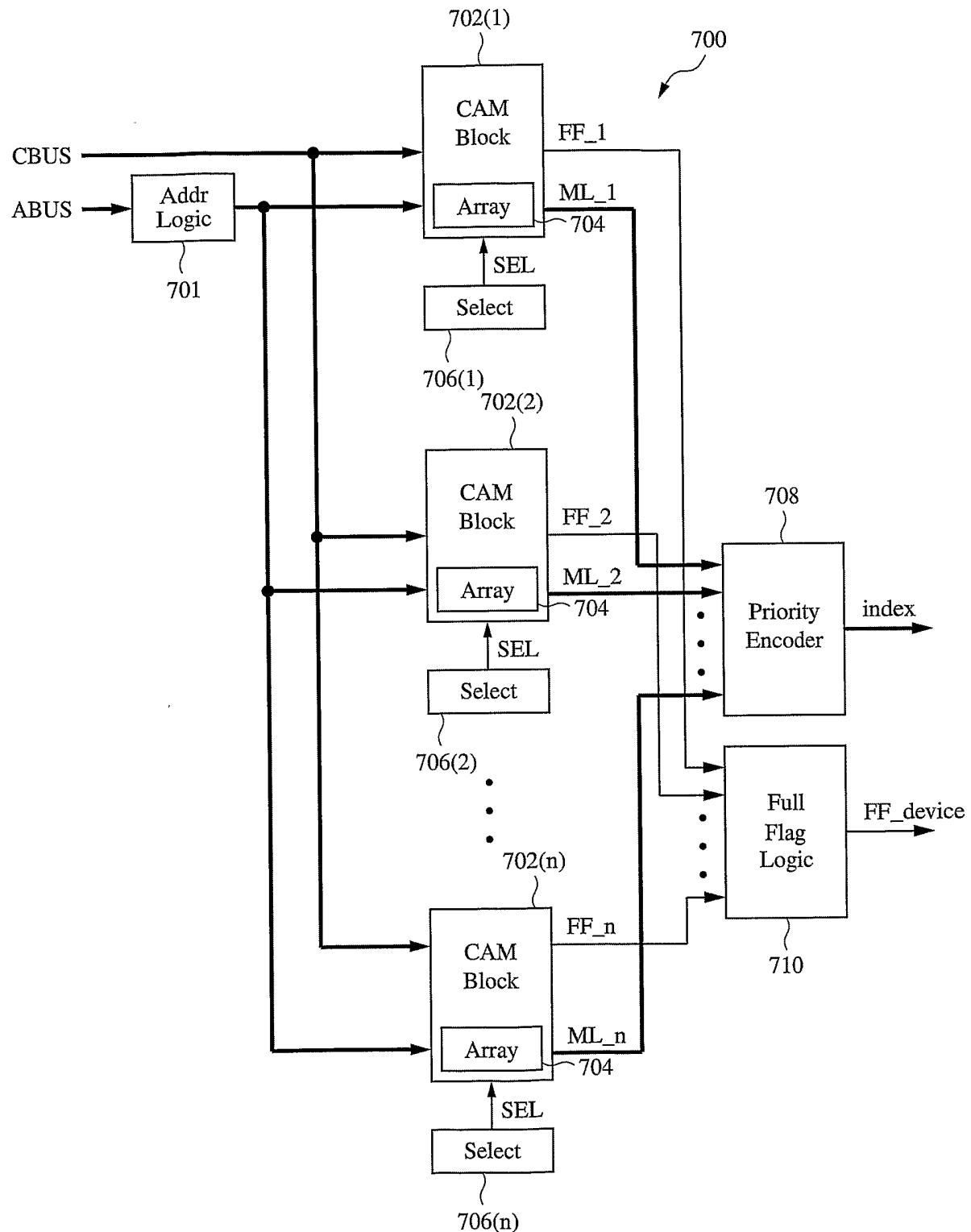

10 Figure 7 is a block diagram of a CAM device including a plurality of CAM blocks in accordance with another embodiment of the present invention configured to translate addresses of one or more defective CAM blocks;

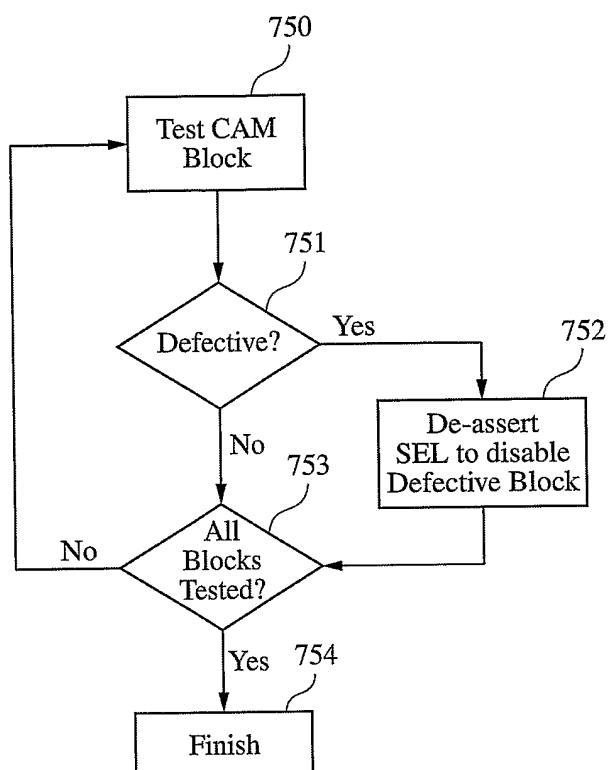

Figure 8 is a flow chart illustrating the disabling of defective CAM blocks in one embodiment;

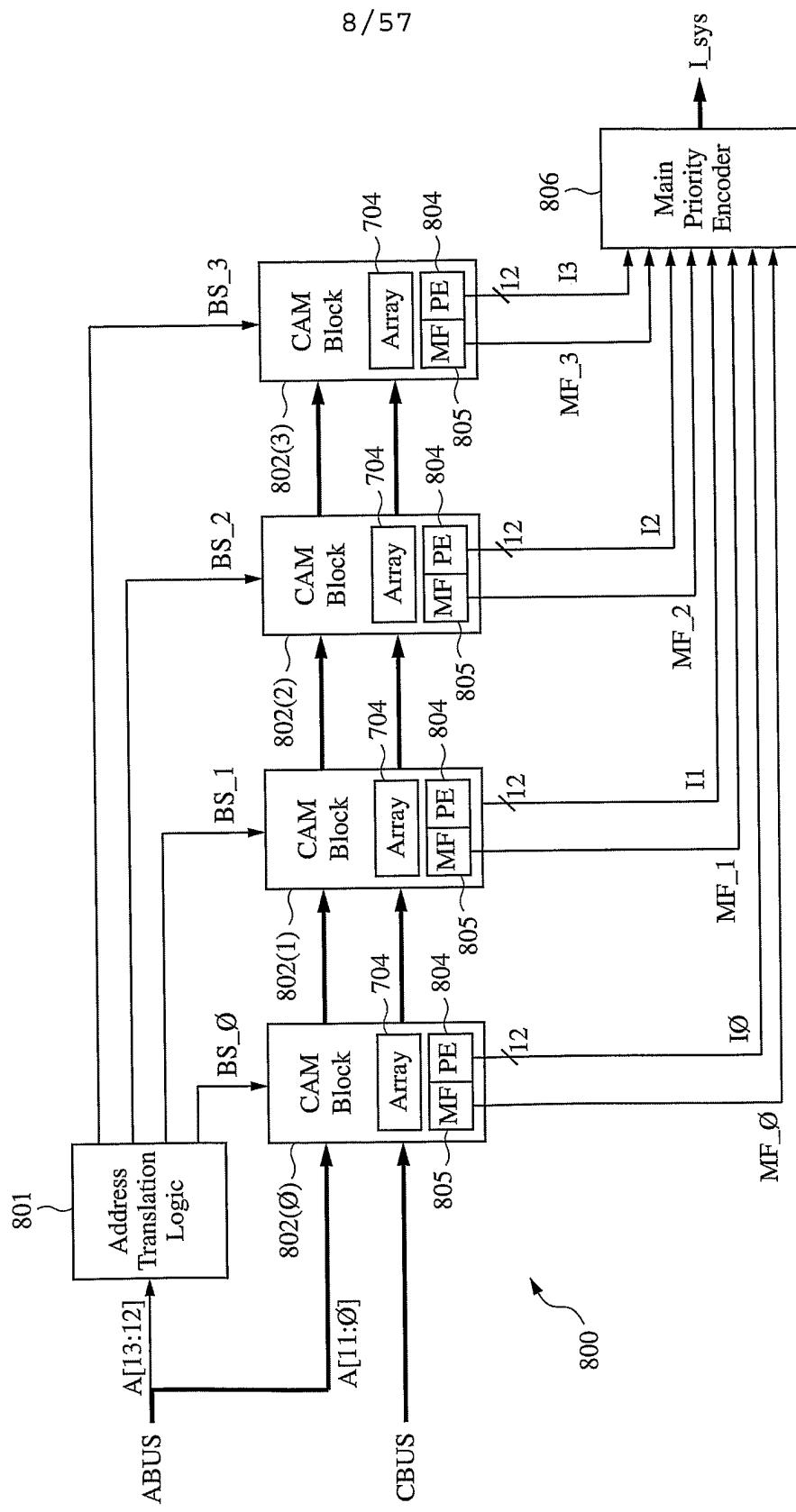

15 Figure 9 is a block diagram of one embodiment of the CAM device of Figure 7;

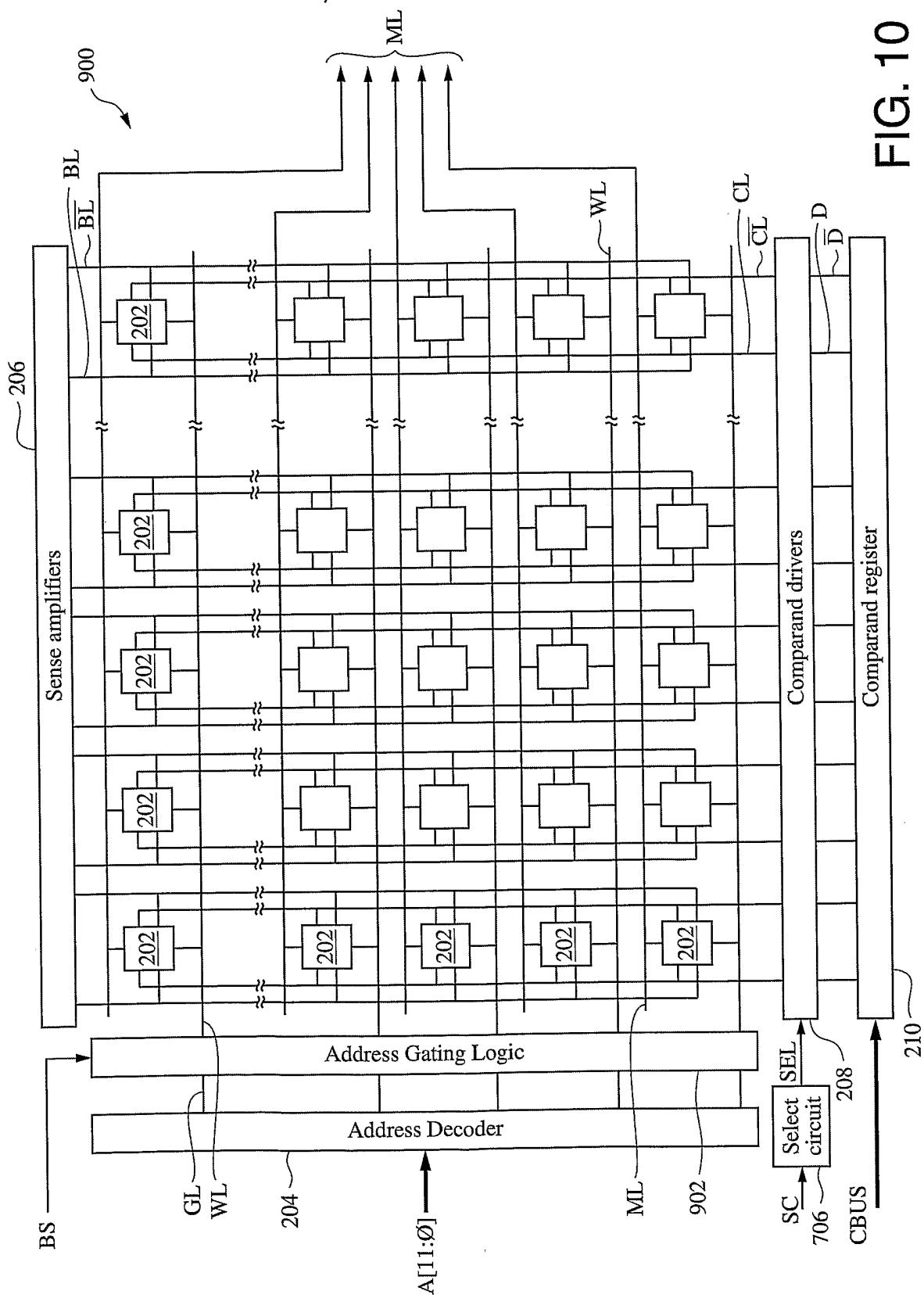

Figure 10 is a block diagram of a CAM block in one embodiment of the device of Figure 9;

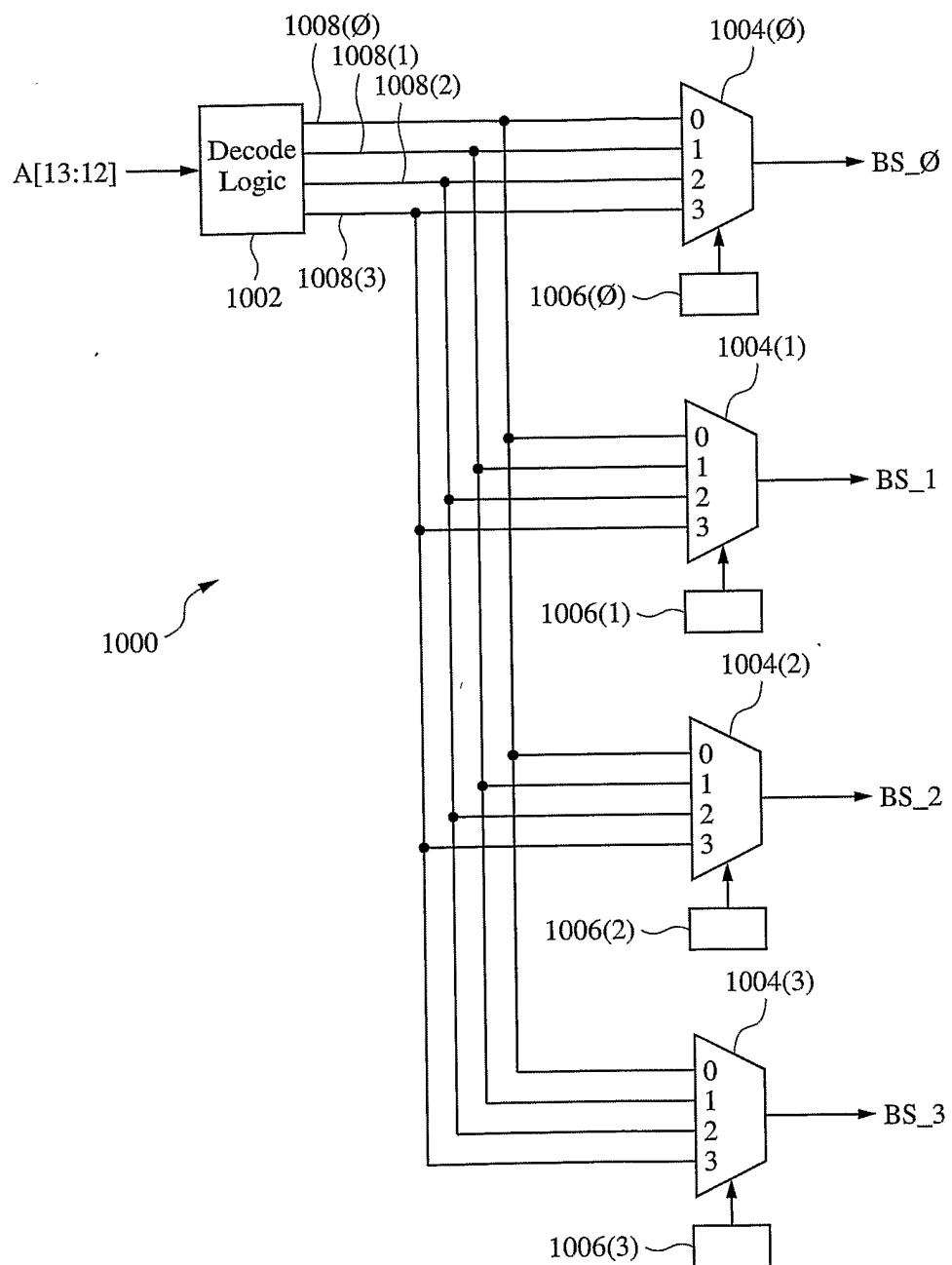

Figure 11 is a block diagram of address translation logic in one embodiment of the CAM block of Figure 10;

20 Figure 12 is a logic diagram of a main priority encoder in one embodiment of the device of Figure 9;

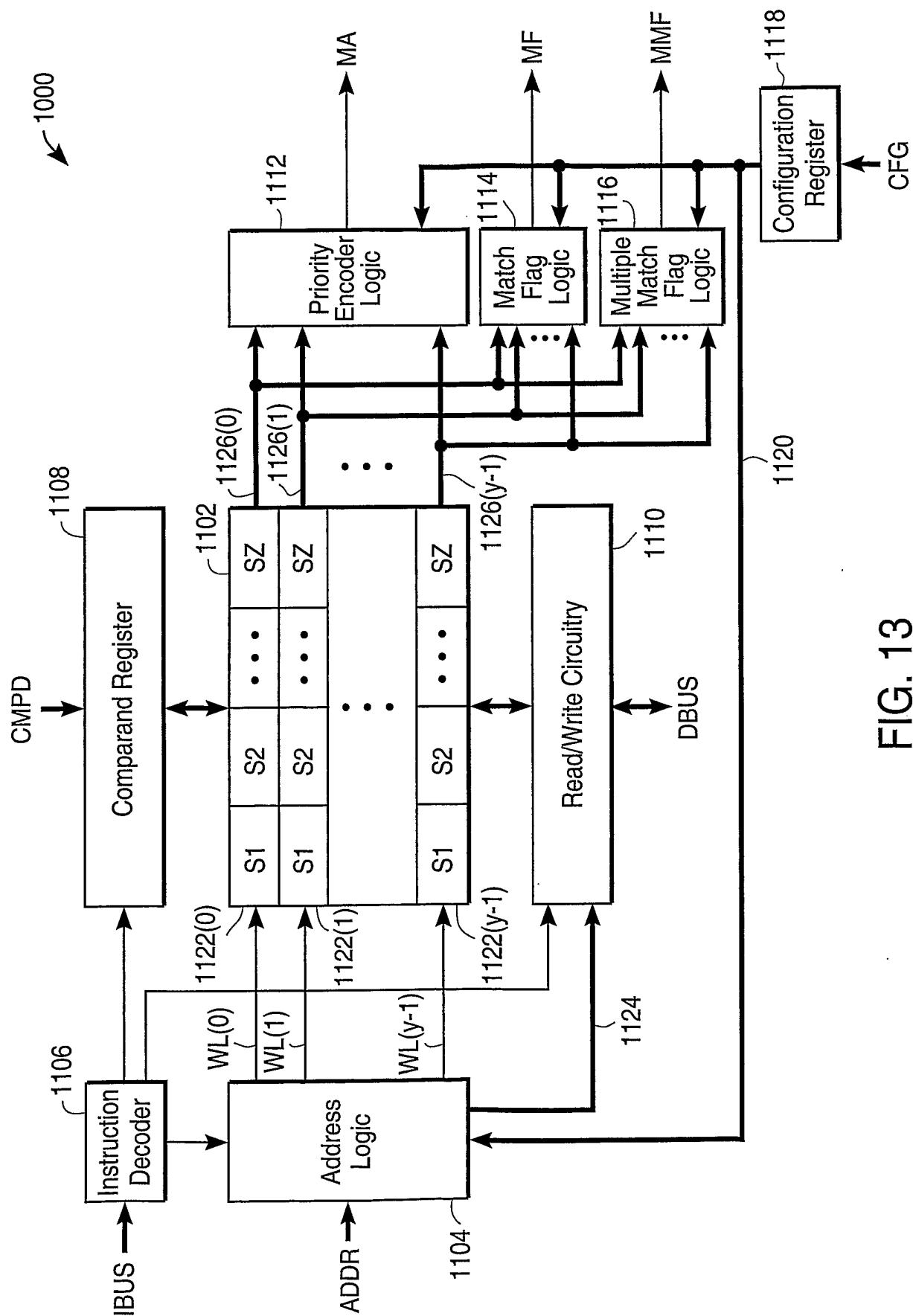

Figure 13 is a block diagram of one embodiment of a configurable CAM system according to the present invention including a CAM array, comparand register, configuration register, address logic, read/write circuitry, an instruction decoder, priority encoder logic, match flag logic, 25 and multiple match flag logic;

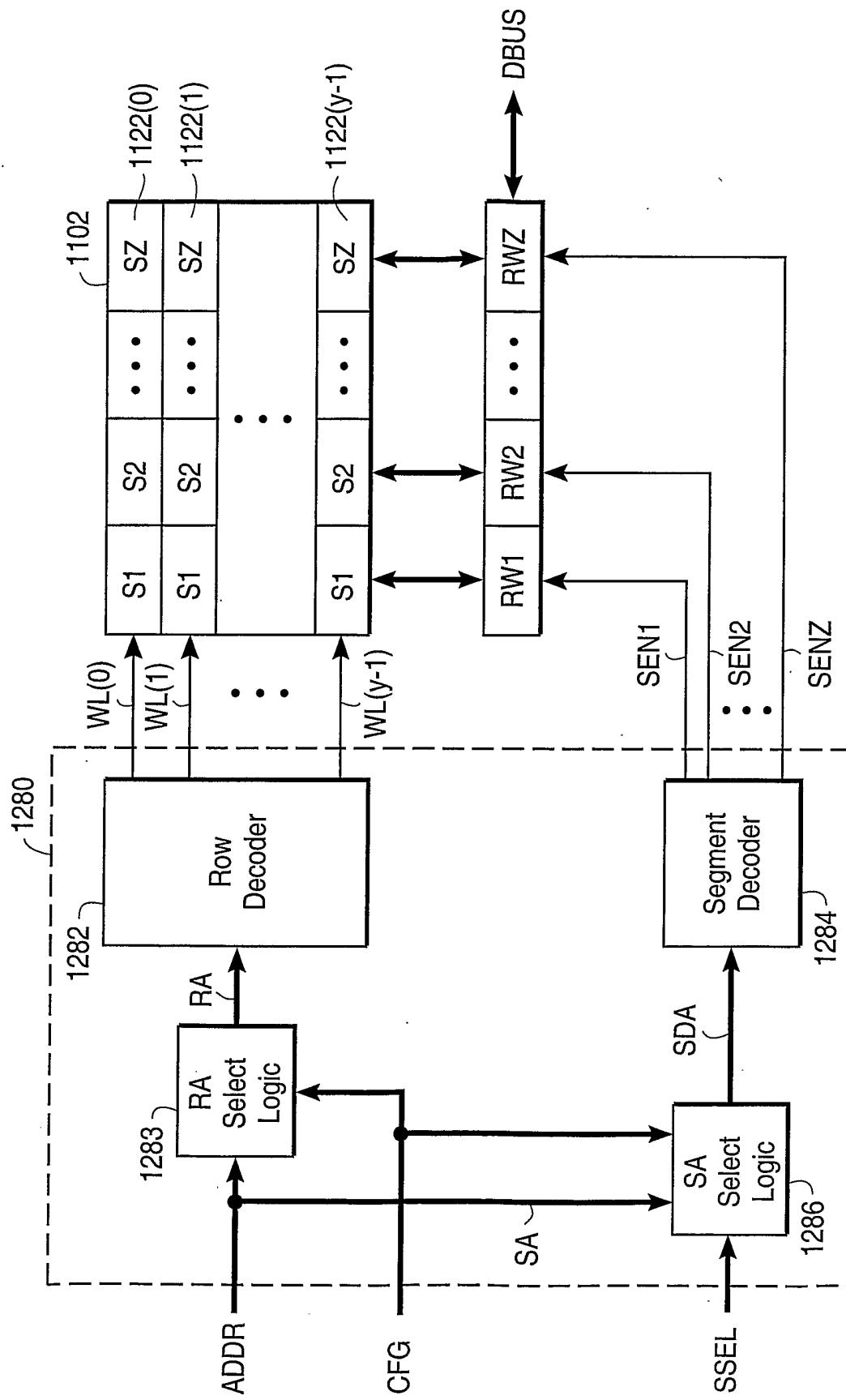

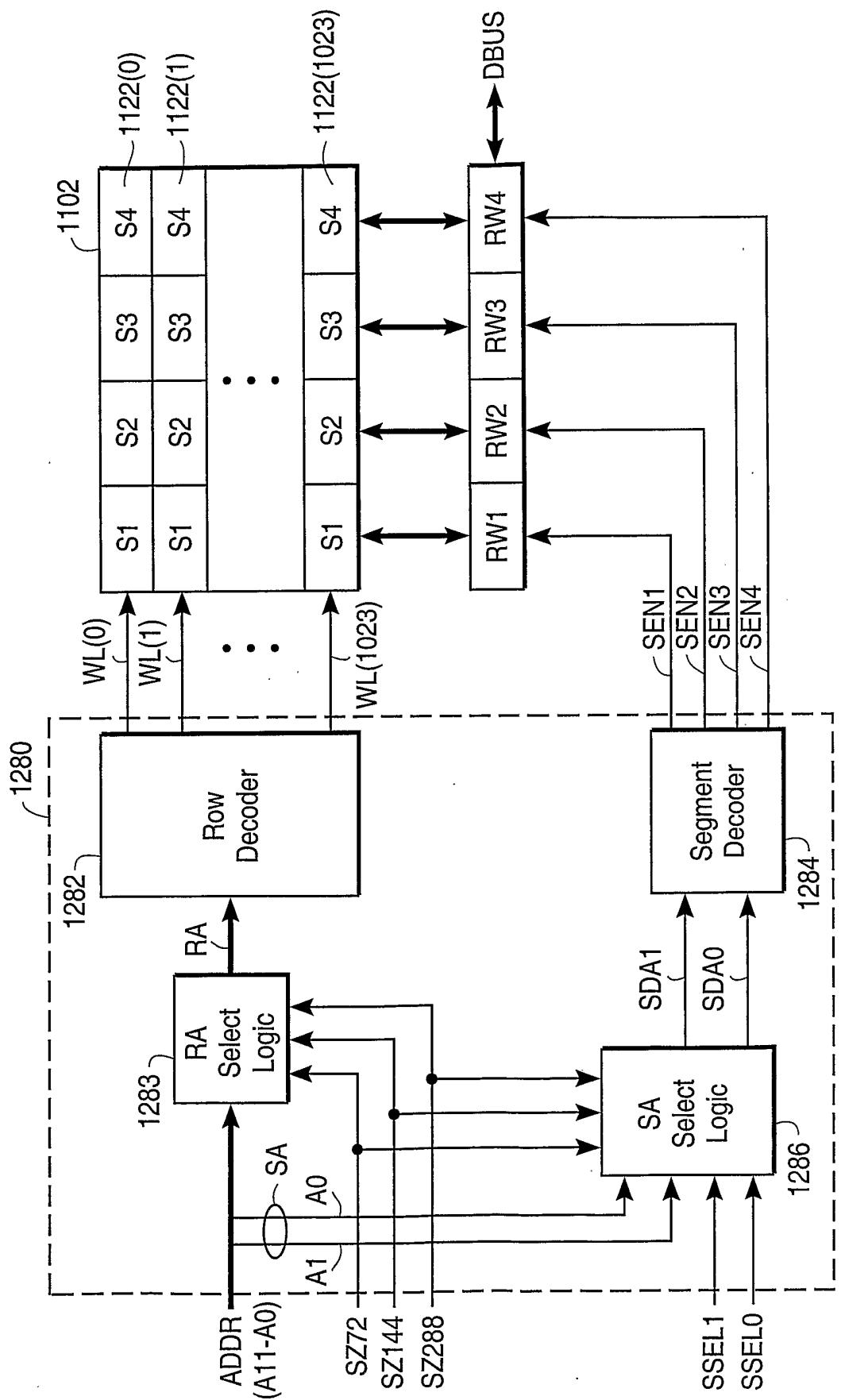

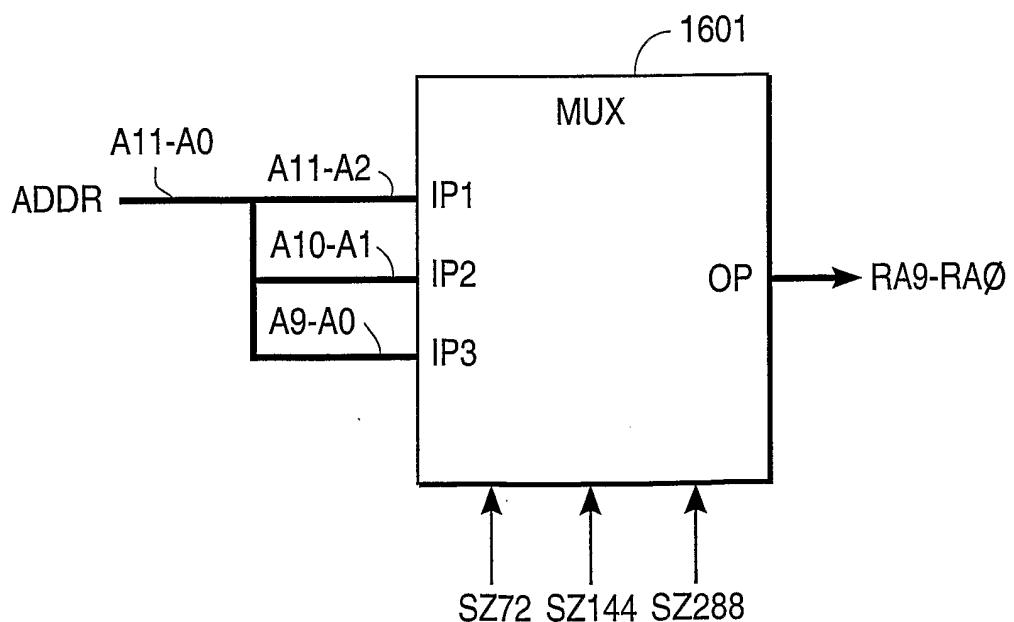

Figure 14 is a block diagram of one embodiment of the address logic of Figure 13 including a row decoder, row address select logic, segment address select logic, and a segment decoder;

30 Figure 15 is one example of the address logic of Figure 14 for particular configurations of the CAM system;

Figure 16 is one embodiment of a truth table for the select logic of Figure 15;

Figure 17 is one embodiment of a truth table for the segment decoder of Figure 15;

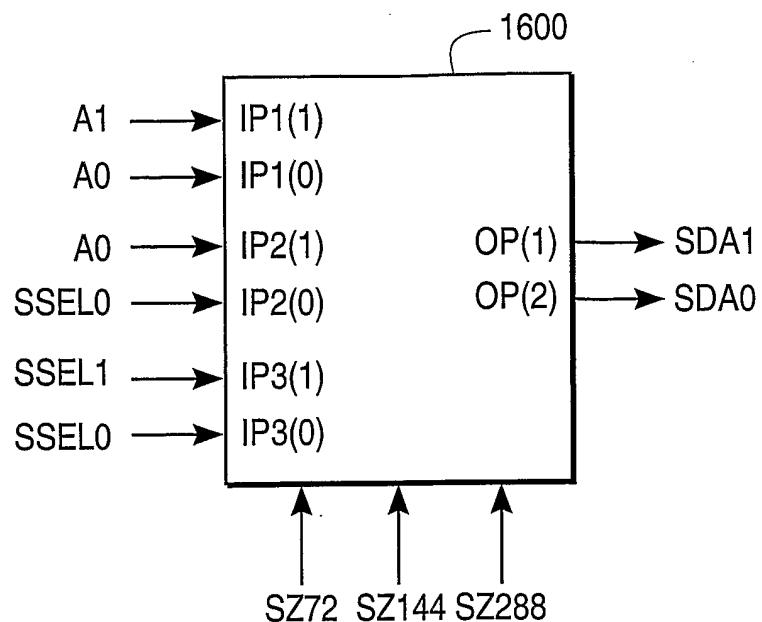

Figure 18A is a logic diagram of one embodiment of the segment address select logic of Figure 15;

Figure 18B is a logic diagram of one embodiment of the row address select logic of Figure 15;

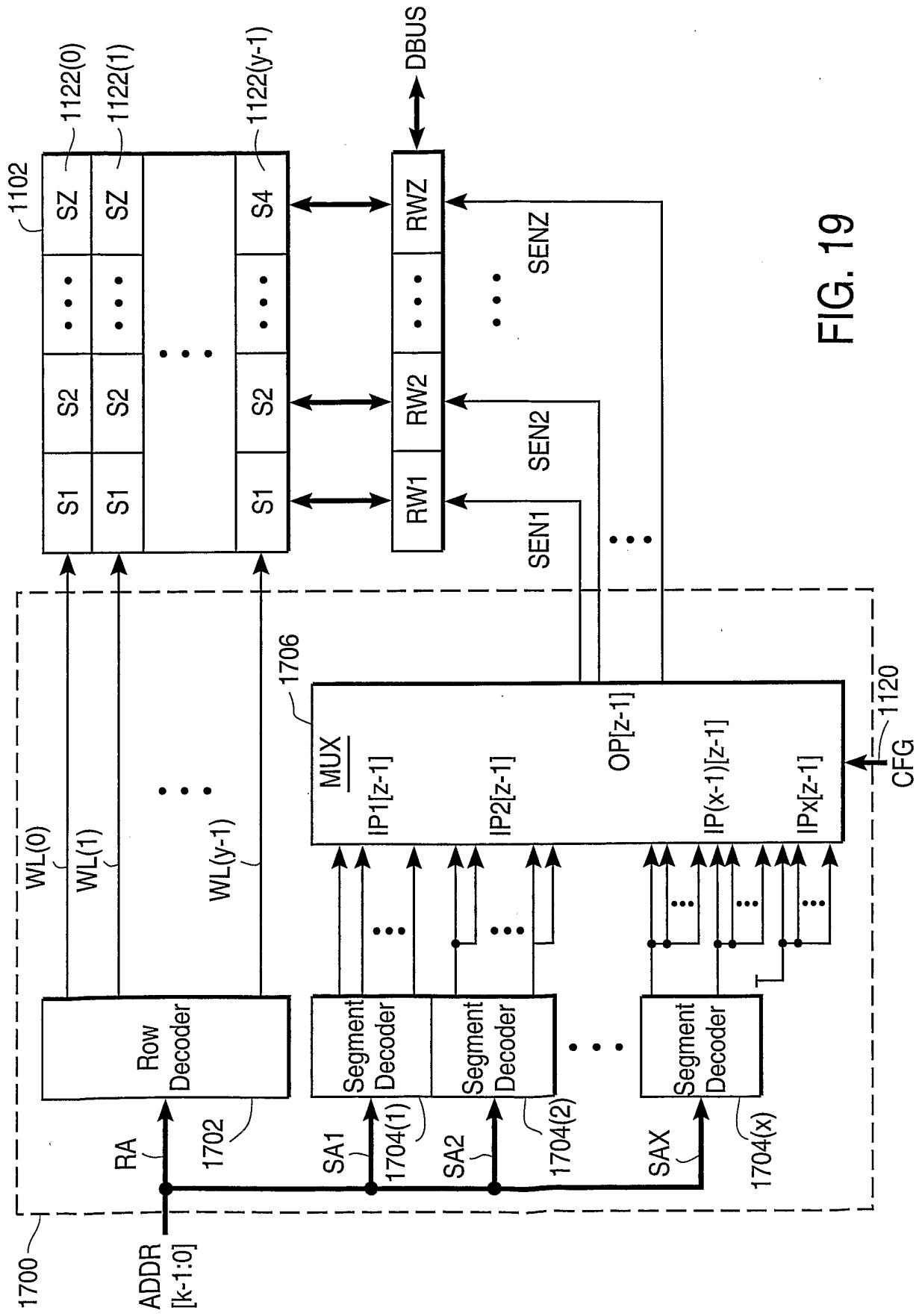

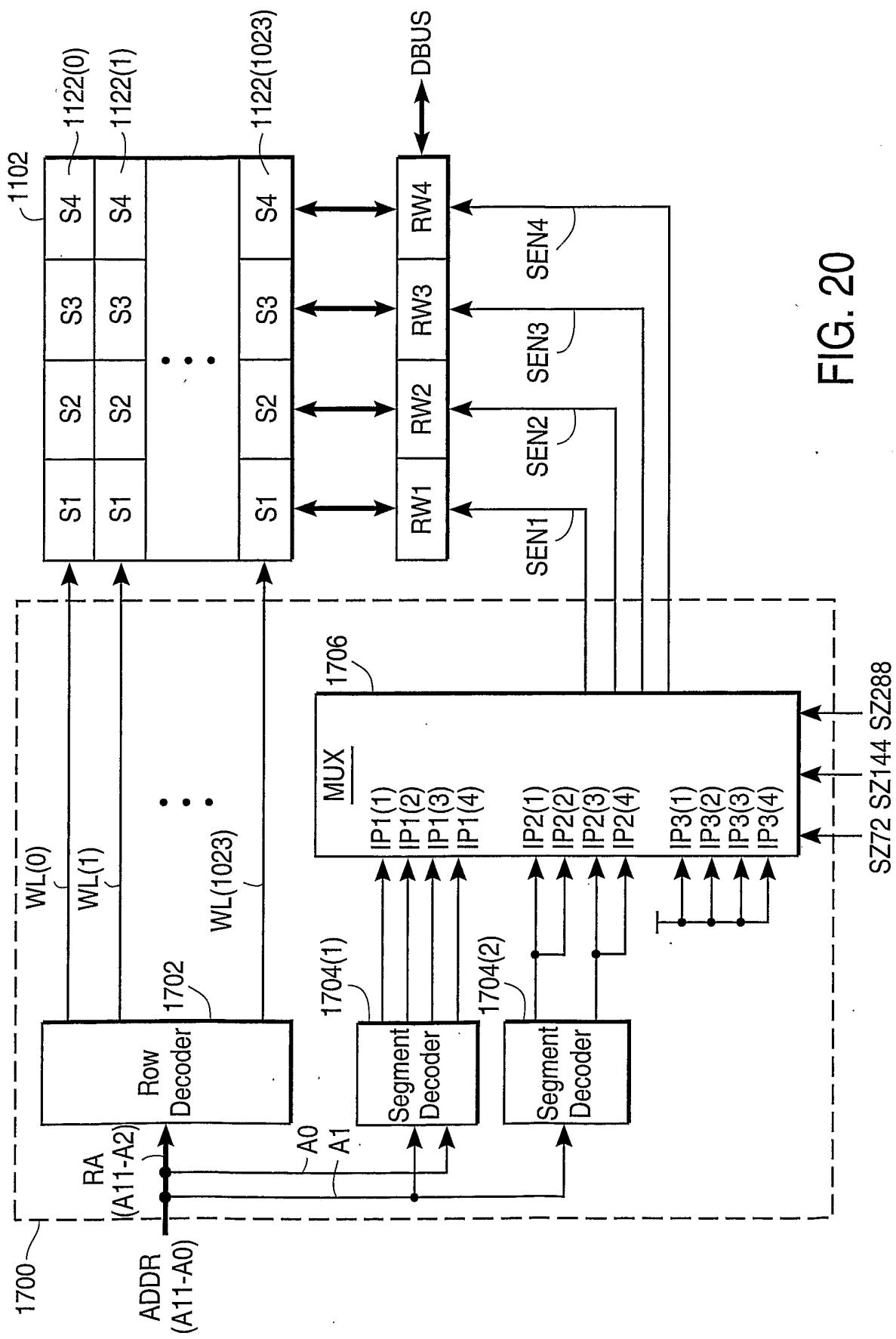

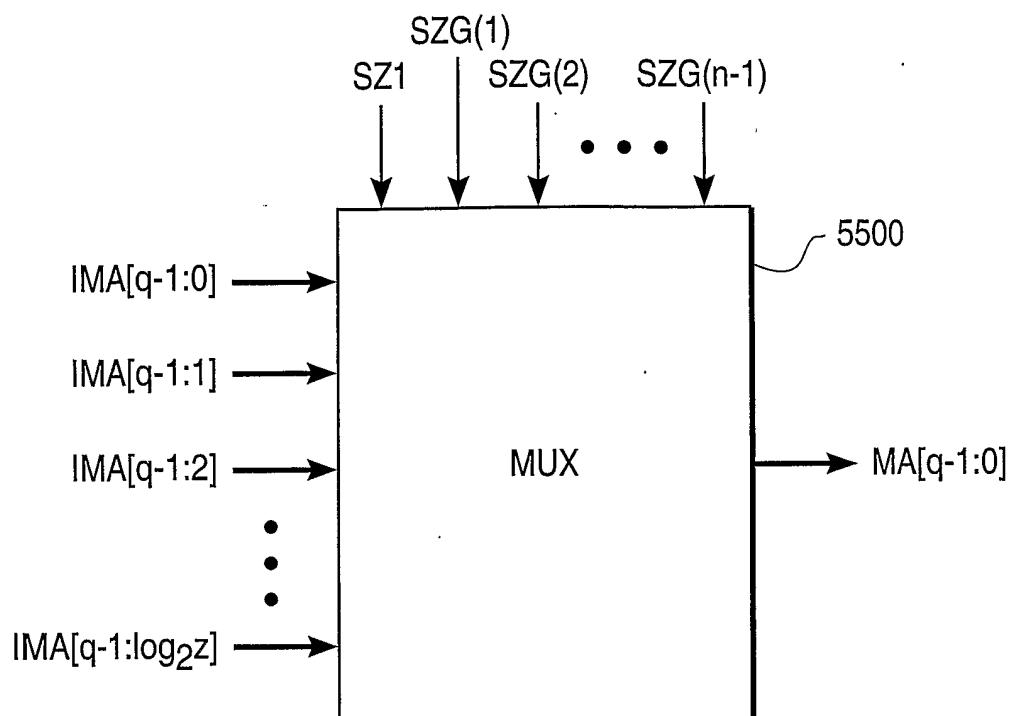

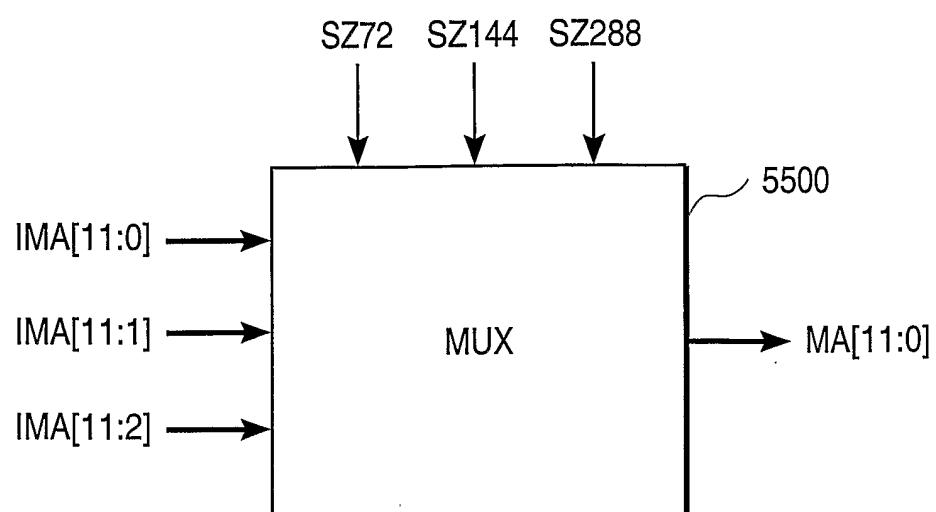

Figure 19 is block diagram of another embodiment of the address logic of Figure 13 including a row decoder, segment decoders, and a multiplexer;

5 Figure 20 is one example of the address logic of Figure 19 for particular configurations of the CAM system;

Figure 21 is a block diagram of one embodiment of circuitry to load comparand data into the comparand register;

10 Figure 22 is one example of the logic of Figure 21 for particular configurations of the CAM system;

Figure 23 is one embodiment of a truth table for the select logic of Figure 22;

Figure 24 is a logic diagram of one embodiment of the select logic for the truth table of Figure 23;

15 Figure 25 is a logic diagram of another embodiment of the select logic for the truth table of Figure 23;

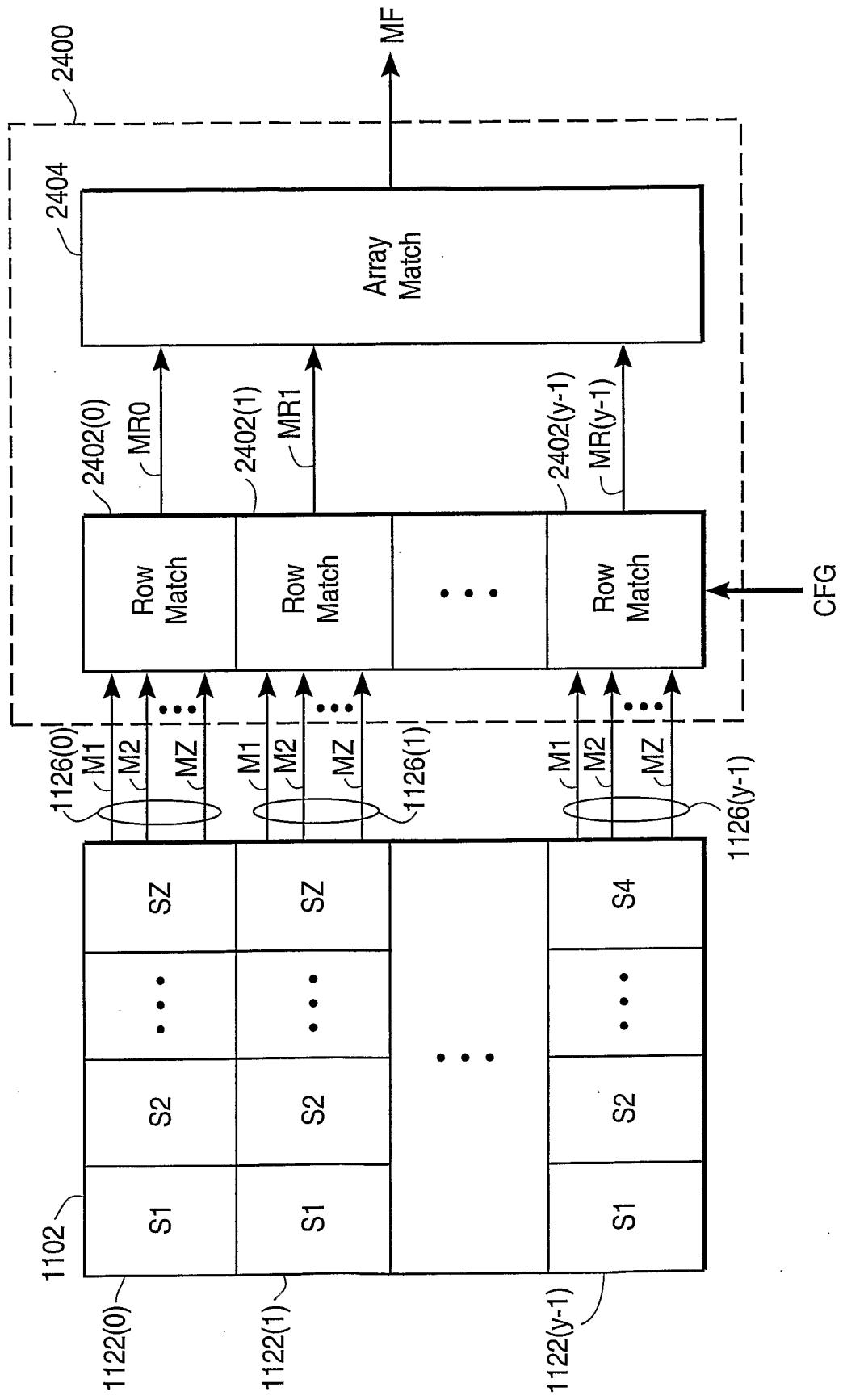

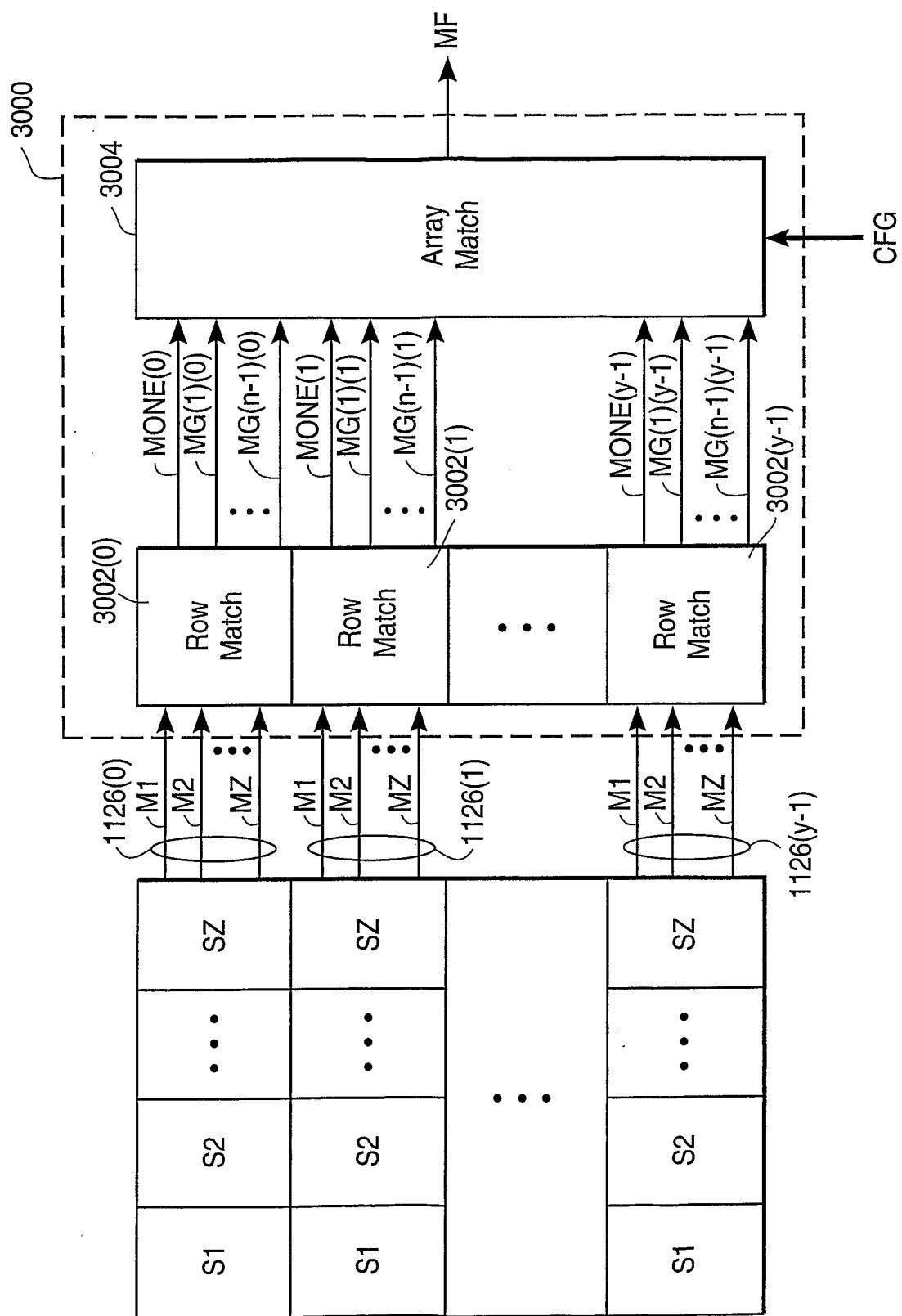

Figure 26 is a block diagram of one embodiment of the match flag logic of Figure 13 including row match circuits and an array match circuit;

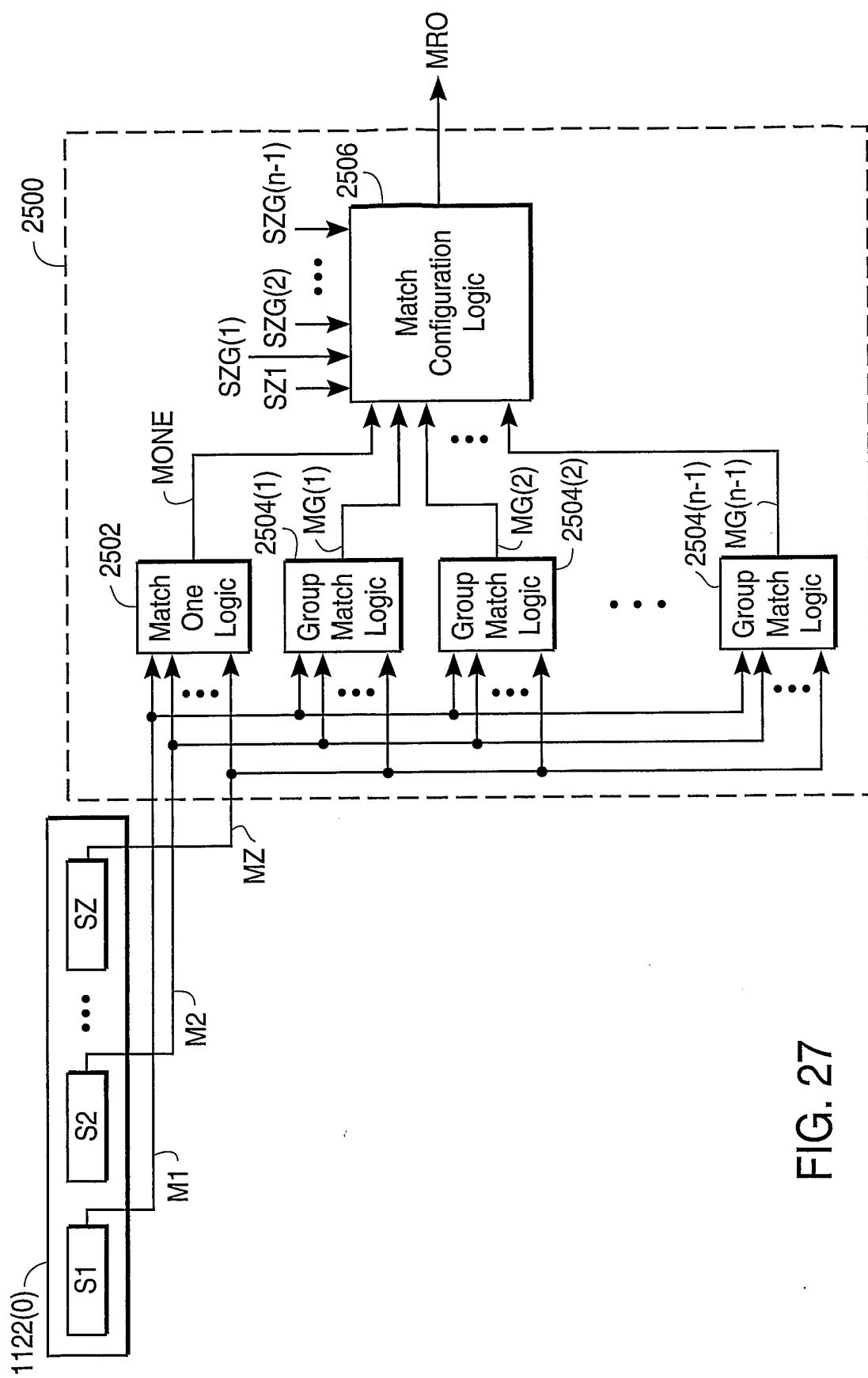

Figure 27 is a block diagram of one embodiment of the row match circuits of Figure 26 including match one logic, group match circuits, and match configuration logic;

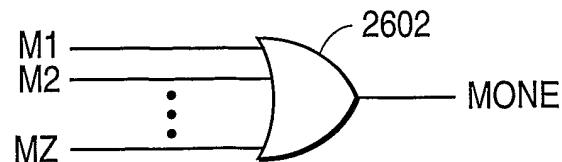

20 Figure 28 is a logic diagram of one embodiment of the match one logic of Figure 27;

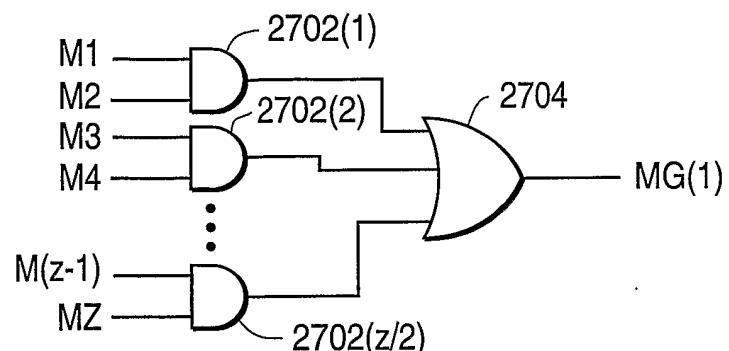

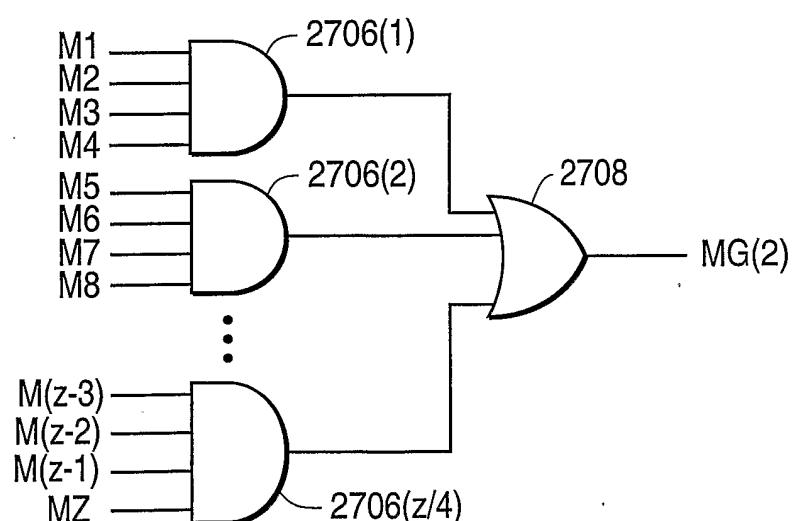

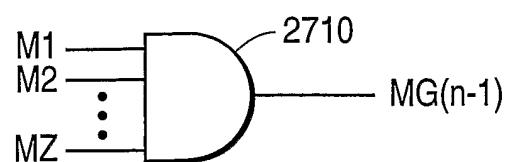

Figures 29A-29C are logic diagrams of embodiments of the group match circuits of Figure 27;

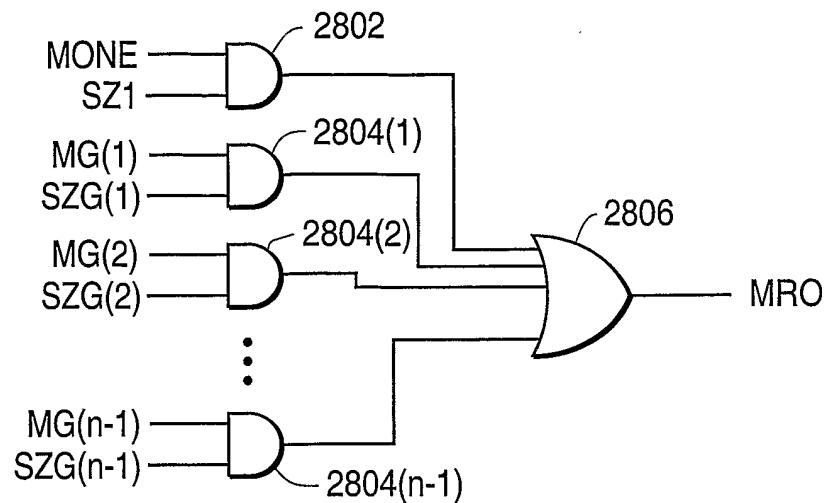

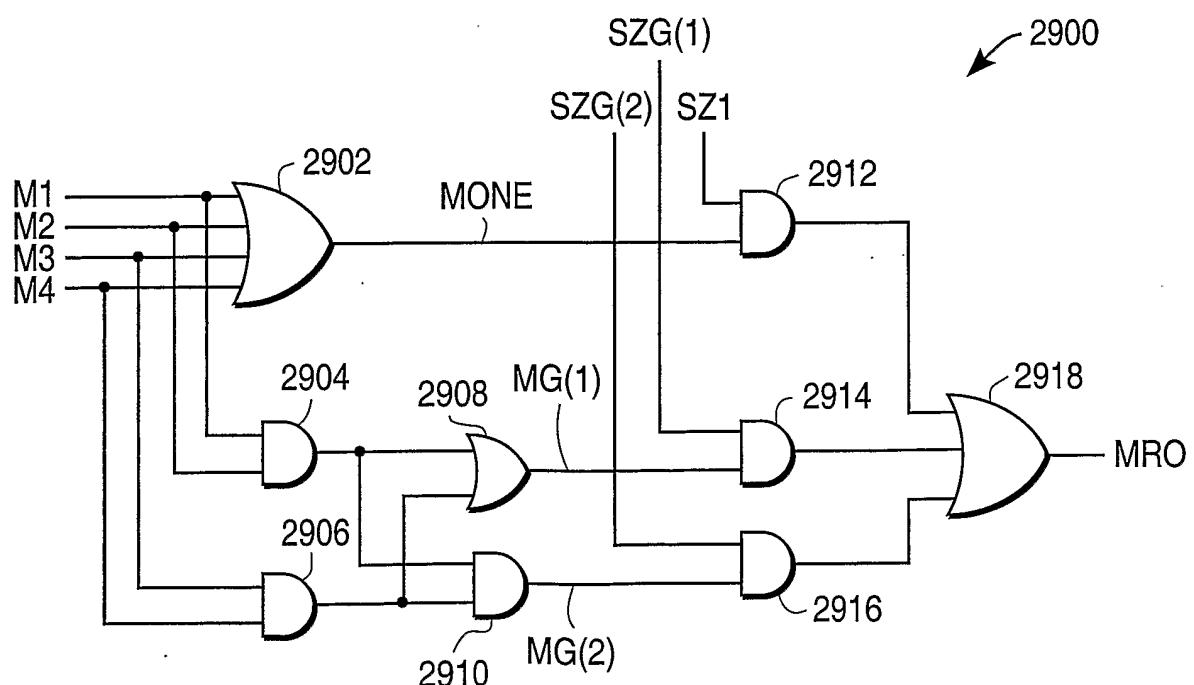

25 Figure 30 is a logic diagram of one embodiment of the match configuration logic of Figure 27;

Figure 31 is a logic diagram of one embodiment of the match flag logic of Figure 13;

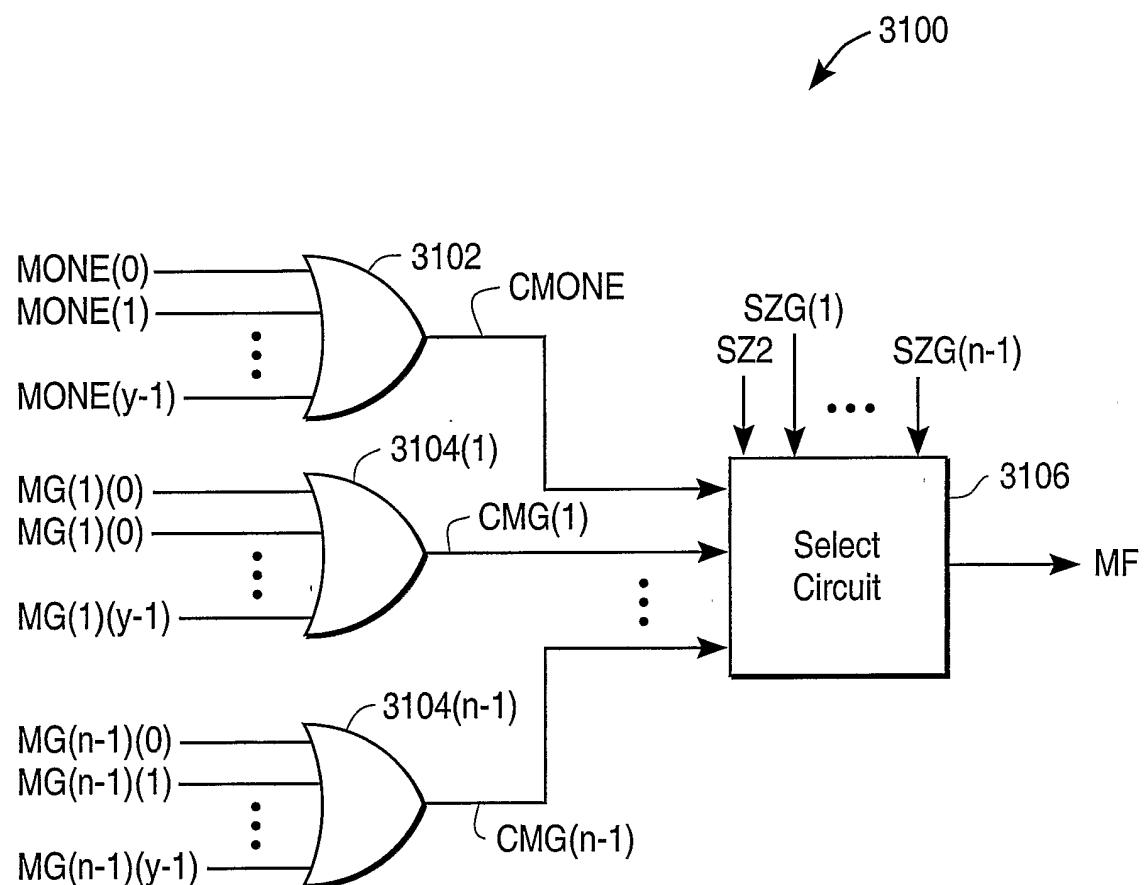

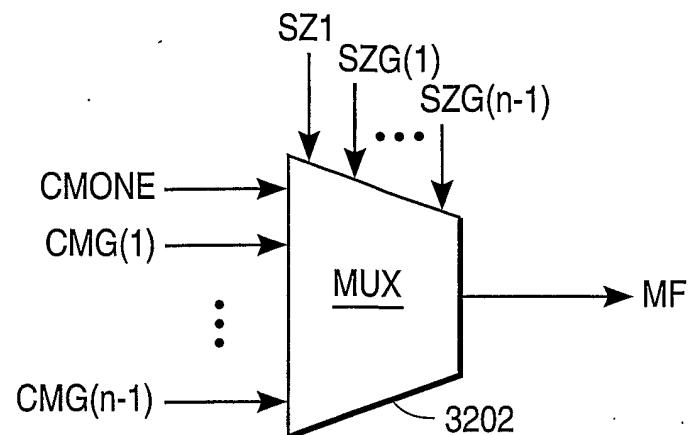

Figure 32 is a block diagram of another embodiment of the match flag logic of Figure 13 including row match circuits and an array match circuit;

Figure 33 is a block diagram of one embodiment of the array match circuit of Figure 32 including OR logic and a select circuit;

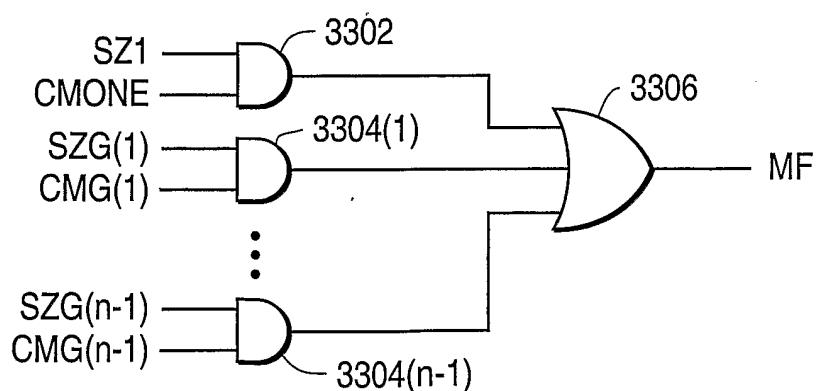

30 Figure 34 is a logic diagram of one embodiment of the select logic of Figure 33;

Figure 35 is a logic diagram of another embodiment of the select logic of Figure 33;

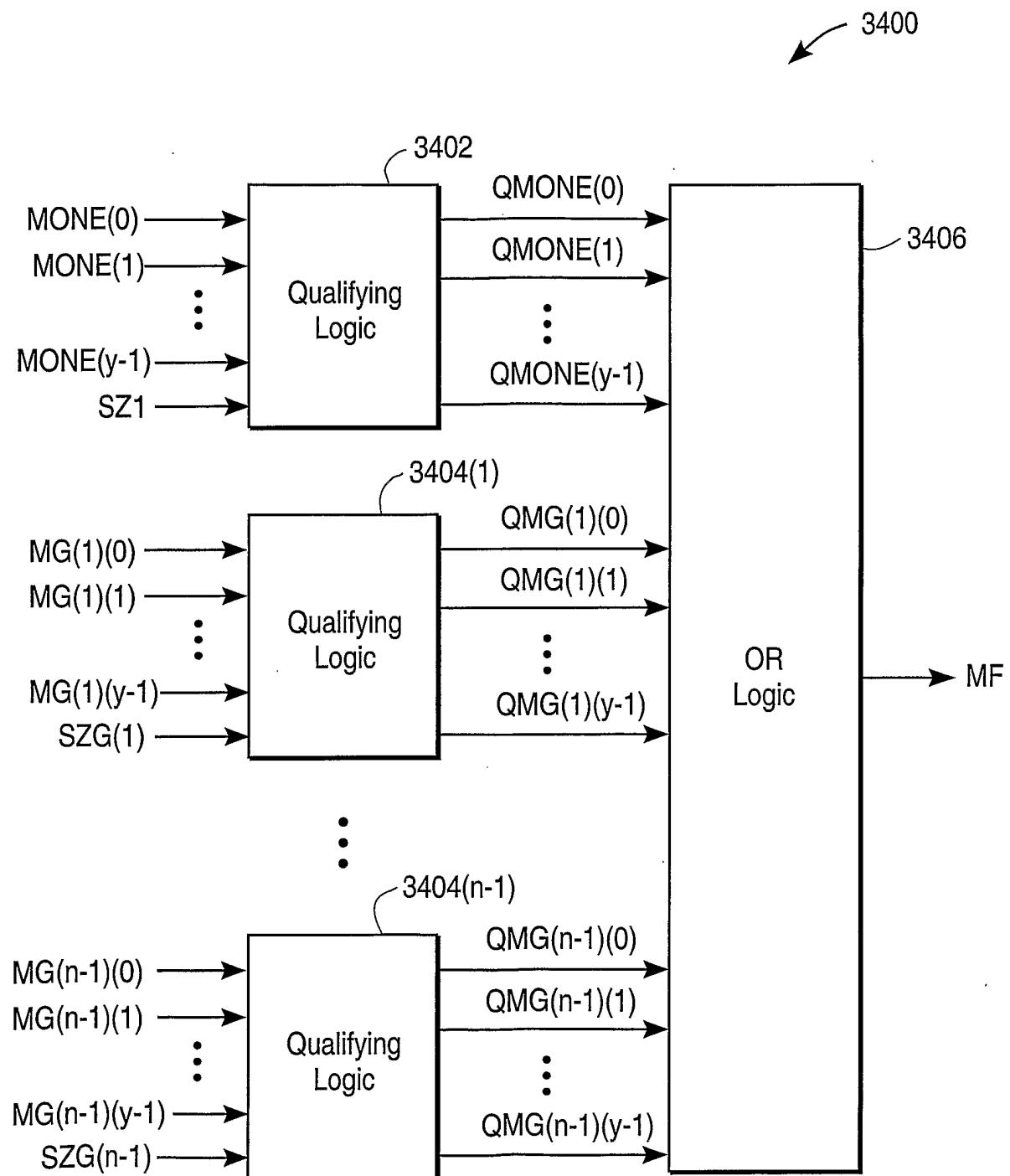

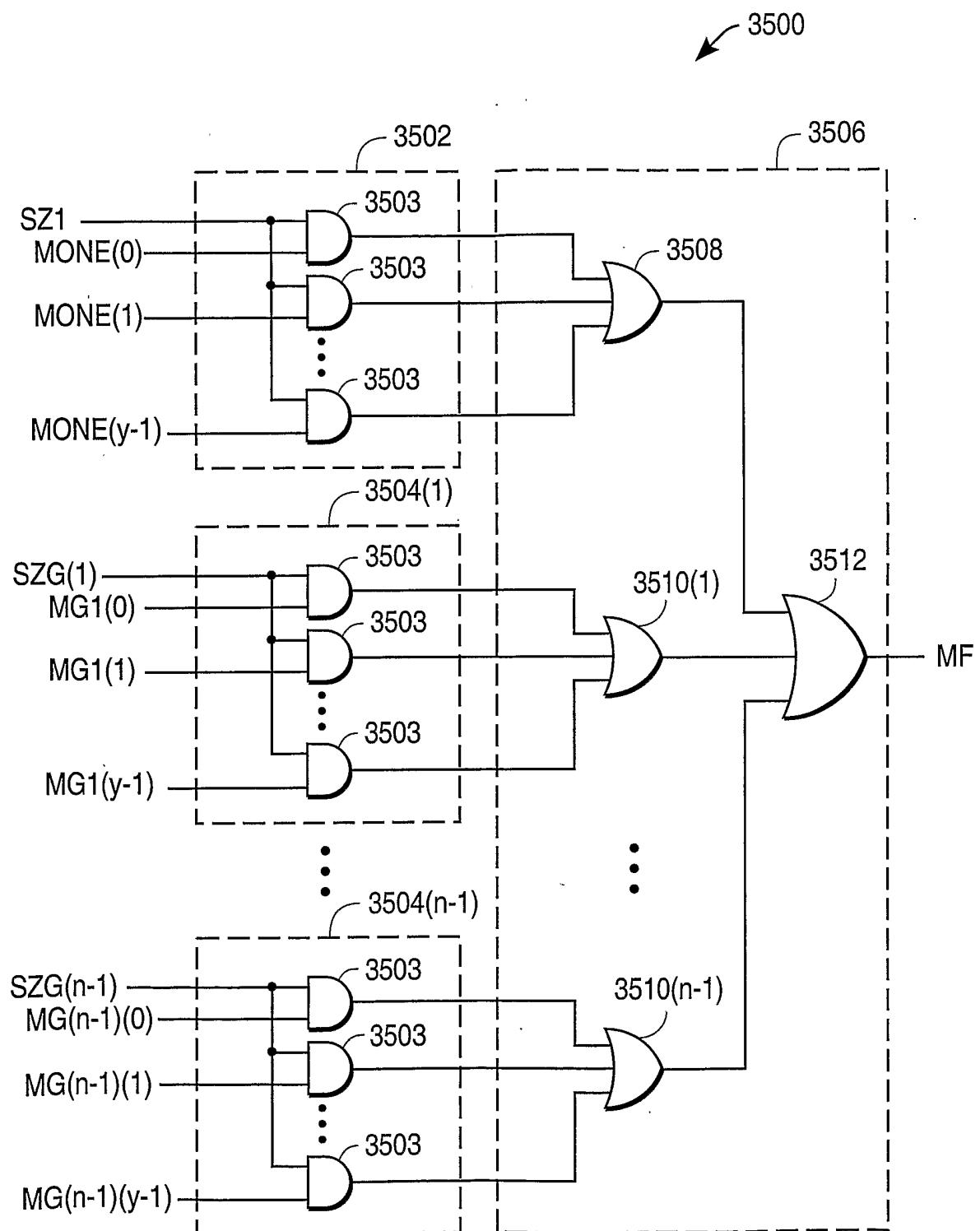

Figure 36 is a block diagram of another embodiment of the array match circuit of Figure 32 including qualifying logic circuits and OR logic;

Figure 37 is a logic diagram of one embodiment of the qualifying logic circuits and the OR logic of Figure 36;

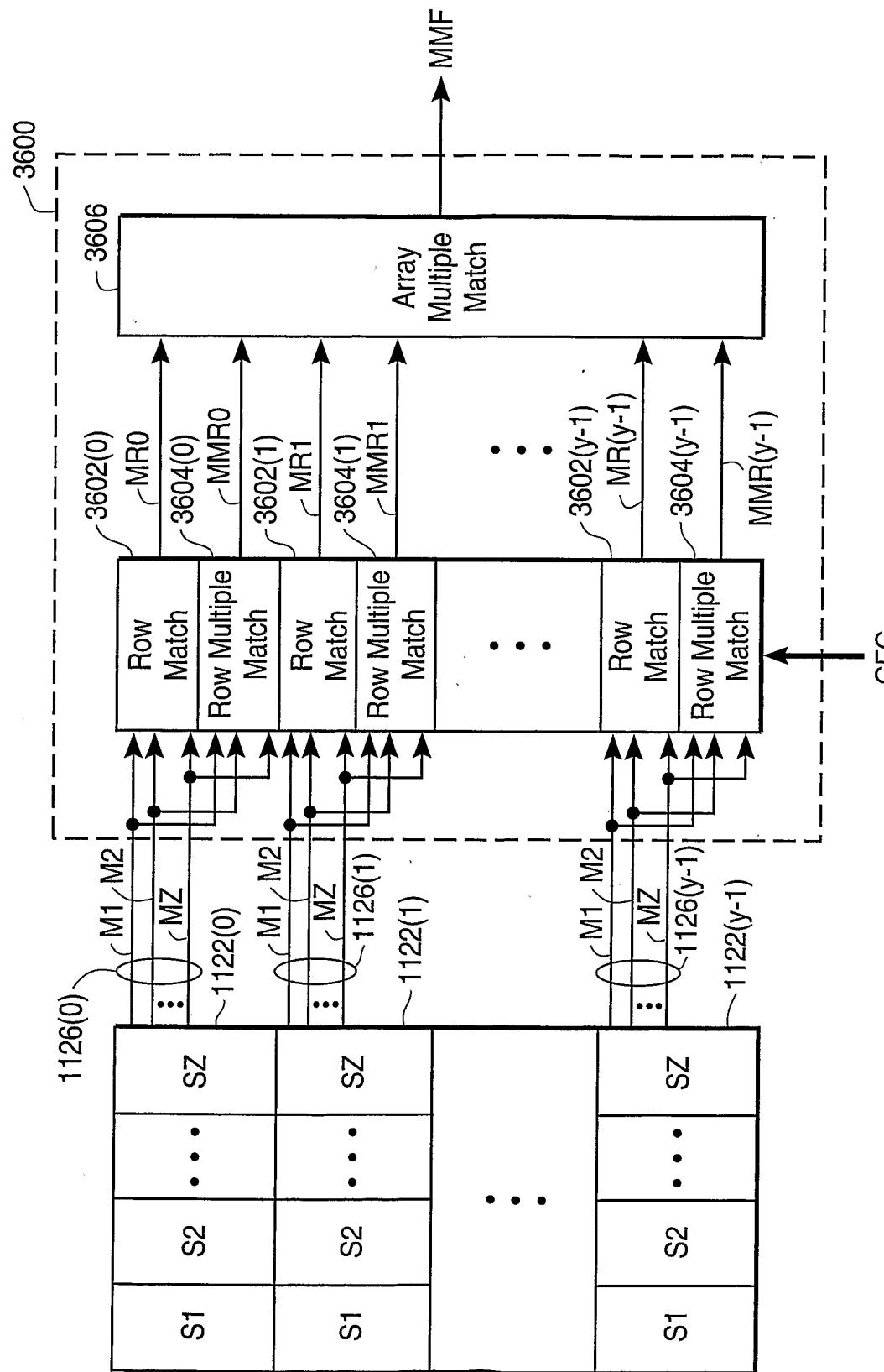

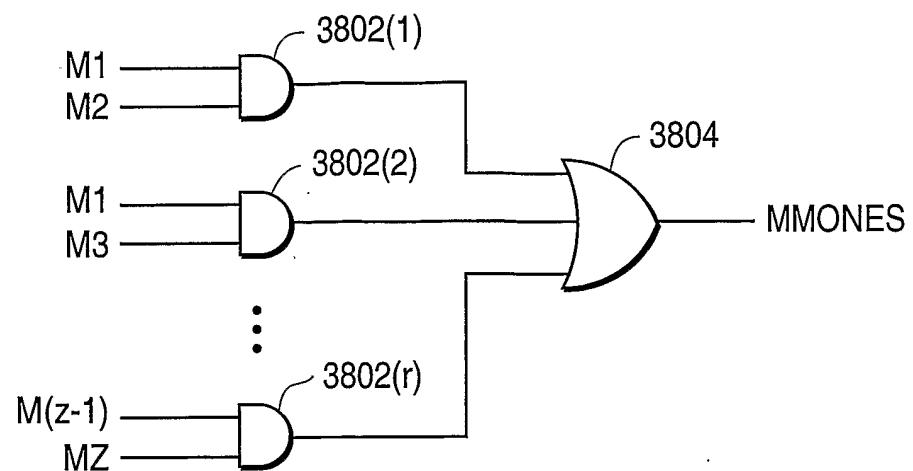

Figure 38 is a block diagram of one embodiment of the multiple match flag logic of Figure 13 including row match circuits, row multiple match circuits, and an array multiple match circuit;

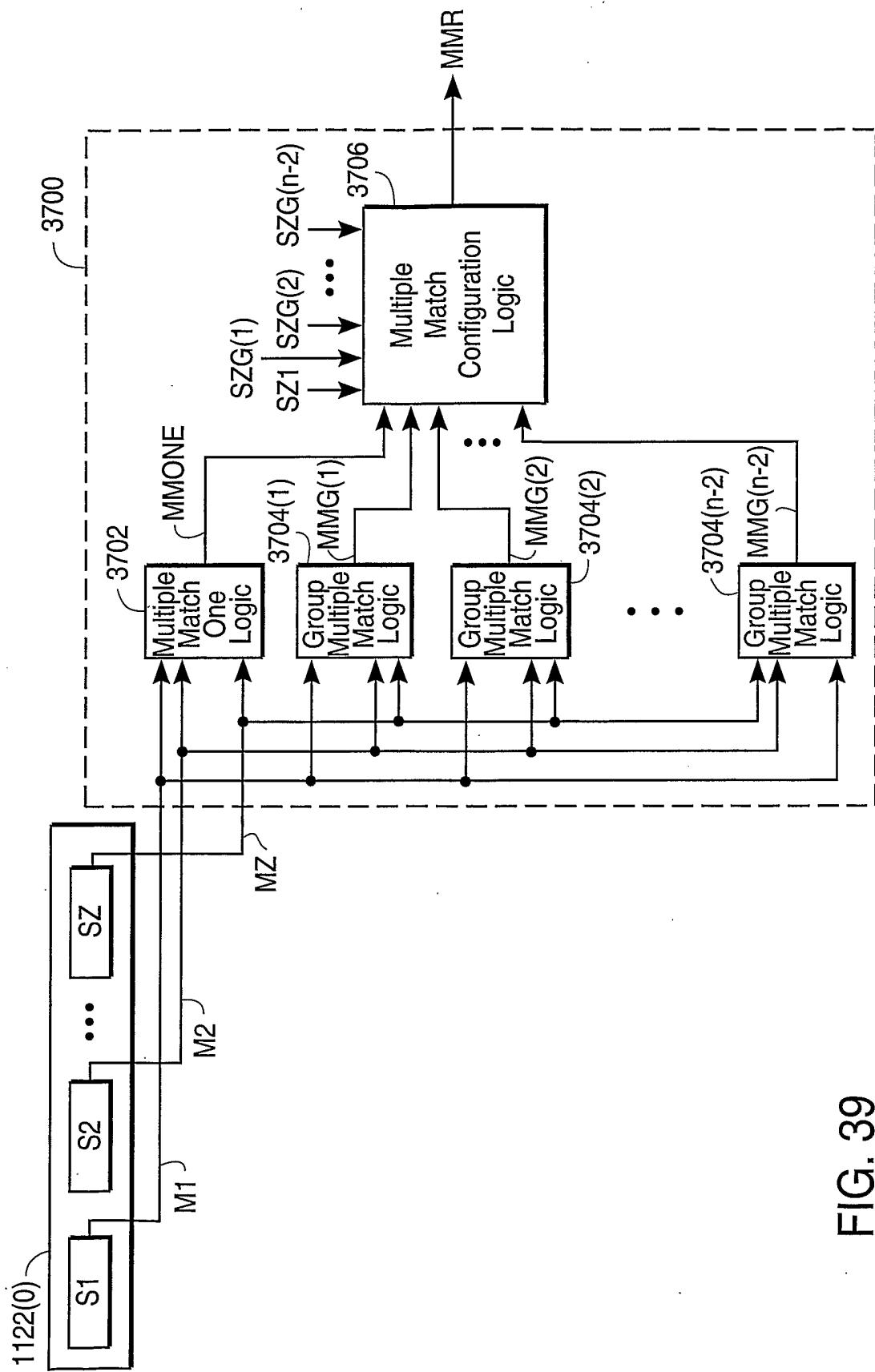

5 Figure 39 is a block diagram of one embodiment of a row multiple match circuit of Figure 38 including multiple match one logic, group multiple match logic circuits, and a multiple match configuration logic circuit;

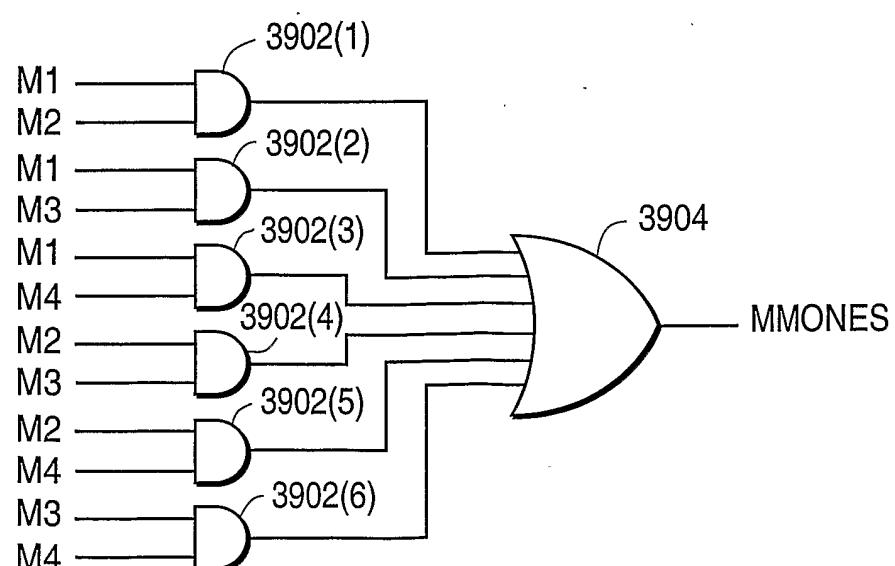

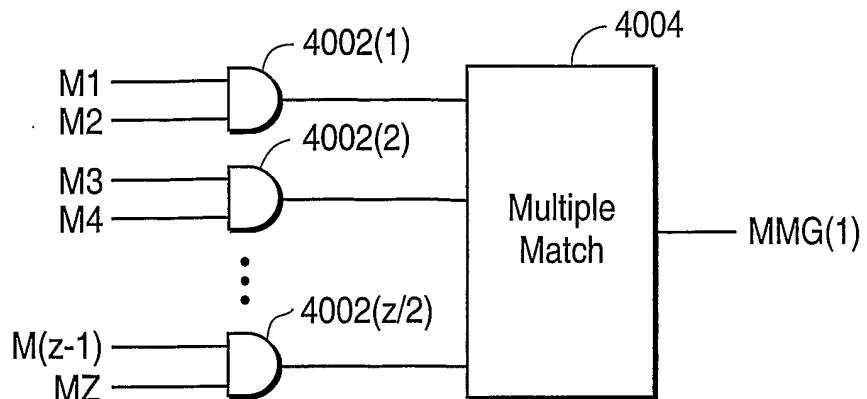

Figure 40 is a logic diagram of one embodiment of the multiple match one logic of Figure 39;

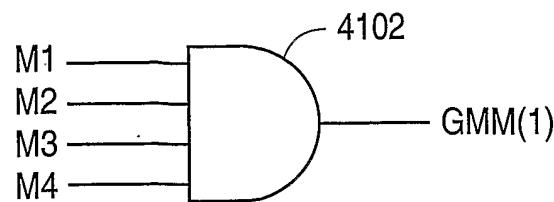

10 Figure 41 is a logic diagram of one embodiment of the multiple match one logic of Figure 40 for four row segments;

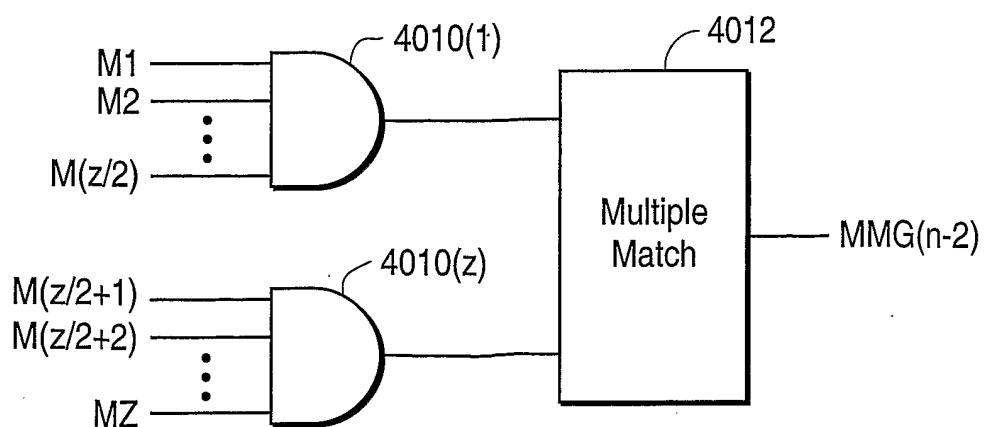

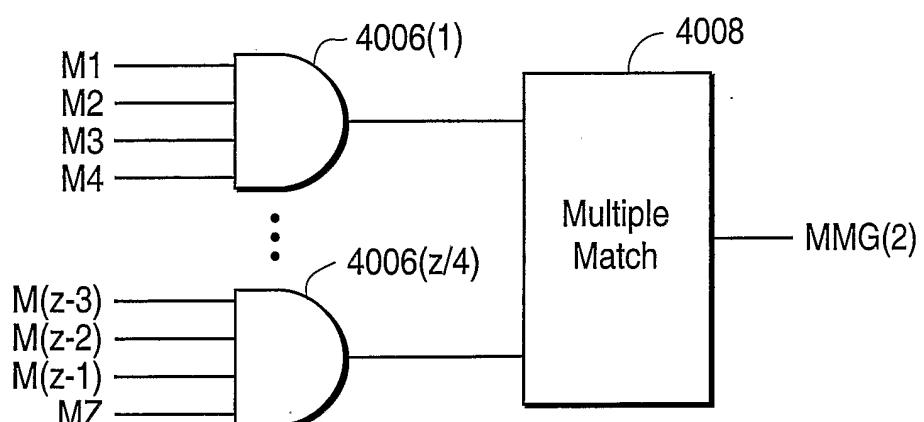

Figures 42A-42C are logic diagrams of embodiments of the group multiple match logic circuits of Figure 39;

15 Figure 43 is a logic diagram of one embodiment of one of the group multiple match circuits for four row segments;

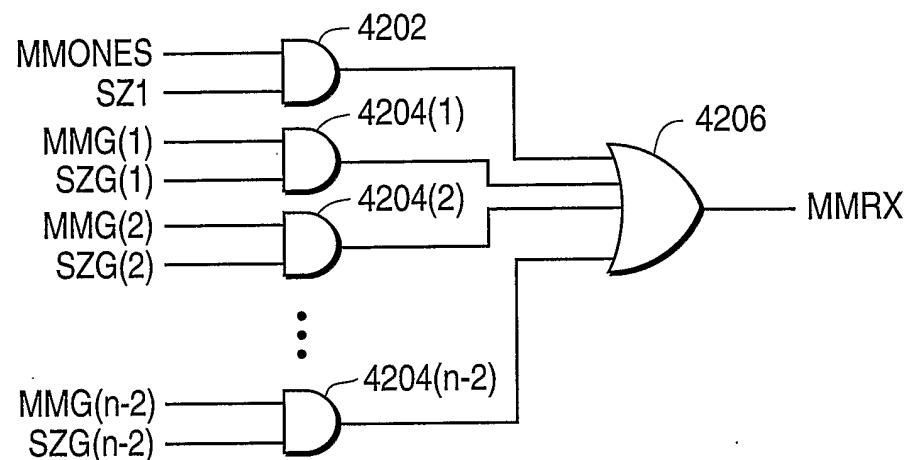

Figure 44 is a logic diagram of one embodiment of the multiple match configuration logic of Figure 39;

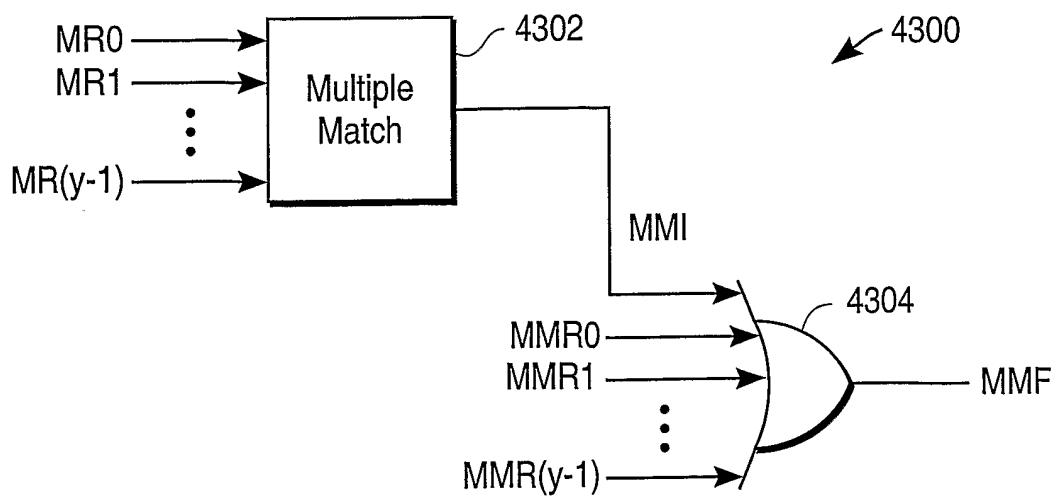

Figure 45 is a block diagram of one embodiment of the array multiple match circuit of Figure 38;

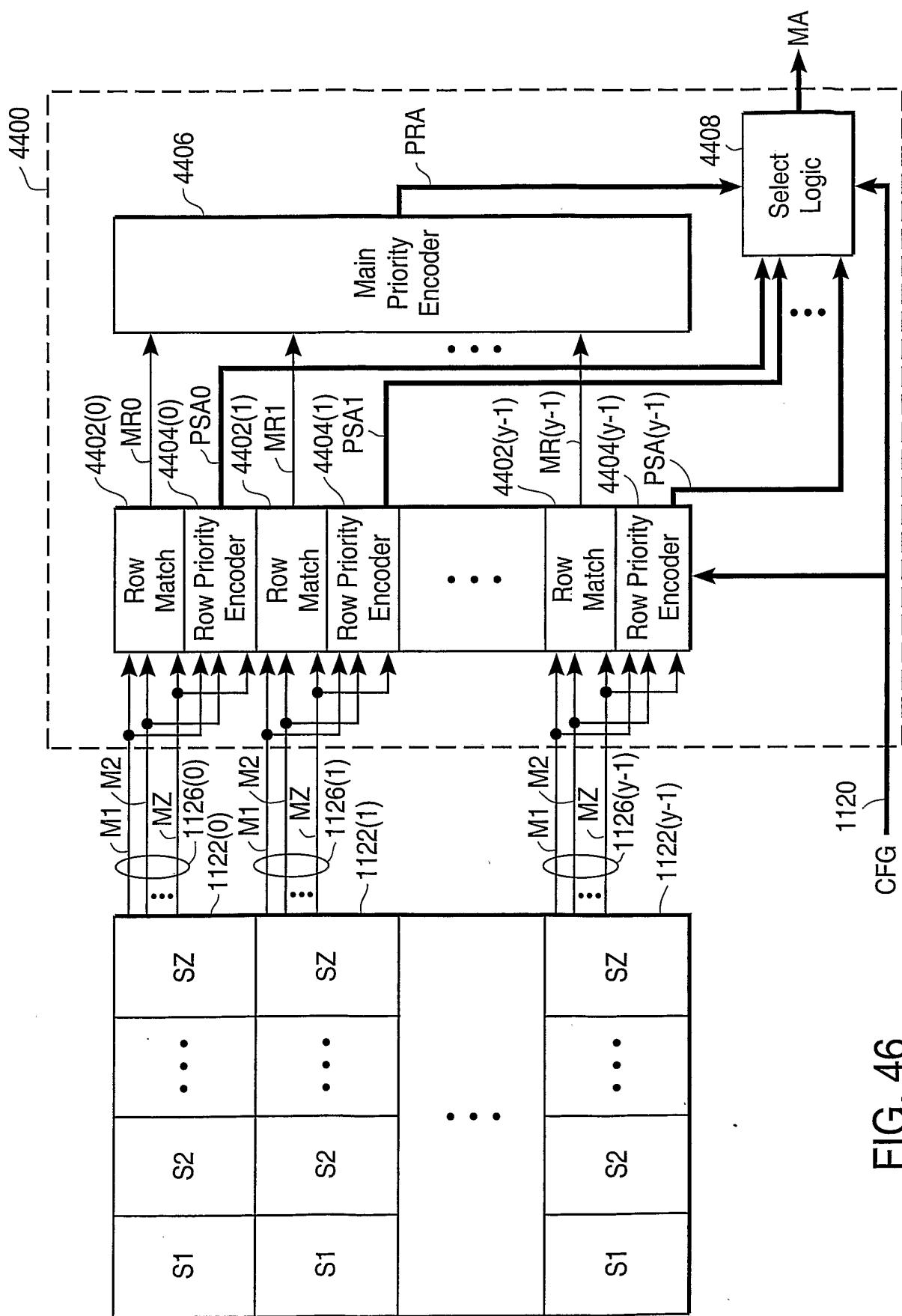

20 Figure 46 is a block diagram of the configurable CAM system of Figure 13 including one embodiment of the priority encoder logic having row match circuits, row priority encoder circuits, a main priority encoder, and select logic;

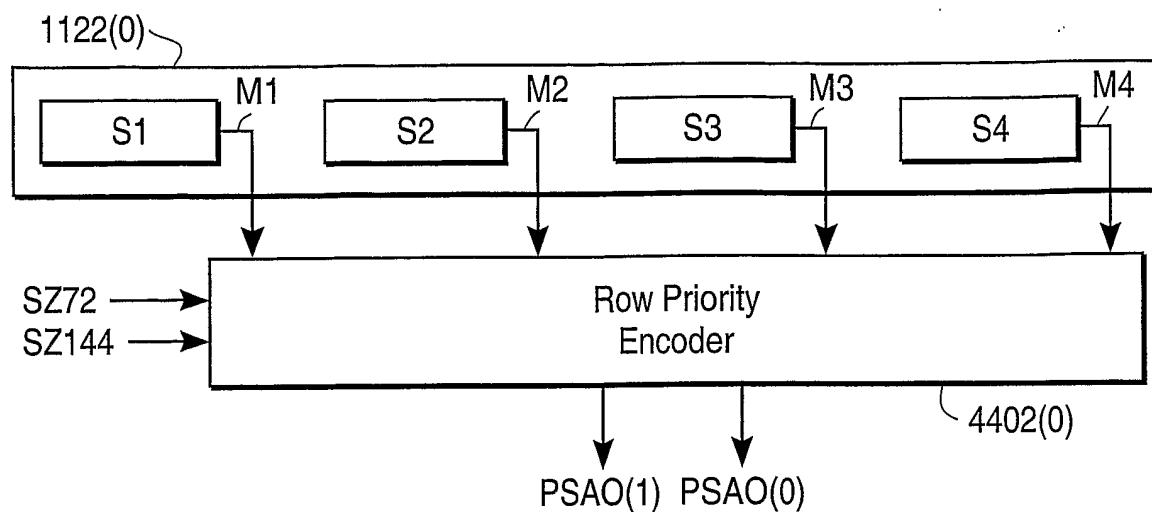

Figure 47 is a block diagram of one of the row priority encoder circuits for particular configurations of the CAM system;

25 Figure 48 is one embodiment of a truth table for one operating configuration for the row priority encoder circuit of Figure 47;

Figure 49 is another embodiment of a truth table for another operating configuration for the row priority encoder circuit of Figure 47;

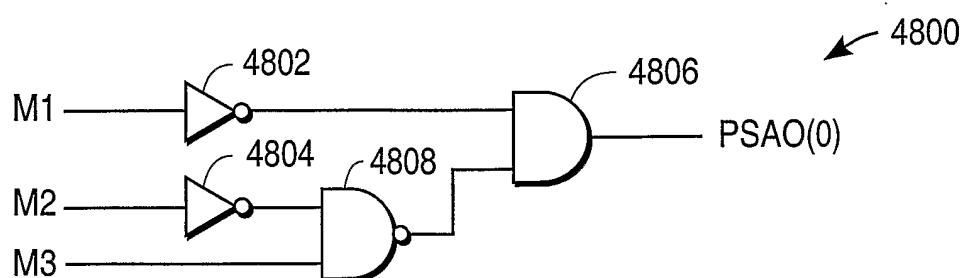

30 Figure 50 is a logic diagram of one embodiment of the row priority encoder circuit of Figure 47 for generating one segment address bit;

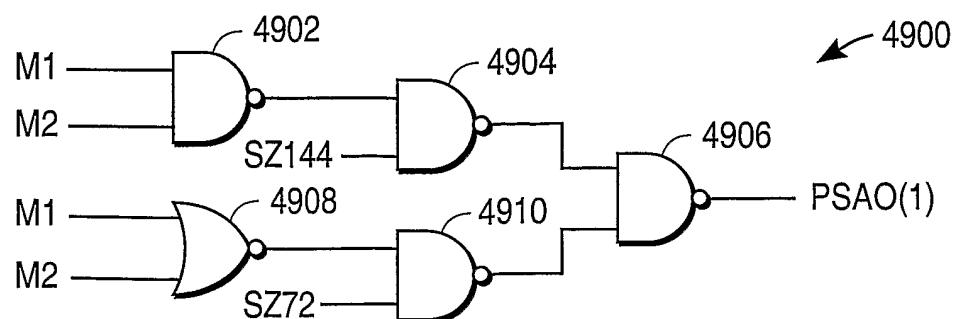

Figure 51 is a logic diagram of one embodiment of the row priority encoder circuit of Figure 47 for generating another segment address bit;

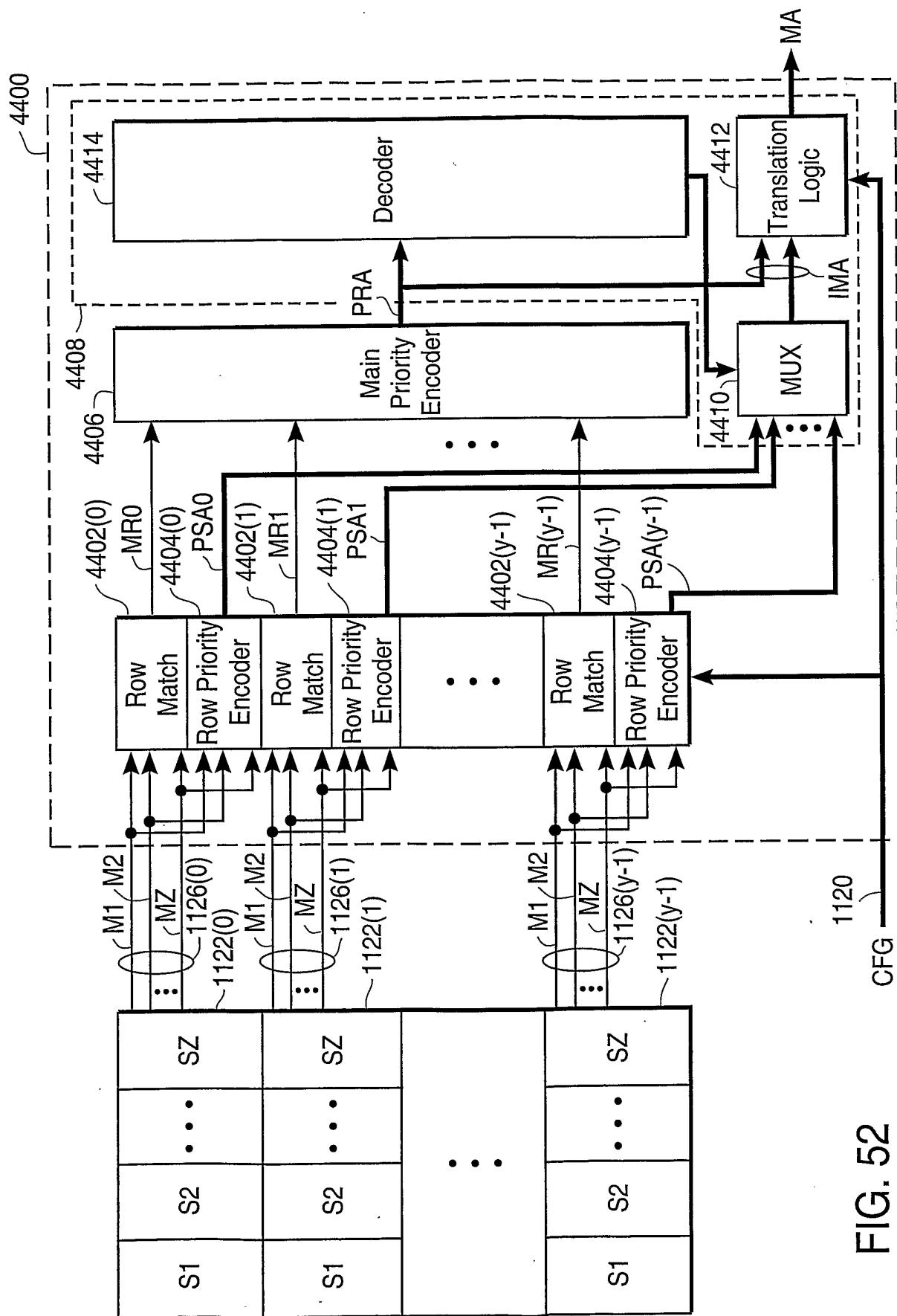

Figure 52 is a block diagram of the configurable CAM system of Figure 13 including one embodiment of the select circuitry having a decoder, a multiplexer, and translation logic;

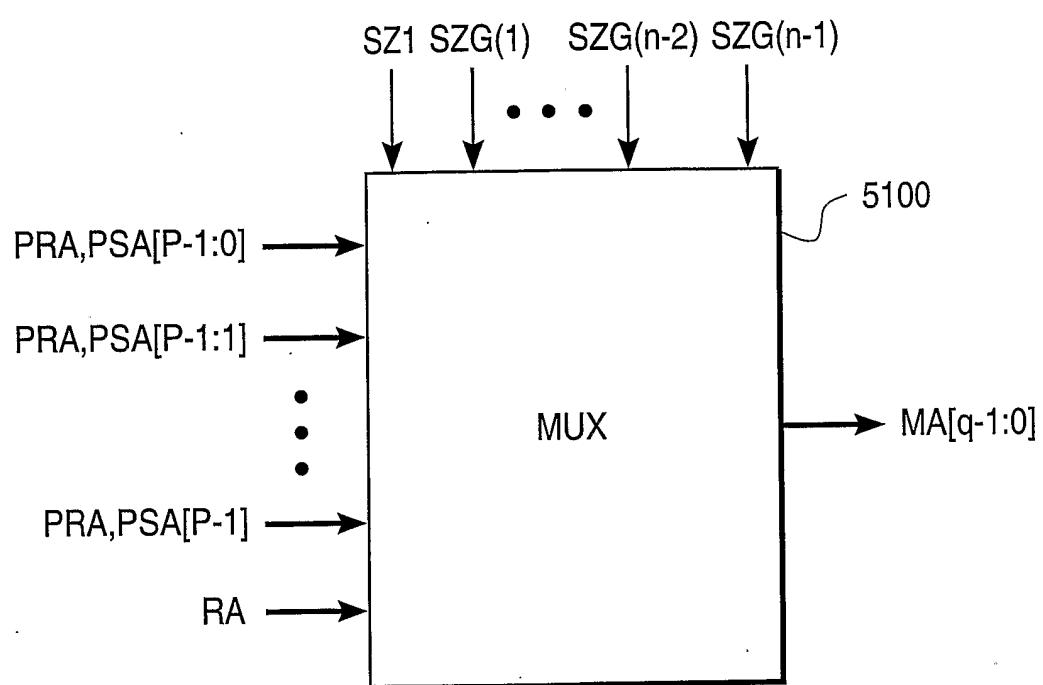

Figure 53 is a logic diagram of embodiment of the translation logic of Figure 52;

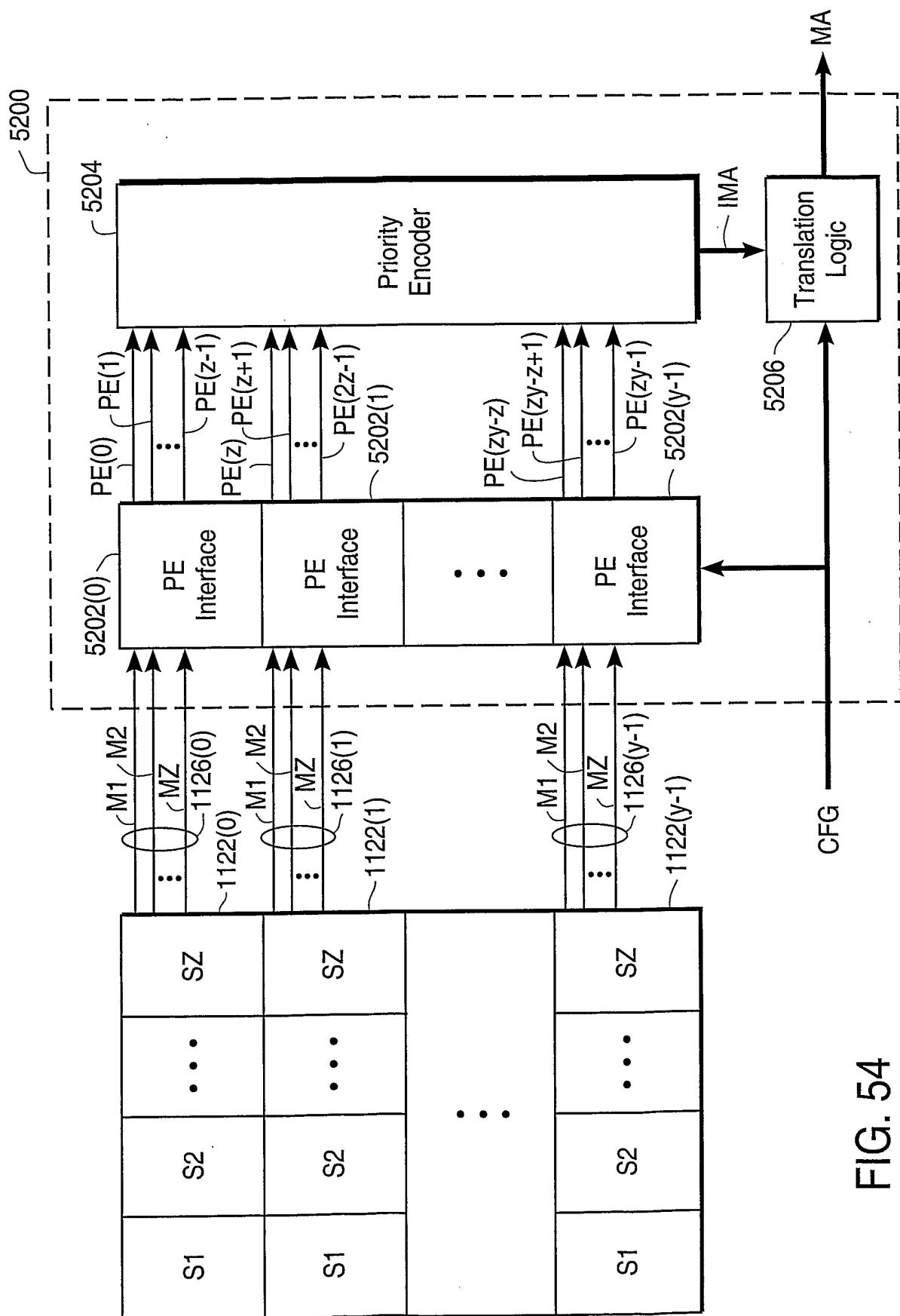

Figure 54 is a block diagram of the configurable CAM system of Figure 13 including another embodiment of the priority encoder having priority encoder interface circuits, a priority encoder, and translation logic;

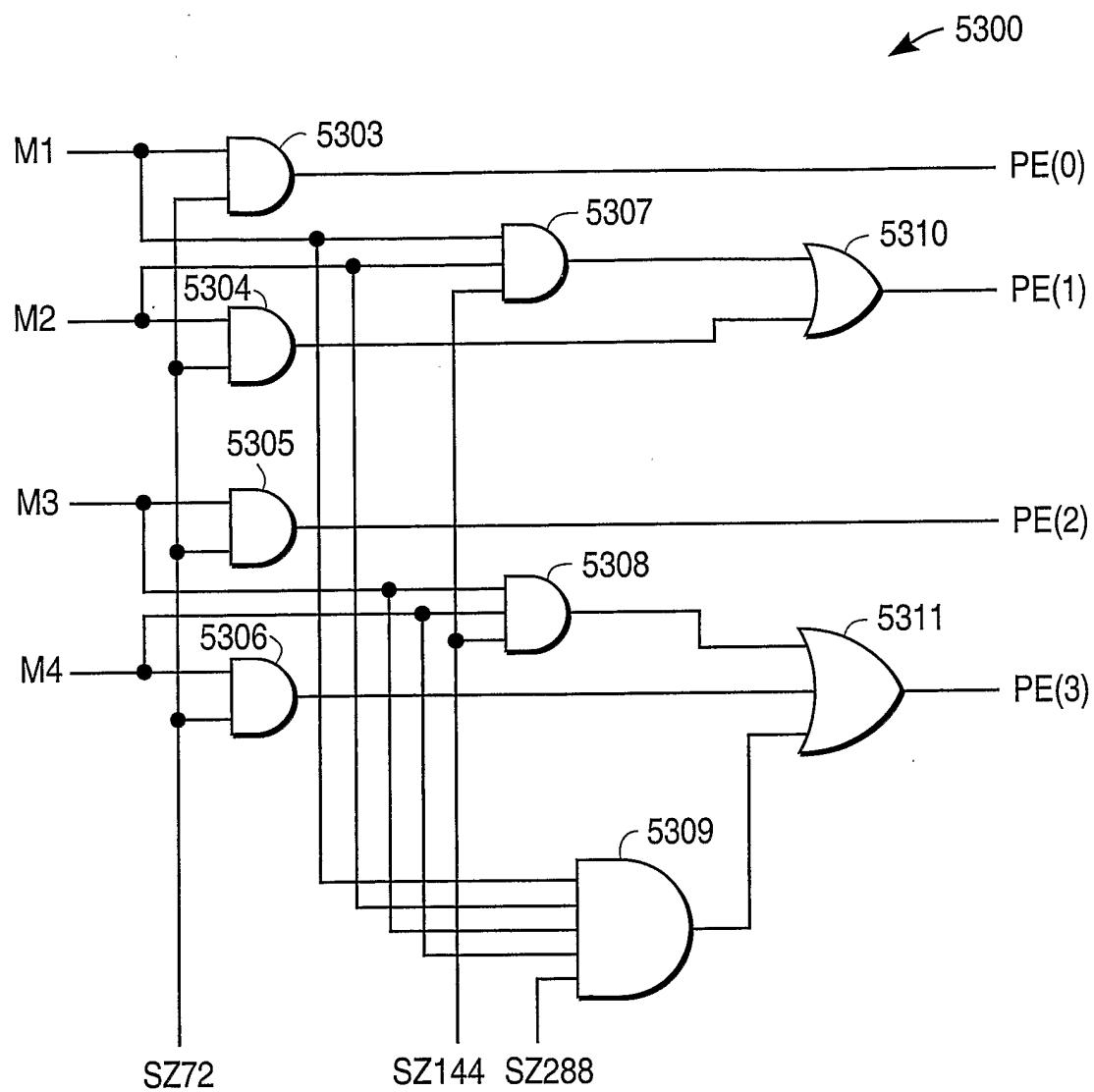

5 Figure 55 is a logic diagram of one embodiment of a priority encoder interface circuit of Figure 54 for particular configurations of the CAM system;

Figure 56 is a table summarizing the function of the priority encoder interface circuits of Figure 54;

Figure 57 is a logic diagram of one embodiment of the translation logic of Figure 54;

10 Figure 58 is a logic diagram of the translation logic of Figure 57 for a particular configuration of the CAM system;

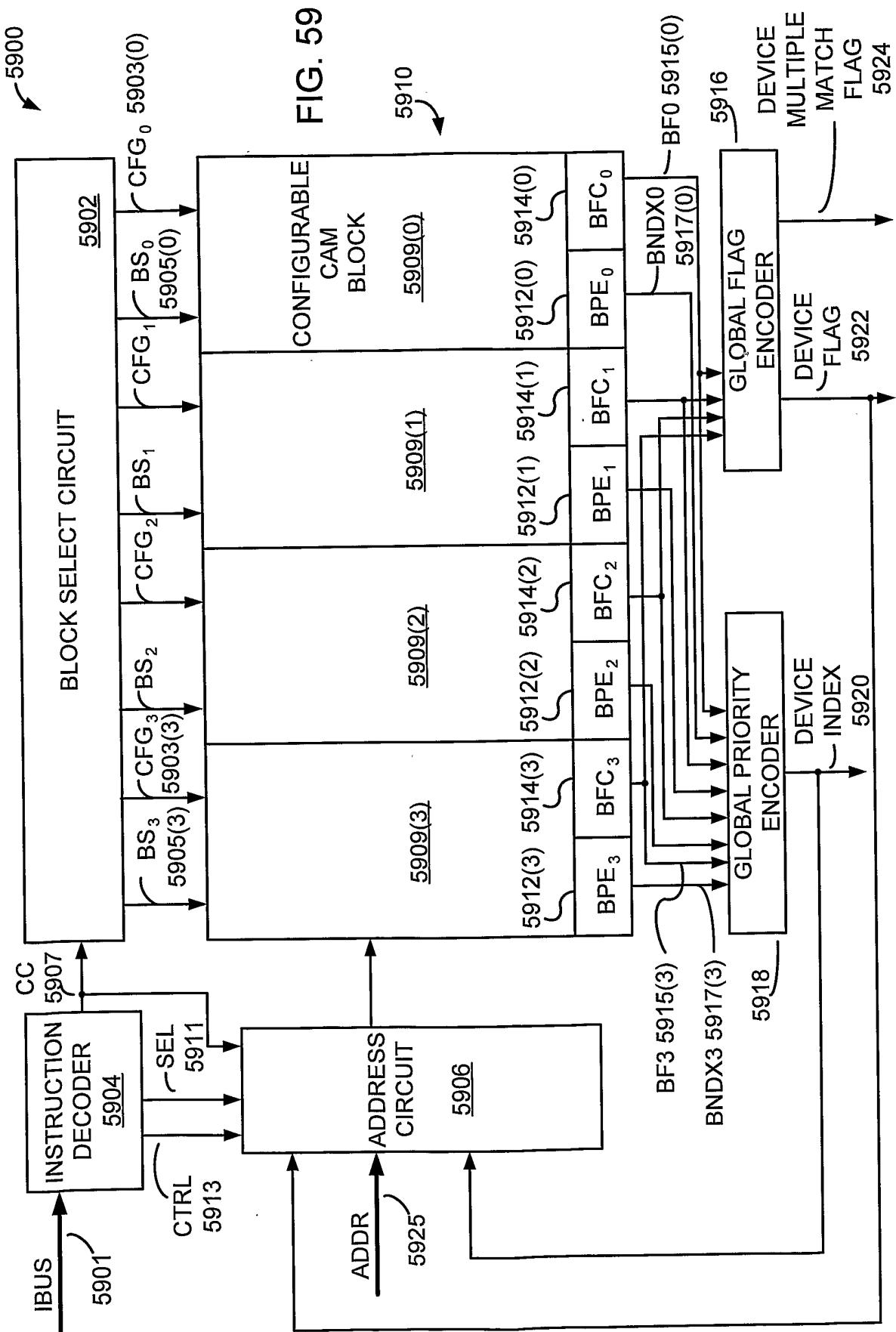

Figure 59 illustrates an embodiment of a CAM device that includes a CAM array formed by independently selectable CAM blocks and that has intra-row configurability;

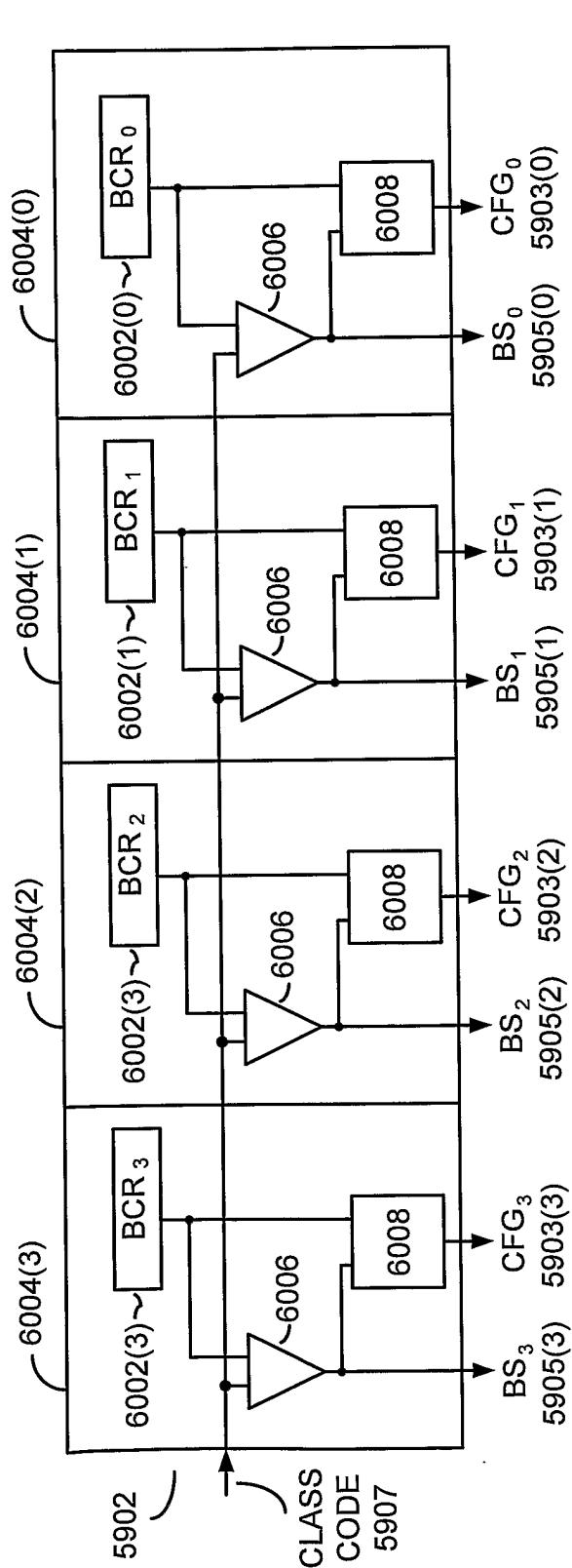

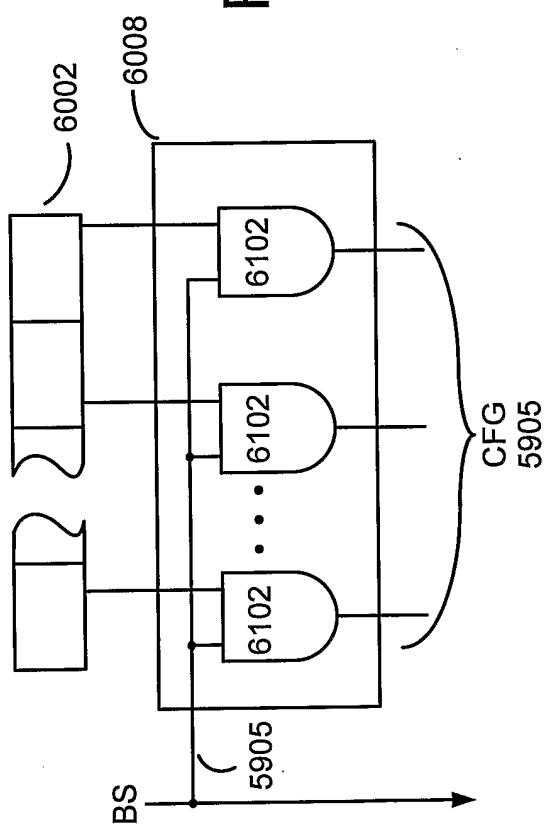

Figure 60 illustrates a block select circuit according to one embodiment;

15 Figure 61 illustrates a gating circuit according to one embodiment;

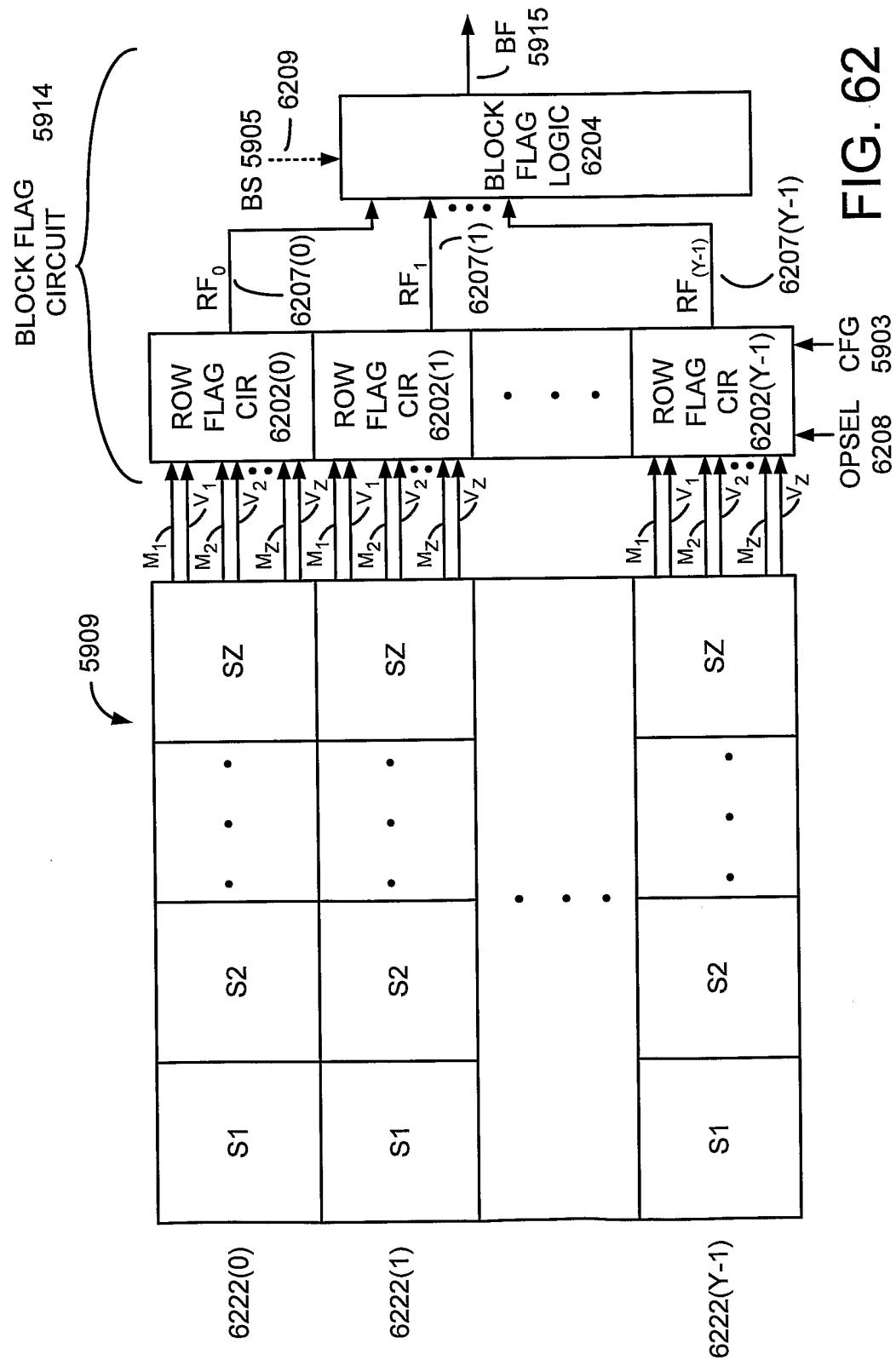

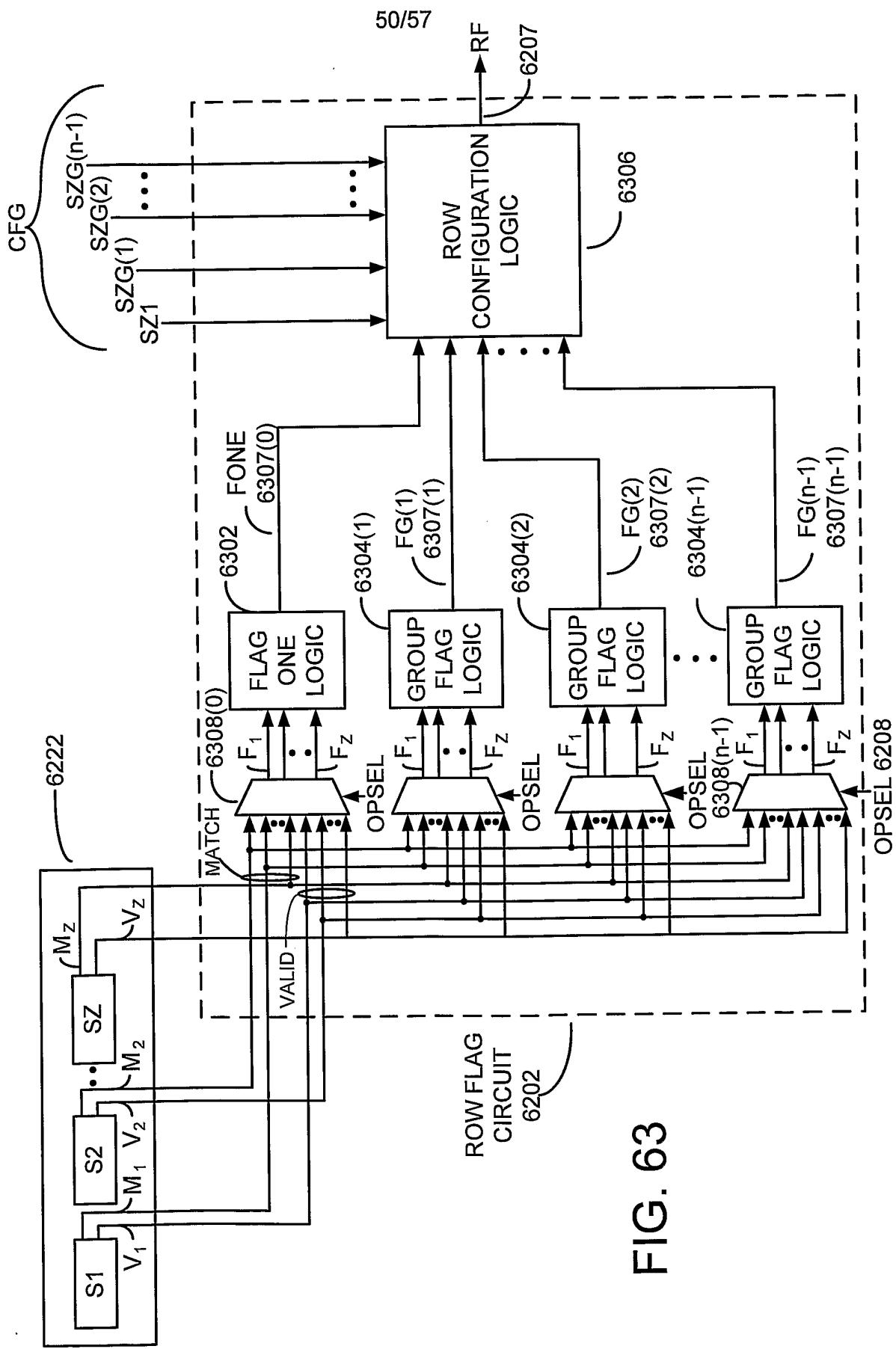

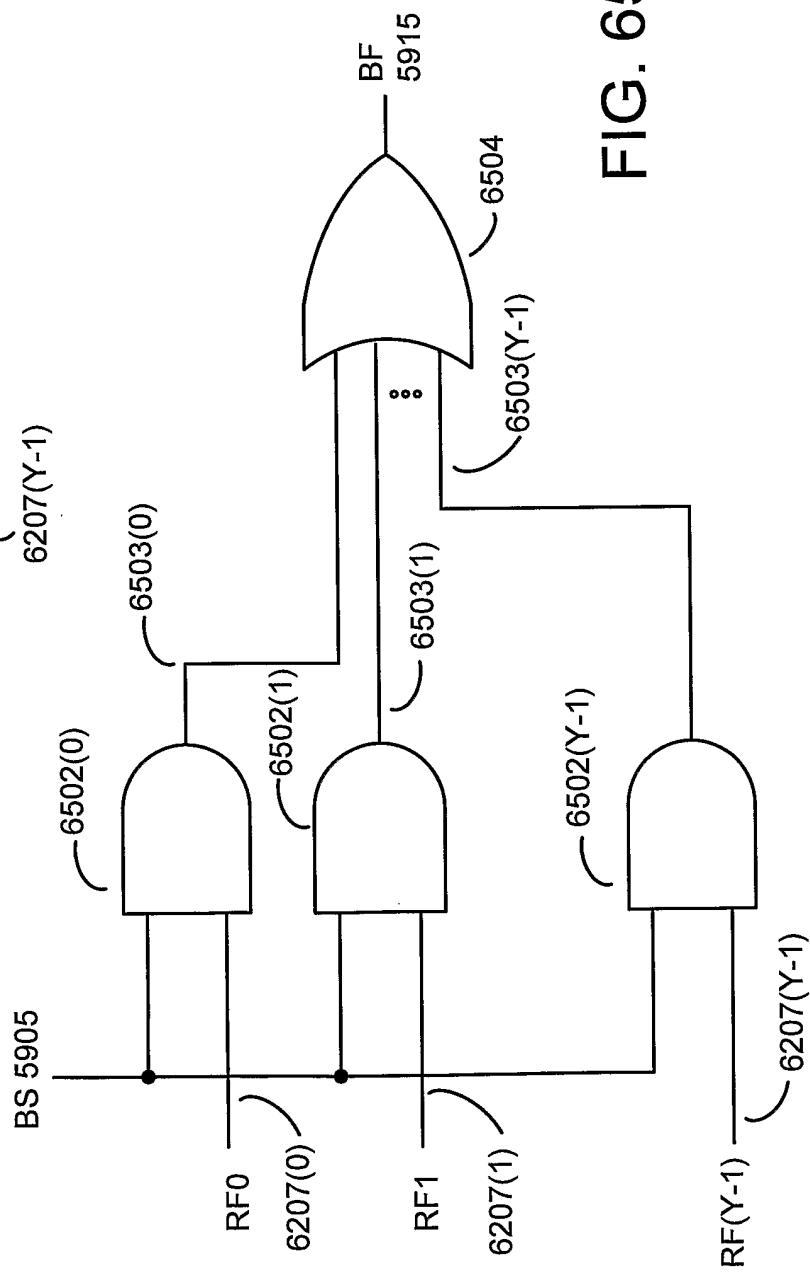

Figure 62 illustrates a block flag circuit according to one embodiment;

Figure 63 illustrates a row flag circuit from Figure 62 in greater detail;

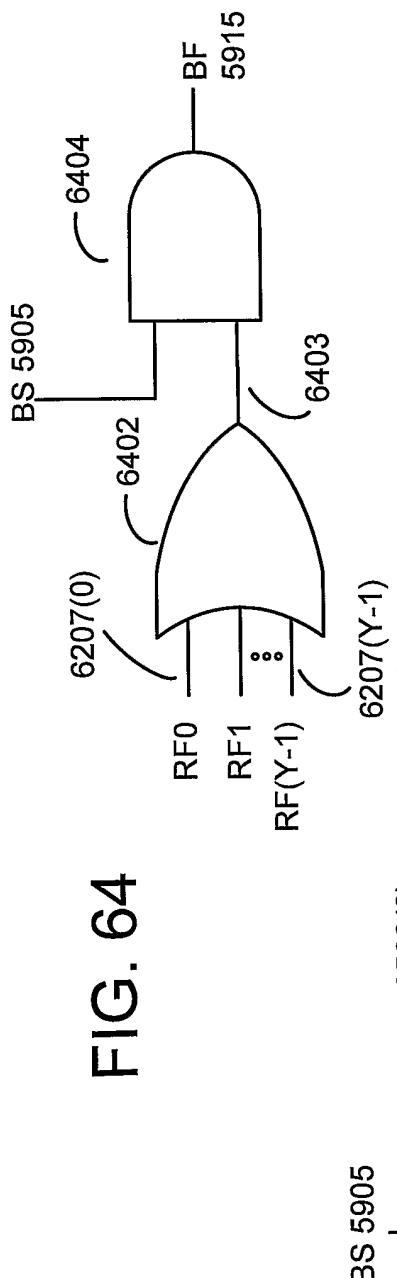

Figures 64 illustrates an embodiment of a block flag logic in which a block select signal is used to gate assertion of the block flag signal;

20 Figures 65 illustrates an alternate embodiment of a block flag logic in which a block select signal is used to gate assertion of the block flag signal;

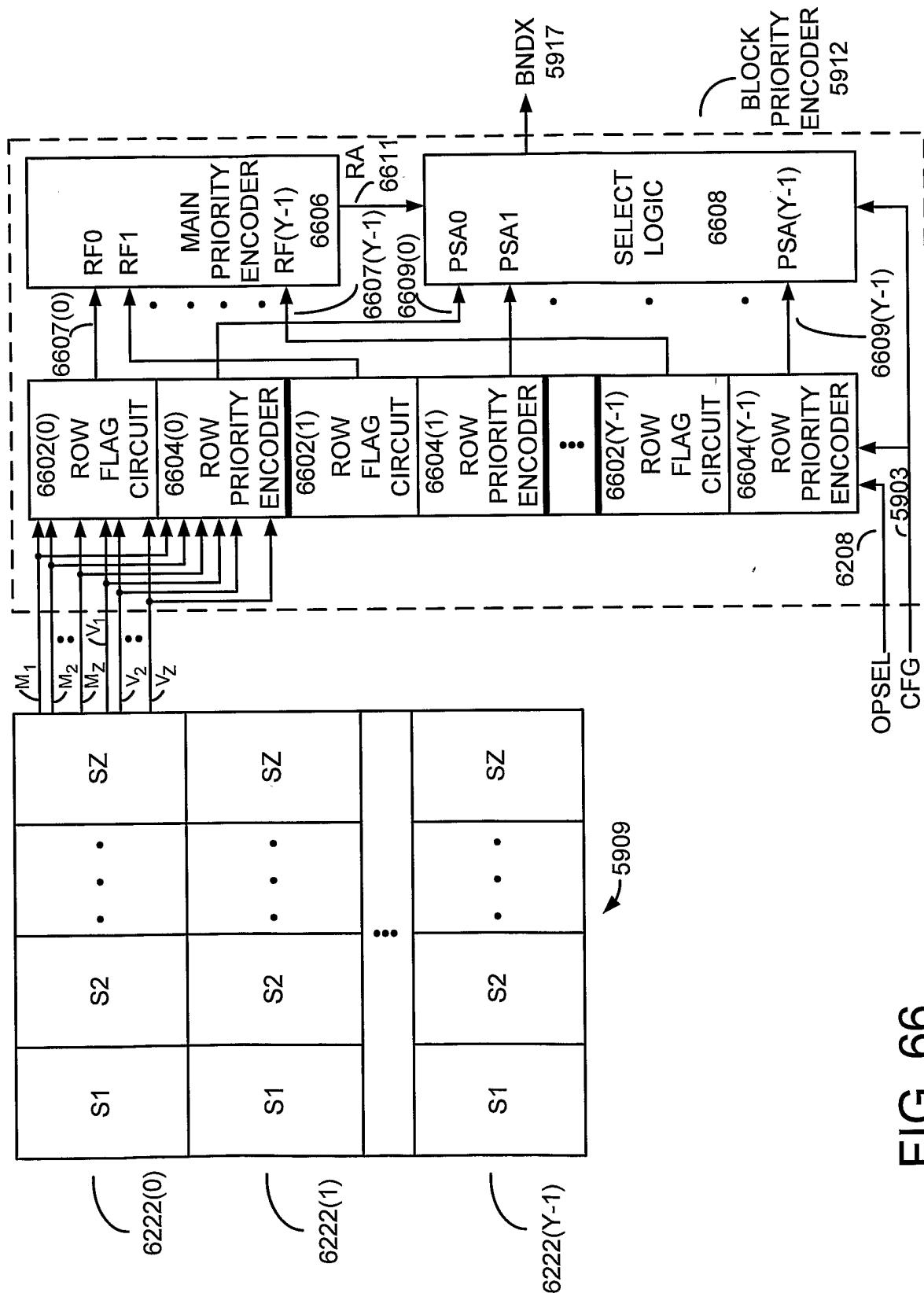

Figure 66 illustrates a block priority encoder according to one embodiment;

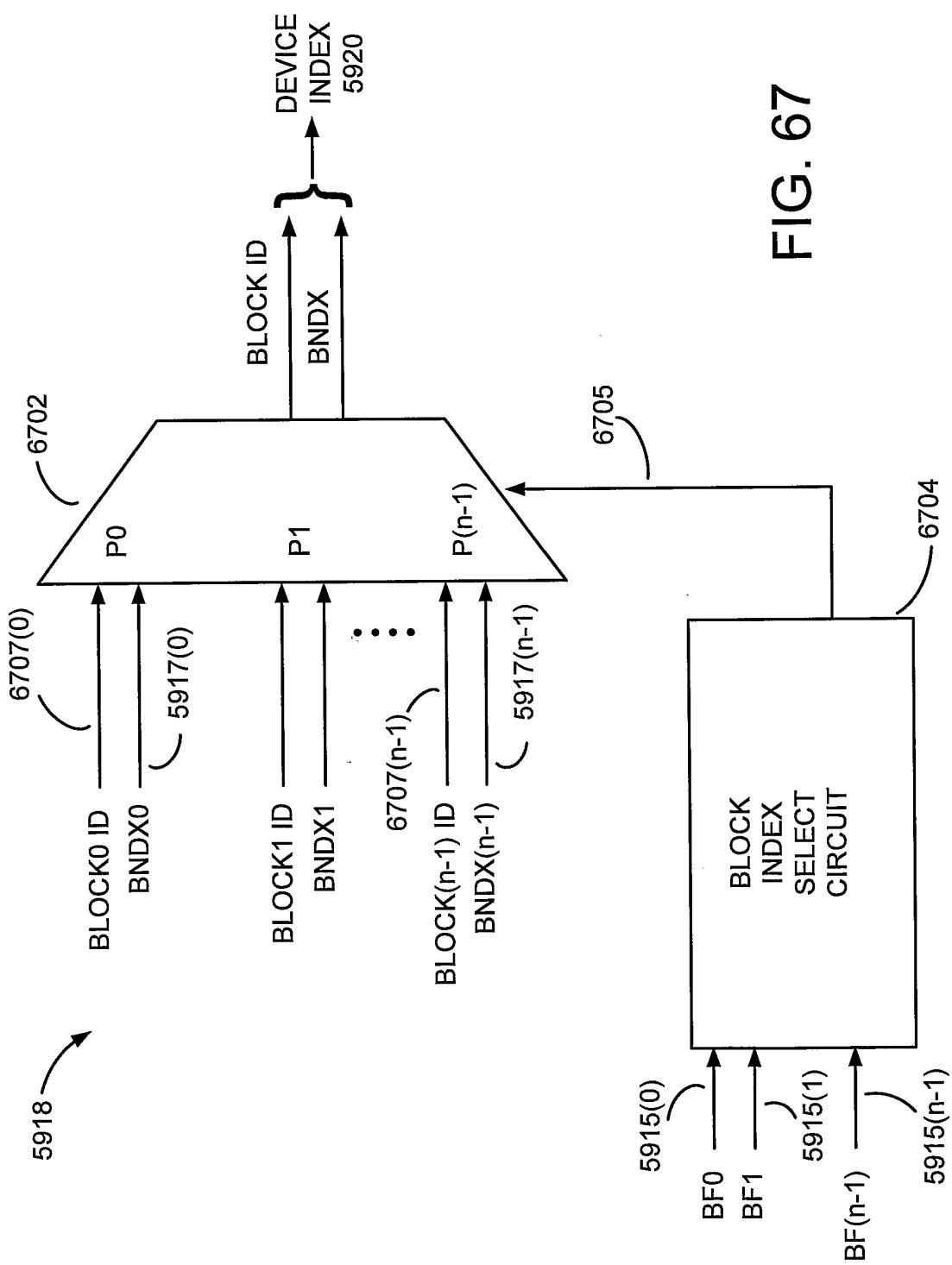

Figure 67 illustrates an embodiment of the global priority encoder of Figure 59;

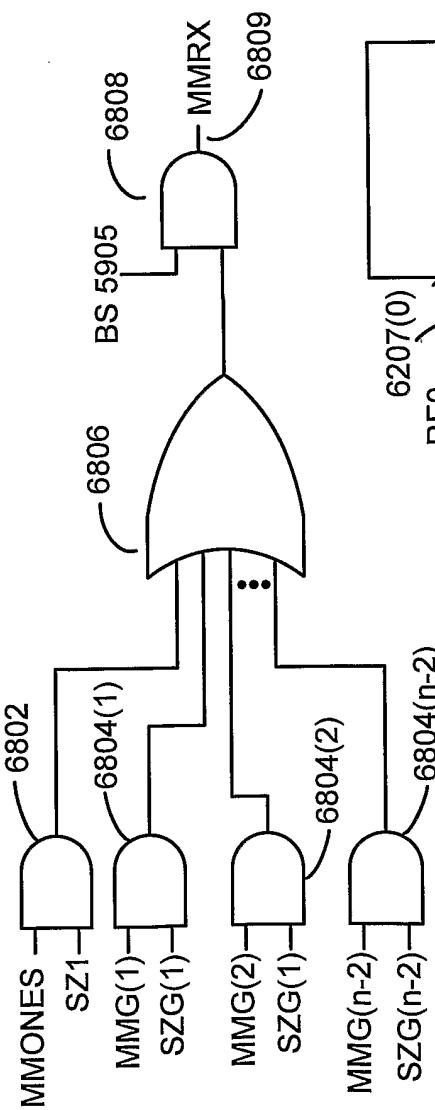

25 Figure 68 shows an alternative implementation of the row multiple match configuration logic of Figure 39;

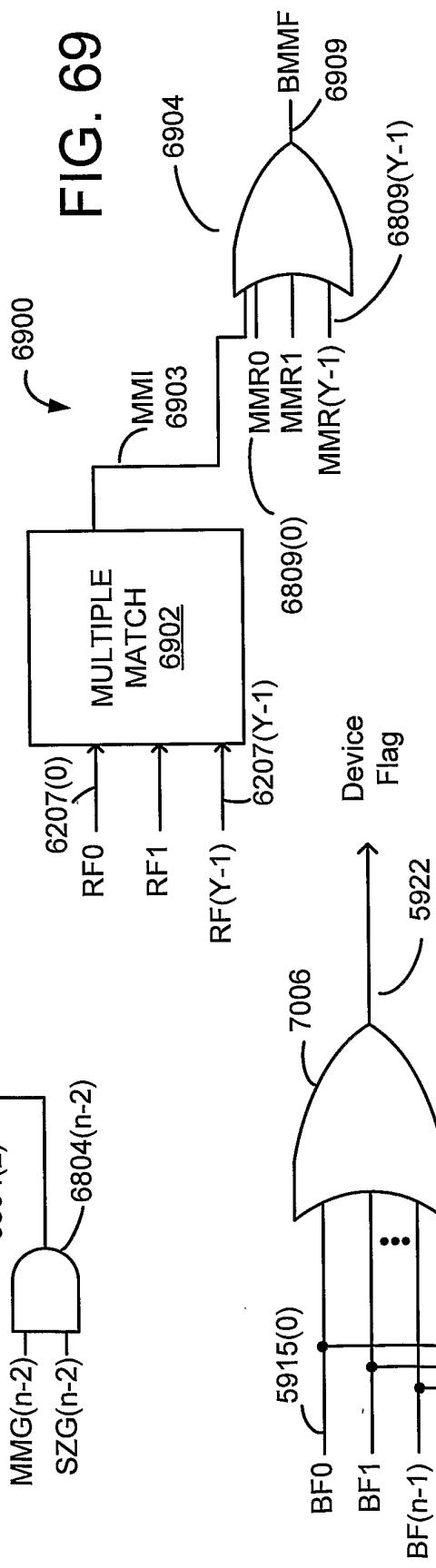

Figure 69 illustrates an embodiment of a block multiple match circuit;

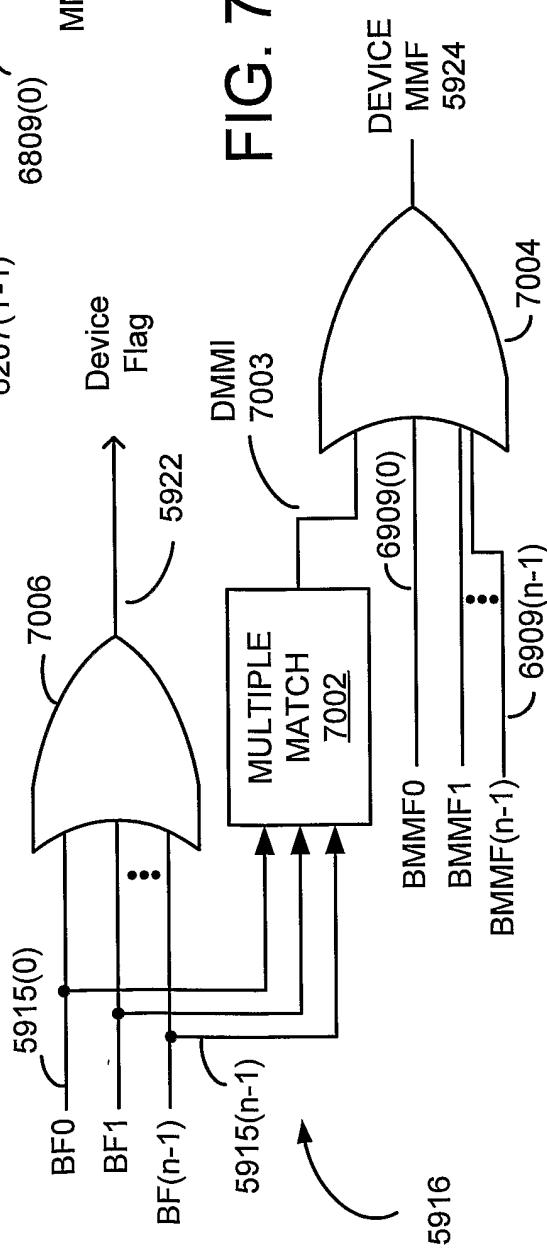

Figure 70 illustrates an embodiment of a global flag circuit of Figure 59;

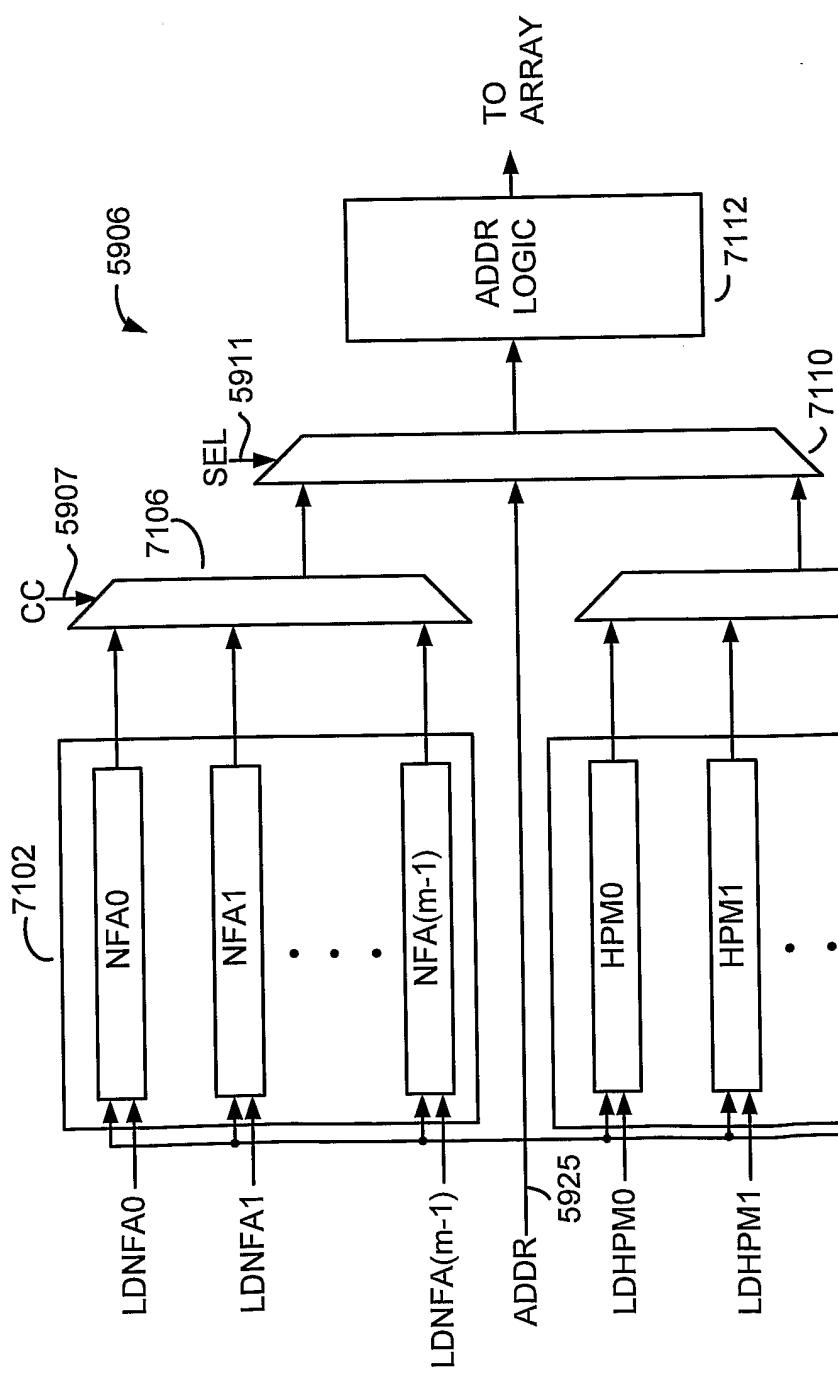

Figure 71 illustrates the address circuit of Figure 59 according to one embodiment;

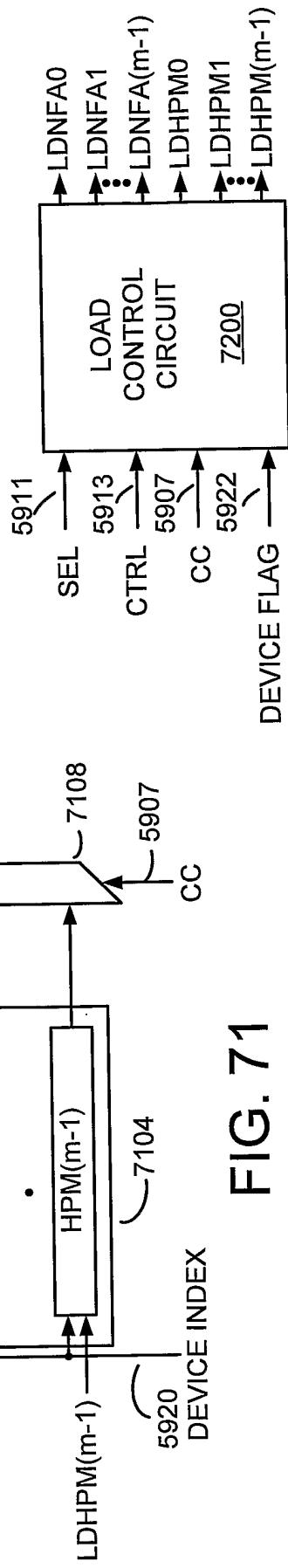

30 Figure 72 illustrates a load control circuit that may be provided within the address circuit of Figure 71;

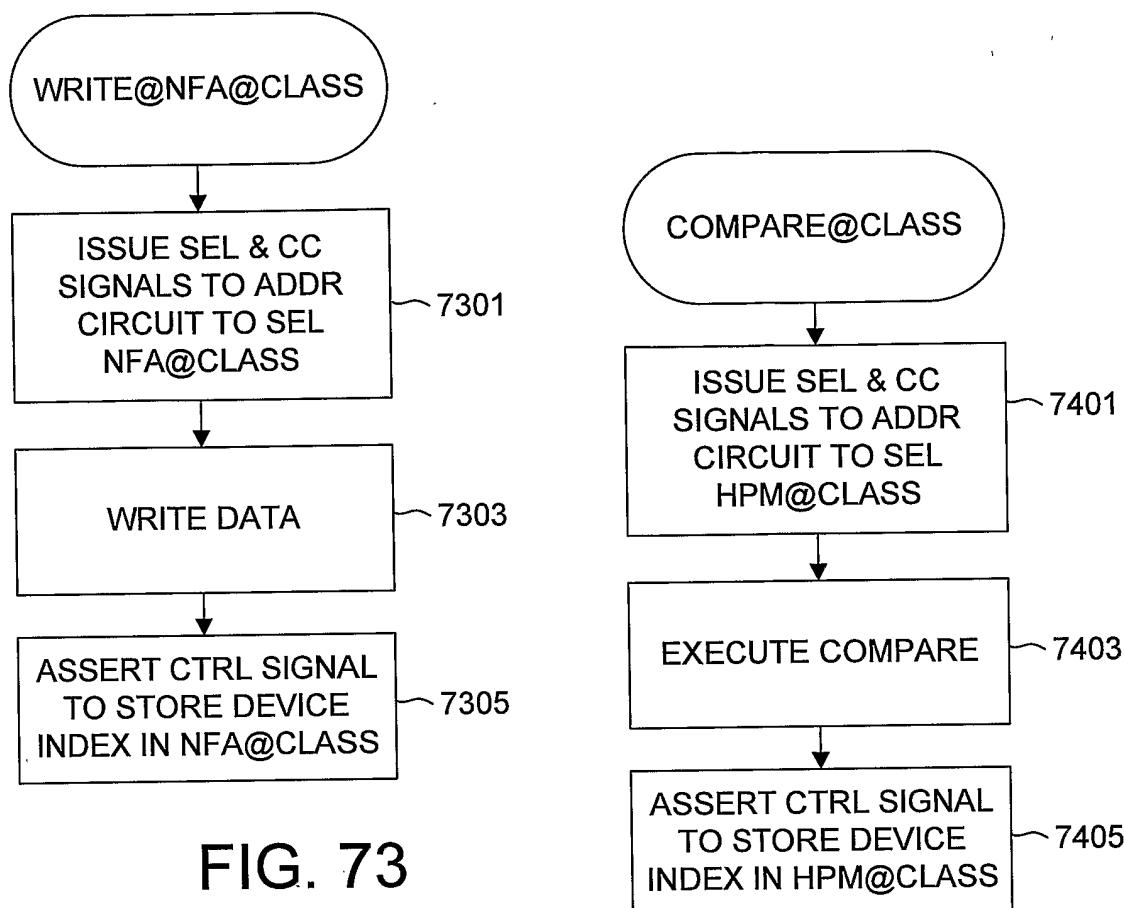

Figure 73 illustrates an exemplary operation of the instruction decoder of Figure 59 in response to an instruction to write to the next free address of a class-based partition of the CAM array;

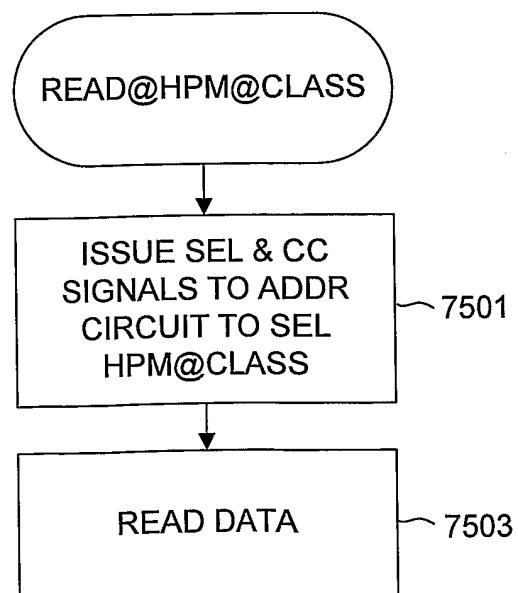

Figure 74 illustrates an exemplary operation of the instruction decoder of Figure 59 in response to an instruction to compare a comparand with the contents of a class-based partition of the CAM array;

5 Figure 75 illustrates an exemplary operation of the instruction decoder of Figure 59 in response to an instruction read a CAM word from the highest priority match address of a class-based partition of the CAM array;

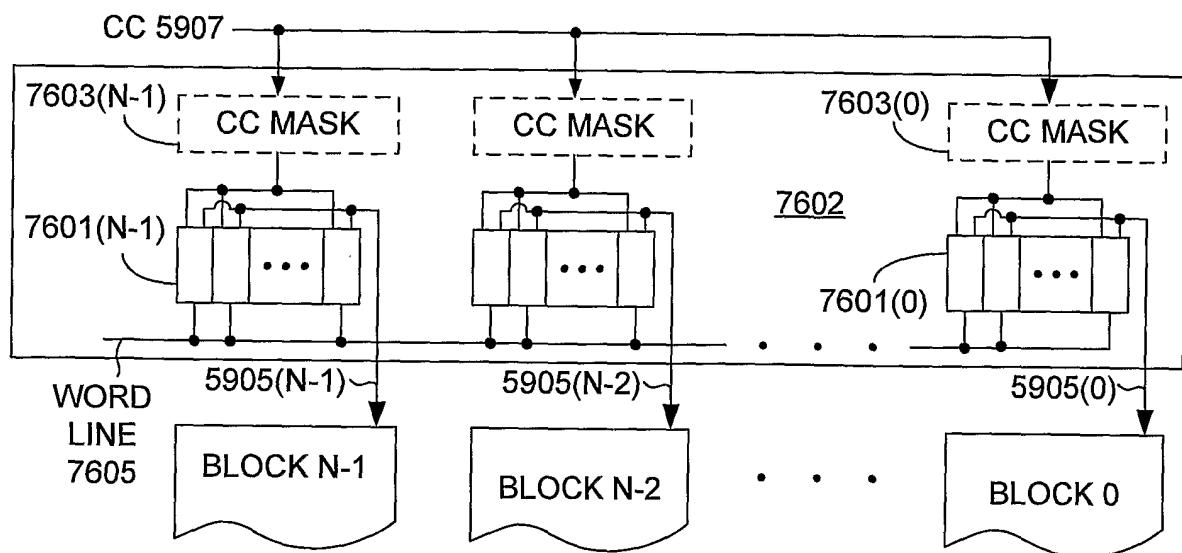

Figure 76 illustrates an alternative block select circuit which may be used in the CAM device of Figure 59; and

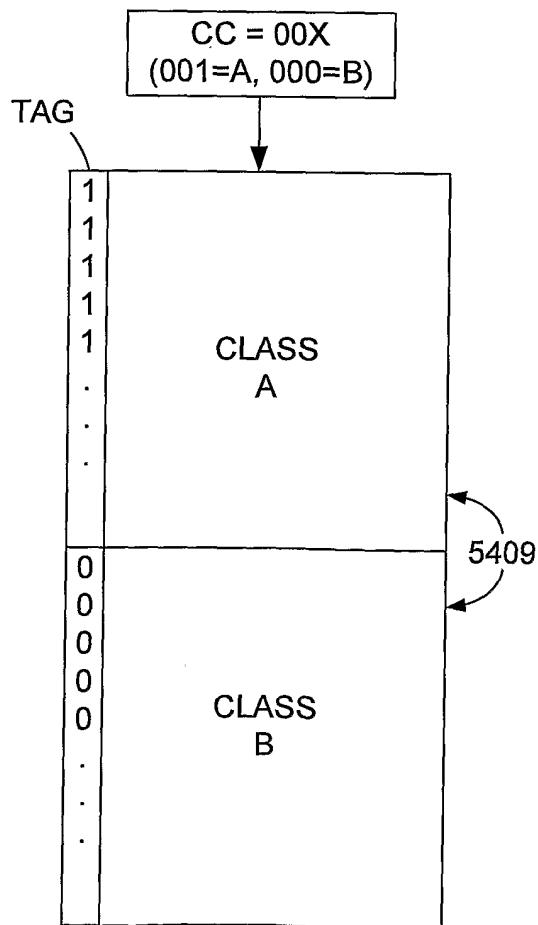

Figure 77 depicts a CAM block two classes of data stored therein.

10 Like reference numerals refer to corresponding parts throughout the drawing figures.

#### DETAILED DESCRIPTION

In the following description, for purposes of explanation, specific nomenclature is set forth to provide a thorough understanding of the present invention. However, it will be apparent to one skilled in the art that these specific details may not be required to practice the present invention.

15 In other instances, well-known circuits and devices are shown in block diagram form to avoid obscuring the present invention unnecessarily. Additionally, the interconnection between circuit elements or blocks may be shown as buses or as single signal lines. Each of the buses may alternatively be a single signal line, and each of the single signal lines may alternatively be buses. In addition, the logic levels assigned to various signals in the description below are arbitrary, and 20 therefore may be modified (e.g., reversed polarity) as desired.

Embodiments of the present invention are discussed below in the context of a CAM device 100 for simplicity only. It is to be understood that embodiments of the present invention are 100 equally applicable to CAM structures having other configurations of any suitable type of CAM cells. Further, architectural configurations of the present invention may be implemented in other 25 types of memory blocks such as, for instance, RAM, Flash, and EEPROM. Accordingly, the present invention is not to be construed as limited to specific examples described herein but rather includes within its scope all embodiments defined by the appended claims.

#### *CAM Device with Class-Based Partition*

Figure 1 shows a CAM device 100 in accordance with one embodiment of the present 30 invention as having a number  $n$  of CAM blocks 102(1)-102( $n$ ), a corresponding number  $n$  of block select circuits 106(1)-106( $n$ ), and a priority encoder 108. Each CAM block 102 includes a CAM array 104 having a plurality of rows of CAM cells for storing a plurality of CAM words therein, and is connected to a corresponding block select circuit 106. Each row may also include

one or more valid bits indicative of whether a valid CAM word is stored in the row. The valid bits may be used in a well-known manner to generate a full flag for the CAM block 102. CAM blocks 102 may be any suitable type of CAM block, including for example, synchronous, asynchronous, binary, and ternary CAMs. Further, each CAM block 102 may be any suitable size, and in some embodiments may be of different sizes. In one embodiment, each CAM block 102 includes 1k (1024) rows of CAM cells.

During a compare operation, each CAM block 102 receives comparand data from a comparand bus CBUS. Other signals provided to the CAM device 100 during the compare operation may be a clock signal CLK, one or more instructions from an instruction decoder (not shown for simplicity), and other control signals. In some embodiments, instructions and comparand data may be provided to the CAM blocks 102(1)-102(n) via the same bus. Other well-known signals which may be provided to the CAM blocks 102, such as word enable signals, reset signals, and enable signals, are not shown for simplicity.

Each CAM block 102 provides a plurality of match line signals to the priority encoder 108 via corresponding match lines ML. The match lines carry match signals indicative of match conditions in the CAM arrays 104. For simplicity, the plurality of match lines ML from each CAM block 102 are represented collectively in Figure 1. The priority encoder 108 generates an index corresponding to one of the matching CAM words in the device 100. In one embodiment, the priority encoder 108 outputs the index of the highest priority match. The highest priority match may be the lowest numbered address, the highest numbered address, or any other selected address.

For purposes of discussion herein, the first CAM block 102(1) in the device 100 is designated as the highest priority block, the second CAM block 102(2) is designated as the next highest priority block, and so on, and the last CAM block 102(n) is designated as the lowest priority block, although in actual embodiments priority may be reversed or otherwise modified. Thus, the highest priority CAM block 102(1) may include the lowest CAM addresses (i.e., CAM addresses 0 to k-1), the next highest priority block 102(2) may include the next lowest CAM addresses (i.e., CAM addresses k to 2k-1), and so on, and the lowest priority CAM block 102(n) may include the highest CAM addresses (i.e., CAM addresses (n-1)k to nk-1).

The block select circuits 106(1)-106(n) control whether corresponding CAM blocks 102(1)-102(n), respectively, participate in compare operations. Each block select circuit 106 stores a class code for the corresponding CAM block 102 which may be used to selectively disable the CAM block from participating in, and therefore from affecting the results of, one or more compare operations. During a compare operation, a comparand word is provided to the

CAM blocks 102 via CBUS, and a search code is provided to the block select circuits 106(1)-106(n) via bus SC. In alternate embodiments, the search code may be provided as part of the comparand word, in which case the CBUS is connected to the block select circuits 106, or may be provided as part of a compare instruction. Each block select circuit 106 compares the received 5 search code with its stored class code, and in response thereto, selectively disables the corresponding CAM block 102 from participating in the compare operation via a select signal SEL. In one embodiment, the block select circuit 106 enables its corresponding CAM block 102 to participate in the compare operation if the class code matches the search code and, conversely, disables the corresponding CAM block 102 if the class code does not match the search code. In 10 alternate embodiments, more than one CAM block 102 may share the same block select circuit 106.

The class codes assigned to the CAM blocks 102 may be used to partition the device 100 into individually selectable partitions of one or more CAM blocks 102. For example, in one embodiment, data stored in the first CAM block 102(1) may be assigned to a first class by storing 15 a first class code in block select circuit 106(1), data stored in the second CAM block 102(2) may be assigned to a second class by storing a second class code in block select circuit 106(2), and data stored in the remaining CAM blocks 102(3)-102(n) may be assigned to a third class by storing a third class code in block select circuits 106(3)-106(n). Then, for example, data stored in the first CAM block 102(1) may be selected for searching by setting the search code to match the 20 first class code stored in the block select circuit 106(1).

When the search code matches the first class code, the block select circuit 106(1) enables the first CAM block 102(1) to compare the comparand word with its stored data corresponding to the first class code. If the search code does not match the second and third class codes, the remaining block select circuits 106(2)-106(n) disable the corresponding, unselected CAM blocks 25 102(2)-102(n). When disabled, the unselected CAM blocks 102(2)-102(n) do not drive the comparand word into their respective CAM arrays 104 for the compare operation, thereby precluding comparison with unselected data corresponding to the second and third class codes. In this manner, the CAM blocks 102(1)-102(n) may be selectively searched according to class assignments, thereby allowing for a dynamically partitionable CAM device 100.

30 Since the comparand word is not compared with data stored in the disabled CAM blocks 102(2)-102(n), the disabled CAM blocks 102(2)-102(n) consume much less power during the compare operation than does the selected, enabled CAM block 102(1). In this manner, the class codes of present embodiments not only restrict compare operations to data in the selected CAM block(s), but also minimize power consumption of the unselected CAM block(s) during compare

operations. The advantage of reduced power consumption in unselected CAM blocks during compare operations achieved by present embodiments may be particularly useful in applications where power consumption is a concern.

The ability to selectively enable or disable one or more CAM blocks from participating in compare operations may be especially useful for combining routing look-up functions for different classes of networks in a single device 100. For example, in one embodiment, routing information for a first virtual private network (VPN) may be stored in a first CAM block 102(1), routing information for a second VPN may be stored in a second CAM block 102(2), routing information for a web search may be stored in a third block 102(3), and routing information for a local area network (LAN) may be stored in a fourth CAM block 102(4). Four unique class codes may be stored in corresponding block select circuits 106. Of course, more than one CAM block may be assigned to a particular network by storing the appropriate class code in more than block select circuit 106. During compare operations, comparand data corresponding to routing functions of one of these four networks may be exclusively compared with data stored in the corresponding CAM block(s) by simply setting the search code to match the appropriate class code. In some embodiments, an associative RAM may be partitioned into four partitions corresponding with the four class-defined partitions in the CAM device 100.

Figure 2 shows a CAM array 200 that is one embodiment of a CAM array 104 of Figure 1. The array 200 includes a plurality of CAM cells 202 organized in any number of rows and columns. Each row of CAM cells 202 is coupled to a match line ML and a word line WL. Each word line WL is driven by an address decoder 204 to select one or more of CAM cells 202 for writing or reading. For alternative embodiments, multiple CAM blocks may share a decoder. Each match line ML provides the match results of a compare operation to the priority encoder 108 (see also Figure 1). A match line ML indicates a match condition for the row only if all CAM cells 202 in that row match the comparand data. Each CAM cell 202 may be a binary, ternary, SRAM-based or DRAM-based CAM cell. In some embodiments, the match line ML is pre-charged for the compare operation. If any CAM cell 202 in the row does not match the comparand data, the CAM cell(s) 202 discharges the match line ML toward ground potential (e.g., logic low). Conversely, if all CAM cells 202 match the comparand data, the match line ML remains in a charged state (e.g., logic high). When the CAM block 102 is disabled in response to the select signal SEL, the comparand word is not driven into the array 200, and the match lines ML may remain in their charged state during the compare operation, regardless if there is a mismatch. The match lines need not be pre-charged for a subsequent compare operation. The ability to maintain the match lines of unselected CAM blocks in their charged state during the

compare operation may further reduce power consumption of present embodiments over prior art architectures.

Each column of CAM cells 202 is coupled to a bit line BL, a complementary bit line  $\overline{BL}$ , a comparand line CL, and a complementary comparand line  $\overline{CL}$ . The bit lines BL and  $\overline{BL}$  are coupled to sense amplifiers 206 that may enable data to be written to or read from a row of CAM cells 202. The comparand lines CL and  $\overline{CL}$  are coupled to comparand drivers 208, which in turn are coupled to a comparand register 210 via complementary data lines D and  $\overline{D}$ . The comparand drivers 208 selectively drive a comparand word received from the comparand register 210 via complementary data lines D and  $\overline{D}$  onto complementary comparand lines CL and  $\overline{CL}$  for comparison with data in CAM cells 202 in response the select signal SEL provided by the block select circuit 106. The comparand register 210 may be shared by all CAM blocks 102(1)-102(n). As discussed above with respect to Figure 1, the block select circuit 106 generates the select signal SEL in response to the search code and its stored class code.

In alternate embodiments, other CAM array architectures may be used. For example, in some embodiments, CAM array 200 may not include complementary comparand lines CL and  $\overline{CL}$ , in which case the complementary bit lines BL and  $\overline{BL}$  may be coupled to the comparand drivers 208 and be used to perform a compare operation as is generally known in the art. For example, in the first part of a compare cycle, compare data may be selectively driven onto BL and  $\overline{BL}$ , and during the second part of the compare cycle, BL and  $\overline{BL}$  may be driven with data to be output from CAM array 200. For other embodiments, only one of comparand lines CL and  $\overline{CL}$  or bit lines BL and  $\overline{BL}$  may be needed.

Figure 3 shows a block select circuit 300 that is one embodiment of the block select circuit 106. The block select circuit 300 includes a memory 302 and a compare circuit 304. The memory 302 stores the class code for the corresponding CAM block 102 of device 100, and may be any suitable programmable memory element such as, for instance, a register, flip-flop, EEPROM, EPROM, SRAM, and so on. The compare circuit 304 compares the class code received from the memory 302 with a search code received from bus SC and, in response thereto, generates the select signal SEL which selectively enables or disables the corresponding CAM block 102. The compare circuit 304 may be any suitable circuit which compares the search code and the class code, including for example an exclusive-OR type logic gate or a CAM cell.

Figure 4 shows a block select circuit 400 that is one embodiment of the block select circuit 300. The block select circuit 400 is shown to include a 3-bit memory 302 and a 3-bit compare circuit 304, although in other embodiments more or less bits may be used. The memory 302

includes three data flip-flops 402(0)-402(2), and the compare circuit 304 includes three exclusive-NOR (XNOR) gates 404(0)-404(2) and an AND gate 406. Each XNOR gate 404(0)-404(2) includes a first input terminal to receive a corresponding search code bit SC, a second input terminal to receive a corresponding class code bit CC from the corresponding flip-flop 402, and an output terminal connected to the AND gate 406. A 3-bit class code CC[0:2] may be clocked into respective flip-flops 402(0)-402(2) using the clock signal CLK, where flip-flop 402(0) stores the first class code bit CC[0], flip-flop 402(1) stores the second class bit code CC[1], and flip-flop 402(2) stores the third class code bit CC[2].

During compare operations, the XNOR gates 404(0)-404(2) compare search code bits SC[0:2] with respective class code bits CC[0:2] and, if there is match, drive their output terminals to logic high. Conversely, if there is a mismatch, the XNOR gate 404 drives its output terminal to logic low. If all search code bits SC[0:2] match corresponding class code bits CC[0:2], then AND gate 406 asserts the select signal SEL to logic high, thereby enabling the corresponding CAM block 102 to participate in the compare operation. Otherwise, if any of the search code bits SC[0:2] mismatch corresponding class code bits CC[0:2], the AND gate 406 de-asserts the select signal to logic low, thereby disabling the corresponding CAM block 102 from participating in the compare operation. Since class code bits may be loaded into flip-flops 402(0)-402(2) before a compare operation, the gate delay associated with generating the select signal during the compare operation is only 2 gate delays, one for XNOR gates 404 and one for AND gate 406, and therefore has a negligible effect upon device performance.

Figure 5 shows a block select circuit 500 that is another embodiment of the block select circuit 300. Here, a logic circuit 502 is coupled to the output terminal of the AND gate 406 to allow for direct control of the select signal SEL using control signals EN and SEL\_OV. The logic circuit 502 includes an OR gate 504 having a first terminal coupled to the output terminal of the AND gate 406, a second terminal to receive EN, and an output terminal coupled to a first input terminal of an AND gate 508. The AND gate 508 includes a second input terminal to receive SEL\_OV, and an output terminal to provide the select signal SEL. The signal EN enables the corresponding CAM block 102 to participate in the compare operation when the output of AND gate 406 is logic high. When asserted to logic high, EN enables the corresponding CAM block 102 for the compare operation and, conversely, when de-asserted to logic low, EN disables the corresponding CAM block 102 for the compare operation regardless if there is a match condition. The EN signal may be used to selectively disable CAM blocks 102, for instance, when defective. The signal EN is shown in Figure 5 as being provided by a fuse 506, although in other embodiments EN may be provided by other means such as a programmable memory element,

e.g., a register, flip-flop, EPROM, EEPROM, SRAM, etc. The signal SEL\_OV is a select override signal that, when asserted to logic high, may be used to force the select signal SEL to logic high to enable the corresponding CAM block 102 to participate in compare operations, irrespective of whether there is a class match. For an alternative embodiment, the relative 5 locations of OR gate 504 and AND gate 508 may be reversed such that when SEL\_OV is set to a logic high state, then SEL will be set to a logic high state irrespective of whether there is a class match or the logic state of EN.

Figure 6 shows a 1-bit comparand driver 600 that is used in one embodiment of the comparand drivers 208. Driver 600 includes AND gates 602, 604, and 606, and also includes 0 buffers 608 and 610. AND gate 602 includes input terminals to receive the clock signal CLK and the select signal SEL, and an output terminal coupled to first input terminals of AND gates 604 and 606. AND gate 604 includes a second input terminal coupled to the data line D, and an output terminal coupled to the buffer 608, which in turn drives the comparand line CL. AND gate 606 includes a second input terminal coupled to the complementary data line  $\bar{D}$ , and an output .5 terminal coupled to the buffer 610, which in turn drives the complementary comparand line  $\bar{CL}$ . Buffers 608 and 610 may be any suitable buffers to drive comparand data onto the comparand lines CL and  $\bar{CL}$ . A plurality of drivers 600 may share the AND gate 602.

During a compare operation, a comparand bit is provided to AND gate 604 via data line D, and a complementary comparand bit is provided to AND gate 606 via complementary data line 20  $\bar{D}$ . When CLK is logic high, the select signal SEL propagates through AND gate 602 to AND gates 604 and 606. If the select signal is asserted to logic high, AND gate 606 passes the comparand bit to the buffer 608, which in turn drives the comparand bit onto the comparand line CL. Similarly, AND gate 608 passes the complementary comparand bit to the buffer 610, which in turn drives the complementary comparand bit onto the complementary comparand line  $\bar{CL}$ . 25 Thus, when the select signal SEL is asserted, the comparand driver 600 drives the comparand lines CL and  $\bar{CL}$  with the comparand data received from the comparand register 210 via data lines D and  $\bar{D}$ .

Conversely, if the select signal SEL is de-asserted to logic low to indicate that the corresponding CAM block 102 is not to participate in the compare operation, AND gates 606 and 30 608 force their respective output terminals to logic low. In response thereto, buffers 608 and 610 force the comparand line CL and the complementary comparand line  $\bar{CL}$ , respectively, to logic low. In this manner, when the select signal SEL is de-asserted, the comparand driver 600 does not drive complementary comparand data onto the comparand lines CL and  $\bar{CL}$ , thereby

precluding the corresponding CAM block 102 from participating in the compare operation while minimizing power consumption in the CAM block.

The present invention is also particularly useful in increasing manufacturing yield of a CAM device by disabling defective CAM blocks in the device. Thus, for instance, during manufacture of a CAM device having  $n$  CAM blocks, if one or more of the CAM blocks are found to be defective or otherwise inoperable after manufacturing, rather than discarding the entire device, the defective blocks may be disabled using the block select circuits as described above, and the remaining non-defective CAM blocks may then be used for compare operations. For example, in one embodiment where the CAM device includes 8 CAM blocks each having 1k rows of CAM cells, if one of the CAM blocks is defective, that CAM block is disabled, and the remaining 7 CAM blocks may be used as a 7k CAM device. Accordingly, the ability to use the CAM device when one or more of its CAM blocks are defective advantageously increases manufacturing yield of the CAM device.

Figure 7 shows a CAM device 700 that is a modified embodiment of the device 100 of Figure 1 which allows for one or more defective CAM blocks to be disabled for CAM operations, and also includes circuitry which translates or re-assigns address locations in defective CAM blocks to address locations in non-defective CAM blocks. The device 700 includes address logic 701, a plurality of CAM blocks 702(1)-702(n), a plurality of block select circuits 706(1)-706(n) corresponding to CAM blocks 702(1)-702(n), respectively, a priority encoder 708, and full flag logic 710. Each of the block select circuits 706(1)-706(n) provides to the corresponding CAM block 702 a select signal which may be used as described above to disable the CAM block 702 if, for example, the CAM block 702 is defective.

The block select circuit 706 may be any suitable circuit to provide either a logic high (enabling) or a logic low (disabling) select signal SEL to the corresponding CAM block 702. In some embodiments, the block select circuit 706 includes a memory (not shown in Figure 7) for storing a binary value indicative of SEL. In some embodiments, the block select circuit 706 provides a logic high SEL signal if the corresponding CAM block 702 is not defective, and provides a logic low SEL signal if the corresponding CAM block 702 is defective. In one embodiment, the block select circuit 706 may include the block select circuit 500 (Figure 5), in which case the signal EN may be set to a low logic state by blowing fuse 506 to disable a defective CAM block 702 via signal SEL. In other embodiments, the block select circuit 706 may be a fuse (or a memory element) connected between the CAM block 702 and a voltage supply, in which case the fuse may be blown to provide a logic low SEL signal to disable the corresponding CAM block 702.

After fabricating the device 700, each of the CAM blocks 702(1)-702(n) is tested in a suitable manner. For each CAM block 702 that is found to be defective, the corresponding block select circuit 706 is configured to provide a logic low select signal SEL to the CAM block 702 to disable the CAM block. Conversely, for each CAM block 702 that is not defective, the 5 corresponding block select circuit 706 is configured to provide a logic high select signal to the CAM block to enable its participation in CAM operations.

Testing the CAM blocks of a CAM device and then selectively disabling the defective CAM blocks in an embodiment using a fuse to provide SEL is illustrated with reference to the flow chart of Figure 8. Here, a fuse (not shown for simplicity) in each block select circuit 706 is 10 coupled to a voltage supply and thus initially provides an asserted (e.g., logic high) SEL to enable the corresponding CAM block 702. Each CAM block 702 is tested in a suitable manner to determine whether it is defective (step 750). If the CAM block is defective, as tested at step 751, SEL is de-asserted (e.g., to logic low) to disable the defective CAM block by blowing the fuse. Otherwise, if the CAM block is not defective, the corresponding fuse is not blown, and the 15 corresponding CAM block remains enabled. If all CAM blocks have been tested, as determined at step 753, processing is finished (step 754). Otherwise, the next CAM block is tested and thereafter disabled if found to be defective (steps 750-752).

During a compare operation, each CAM block 702 receives comparand data from the comparand bus CBUS in a manner similar to that of CAM blocks 102 of device 100 of Figure 1. 20 Other signals provided to device 700 during the compare operation may be a clock signal CLK, one or more instructions from an instruction decoder (not shown for simplicity), and other control signals. Each CAM block 702 provides a plurality of match line signals to the priority encoder 708 via corresponding match lines ML. The match lines carry match signals indicative of match conditions in the CAM arrays 704. For simplicity, the plurality of match lines ML from each 25 CAM block 702 are represented collectively in Figure 7. The priority encoder 708 generates an index corresponding to one of the matching CAM words in the device 700, which as described above may be index of the highest-priority matching CAM row.

Each CAM block 702 provides a full flag signal FF indicative of whether the CAM block is full, i.e., whether there are any available row in the CAM block 702 to store data, to full flag 30 logic 710. The full flag signal FF may be generated for each CAM block 702 in a well-known manner using one or more valid bits in each row of the CAM block. The full flag signals FF\_1 to FF\_n provided by CAM blocks 702(1)-702(n), respectively, are combined in a well-known manner in full flag logic 710 to generate a device full flag, FF\_device, indicative of whether there are any available rows in the device 700. When a CAM block 702 is found to be defective or

otherwise inoperable for its intended purpose, the CAM block 702 is configured to maintain an asserted full flag signal FF to indicate that the defective CAM block 702 does not include any available memory locations. In one embodiment, the full flag signal FF for the defective CAM block may be maintained in the asserted state by forcing the valid bits in its array 704 to an asserted state. In other embodiments, a fuse may be provided within or associated with each CAM block 702 that, when blown, forces the corresponding full signal FF to be asserted.

Address logic 701 is shown in Figure 7 as coupled to an address bus ABUS and each of the CAM blocks 702(1)-702(n). During read and write operations, an address provided to the device 700 may be received into address logic 701 via address bus ABUS, and thereafter used to select a row in one of the CAM blocks 702(1)-702(n) for the read or write operation. In accordance with the present invention, if a CAM block 702 to which the address refers is defective, and is thus disabled for the operation using the corresponding block select circuit 706 as described above, address logic 701 translates the address from the defective or disabled CAM block to a non-defective CAM block. Conversely, if the CAM block 702 to which the address refers is non-defective, and is thus enabled for operation, address logic 701 forwards the address to the appropriate CAM block 702. As explained more fully below, address logic 701 ensures a contiguous addressing scheme in the CAM blocks 702 when one or more CAM blocks 702 are defective and disabled, even when the non-defective CAM block(s) 702 are not adjacent to each other.

For alternate embodiments, address logic 701 may be omitted. For one example, contiguous non-defective blocks starting from block 702(1) may still be used. For other embodiments, any non-defective block may be used.

Figure 9 shows a CAM device 800 that is one embodiment of the CAM device 700. CAM device 800 is shown to include address translation logic 801, four CAM blocks 802(0)-802(3), and a main priority encoder 806. Each CAM block 802 includes a CAM array 704 (e.g., a 1k CAM array), a block priority encoder 804, and match flag logic 805. Of course, in other embodiments, there may be any number of CAM blocks 802, and each CAM block array 704 may include any number of rows of CAM cells. The address A may include any suitable number of bits. In the embodiment of Figure 9, the function of the priority encoder 708 of Figure 7 is distributed between the individual block priority encoders 804 within the CAM blocks 802(0)-802(3) and the main priority encoder 806. During a read or write operation, a 14-bit address A[13:0] may be provided to the device 800 via the address bus ABUS. The first two address bits A[13:12] are the block address bits and are provided to address translation logic 801, which in turn selects one of the CAM blocks 802(0)-802(3) for the read or write operation via block select

signals BS\_0 to BS\_3, respectively. The remaining twelve address bits, A[11:0], select a row in the CAM array 704 selected by address translation logic 801 for the operation, and may be provided to each CAM block 802. During read or write operations, data may be read from or written to the row identified by row address bits A[11:0] in the CAM block 802 selected by address translation logic 801.

Information indicative of which CAM blocks 802 are found to be defective during testing may be used to configure address translation logic 801 to re-address the non-defective CAM blocks 802 so as to occupy, for instance, the contiguous highest-priority address space (e.g., the lowest numbered addresses). During a read or write operation, address translation logic 801 receives block address bits A[13:12]. If a CAM block 802 selected by block address bits A[13:12] is non-defective or otherwise enabled, address translation logic 801 asserts the corresponding block select signal BS to enable the selected CAM block 802 for the operation. For example, if an address [13:0] selects the first row in the first CAM block 802(0) for reading, and CAM block 802(0) is non-defective, address translation logic 801 asserts BS\_0 to logic high while maintaining BS\_1, BS\_2, and BS\_3 in a logic low, de-asserted state. The asserted BS\_0 signal causes row address bits A[11:0] to be latched into the first CAM block 802(0), thereby facilitating a read from the first CAM block 802(0).

Conversely, if a CAM block 802 selected by block address bits A[13:12] is defective or otherwise disabled, address translation logic 801 selects another CAM block for the operation by asserting its corresponding block select signal BS. For example, if the address [13:0] selects the first row in the first CAM block 802(0) for reading, and CAM block 802(0) is defective and the second CAM block 802(1) is non-defective, address translation logic 801 may assert BS\_1 to logic high while maintaining BS\_0, BS\_2, and BS\_3 in a logic low, de-asserted state. The asserted BS\_1 signal causes row address bits A[11:0] to be latched into the second CAM block 802(1), thereby facilitating a read from the second CAM block 802(1). In this manner, address translation logic 801 may re-address read or write operations from defective CAM blocks to non-defective CAM blocks.

In some embodiments, the block select signal BS provided to the CAM block 802 may be used as an address gating signal to facilitate address translation in accordance with present embodiments. For example, Figure 10 shows a CAM array 900 that is one embodiment of the array 704 of Figure 7. The array 900 includes a plurality of CAM cells 202 organized in any number of rows and columns, and operates in a manner similar to the CAM array 200 described above with respect to Figure 2. That is, during compare operations, comparand data provided by the comparand register 210 is selectively driven onto the complementary comparand lines CL and

CL in response to the select signal SEL provided by the block select circuit 706. If the array 900 is non-defective, the select signal SEL is asserted to logic high to allow the comparand word to be driven into the array 900 for comparison with CAM words stored therein. Conversely, if the array 900 is found to be defective during testing, the block select circuit 706 is configured to provide a 5 de-asserted select signal SEL to the comparand drivers 208 to prevent comparand data from being driven onto the comparand lines CL and  $\overline{CL}$ , thereby disabling the array 900.

Address bits A[11:0] are provided from address bus ABUS to the address decoder 204. Address gating logic 902 is connected between the address decoder 204 and corresponding word lines WL of the array 900 via gated lines GL, and selectively drives a word line WL identified by 10 A[11:0] in response to the block select signal BS. For example, during a read or write operation, address decoder 204 decodes A[11:0] to select a row of CAM cells 202 for the operation, and drives a corresponding gated line GL to logic high. If BS is asserted to logic high, address gating logic 902 drives the corresponding word line WL to select the row of CAM cells 202 for the 15 operation. Conversely, if BS is de-asserted to logic low, address logic 902 does not drive any of the word lines WL to logic high, regardless of A[11:0], thereby preventing CAM cells 202 in the array from being addressed for the operation. In one embodiment, address gating logic 902 may include for each word line WL in the array 900 an AND gate (not shown) having an output terminal coupled to the word line, a first input terminal coupled to the corresponding gated line GL, and a second input terminal to receive the block select signal BS. In this manner, the AND 20 gates may be used to selectively gate the addressing of CAM cells in the block in response to BS. Of course, in other embodiments other suitable logic may be used.

Figure 11 shows address translation logic 1000 that is one embodiment of the address translation logic 801 of Figure 9. Logic 1000 includes decode logic 1002, four 4-input multiplexers 1004(0)-1004(3), and four corresponding memory elements 1006(0)-1006(3), 25 respectively. Decode logic 1002 has an input terminal to receive block address bits A[13:12], and has four output terminals coupled to corresponding input terminals of the multiplexers 1004(0)-1004(3) via lines 1008(0)-1008(3), respectively. Decode logic 1002 decodes block address bits A[13:12], and in response thereto, asserts one of output lines 1008(0)-1008(3) to logic high. For example, if address bits A[13:12] are “00”, which is equivalent to the decimal value “0”, decode 30 logic asserts line 1008(0); if address bits A[13:12] are “01”, which is equivalent to the decimal value “1”, decode logic 1002 asserts line 1008(1); if address bits A[13:12] are “10”, which is equivalent to the decimal value “2”, decode logic 1002 asserts line 1008(2); and if address bits

A[13:12] are “11”, which is equivalent to the decimal value “3”, decode logic 1002 asserts line 1008(3).

The multiplexers 1004(0)-1004(3) each include an output terminal coupled to a corresponding one of the CAM blocks 802(0)-802(3), respectively, and a control terminal coupled 5 to a corresponding one of the memory elements 1006(0)-1006(3), respectively. Each memory element 1006 stores address translation information that when provided to the corresponding multiplexer 1004 selects one of the signals provided by decode logic 1002 to be output as the block select signal BS. In this manner, multiplexers 1004(0)-1004(3) may dynamically assign block address values to CAM blocks 802(0)-802(3), respectively.

10 In accordance with present embodiments, a read or write operation to a defective CAM block may be re-addressed to a non-defective CAM block by manipulating the address translation information stored in the memory elements 1006(0)-1006(3). In some embodiments, where all CAM blocks 802(0)-802(3) are non-defective, the memory elements 1006(0)-1006(3) store default block address values so as to not alter CAM addressing during the read or write operation. 15 That is, the default block address values cause respective multiplexers 1004(0)-1004(3) to select corresponding signals on lines 1008(0)-1008(3) as block select signals BS\_0 to BS\_3, respectively. For example, memory element 1006(0) may store a default block address value of “0” to cause multiplexer 1004(0) to select the signal on line 1008(0) as BS\_0, memory element 1006(1) may store a default block address value of “1” to cause multiplexer 1004(1) to select the 20 signal on line 1008(1) as BS\_1, memory element 1006(2) may store a default block address value of “2” to cause multiplexer 1004(2) to select the signal on line 1008(2) as BS\_2, and memory element 1006(3) may store a default block address value of “3” to cause multiplexer 1004(3) to select the signal on line 1008(3) as BS\_3. In this manner, address translation logic 1000 selects for the read or write operation the CAM block identified by address bits A[13:12]. Table 1 25 summarizes the four default block address/multiplexer select values (MUX) and corresponding address space when all CAM blocks are non-defective.

| Block      | Status        | MUX | address space |

|------------|---------------|-----|---------------|

| CAM 802(0) | non-defective | 0   | 0 to k-1      |

| CAM 802(1) | non-defective | 1   | k to 2k-1     |

| CAM 802(2) | non-defective | 2   | 2k to 3k-1    |

| CAM 802(3) | non-defective | 3   | 3k to 4k-1    |

Table 1

The CAM device 800 is then tested to determine if any CAM blocks are defective. Where it is determined that one or more CAM blocks are defective, the select values stored in memory elements 1006(0)-1006(3) may be modified to re-address the non-defective CAM blocks. For 5 example, if after testing it is determined that CAM block 802(0) is defective, and is thereafter disabled using the corresponding block select circuit 706 as described above (see also Figure 7), the 1k CAM rows in the defective CAM block 802(0) are no longer available, and therefore the device 800 now has only 3k available CAM rows available, i.e., 1k rows in each of the 3 non-defective CAM blocks 802(1)-802(3). Since the first CAM block 802(0) is not available, it is 10 desirable for the second CAM block 802(1) to be the highest-priority CAM block (e.g., having address space 0 to k-1), for the third CAM block 802(2) to be the second highest-priority CAM block (e.g., having address space k to 2k-1), and for the fourth CAM block 802(3) to be the third highest-priority CAM block (e.g., having address space 2k to 3k-1).

The block address values stored in corresponding memory elements 1006(0)-1006(3) may 15 be modified to implement a new addressing scheme for the non-defective CAM blocks 802(1)-802(3). For example, in one embodiment, the block address value stored in the memory element 1006(1) is set to “0” so that multiplexer 1004(1) selects the signal on line 1008(0) as BS\_1 to be provided to CAM block 802(1). When A[13:12] equals “00”, decode logic 1002 asserts line 1008(0) to logic high, which in turn now passes through multiplexer 1006(1) to select the second 20 CAM block 802(1) for the operation. In this manner, address translation logic 1000 translates address space 0 to k-1 from CAM block 802(0) to CAM block 802(1).

Similarly, the block address value stored in the memory element 1006(2) is set to “1” so 25 that multiplexer 1004(2) selects the signal on line 1008(1) as BS\_2 to provide to CAM block 802(2). When A[13:12] equals “01”, decode logic 1002 asserts line 1008(1) to logic high, which in turn now passes through multiplexer 1004(2) to select the third CAM block 802(2) for the operation, thereby translating address space k to 2k-1 from CAM block 802(1) to CAM block 802(2). Similarly, the block address value stored in the memory element 1006(3) is set to “2” so 30 that multiplexer 1004(3) selects the signal on line 1008(2) as BS\_3 to provide to CAM block 802(3). When A[13:12] equals “10”, decode logic 1002 asserts line 1008(2) to logic high, which in turn now passes through multiplexer 1004(3) to select the fourth CAM block 802(3) for the operation, thereby translating address space 2k to 3k-1 from CAM block 802(2) to CAM block 802(3). Table 2 summarizes the select values when CAM block 802(0) is defective and CAM blocks 802(1)-802(3) are non-defective.

| Block      | Status        | MUX | address space |

|------------|---------------|-----|---------------|

| CAM 802(0) | defective     | 3   | 3k to 4k-1*   |

| CAM 802(1) | non-defective | 0   | 0 to k-1      |

| CAM 802(2) | non-defective | 1   | k to 2k-1     |

| CAM 802(3) | non-defective | 2   | 2k to 3k-1    |

\* not used

Table 2

By translating address space in CAM blocks 802(1)-802(3), respectively, present

5 embodiments may re-address rows in non-defective CAM blocks 802(1)-802(3) with the highest-

priority CAM addresses, e.g., row addresses 0 to 3k-1. In this manner, the three non-defective

CAM blocks 802(1)-802(3) of device 800 may be sold and operated as a 3k CAM array. This is

in contrast to prior art CAM devices, which are typically discarded if any of the CAM blocks

therein are found to be defective. The ability to re-address the defective CAM block 802(0) and

10 use the non-defective CAM blocks 802(1)-802(3) of device 800 as a 3k CAM array, rather than

discarding the device 800, may significantly increase manufacturing yield.

In the example above, address space in the defective CAM block 802(0) is translated from

row assignments 0 to k-1 to row assignments 3k to 4k-1 by changing the select value stored in the

memory element 1006(0) from "0" to "3". This ensures that the defective CAM block 802(0) will

15 not be addressed during read or write operations. That is, since the 3 non-defective CAM blocks

are used as a 3k CAM array having address space 0 to 3k-1, address space higher than 3k-1 is not

used, and therefore the defective CAM block 802(0) will not be addressed. For an alternate

embodiment, the block select signal BS\_0 can be set to a low logic state to disable block 802(0).

For one example, the output of each MUX can be coupled to a logic circuit (e.g., one or more

20 AND, OR, XOR, NOT circuits) and memory 1006 configured to disable BS and its corresponding

block when a particular value is programmed into memory 1006 (or the value is changed in

memory 1006).

In other embodiments, the block address values stored in memory elements 1006(0)-

1006(3) may be modified to translate address space in any number n of non-defective CAM

25 blocks into a contiguous address space of 0 to (k)n-1, irrespective of whether the non-defective

CAM blocks are adjacent to one another. Thus, for example, if in one embodiment the CAM

blocks 802(0) and 802(2) are defective and CAM blocks 802(1) and 802(3) are non-defective, the

non-defective CAM blocks 802(1) and 802(3) may be configured for operation as a 2k CAM

array by setting the block address values for memory elements 1006(1) and 1006(3) to "0" and

“1”, respectively. In this manner, the first 1k address space corresponding A[13:12] equal to “00” selects CAM block 802(1), and the second 1k address space corresponding to A[13:12] equal to “01” selects CAM block 802(3). The block address values stored in memory elements 1006(0) and 1006(2) each may be either “2” or “3” to preclude their selection during operation, since 5 addresses above 2k-1, i.e., the third or fourth 1k address spaces corresponding to A[13:12] equal to “10” or “11”, respectively, are not used. Table 3 summarizes the block address values and corresponding address space when CAM blocks 802(0) and 802(2) are defective and CAM blocks 802(1) and 802(3) are non-defective.

| Block      | Status        | MUX    | Address Space |

|------------|---------------|--------|---------------|

| CAM 802(0) | defective     | 2 or 3 | > 2k*         |

| CAM 802(1) | non-defective | 0      | 0 to k-1      |

| CAM 802(2) | defective     | 2 or 3 | > 2k*         |

| CAM 802(3) | non-defective | 1      | k to 2k-1     |

10 \* not used

Table 3

Each memory element 1006 may be any suitable structure to provide a block address value to the corresponding multiplexer 1004 to select one of lines 1008(0)-1008(3) to pass as the block 15 select signal BS. In some embodiments, the memory element may be a flip-flop, register, look-up table, or non-volatile memory such EPROM or Flash memory. In other embodiments, the memory element 1006 may include one or more fuses to provide the block address value to the corresponding multiplexer 1004.

For one example, in one embodiment of the CAM device 800, each memory element 1006 20 includes two fuses coupled to a voltage supply to initially provide the binary value “11” to corresponding multiplexers 1004. In this example, since each multiplexer 1004 initially selects the signal line connected to its “3” input in response to the binary block address value “11”, the “3” input of each multiplexer 1004 is connected to a corresponding numbered signal line 1008 from decode logic 1002. That is, input 3 of multiplexer 1004(0) is connected to the line 1008(0), 25 input number 3 of multiplexer 1004(1) is connected to the line 1008(1), input number 3 of multiplexer 1004(2) is connected to the line 1008(2), and input number 3 of multiplexer 1004(3) is connected to the line 1008(3). The remaining multiplexer inputs 0, 1, and 2 may be connected to lines 1008 in any suitable configuration. In this manner, multiplexer 1004(0) asserts BS\_0 when A[13:12] equals “00”, multiplexer 1004(1) asserts BS\_1 when A[13:12] equals “01”,

multiplexer 1004(2) asserts BS\_2 when A[13:12] equals “10”, and multiplexer 1004(3) asserts BS\_3 when A[13:12] equals “11”. Then, if after testing one or more of the CAM blocks 802 are found to be defective, the fuses of each memory element 1008 may be selectively blown to translate address space from defective CAM blocks to non-defective CAM blocks 802 to facilitate 5 contiguous addressing in the manner described above. Additionally, the two logic ones may be ANDed together and provided as one input to an AND gate, and the other input to the AND gate coupled to a respective BS signal output by each MUX. When a defective row is programmed to a value other than “11”, then the respective BS signal and corresponding block will be disabled.

In order to maintain address consistency between read or write operations and compare 0 operations when address space in a defective CAM block is translated to a non-defective CAM block, address translation information used during the read or write operation is also used to calculate the address or index of a matching CAM row during compare operations. Thus, for example, if address space 0 to k-1 is translated from CAM block 802(0) to 802(1), and there is a match in CAM block 802(1) during a subsequent compare operation, the priority encoder 806 5 ensures that the matching index from CAM block 802(1) lies within address space 0 to k-1, rather than within address space k to 2k-1. In this manner, address translations facilitated during a read or write operation are reflected during subsequent compare operations.

Referring again to Figure 9, during compare operations, a comparand word provided on CBUS is compared to data stored in all enabled (e.g., non-defective) CAM blocks 802. For each 20 enabled CAM block 802, if there is a match condition in response to the compare operation, match flag logic 805 asserts a match flag (MF\_0 to MF\_3) to a logic high state, and the priority encoder 804 within the CAM block 802 outputs the 12-bit row index I (or address) of the highest priority matching CAM row in the block. If there is not a match, the match flags are not asserted (i.e., match flag logic 805 sets MF to low logic state). For one embodiment, each match flag logic 25 includes a programmable element (e.g., a fuse or other memory element) that is programmed when the CAM block is disabled. The match flags MF\_0 to MF\_3 and row indexes I0-I3 from CAM blocks 802(0)-802(3), respectively, are provided to the main priority encoder 806. The main priority encoder 806 adds a unique block index to each row index I provided by CAM blocks 802(0)-802(3) to form a corresponding device index. The main priority encoder 806 uses 30 the match flag signals MF\_0 to MF\_3 to select the highest-priority device index from CAM blocks 802(0)-802(3) to output as the system index, I\_sys.

The main priority encoder 806 is programmable and stores the block indexes for CAM blocks 802(0)-802(3) in memory (not shown in Figure 9). The block indexes are dynamic values that may be modified or programmed to reflect and thus maintain consistency with address

translations as described above in a read or write operation. Initially, the main priority encoder stores a block index of “00” for CAM block 802(0), a block index of “01” for CAM block 802(1), a block index of “10” for CAM block 802(2), and a block index of “11” for CAM block 802(3). These initial block indexes, which are used when all CAM blocks 802(0)-802(3) are enabled, 5 mirror the block address values stored in memory elements 1006(0)-1006(3) of address translation logic 1000 of Figure 11. If one or more CAM blocks 802 are found to be defective or are otherwise disabled, the block indexes stored in main priority encoder 806 are modified to reflect address translations during the read or write operation. For example, if CAM blocks 802(0) and 802(2) are disabled and address spaces in non-defective CAM blocks 802(1) and 802(3) are 10 translated to address space 0 to k-1 and address space k to 2k-1, respectively, main priority encoder 806 adds a block index of “00” to row index I1 to generate the device index for CAM block 802(1) and adds a block index “01” to row index I3 to generate the device index for CAM block 802(3). In this manner, address consistency between read/write operations and compare operations is maintained.

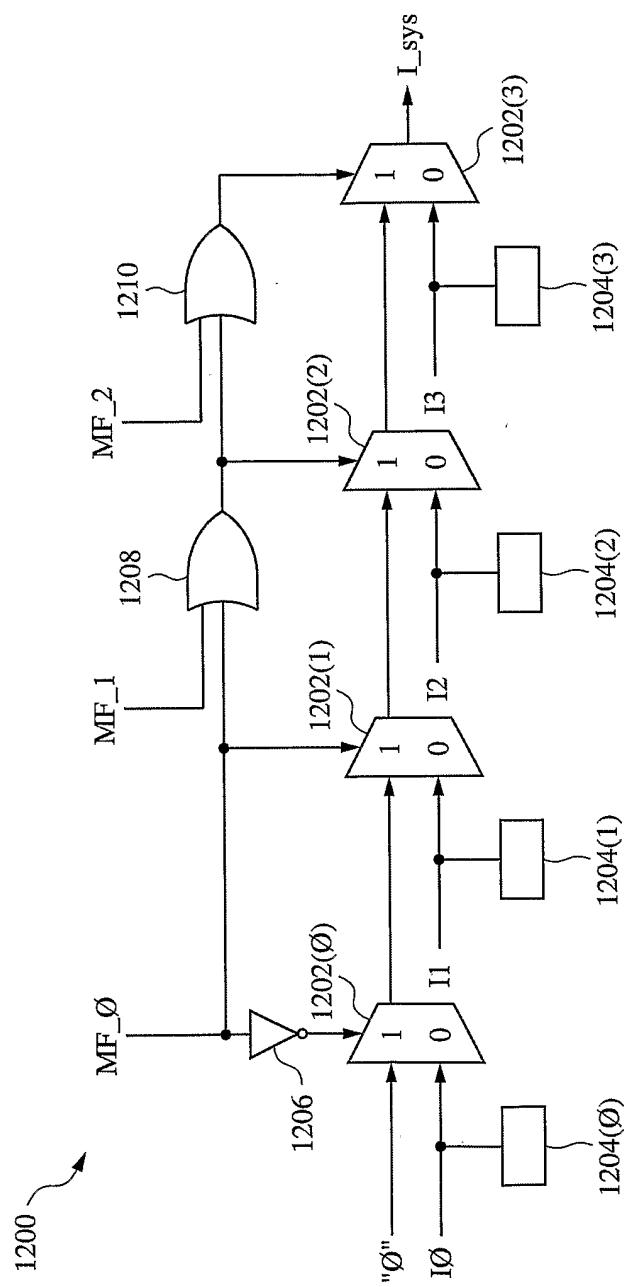

15 Figure 12 shows a priority encoder 1200 that is one embodiment of the main priority encoder 806 of Figure 9. The priority encoder 1200 includes a chain of four multiplexers 1202(0)-1202(3), four corresponding memory elements 1204(0)-1204(3), and select logic including an inverter 1206 and OR gates 1208 and 1210. Each memory element 1204 stores a 2-bit block index for a corresponding CAM block 802. The memory elements 1204 may be the 20 same as memory elements 1006 of Figure 11, or they may be separate memory elements. Each multiplexer 1202 includes a first input (i.e., the “1” input) coupled to the output of a preceding multiplexer 1202 in the chain, a second input (i.e., the “0” input) to receive a concatenation of a 12-bit index I of the highest priority match (if any) from a corresponding CAM block 802 and a 2-bit block index from the corresponding memory element 1204, an output coupled to input “1” of a 25 next multiplexer 1202, and a select terminal to receive match information from the CAM blocks 802.

The concatenation of a 12-bit row index I and the 2-bit block index forms a 14-bit device index of the highest-priority match, if any, from a corresponding CAM block 802. The 1 input of the first multiplexer 1202(0) receive a default binary “0” value. MF\_0 is inverted by inverter 30 1206 and provided as the select signal to multiplexer 1202(0), and provided directly as the select signal to multiplexer 1202(1). MF\_0 and MF\_1 are combined in OR gate 1208 and provided as the select signal for multiplexer 1202(2). MF\_2 and the result from OR gate 1208 (i.e., MF\_0 + MF\_1, where + is the logic OR function) are combined in OR gate 1210 and provided as the select signal for multiplexer 1202(3). As explained below, the match flags MF control whether

each multiplexer 1202 passes a concatenated device index from a previous CAM block or the concatenated device index of the corresponding CAM block.

In this example, CAM block 802(0) is the highest-priority block, CAM block 802(1) is the next highest-priority block, and so on. For each multiplexer stage, if there is a match in the 5 corresponding CAM block 802, the row index I and block index are forwarded to the next stage if there is not a match condition in a previous or higher-priority CAM block 802. If there is a match condition in a higher-priority CAM block 802, the row index I plus block index from the higher-priority CAM block are forwarded to the next stage.

For example, if there is a match condition in the first CAM block 802(0), priority encoder 0 804 of CAM block 802(0) provides the 12-bit row index I0 of its highest-priority match to input 0 of multiplexer 1202(0), where it is concatenated with the block index from memory element 1204(0) to generate the device index for CAM block 802(0). The match flag MF\_0 is asserted to logic high to indicate the match condition. In response thereto, inverter 106 provides a logic low or “0” select signal to multiplexer 1202(0), which in turn forwards the device index from CAM .5 block 802(0) to the next multiplexer 1204(1). The logic high MF\_0 signal causes multiplexer 1204(1) to select input 1, and thus forwards the device index from CAM block 802(0) to the next multiplexer 1202(2). MF\_0 ripples through OR gates 1208 and 1210 and causes multiplexers 1202(2) and 1202(3) to output the device index from CAM block 802(0) as I\_sys.

Maintaining equivalent values in corresponding memory elements 1006(0)-1006(3) and 20 1204(0)-1204(3) ensures addressing consistency between read or write operations and compare operations. For instance, in one embodiment where all CAM blocks 802(0)-802(3) are non-defective or otherwise enabled, memory elements 1204(0)-1204(3) store values of “00”, “01”, “10” and “11”, respectively. In this manner, “00” is added to row index I0 so that the first 1k addresses are mapped to the first block 802(0), “01” is added to row index I1 so that the second 25 1k addresses are mapped to the second block 802(1), “10” is added to row index I2 so that the third 1k addresses are mapped to the third block 802(2), and “11” is added to row index I3 from block 802(3) so that the fourth 1k addresses are mapped to the fourth block 802(3).

The block indexes stored in memory elements 1204(0)-1204(3) may be changed when address space in one or more CAM blocks 802 is translated to maintain addressing consistency. 30 For example, in one embodiment where CAM block 802(0) is defective, CAM blocks 802(1)-802(3) may be configured to operate as a 3k CAM array as described above with respect to address translation logic 1000 (Figure 11) by setting block address values or their binary equivalents of “0”, “1” and “2” into memory elements 1006(1), 1006(2), and 1006(3), respectively. This configures CAM block 802(1) to have the highest-priority address space, i.e.,

addresses 0 to  $k-1$ , CAM block 802(2) to have the next highest-priority address space, i.e.,  $k$  to  $2k-1$ , and CAM block 802(3) to have the lowest-priority address space, i.e., addresses  $2k$  to  $2k-1$ .

In accordance with present embodiments, the block indexes stored in memory elements 1204(0)-1204(3) are modified to reflect address translations facilitated in address translation logic 5 1000. Since CAM block 802(0) is disabled (and thus does not require address space), the block indexes of the remaining enabled CAM blocks 802(1)-802(3) may be modified to re-assign block priority in the CAM device 800. For example, the block index stored in memory element 1204(1) 0 may be set to "00" so that when concatenated with row index I1 from the highest-priority CAM block 802(1), the resultant device index corresponds to the highest-priority address space, i.e., addresses 0 to  $k-1$ . Similarly, the block indexes stored in memory elements 1204(2) and 1204(3) 5 may be modified to "01" and "10", respectively, to reflect address spaces  $k$  to  $2k-1$  and  $2k$  to  $3k-1$ , respectively. Since in this embodiment addresses larger than  $3k$  are not used, the block index stored in memory element 1204(0), which corresponds to the defective CAM block 802(0), may be set to "11" so that disabled CAM block 802(0) is not addressed. Note that the match flag 5.5 signal for a disabled CAM block will be set to a low logic state.

#### ***CAM Device having Intra-Row Configurability***

A CAM system having intra-row configurability is disclosed in reference to Figures 13-58.

The intra-row configurability enables a single CAM array to be configured to operate in one of many different width and depth configurations. For example, a CAM array having  $Y$  rows of 20 CAM cells each having  $Z$  row segments of  $W$  CAM cells can be configured into  $n$  different  $ZY/n$  depth by  $nW$  width configurations, where  $n$  is an integer from 1 to  $Z$ . For example, the CAM array can be configured as  $ZY$  rows of  $W$  cells when  $n=1$ , as  $ZY/2$  rows of  $2W$  cells when  $n=2$ , and so on up to  $Y$  rows of  $ZW$  cells when  $n=Z$ . A user can select or program one of the configurations by loading specific configuration information into the CAM system. This single 25 CAM system can be configured to store and maintain many different desired table configurations. The CAM system may also be used to store and maintain multiple tables of different sizes. For example, a first section of the CAM array may be configured such that each row in the section has a first number of row segments, while a second section of the CAM array may be configured such that each row in that section has a different number of row segments.

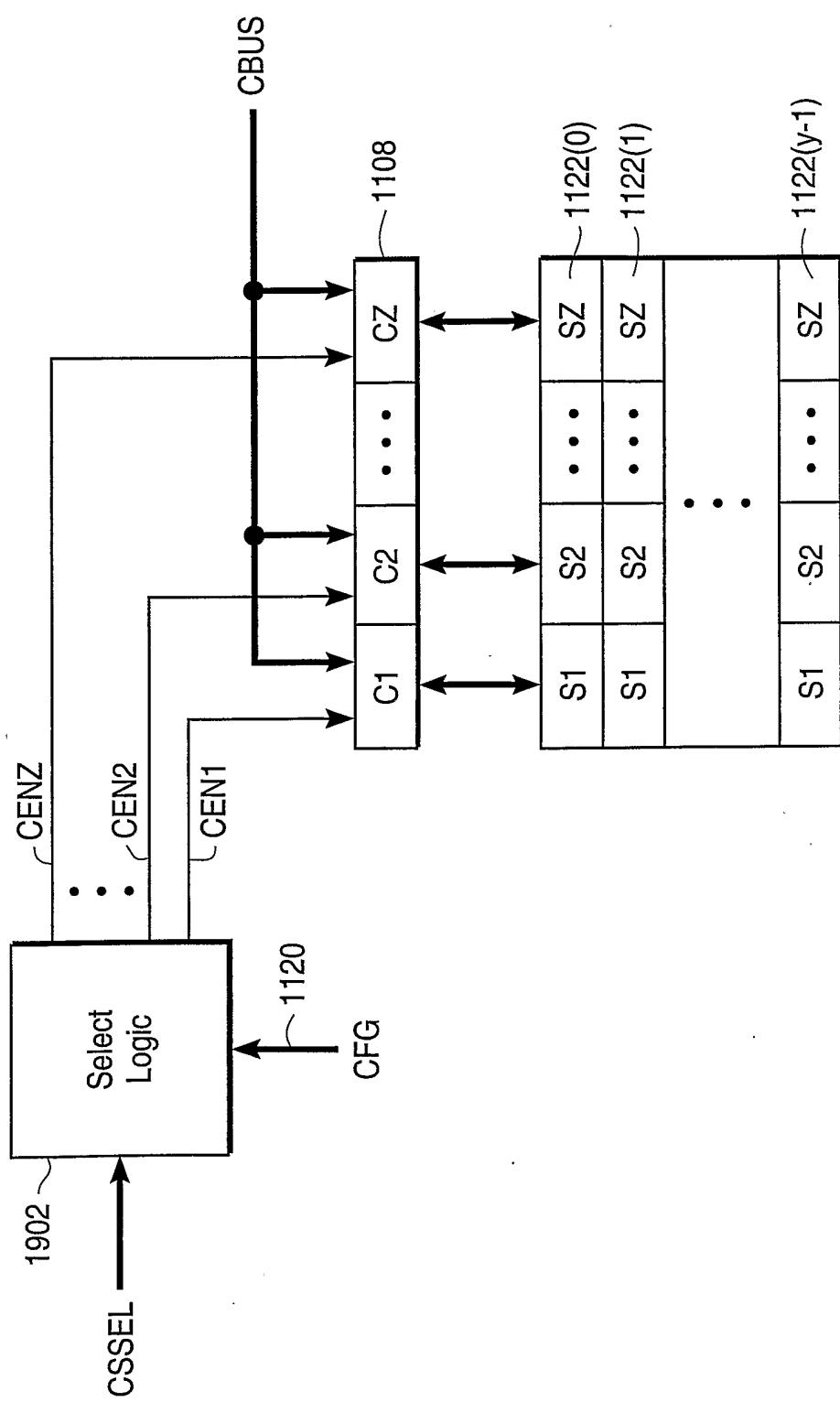

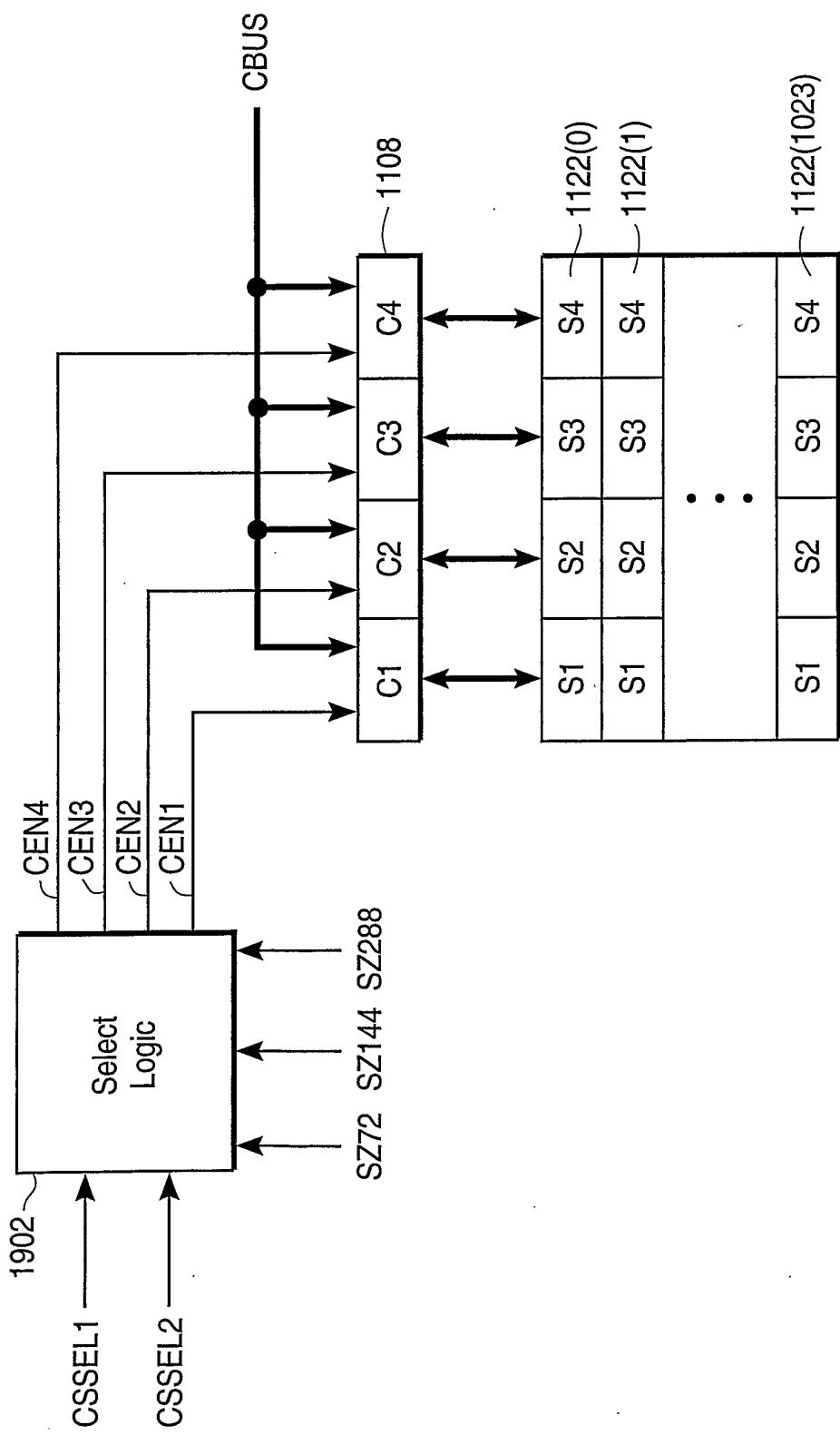

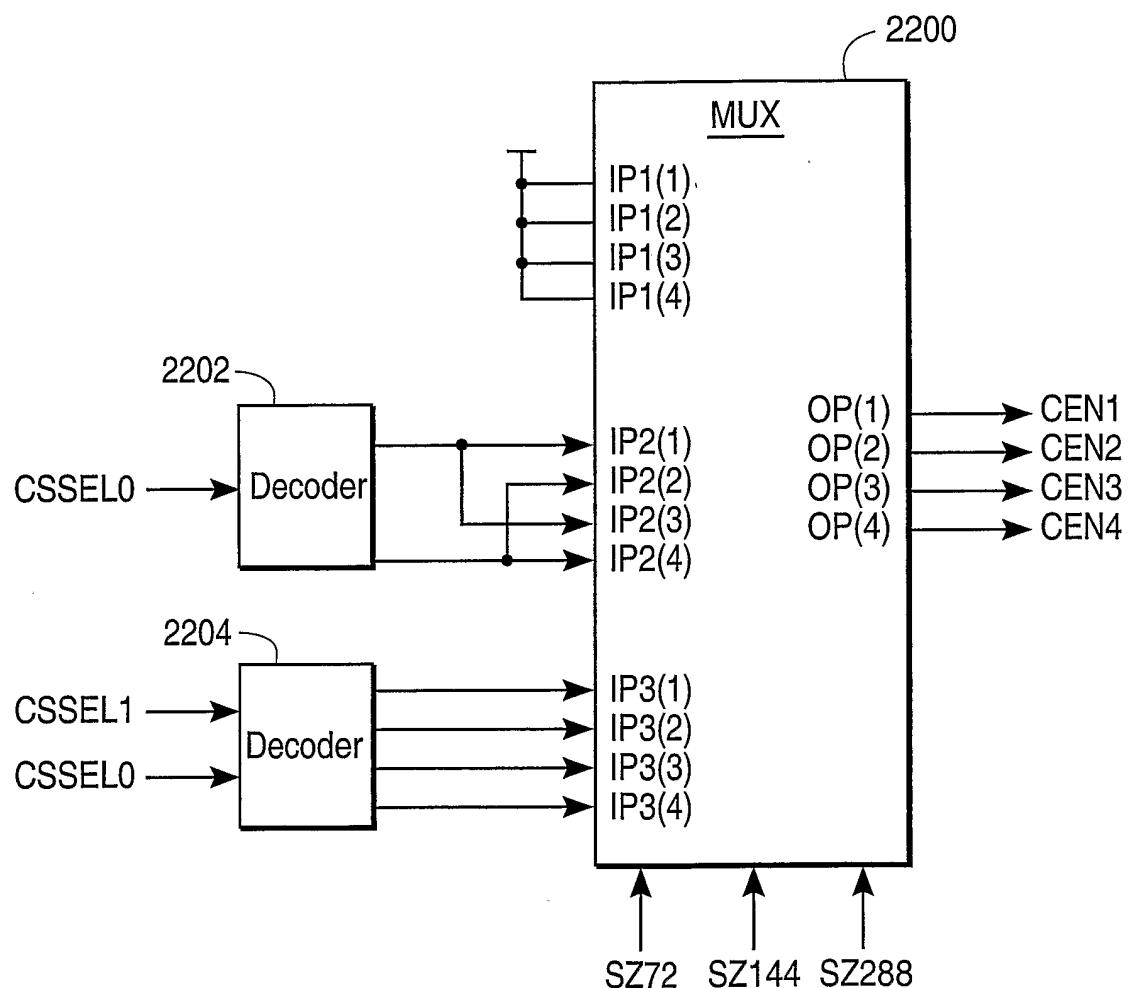

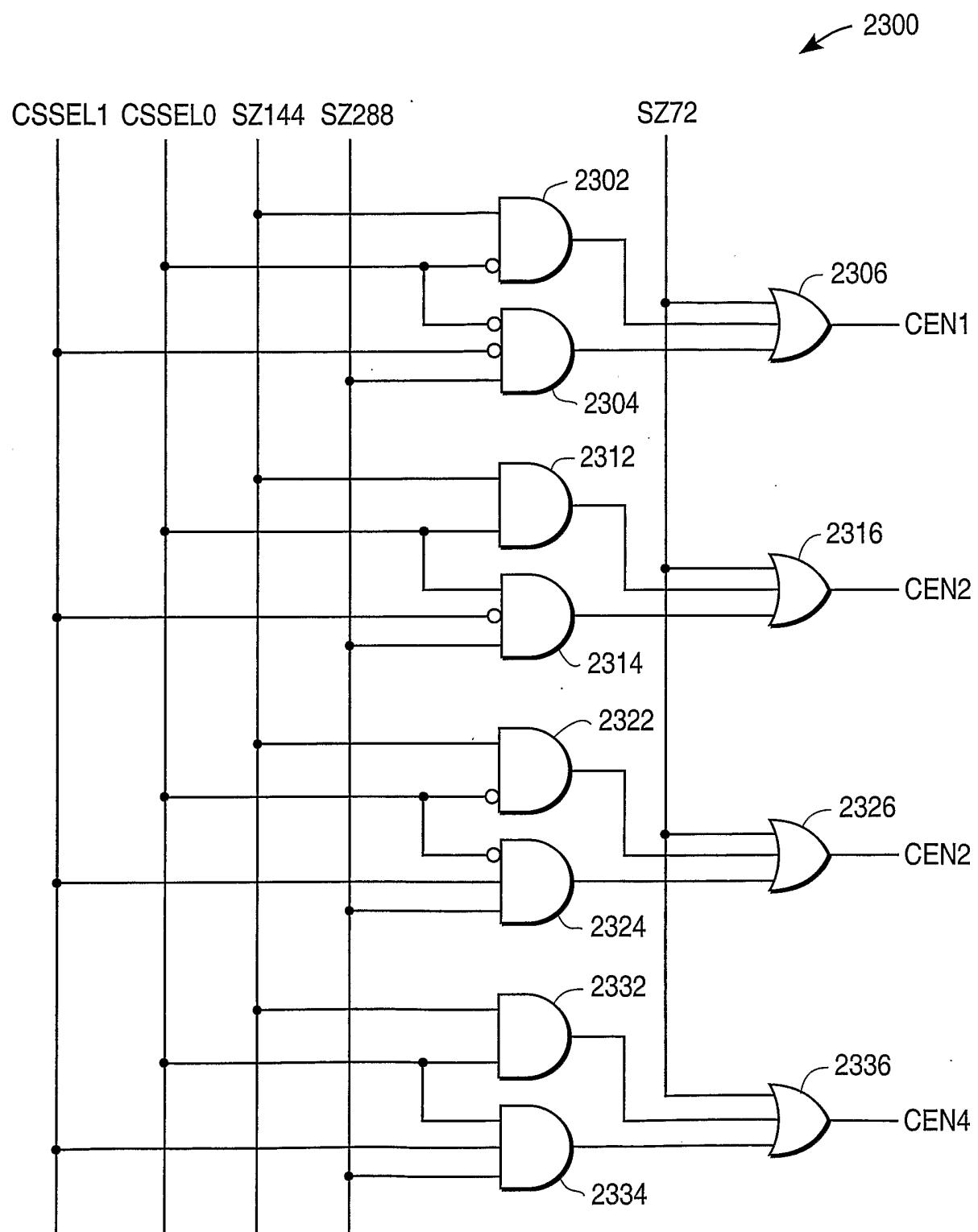

30 Figure 13 is one embodiment of a CAM system 1100 according to the present invention. CAM system 1100 includes a CAM array 1102 that includes  $Y$  rows 1122(0)-1122( $Y-1$ ) of CAM cells each segmented into  $Z$  row segments S1-SZ of  $W$  CAM cells each, where  $W$ ,  $Y$ , and  $Z$  are any integer numbers. The  $W$  CAM cells that may be any type of CAM cells including binary and