(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2008년05월29일

(11) 등록번호 10-0833760

(24) 등록일자 2008년05월23일

(51) Int. Cl.

G09G 3/30 (2006.01) G09G 3/32 (2006.01)

G09G 3/20 (2006.01) H05B 33/12 (2006.01)

(21) 출원번호 10-2007-0004860

(22) 출원일자 2007년01월16일

심사청구일자 2007년01월16일

(56) 선행기술조사문현

KR1020060064129 A

(73) 특허권자

삼성에스디아이 주식회사

경기 수원시 영통구 신동 575

(72) 발명자

김양완

경기 용인시 기흥구 공세동 428-5

(74) 대리인

서경민, 서만규

전체 청구항 수 : 총 25 항

심사관 : 김남인

(54) 유기 전계 발광 표시 장치

### (57) 요 약

본 발명은 유기 전계 발광 표시 장치에 관한 것으로서, 해결하고자 하는 기술적 과제는 다음과 같다.

첫째로, 기존의 화소 회로에 비하여 적은 숫자인 3개의 트랜지스터를 사용함으로써 고집적화를 꾀할 수 있으며, 이에 따라 고해상도를 가능하게 함에 있다.

둘째로, 제1용량성소자 및 제2용량성소자의 비율(C1 : C2)을 적절히 조절함으로써 구동 트랜지스터의 문턱전압(Vth)을 보상하여 회도의 균일성을 향상시킬 수 있으며, 상기 제1용량성소자 및 제2용량성소자의 비율 조절에 따라 제1전원전압선 (VDD)에 의한 전압강하(IR-DROP) 현상을 개선함에 있다.

셋째로, 본 발명에 따른 화소 회로는 구동 트랜지스터의 제어 전극으로부터 네가티브 전원쪽으로 누설전류가 흐를 수 있는 전기적 연결관계가 존재하지 않기 때문에 누설전류에 의한 유기 전계 발광 소자의 부적절한 발광을 막을 수 있다.

이를 위하여 본 발명은 주사선에 제어 전극이 전기적으로 연결되고, 구동 트랜지스터의 제어 전극과 데이터선 사이에 전기적으로 연결된 제1스위칭소자와, 상기 제1스위칭소자에 제어 전극이 전기적으로 연결되고, 제1전원전압선과 제2전원전압선 사이에 전기적으로 연결된 구동 트랜지스터와, 상기 제1스위칭소자와 상기 제1전원전압선 및 상기 구동 트랜지스터 사이에 전기적으로 연결된 제1용량성소자와, 발광제어선에 제어전극이 전기적으로 연결되고, 상기 제1전원전압선과 상기 구동 트랜지스터 사이에 전기적으로 연결된 제2스위칭소자와, 상기 제1스위칭소자, 상기 제1용량성소자, 상기 제2스위칭소자 및 상기 구동 트랜지스터 사이에 전기적으로 연결된 제2용량성소자와, 상기 구동 트랜지스터와 상기 제2전원전압선 사이에 전기적으로 연결된 유기 전계 발광 소자를 포함하는 유기 전계 발광 표시 장치를 개시한다.

**대표도** - 도5

## 특허청구의 범위

### 청구항 1

주사선, 데이터선, 발광제어선 및 상기 주사선, 데이터선 및 발광제어선에 전기적으로 연결된 화소 회로를 포함하는 유기 전계 발광 표시 장치에 있어서,

상기 화소 회로는,

상기 주사선에 제어 전극이 전기적으로 연결되고, 상기 데이터선에 제1전극이 전기적으로 연결된 제1스위칭소자;

상기 제1스위칭소자의 제2전극에 제어 전극이 전기적으로 연결되고, 제1전원전압선과 제2전원전압선 사이에 전기적으로 연결된 구동 트랜지스터;

상기 제1전원전압선 및 상기 구동 트랜지스터의 제어 전극 사이에 전기적으로 연결된 제1용량성소자;

상기 발광제어선에 제어전극이 전기적으로 연결되고, 상기 제1전원전압선과 상기 구동 트랜지스터의 제1전극 사이에 전기적으로 연결된 제2스위칭소자;

상기 구동 트랜지스터의 제1전극 및 제어 전극 사이에 전기적으로 연결된 제2용량성소자; 및

상기 구동 트랜지스터의 제2전극 및 상기 제2전원전압선 사이에 전기적으로 연결된 유기 전계 발광 소자를 포함하여 이루어진 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 2

삭제

### 청구항 3

제 1항에 있어서,

상기 제1스위칭소자는 상기 주사선에 상기 제어 전극이 전기적으로 연결되어, 상기 제1전극에서 제2전극 방향으로 데이터를 전달함을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 4

제 1항에 있어서,

상기 구동 트랜지스터의 제2전극은 상기 유기 전계 발광 소자의 애노드 전극에 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 5

제 1항에 있어서,

상기 구동 트랜지스터는 상기 제어 전극이 상기 제1스위칭 소자의 제2전극에 전기적으로 연결되어, 상기 제1전원전압선으로부터의 구동 전류를 제어함을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 6

제 1항에 있어서,

상기 제1용량성소자의 제2전극은 상기 제1스위칭소자의 제2전극과 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 7

제 1항에 있어서,

상기 제1용량성소자는 제1전극이 상기 제1전원전압선과 전기적으로 연결되고, 제2전극이 상기 제2용량성소자의 제2전극과 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 8

제 1항에 있어서,

상기 제2스위칭소자는 상기 제어전극이 상기 발광제어선에 전기적으로 연결되고, 제1전극이 상기 제1전원전압선에 전기적으로 연결되며, 제2전극이 상기 구동 트랜지스터의 제1전극에 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 9

제 1항에 있어서,

상기 제2스위칭소자는 상기 제어전극이 상기 발광제어선에 전기적으로 연결되고, 제1전극이 상기 제1전원전압선에 전기적으로 연결되며, 제2전극이 상기 제2용량성소자의 제1전극에 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 10

제 1항에 있어서,

상기 제2용량성소자는 제1전극이 상기 제2스위칭소자의 제2전극 및 상기 구동 트랜지스터의 제1전극에 전기적으로 연결되고, 제2전극이 상기 제1용량성소자의 제2전극, 상기 제1스위칭소자의 제2전극 및 상기 구동 트랜지스터의 제어 전극과 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 11

삭제

### 청구항 12

제 1항에 있어서,

상기 유기 전계 발광 소자는 애노드 전극이 상기 구동 트랜지스터의 제2전극과 전기적으로 연결되고, 캐소드 전극이 상기 제2전원전압선에 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 13

제 1항에 있어서,

상기 제1스위칭소자, 제2스위칭소자, 구동 트랜지스터는 N형 채널 트랜지스터인 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 14

제 1항에 있어서,

상기 제1스위칭소자, 제2스위칭소자, 구동 트랜지스터는 P형 채널 트랜지스터인 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 15

제 1항에 있어서,

상기 유기 전계 발광 소자는 발광층을 구비하고 있으며, 상기 발광층은 형광 재료 및 인광 재료중 선택된 어느 하나 또는 그 혼합물인 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 16

제 15항에 있어서,

상기 발광층은 적색 발광 재료, 녹색 발광 재료, 청색 발광 재료중 선택된 어느 하나 또는 그 혼합물인 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 17

제 1항에 있어서,

상기 구동 트랜지스터는 비정질 실리콘 박막 트랜지스터, 폴리 실리콘 박막 트랜지스터, 유기 박막 트랜지스터 및 나노 박막 트랜지스터중 선택된 어느 하나인 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 18

제 1항에 있어서,

상기 구동 트랜지스터는 니켈(Ni), 카드뮴(Cd), 코발트(Co), 티타늄(Ti), 팔라듐(Pd) 및 텉스텐(W)중 선택된 어느 하나를 갖는 폴리 실리콘 트랜지스터인 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 19

제 1항에 있어서,

상기 제2전원전압선의 제2전원전압은 상기 제1전원전압선의 제1전원전압보다 낮은 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 20

제 1항에 있어서,

상기 제2전원전압선의 제2전원전압은 접지전압인 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 21

제 1항에 있어서,

한 프레임의 화상 표시 기간중 상기 제1스위칭소자 및 제2스위칭소자가 턴온되면, 상기 데이터선으로부터 데이터 전압이 상기 제1용량성소자의 제2전극, 제2용량성소자의 제2전극 및 상기 구동 트랜지스터의 제어전극에 인가되고, 상기 제1전원전압선으로부터의 제1전원전압이 상기 제1용량성소자의 제1전극 및 상기 제2용량성소자의 제1전극에 인가됨을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 22

제 1항에 있어서,

한 프레임의 화상 표시 기간중 상기 제1스위칭소자가 턴온되고, 상기 제2스위칭소자가 턴오프되면, 상기 데이터선으로부터 데이터 전압이 상기 제1용량성소자의 제2전극, 제2용량성소자의 제2전극 및 상기 구동 트랜지스터의 제어전극에 인가되고, 상기 제1전원전압선으로부터의 제1전원전압이 상기 제1용량성소자의 제1전극에 인가됨을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 23

제 1항에 있어서,

한 프레임의 화상 표시 기간중 상기 제1스위칭소자가 턴오프되고, 상기 제2스위칭소자가 턴온되면, 상기 제1전원전압선, 구동 트랜지스터 및 유기 전계 발광 소자가 전기적으로 연결되고, 상기 유기 전계 발광 소자의 애노드 전극에서 캐소드 전극 방향으로 전류가 인가됨을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 24

제 1항에 있어서,

상기 구동 트랜지스터와 상기 유기 전계 발광 소자 사이에는 발광제어 스위칭소자가 더 포함된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 25

제 24항에 있어서,

상기 발광제어 스위칭소자의 제어전극은 상기 발광제어선이 전기적으로 연결되어 있고, 상기 발광제어 스위칭소자의 제1전극은 상기 구동 트랜지스터의 제2전극과 전기적으로 연결되어 있으며, 상기 발광제어 스위칭소자의 제2전극은 상기 유기 전계 발광 소자의 애노드전극과 전기적으로 연결된 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 26

제 24항에 있어서,

상기 발광제어 스위칭소자는 N형 채널 트랜지스터인 것을 특징으로 하는 유기 전계 발광 표시 장치.

### 청구항 27

제 24항에 있어서,

상기 발광제어 스위칭소자는 P형 채널 트랜지스터인 것을 특징으로 하는 유기 전계 발광 표시 장치.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

&lt;30&gt;

본 발명은 유기 전계 발광 표시 장치에 관한 것으로서, 보다 상세히는 기존의 화소 회로에 비해 적은 숫자의 트랜지스터를 사용함으로써 화소 회로의 고집적화, 나아가 고해상도를 실현할 수 있게하고, 화소 회로내의 제1용량성소자 및 제2용량성소자의 비율을 적절히 조절함으로써 구동 트랜지스터의 문턱전압을 보상하고, 제1전원전압선에 의한 전압강하(IR-DROP) 현상을 개선할 수 있는 유기 전계 발광 표시 장치에 관한 것이다.

&lt;31&gt;

또한, 본 발명은 상기 화소 회로의 구동방법으로서 디멀티플렉서(Demultiplexer, 이하 디믹스(Demux)라고 한다)를 사용하여 알지비(RGB)데이터신호를 인가하는 경우, 주사신호의 온(On)/오프(Off)에 관계없이 발광제어 신호의 온(On) 기간동안 상기 알지비(RGB)데이터신호를 인가함으로써 상기 알지비(RGB)데이터가 화소 회로들의 각 용량성소자에 올바르게 저장될 수 있도록 하는 디믹스 구동 방법에 관한 내용을 포함하고 있다.

&lt;32&gt;

아울러, 본 발명은 상기 화소 회로의 또 다른 구동방법으로서 디멀티플렉서 (Demultiplexer, 이하 디믹스 (Demux)라고 한다)를 사용하여 알지비(RGB)데이터신호를 인가하는 경우, 발광기간의 중간에 화이트 밸런스 보상기간을 진행함으로써 시간이 지남으로써 화이트 밸런스가 달라져 원하는 색을 재현할 수 없게 되는 문제점을 개선할 수 있도록 하는 디믹스 구동 방법에 관한 내용을 포함하고 있다.

&lt;33&gt;

최근에 유기 전계 발광 표시 장치는 얇은 두께와 넓은 시야각 그리고 빠른 반응 속도 등의 장점으로 인하여 차세대 평판 디스플레이로서 각광 받고 있다.

&lt;34&gt;

이러한 유기 전계 발광 표시 장치는 각 화소(Pixel)의 유기 전계 발광 소자(OLED)에 흐르는 전류의 양을 제어함으로써, 각 화소의 밝기(Brightness)를 제어하고 영상을 표시하게 된다.

&lt;35&gt;

다시 말하자면, 데이터 전압에 대응하는 전류가 유기 전계 발광 소자에 공급되고, 공급된 전류에 대응하여 유기 전계 발광 소자가 발광하게 된다. 이때, 인가되는 데이터 전압은 계조를 표현하기 위하여 일정 범위에서 다단계의 값을 갖는다.

&lt;36&gt;

구동 트랜지스터로서 비정질 실리콘(a-si)을 사용한 박막 트랜지스터(Thin Film Transistor; TFT)를 이용할 경우 전류 구동 능력은 상대적으로 낮지만 표시 장치의 균일도가 우수하고 대면적 공정에 유리한 장점을 가진다.

&lt;37&gt;

이러한 유기 전계 발광 표시 장치의 각 화소 회로들의 구동 트랜지스터들은 상이한 문턱전압( $V_{th}$ )을 가질 수 있는바, 이는 결국 디스플레이 패널의 회도의 균일성(Uniformity) 저하의 문제를 가져오게 된다. 또한, 제1전원전압선(VDD)이 각 화소 회로를 지남에 따라 전압강하(IR-DROP)가 생기게 되어 패널의 하단으로 갈수록 화소의 회도가 저하하는 문제가 있다.

- <38> 더욱이, 유기 전계 발광 표시 장치의 화소 회로가 다수의 트랜지스터를 포함할 경우, 고집적화가 불가능하게 되므로 상기 화소 회로를 장착한 디스플레이 패널의 고해상도 실현에 장애가 된다.

- <39> 상술한 화소 회로내 구동 트랜지스터의 문턱전압 보상을 위한 종래의 회로들은 상기 구동 트랜지스터의 제어전극과 제어전극으로부터 네거티브(Negative)전원쪽으로 패쓰(Path)가 형성되어 이를 통하여 누설전류(Leakage current)가 흐를 수 있게 되고, 이는 유기 전계 발광 소자의 부적절한 발광을 일으키는 문제가 있다.

- <40> 그리고, 디믹스(Demux)를 사용하여 알지비(RGB)데이터신호들을 화소회로들에 인가하는 경우, 화소 회로들과 전기적으로 연결된 발광제어선(EM[N])을 통해 인가되는 발광제어신호들이 오프(Off)된 상태이면 상기 알지비(RGB)데이터신호들이 상기 화소 회로내의 용량성 소자에 올바르게 저장되지 않을 수 있게 된다.

- <41> 즉, 상기 용량성 소자들에 이미 저장되어있던 알지비(RGB)데이터신호(전압)들이 초기화되지 않은 상태에서 디믹스(Demux)를 계속 구동하여 알지비(RGB)데이터신호(전압)를 계속인가할 경우, 상기 용량성 소자들에 올바른 알지비(RGB)데이터신호(전압)들이 저장될 수 없는 문제가 있다.

- <42> 아울러, 풀컬러 유기 전계 발광 표시 장치의 경우에는 유기 전계 발광 소자로서 적색(R), 녹색(G), 청색(B)의 삼색을 발광하는 유기 전계 발광 소자를 구비도록 함으로써 풀컬러를 구현한다.

- <43> 그런데, 유기 전계 발광층으로 사용되는 재료들은 자체 발광시 발생되는 열에 의해 열화될 수 있다. 이러한 열화 진행으로 인하여 유기 전계 발광 소자(OLED)는 휴대 저하 현상이 일어날 수 있으며, 이는 상기 유기 전계 발광 소자(OLED)의 수명이 저하되는 결과가 될 수 있다.

- <44> 한편, 유기 전계 발광 소자(OLED)내의 적색(Red, R), 녹색(Green, G) 및 청색(Blue, B)을 형성하는 유기 전계 발광층의 열화(Degradation)정도는 각각 차이가 있어, 상기 적색(R) 유기 전계 발광층, 상기 녹색(G) 유기 전계 발광층 및 상기 청색(B) 유기 전계 발광층의 휴대 차이가 시간이 시간이 흐름에 따라 커질 수 있다. 따라서, 초기 설정치에 비해 화이트 밸런스(White Balance)가 시간의 흐름에 따라 달라져 색좌표의 전이가 생기므로 원하는 색을 재현할 수 없는 문제가 생긴다.

- <45> 즉, 적색(R), 녹색(G), 청색(B) 각각에 해당하는 발광층은 서로 다른 수명특성을 가지고 있는바, 장시간 구동할 경우 화이트 밸런스를 유지하기 어려운 단점이 있다.

### 발명이 이루고자 하는 기술적 과제

- <46> 본 발명은 상술한 종래의 문제점을 극복하기 위한 것으로,

- <47> 본 발명의 목적은 기존의 화소 회로에 비하여 적은 숫자인 3개의 트랜지스터를 사용함으로써 고 집적화를 꾀할 수 있으며, 고해상도를 가능하게 함에 있다.

- <48> 본 발명의 다른 목적으로는 제1용량성소자 및 제2용량성소자의 비율(C1 : C2)을 적절히 조절함으로써 구동 트랜지스터의 문턱전압(Vth)을 보상하여 휴대의 균일성을 향상시킬 수 있으며, 상기 제1용량성소자 및 제2용량성 소자의 비율 조절에 따라 제1전원전압선 (VDD)에 의한 전압강하(IR-DROP) 현상을 개선함에 있다.

- <49> 본 발명의 또 다른 목적으로는 화소 회로내 구동 트랜지스터의 제어 전극으로부터 네거티브(Negative)전원쪽으로 누설전류가 흐를 수 있는 패스(Path)를 두지 않음으로써 상기 패스(Path)를 통해 흐르는 누설전류에 의한 유기 전계 발광 소자의 부적절한 발광을 막는데 있다.

- <50> 본 발명의 또 다른 목적은 디멀티플렉서를 사용하여 알지비(RGB)데이터신호를 인가하는 경우, 주사신호의 온(On)/오프(Off)에 관계없이 발광제어신호의 온(On) 기간동안 상기 알지비(RGB)데이터신호를 인가함으로써 상기 알지비(RGB)데이터가 화소 회로들의 각 용량성소자에 올바르게 저장될 수 있도록 하는데 있다.

- <51> 본 발명의 또 다른 목적은 적색, 녹색, 청색의 3원색을 표현하는 유기 전계 발광 소자의 발광회수 또는 발광강도를 제어하여 컬러표시를 하는 유기 전계 발광 표시 장치에 있어서, 발광기간의 중간에 화이트 밸런스 보상기간을 진행함으로써 시간이 지남으로써 화이트 밸런스가 달라져 원하는 색을 재현할 수 없게 되는 문제를 개선함에 있다.

- <52> 본 발명의 주 목적을 실현하기 위해 세부적으로는,

- <53> 한 프레임의 화상 표시 기간을 제1기간(T1), 제2기간(T2) 및 제3기간(T3)으로 나누어 볼 수 있다. 제1기간은 데이터 기입기간이고, 제2기간은 구동 트랜지스터의 문턱전압을 저장하는 기간이며, 제3기간은 발광기간이 된다. 이러한 제1기간, 제2기간 및 제3기간을 순차적으로 진행하는 동시에 저장 소자인 제1용량성소자 및 제2용량성소

자의 비율(C1 : C2)을 적절히 조절하여 각 화소 회로내 구동 트랜지스터의 문턱전압의 불균일에 의한 패널의 휘도 불균일성 및 제1전원전압선의 전압강하(IR-DROP)를 개선할 수 있다.

- <54> 이 경우 제1기간 및 제2기간은 비 발광기간이 되고, 제3기간은 발광기간이 된다. 비 발광기간은 발광기간에 비해 상대적으로 짧게 할 수 있다.

- <55> 또한, 디멀티플렉서를 사용하여 상기 화소 회로를 구동하는 경우,

- <56> 주사신호 및 발광제어신호가 각각 온(On)인 기간 동안 상기 디믹스(Demux)에서 알지비(RGB)데이터신호를 인가하는 방법으로 구동할 수 있다.

- <57> 또한, 주사신호가 오프(Off), 발광제어신호가 온(On)인 기간 동안 디믹스(Demux)에서 알지비(RGB)데이터신호를 인가하는 방법으로 구동할 수도 있다.

- <58> 이에 따라, 알지비(RGB)데이터신호가 화소 회로내 용량성 소자들에 올바르게 저장되지 않는 것을 개선할 수 있다.

- <59> 아울러, 화이트 밸런스 보상을 위한 디멀티플렉서 구동 방법으로는,

- <60> 주사신호 및 발광제어신호가 각각 온(On)인 기간 동안 상기 디믹스(Demux)에서 알지비(RGB)데이터신호를 인가할 수 있다.

- <61> 또한, 이러한 알지비(RGB)데이터신호를 인가하는 동안 화이트 밸런스(White Balance)보상기간을 수행할 수 있다.

- <62> 상기 화이트 밸런스 보상기간에는 유기 전계 발광 소자에 전류를 흐르게 하며, 상기 유기 전계 발광 소자에 화이트 밸런스 보상을 위해 전류를 흐르게 하는 시간은 시간이 긴 쪽부터 녹색(G), 적색(R) 및 청색(B)의 순서로 할 수 있다. 또한, 상기 전류는 발광 기간동안 상기 유기 전계 발광 소자에 흐르는 전류보다 크게 할 수 있다.

- <63> 이렇듯, 가장 수명이 길다고 할 수 있는 녹색 유기 전계 발광 소자에는 수명이 상대적으로 짧은 청색 유기 전계 발광 소자보다 화이트 밸런스 보상을 위한 전류를 장시간 흘려줌으로써, 발광 기간동안의 수명차이를 화이트 밸런스 보상기간 동안의 전류로서 보상할 수 있게 된다.

### 발광의 구성 및 작용

- <64> 일반적으로 유기 전계 발광 표시 패널은 행렬 형태로 배열된 NxM 개의 유기 발광셀들을 전압 구동 혹은 전류 구동하여 영상을 표현한다.

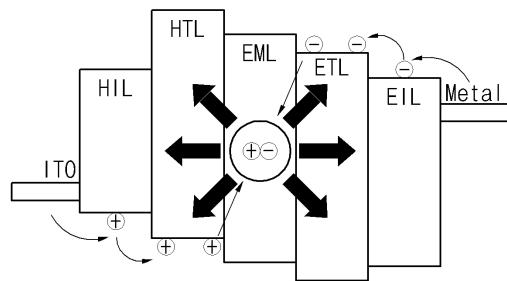

- <65> 다이오드 특성을 가지는 유기 전계 발광 소자(일반적으로 OLED라고 불린다)

- <66> 는 도 1에 도시된 바와 같이 애노드(Anode; ITO)전극, 유기박막(유기층) 및 캐소드 (Cathode; Metal)전극으로 이루어져 있다. 상기 유기박막은 정공의 균형을 좋게 하여 발광 효율을 향상시키기 위해 발광층(Emitting Layer,EML), 전자를 수송하는 전자 수송층(Electron Transport Layer,ETL) 및 정공을 수송하는 정공 수송층(Hole Transport Layer,HTL)을 포함한 다층 구조로 이루어질 수 있다. 또한, 이와 별도로 상기 전자 수송층의 일측면에 전자를 주입하는 전자 주입층(Electron Injecting Layer,EIL)과 상기 정공 수송층의 일측면에 정공을 주입하는 정공 주입층(Hole Injection Layer)이 더 형성될 수 있다.

- <67> 더불어, 인광형 유기 전계 발광 소자의 경우에는 정공 억제층(Hole Blocking Layer; HBL)이 상기 발광층(EML)과 상기 전자 수송층(ETL) 사이에 선택적으로 형성될 수 있으며, 전자 억제층(Electron Blocking Layer; EBL)이 상기 발광층(EML)과 정공 수송층(HTL) 사이에 선택적으로 형성될 수 있다.

- <68> 또한, 상기 유기박막(유기층)은 두 종류의 층을 혼합하여 그 두께를 감소시키는 슬림형 유기 전계 발광 소자(Slim OLED) 구조로 형성할 수도 있다. 예를들면, 상기 정공 주입층(HIL)과 상기 정공 수송층(HTL)을 동시에 형성하는 정공 주입 수송층(Hole Injection Transport Layer; HITL) 구조 및 상기 전자 주입층(EIL)과 상기 전자 수송층(ETL)을 동시에 형성하는 전자 주입 수송층(Electron Injection Transport Layer; EITL) 구조를 선택적으로 형성할 수 있다. 상기와 같은 슬림형 유기 전계 발광 소자는 발광 효율을 증가시키는데 그 사용의 목적이 있다.

- <69> 또한, 상기 애노드전극과 발광층(EML) 사이에 선택적으로 버퍼층(Buffer Layer)을 형성할 수 있다. 상기 버퍼층은 전자를 버퍼링하는 전자 버퍼층(Electron Buffer Layer)과 정공을 버퍼링하는 정공 버퍼층(Hole Buffer

Layer)으로 구분 할 수 있다. 상기 전자 베피층은 음극과 전자 주입층(EIL) 사이에 선택적으로 형성할 수 있으며, 상기 전자 주입층(EIL)의 기능을 대신하여 형성할 수 있다. 이때, 상기 유기박막의 적층 구조는 발광층(EML) / 전자 수송층(ETL) / 전자 베피층 / 캐소드가 될 수 있다. 또한, 상기 정공 베피층은 상기 애노드전극과 상기 정공 주입층(EIL) 사이에 선택적으로 형성될 수 있으며, 상기 정공 주입층(HIL)의 기능을 대신하여 형성할 수 있다. 이때, 상기 유기박막의 적층 구조는 애노드전극 / 정공 베피층(Hole buffer layer) / 정공 수송층(HTL) / 발광층(EML)이 될 수 있다.

<70> 상기 구조에 대하여 가능한 적층 구조를 기재하면 다음과 같다.

<71> a) 정상 적층 구조 (Normal Stack Structure)

<72> 1) 애노드/정공 주입층/정공 수송층/발광층/전자 수송층/전자 주입층/캐소드

<73> 2) 애노드/정공 베피층/정공 주입층/정공 수송층/발광층/전자 수송층/전자 주입층/캐소드

<74> 3) 애노드/정공 주입층/정공 수송층/발광층/전자 수송층/전자 주입층/전자 베피층/캐소드

<75> 4) 애노드/정공 베피층/정공 주입층/정공 수송층/발광층/전자 수송층/전자 주입층/전자 베피층/캐소드

<76> 5) 애노드/정공 주입층/정공 베피층/정공 수송층/발광층/전자 수송층/전자 주입층/캐소드

<77> 6) 애노드/정공 주입층/정공 수송층/발광층/전자 수송층/전자 베피층/전자 주입층/캐소드

<78> b) 정상 슬림 구조(Normal Slim Structure)

<79> 1) 애노드/정공 주입 수송층/발광층/전자 수송층/전자 주입층/음극

<80> 2) 애노드/정공베피층/정공주입수송층/발광층/전자수송층/전자주입층/캐소드

<81> 3) 애노드/정공주입층/정공수송층/발광층/전자주입수송층/전자베피층/캐소드

<82> 4) 애노드/정공베피층/정공수송층/발광층/전자주입수송층/전자베피층/캐소드

<83> 5) 애노드/정공주입수송층/정공베피층/발광층/전자수송층/전자주입층/캐소드

<84> 6) 애노드/정공주입층/정공수송층/발광층/전자베피층/전자주입수송층/캐소드

<85> c) 역상적층 구조(Inverted Stack Structure)

<86> 1) 캐소드/전자주입층/전자수송층/발광층/정공수송층/정공주입층/애노드

<87> 2) 캐소드/전자 주입층/전자 수송층/발광층/정공 수송층/정공 주입층/정공 베피층/애노드

<88> 3) 캐소드/전자 베피층/전자 주입층/전자 수송층/발광층/정공 수송층/정공 주입층/애노드

<89> 4) 캐소드/전자 베피층/전자 주입층/전자 수송층/발광층/정공 수송층/정공 베피층/애노드

<90> 5) 캐소드/전자 주입층/전자 수송층/발광층/정공 수송층/정공 베피층/정공 주입층/애노드

<91> 6) 캐소드/전자 주입층/전자 베피층/전자 수송층/발광층/정공 수송층/정공 주입층/애노드

<92> d) 역상 슬림 구조(Inverted Slim Structure)

<93> 1) 캐소드/전자 주입층/전자 수송층/발광층/정공 주입층/애노드

<94> 2) 캐소드/전자주입층/전자수송층/발광층/정공주입수송층/정공베피층/애노드

<95> 3) 캐소드/전자베피층/전자주입수송층/발광층/정공수송층/정공주입층/애노드

<96> 4) 캐소드/전자베피층/전자주입수송층/발광층/정공수송층/정공주입층/애노드

<97> 5) 캐소드/전자주입층/전자수송층/발광층/정공베피층/정공주입수송층/애노드

<98> 6) 캐소드/전자주입수송층/전자베피층/발광층/정공수송층/정공주입층/애노드

<99> 여기에서 캐소드(Cathode)는 음극을 애노드(Anode)는 양극을 의미한다.

<100> 또한, 이러한 유기 전계 발광 표시 장치는 데이터 라인에 기입되는 데이터 종류에 따라 전압프로그래밍(Voltage Programming)유기전계발광표시장치와 전류프로그래밍(Current Programming)유기전계발광표시장치로 구분될 수

있다.

<101> 이와 같은 유기 전계 발광 소자의 구동 방식으로서는 수동 매트릭스(Passive Matrix) 방식과 능동 매트릭스(Active Matrix) 방식이 알려져 있다. 상기 수동 매트릭스 방식은 양극과 음극을 직교하도록 형성하고 라인을 선택하여 구동함으로써 제작 공정이 단순하고 투자비가 적으나 대화면 구현시 전류 소모량이 많다는 단점이 있다. 상기 능동 매트릭스 방식은 박막 트랜지스터와 같은 능동 소자 및 용량성 소자를 각 화소에 형성함으로써 전류 소모량이 적고 화질 및 수명이 우수하여 중대형까지 확대 가능하다는 장점이 있다.

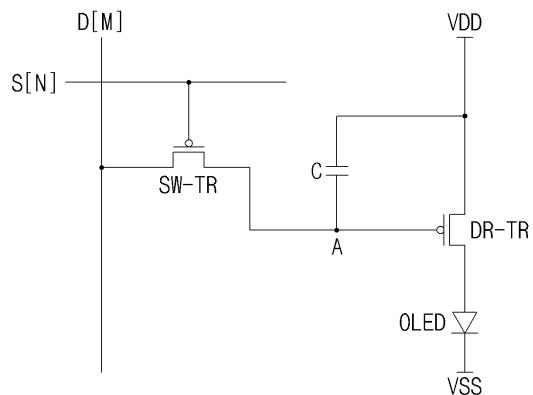

<102> 상술한 바와 같이 능동 매트릭스 방식에서는 유기 전계 발광 소자와 박막 트랜지스터를 기반으로 한 화소 회로 구성이 필수적인데, 이때 상기 박막 트랜지스터로서는 비정질 실리콘 박막 트랜지스터 또는 다결정 실리콘 박막 트랜지스터를 이용하게 된다. 도 2를 참조하면, 유기 전계 발광 표시 장치의 화소 회로가 도시되어 있고, 도3을 참조하면, 도2에 도시된 화소 회로의 구동 타이밍도가 도시되어 있다. 이러한 화소 회로는  $N \times M$  개의 화소중 하나를 대표적으로 도시한 것이다.

<103> 도 2에 도시된 바와 같이 유기 전계 발광 표시 장치의 화소 회로는 주사 신호를 공급하는 주사선(S[N]), 데이터 신호를 공급하는 데이터선(D[M]), 제1전원전압을 공급하는 제1전원전압선(VDD), 제2전원전압을 공급하는 제2전원전압선(VSS), 구동 트랜지스터(DR\_TR), 스위칭 소자(SW\_TR), 용량성 소자(C) 및 유기 전계 발광소자(OLED)를 포함한다. 여기서, 상기 제1전원전압은 상기 제2전원전압에 비해 상대적으로 높은 레벨의 전압일 수 있다.

<104> 상술한 화소 회로의 한 프레임 동안의 동작을 도 3을 참조하여 설명한다.

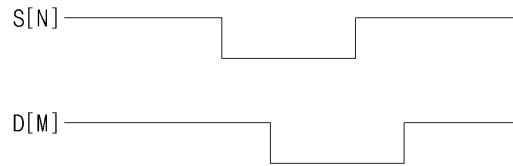

<105> 도 3에 표시된 바와 같이 주사 신호가 공급되고, 그 후 약간의 시간차를 두고 데이터 신호가 공급된다. 약간의 시간차를 두는 이유는 주사 신호의 공급에 의한 스위칭 소자의 턴온 시간 부터 데이터 신호의 공급 시간까지의 마진(Margin)을 확보해주기 위함이다. 다시 도 2의 화소 회로를 도 3의 타이밍도에 따라 설명해보면,

<106> 상기 주사선(S[N])으로부터 주사 신호가 공급되면, 상기 스위칭 소자(SW\_TR)가 턴온된다. 따라서, 상기 데이터 선(D[M])으로부터의 데이터 신호(전압)는 상기 구동 트랜지스터(DR\_TR)의 제어 전극 및 상기 용량성 소자(C)의 제1전극(A)에 공급된다. 따라서, 상기 제1전원전압선(VDD)으로부터의 제1전원전압이 상기 구동 트랜지스터(DR\_TR)를 통하여 상기 유기 전계 발광 소자(OLED)에 공급됨으로써, 상기 유기 전계 발광 소자(OLED)는 한 프레임 동안 일정 휘도로 발광하게 된다. 물론, 상기 용량성 소자(C)에는 상기 데이터선(D[M])으로부터 공급되는 데이터 전압이 저장되기 때문에, 상기 주사 신호선(S[N])으로부터의 주사 신호 공급이 차단된다고 해도 한 프레임 동안 상기 구동 트랜지스터(DR\_TR)는 계속 턴온 상태를 유지한다.

<107> 그런데, 상기와 같은 종래의 구조에서 전압구동을 이용할 경우 구동 트랜지스터로써 사용되는 박막 트랜지스터(Thin Film Transistor; TFT)의 문턱전압(Threshold Voltage; V<sub>th</sub>)의 불규칙성으로 인해 고계조를 얻기 어려운 문제점이 있다. 예를 들어, 3V로 픽셀을 구동할 경우에 8비트(256)계조를 표현하기 위해서는  $3/256=12mV$ 로 10mV 단위를 갖는 반면, 박막 트랜지스터의 문턱전압(V<sub>th</sub>)의 변화는 100mV의 단위를 갖기 때문에 고계조를 표현하기 어려운 문제점이 있다.

<108> 또한, 제1전원전압선(VDD)에서 유기 전계 발광 소자(OLED)를 구동하는 전류를 공급하기 때문에 화소의 수가 많아질수록 VDD에서는 더 많은 양의 전류를 공급해야 한다. 따라서, 로우(ROW)방향으로 화소수가 많아질수록 VDD 공급 라인(Line)에서 라인 저항에 의해 전압 강하(IR-DROP)가 발생한다. (즉,  $V=I \times R$ )

<109> 이것은 화소 각각에 배치되어 있는 박막 트랜지스터(TFT)의 V<sub>gs</sub> 값이 달라지도록 하여 유기 전계 발광 소자(OLED)의 전류차이를 유발시키게 되며, 이와 같은 전류차이는 대면적화될 수록 더욱 심화되어 화질 불균일로 나타나게 된다.

<110> 상술한, 문턱전압(V<sub>th</sub>)보상, VDD 라인의 전압강하(IR-DROP)보상을 위해서 화소 회로를 다양하게 구성해볼 수 있으나, 화소회로가 복잡해질 수 있으며, 이러한 화소 회로의 복잡화는 고집적화를 어렵게 한다. 고집적화는 고해상도 구현을 가능하게 하는바, 화소회로의 단순화는 유기 전계 발광 표시 장치의 고해상도 구현을 위해 필요한 과제라고 할 수 있다.

<111> 또한, 디믹스(Demux)를 사용하여 알지비(RGB)데이터신호들을 화소회로들에 인가하는 경우, 화소 회로들과 전기적으로 연결된 발광제어신호(EM[N]으로부터의 신호)들이 오프(Off)된 상태이면 상기 알지비(RGB)데이터신호들이 상기 화소 회로내의 용량성 소자에 올바르게 저장되지 않을 수 있게 된다. 즉, 상기 용량성 소자들에 이미 저장되어있던 알지비(RGB)데이터신호(전압)들이 초기화되지 않은 상태에서 디믹스(Demux)를 계속 구동하여 알지비(RGB)데이터신호(전압)를 계속인가할 경우, 상기 용량성 소자들에 올바른 알지비(RGB)데이터신호(전압)들이 저

장될 수 없는 문제가 있다.

<112> 아울러, 유기 전계 발광층으로 사용되는 재료들(예를들어, DCM2, 키나크리든, DPVB1등)은 자체 발광시 발생되는 열에 의해 열화될 수 있다. 이러한 열화 진행으로 인하여 유기 전계 발광 소자(OLED)는 휘도 저하 현상이 일어날 수 있으며, 이는 상기 유기 전계 발광 소자(OLED)의 수명이 저하되는 결과가 될 수 있다.

<113> 상기 유기 전계 발광 소자(OLED)내의 적색(Red, R), 녹색(Green, G) 및 청색(Blue, B)을 형성하는 유기 전계 발광층의 열화(Degradation)정도는 각각 차이가 있다. 따라서, 상기 적색(R) 유기 전계 발광층, 상기 녹색(G) 유기 전계 발광층 및 상기 청색(B) 유기 전계 발광층의 휘도 차이가 시간이 시간이 흐름에 따라 커질수 있게된다. 이러한 시간의 변화에 따라 초기 설정치에 비해 화이트 밸런스(White Balance)가 달라져 색좌표의 전이가 생기므로 원하는 색을 재현할 수 없다는 문제가 있다.

<114> 상기한 문제를 해결하기 위해 본 발명에 의한 유기 전계 발광 표시 장치는

<115> 주사선, 데이터선, 상기 주사선에 제어 전극이 전기적으로 연결되고, 구동 트랜지스터의 제어 전극과 상기 데이터선 사이에 전기적으로 연결된 제1스위칭소자와, 상기 제1스위칭소자에 제어 전극이 전기적으로 연결되고, 제1전원전압선과 제2전원전압선 사이에 전기적으로 연결된 구동 트랜지스터와, 상기 제1스위칭소자와 상기 제1전원전압선 및 상기 구동 트랜지스터 사이에 전기적으로 연결된 제1용량성소자와, 발광제어선에 제어전극이 전기적으로 연결되고, 상기 제1전원전압선과 상기 구동 트랜지스터 사이에 전기적으로 연결된 제2스위칭소자와, 상기 제1스위칭소자, 상기 제1용량성소자, 상기 제2스위칭소자 및 상기 구동 트랜지스터 사이에 전기적으로 연결된 제2용량성소자와, 상기 구동 트랜지스터와 상기 제2전원전압선 사이에 전기적으로 연결된 유기 전계 발광 소자를 포함한다.

<116> 상기 제1스위칭소자는 상기 주사선에 제어 전극이 전기적으로 연결되고, 제1전극이 상기 데이터선에 연결되며, 제2전극이 상기 구동 트랜지스터의 제어 전극에 연결될 수 있다.

<117> 상기 제1스위칭소자는 상기 주사선에 제어 전극이 전기적으로 연결되어, 제1전극에서 제2전극 방향으로 데이터를 전달할 수 있다.

<118> 상기 구동 트랜지스터는 제어 전극이 상기 제1스위칭 소자의 제2전극에 전기적으로 연결되고, 제1전극이 상기 제2스위칭소자의 제2전극에 연결되며, 제2전극이 상기 유기 전계 발광 소자의 애노드에 전기적으로 연결될 수 있다.

<119> 상기 구동 트랜지스터는 제어 전극이 상기 제1스위칭 소자의 제2전극에 전기적으로 연결되어, 상기 제1전원전압선으로부터의 구동 전류를 제어할 수 있다.

<120> 상기 제1용량성소자는 제1전극이 상기 제1전원전압선과 전기적으로 연결되고, 제2전극이 상기 제1스위칭소자의 제2전극 및 상기 구동 트랜지스터의 제어 전극과 전기적으로 연결될 수 있다.

<121> 상기 제1용량성소자는 제1전극이 상기 제1전원전압선과 전기적으로 연결되고, 제2전극이 상기 제2용량성소자의 제2전극과 전기적으로 연결될 수 있다.

<122> 상기 제2스위칭소자는 제어전극이 상기 발광제어선에 전기적으로 연결되고, 제1전극이 상기 제1전원전압선에 전기적으로 연결되며, 제2전극이 상기 구동 트랜지스터의 제1전극에 전기적으로 연결될 수 있다.

<123> 상기 제2스위칭소자는 제어전극이 상기 발광제어선에 전기적으로 연결되고, 제1전극이 상기 제1전원전압선에 전기적으로 연결되며, 제2전극이 상기 제2용량성소자의 제1전극에 전기적으로 연결될 수 있다.

<124> 상기 제2용량성소자는 제1전극이 상기 제2스위칭소자의 제2전극 및 상기 구동 트랜지스터의 제1전극에 전기적으로 연결되고, 제2전극이 상기 제1용량성소자의 제2전극, 상기 제1스위칭소자의 제2전극 및 상기 구동 트랜지스터의 제1전극과 전기적으로 연결될 수 있다.

<125> 상기 제2용량성 소자는 상기 구동 트랜지스터의 제어 전극 및 상기 구동 트랜지스터의 제1전극 사이에 전기적으로 연결될 수 있다.

<126> 상기 유기 전계 발광 소자는 애노드가 상기 구동 트랜지스터의 제2전극과 전기적으로 연결되고, 캐소드가 상기 제2전원전압선에 전기적으로 연결될 수 있다.

<127> 상기 제1스위칭소자, 제2스위칭소자, 구동 트랜지스터는 N형 채널 트랜지스터일 수 있다.

- <128> 상기 제1스위칭소자, 제2스위칭소자, 구동 트랜지스터는 P형 채널 트랜지스터일 수 있다.

- <129> 상기 유기 전계 발광 소자는 발광층을 구비하고 있으며, 상기 발광층은 형광 재료 및 인광 재료중 선택된 어느 하나 또는 그 혼합물일 수 있다.

- <130> 상기 발광층은 적색 발광 재료, 녹생 발광 재료, 청색 발광 재료중 선택된 어느 하나 또는 그 혼합물일 수 있다.

- <131> 상기 구동 트랜지스터는 비정질 실리콘 박막 트랜지스터, 폴리 실리콘 박막 트랜지스터, 유기 박막 트랜지스터 및 나노 박막 트랜지스터중 선택된 어느 하나일 수 있다.

- <132> 상기 구동 트랜지스터는 니켈(Ni), 카드뮴(Cd), 코발트(Co), 티타늄(Ti), 팔라듐(Pd) 및 텉스텐(W)중 선택된 어느 하나를 갖는 폴리 실리콘 트랜지스터일 수 있다.

- <133> 상기 제2전원전압선의 제2전원전압은 상기 제1전원전압선의 제1전원전압보다 낮을 수 있다.

- <134> 상기 제2전원전압선의 제2전원전압은 접지전압일 수 있다.

- <135> 한 프레임의 화상 표시 기간중 상기 제1스위칭소자 및 제2스위칭소자가 턴온되면, 상기 데이터선으로부터 데이터 전압이 상기 제1용량성소자의 제2전극, 제2용량성소자의 제2전극 및 상기 구동 트랜지스터의 제어전극에 인가되고, 상기 제1전원전압선으로부터의 제1전원전압이 상기 제1용량성소자의 제1전극 및 상기 제2용량성소자의 제1전극에 인가될 수 있다.

- <136> 한 프레임의 화상 표시 기간중 상기 제1스위칭소자가 턴온되고, 상기 제2스위칭소자가 턴오프되면, 상기 데이터 선으로부터 데이터 전압이 상기 제1용량성소자의 제2전극, 제2용량성소자의 제2전극 및 상기 구동 트랜지스터의 제어전극에 인가되고, 상기 제1전원전압선으로부터의 제1전원전압이 상기 제1용량성소자의 제1전극에 인가될 수 있다.

- <137> 한 프레임의 화상 표시 기간중 상기 제1스위칭소자가 턴오프되고, 상기 제2스위칭소자가 턴온되면, 상기 제1전원전압선, 구동 트랜지스터 및 유기 전계 발광 소자가 전기적으로 연결되고, 상기 유기 전계 발광 소자의 애노드에서 캐소드 방향으로 전류가 인가될 수 있다.

- <138> 상기 구동 트랜지스터와 상기 유기 전계 발광 소자 사이에는 발광제어 트랜지스터가 더 포함될 수 있다.

- <139> 상기 발광제어 트랜지스터의 제어전극은 상기 발광제어선이 전기적으로 연결될 수 있고, 상기 발광제어 트랜지스터의 제1전극은 상기 구동 트랜지스터의 제2전극과 전기적으로 연결될 수 있으며, 상기 발광제어 트랜지스터의 제2전극은 상기 유기 전계 발광 소자의 애노드와 전기적으로 연결될 수 있다.

- <140> 상기 발광제어 스위칭소자는 N형 채널 트랜지스터일 수 있다.

- <141> 상기 발광제어 스위칭소자는 P형 채널 트랜지스터일 수 있다.

- <142> 상술한 바와 같이, 본 발명에 따른 유기 전계 발광 표시 장치는 한 프레임의 화상 표시 기간을 제1기간, 제2기간 및 제3기간으로 나눌 수 있다. 상기 제1기간(T1)은 데이터선으로부터 데이터 전압이 인가되는 데이터 기입구간이고, 상기 제2기간(T2)은 구동 트랜지스터의 문턱전압(Vth)을 저장하는 기간이 되며, 상기 제3기간(T3)은 발광기간이 된다.

- <143> 이러한 제1기간, 제2기간 및 제3기간을 순차적으로 진행하는 동시에 저장 소자인 제1용량성소자 및 제2용량성소자의 비율(C1 : C2)을 적절히 조절하여 각 화소 회로내 구동 트랜지스터의 문턱전압의 불균일에 의한 패널의 휘도 불균일성 및 제1전원전압선의 전압강하(IR-DROP)를 개선할 수 있다.

- <144> 이 경우 제1기간 및 제2기간은 비 발광기간이 되고, 제3기간은 발광기간이 된다. 비 발광기간은 발광기간에 비해 상대적으로 짧게 할 수 있다.

- <145> 이하, 본 발명이 속하는 기술 분야에서 통상의 지식을 가진자가 본 발명을 용이하게 실시할 수 있을 정도로 본 발명의 바람직한 실시예를 첨부된 도면을 참조하여 상세하게 설명하면 다음과 같다.

- <146> 본 발명을 명확하게 설명하기 위해 첨부된 도면에서 발명과 관계없는 부분은 생략하였다. 명세서 전체를 통하여 유사한 구성 및 동작을 갖는 부분에 대해서는 동일한 도면 부호를 붙였다. 어떤 부분이 다른 부분과 전기적으로 연결되어 있다고 할 때, 이는 전기적으로 연결되어 있는 경우뿐만 아니라 그 중간에 다른 소자를 사이에 두고 연결되어 있는 경우도 포함한다.

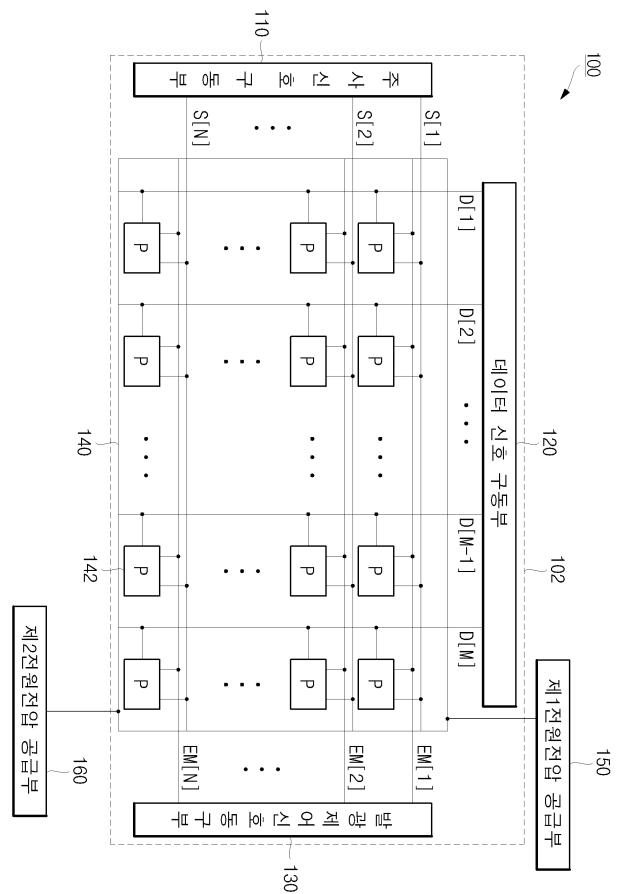

- <147> 도 4를 참조하면, 본 발명에 따른 유기 전계 발광 표시 장치의 구성이 블록도로서 도시되어 있다.

- <148> 도 4에 도시된 바와 같이 유기 전계 발광 표시 장치(100)는 주사 신호 구동부(110), 데이터 신호 구동부(120), 발광 제어 신호 구동부(130), 유기 전계 발광 표시 패널(140) (이하, 패널(140)이라한다), 제1전원전압 공급부(150) 및 제2전원 전압 공급부(160)를 포함할 수 있다.

- <149> 상기 주사 신호 구동부(110)는 다수의 주사선(S[1], ,S[N])을 통하여 상기 패널(140)에 주사 신호를 순차적으로 공급할 수 있다.

- <150> 상기 데이터 신호 구동부(120)는 다수의 데이터선(D[1], ,...,D[M])을 통하여 상기 패널에 데이터 신호를 공급할 수 있다.

- <151> 상기 발광 제어 신호 구동부(130)는 다수의 발광제어선(EM[1]...,EM[N])을 통하여 상기 패널(140)에 발광제어 신호를 순차적으로 공급할 수 있다.

- <152> 또한, 상기 패널(140)은 열방향으로 배열되어 있는 다수의 주사 선(S[1], ,S[N]), 발광제어선(EM[1]...,EM[N])과 행방향으로 배열되는 다수의 데이터 선(D[1], ,...,D[M])과, 상기 주사선(S[1], ,S[N]), 발광제어선(EM[1]...,EM[N])과 데이터선(D[1], ,...,D[M])에 의해 정의되는 화소 회로(142,Pixel)를 포함할 수 있다.

- <153> 여기서, 상기 화소 회로(142,Pixel)는 주사선과 데이터선에 의해 정의되는 화소 영역에 형성될 수 있다. 물론, 상술한 바와 같이 상기 주사선(S[1], ,S[N])에는 상기 주사 신호 구동부(110)로부터 주사 신호가 공급될 수 있고, 상기 데이터 선(D[1], ,...,D[M])에는 상기 데이터 구동부(120)로부터 데이터 신호가 공급될 수 있으며, 상기 발광 제어 신호선(EM[1]...,EM[N])에는 상기 발광 제어 신호 구동부(130)로부터 발광 제어 신호가 공급될 수 있다.

- <154> 또한, 상기 제1전원전압 공급부(150), 제2전원전압 공급부(160)는 패널(140)에 구비된 각 화소회로(142)에 제1전원전압, 제2전원전압을 공급하는 역할을 한다.

- <155> 한편, 도 4에 도시된 바와 같이 이러한 주사 신호 구동부(110), 데이터 신호 구동부(120), 발광 제어 신호 구동부(130), 패널(140), 제1전원전압 공급부(150) 및 제2전원전압 공급부(160)는 하나의 기판(102)에 모두 형성될 수 있다.

- <156> 특히, 상기 구동부들 및 전원 공급부들(110, 120, 130, 150, 160)은 주사 선(S[1], ,S[N]), 데이터선(D[1], ,...,D[M]), 발광제어선(EM[1]...,EM[N]) 및 화소 회로(142)의 트랜지스터(도시되지 않음)를 형성하는 층과 동일한 층에 형성될 수도 있다. 물론, 상기 구동부들 및 전원 공급부들(110, 120, 130, 150, 160)은 상기 기판(102)과 별도로 다른 기판(도시되지 않은)에 형성하고, 이를 상기 기판(102)에 전기적으로 연결할 수도 있다. 더불어, 상기 구동부들 및 전원 공급부들(110, 120, 130, 150, 160)은 상기 기판(102)에 전기적으로 연결하는 TCP(Tape Carrier Package), FPC(Flexible Printed Circuit), TAB(Tape Automatic Bonding), COG(Chip On Glass) 및 그 등가물중 선택된 어느 하나의 형태로 형성할 수 있으며, 본 발명에서 상기 구동부들 및 전원 공급부들(110, 120, 130, 150, 160)의 형태 및 형성 위치를 한정하는 것은 아니다.

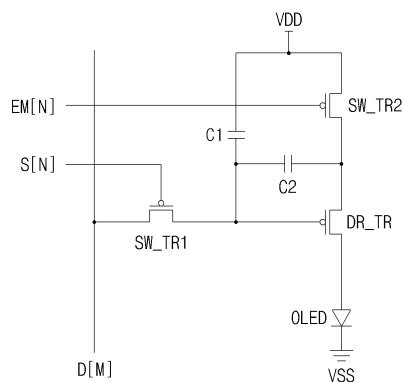

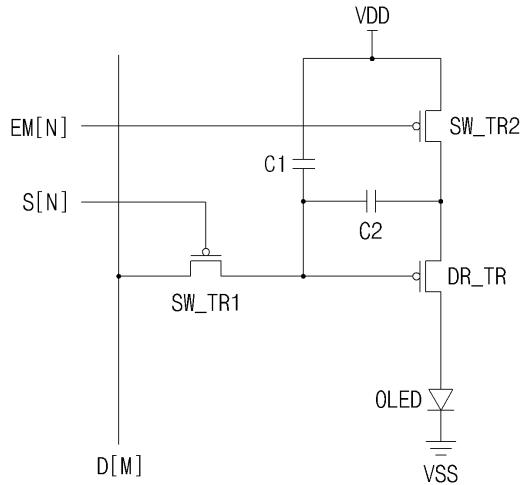

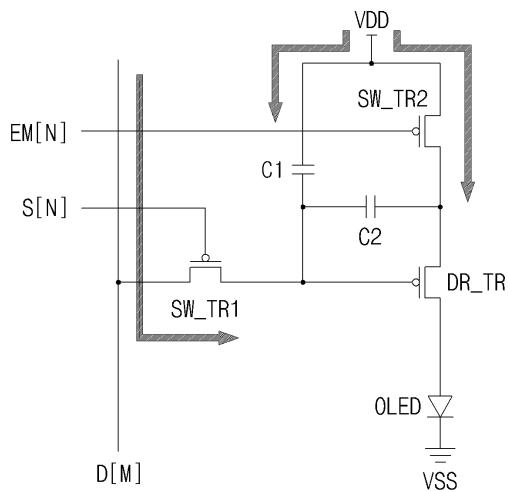

- <157> 도 5를 참조하면, 본 발명의 유기 전계 발광 장치의 일실시예에 따른 화소 회로를 도시한 회로도가 도시되어 있다. 이하에서 설명하는 화소 회로는 모두 도 4에 개시된 유기 전계 발광 표시 장치(100)중 하나의 화소 회로(Pixel)를 의미한다.

- <158> 도 5에 도시된 바와 같이, 본 발명에 따른 유기 전계 발광 표시 장치의 화소회로는 주사선(S[N]), 데이터선(D[M]), 발광제어선(EM[N]), 제1전원전압선(VDD), 제2전원전압선(VSS), 제1스위칭소자(SW\_TR1), 제2스위칭소자(SW\_TR2), 구동 트랜지스터(DR\_TR), 제1용량성소자(C1), 제2용량성소자(C2) 및 유기 전계 발광 소자(OLED)를 포함할 수 있다.

- <159> 상기 주사선(S[N])은 켜고자하는 유기 전계 발광 소자(OLED)를 선택하는 주사 신호를 상기 제1스위칭소자(SW\_TR1)의 제어 전극에 공급하는 역할을 한다. 이러한 주사선(S[N])은 주사 신호를 생성하는 주사 신호 구동부(110, 도 4 참조)에 전기적으로 연결될 수 있다.

- <160> 상기 데이터선(D[M])은 발광 회로에 비례하는 데이터 신호(전압)를 상기 제1용량성소자(C1)의 제2전극, 상기 제2용량성소자(C2)의 제2전극 및 상기 구동 트랜지스터(DR\_TR)의 제어 전극에 공급하는 역할을 한다. 물론 이러한 데이터선(D[M])은 데이터 신호를 생성하는 데이터 신호 구동부(120, 도 4 참조)에 전기적으로 연결될 수 있다.

- <161> 상기 발광 제어선(EM[N])은 상기 제2스위칭소자(SW\_TR2)의 제어 전극에 전기적으로 연결되어 발광 제어 신호를

공급하는 역할을 한다. 상기 발광 제어 신호에 의해 상기 제2스위칭소자(SW\_TR2)가 턴온되면 상기 제1전원전압선(VDD)으로부터 제1전원전압이 상기 제1용량성소자(C1)의 제1전극, 상기 제2용량성소자(C2)의 제1전극 및 상기 구동 트랜지스터(DR\_TR)의 제1전극으로 인가될 수 있다. 물론, 이러한 발광 제어선(EM[N])은 발광 제어 신호를 생성하는 발광 제어 신호 구동부(130, 도 4 참조)에 전기적으로 연결될 수 있다.

<162> 상기 제1전원전압선(VDD)은 제1전원전압이 상기 유기 전계 발광 소자(OLED)에 공급되도록 한다. 물론, 이러한 제1전원전압선(VDD)은 제1전원전압을 공급하는 제1전원전압 공급부(150, 도 4 참조)에 전기적으로 연결될 수 있다.

<163> 상기 제2전원전압선(VSS)은 제2전원전압이 유기 전계 발광 소자(OLED)에 공급되도록 한다. 물론, 이러한 제2전원전압선(VSS)은 제2전원전압을 공급하는 제2전원전압 공급부(160, 도 4 참조)에 전기적으로 연결될 수 있다. 여기서, 상기 제1전원전압은 통상적으로 상기 제2전원전압에 비해 하이 레벨(High Level)일 수 있다.

<164> 또한, 제2전원전압은 접지(Ground) 전압을 이용할 수 있다.

<165> 상기 제1스위칭소자(SW\_TR1)는 제1전극(소스 또는 드레인 전극)이 상기 데이터선(D[M])에 전기적으로 연결되고, 제2전극(소스 또는 드레인 전극)이 상기 구동 트랜지스터(DR\_TR)의 제어 전극(게이트 전극), 상기 제1용량성소자(C1)의 제2전극 및 상기 제2용량성소자(C2)의 제2전극에 전기적으로 연결되며, 제어 전극(게이트 전극)이 상기 주사선(S[N])에 전기적으로 연결될 수 있다. 이러한, 제1스위칭 소자(SW\_TR1)는 P형 채널 트랜지스터일 수 있으며, 상기 주사선(S[N])을 통하여 제어 전극에 로우 레벨의 주사 신호가 인가되어 턴온되면, 상기 데이터선(D[M])을 통하여 데이터 전압을 상기 제1용량성소자(C1)의 제2전극, 상기 제2용량성소자(C2)의 제2전극 및 상기 구동 트랜지스터(DR\_TR)의 제어 전극에 인가한다.

<166> 상기 구동 트랜지스터(DR\_TR)는 제1전극이 상기 제2용량성소자(C2)의 제1전극 및 상기 제2스위칭소자(SW\_TR2)의 제2전극과 전기적으로 연결되고, 제2전극이 상기 유기 전계 발광 소자(OLED)의 애노드(Anode)전극과 전기적으로 연결되며, 제어 전극이 상기 제1스위칭소자(SW\_TR1)의 제2전극, 상기 제1용량성소자(C1)의 제2전극 및 상기 제2용량성소자(C2)의 제2전극과 전기적으로 연결될 수 있다. 이러한, 구동 트랜지스터(DR\_TR)는 P형 채널 트랜지스터일 수 있다. 동작으로는, 제어 전극을 통하여 로우 레벨의 신호가 인가되어 턴온되면, 상기 제1전원전압선(VDD)으로부터 일정량의 전류를 유기 전계 발광 소자(OLED) 쪽으로 공급하는 역할을 한다. 물론, 데이터 신호는 용량성 소자에 공급되어 그것을 충전시키므로, 상기 제1스위칭소자(SW\_TR1)가 턴오프되어 상기 데이터선(D[M])과의 전기적 연결관계가 끊어진다고 하여도 일정 기간동안은 용량성 소자에 충전된 전압에 의해 상기 구동 트랜지스터(DR\_TR)의 제어 전극에 로우 레벨의 신호가 계속 인가될 수 있다.

<167> 여기서 상기 구동 트랜지스터(DR\_TR)는 비정질 실리콘 박막 트랜지스터, 폴리 실리콘 박막 트랜지스터, 유기 박막 트랜지스터, 나노 박막 트랜지스터 및 그 등가물중 선택된 어느 하나일 수 있으나 여기서 그 재질 또는 종류를 한정하는 것은 아니다.

<168> 또한, 상기 구동 트랜지스터(DR\_TR)가 폴리 실리콘 박막 트랜지스터인 경우 결정화 방법으로는 엑시머 레이저(Excimer Laser)를 사용한 레이저 결정화 방법(ELA)과 금속촉매(Promoting Material)을 사용한 금속촉매 결정화 방법(MIC: Metal Induced Crystallization)과 고상결정화(SPC:Solid Phase Crystallization)방법, 고온 고습한 분위기에서 결정화를 진행하는 고압결정화 방법(HPA:High Pressure Annealing)방법 및 기존 레이저 결정화 방법에 마스크를 추가로 사용하는(SLS: Sequential Lateral Solidification)방법들이 있다.

<169> 또한 비정질 실리콘(a-Si)과 다결정 실리콘(Poly Silicon)사이의 결정립 크기를 가지는 마이크로 실리콘(micro Silicon)이 있다.

<170> 상기 마이크로 실리콘은 결정립의 크기가 1nm에서 100nm까지 인 것을 통상적으로 말한다. 상기 마이크로 실리콘의 전자이동도는 1에서 50이하이며 정공이동도는 0.01에서 0.2이하인 것인 특징이다. 상기 마이크로 실리콘은 상기 다결정 실리콘에 비해 결정립의 크기가 작은 것이 특징이며 폴리실리콘에 비해 결정립사이의 돌출부 영역이 작게 형성되어 결정립간에 전자가 이동할 경우에 지장을 주지 않게 되어 균일한 특성을 보여줄 수 있다. 상기 마이크로 실리콘의 결정립 방법에는 크게 열결정화 방법(Thermal Crystallization Method)와 레이저 결정화 방법(Laser Crystallization Method)가 있다. 상기 열결정화 방법은 비정질 실리콘을 증착함과 동시에 결정화구조를 얻는 방법과 재가열(Reheating)방법이 있다.

<171> 본 발명의 박막 트랜지스터(TFT)의 경우 상기의 결정화 방법들 및 그 등가 방법중 선택된 어느 하나의 방법으로 형성될 수 있으나, 본 발명에서 상기 폴리 실리콘 박막 트랜지스터의 제조 방법을 한정하는 것은 아니다.

- <172> 상기 레이저 결정화 방법은 박막트랜지스터를 다결정실리콘(Poly Silicon)으로 결정화 하는 방법중 가장 많이 이용되고 있다. 기존의 다결정 액정표시장치의 결정화 방법을 그대로 이용할 수 있을 뿐만 아니라 공정방법이 간단하며 공정방법에 대한 기술 개발이 완료된 상태이다.

- <173> 상기 금속촉매 결정화 방법은 상기 레이저 결정화 방법을 사용하지 않고 저온에서 결정화 할 수 방법중 하나이다. 초기에는 비정질 실리콘(a-Si)표면에 금속촉매금속인 Ni, Co, Pd, Ti등을 중착 혹은 스판코팅하여 상기 금속촉매 금속이 상기 비정질 실리콘 표면에 직접 침투하여 상기 비정질 실리콘의 상을 변화시키면서 결정화 하는 방법으로 저온에서 결정화 할 수 있는 장점이 있다.

- <174> 상기 금속촉매 결정화 방법의 다른 하나는 상기 비정질 실리콘 표면에 금속층을 개재시킬 때 마스크를 이용해 상기 박막트랜지스터의 특정 영역에 니켈실리사이드와 같은 오염물이 개재되는 최대한 억제할 수 있는 장점이 있다. 상기 결정화 방법을 금속촉매유도측면결정화 방법(MILC: Metal Induced Lateral Crystalization)이라고 한다. 상기 금속촉매유도측면결정화 방법에 사용되는 마스크로는 새도우 마스크(Shadow Mask)가 사용될 수 있는데 상기 새도우 마스크는 선형 마스크 혹은 점형 마스크일 수 있다.

- <175> 상기 금속촉매 결정화 방법의 또 다른 하나는 상기 비정질 실리콘 표면에 금속촉매층을 중착 혹은 스판코팅할 때 캡핑층(Capping Layer)을 먼저 개재시켜 상기 비정질 실리콘으로 유입되는 금속 촉매량을 컨트롤하는 금속촉매유도캡핑층결정화 방법(MICC: Metal Induced Crystalization with Capping Layer)이 있다. 상기 캡핑층으로는 실리콘질화막(Silicon Nitride)막을 사용할 수 있다. 상기 실리콘 질화막의 두께에 따라 상기 금속 촉매층에서 상기 비정질 실리콘으로 유입되는 금속 촉매량이 달라진다. 이때 상기 실리콘 질화막으로 유입되는 금속 촉매는 상기 실리콘 질화막 전체에 형성될 수 도 있고, 새도우 마스크등을 사용하여 선택적으로 형성될 수 있다. 상기 금속 촉매층이 상기 비정질 실리콘을 다결정 실리콘으로 결정화가 된 이후에 선택적으로 상기 캡핑층을 제거할 수 있다. 상기 캡핑층 제거방법에는 습식 식각방법(Wet Etching)방법 혹은 건식 식각방법(Dry Etching)을 사용할 수 있다. 추가적으로, 상기 다결정 실리콘이 형성된 이후에 게이트 절연막을 형성하고 상기 게이트 절연막 상에 게이트 전극을 형성한다. 상기 게이트 전극상에 층간절연막(Interlayer)을 형성할 수 있다. 상기 층간 절연막상에 비아홀(Via Hole)을 형성한 후에 불순물을 상기 비아홀을 통해서 결정화된 다결정실리콘 상으로 투입하여 내부의 형성된 금속촉매 불순물을 추가적으로 제거할 수 있다. 상기 금속 촉매 불순물을 추가적으로 제거하는 방법을 게터링 공정(Gatterring Process)라고 한다. 상기 게터링 공정에는 상기 불순물을 주입하는 공정외에 저온에서 박막트랜지스터를 가열하는 가열공정(Heating Process)가 있다. 상기 게터링 공정을 통해서 양질의 박막트랜지스터를 구현할 수 있다.

- <176> 더불어, 상기 금속촉매 결정화 방법에 의해 구동 트랜지스터(DR\_TR)가 제조되었을 경우, 상기 구동 트랜지스터(DR\_TR)에는 니켈(Ni), 카드늄(Cd), 코발트(Co), 티타늄(Ti), 팔라듐(Pd), 텉스텐(W), 알루미늄(Al) 및 그 등 가물중 선택된 어느 하나가 더 포함될 수 있다.

- <177> 상기 유기 전계 발광 소자(OLED)는 애노드(Anode)전극이 상기 구동 트랜지스터(DR\_TR)의 제2전극과 전기적으로 연결되고, 캐소드(Cathode)전극이 제2전원전압선(VSS)과 전기적으로 연결될 수 있다. 이러한, 유기 전계 발광 소자(OLED)는 상기 제2스위칭소자(SW\_TR2)가 턴온되어 있는 동안, 상기 구동 트랜지스터(DR\_TR)를 통하여 제어되는 전류에 의해 소정 밝기로 발광하는 역할을 한다.

- <178> 여기서, 상기 유기 전계 발광 소자(OLED)는 발광층(도시되지 않음)을 구비하고 있으며, 상기 발광층은 형광 재료, 인광 재료, 그 혼합물 및 그 등가물중 선택된 어느 하나일 수 있다. 그러나, 여기서 상기 발광층의 재질 또는 종류를 한정하는 것은 아니다.

- <179> 또한, 상기 발광층은 적색 발광 재료, 녹색 발광 재료, 청색 발광 재료, 그 혼합물질 및 그 등가물중 선택된 어느 하나일 수 있으나, 여기서 그 재질 또는 종류를 한정하는 것은 아니다.

- <180> 상기 제2스위칭소자(SW\_TR2)는 제1전극이 상기 제1전원전압선(VDD) 및 상기 제1용량성소자(C1)의 제1전극과 전기적으로 연결되고, 제2전극이 상기 제2용량성소자(C2)의 제1전극 및 상기 구동 트랜지스터(DR\_TR)의 제1전극과 전기적으로 연결되며, 제어 전극이 상기 발광 제어선(EM[N])에 전기적으로 연결될 수 있다. 이러한 제2스위칭소자(SW\_TR2)는 P형 채널 트랜지스터일 수 있으며, 상기 발광 제어선(EM[N])을 통하여 제어 전극에 로우 레벨의 신호가 인가되면 턴온 되어 상기 제1전원전압선(VDD)으로부터의 전류를 상기 유기 전계 발광 소자(OLED)로 흐르게 한다.

- <181> 상기 제1용량성소자(C1)는 제1전극이 상기 제1전원전압선(VDD) 및 상기 제2스위칭소자(SW\_TR2)의 제1전극과 전기적으로 연결되고, 제2전극이 상기 제2용량성소자(C2)의 제2전극, 상기 제1스위칭소자(SW\_TR1)의 제2전극 및

상기 구동 트랜지스터(DR\_TR)의 제어 전극과 전기적으로 연결될 수 있다.

<182> 상기 제2용량성소자(C2)는 제1전극이 상기 제2스위칭소자(SW\_TR2)의 제2전극 및 상기 구동 트랜지스터(DR\_TR)의 제1전극과 전기적으로 연결되고, 제2전극이 상기 제1용량성소자(C1)의 제2전극, 상기 제1스위칭소자(SW\_TR1)의 제2전극 및 상기구동 트랜지스터의 제어 전극과 전기적으로 연결될 수 있다.

<183> 이러한 용량성 소자는 데이터 신호 전압 및 구동 트랜지스터의 문턱 전압을 일정기간 유지하고, 상기 발광 제어 선(EM[N])에 의해 제2스위칭소자(SW\_TR2)의 제어 전극에 로우 레벨의 신호가 인가되어 턴온 되면 데이터 신호의 크기에 비례하는 전류를 상기 제1전원전압선으로부터 상기 유기 전계 발광 소자로 흐르게 하여 상기 유기 전계 발광 소자가 발광하게 한다. 또한, 상기 제1용량성소자 및 제2용량성소자의 비율(C1 : C2)을 다양하게 조절함으로써 하술할 IR-DROP 보상 또는 구동 트랜지스터의 문턱전압 보상등의 효과를 달성할 수 있다.

<184> 여기서, 상기 제1스위칭소자(SW\_TR1), 구동 트랜지스터(DR\_TR), 제2스위칭소자(SW\_TR2)는 모두 P형 채널 트랜지스터 및 그 등가물중 선택된 어느 하나일 수 있으나 여기서 그 트랜지스터의 종류를 한정하는 것은 아니다.

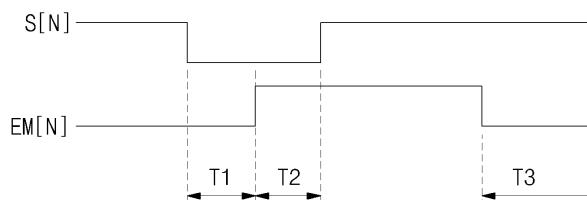

<185> 도 6을 참조하면, 도 5에 도시된 화소 회로의 구동 타이밍도가 도시 되어 있다. 도 6에 도시된 바와 같이 본 발명에 의한 유기 전계 발광 표시 장치의 화소 회로는 한 프레임이 제1기간, 제2기간 및 제3기간으로 구분될 수 있다. 좀 더 구체적으로, 한 프레임은 데이터 기입기간(T1), 구동 트랜지스터의 문턱전압 저장기간(T2) 및 발광 기간(T3)으로 이루어 질 수 있다. 상기 데이터 기입기간(T1) 및 구동 트랜지스터의 문턱전압 저장기간(T2)과 발광 기간(T3)의 비율은 다양하게 이루어 질 수 있으며, 바람직하게는, 발광 기간(T3)에 비해 상기 데이터 기입기간(T1) 및 구동 트랜지스터의 문턱전압 저장기간(T2)은 짧은 것이 좋다.

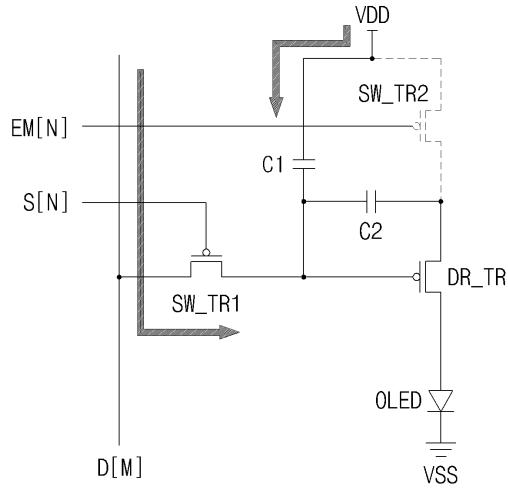

<186> 도 7을 참조하면, 도 5에 도시된 화소 회로에서 데이터 기입기간(T1)중 전류 흐름이 도시되어 있다. 여기서, 상기 화소 회로의 동작은 도 6의 타이밍도를 참조하여 설명한다.

<187> 먼저, 제1스위칭소자(SW\_TR1)의 제어 전극에 주사선(S[N])으로부터 로우 레벨의 주사 신호가 인가됨으로써 상기 제1스위칭소자(SW\_TR1)가 턴온 되고, 제2스위칭소자(SW\_TR2)의 제어 전극에 발광제어선(EM[N])의 로우 레벨의 신호가 인가됨으로써 상기 제2스위칭소자(SW\_TR2)가 턴온 된다.

<188> 상기 제1스위칭소자(SW\_TR1)가 턴온 됨에따라 데이터선(D[M])의 데이터 전압(Vdata)이 상기 제1스위칭소자(SW\_TR1)의 제1전극으로부터 제2전극 방향으로 인가되며, 따라서, 상기 제1스위칭소자(SW\_TR1)의 제2전극, 제1용량성소자(C1)의 제2전극, 제2용량성소자(C2)의 제2전극 및 구동 트랜지스터(DR\_TR)의 제어 전극에 상기 데이터 전압(Vdata)이 인가될 수 있다.

<189> 이때, 상기 제2스위칭소자(SW\_TR2)가 턴온 됨에따라 제1전원전압선(VDD)으로부터 제1전원전압이 상기 제2스위칭소자(SW\_TR2)의 제1전극으로부터 제2전극 방향으로 인가되며, 따라서, 상기 제2스위칭소자(SW\_TR2)의 제2전극, 상기 제2용량성소자(C2)의 제1전극 및 상기 구동 트랜지스터(DR\_TR)의 제1전극에 상기 제1전원전압이 인가될 수 있다.

<190> 또한, 상기 제1전원전압선(VDD)으로부터 제1전원전압은 상기 제1용량성소자(C1)의 제1전극에도 인가될 수 있다.

<191> 이 기간 동안에 상기 구동 트랜지스터(DR\_TR)는 턴오프된 상태로서 유기 전계 발광 소자(OLED)로 전류는 흐르지 않게 되므로 상기 유기 전계 발광 소자(OLED)는 발광 하지 않게 된다.

<192> 다시 말하자면, 데이터 기입기간(T1)동안 상기 구동 트랜지스터(DR\_TR)의 제어 전극(게이트 전극), 상기 제2용량성소자(C2)의 제2전극, 상기 제1용량성소자(C1)의 제2전극에 Vdata의 전압이 인가되고( $Vg=Vdata$ ), 상기 구동 트랜지스터(DR\_TR)의 제1전극(소스 전극), 상기 제2용량성소자(C2)의 제1전극 및 상기 제1용량성소자(C1)의 제1전극에 VDD의 전압이 인가된다( $Vs=VDD$ ). 따라서, 상기 용량성 소자들에 의해 제1전원전압(VDD)에서 데이터 전압(Vdata)을 뺀 값 만큼의 전압( $VDD-Vdata$ )이 일정 기간동안 저장된다.

<193> 도 8을 참조하면, 도 5에 도시된 화소 회로에서 구동 트랜지스터의 문턱전압 저장기간(T2)중 전류 흐름이 도시되어 있다. 여기서, 상기 화소 회로의 동작은 도 6의 타이밍도를 참조하여 설명한다.

<194> 먼저, 제1스위칭소자(SW\_TR1)의 제어 전극에 주사선(S[N])으로부터 로우 레벨의 주사 신호가 인가됨으로써 상기 제1스위칭소자(SW\_TR1)가 턴온 되고, 제2스위칭소자(SW\_TR2)의 제어 전극에 발광제어선(EM[N])의 하이 레벨의 신호가 인가됨으로써 상기 제2스위칭소자(SW\_TR2)가 턴오프 된다.

<195> 상기 제1스위칭소자(SW\_TR1)가 턴온 됨에따라 데이터선(D[M])의 데이터 전압(Vdata)이 상기 제1스위칭소자(SW\_TR1)의 제1전극으로부터 제2전극 방향으로 인가되며, 따라서, 상기 제1스위칭소자(SW\_TR1)의 제2전극, 제1

용량성소자(C1)의 제2전극, 제2용량성소자(C2)의 제2전극 및 구동 트랜지스터(DR\_TR)의 제어 전극에 상기 데이터 전압(Vdata)이 인가될 수 있다.

<196> 이때, 상기 제2스위칭소자(SW\_TR2)가 턴오프 됨에따라 제1전원전압선(VDD)으로 부터의 제1전원전압은 상기 제1용량성소자(C1)의 제1전극에만 인가 될 수 있다.

<197> 이 기간 동안에 상기 구동 트랜지스터(DR\_TR)는 턴오프된 상태로서 유기 전계 발광 소자(OLED)로 전류는 흐르지 않게 되므로 상기 유기 전계 발광 소자(OLED)는 발광 하지 않게 된다.

<198> 다시 말하자면, 구동 트래지스터의 문턱전압 저장기간(T2)동안 상기 구동 트랜지스터(DR\_TR)의 제어 전극(케이트 전극), 상기 제2용량성소자(C2)의 제2전극, 상기 제1용량성소자(C1)의 제2전극에 Vdata의 전압이 인가되고 (Vg=Vdata), 상기 제1용량성소자(C1)의 제1전극에 VDD의 전압이 인가된다. 따라서, 상기 제1용량성소자(C1)에는 상기 제1전원전압(VDD)에서 상기 데이터 전압을 뺀 값(VDD-Vdata)이 일정 기간동안 저장된다.

<199> 이 때, 상기 구동 트랜지스터(DR\_TR)의 제1전극(소스 전극)의 전압(Vs)은 데이터 전압(Vdata)에 상기 구동 트랜지스터(DR\_TR)의 문턱전압(Vth)을 더한 값으로서(Vs=Vdata+Vth), 상기 제2용량성소자(C2)에는 상기 구동 트랜지스터(DR\_TR)의 제1전극전압(소스전극전압,Vs=Vdata+Vth)에서 상기 구동 트랜지스터(DR\_TR)의 제어전극전압(케이트 전극전압, Vg=Vdata)을 뺀 값(Vth)이 일정 기간동안 저장된다.

<200> 도 6의 구동 타이밍도를 참조하면, 제2기간(T2)과 제3기간(T3) 사이에는 제1스위칭소자(SW\_TR1)의 제어 전극에 주사선(S[N])으로부터 하이 레벨의 신호가 인가됨으로써 상기 제1스위칭소자(SW\_TR1)가 턴오프 되고, 제2스위칭소자(SW\_TR2)의 제어 전극에 발광제어선(EM[N])으로부터 하이 레벨의 신호가 인가됨으로써 상기 제2스위칭소자(SW\_TR2)가 턴오프 된다.

<201> 따라서, 이 기간동안에는 상기 제2기간(T2)동안 상기 용량성소자에 저장되었던 전압값이 그대로 유지된다.

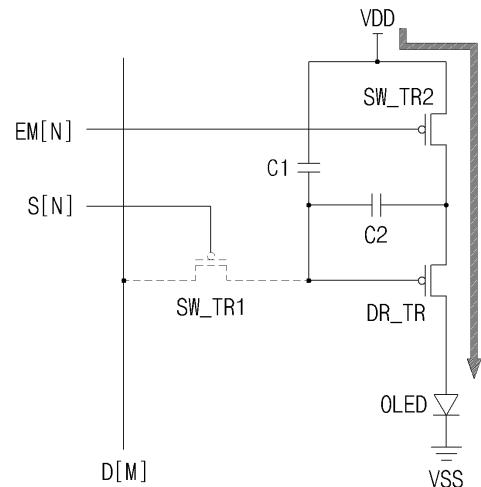

<202> 도 9를 참조하면, 도 5에 도시된 화소 회로에서 발광기간(T3)중 전류 흐름이 도시되어 있다. 여기서, 상기 화소 회로의 동작은 도 6의 구동 타이밍도를 참조하여 설명한다.

<203> 먼저, 제1스위칭소자(SW\_TR1)의 제어 전극에 주사선(S[N])으로부터 하이 레벨의 신호가 인가됨으로써 상기 제1스위칭소자(SW\_TR1)가 턴오프 되고, 제2스위칭소자(SW\_TR2)의 제어 전극에 발광제어선(EM[N])의 로우 레벨의 신호가 인가됨으로써 상기 제2스위칭소자(SW\_TR2)가 턴온 된다.

<204> 상기 제1스위칭소자(SW\_TR1)가 턴오프 됨에따라 데이터선(D[M])의 데이터 전압(Vdata)이 더이상 화소 회로로 인가될 수 없게 된다.

<205> 이때, 상기 제2스위칭소자(SW\_TR2)가 턴온 됨에 따라 제1전원전압선(VDD)으로부터 제1전원전압이 상기 제2스위칭소자(SW\_TR2)의 제1전극으로부터 제2전극 방향으로 인가되며, 따라서 구동 트랜지스터(DR\_TR)의 제1전극(소스 전극)에 상기 제1전원전압이 인가될 수 있다. 이러한 제1전원전압(VDD)에 의한 전류는 발광기간(T3)중 제2전원전압선(VSS)의 방향으로 유기 전계 발광 소자(OLED)를 통하여 흐를 수 있게 되어 상기 유기 전계 발광 소자(OLED)를 발광할 수 있게 한다.

<206> 이러한, 발광기간(T3)중 상기 구동 트랜지스터(DR\_TR)의 제1전극(소스 전극)의 전압(Vs)은 VDD가 되며, 상기 구동 트랜지스터(DR\_TR)의 제어 전극(케이트 전극)의 전압(Vg) 및 상기 구동 트랜지스터(DR\_TR)의 소스-케이트간 전압(Vsg)는 하기할 수학식 1과 같이 될 수 있다.

## 수학식 1

$$<207> V_g = V_{data} + \left( \frac{C2}{C1+C2} \right) * (VDD - V_{data} - Vth)$$

$$<208> V_s = VDD$$

$$<209> V_{sg} = V_s - V_g$$

$$V_{sg} = VDD - [V_{data} + \left(\frac{C2}{C1+C2}\right) * (VDD - V_{data} - Vth)]$$

&lt;210&gt;

&lt;211&gt;

이때, 유기 전계 발광 소자(OLED)에 흐르는 전류는 하기할 수학식 2와 같이 될 수 있다.

## 수학식 2

$$I_{OLED} = \frac{\beta}{2} * (V_{sg} - |Vth|)^2$$

&lt;212&gt;

&lt;213&gt;

즉, 본 발명은 제2기간(T2)동안 제2용량성소자(C2)에 구동 트랜지스터(DR\_TR)의 문턱전압(Vth)을 저장한 후, 발광기간(T3)동안 데이터 전압(Vdata) 및 C1과 C2의 비에 의해 데이터를 표현하는 방법을 특징으로 한다.

&lt;214&gt;

이때, 최적의 C1과 C2 비율은 각각의 화소 회로에 포함된 구동 트랜지스터의 문턱전압(Vth)의 산포에 따라 달라지게 된다. 예를 들면, 유기 전계 발광 표시 장치의 패널(panel)에서 문턱전압(Vth)의 산포가 0.1V이면 화질의 문제가 없다고 할 수 있는데, 공정의 문턱전압(Vth)의 산포가 0.5V인 경우라면 화질상의 문제가 발생할 수 있다. 위의 경우 C1과 C2의 비율을 1대 5로 하면(C1 : C2 = 1: 5), 공정의 문턱전압(Vth)의 산포는 0.5V이라 하더라도 패널에서 느끼는 문턱전압(Vth) 산포는 0.1V보다 작게 되어 화질의 문제가 없게 될 수 있다.

&lt;215&gt;

만약, C2의 값을 C1의 값보다 크게 하는 경우( $C2 > C1$ )  $C2/(C1+C2)$ 는 근사하여 1이 될 수 있다. 이 경우, 상기 수학식 1의  $V_{sg}$ 의 값은  $Vth$ 만 남게 된다. 그리고, 이 값을 상기 수학식 2의  $I_{OLED}$  대입하여 생각하여 보면, 유기 전계 발광 소자(OLED)에 흐르는 전류에 구동 트랜지스터의 문턱전압(Vth) 값이 보상될 수 있다.

&lt;216&gt;

다만, C2의 값이 C1의 값보다 매우 커서  $C2/(C1+C2)$ 가 1이 된다면,  $V_{sg}$ 는  $Vth$ 가 되고, 이 경우 데이터 전압(Vdata)이 아무리 바뀌어도 구동 트랜지스터(DR\_TR)의  $V_{sg}$ 는  $Vth$ 이고, 수학식 2에서 볼 수 있듯이 유기 전계 발광 소자의 전류식에 데이터 전압(Vdata)이 나타나지 않게되어, 데이터 전압(Vdata)에 따라 원하는 전류를 발생시킬 수 없게 된다는 문제가 있다. 즉, 이 말은 데이터 범위(data range)가 무한대로 늘어난다는 것을 의미한다. 그렇다고 하여, C1의 값을 C2의 값보다 매우 크게 조정하면  $C2/(C1+C2)$ 가 근사적으로 0이되어 수학식 1의  $V_{sg}$ 는  $VDD - Vdata$ 가 되고, 이 경우 데이터 전압(Vdata)에 따라 원하는 전류를 발생시킬 수는 있으나 구동 트랜지스터(DR\_TR)의 문턱전압(Vth) 보상이나, 제1전원전압선(VDD)의 전압강하(IR-DROP) 보상이 제대로 되지 않을 수 있다.

&lt;217&gt;

다시 말하자면, 본 발명에 의한 유기 전계 발광 표시 장치는 C1과 C2의 비를 적절히 조절함으로써 구동 트랜지스터(DR\_TR)의 문턱전압(Vth) 및 제1전원전압선(VDD)에 의한 전압강하(IR-DROP)을 보상할 수 있다.

&lt;218&gt;

예를 들어,  $C2/(C1+C2)$ 가 0.5라고 한다면  $V_{sg} = VDD - Vdata - 0.5VDD + 0.5Vdata + 0.5Vth$ 가 되어 데이터 범위(data range)는 2배 증가 하고, 구동 트랜지스터(DR\_TR)의 문턱전압(Vth) 및 제1전원전압선(VDD)의 전압강하(IR-DROP)의 영향은 반으로 감소시킬 수 있다. 즉, 바람직하게는 C2의 값을 C1의 값보다 크게 조정하여 구동 트랜지스터(DR\_TR)의 문턱전압(Vth) 및 제1전원전압선(VDD)의 전압강하(IR-DROP)의 영향을 최소화 시킬 수 있다.

&lt;219&gt;

또한, 종래의 구동 트랜지스터의 문턱전압 및 제1전원전압선의 전압강하 보상을 위한 회로들은 본 발명에 따른 화소 회로보다 더 많은 수의 소자를 필요로 하여 고집적화의 어려움이 있을 수 있었다. 그러나 본 발명에 의한 화소 회로의 경우 3개의 트랜지스터와 2개의 용량성소자로만 구성됨으로써 고집적화를 이를 수 있으며, 이에 따라, 고해상도의 유기 전계 발광 표시 장치를 구현할 수 있다.

&lt;220&gt;

아울러, 일반적으로 구동 트랜지스터의 문턱전압을 보상하는 회로의 경우 상기 구동 트랜지스터의 제어 전극(게이트 전극)으로부터 네거티브(Negative)전원쪽으로의 패쓰(Path)가 형성되어 누설 전류(Leakage current)가 흐를 수 있게 된다. 여기서 누설 전류(구동 트랜지스터의 off current)가 클 경우에는 검은색 이미지(Black image)를 표현해야 하는데도 불구하고 누설전류(Leakage current)가 유기 전계 발광 소자(OLED)로 유입되어 부적절한 발광이 일어날 수 있다. 패널내에서 구동 트랜지스터가 갖는 누설(Leakage) 특성이 모두 다르기 때문에 검은색 이미지(Black image)를 표현해야 할 경우 인데도 불구하고 누설(Leakage)특성이 큰 몇몇의 화소는 발광하게 될 수 있다. 이러한 현상은 구동 트랜지스터에 리버스 에이징(Reverse aging)을 가하면 구동 트랜지스터의 누설 전류(Leakage current)가 감소되어 상술한 부적절한 발광 현상을 감소시킬 수 있다. 하지만, 본 발명에 따른 화소 회로의 경우 3개의 트랜지스터와 2개의 용량성 소자로 구성된 경우로서, 구동 트랜지스터의 제어 전극

으로 부터 네거티브 전원쪽으로 누설전류(Leakage current)가 흐를수 있는 패쓰(Path)가 존재하지 않기 때문에 상술한 구동 트랜지스터의 리버스 에이징(Reverse aging)을 가할 필요가 없게 된다.

<221> 상기 데이터 기입기간(T1) 및 구동 트랜지스터의 문턱전압 저장기간(T2)은 상기 발광 기간(T3)보다 짧도록 하여 상기 유기 전계 발광 소자(OLED)가 발광 되는 시간이 길도록 하는 것이 바람직하다.

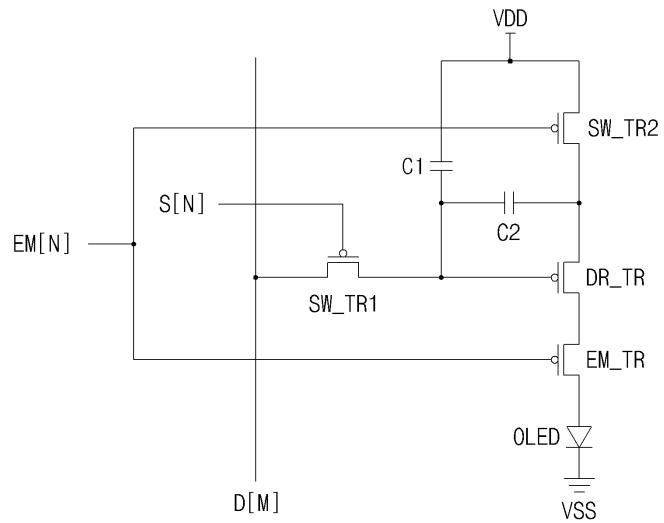

<222> 도 10을 참조하면, 본 발명의 유기 전계 발광 표시 장치의 다른 실시예에 따른 화소 회로가 도시되어 있다. 도 10에 도시된 화소 회로는 도 5에 도시된 화소 회로와 유사하다. 다만, 도 10에 도시된 화소 회로에서는 도 5에 도시된 화소 회로에 발광제어 스위칭소자(EM\_TR)가 더 포함되어 있다.

<223> 상기 발광제어 스위칭소자(EM\_TR)는 제어 전극이 발광제어선(EM[N])과 전기적으로 연결되어 있고, 제1전극이 구동 트랜지스터의 제2전극과 전기적으로 연결되어 있으며, 제2전극이 유기 전계 발광 소자(OLED)의 애노드전극과 전기적으로 연결되어 있다. 이러한 발광 제어 트랜지스터는 제1전원전압선(VDD)에서 제2전원전압선(VSS) 방향으로 상기 유기 전계 발광 소자(OLED)를 통하여 흐르는 전류를 제어할 수 있다. 즉, 발광 기간(T3)중 발광 제어선(EM[N])으로 부터 상기 발광 제어 스위칭소자(EM\_TR)의 제어 전극에 로우 레벨의 신호가 인가되면, 상기 발광 제어 스위칭소자(EM\_TR)는 턴온 되고, 이에 따라 상기 유기 전계 발광 소자(OLED)를 통하여 상기 제1전원전압선(VDD)으로부터 상기 제2전원전압선(VSS) 방향으로 흐르는 전류를 통해 상기 유기 전계 발광 소자(OLED)는 발광 할 수 있게 된다.

<224> 상기 발광제어 스위칭소자(EM\_TR)는 도 10에 도시된 바와 같이 P형 채널 트랜지스터를 이용할 수 있다.

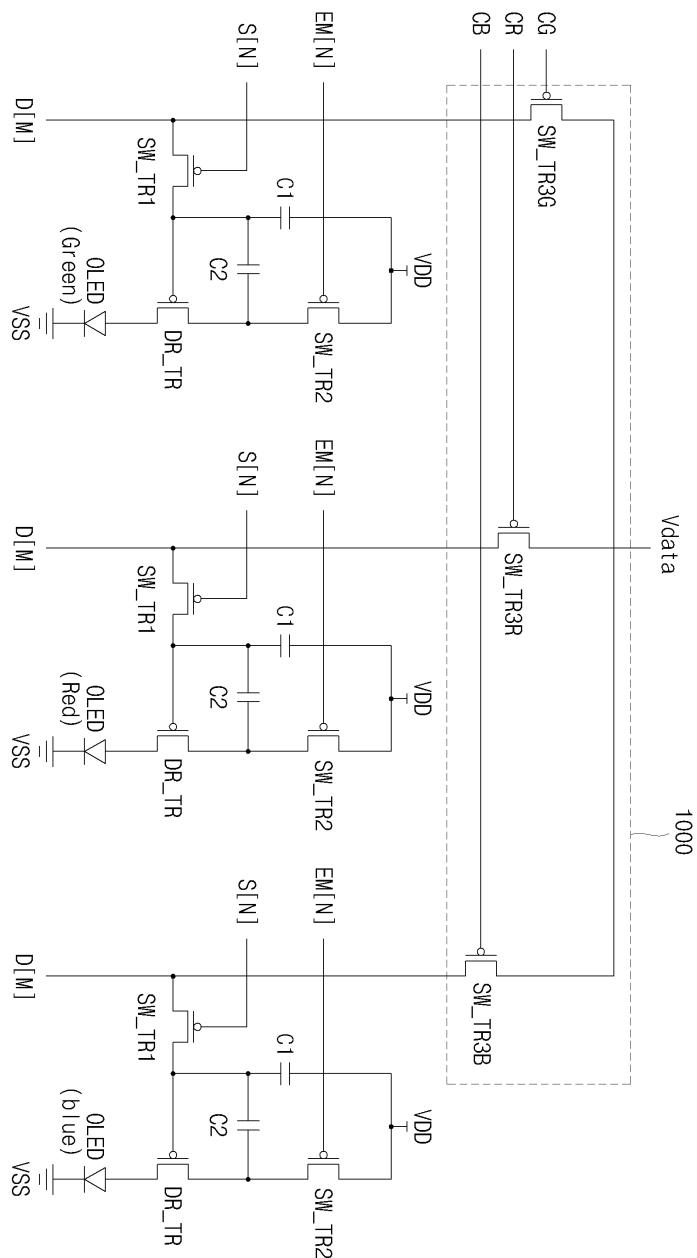

<225> 도 11을 참조하면, 본 발명의 알지비(RGB)화소회로들과 디멀티플렉서의 일실시예에 따른 전기적 연결관계가 도시되어 있다.

<226> 본 발명에서 말하는 디멀티플렉서(1000)는 유기 전계 발광 표시 장치의 데이터 신호 구동부에 있어서 알지비(RGB)데이터신호 각각에 대한 레이아웃 구조를 갖는 디멀티플렉서이다.

<227> 최근에 고해상도가 요구되는 추세에 따라 유기 전계 발광 표시 장치의 데이터라인이 증가되고, 이를 구동하는 데이터 신호 구동부에는 더 많은 집적 회로(Integrated Circuit)들이 포함된다. 이러한 문제를 해결하기 위하여 데이터 신호 구동부의 출력선 수가 감소되는 디멀티플렉서가 사용되고 있다. 디멀티플렉서는 데이터 신호 구동부의 출력선에 공통으로 연결되는 다수의 데이터 신호 공급용 스위칭소자를 포함하며, 이러한 데이터 신호 공급 용 스위칭소자들은 각각 정해진 데이터라인과 전기적으로 연결되어 있다. 이에 따라, 디멀티플렉서는 데이터 신호 공급용 스위칭소자의 동작을 통하여 각각의 데이터 라인에 순차적으로 데이터 신호를 공급하게 된다.

<228> 여기서 알지비(RGB)는 레드(Red, R), 그린(Green, G) 및 블루(Blue, B)를 의미한다. 도 11에는 상기 디멀티플렉서(1000)에 화소 회로 3개가 전기적으로 연결되어 있으나, 상기 개수로 본 발명을 한정하는 것은 아니다. 또한, 다수의 디멀티플렉서를 사용하여 데이터신호를 화소회로들에 인가할 수 있으며, 사용되는 디멀티플렉서의 개수로 본 발명을 한정하는 것은 아니다.

<229> 상기 디멀티플렉서(1000)를 살펴보면, 각각 레드(Red)데이터선, 그린(Green)데이터선 및 블루(Blue)데이터선이 각각의 화소 회로들의 데이터선(D[M])과 전기적으로 연결되어 있다. 또한, 각각의 알지비(RGB)데이터선에는 알지비(RGB)스위칭소자(SW\_TR3)가 전기적으로 연결되어 있다. 상기 스위칭소자는 다시 레드(Red)데이터선 스위칭소자(SW\_TR3R), 그린(Green)데이터선 스위칭소자(SW\_TR3G) 및 블루(Blue)데이터선 스위칭소자(SW\_TR3B)로 이루어질 수 있다. 상기 알지비(RGB)스위칭소자들의 제어 전극에는 각각 알지비(RGB)제어선(CR, CG, CB)들을 통하여 알지비(RGB)제어신호들이 인가될 수 있다.

<230> 이러한 알지비(RGB)제어신호(CR, CG, CB)들에 의해 상기 알지비(RGB)스위칭소자가 턴온 되면, 상기 데이터 신호 구동부로부터 디멀티플렉서를 통하여 각각의 알지비(RGB)화소회로에 알맞은 데이터 신호(전압)이 인가될 수 있다.

<231> 상기 알지비(RGB)스위칭소자들은 P형 채널 트랜지스터일 수 있으나, 상기 트랜지스터의 종류로 본 발명을 한정하는 것은 아니다.

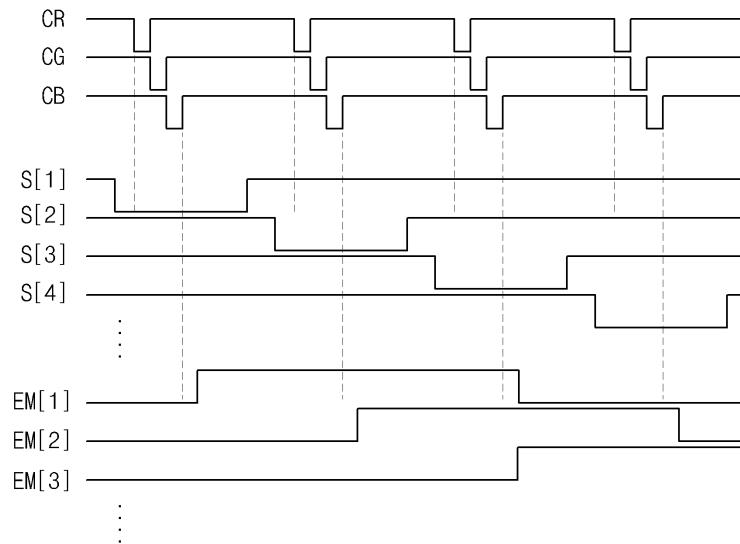

<232> 도 12 및 도 13을 참조하면, 도 11에서 도시한 본 발명의 알지비(RGB) 화소 회로들의 일실시에 및 다른 실시예에 따른 구동 타이밍도가 도시되어 있다.

<233> 먼저, 도 12의 구동 타이밍도를 참조하여 도 11에 도시된 본 발명에 따른 알지비(RGB)화소회로들의 동작을 설명하도록 한다.

- <234> 주사선(S[N])을 통해 로우 레벨의 주사신호가 인가되면 알지비(RGB)화소회로들의 각 제1스위칭소자(SW\_TR1)는 턴온 되며, 발광제어선(EM[N])을 통해 로우 레벨의 발광제어신호가 인가되면 알지비(RGB)화소회로들의 각 제2스위칭소자(SW\_TR2)는 턴온 될 수 있다.

- <235> 이렇듯, 도 12에 도시된 본 발명의 일 실시예에 따른 유기 전계 발광 표시 장치의 구동 방법은 상술한바와 같이, 상기 주사신호 및 발광제어신호가 로우 레벨인 기간동안 알지비(RGB)제어선(CR, CG, CB)들을 통하여 로우 레벨의 신호를 인가하여 알지비(RGB)스위칭소자(SW\_TR3)들을 턴온 시키는 것이다. 따라서, 상기 기간동안 알지비(RGB)데이터신호가 인가될 수 있게 된다.

- <236> 물론 도 11에 도시된 바와 같이 P형 채널 트랜지스터를 사용하는 경우에는, 로우 레벨의 신호가 인가되는 경우 턴온 되는바, 상기와 같이 설명하였으나, N형 채널 트랜지스터들을 사용하는 경우에는 하이 레벨의 신호가 인가될 때 턴온 되는 등, 구동 타이밍도가 상이할 수 있으며, 트랜지스터의 종류 및 구동 타이밍도로서 본 발명의 기술적 사상을 한정하는 것은 아니다.

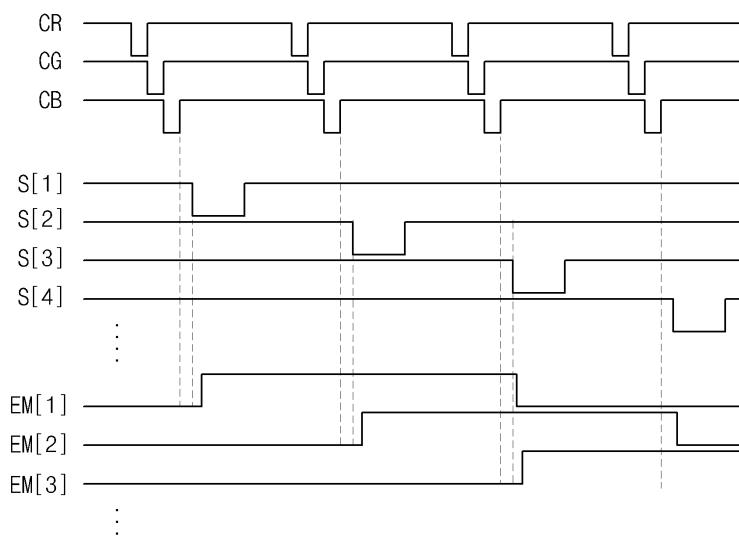

- <237> 다음으로, 도 13의 구동 타이밍도를 참조하여 도 11에 도시된 본 발명에 따른 알지비(RGB)화소회로들의 동작을 설명하도록 한다.

- <238> 주사선(S[N])을 통해 하이 레벨의 주사신호가 인가되면 알지비(RGB)화소회로들의 각 제1스위칭소자(SW\_TR1)는 턴오프 되며, 발광제어선(EM[N])을 통해 로우 레벨의 발광제어신호가 인가되면 알지비(RGB)화소회로들의 각 제2스위칭소자(SW\_TR2)는 턴온될 수 있다.

- <239> 이렇듯, 도 13에 도시된 본 발명의 다른 실시예에 따른 유기 전계 발광 표시 장치의 구동방법은 상술한바와 같이, 상기 주사신호가 하이 레벨이고, 상기 발광제어신호가 로우 레벨인 기간 동안 알지비(RGB)제어선(CR, CG, CB)들을 통하여 로우 레벨의 신호를 인가하여 알지비(RGB)스위칭소자(SW\_TR3)들을 턴온시키는 것이다. 따라서, 상기 기간동안 알지비(RGB)데이터신호가 인가될 수 있게 된다.

- <240> 물론, 하이 레벨의 주사신호가 화소 회로의 제1스위칭소자(SW\_TR1)의 제어 전극에 인가되는 경우, 상기 제1스위칭소자(SW\_TR1)는 턴오프 되게 된다. 따라서, 턴오프의 주사신호가 인가되는 기간 동안에는 알지비(RGB)데이터신호가 상기 화소 회로의 용량성소자에 즉각적으로 인가될 수 없다. 다만, 상기 데이터선(D[M])들에 형성되는 기생 캐패시터(Cd)에 의해 데이터신호(전압)를 충전한 이후, 턴온의 주사신호가 상기 화소 회로의 제1스위칭소자(SW\_TR1)의 제어 전극에 인가되어 상기 제1스위칭소자(SW\_TR1)가 턴온되면 상기 제1스위칭소자(SW\_TR1)를 통하여 상기 데이터선(D[M])들에 형성되는 기생 캐패시터(Cd)에 의해 충전된 데이터 신호들이 인가될 수 있다. 상기 기생 캐패시턴스(Cd)는 화소 회로내의 제1용량성소자(C1) 및 제2용량성소자(C2)의 캐패시턴스 보다 클 수 있다.

- <241> 물론 도 11에 도시된 바와 같이 P형 채널 트랜지스터를 사용하는 경우에는 로우 레벨의 신호가 인가되는 경우 턴온 되는바, 상기와 같이 설명하였으나, N형 채널 트랜지스터들을 사용하는 경우에는 하이 레벨의 신호가 인가될 때 턴온 되는 등, 구동 타이밍도가 상이할 수 있으며, 트랜지스터의 종류 및 구동 타이밍도로서 본 발명의 기술적 사상을 한정하는 것은 아니다.

- <242> 상술한 바와 같이, 상기 주사선(S[N])으로부터 로우 레벨의 신호 또는 하이 레벨의 신호가 인가되는가에 상관없이 상기 발광제어선(EM[N])으로부터 로우 레벨의 신호가 인가되는 기간 동안 상기 알지비(RGB)제어선(CR, CR, CB)들을 통하여 로우 레벨의 신호를 인가하여 알지비(RGB)스위칭소자(SW\_TR3)들을 턴온시키는 이유는, 상기 발광 제어선(EM[N])으로부터 로우 레벨의 신호가 인가되어 화소회로들의 제2스위칭소자(SW\_TR2)들이 턴온되어야 이전 데이터전압을 저장하고 있던 용량성소자들이 제1전원전압선(VDD)과 전기적으로 연결되어 초기화 될 수 있기 때문이다. 이렇듯 상기 용량성소자들이 초기화 된 후에 새로운 알지비(RGB)데이터신호들을 인가하여 상기 용량성소자들에 올바른 데이터를 기입할 수 있게 하는 것에 본 발명의 특징이 있다.

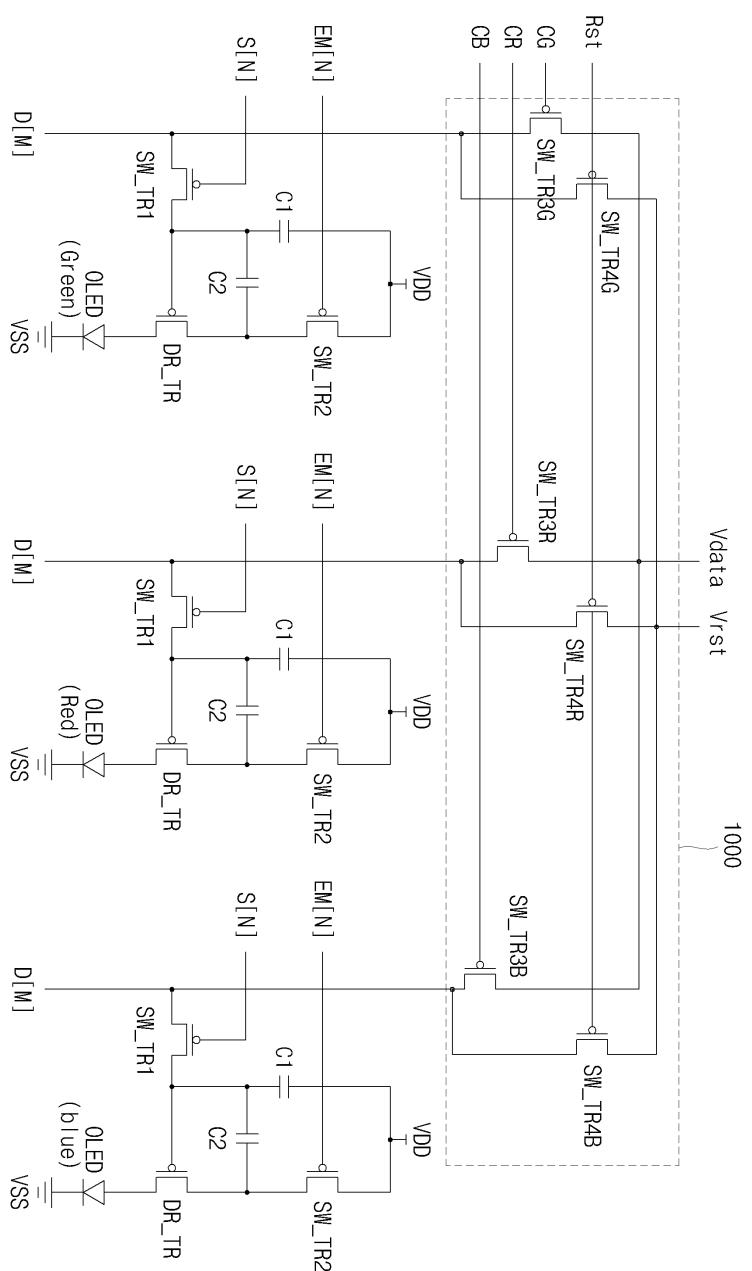

- <243> 도 14를 참조하면, 본 발명의 알지비(RGB)화소회로들과 디멀티플렉서의 다른 실시예에 따른 전기적 연결관계가 도시되어 있다.

- <244> 본 발명에서 말하는 디멀티플렉서(1000)는 유기 전계 발광 표시 장치의 데이터 신호 구동부에 있어서 알지비(RGB)데이터신호 각각에 대한 레이아웃 구조를 갖는 디멀티플렉서로서 도 11에 도시한 디멀티플렉서와 대부분 동일하나 초기화전원선(Vrst)과 상기 초기화전원전압선(Vrst)과 알지비(RGB)데이터 전압선을 전기적으로 연결하는 초기화스위칭소자(SW\_TR4)가 포함된다는 점이 다르다.

- <245> 도 14 에서는 상기 디멀티플렉서(1000)에 화소 회로 3개가 전기적으로 연결되어 있으나, 상기 개수로 본 발명을

한정하는 것은 아니다. 또한, 다수의 디멀티플렉서를 사용하여 데이터신호를 화소회로들에 인가할 수 있으며, 사용되는 디멀티플렉서의 개수로 본 발명을 한정하는 것은 아니다.

<246> 도 14에 도시된 디멀티플렉서(1000)를 살펴보면, 각각 레드(Red)데이터선, 그린(Green)데이터선 및 블루(Blue)데이터선이 각각의 화소 회로들의 데이터선(D[M])과 전기적으로 연결되어 있다. 또한, 각각의 알지비(RGB)데이터선에는 알지비(RGB)스위칭소자(SW\_TR3)가 전기적으로 연결되어 있다. 상기 스위칭소자는 다시 레드(R)데이터선 스위칭소자(SW\_TR3R), 그린(G)데이터선 스위칭소자(SW\_TR3G) 및 블루 데이터선 스위칭소자(SW\_TR3B)로 이루어질 수 있다. 상기 알지비(RGB)스위칭소자들의 제어 전극에는 각각 알지비(RGB)제어선(CR, CG, CB)들을 통하여 알지비(RGB)제어신호들이 인가될 수 있다.

<247> 이러한 알지비(RGB)제어신호(CR, CG, CB)들에 의해 상기 알지비(RGB)스위칭소자가 턴온 되면, 상기 데이터 신호 구동부로부터 디멀티플렉서를 통하여 각각의 알지비(RGB) 제어신호(CR, CG, CB)들에 의해 상기 알지비(RGB) 스위칭소자가 턴온 되면, 상기 데이터 신호 구동부로부터 디멀티플렉서를 통하여 각각의 알지비(RGB)화소회로에 알맞은 데이터 신호(전압)이 인가될 수 있다.

<248> 또한, 초기화전원압선(Vrst)은 초기화스위칭소자(SW\_TR4)를 통하여 각각의 알지비(RGB)데이터선에 전기적으로 연결되어 있다. 상기 초기화스위칭소자(SW\_TR4)에 턴온의 초기화신호(Rst)가 인가되면, 상기 초기화스위칭소자들(SW\_TR4G, SW\_TR4R, SW\_TR4B)은 턴온 되며 상기 초기화전원전압선(Vrst)으로부터 각각의 알지비(RGB)데이터선으로 초기화전원전압이 인가될 수 있다. 상기 초기화전원전압이 인가됨에 따라 상기 알지비(RGB)데이터선들에 인가되었던 이전 데이터전압들이 초기화되며, 새로운 알지비(RGB)데이터신호(전압)들이 인가될 수 있다.

<249> 상기 알지비(RGB)스위칭소자 및 상기 초기화전원전압은 P형 채널 트랜지스터일 수 있으나, 상기 트랜지스터의 종류로 본 발명을 한정하는 것은 아니다.

<250> 상기 도 11에 도시된 알지비(RGB)스위칭소자(SW\_TR3) 및 도 14에 도시된 초기화스위칭소자(SW\_TR4)로는 박막 트랜지스터(Thin Film Transistor; TFT)를 사용할 수 있고, 상기 박막트랜지스터의 결정화 방법으로는 액시머 레이저(Excimer Laser)를 사용한 레이저 결정화 방법(ELA)과 금속촉매(Promoting Material)을 사용한 금속촉매 결정화 방법(MIC: Metal Induced Crystalization)과 고상결정화(SPC:Solid Phase Crystalization)방법등이 있다. 이외에도 고온 고습한 분위기에서 결정화를 진행하는 고압결정화 방법(HPA:High Pressure Annealing)방법, 기존 레이저 결정화 방법에 마스크를 추가로 사용하는(SLS: Sequential Lateral Solidification)방법들이 있다.

<251> 상기 레이저 결정화 방법은 박막트랜지스터를 다결정실리콘(Poly Silicon)으로 결정화 하는 방법중 가장 많이 이용되고 있다. 기존의 다결정 액정표시장치의 결정화 방법을 그대로 이용할 수 있을 뿐만 아니라 공정방법이 간단하며 공정방법에 대한 기술 개발이 완료된 상태이다.

<252> 상기 금속촉매 결정화 방법은 상기 레이저 결정화 방법을 사용하지 않고 저온에서 결정화 할 수 방법중 하나이다. 초기에는 비정질 실리콘(a-Si)표면에 금속촉매금속인 Ni, Co, Pd, Ti등을 증착 혹은 스팍코팅하여 상기 금속촉매 금속이 상기 비정질 실리콘 표면에 직접 침투하여 상기 비정질 실리콘의 상을 변화시키면서 결정화 하는 방법으로 저온에서 결정화 할 수 있는 장점이 있다.

<253> 상기 금속촉매 결정화 방법의 다른 하나는 상기 비정질 실리콘 표면에 금속층을 개재시킬 때 마스크를 이용해 상기 박막트랜지스터의 특정 영역에 니켈실리사이드와 같은 오염물이 개재되는 최대한 억제할 수 있는 장점이 있다. 상기 결정화 방법을 금속촉매유도측면결정화 방법(MILC: Metal Induced Lateral Crystalization)이라고 한다. 상기 금속촉매유도측면결정화 방법에 사용되는 마스크로는 새도우 마스크(Shadow Mask)마스크가 사용될 수 있는데 상기 새도우 마스크는 선형 마스크 혹은 점형 마스크일 수 있다.

<254> 상기 금속촉매 결정화 방법의 또 다른 하나는 상기 비정질 실리콘 표면에 금속촉매층을 증착 혹은 스팍코팅할 때 캡핑층(Capping Layer)을 먼저 개재시켜 상기 비정질 실리콘으로 유입되는 금속 촉매량을 컨트롤하는 금속촉매유도캡핑층결정화 방법(MICC: Metal Induced Crystalization with Capping Layer)이 있다. 상기 캡핑층으로는 실리콘질화막(Silicon Nitride)막을 사용할 수 있다. 상기 실리콘 질화막의 두께에 따라 상기 금속 촉매층에서 상기 비정질 실리콘으로 유입되는 금속 촉매량이 달라진다. 이때 상기 실리콘 질화막으로 유입되는 금속 촉매는 상기 실리콘 질화막 전체에 형성될 수 도 있고, 새도우 마스크등을 사용하여 선택적으로 형성될 수 있다. 상기 금속 촉매층이 상기 비정질 실리콘을 다결정 실리콘으로 결정화가 된 이후에 선택적으로 상기 캡핑층을 제거할 수 있다. 상기 캡핑층 제거방법에는 습식 식각방법(Wet Etching)방법 혹은 건식 식각방법(Dry Etching)을 사용 할 수 있다. 추가적으로, 상기 다결정 실리콘의 형성된 이후에 게이트 절연막을 형성하고 상기 게이트 절연막

상에 게이트 전극을 형성한다. 상기 게이트 전극상에 층간절연막(Interlayer)을 형성할 수 있다. 상기 층간 절연막상에 비아홀(Via Hole)을 형성한 후에 불순물을 상기 비아홀을 통해서 결정화된 다결정실리콘 상으로 투입하여 내부의 형성된 금속촉매 불순물을 추가적으로 제거할 수 있다. 상기 금속 촉매 불순물을 추가적으로 제거하는 방법을 게터링 공정(Gattering Process)라고 한다. 상기 게터링 공정에는 상기 불순물을 주입하는 공정외에 저온에서 박막트랜지스터를 가열하는 가열공정(Heating Process)가 있다. 상기 게터링 공정을 통해서 양질의 박막트랜지스터를 구현할 수 있다.

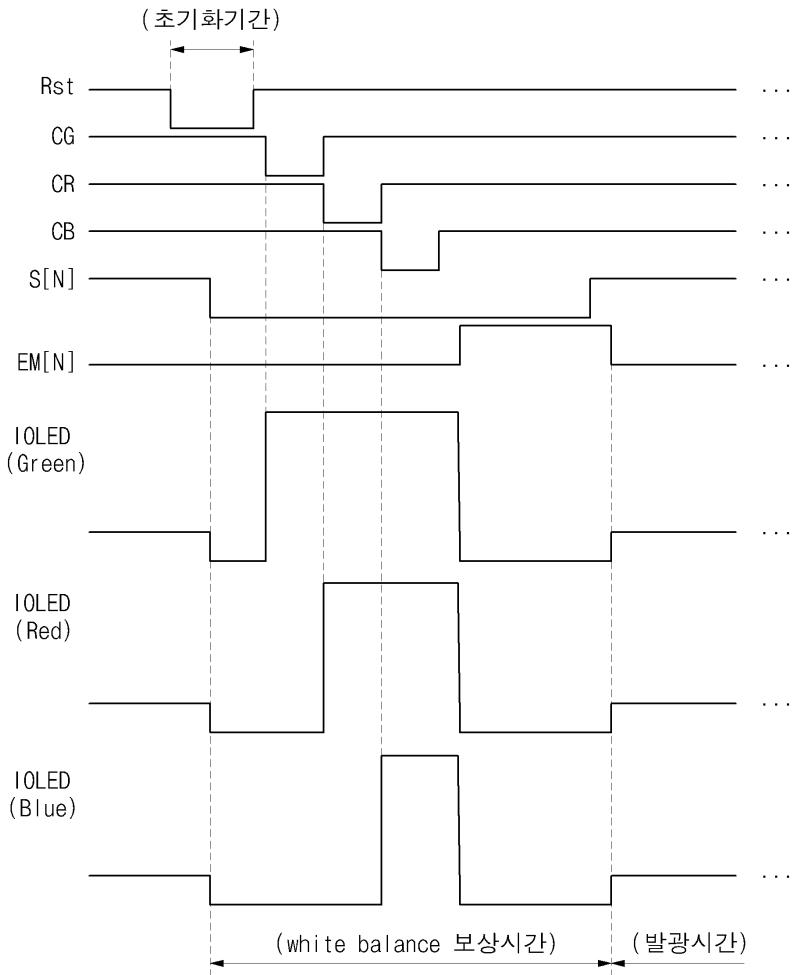

<255> 도 15를 참조하면, 도 14에 도시한 본 발명의 알지비(RGB)화소회로들의 구동 타이밍도가 도시되어 있다.

<256> 이하, 도 15의 구동 타이밍도를 참조하여 도 14에 도시된 본 발명의 알지비(RGB)화소회로들의 동작을 설명하도록 한다.

<257> 먼저, 초기화신호선(Rst)를 통해 로우 레벨의 초기화신호가 인가되면 디멀티플렉서내의 초기화스위칭소자(SW\_TR4)들이 턴온 되며, 이에따라 데이터선들이 초기화전원전압선(Vrst)으로부터의 초기화전원전압에 의해 초기화될 수 있다.

<258> 한편, 발광제어선(EM[N])을 통해 로우 레벨의 발광제어신호가 인가되고, 주사선(S[N])으로부터 로우 레벨의 주사신호가 인가되면, 이 기간동안 알지비(RGB)제어신호선을 통하여 로우 레벨의 신호가 인가되면 디멀티플렉서내의 알지비(RGB)스위칭소자들(SW\_TR3R, SW\_TR3G, SW\_TR3B)이 턴온될 수 있다.

<259> 상기 알지비(RGB)제어신호는 녹색(G), 적색(R) 및 청색(B)제어신호의 순서로 인가되며, 따라서 알지비(RGB)데이터전압은 각각 녹색(G), 적색(R) 및 청색(B)의 화소 회로들에 순차적으로 인가된다.

<260> 도 15에 도시된 바와 같이, 녹색(G)제어신호가 인가되는 기간부터 상기 발광제어선(EM[N])으로부터 하이 레벨의 발광제어신호가 인가되는 기간까지 화소 회로내의 녹색 유기 전계 발광 소자(OLED Green)에 전류가 흐름으로써 발광하게 된다.

<261> 적색(R)제어신호가 인가되는 기간부터 상기 발광제어선(EM[N])으로부터 하이 레벨의 발광제어신호가 인가되는 기간까지에는 화소 회로내의 적색 유기 전계 발광 소자(OLED Red)에 전류가 흐름으로써 발광하게 된다.

<262> 또한, 청색(B)제어신호가 인가되는 기간부터 상기 발광제어선(EM[N])으로부터 하이 레벨의 발광제어신호가 인가되는 기간까지에는 화소 회로내의 청색 유기 전계 발광 소자(OLED Blue)에 전류가 흐름으로써 발광하게 된다.

<263> 즉, 도 15에 도시된 바와 같이, 화이트 밸런스 보상기간동안 녹색(G)유기 전계 발광 소자에 가장 긴 시간동안의 전류가 흐르고, 그 다음은 적색(R)유기 전계 발광 소자 및 청색(B)유기 전계 발광 소자의 순서가 된다.

<264> 이렇게, 화이트 밸런스 보상 시간이 녹색(G), 적색(R) 및 청색(B)의 순서가 되는 이유는, 일반적으로 적색(R), 청색(B) 신호에 비해 녹색(G) 신호가 발광 효율이 높기 때문이다. 다시 말하자면, 화이트 밸런스를 맞추기 위해서는 비발광기간(화이트 밸런스 보상기간)동안 가장 발광 효율이 좋은 녹색(G) 유기 전계 발광 소자에 가장 긴 시간동안의 전류를 흐르게 하고, 다음에는 적색(R), 그 다음에는 청색(B)의 순서로 화이트 밸런싱 기간을 수행함으로써 동일한 휘도 레벨을 구현할 수 있다. 이러한, 화이트 밸런스 기간 동안에 유기 전계 발광 소자들에 흐르는 전류는 발광기간 동안 상기 유기 전계 발광 소자들에 흐르는 전류 보다 더 큰 전류가 흐르게 된다.

<265> 한 프레임의 화상 표시 기간중, 상술한 화이트 밸런스 보상 기간은 발광 기간에 비해 짧을 수 있다.

### 발명의 효과

<266> 상술한 바와 같이, 본 발명에 따른 유기 전계 발광 표시 장치는 한 프레임의 화상 표시 기간을 제1기간(T1), 제2기간(T2) 및 제3기간으로 나눌 수 있고, 각각의 기간들은 데이터 기입기간(T1), 구동 트랜지스터의 문턱전압 저장기간(T2) 및 발광 기간(T3)으로 이루어 진다.

<267> 이러한 본 발명에 따른 유기 전계 발광 표시 장치는,

<268> 첫째로, 기존의 화소 회로에 비하여 적은 숫자인 3개의 트랜지스터를 사용함으로써 고 집적화를 꾀할 수 있으며, 이에따라 고해상도를 가능하게 하는 효과가 있다.

<269> 둘째로, 제1용량성소자 및 제2용량성소자의 비율(C1 : C2)을 적절히 조절함으로써 구동 트랜지스터의 문턱전압(Vth)을 보상하여 휘도의 균일성을 향상시킬 수 있으며, 상기 제1용량성소자 및 제2용량성소자의 비율 조절에 따라 제1전원전압선 (VDD)에 의한 전압강하(IR-DROP) 현상을 개선하는 효과가 있다.

<270> 셋째로, 본 발명에 따른 화소 회로는 구동 트랜지스터의 제어 전극으로부터 네거티브(Negative)전원쪽으로 누설 전류가 흐를 수 있는 전기적 연결관계가 존재하지 않기 때문에 누설 전류(Leakage current)에 의한 유기 전계 발광 소자의 부적절한 발광을 막을 수 있는 효과가 있다.

<271> 또한, 디멀티플렉서를 사용하여 알지비(RGB)데이터신호를 인가하는 본 발명의 일실시예에 따른 구동방법의 경우, 주사신호의 온(On)/오프(Off)에 관계없이 발광제어신호의 온(On) 기간동안 상기 알지비(RGB)데이터신호를 인가함으로써 상기 알지비(RGB)데이터가 화소 회로들의 각 용량성소자에 올바르게 저장될 수 있도록 한다. 즉, 알지비(RGB)데이터가 화소 회로들의 각 용량성소자에 인가되기 전에 각 용량성소자들을 제1전원전압선(VDD)의 제1전원전압에 의해 초기화 시킴으로서 새로운 알지비(RGB)데이터신호가 상기 용량성소자들에 올바르게 저장될 수 있도록하는 효과가 있다.

<272> 아울러, 디멀티플렉서를 사용하여 알지비(RGB)데이터신호를 인가하는 다른 실시예에 따른 구동방법의 경우, 비발광기간(화이트 밸런스 보상기간)동안 가장 발광 효율이 좋은 녹색(G) 유기 전계 발광 소자에 가장 긴 시간동안의 전류를 흐르게 하고, 다음에는 적색(R), 그 다음에는 청색(B)의 순서로 화이트 밸런싱 시간을 수행함으로써 동일한 휘도 레벨을 구현할 수 있게 된다.

<273> 다시 말하자면, 발광기간의 중간에 화이트 밸런스 보상기간을 진행함으로써 시간이 지남으로써 화이트 밸런스가 달라져 원하는 색을 재현할 수 없게 되는 문제를 개선하는 효과가 있다.

<274> 이상에서 설명한 것은 본 발명에 따른 유기 전계 발광 표시 장치를 실시하기 위한 하나의 실시예에 불과한 것으로서, 본 발명의 상기한 실시예에 한정되지 않고, 이하의 특허청구범위에서 청구하는 바와 같이 본 발명의 요지를 벗어남이 없이 당해 발명이 속하는 분야에서 통상의 지식을 가진 자라면 누구든지 다양한 변경 실시가 가능한 범위까지 본 발명의 기술적 정신이 있다고 할 것이다.

### **도면의 간단한 설명**

- <1> 도 1은 통상의 유기 전계 발광 소자의 기본 구조를 도시한 개략도이다.

- <2> 도 2는 전압 구동 방식의 기본 화소 회로를 도시한 개략도이다.

- <3> 도 3은 도 2에 도시된 화소 회로의 구동 타이밍도이다.

- <4> 도 4는 본 발명에 따른 유기 전계 발광 표시 장치의 기본 구조 블록도이다.

- <5> 도 5는 본 발명의 유기 전계 발광 표시 장치의 일실시예에 따른 화소 회로를 도시한 회로도이다.

- <6> 도 6은 도 5에 도시된 화소 회로의 구동 타이밍도이다.

- <7> 도 7은 도 5에 도시된 화소 회로에서 데이터 기입기간(T1)중 전류흐름을 도시한 것이다.

- <8> 도 8은 도 5에 도시된 화소 회로에서 구동 트랜지스터의 문턱전압 저장기간(T2)중 전류흐름을 도시한 것이다.

- <9> 도 9는 도 5에 도시된 화소 회로에서 발광기간(T3)중 전류흐름을 도시한 것이다.

- <10> 도 10은 본 발명의 유기 전계 발광 표시 장치의 다른 실시예에 따른 화소 회로 도시한 회로도이다.

- <11> 도 11은 본 발명의 알지비(RGB)화소회로들과 디멀티플렉서의 일실시예에 따른 전기적 연결관계를 도시한 것이다.

- <12> 도 12는 도 11에서 도시한 본 발명의 알지비(RGB) 화소회로들의 일실시예에 따른 구동 타이밍도이다.

- <13> 도 13은 도 11에서 도시한 본 발명의 알지비(RGB) 화소회로들의 다른 실시예에 따른 구동 타이밍도이다.

- <14> 도 14는 본 발명의 알지비(RGB)화소회로들과 디멀티플렉서의 다른 실시예에 따른 전기적 연결관계를 도시한 것이다.

- <15> 도 15는 도 14에 도시한 본 발명의 알지비(RGB) 화소회로들의 구동 타이밍도이다.

- <16> <도면의 주요 부분에 대한 부호의 설명>

- <17> 100; 본 발명에 의한 유기 전계 발광 표시 장치

- <18> 110; 주사 신호 구동부            120; 데이터 신호 구동부

- <19> 130; 발광 제어 신호 구동부 140; 유기 전계 발광 표시 패널

<20> 142; 화소 회로(P) 150; 제1전원전압 공급부

<21> D[M]; 테이터선 160; 제2전원전압 공급부

<22> S[N]; 주사선 EM[N]; 발광제어선

<23> VDD; 제1전원전압선 VSS; 제2전원전압선

<24> SW\_TR1; 제1스위칭소자 SW\_TR2; 제2스위칭소자

<25> C1; 제1용량성소자 C2; 제2용량성소자

<26> DR\_TR; 구동 트랜지스터 EM\_TR; 발광제어 트랜지스터

<27> OLED (Organic Light Emitting Diode); 유기 전계 발광 소자

<28> 1000: 디멀티플렉서(Demultiplexer)

<29> SW\_TR3: 알지비(RGB)스위칭소자 SW\_TR4: 초기화스위칭소자

## 도면

### 도면1

### 도면2

도면3

도면4

**도면5****도면6****도면7**

도면8

도면9

도면10

도면11

도면12

도면13

도면14

## 도면15