(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-24598

(P2006-24598A)

(43) 公開日 平成18年1月26日(2006.1.26)

| (51) Int.C1.                  | F 1            | テーマコード (参考) |

|-------------------------------|----------------|-------------|

| <b>HO1L 21/8247 (2006.01)</b> | HO1L 27/10 434 | 5FO38       |

| <b>HO1L 27/115 (2006.01)</b>  | HO1L 27/10 461 | 5FO83       |

| <b>HO1L 27/10 (2006.01)</b>   | HO1L 27/10 481 | 5F1O1       |

| <b>HO1L 29/792 (2006.01)</b>  | HO1L 27/10 491 |             |

| <b>HO1L 29/788 (2006.01)</b>  | HO1L 29/78 371 |             |

審査請求 未請求 請求項の数 10 O L (全 28 頁) 最終頁に続く

|           |                              |            |                                                   |

|-----------|------------------------------|------------|---------------------------------------------------|

| (21) 出願番号 | 特願2004-198888 (P2004-198888) | (71) 出願人   | 000005223<br>富士通株式会社<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 |

| (22) 出願日  | 平成16年7月6日 (2004.7.6)         | (74) 代理人   | 100090273<br>弁理士 國分 孝悦                            |

|           |                              | (72) 発明者   | 高橋 浩司<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内       |

|           |                              | (72) 発明者   | 中川 進一<br>神奈川県川崎市中原区上小田中4丁目1番<br>1号 富士通株式会社内       |

|           |                              | F ターム (参考) | 5F038 AV06 BH04 BH07 BH11 CD12<br>CD18 DF05 EZ20  |

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【要約】

【課題】 使用中の電荷の不要な移動に伴う閾値電圧の変動を抑制することができる半導体装置の製造方法を提供する。

【解決手段】 Si 基板 1 の表面に、不揮発性メモリセル、n MOS トランジスタ及び p MOS トランジスタを形成した後、不揮発性メモリセル、n MOS トランジスタ及び p MOS トランジスタを覆う層間絶縁膜 19 を形成する。次に、層間絶縁膜 19 中に、夫々、不揮発性メモリセルのコントロールゲート 11、n MOS トランジスタのソース又はドレイン 17、p MOS トランジスタのソース又はドレイン 18 に接続される複数個のコンタクトプラグ 20 を形成する。そして、複数個のコンタクトプラグ 20 を介して、コントロールゲート 11 と n MOS トランジスタ及び p MOS トランジスタのソース又はドレイン 17、18 とを接続する単層の配線 21 を形成する。

【選択図】 図 3 2

**【特許請求の範囲】****【請求項 1】**

半導体基板の表面に、不揮発性メモリセル、nMOSトランジスタ及びpMOSトランジスタを形成する工程と、

前記不揮発性メモリセル、nMOSトランジスタ及びpMOSトランジスタを覆う層間絶縁膜を形成する工程と、

前記層間絶縁膜中に、夫々、前記不揮発性メモリセルのコントロールゲート、前記nMOSトランジスタのソース又はドレイン、前記pMOSトランジスタのソース又はドレインに接続される複数個のコンタクトプラグを形成する工程と、

前記複数個のコンタクトプラグを介して、前記コントロールゲートと前記nMOSトランジスタ及びpMOSトランジスタのソース又はドレインとを接続する配線を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

**【請求項 2】**

前記配線として、単層の配線を形成することを特徴とする請求項1に記載の半導体装置の製造方法。

**【請求項 3】**

前記不揮発性メモリセルを複数個形成して、不揮発性メモリセルアレイを形成し、

前記nMOSトランジスタ及びpMOSトランジスタを、前記不揮発性メモリセルアレイの動作を制御する制御回路内のデコーダを構成する素子として形成することを特徴とする請求項1又は2に記載の半導体装置の製造方法。

**【請求項 4】**

エンベッデッド型の構造とすることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置の製造方法。

**【請求項 5】**

前記配線を形成する工程の後に、前記コントロールゲートに接続される複数の上層配線を形成する工程を有することを特徴とする請求項1乃至4のいずれか1項に記載の半導体装置の製造方法。

**【請求項 6】**

前記不揮発性メモリセル、nMOSトランジスタ及びpMOSトランジスタを形成する工程は、前記不揮発性メモリセル用のウェルと前記nMOSトランジスタ用のウェルとを同時に形成する工程を有することを特徴とする請求項1乃至5のいずれか1項に記載の半導体装置の製造方法。

**【請求項 7】**

前記不揮発性メモリセル、nMOSトランジスタ及びpMOSトランジスタを形成する工程は、前記コントロールゲートと前記nMOSトランジスタのゲートと前記pMOSトランジスタのゲートとを同一の材料から形成する工程を有することを特徴とする請求項1乃至6のいずれか1項に記載の半導体装置の製造方法。

**【請求項 8】**

前記コントロールゲート、前記nMOSトランジスタのゲート及び前記pMOSトランジスタのゲートを、不純物がドープされていない多結晶Si膜から形成することを特徴とする請求項7に記載の半導体装置の製造方法。

**【請求項 9】**

前記不揮発性メモリのフローティングゲートを、リンがドープされたアモルファスSi膜を形成することを特徴とする請求項1乃至8のいずれか1項に記載の半導体装置の製造方法。

**【請求項 10】**

面積に関し、前記不揮発性メモリセルアレイの占有率を2%乃至5%とすることを特徴とする請求項3乃至9のいずれか1項に記載の半導体装置の製造方法。

**【発明の詳細な説明】**

10

20

30

40

50

**【技術分野】****【0001】**

本発明は、例えば電界効果トランジスタを備えた半導体装置の製造方法に関する。

**【背景技術】****【0002】**

フラッシュメモリ等の不揮発性メモリを製造するに際して、そのウェーハプロセス終了後において、閾値電圧( $V_{th}$ )にバラツキが生じ易いという問題がある。これは、ウェーハプロセスにおいて、フローティングゲートに不要な電荷が注入されることを主な要因として発生するものと推定される。

**【0003】**

従来では、この問題に対処するため、フラッシュメモリを製造するに当たり、特許文献1,2のように、コントロールゲートを複数の配線を介していわゆる保護ダイオードに接続する技術が提案されている。

**【0004】**

【特許文献1】特開2002-43446号公報

【特許文献2】特開平7-183502号公報

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

しかしながら、これらの従来の製造方法によっても、製造時に生じるフローティングゲートへの電荷の注入による閾値電圧の変動を十分に抑制することができない。

**【0006】**

本発明は、上記の課題に鑑みてなされたものであり、フローティングゲートへの電荷の注入による閾値電圧の変動をより一層抑制することを可能とし、信頼性の高い高性能の半導体装置を実現する製造方法を提供することを目的とする。

**【課題を解決するための手段】****【0007】**

本願発明者は、前記課題を解決すべく鋭意検討を重ねた結果、以下に示す発明の諸態様に想到した。

**【0008】**

本発明に係る半導体装置の製造方法では、半導体基板の表面に、不揮発性メモリセル、nMOSトランジスタ及びpMOSトランジスタを形成した後、前記不揮発性メモリセル、nMOSトランジスタ及びpMOSトランジスタを覆う層間絶縁膜を形成する。次に、前記層間絶縁膜中に、夫々、前記不揮発性メモリセルのコントロールゲート、前記nMOSトランジスタのソース又はドレイン、前記pMOSトランジスタのソース又はドレインに接続される複数個のコンタクトプラグを形成する。そして、前記複数個のコンタクトプラグを介して、前記コントロールゲートと前記nMOSトランジスタ及びpMOSトランジスタのソース又はドレインとを接続する配線を形成する。

**【発明の効果】****【0009】**

本発明によれば、nMOSトランジスタ及びpMOSトランジスタを保護ダイオードとして用いているため、不揮発性メモリの配線に蓄積してコントロールゲートまで移動する可能性がある電荷を高い効率で排除することができる。また、このような電荷の排除により、製造時の閾値電圧の変動を抑制することができると共に、使用中の閾値電圧の変動を抑制することもできる。これにより、信頼性の高い高性能の半導体装置が実現する。

**【発明を実施するための最良の形態】****【0010】**

(本発明の骨子)

先ず、本発明の骨子について説明する。

従来のフラッシュメモリ等の不揮発性メモリの製造方法の問題点は、具体的には以下の

10

20

30

40

50

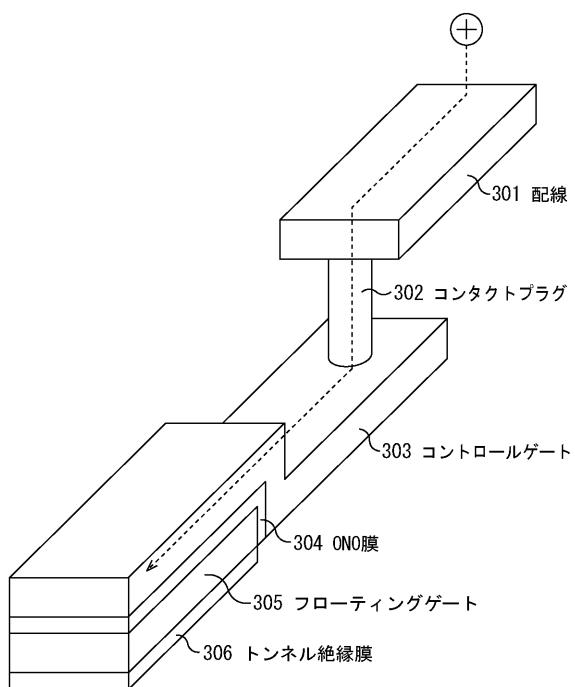

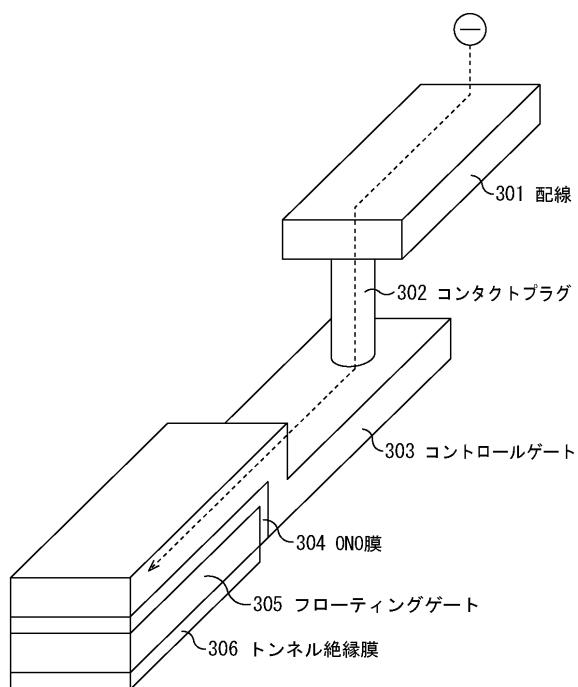

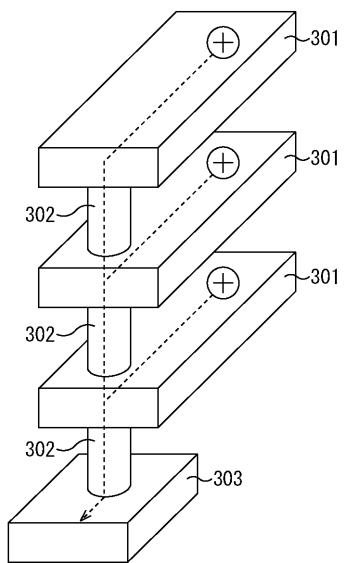

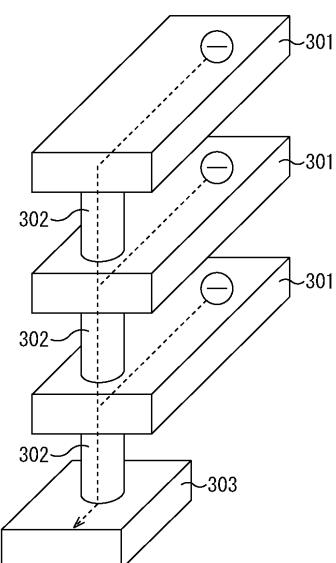

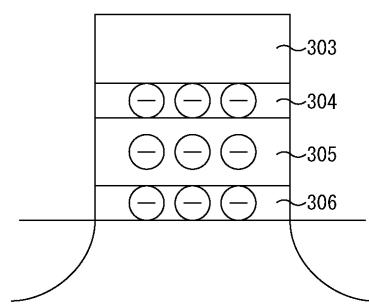

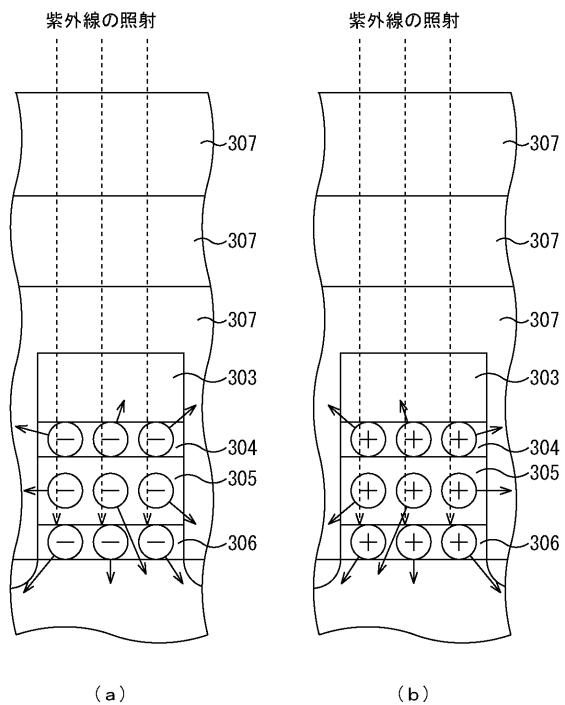

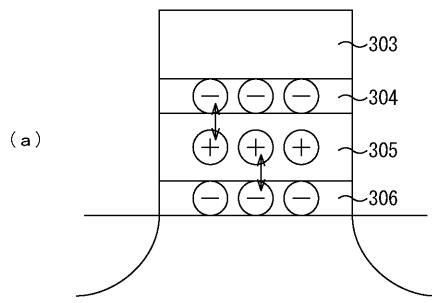

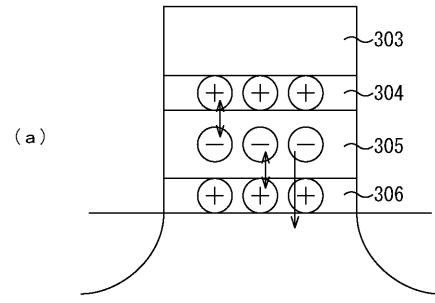

ようになると考えられる。この製造方法では、多層配線を形成する際に行われるプラズマ処理によって、コントロールゲートに接続された配線に電子又は正孔が蓄積され、これらの電荷がコントロールゲートまで移動し、フローティングゲートに不要な電荷が注入されることがある。例えば、図1に示すように、配線301に正孔が蓄積されると、この正孔は、コンタクトプラグ302を介してコントロールゲート303まで移動してしまう。同様に、図2に示すように、配線301で電子が蓄積された場合にも、この電子は、コンタクトプラグ302を介してコントロールゲート303まで移動してしまう。一方で、Si基板(図示せず)の電位は、概ね接地電位とされている。このため、コントロールゲート303とSi基板との間に電位差が生じ、これらの間に存在するフローティングゲート305とSi基板との間に存在するトンネル絶縁膜306に電圧が印加され、この値が一定値を超えるとトンネル電流が流れる。そして、図1に示すように、コントロールゲート303が正に帯電している場合には、フローティングゲート305にSi基板から電子が注入され、図2に示すように、コントロールゲート303が負に帯電している場合には、フローティングゲート305からSi基板に電子が抜ける。また、配線301からコントロールゲート303まで移動してくる電荷の量は、図3及び図4に示すように、配線301の数が増えるほど多くなる。

## 【0011】

そして、その後に熱処理が行われると、熱励起によってトンネル絶縁膜306の電荷がフローティングゲート305及びONO膜304に移動し、そこでトラップされてしまうと推察される。

## 【0012】

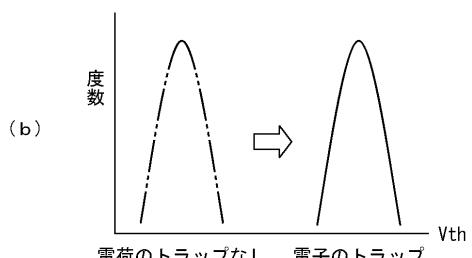

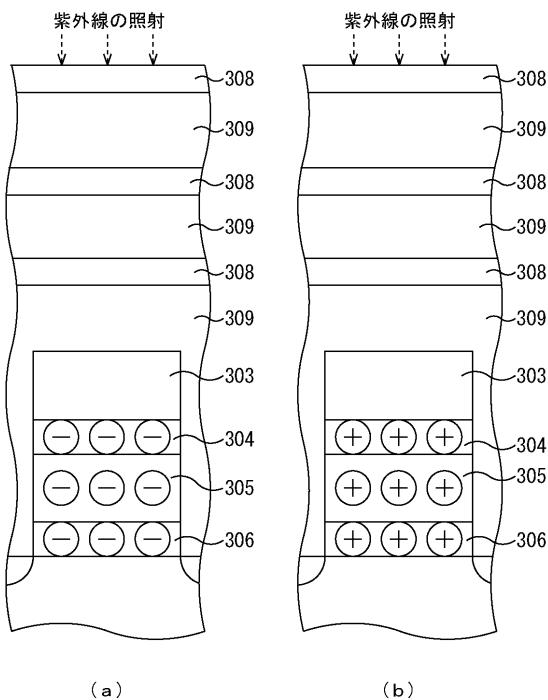

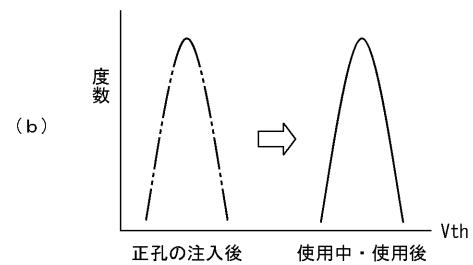

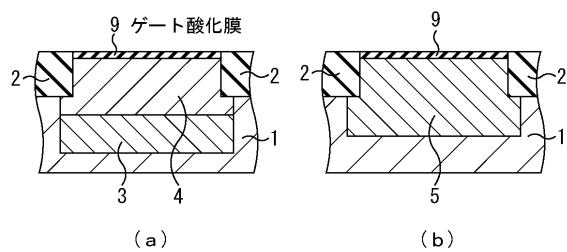

図5(a)に示すように、正孔がONO膜304、フローティングゲート305及びトンネル酸化膜306にトラップされると、図5(b)に示すように、閾値電圧は、電荷がトラップされていないときと比べて低くなる。一方、図6(a)に示すように、電子がONO膜304、フローティングゲート305及びトンネル酸化膜306にトラップされると、図6(b)に示すように、閾値電圧は、電荷がトラップされていないときと比べて高くなる。このように閾値電圧が変動してしまう。

## 【0013】

そこで、ONO膜304、フローティングゲート305及びトンネル酸化膜306にトラップされた電荷を消去するために、図7(a)及び(b)に示すように、複数の層間絶縁膜307を介して、これらに紫外線を照射することが考えられる。

## 【0014】

本発明では、配線抵抗の低減化を図るために、不揮発性メモリセル(例えばフラッシュメモリ)と、そのコントロールゲートに接続された複数の上層配線であるCu配線とを備えた半導体装置、及び配線容量の低減化を図るために、不揮発性メモリセルと、そのコントロールゲートに接続される複数の上層配線と、これら上層配線を覆う層間絶縁膜である低誘電率膜とを備えた半導体装置を提示する。

## 【0015】

本願発明者は、上述した従来の製造方法では、フローティングゲートへの電荷の注入による閾値電圧の変動を十分に抑制できない原因について調査を行った結果、紫外線照射を行っても、フローティングゲート等にトラップされている電荷を除去できていないことを見出した。図7(a)及び(b)に示すように、複数の層間絶縁膜307を介して、これらに紫外線を照射しても、近時、図8(a)及び(b)に示すように、微細化等を目的としたプロセスのためにCuの拡散防止用のSi窒化膜308が使用されるようになると、Si窒化膜308により紫外線の透過が遮断されてしまうことが判った。また、このようなプロセスでは、層間絶縁膜309として低誘電率膜を使用する場合、低誘電率膜に紫外線を照射すると分解又は変質が生じることがあるため、紫外線を照射すること自体が好ましくないという事情もある。

## 【0016】

本願発明者は、上述のような閾値電圧の変動について調査を行ったところ、更に、従来の方法により製造された半導体装置では、その使用中に閾値電圧が変動してくることも見出した。

#### 【0017】

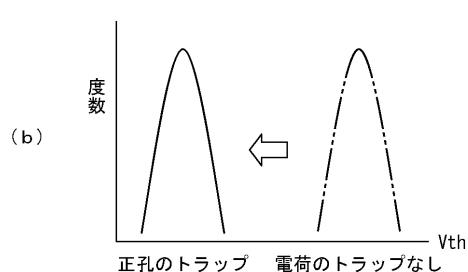

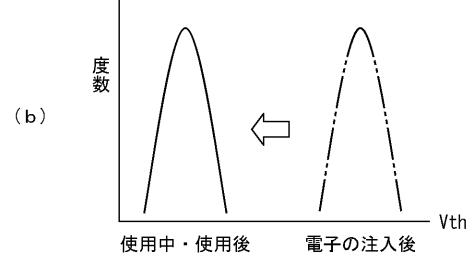

例えば、電子がONO膜304及びトンネル絶縁膜306にトラップされた状態で、製造後の不揮発性メモリが使用されると、熱の影響等で電子がフローティングゲート305に戻ってきたり、コントロールゲート303に抜けたりする。ONO膜304中の電子がフローティングゲート305に戻ってくると、例えば、図9(a)に示すように、プログラミングによってフローティングゲート305に正孔が注入されている場合には、図9(b)に示すように、閾値電圧が上昇してしまう。即ち、使用時間が長くなるに連れて閾値電圧が徐々に上昇することが判った。また、トンネル絶縁膜306中の電子がフローティングゲート305に移動した場合には、使用時間が長くなるに連れて閾値電圧が徐々に上昇してしまうことも判明した。

#### 【0018】

同様に、正孔がONO膜304及びトンネル絶縁膜306にトラップされた状態で、製造後の不揮発性メモリが使用されると、熱の影響等で正孔がフローティングゲート305に戻ってきたり、コントロールゲート303に抜けたりする。ONO膜304中の電子がフローティングゲート305に戻ってくると、例えば、図10(a)に示すように、プログラミングによってフローティングゲート305に電子が注入されている場合には、図10(b)に示すように、閾値電圧が低下してしまう。即ち、使用時間が長くなるに連れて閾値電圧が徐々に低下することが判った。

#### 【0019】

製造後に、ONO膜304等に電荷が蓄積して閾値電圧が変動している場合には、プログラミング時にフローティングゲート305の電荷を調節することにより、閾値電圧を所望の値にすることは可能である。しかしながら、上述のような使用中に閾値電圧が変動すると、これを調整することはできず、記憶情報が変化する虞がある。

#### 【0020】

そこで、本願発明者がこれらの問題点を解決すべく鋭意検討を重ねた結果、保護ダイオードとして例えばnMOSトランジスタ及びpMOSトランジスタを用いることにより、紫外線の照射を行わなくても、製造後の閾値電圧の変動を抑制し、且つ、使用中の熱の影響による閾値電圧の変動をも抑制することができることに想到した。

#### 【0021】

本発明では、半導体基板の表面に形成されてなる不揮発性メモリセル(例えばフラッシュメモリ)及び保護ダイオードと、不揮発性メモリセルのコントロールゲートと保護ダイオードの拡散層とを接続する単層の金属配線とを有する半導体装置を提示する。

#### 【0022】

即ち、汎用的なフラッシュメモリでは、単位面積当たりの記憶容量を向上させるために、狭いセルピッチが採用されている。即ち、メモリセルアレイには、複数のメモリセルのコントロールゲートとして複数本のワード線が形成されており、このワード線同士の間隔が狭く設計されている。このため、このようなフラッシュメモリに対して1本のワード線にnMOSトランジスタ及びpMOSトランジスタを接続しようとすると、セルピッチが狭いほど、複数層の配線を用いて引き回しを行う必然性が高くなる。また、狭いセルピッチのフラッシュメモリを製造する際にはセルファーラインプロセスが採用されるが、工程数が多くなり、コストが高くなる。

#### 【0023】

これに対して、例えばフラッシュメモリと論理回路とが混載されたエンベッド型構造の半導体装置では、単位面積当たりの記憶容量はフラッシュメモリ単体で構成された半導体装置ほど重要視されていないため、広めのセルピッチを採用することが可能である。即ち、エンベッド型構造の半導体装置では、一般に、論理回路が存在する領域の面積がフラッシュメモリが存在する領域の面積よりも大きいため、フラッシュメモリが存在す

る領域の面積が多少増加したとしても、全体の面積への影響は小さいのである。従って、ワード線同士の間隔を比較的広めに設計することも許容され、1本のワード線にnMOSトランジスタ及びpMOSトランジスタを接続するに当たって、単層の配線、例えば1層の金属配線を用いて引き回しを行うことが可能となる。エンベッデッド型構造では、少ない工程数で、且つ低コストで製造することが重要視されるため、単層で引き回しを行うことが可能ということは極めて好ましいと言える。

#### 【0024】

この場合、紫外線の照射を行わなくても、製造後における閾値電圧の変動及び使用中の閾値電圧の変動を抑制することが可能であるため、Cu配線及びその拡散防止膜としてのSi窒化膜が必要とされる製造方法や、層間絶縁膜として低誘電率膜を形成する製造方法に本発明を適用することが好ましい。

#### 【0025】

##### (本発明の実施形態)

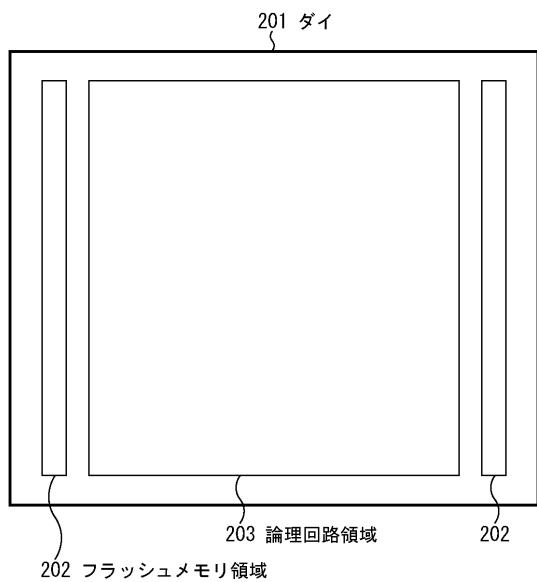

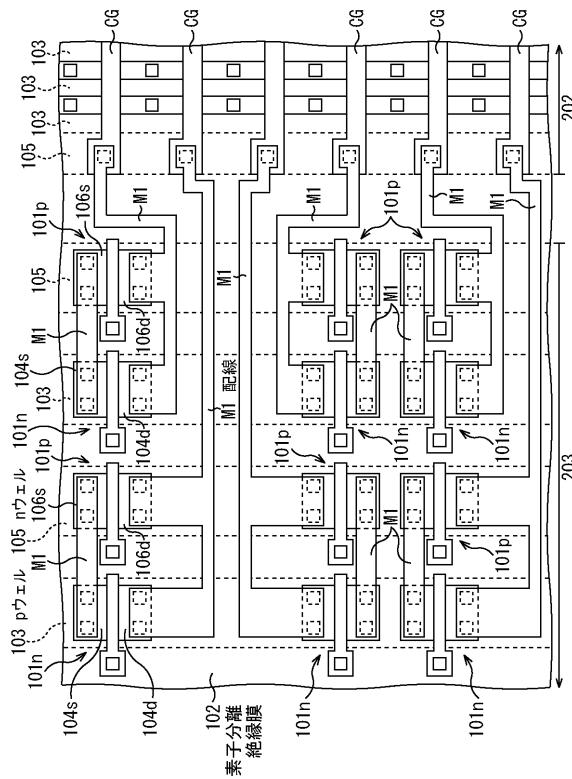

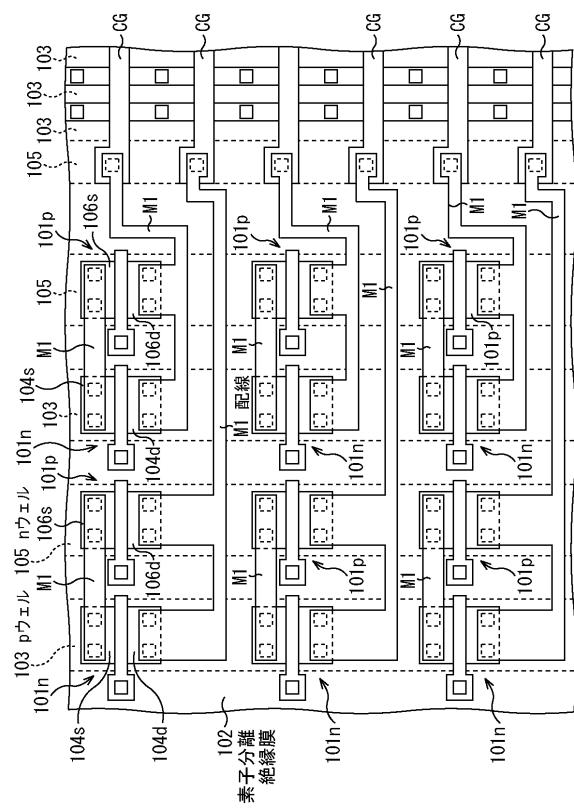

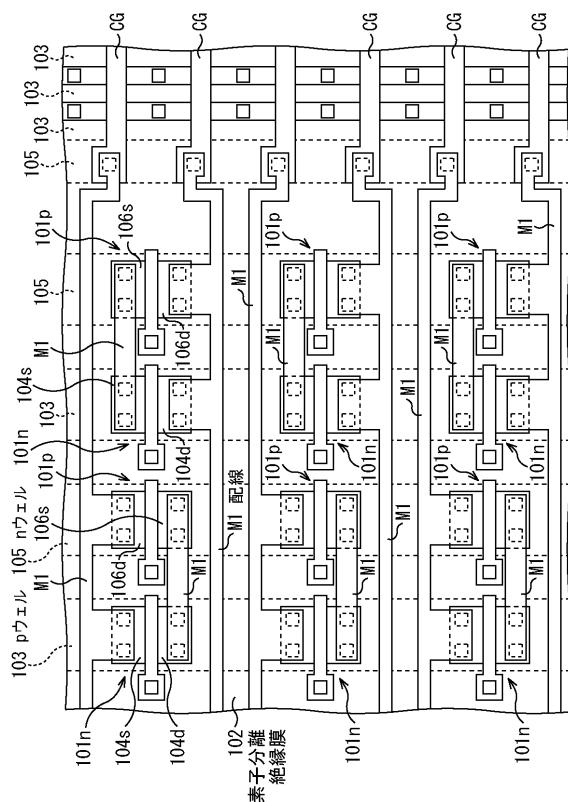

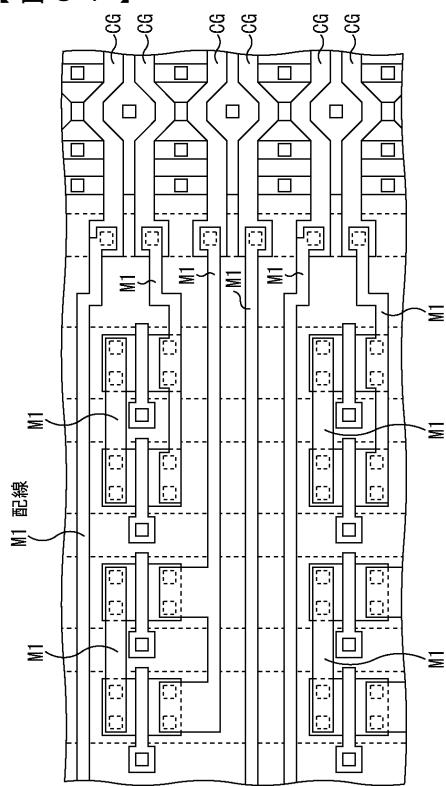

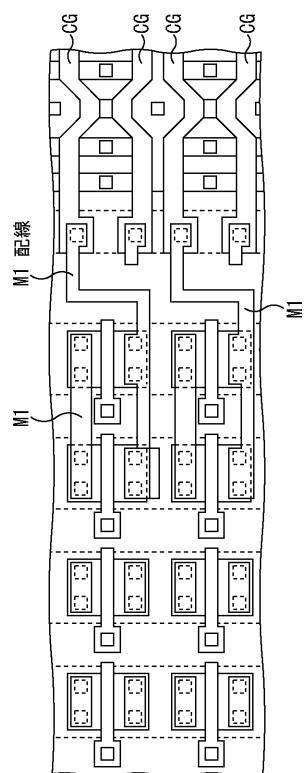

以下、本発明の実施形態について、添付の図面を参照して具体的に説明する。図11は、本発明の実施形態に方法によって製造する半導体装置の全体像を示すレイアウト図である。また、図12は、図11中の一部を拡大して示すレイアウト図である。

#### 【0026】

この半導体装置においては、図11に示すように、ダイ(半導体チップ)201の内部に論理回路領域203及びフラッシュメモリ領域202を設ける。また、この半導体装置はエンベッデッド型とし、フラッシュメモリ領域202の大きさを論理回路領域203の大きさよりも小さなものとし、フラッシュメモリ領域202の占有面積は、例えば2%~5%程度とする。

#### 【0027】

また、図12に示すように、フラッシュメモリ領域202内では、n型の不純物拡散層をソース及びドレインとする複数個のフラッシュメモリセルをpウェル103上にアレイ状に形成する。また、pウェル103の周辺にはnウェル105を形成する。

#### 【0028】

一方、論理回路領域203内には、フラッシュメモリ領域202の近傍に、デコーダの一部を構成し、且つフラッシュメモリセルの保護ダイオードとして機能する複数個のpMOSトランジスタ101p及びnMOSトランジスタ101nを形成する。pMOSトランジスタ101pについては、素子分離絶縁膜102によって区画された素子活性領域内にpウェル103を形成し、その内部にソース104s及びドレイン104dを形成する。nMOSトランジスタ101nについては、素子分離絶縁膜102によって区画された素子活性領域内にnウェル105を形成し、その内部にソース106s及びドレイン106dを形成する。また、素子分離絶縁膜102、ソース104s及び106s並びにドレイン104d及び106d上には層間絶縁膜(図示せず)を形成し、その上に最下層の金属配線M1を形成する。この金属配線M1はフラッシュメモリ領域202内のコントロールゲートCGとコンタクトホールを介して接続する。

#### 【0029】

また、各トランジスタと配線との位置関係に関し、コントロールゲートCGが延びる方向と並行に、2組のpMOSトランジスタ101p及びnMOSトランジスタ101n(4個のトランジスタ)を配置する。そして、金属配線M1の配置に関し、これら4個のトランジスタのゲートを基準として互いに同じ側に位置するソース・ドレインに金属配線M1が接続されるようにする。また、コントロールゲートCGが延びる方向に対して直交する方向で隣り合う2個のトランジスタについては、互いに線対称となるようにする。

#### 【0030】

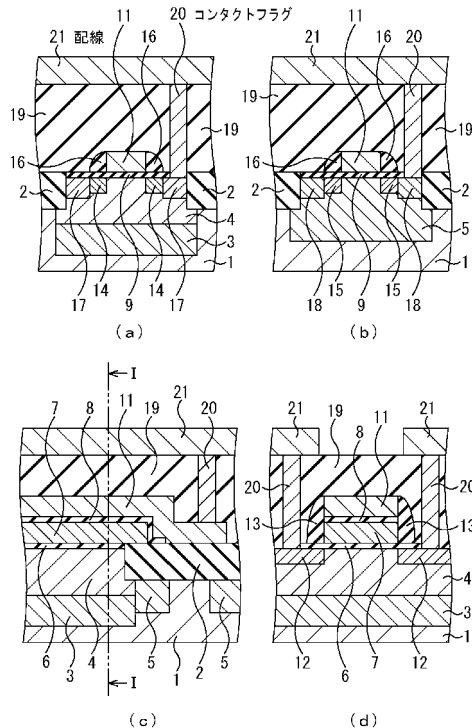

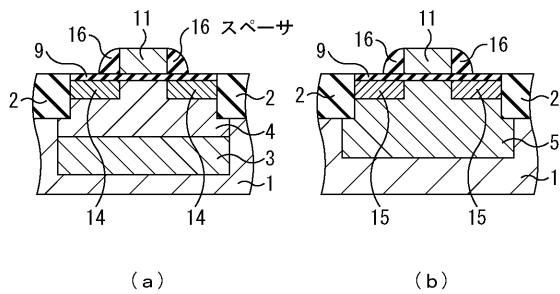

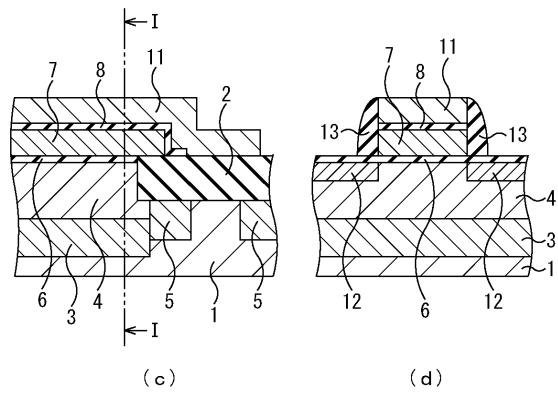

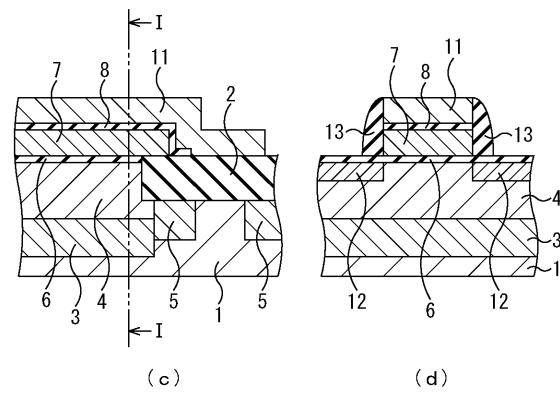

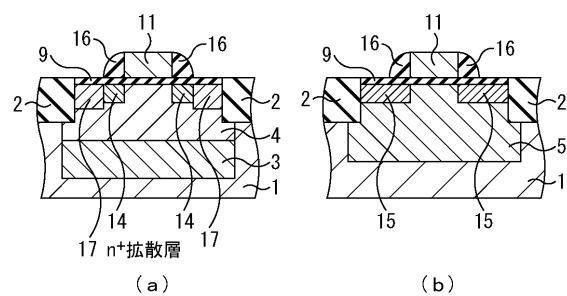

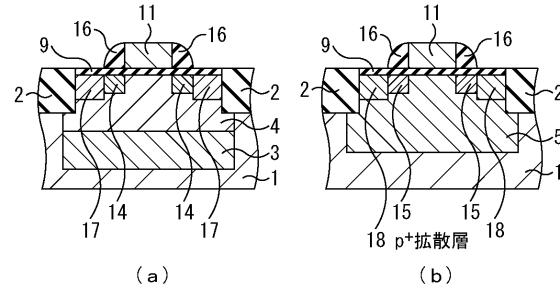

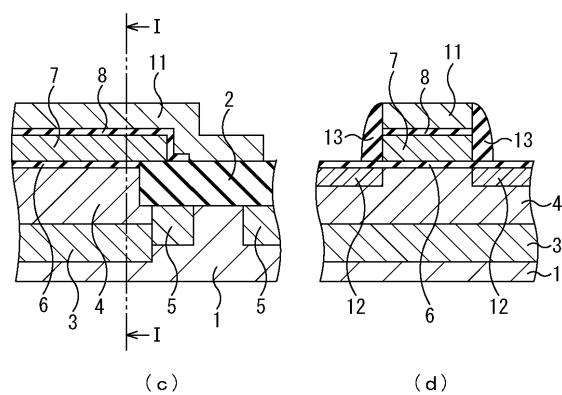

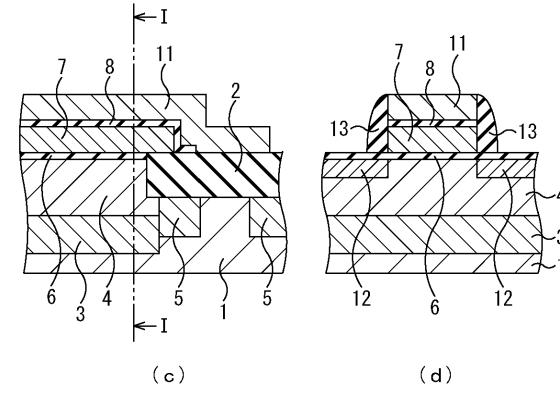

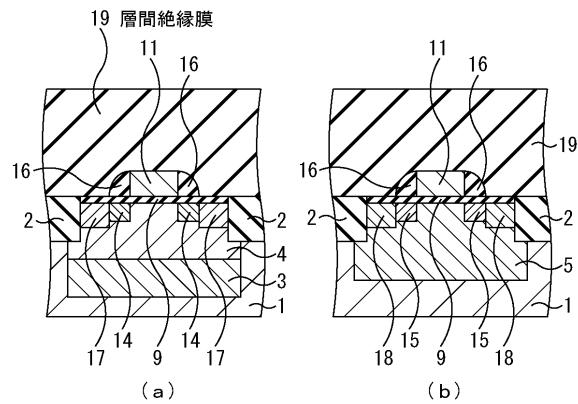

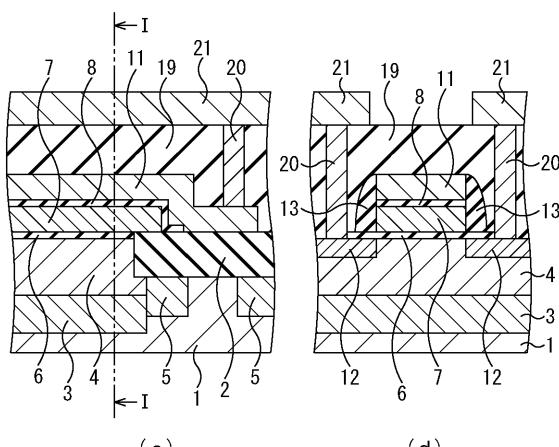

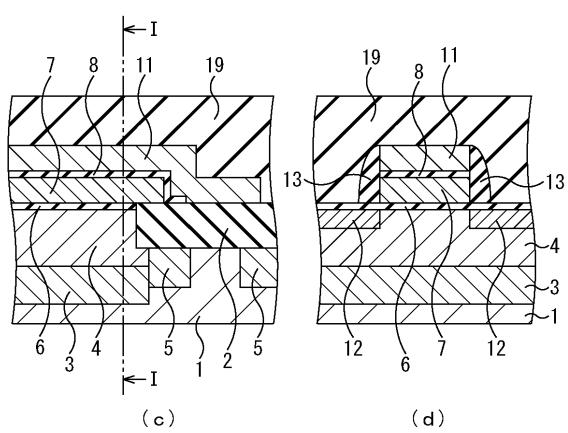

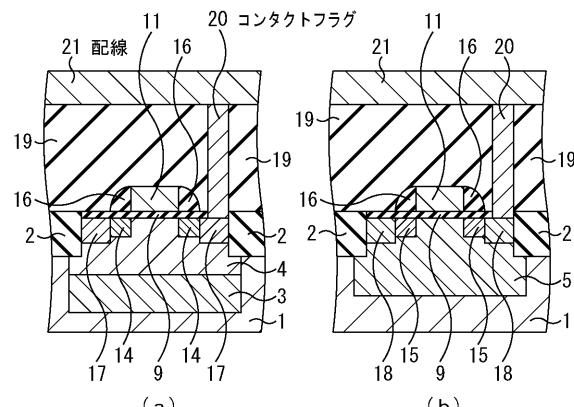

次に、本実施形態に係る半導体装置の製造方法について詳述する。図13乃至図32は、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。各図中の(a)はnMOSトランジスタ101nを形成する領域(nMOS領域)を示し、(b)はpMOSトランジスタ101pを形成する領域(pMOS領域)を示し、(c)はフラ

ッシュメモリセルを形成する領域(セル領域)を示している。また、図21乃至図32中の(d)は(c)中のI-I線に沿った断面を示している。

### 【0031】

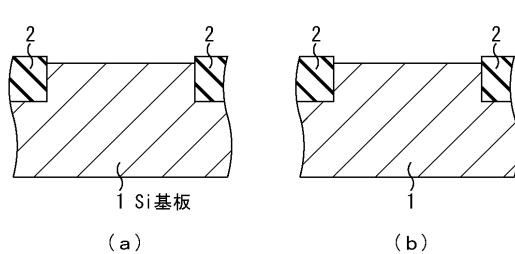

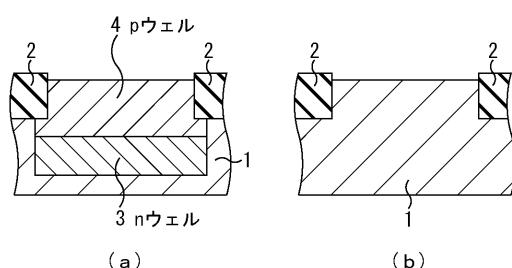

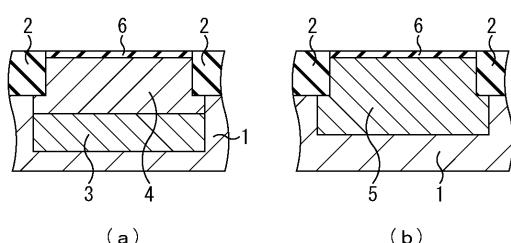

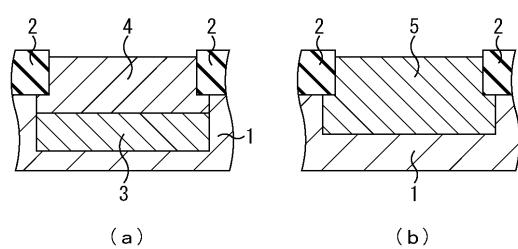

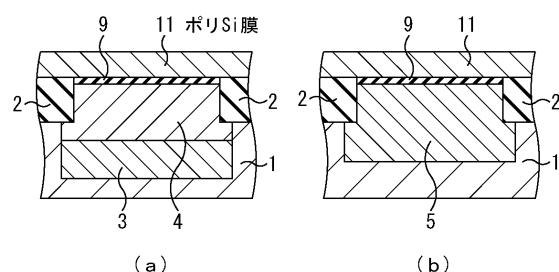

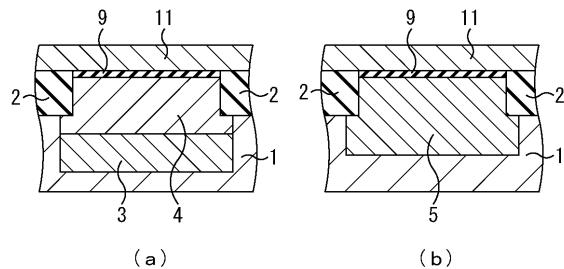

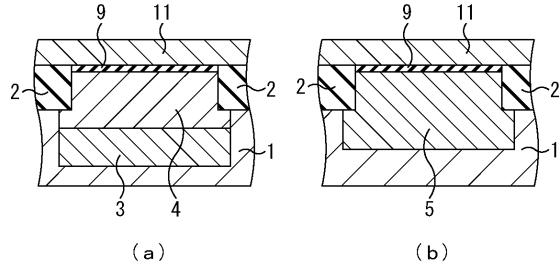

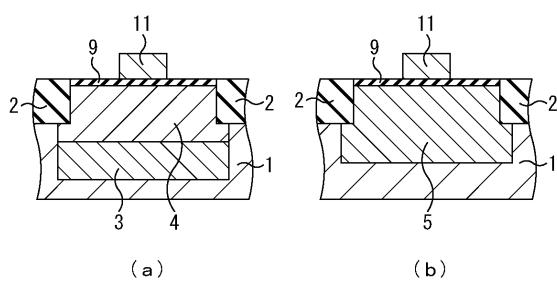

本実施形態では、先ず、図13(a)乃至(c)に示すように、p型のSi基板1の表面に、深さが250nm乃至400nm程度の素子分離絶縁膜2をSTI(Shallow Trench Isolation)により形成する。素子分離絶縁膜2の形成に当たっては、例えば、Si基板1の表面に溝を形成し、この溝内にSi酸化膜としてTEOS(Tetraethylorthosilicate)膜又はHDP(High Density Plasma)膜を埋め込み、化学機械的研磨(CMP:Chemical Mechanical Polishing)による平坦化を行う。

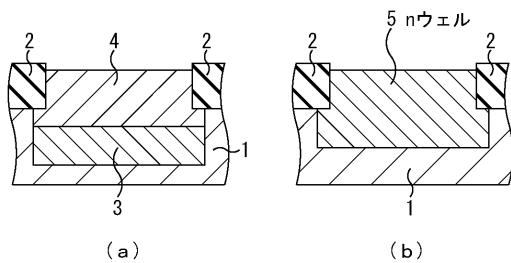

### 【0032】

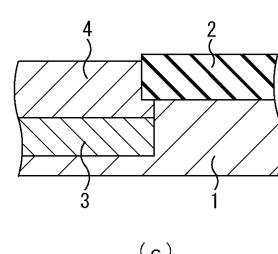

次に、図14(a)乃至(c)に示すように、nMOS領域及びセル領域内に、深いnウェル3及びpウェル4を順次形成する。nウェル3の形成に当たっては、例えばリンイオンを1.5MeV~2.5MeVのエネルギーで、ドーズ量を $1 \times 10^{13} \sim 3 \times 10^{13}$ としてイオン注入する。pウェル4の形成に当たっては、例えばボロンイオンを400keV~500keVのエネルギーで、ドーズ量を $1 \times 10^{13} \sim 3 \times 10^{13}$ としてイオン注入する。なお、本実施形態では、このようにトリプルウェル構造を採用しているが、これは、フラッシュメモリセルにおけるデータの消去に基板へのFN(Fowler-Nordheim)トンネリングを使用するためである。従って、消去を他の方法で行う場合には、トリプルウェル構造を採用する必要はない。

### 【0033】

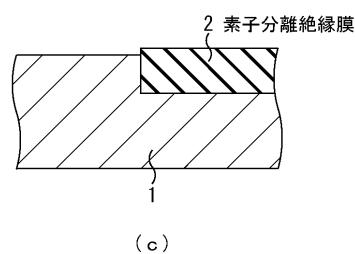

次いで、図15(a)乃至(c)に示すように、pMOS領域及びセル領域内に、nウェル5を形成する。nウェル5の形成に当たっては、例えばリンイオンを500keV~700keVのエネルギーで、ドーズ量を $1 \times 10^{13} \sim 3 \times 10^{13}$ としてイオン注入する。

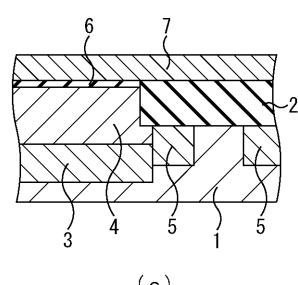

### 【0034】

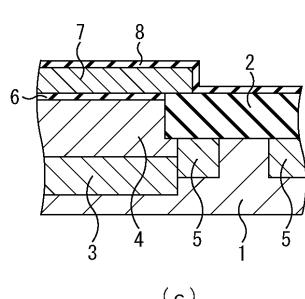

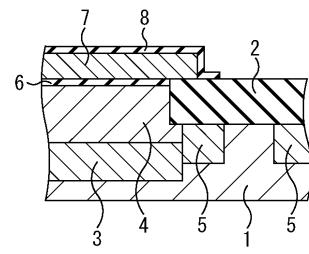

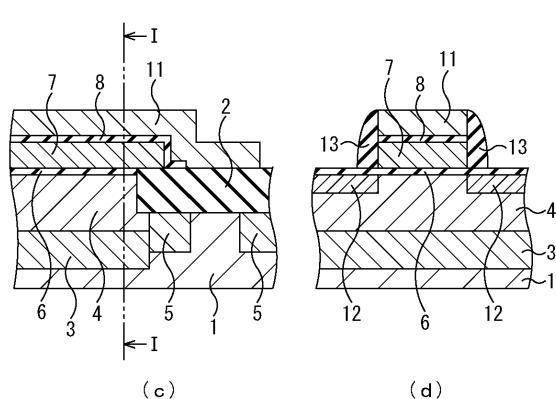

その後、図16(a)乃至(c)に示すように、nMOS領域、pMOS領域及びセル領域内に、1000~1100のドライ酸化によって、厚さが9.5nm~11nm程度のトンネル酸化膜6を形成する。続いて、リンをドープしたアモルファスシリコン(-Si)膜7を、CVD(Chemical Vapor Deposition)法により全面に80nm~100nm程度の厚さで形成する。-Si膜7中のリンのドープ量は、例えば $4 \times 10^{19} \text{ cm}^{-3} \sim 6 \times 10^{19} \text{ cm}^{-3}$ 程度とする。なお、トンネル酸化膜6は、例えば750~900程度のウェット酸化によって形成してもよい。

### 【0035】

次に、図17(a)乃至(c)に示すように、フォトリソグラフィ技術及びエッチング技術により、-Si膜7をパターニングし、-Si膜7をセル領域内にのみ残存させる。即ち、論理回路領域203内の-Si膜7を除去する。

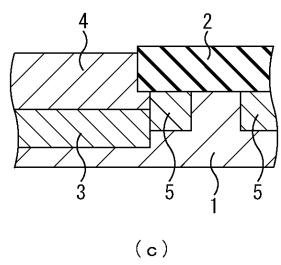

### 【0036】

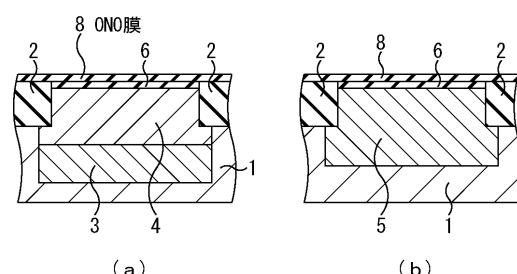

次いで、図18(a)乃至(c)に示すように、ONO膜8を全面に形成する。ONO膜8の形成に当たっては、例えば、厚さが4nm~7nm程度のSi酸化膜をCVD法により形成し、厚さが7nm~9nm程度のSi窒化膜をCVD法により形成した後、厚さが4nm~6nm程度のSi酸化膜を900~1100程度の熱酸化により形成する。

### 【0037】

その後、図19(a)乃至(c)に示すように、フォトリソグラフィ技術及びエッチング技術により、ONO膜8をパターニングし、ONO膜8をセル領域内にのみ残存させる。即ち、論理回路領域203内のONO膜8を除去する。

### 【0038】

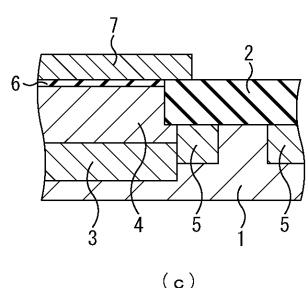

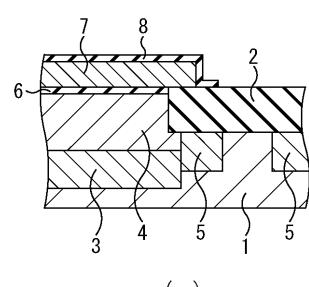

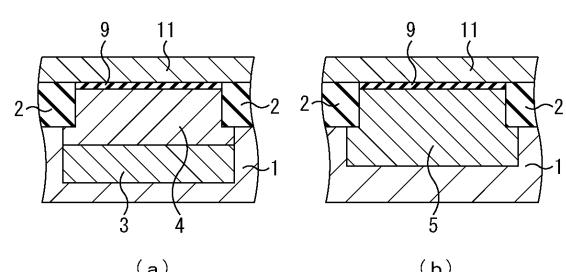

続いて、図20(a)乃至(c)に示すように、nMOS領域及びpMOS領域内に、750~900のウェット酸化によって、厚さが14nm~16nm程度のゲート酸化膜9を形成する。本実施形態では、nMOSトランジスタ101n及びpMOSトランジスタ101pとして、いずれも高電圧で動作するものを形成する。低電圧で動作するト

10

20

30

40

50

ランジスタ及び／又は中電圧で動作するトランジスタを混載する場合には、例えば、厚いゲート酸化膜の除去及び熱酸化を適当な回数だけ行えばよい。

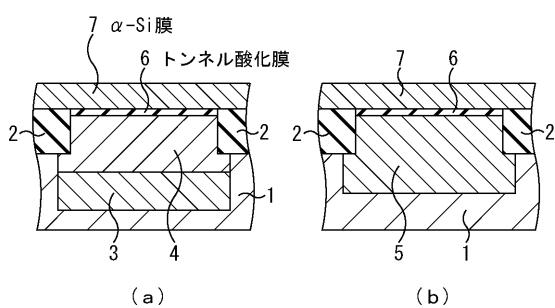

【0039】

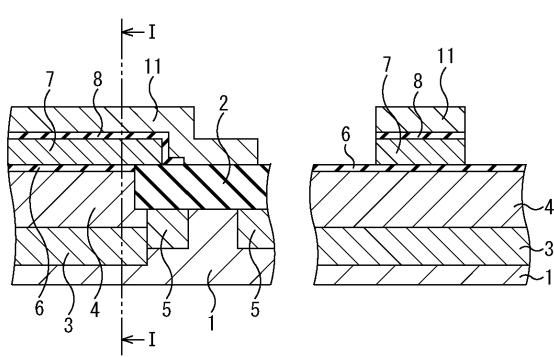

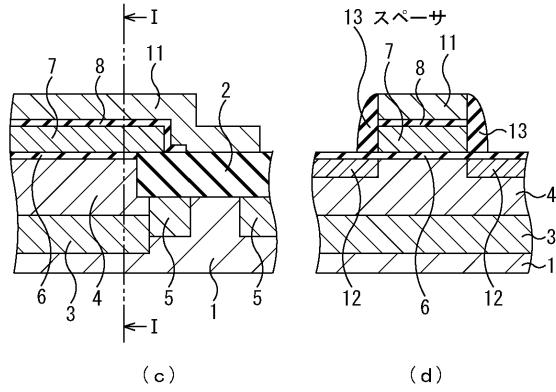

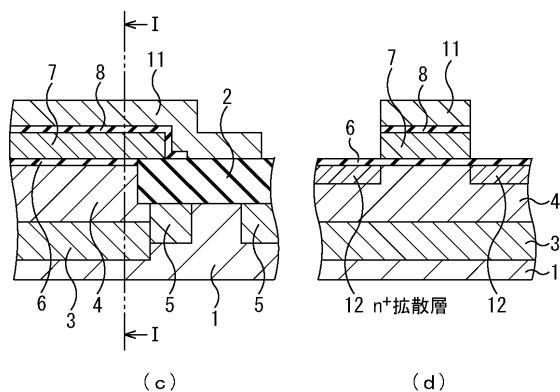

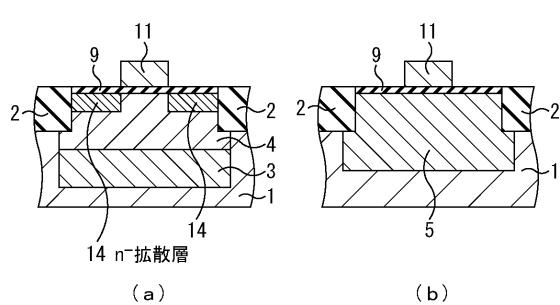

次に、図21(a)乃至(d)に示すように、不純物をドープしていないポリSi膜11を、CVD法により全面に150nm～200nm程度の厚さで形成する。

【0040】

次いで、図22(a)乃至(d)に示すように、フォトリソグラフィ技術及びエッチング技術により、セル領域内のポリSi膜11、ONO膜8及び-n-Si膜7をゲートの平面形状にパターニングする。

【0041】

その後、図23(a)乃至(d)に示すように、セル領域内に、ソース及びドレインとして、n<sup>+</sup>拡散層12を形成する。n<sup>+</sup>拡散層12の形成に当たっては、例えば砒素イオンを30keV～60keVのエネルギーで、ドーズ量を6×10<sup>14</sup>～1.5×10<sup>15</sup>とし、ポリSi膜11をマスクとしてイオン注入する。

【0042】

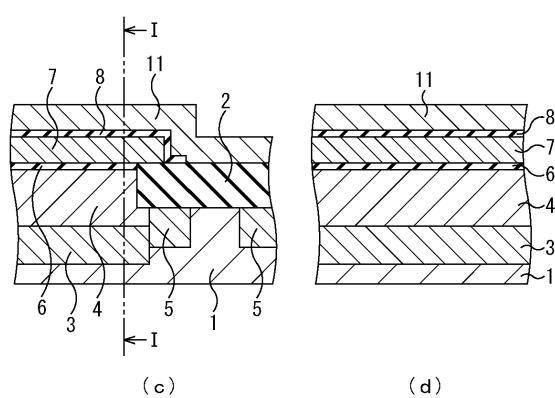

続いて、図24(a)乃至(d)に示すように、セル領域内に形成したゲートの側方にスペーサ13を形成する。スペーサ13の形成に当たっては、例えば厚さが100nm～120nm程度のSi窒化膜を形成した後、これを異方性エッチングすればよい。

【0043】

次に、図25(a)乃至(d)に示すように、フォトリソグラフィ技術及びエッチング技術により、nMOS領域及びpMOS領域内のポリSi膜11をゲートの平面形状にパターニングする。

【0044】

次いで、図26(a)乃至(d)に示すように、nMOS領域内にn<sup>-</sup>拡散層14を形成する。n<sup>-</sup>拡散層14の形成に当たっては、例えば砒素イオンを100keV～120keVのエネルギーで、ドーズ量を2×10<sup>13</sup>～3×10<sup>13</sup>とし、ポリSi膜11をマスクとしてイオン注入する。なお、低電圧で動作するトランジスタ及び／又は中電圧で動作するトランジスタを形成する場合には、イオン種、エネルギー及びドーズ量を適宜調整すればよい。

【0045】

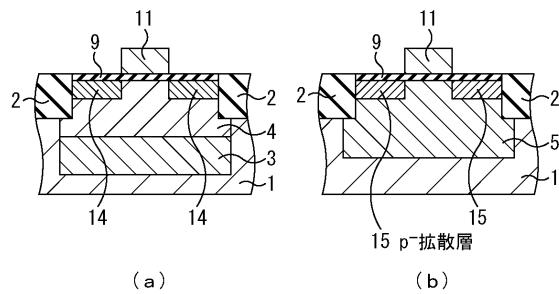

その後、図27(a)乃至(d)に示すように、pMOS領域内にp<sup>-</sup>拡散層15を形成する。p<sup>-</sup>拡散層15の形成に当たっては、例えばBF<sub>2</sub>イオンを100keV～120keVのエネルギーで、ドーズ量を2×10<sup>13</sup>～3×10<sup>13</sup>とし、ポリSi膜11をマスクとしてイオン注入する。なお、低電圧で動作するトランジスタ及び／又は中電圧で動作するトランジスタを形成する場合には、イオン種、エネルギー及びドーズ量を適宜調整すればよい。

【0046】

続いて、図28(a)乃至(d)に示すように、nMOS領域及びpMOS領域内に形成したゲートの側方にスペーサ16を形成する。スペーサ16の形成に当たっては、例えば厚さが100nm～120nm程度のSi酸化膜を形成した後、これを異方性エッチングすればよい。また、スペーサ16の形成に伴って、スペーサ13の側方にもSi酸化膜が形成され、実質的にスペーサ13が厚くなる。

【0047】

次に、図29(a)乃至(d)に示すように、nMOS領域内にn<sup>+</sup>拡散層17を形成する。n<sup>+</sup>拡散層17の形成に当たっては、例えばリンイオンを10keV～20keVのエネルギーで、ドーズ量を5×10<sup>15</sup>～8×10<sup>15</sup>とし、ポリSi膜11及びスペーサ16をマスクとしてイオン注入する。n<sup>-</sup>拡散層14及びn<sup>+</sup>拡散層17からLDD構造のソース104s及びドレイン104dが構成される。

【0048】

次いで、図30(a)乃至(d)に示すように、pMOS領域内にp<sup>+</sup>拡散層18を形

10

20

30

40

50

成する。 $p^+$ 拡散層18の形成に当たっては、例えばボロンイオンを3keV~5keVのエネルギーで、ドーズ量を $3 \times 10^{15}$ ~ $5 \times 10^{15}$ とし、ポリSi膜11及びスペーサ16をマスクとしてイオン注入する。 $p^-$ 拡散層15及び $p^+$ 拡散層18からLDD構造のソース106s及びドレイン106dが構成される。その後、ソース、ドレイン及びゲートの表面にシリサイド膜(図示せず)を形成する。シリサイド膜の形成に当たっては、例えば、Co膜を形成した後、窒化アニールを行う。

#### 【0049】

続いて、図31(a)乃至(d)に示すように、全面に層間絶縁膜19を形成し、その平坦化をCMPにより行う。層間絶縁膜19としては、例えばHDP膜等を形成する。

#### 【0050】

次に、図32(a)乃至(d)に示すように、フォトリソグラフィ技術及びエッチング技術により、夫々、セル領域内のポリSi膜7(図12中のコントロールゲートCG)及び $n^+$ 拡散層12、nMOS領域内のドレイン又はソース用の $n^+$ 拡散層17、並びにpMOS領域内のドレイン又はソース用の $p^+$ 拡散層18まで到達する複数のコンタクトホールを形成し、この内部にW等を埋め込むことにより、コンタクトプラグ20を形成する。次いで、第1層目の配線21(図12中の金属配線M1)を形成する。このとき、本実施形態では、配線21により、セル領域内のポリSi膜7(コントロールゲートCG)とドレイン又はソース用の $n^+$ 拡散層17及び $p^+$ 拡散層18とを互いに電気的に接続する。

#### 【0051】

その後、更に上層の層間絶縁膜及び配線等の形成を行うことにより、論理回路及びフラッシュメモリが混載された半導体装置を完成させる。例えば、上層配線としては、複数のCu配線を形成し、多層配線を形成するに当たっては、層間絶縁膜として低誘電率膜を形成すると共に、プラズマ処理を行うことが好ましい。更に、Cuの拡散防止膜としてSi窒化膜を形成することも好ましい。

#### 【0052】

このような方法によれば、フラッシュメモリ領域202内の配線のピッチを大きめに設定しても、フラッシュメモリ領域202の占有面積を予め比較的小さくしているため、ダイ201全体の面積の増加は極めて小さい。このため、ダイ201全体の面積の増加を抑制しながら、配線ピッチを大きめに設定することにより、各メモリのコントロールゲートCG(ポリSi膜7)と $n^+$ 拡散層17及び $p^+$ 拡散層18とを電気的に接続するための配線層としては、1層の配線21のみを用いればよい。また、これらの拡散層を備えた各MOSトランジスタは、保護ダイオードとしてのみではなくデコーダの一部として用いられる。従って、その設計及び製造のプロセスが簡素なものとなる。

#### 【0053】

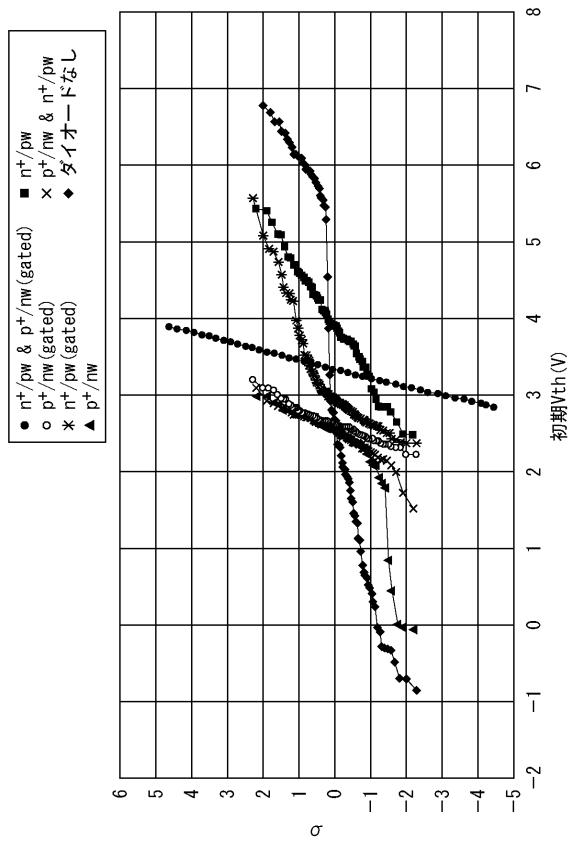

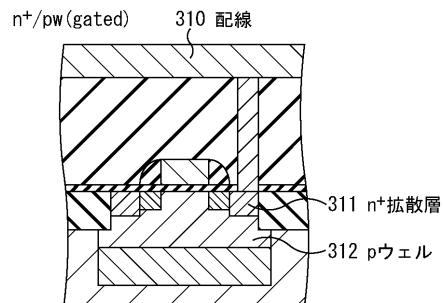

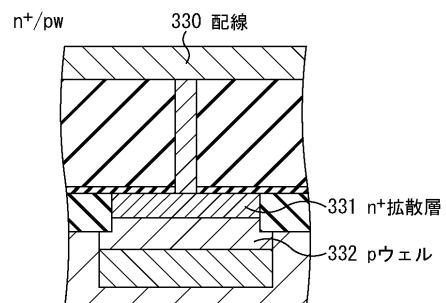

更に、夫々nMOSトランジスタ及びpMOSトランジスタのドレインを構成する $n^+$ 拡散層17及び $p^+$ 拡散層18にコントロールゲートCGを接続しているため、閾値電圧の変動も小さい。実際に、本願発明者が種々の保護ダイオードについて、製造後の初期閾値電圧Vthの測定を行ったところ、図33に示すような結果が得られた。図33中の「 $n^+ / p_w & p^+ / n_w$  (gated)」が本発明の実施形態により製造された半導体装置についての結果を示している。

#### 【0054】

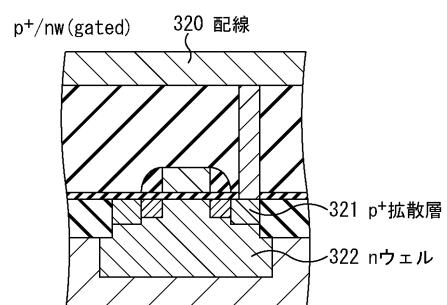

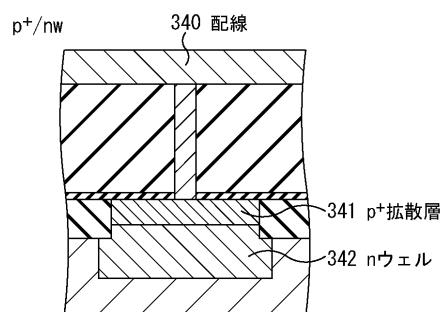

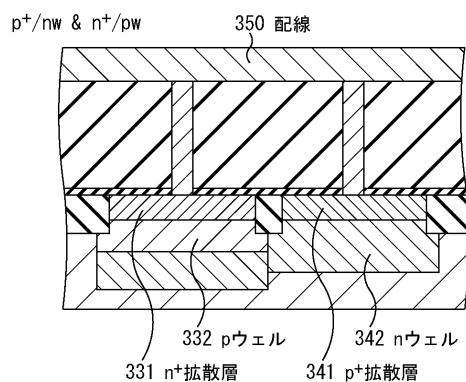

また、「 $p^+ / n_w$  (gated)」は図40に示す従来の保護ダイオード(pMOSトランジスタのnウェル322上の $p^+$ 拡散層321に、配線320を介してコントロールゲートを接続するもの)についての結果を示し、「 $n^+ / p_w$  (gated)」は図39に示す従来の保護ダイオード(nMOSトランジスタのpウェル312上の $n^+$ 拡散層311に、配線310を介してコントロールゲートを接続するもの)についての結果を示し、「 $p^+ / n_w$ 」は図42に示す保護ダイオード(ダイオードのnウェル342上の $p^+$ 拡散層341に、配線340を介してコントロールゲートを接続するもの)についての結果を示し、「 $n^+ / p_w$ 」は図41に示す従来の保護ダイオード(ダイオードのpウェル332上の $n^+$ 拡散層331に、配線330を介してコントロールゲートを接続するもの

10

20

30

40

50

)についての結果を示し、「p<sup>+</sup> / n w & n<sup>+</sup> / p W」は図43に示す従来の保護ダイオード(2個のダイオードのn<sup>+</sup>拡散層及びp<sup>+</sup>拡散層にコントロールゲートを接続するもの)についての結果を示し、「保護ダイオードなし」はコントロールゲートに保護ダイオードを接続しなかった場合の結果を示している。

【0055】

図33に示すように、本発明の実施形態により製造された半導体装置において、初期V<sub>t</sub>hの変動が最も小さくなつた。このことから、本実施形態によれば、フラッシュメモリの製造中にコントロールゲートに電荷が発生したとしても、保護ダイオードから極めて効果的にこの電荷を排除することができるといえる。このため、紫外線照射を行わなくとも、使用中の発熱によつても、不要な電荷の移動が生じにくく、閾値電圧が変動しにくく。

10

【0056】

なお、保護ダイオードとして用いられるnMOSトランジスタ及びpMOSトランジスタのレイアウトは特に限定されず、例えば図34又は図35に示すものを採用してもよい。

【0057】

コントロールゲートCGが延びる方向に対して直交する方向で隣り合う2個のトランジスタについて、図12に示す例では、互いに線対称となるようにしているが、図34に示す例では、互いに繰り返しとなるようにする。また、図35に示す例では、金属配線M1の配置に関し、これら4個のトランジスタのゲートを基準として、コントロールゲートCGが延びる方向で隣り合う2組の間で互いに異なる側に位置するソース・ドレインに金属配線M1が接続されるようとする。また、コントロールゲートCGが延びる方向に対して直交する方向で隣り合う2個のトランジスタについては、互いに繰り返しとなるようする。

20

【0058】

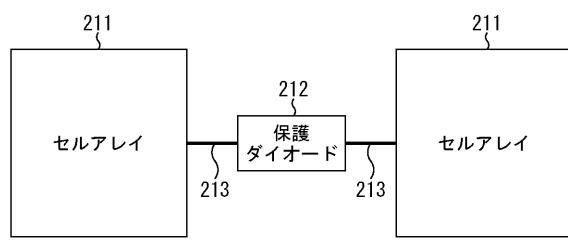

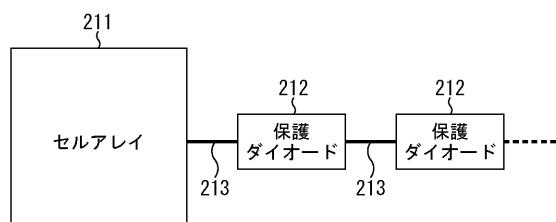

図34又は図35に示すレイアウトと図12に示すレイアウトとを比較すると、nMOSトランジスタ101n又はpMOSトランジスタ101pを形成する素子活性領域同士の間隔が、図34又は図35に示すレイアウトにおいて広くなる。このため、より高い歩留りで製造することができる。更に、図35に示すレイアウトを採用した場合には、図36(a)に示すように、互いに分離して配置された2個のセルアレイ211に、1対のnMOSトランジスタ及びpMOSトランジスタからなる保護ダイオード212を、最下層の単層の配線213を介して接続することも可能となる。また、図36(b)に示すように、1個のセルアレイ211に、複数の保護ダイオード212を接続することも可能となる。

30

【0059】

従来、チップ全体にメモリセルが配置されたフラッシュメモリ等の不揮発性メモリに保護ダイオードを接続することも検討されているが、このような不揮発性メモリでは、製造のための工程数よりも集積度が重視されているため、配線間のピッチが極めて狭い。このため、図37及び図38に示すように、上述の実施形態のように、コントロールゲートCGをnMOSトランジスタ及びpMOSトランジスタのソース又はドレインに、単層の金属配線M1を介して接続することは不可能である。

40

【0060】

以下、本発明の諸態様を付記としてまとめて記載する。

【0061】

(付記1)

半導体基板の表面に、不揮発性メモリセル、nMOSトランジスタ及びpMOSトランジスタを形成する工程と、

前記不揮発性メモリセル、nMOSトランジスタ及びpMOSトランジスタを覆う層間絶縁膜を形成する工程と、

前記層間絶縁膜中に、夫々、前記不揮発性メモリセルのコントロールゲート、前記nMOSトランジスタのソース又はドレイン、前記pMOSトランジスタのソース又はドレイ

50

ンに接続される複数個のコンタクトプラグを形成する工程と、

前記複数個のコンタクトプラグを介して、前記コントロールゲートと前記nMOSトランジスタ及びpMOSトランジスタのソース又はドレインとを接続する配線を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【0062】

(付記2)

前記配線として、単層の配線を形成することを特徴とする付記1に記載の半導体装置の製造方法。

【0063】

(付記3)

前記不揮発性メモリセルを複数個形成して、不揮発性メモリセルアレイを形成し、

前記nMOSトランジスタ及びpMOSトランジスタを、前記不揮発性メモリセルアレイの動作を制御する制御回路内のデコーダを構成する素子として形成することを特徴とする付記1又は2に記載の半導体装置の製造方法。

【0064】

(付記4)

エンベッデッド型の構造とすることを特徴とする付記1乃至3のいずれか1項に記載の半導体装置の製造方法。

【0065】

(付記5)

前記配線を形成する工程の後に、前記コントロールゲートに接続される複数の上層配線を形成する工程を有することを特徴とする付記1乃至4のいずれか1項に記載の半導体装置の製造方法。

【0066】

(付記6)

前記複数の上層配線を形成する工程の間に、低誘電率膜を層間絶縁膜として形成する工程を有することを特徴とする付記5に記載の半導体装置の製造方法。

【0067】

(付記7)

前記上層配線として、Cu配線を形成し、

前記複数の上層配線を形成する工程の間に、Si窒化膜を形成する工程を有することを特徴とする付記5又は6に記載の半導体装置の製造方法。

【0068】

(付記8)

前記複数の上層配線を形成する工程の間に、プラズマ処理を行う工程を有することを特徴とする付記5乃至7のいずれか1項に記載の半導体装置の製造方法。

【0069】

(付記9)

前記不揮発性メモリセル、nMOSトランジスタ及びpMOSトランジスタを形成する工程は、前記不揮発性メモリセル用のウェルと前記nMOSトランジスタ用のウェルとを同時に形成する工程を有することを特徴とする付記1乃至8のいずれか1項に記載の半導体装置の製造方法。

【0070】

(付記10)

前記不揮発性メモリセル、nMOSトランジスタ及びpMOSトランジスタを形成する工程は、前記コントロールゲートと前記nMOSトランジスタのゲートと前記pMOSトランジスタのゲートとを同一の材料から形成する工程を有することを特徴とする付記1乃至9のいずれか1項に記載の半導体装置の製造方法。

【0071】

10

20

30

40

50

(付記 1 1)

前記コントロールゲート、前記 n M O S トランジスタのゲート及び前記 p M O S トランジスタのゲートを、不純物がドープされていない多結晶 S i 膜から形成することを特徴とする付記 1 0 に記載の半導体装置の製造方法。

【0072】

(付記 1 2)

前記不揮発性メモリのフローティングゲートを、リンがドープされたアモルファス S i 膜を形成することを特徴とする付記 1 乃至 1 1 のいずれか 1 項に記載の半導体装置の製造方法。

【0073】

(付記 1 3)

前記コントロールゲートの平面形状を、直線状に延びる形状とすることを特徴とする付記 1 乃至 1 2 のいずれか 1 項に記載の半導体装置の製造方法。

【0074】

(付記 1 4)

面積に関し、前記不揮発性メモリセルアレイの占有率を 2 % 乃至 5 % とすることを特徴とする付記 3 乃至 1 3 のいずれか 1 項に記載の半導体装置の製造方法。

【0075】

(付記 1 5) 半導体基板の表面に形成されてなる、不揮発性メモリセル、n M O S トランジスタ及び p M O S トランジスタと、

前記不揮発性メモリセル、n M O S トランジスタ及び p M O S トランジスタを覆う層間絶縁膜と、

前記層間絶縁膜中に、夫々、前記不揮発性メモリセルのコントロールゲート、前記 n M O S トランジスタのソース又はドレイン、前記 p M O S トランジスタのソース又はドレンに接続されてなる複数個のコンタクトプラグと、

前記複数個のコンタクトプラグを介して、前記コントロールゲートと前記 n M O S トランジスタ及び p M O S トランジスタのソース又はドレンとを接続する配線と、

を有することを特徴とする半導体装置。

【0076】

(付記 1 6) 前記配線は単層の配線であることを特徴とする付記 1 5 に記載の半導体装置。

【0077】

(付記 1 7)

複数個の前記不揮発性メモリセルから不揮発性メモリセルアレイが構成されており、

前記 n M O S トランジスタ及び p M O S トランジスタは、前記不揮発性メモリセルアレイの動作を制御する制御回路内のデコーダを構成する素子であることを特徴とする付記 1 5 又は 1 6 に記載の半導体装置。

【0078】

(付記 1 8)

エンベッデッド型の構造であることを特徴とする付記 1 5 乃至 1 7 のいずれか 1 項に記載の半導体装置。

【0079】

(付記 1 9)

前記コントロールゲートに接続される複数の上層配線を有することを特徴とする付記 1 5 乃至 1 8 のいずれか 1 項に記載の半導体装置。

【0080】

(付記 2 0)

前記複数の上層配線の層間絶縁膜として、低誘電率膜が形成されていることを特徴とする付記 1 9 に記載の半導体装置。

【0081】

10

20

30

40

50

(付記 21)

前記上層配線として、Cu配線を有し、

前記複数の上層配線の層間絶縁膜として、Si窒化膜が形成されていることを特徴とする付記19又は20に記載の半導体装置。

【0082】

(付記 22)

前記不揮発性メモリセル、nMOSトランジスタ及びpMOSトランジスタは、前記コントロールゲートと前記nMOSトランジスタのゲートと前記pMOSトランジスタのゲートとを同一の材料から形成されてなることを特徴とする付記15乃至21のいずれか1項に記載の半導体装置。

10

【0083】

(付記 23)

前記コントロールゲート、前記nMOSトランジスタのゲート及び前記pMOSトランジスタのゲートを、不純物がドープされていない多結晶Si膜から形成することを特徴とする付記22に記載の半導体装置。

【0084】

(付記 24)

前記不揮発性メモリのフローティングゲートは、リンがドープされたアモルファスSi膜であることを特徴とする付記15乃至23のいずれか1項に記載の半導体装置。

20

【0085】

(付記 25)

前記コントロールゲートは、その平面形状が直線状に延びる形状であることを特徴とする付記15乃至24のいずれか1項に記載の半導体装置。

【0086】

(付記 26)

面積に関し、前記不揮発性メモリセルアレイの占有率が2%乃至5%であることを特徴とする付記17乃至25のいずれか1項に記載の半導体装置。

30

【0087】

(付記 27) 半導体基板の表面に不揮発性メモリセルを形成する工程と、

前記不揮発性メモリセルのコントロールゲートに接続される複数の上層配線としてCu配線を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

40

【0088】

(付記 28) 前記Cu配線の拡散防止膜としてSi窒化膜を形成する工程を有することを特徴とする付記27に記載の半導体装置の製造方法。

【0089】

(付記 29) 半導体基板の表面に不揮発性メモリセルを形成する工程と、

低誘電率膜を層間絶縁膜として形成するとともに、前記不揮発性メモリセルのコントロールゲートに接続される複数の上層配線を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【0090】

(付記 30) 半導体基板の表面に、前記不揮発性メモリセルとともに保護ダイオードを形成することを特徴とする付記27乃至29のいずれか1項に記載の半導体装置の製造方法。

【0091】

(付記 31) 前記保護ダイオードは、nMOSトランジスタ及びpMOSトランジスタであることを特徴とする付記30に記載の半導体装置の製造方法。

【0092】

(付記 32) 前記保護ダイオードは、前記nMOSトランジスタのn<sup>+</sup>拡散層を有するソース又はドレインがpウェル内に形成されており、前記pMOSトランジスタのp<sup>+</sup>拡

50

散層を有するソース又はドレインがnウェル内に形成されてなることを特徴とする付記31に記載の半導体装置の製造方法。

【0093】

(付記33) 半導体基板の表面に、不揮発性メモリセル及び保護ダイオードを形成する工程と、

前記不揮発性メモリセルのコントロールゲートと前記保護ダイオードの拡散層とを接続する単層の金属配線を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

【0094】

(付記34) 前記保護ダイオードは、nMOSトランジスタ及びpMOSトランジスタであることを特徴とする付記33に記載の半導体装置の製造方法。 10

【0095】

(付記35) 前記保護ダイオードは、前記nMOSトランジスタのn<sup>+</sup>拡散層を有するソース又はドレインがpウェル内に形成されており、前記pMOSトランジスタのp<sup>+</sup>拡散層を有するソース又はドレインがnウェル内に形成されてなることを特徴とする付記34に記載の半導体装置の製造方法。

【0096】

(付記36) 半導体基板の表面に形成された不揮発性メモリセルと、

前記不揮発性メモリセルのコントロールゲートに接続された複数の上層配線であるCu配線と、

を有することを特徴とする半導体装置。 20

【0097】

(付記37) 前記Cu配線の拡散防止膜としてSi窒化膜を有することを特徴とする付記36に記載の半導体装置。

【0098】

(付記38) 半導体基板の表面に形成された不揮発性メモリセルと、

前記不揮発性メモリセルのコントロールゲートに接続される複数の上層配線と、

前記上層配線を覆う層間絶縁膜である低誘電率膜と、

を有することを特徴とする半導体装置。

【0099】

(付記39) 半導体基板の表面に、前記不揮発性メモリセルとともに保護ダイオードを有することを特徴とする付記36乃至38のいずれか1項に記載の半導体装置。 30

【0100】

(付記40) 前記保護ダイオードは、nMOSトランジスタ及びpMOSトランジスタであることを特徴とする付記39に記載の半導体装置。

【0101】

(付記41) 前記保護ダイオードは、前記nMOSトランジスタのn<sup>+</sup>拡散層を有するソース又はドレインがpウェル内に形成されており、前記pMOSトランジスタのp<sup>+</sup>拡散層を有するソース又はドレインがnウェル内に形成されてなることを特徴とする付記40に記載の半導体装置。 40

【0102】

(付記42) 半導体基板の表面に形成されてなる不揮発性メモリセル及び保護ダイオードと、

前記不揮発性メモリセルのコントロールゲートと前記保護ダイオードの拡散層とを接続する単層の金属配線と、

を有することを特徴とする半導体装置。

【0103】

(付記43) 前記保護ダイオードは、nMOSトランジスタ及びpMOSトランジスタであることを特徴とする付記42に記載の半導体装置。

【0104】

(付記 4 4) 前記保護ダイオードは、前記 n M O S トランジスタの  $n^+$  拡散層を有するソース又はドレインが p ウェル内に形成されており、前記 p M O S トランジスタの  $p^+$  拡散層を有するソース又はドレインが n ウェル内に形成されてなることを特徴とする付記 4 3 に記載の半導体装置。

【図面の簡単な説明】

【0 1 0 5】

【図 1】正孔の移動を示す模式図である。

【図 2】電子の移動を示す模式図である。

【図 3】正孔の増加を示す模式図である。

【図 4】電子の増加を示す模式図である。

10

【図 5】正孔のトラップに伴う閾値電圧の変動を示す図である。

【図 6】電子のトラップに伴う閾値電圧の変動を示す図である。

【図 7】紫外線照射による電荷の消去を示す図である。

【図 8】紫外線照射によっても電荷が消去されない機構を示す図である。

【図 9】発熱による正孔の移動に伴う閾値電圧の変動を示す図である。

【図 10】発熱による電子の移動に伴う閾値電圧の変動を示す図である。

【図 11】本発明の実施形態に方法によって製造する半導体装置の全体像を示すレイアウト図である。

【図 12】図 11 中の一部を拡大して示すレイアウト図である。

20

【図 13】本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 14】図 13 に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 15】図 14 に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 16】図 15 に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 17】図 16 に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 18】図 17 に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

30

【図 19】図 18 に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 20】図 19 に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 21】図 20 に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 22】図 21 に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 23】図 22 に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

40

【図 24】図 23 に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 25】図 24 に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 26】図 25 に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 27】図 26 に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図 28】図 27 に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

50

【図29】図28に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図30】図29に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図31】図30に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図32】図31に引き続き、本発明の実施形態に係る半導体装置の製造方法を工程順に示す断面図である。

【図33】初期閾値電圧  $V_{th}$  のばらつきを示すグラフである。

10

【図34】保護ダイオードの一例を示すレイアウト図である。

【図35】保護ダイオードの他の一例を示すレイアウト図である。

【図36】セルアレイと保護ダイオードとの関係を示す模式図である。

【図37】実現不可能なレイアウトの一例を示すレイアウト図である。

【図38】実現不可能なレイアウトの他の一例を示すレイアウト図である。

【図39】従来の保護ダイオードの一例を示す断面図である。

【図40】従来の保護ダイオードの他の一例を示す断面図である。

【図41】従来の保護ダイオードの他の一例を示す断面図である。

【図42】従来の保護ダイオードの他の一例を示す断面図である。

【図43】従来の保護ダイオードの他の一例を示す断面図である。

【符号の説明】

20

【0106】

1 : Si 基板

2 : 素子分離絶縁膜

3 : n ウェル

4 : p ウェル

5 : n ウェル

6 : トンネル酸化膜

30

7 : - Si 膜

8 : ONO 膜

9 : ゲート酸化膜

11 : ポリ Si 膜

12 : n<sup>+</sup>拡散層

13 : スペーサ

14 : n<sup>-</sup>拡散層

15 : p<sup>-</sup>拡散層

16 : スペーサ

17 : n<sup>+</sup>拡散層

18 : p<sup>+</sup>拡散層

19 : 層間絶縁膜

40

20 : コンタクトプラグ

21 : 配線

101p : pMOS トランジスタ

101n : nMOS トランジスタ

102 : 素子分離絶縁膜

103 : p ウェル

104d : ドレイン

104s : ソース

105 : n ウェル

106d : ドレイン

106s : ソース

50

201：ダイ

202：フラッシュメモリ領域

203：論理回路領域

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

(a)

(b)

【図8】

(a)

(b)

【図9】

(a)

(b)

【図10】

(a)

(b)

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

(d)

(d)

【図23】

【図24】

【図25】

【図26】

【図27】

(a)

(b)

【図28】

(a)

(b)

(a)

(b)

(a)

(b)

【図29】

(a)

(b)

【図30】

(a)

(b)

(a)

(b)

(a)

(b)

【 図 3 1 】

### 【図32】

【 図 3 3 】

【 図 3 4 】

【図35】

【図36】

(a)

(b)

【 図 3 7 】

【 図 3 8 】

【図39】

【図41】

【図40】

【図42】

【図43】

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

H 01L 27/04 (2006.01)

H 01L 27/04

H

H 01L 21/822 (2006.01)

F ターム(参考) 5F083 EP02 EP23 EP55 EP56 GA11 JA04 JA33 JA35 JA37 JA39

MA06 MA19 NA01 PR21 PR33 PR36 PR40 PR46 PR56 ZA12

ZA30

5F101 BA19 BA29 BA36 BB05 BD02 BD35 BD36 BD45 BE07 BH02

BH03 BH09 BH14 BH19