(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6069137号

(P6069137)

(45) 発行日 平成29年2月1日(2017.2.1)

(24) 登録日 平成29年1月6日(2017.1.6)

(51) Int.Cl.

F 1

|              |           |      |       |         |

|--------------|-----------|------|-------|---------|

| HO1L 27/115  | (2017.01) | HO1L | 27/10 | 4 3 4   |

| HO1L 21/336  | (2006.01) | HO1L | 29/78 | 3 7 1   |

| HO1L 29/788  | (2006.01) | HO1L | 27/10 | 3 8 1   |

| HO1L 29/792  | (2006.01) | G11C | 17/00 | 6 2 1 A |

| HO1L 21/8244 | (2006.01) | G11C | 17/00 | 6 2 5   |

請求項の数 7 (全 19 頁) 最終頁に続く

|            |                                     |

|------------|-------------------------------------|

| (21) 出願番号  | 特願2013-182777 (P2013-182777)        |

| (22) 出願日   | 平成25年9月4日(2013.9.4)                 |

| (62) 分割の表示 | 特願2012-231439 (P2012-231439)<br>の分割 |

| 原出願日       | 平成24年10月19日(2012.10.19)             |

| (65) 公開番号  | 特開2014-86722 (P2014-86722A)         |

| (43) 公開日   | 平成26年5月12日(2014.5.12)               |

| 審査請求日      | 平成27年10月16日(2015.10.16)             |

|           |                                               |

|-----------|-----------------------------------------------|

| (73) 特許権者 | 511229547<br>株式会社フローディア<br>東京都小平市小川東町1丁目30番9号 |

| (74) 代理人  | 100137800<br>弁理士 吉田 正義                        |

| (74) 代理人  | 100148253<br>弁理士 今枝 弘充                        |

| (74) 代理人  | 100148079<br>弁理士 梅村 裕明                        |

| (74) 代理人  | 100158241<br>弁理士 吉田 安子                        |

| (72) 発明者  | 谷口 泰弘<br>東京都小平市小川東町1丁目29番9号<br>株式会社フローディア内    |

最終頁に続く

(54) 【発明の名称】不揮発性半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

電気的に絶縁された複数のフローティングゲートと、第1ビット線および第2ビット線とを備え、前記フローティングゲート毎にセルを構成した不揮発性半導体記憶装置であって、

各前記セルは、

前記フローティングゲート内の電荷の有無に応じた電圧を読み出すためのリードトランジスタと、前記フローティングゲートに電荷を注入するプログラムトランジスタと、前記フローティングゲートから電荷を引き抜くイレーストランジスタと、前記フローティングゲートの電位を調整するコントロールキャパシタとを備え、前記リードトランジスタ、前記プログラムトランジスタ、前記イレーストランジスタ、および前記コントロールキャパシタの各活性領域上に前記フローティングゲートが延在しており、

一の前記セルは、

前記第1ビット線が前記一のセルのスイッチトランジスタを介して前記一のセルの前記リードトランジスタに接続され、前記第2ビット線が前記一のセルの前記プログラムトランジスタに直接接続された構成を有し、

前記一のセルと対をなす他の前記セルは、

前記第2ビット線が前記他のセルのスイッチトランジスタを介して前記他のセルの前記リードトランジスタに接続され、前記第1ビット線が前記他のセルの前記プログラムトランジスタに直接接続された構成を有しております、

10

20

前記第1ビット線は、前記一のセルのスイッチトランジスタがオフ動作している場合には前記他のセルのデータ書き込み用となり、前記一のセルのスイッチトランジスタがオン動作している場合には前記一のセルのデータ読み出し用となり、

前記第2ビット線は、前記他のセルのスイッチトランジスタがオフ動作している場合には前記一のセルのデータ書き込み用となり、前記他のセルのスイッチトランジスタがオン動作している場合には前記他のセルのデータ読み出し用となる

ことを特徴とする不揮発性半導体記憶装置。

#### 【請求項2】

前記一のセルと、前記一のセルと対をなす前記他のセルとは、

電気的に絶縁された第1活性領域、第2活性領域、第3活性領域、および第4活性領域に亘

つて並列に形成されている

ことを特徴とする請求項1記載の不揮発性半導体記憶装置。

#### 【請求項3】

前記一のセルにおける前記リードトランジスタおよび前記スイッチトランジスタと、前

記他のセルにおける前記プログラムトランジスタとが同じ活性領域に形成されており、

前記他のセルにおける前記リードトランジスタおよび前記スイッチトランジスタと、前

記一のセルにおける前記プログラムトランジスタとが該活性領域とは異なる他の同じ活性

領域に形成されている

ことを特徴とする請求項1または2記載の不揮発性半導体記憶装置。

#### 【請求項4】

各前記セルは、

前記イレーストランジスタがN型ウェルに形成され、前記コントロールキャパシタが該

N型ウェルと異なるN型ウェルに形成されており、

前記リードトランジスタ、前記スイッチトランジスタおよび前記プログラムトランジス

タがP型ウェルに形成されている

ことを特徴する請求項1記載の不揮発性半導体記憶装置。

#### 【請求項5】

前記フローティングゲート毎に設けた前記イレーストランジスタに共通の電圧を一律に

印加するイレースゲート線と、

前記フローティングゲート毎に設けた前記リードトランジスタに共通の電圧を一律に印

加するソース線と

を備えることを特徴とする請求項1～4のうちいずれか1項記載の不揮発性半導体記憶

装置。

#### 【請求項6】

前記一のセルと前記他のセルとで1ビットを構成し、

前記セル毎に設けられた各前記スイッチトランジスタには個別にゲート線が接続されて

おり、各前記スイッチトランジスタが独立にオンオフ制御される

ことを特徴とする請求項1～5のうちいずれか1項記載の不揮発性半導体記憶装置。

#### 【請求項7】

前記第1ビット線がS R A Mセルの一のストレージノードに接続され、前記第2ビット線

が前記S R A Mセルの前記一のストレージノードと相補的な他のストレージノードに接続

されており、

前記S R A Mセルと、前記一のセルおよび前記他のセルの2セルとから1ビットを構成す

る

ことを特徴とする請求項1～6のうちいずれか1項記載の不揮発性半導体記憶装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0 0 0 1】

本発明は、不揮発性半導体記憶装置に関し、例えば単層のポリシリコンを用いて製造さ

れる不揮発性半導体記憶装置に適用して好適なものである。

10

20

30

40

50

**【背景技術】****【0002】**

一般に、単層ポリシリコンによる不揮発性半導体記憶装置は、ウェルをコントロールゲートとして利用する大面積のキャパシタと、データ読み出し用のMOS (Metal-Oxide-Semiconductor) ランジスタ（以下、単にリードトランジスタと呼ぶ）とを構成要素として持つことが多い。従来では、さらに消去機能を追加するために、別のキャパシタを付加し、不揮発性半導体記憶装置として使われている。

**【0003】**

特表2009-538519号公報（以下、特許文献1と呼ぶ）は、その一例であり、PMOSアクセストランジスタがリードトランジスタとして設けられており、データの読み出し動作時、このリードトランジスタに流れる電流を検知し、それによって対応するフローティングゲートにデータが書き込まれているか、或いは消去されているかを判定し得る。また、この特許文献1では、データの消去動作時、このリードトランジスタのゲート絶縁膜の両端間に高い電圧降下を発生させ、当該リードトランジスタのゲート絶縁膜を介してフローティングゲートから電荷を引き抜いてメモリセルからデータを消去し得るようになされている。

10

**【0004】**

さらに、この特許文献1では、他の実施例として、リードトランジスタとしてNMOSアクセストランジスタを設け、フローティングゲートにデータを書き込む際、このリードトランジスタのチャネルからフローティングゲート内に電荷をトンネルさせ、フローティングゲートにデータを書き込むような構成についても開示されている。

20

**【0005】**

しかしながら、一般に電荷が通過したゲート絶縁膜の領域では、ゲート絶縁膜への印加電界やホットキャリアのストレスによって電荷通過領域にダメージが与えられてしまう。そのため、データの書き込み動作や消去動作時にゲート絶縁膜を電荷が通過する従来のリードトランジスタでは、ゲート絶縁膜にダメージが与えられ、界面準位の生成などにより、このリードトランジスタから得られる読み出し電流が低下してしまい、誤動作が発生する虞があるという問題があった。

**【0006】**

また、特許文献1のようにリードトランジスタをデータの書き込みに用いると、例えばリードトランジスタのサイドウォール領域に電荷の一部が注入されてしまうこともある。サイドウォール領域内の電荷は除去することが困難であり、リードトランジスタでは、データの書き込みが繰り返されることにより、閾値電圧（リードトランジスタがオフからオンに切り替わるときの電圧であり、以下、 $V_{th}$ と呼ぶ）がシフトして誤動作が発生してしまう虞があるという問題があった。

30

**【0007】**

このような問題点を解決する構成としては、データの書き込み時および消去時にリードトランジスタを電荷の移動経路に用いないような構成が考えられる。この場合、特開2005-175411号公報（以下、特許文献2と呼ぶ）に示す不揮発性半導体記憶装置のように、書き込みの選択・非選択を決定するための書き込み用のビット線と、読み出し用のビット線とを独立に設け、これらビット線によって、データ書き込み時および消去時にリードトランジスタ領域が電荷の移動経路とならない構成を実現し得る。

40

**【先行技術文献】****【特許文献】****【0008】**

【特許文献1】特表2009-538519号公報

【特許文献2】特開2005-175411号公報

**【発明の概要】****【発明が解決しようとする課題】****【0009】**

50

しかしながら、このような構成でなる不揮発性半導体記憶装置では、書き込みの選択・非選択を決定するための書き込み用のビット線に加えて、これとは別に読み出し用のビット線も独立に必要となることから、制御するビット線の本数が2倍となってしまい、セル面積の増大を招く他、メモリマット周辺の制御回路が複雑化し、制御回路の面積増大をも招くという問題があった。

#### 【0010】

そこで、本発明は以上の点を考慮してなされたもので、ビット線本数を増やすことなく、リードトランジスタの誤作動を確実に防止し得る不揮発性半導体記憶装置を提案することを目的とする。

#### 【課題を解決するための手段】

10

#### 【0011】

かかる課題を解決するため本発明の請求項1は、電気的に絶縁された複数のフローティングゲートと、第1ビット線および第2ビット線とを備え、前記フローティングゲート毎にセルを構成した不揮発性半導体記憶装置であって、各前記セルは、前記フローティングゲート内の電荷の有無に応じた電圧を読み出すためのリードトランジスタと、前記フローティングゲートに電荷を注入するプログラムトランジスタと、前記フローティングゲートから電荷を引き抜くイレーストランジスタと、前記フローティングゲートの電位を調整するコントロールキャパシタとを備え、前記リードトランジスタ、前記プログラムトランジスタ、前記イレーストランジスタ、および前記コントロールキャパシタの各活性領域上に前記フローティングゲートが延在しており、一の前記セルは、前記第1ビット線が前記一のセルのスイッチトランジスタを介して前記一のセルの前記リードトランジスタに接続され、前記第2ビット線が前記一のセルの前記プログラムトランジスタに直接接続された構成を有し、前記一のセルと対をなす他の前記セルは、前記第2ビット線が前記他のセルのスイッチトランジスタを介して前記他のセルの前記リードトランジスタに接続され、前記第1ビット線が前記他のセルの前記プログラムトランジスタに直接接続された構成を有しており、前記第1ビット線は、前記一のセルのスイッチトランジスタがオフ動作している場合には前記他のセルのデータ書き込み用となり、前記一のセルのスイッチトランジスタがオン動作している場合には前記一のセルのデータ読み出し用となり、前記第2ビット線は、前記他のセルのスイッチトランジスタがオフ動作している場合には前記一のセルのデータ書き込み用となり、前記他のセルのスイッチトランジスタがオン動作している場合には前記一のセルのデータ読み出し用となることを特徴とする。

20

#### 【発明の効果】

#### 【0012】

本発明によれば、スイッチトランジスタの切り替えによって、一方のセルのプログラムトランジスタに接続されてデータ書き込み用となる第2ビット線が、他方のセルにて読み出し用のビット線を兼ねつつ、データの書き込み時および消去時に電荷移動経路となるプログラムトランジスタおよびイレーストランジスタを設けたことにより、ビット線本数を増やすことなく、データ書き込みや消去に用いられることにより生じてしまうリードトランジスタの誤作動を確実に防止し得る。

#### 【図面の簡単な説明】

40

#### 【0013】

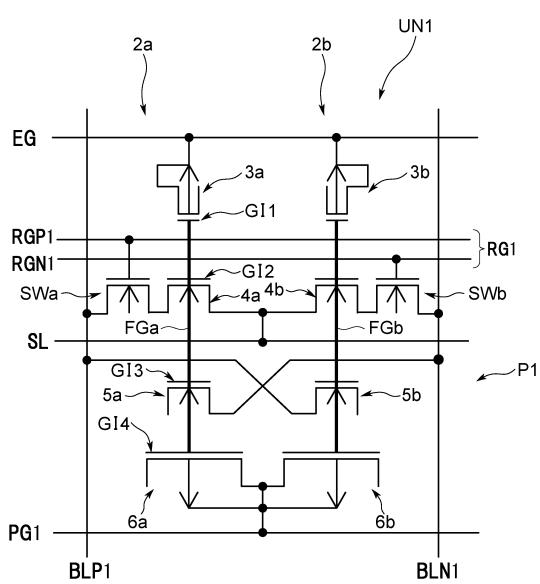

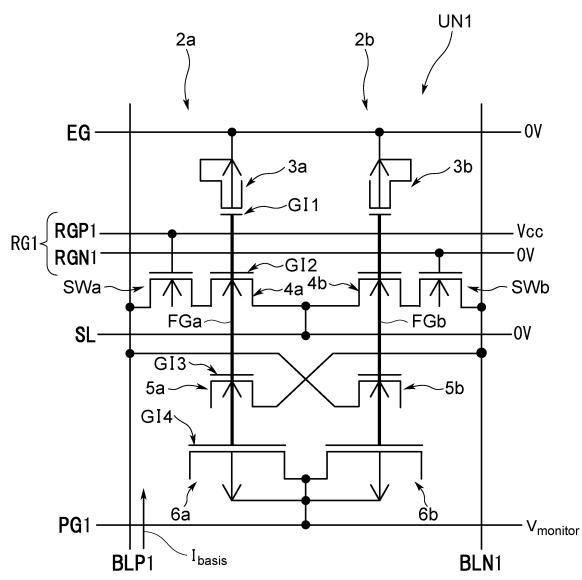

【図1】メモリユニットの回路構成を示す回路図である。

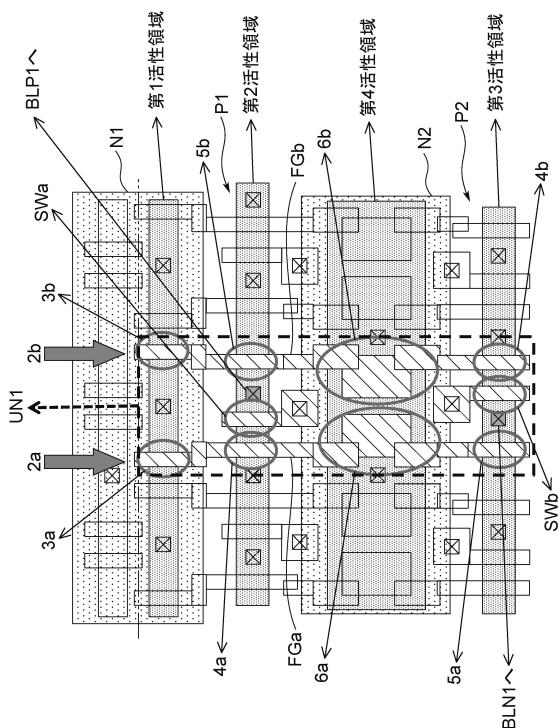

【図2】図1に示したメモリユニットの回路構成のレイアウトを示す概略図である。

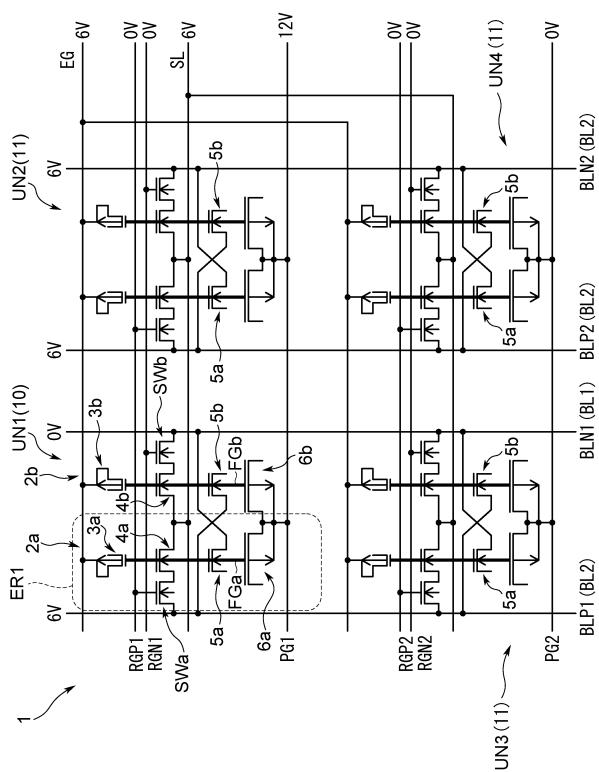

【図3】データの書き込み時における各部位の電圧値を示す回路図である。

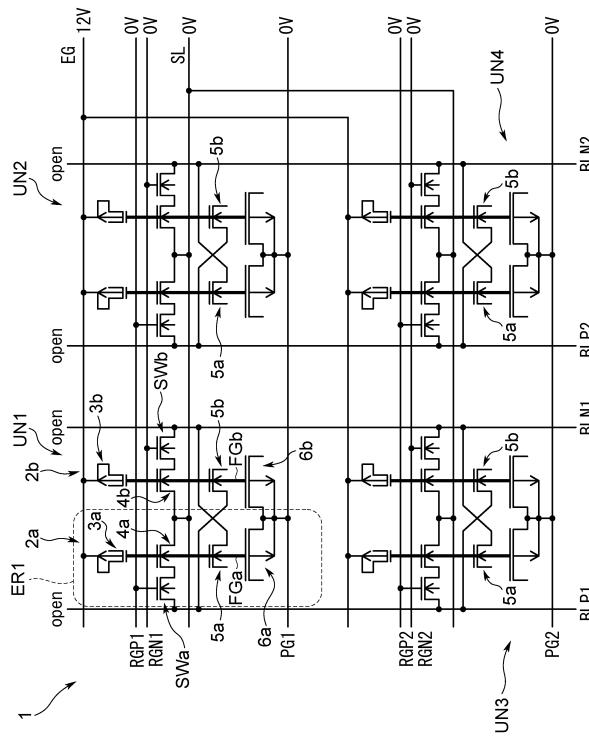

【図4】データの消去時における各部位の電圧値を示す回路図である。

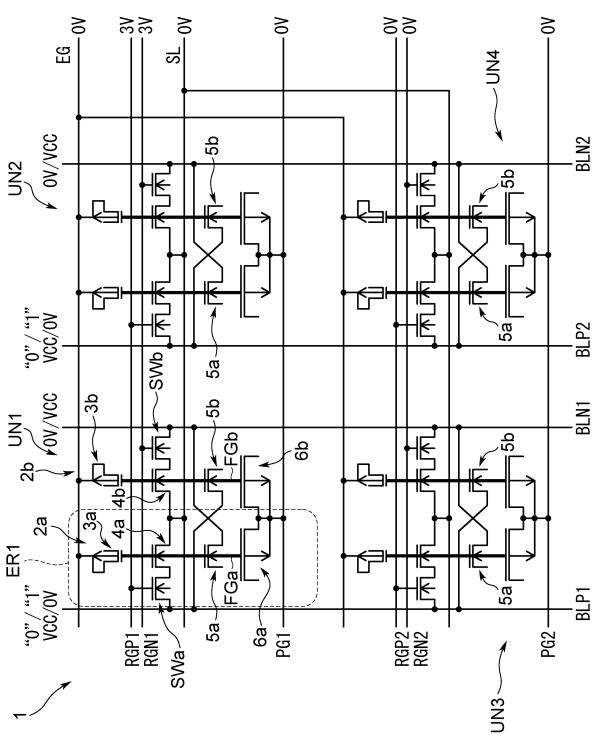

【図5】データの読み出し時における各部位の電圧値を示す回路図である。

【図6】相補型の第1セルおよび第2セルのV<sub>th</sub>モニターの説明に供する回路図である。

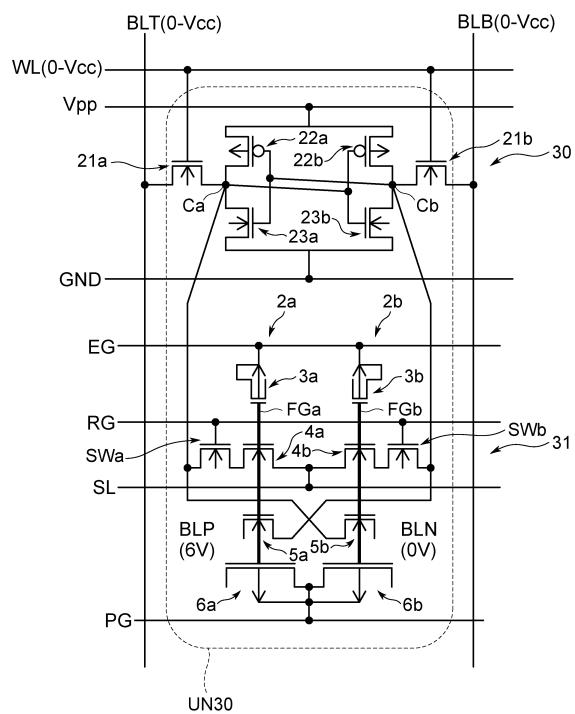

【図7】S R A Mセルを備えたメモリユニットの回路構成を示す回路図である。

【図8】図7に示すメモリユニットにおいて、データのプログラム時、消去時、データコード時、書き込み時および読み出し時における各部位の電圧値を示す表である。

50

**【発明を実施するための形態】****【0014】**

以下図面に基づいて本発明の実施の形態を詳述する。

**【0015】****(1) 不揮発性半導体記憶装置の回路構成**

図1において、UN1は本発明による不揮発性半導体記憶装置を構成するメモリユニットを示す。不揮発性半導体記憶装置は、図3にて後述するように複数のメモリユニットが行列状に配置されるが、先ず初めに1つのメモリユニットUN1に着目して以下この構成について説明する。図1に示すように、メモリユニットUN1は、第1セル2aおよび第2セル2bを備え、第1ビット線BLP1および第2ビット線BLN1が第1セル2aに接続されているとともに、これら第1ビット線BLP1および第2ビット線BLP2が第2セル2bにも接続されている。10

**【0016】**

また、第1セル2aおよび第2セル2bには、イレースゲート線EG、ソース線SL、リードゲート線RG1、およびコントロールゲート線PG1が接続されており、これらイレースゲート線EG、ソース線SL、リードゲート線RG1、およびコントロールゲート線PGから必要に応じて所定の電圧が印加され得るようになされている。

**【0017】**

ここでメモリユニットUN1では、一方の第1セル2aのみに着目すると、この第1セル2aに対して第1ビット線BLP1および第2ビット線BLN1の2本が接続され、ビット線本数がセル当たり2本存在することになる。しかしながら、このメモリユニットUN1では、例えば一方の第1セル2aにて書き込み用となる第2ビット線BLN1が、他方の第2セル2bにて読み出し用のビット線を兼ねるため、全体ではビット線本数とセル数とが同じとなり、実効的なビット線本数がセル当たり1本となる。20

**【0018】**

この実施の形態の場合、第1セル2aおよび第2セル2bは同一構成を有しており、例えばこれら2セルで1ビットを記憶する相補型セルを構成している。なお、この実施の形態においては、第1セル2aと第2セル2bの2セルで1ビットを記憶する相補型セルを構成する場合について述べるが、本発明はこれに限らず、各セル毎に1ビットを記憶するメモリユニット（すなわち、第1セル2aおよび第2セル2bでそれぞれ1ビットを記憶し、合わせて2ビットを記憶するメモリユニット）としてもよい。30

**【0019】**

ここで、第1セル2aの構成に着目すると、この第1セル2aは、イレース（消去）MOSトランジスタ（以下、イレーストランジスタと呼ぶ）3aと、リード（読み出し）MOSトランジスタ（以下、リードトランジスタと呼ぶ）4aと、プログラム（書き込み）MOSトランジスタ（以下、プログラムトランジスタと呼ぶ）5aと、コントロールキャパシタ6aと、スイッチMOSトランジスタ（以下、スイッチトランジスタと呼ぶ）SWaとを備えており、イレーストランジスタ3a、リードトランジスタ4a、プログラムトランジスタ5a、およびコントロールキャパシタ6aで1つのフローティングゲートFGaを共有している。

**【0020】**

フローティングゲートFGaは、イレーストランジスタ3a、リードトランジスタ4a、プログラムトランジスタ5a、およびコントロールキャパシタ6aの各活性領域に延在しており、イレーストランジスタ3a、リードトランジスタ4aおよびプログラムトランジスタ5aの制御ゲートとして機能し、かつコントロールキャパシタ6aの電極として機能し得る。この場合、フローティングゲートFGaは、イレーストランジスタ3aのゲート絶縁膜GI1と、リードトランジスタ4aのゲート絶縁膜GI2と、プログラムトランジスタ5aのゲート絶縁膜GI3と、コントロールキャパシタ6aの絶縁膜GI4とに接続されている。40

**【0021】**

ここで、コントロールキャパシタ6aは、一端の拡散層がコントロールゲート線PG1に接続されており、コントロールゲート線PG1の電位をフローティングゲートFGaへ伝え得る。イレーストランジスタ3aは、P型MOSであり、一端の拡散層にイレースゲート線EGが接50

続され、イレースゲート線EGの電位を、ゲート絶縁膜GI1を介してフローティングゲートFGaに伝え得る。なお、イレーストランジスタ3aの他端の拡散層は後述する第1のN型ウェルN1と短絡（ショート）している。

#### 【0022】

また、リードトランジスタ4aは、N型MOSであり、ソース線SLが一端の拡散層に接続され、スイッチトランジスタSWaの一端の拡散層が他端の拡散層に接続されている。ここで、スイッチトランジスタSWaは、N型MOSであり、第1ビット線BLP1が他端の拡散層に接続された構成を有し、必要に応じてオンオフ動作することで第1ビット線BLP1とリードトランジスタ4aとを電気的に接続させたり、或いは電気的な接続を遮断し得る。

#### 【0023】

この実施の形態の場合、スイッチトランジスタSWa, SWbに接続されるリードゲート線RG1は、第1セル2aのスイッチトランジスタSWaのゲートに接続される第1リードゲート線RGP1と、第2セル2bのスイッチトランジスタSWbのゲートに接続される第2リードゲート線RGN1とで構成されており、所定の電圧を各スイッチトランジスタSWa, SWbに印加して必要に応じてこれらスイッチトランジスタSWa, SWbをオンオフ動作させ得るようになされている。

#### 【0024】

一端がスイッチトランジスタSWa, SWbにそれぞれ接続されたリードトランジスタ4a, 4bには、他端に共通のソース線SLが接続されており、ソース線SLを介して所定の電圧がこれらリードトランジスタ4a, 4b双方に印加され得るようになされている。

#### 【0025】

かかる構成に加えて、プログラムトランジスタ5a, 5bはN型MOSであり、一方の第1セル2aに配置されたプログラムトランジスタ5aにはその一端の拡散層に第2ビット線BLN1が接続され、他方の第2セル2bに配置されたプログラムトランジスタ5bにはその一端の拡散層に第1ビット線BLP1が接続されている。

#### 【0026】

このように、本発明では、第1ビット線BLP1が、第1セル2aのリードトランジスタ4aにスイッチトランジスタSWaを介して接続されるとともに、第2セル2bのプログラムトランジスタ5bに直接接続されている。また、第2ビット線BLN1も、第1ビット線BLP1と同様に、第2セル2bのリードトランジスタ4bにスイッチトランジスタSWbを介して接続されるとともに、第1セル2aのプログラムトランジスタ5aに直接接続されている。なお、これらプログラムトランジスタ5a, 5bの他端は、隣接する他のプログラムトランジスタの拡散層とは電気的に分離されている。コントロールキャパシタ6a, 6bは、その一端の拡散層がコントロールゲート線PG1に接続され、他端の拡散層が後述する第2のN型ウェルN2とショートしており、コントロールゲート線PG1の電位を、絶縁膜GI4を介してフローティングゲートFGaに伝え得るようになされている。

#### 【0027】

なお、図1では、コントロールキャパシタ6aの絶縁膜GI4の面積が、イレーストランジスタ3aのゲート絶縁膜GI1の面積よりも大きく形成されている。このようにこの実施の形態の場合には、コントロールキャパシタ6aの絶縁膜GI4の面積を大きくした分だけ、コントロールゲート線PG1からの電位がフローティングゲートFGaへ伝わり易くなり、データを書き込む際、当該プログラムトランジスタ5aの絶縁膜GI3にて大容量のトンネル電流を発生させ、基板からフローティングゲートFGaへ多くの電荷を注入し得るようになされている。

#### 【0028】

ここで、図2は、図1に示したメモリユニットUN1の回路構成を実現するレイアウトの一例を示す概略図である。この場合、メモリユニットUN1は、図示しない基板上に第1のN型ウェルN1、第1のP型ウェルP1、第2のN型ウェルN2、および第2のP型ウェルP2が順に配置されており、これら第1のN型ウェルN1、第1のP型ウェルP1、第2のN型ウェルN2、および第2のP型ウェルP2に亘って第1セル2aおよび第2セル2bが並列に形成されている。

実際に、第1のN型ウェルN1には、第1セル2aおよび第2セル2bに亘って第1活性領域が形成

10

20

30

40

50

されており、第1セル2aおよび第2セル2bのイレーストランジスタ3a,3bが第1活性領域に形成されている。

#### 【 0 0 2 9 】

また、第1のN型ウェルN1に隣接した第1のP型ウェルP1には、第1セル2aおよび第2セル2bに亘って第2活性領域が形成されており、第1セル2aのスイッチトランジスタSWaおよびリードトランジスタ4aと、他方の第2セル2bのプログラムトランジスタ5bとがこの第2活性領域に形成されている。さらに、第1のN型ウェルN1と電気的に絶縁された第2のN型ウェルN2には、第1セル2aおよび第2セル2bに亘って第4活性領域が形成されており、第1セル2aおよび第2セル2bのコントロールキャパシタ6a,6bがこの第4活性領域に形成されている。

#### 【 0 0 3 0 】

第2のN型ウェルN2に隣接した第2のP型ウェルP2には、第1セル2aおよび第2セル2bに亘って第3活性領域が形成されており、第1セル2aのプログラムトランジスタ5aと、第2セル2bのスイッチトランジスタSWbおよびリードトランジスタ4bとがこの第3活性領域に形成されている。そして、メモリユニットUN1では、これら第1活性領域、第2活性領域、第4活性領域、および第3活性領域に亘ってフローティングゲートFGa,FGbが並走するように配置され、当該フローティングゲートFGa,FGbが、イレーストランジスタ3a,3a、リードトランジスタ4a,4b、プログラムトランジスタ5a,5b、およびコントロールキャパシタ6a,6bに亘って形成されている。

#### 【 0 0 3 1 】

メモリユニットUN1は、図2に示すような配置構成としたことにより、これらイレーストランジスタ3a,3b、リードトランジスタ4a,4b、プログラムトランジスタ5a,5b、コントロールキャパシタ6a,6b、およびスイッチトランジスタSWa,SWbを効率良く実装し得、全体として小型化を図ることができる。なお、この場合、上述したように例えばプログラムトランジスタ5bは、他のメモリユニットのプログラムトランジスタと隣接するものの、他端の拡散層がこの他のプログラムトランジスタの拡散層と電気的に絶縁されている。このようなプログラムトランジスタ間の絶縁手法としては、例えば素子分離層によって隣接するプログラムトランジスタの拡散層を電気的に絶縁させるか、或いは他端を極性が異なるP型ウェルとショートさせる構成とすればよい。

#### 【 0 0 3 2 】

因みに、本発明では、図1に示すメモリユニットUN1の回路構成を実現できれば、図2に示すレイアウトに限らず、その他種々のレイアウトとしても良い。他のレイアウトとしては、例えば上述の第3活性領域を第1のP型ウェルP1に形成し、当該第1のP型ウェルP1に第2活性領域および第3活性領域を形成するようにしても良い。

#### 【 0 0 3 3 】

##### ( 2 ) データの書き込み動作

図3は、図1に示したメモリユニットUN1を2行2列に配置した不揮発性半導体記憶装置1を示し、これら複数のメモリユニットUN1,UN2,UN3,UN4のうち、1行1列目のメモリユニットUN1の第1セル2a(すなわち、エリアER1)にのみデータを書き込む際の各部位の電圧値を示している。なお、ここでは、第1セル2aまたは第2セル2bのいずれかにデータの書き込みが行われるメモリユニットUN1を選択メモリユニット10と呼び、第1セル2aおよび第2セル2bのいずれにもデータの書き込みを行わないメモリユニットUN2,UN3,UN4を非選択メモリユニット11と呼ぶ。

#### 【 0 0 3 4 】

この場合、不揮発性半導体記憶装置1では、選択メモリユニット10が配置された1列目(以下、選択列と呼ぶ)において、データの書き込みを行う第1セル(以下、選択セルとも呼ぶ)2aのプログラムトランジスタ5aに接続された第2ビット線BLN1を選択ビット線BL1とし、この選択ビット線BL1に0[V]の書き込み電圧が印加され得る。また、この際、選択メモリユニット10に接続されたコントロールゲート線PG1には12[V]の書き込みゲート電圧が印加され得る。これにより、コントロールゲート線PG1に接続されたコントロールキャパシタ6aは、絶縁膜G14(図1)とフローティングゲートFGaとの容量結合により、フロー

10

20

30

40

50

イングゲートFGaの電圧を上昇させ得る。

【0035】

不揮発性半導体記憶装置1は、選択ビット線BL1に0[V]の書き込み電圧が印加されることで、選択セル2aのプログラムトランジスタ5aのチャネル電位が選択ビット線BL1と同じ0[V]となり、コントロールゲート線PG1の書き込みゲート電圧(12[V])によって、フローティングゲートFGaとプログラムトランジスタ5aのチャネルとの間に大きな電圧降下が生じる。

【0036】

これにより選択メモリユニット10では、フローティングゲートFGaとプログラムトランジスタ5aとの電位差により生じる量子トンネル効果によって、プログラムトランジスタ5aのチャネルにおいて電荷が基板からフローティングゲートFGaに注入され得る。その結果、選択メモリユニット10では、フローティングゲートFGa中に電荷が蓄積して、データが書き込まれた状態となり得る。10

【0037】

このとき、非選択ビット線BL2となる第1ビット線BLP1には6[V]の書き込み禁止電圧が印加される。これにより選択メモリユニット10では、データ書き込みを行わない他方の第2セル(以下、非選択セルとも呼ぶ)2bのプログラムトランジスタ5bの一端に、第1ビット線BLP1から6[V]の書き込み禁止電圧が印加され得る。これにより選択メモリユニット10の非選択セルたる第2セル2bでは、プログラムトランジスタ5bのチャネル電位が第1ビット線BLP1の書き込み禁止電圧と同じ6[V]になることから、コントロールゲート線PG1の書き込みゲート電圧(12[V])との電位差が小さくなり、その結果、量子トンネル効果が発生することなく、フローティングゲートFGbに電荷が注入され得ない。20

【0038】

なお、このときイレースゲート線EGおよびソース線SLにも6[V]の書き込み禁止電圧が印加されており、選択メモリユニット10の第1セル2aおよび第2セル2bでは、イレースゲート線EGに接続されたイレーストランジスタ3a,3bのゲート絶縁膜GI1(図1)と、ソース線SLに接続されたリードトランジスタ4a,4bのゲート絶縁膜GI2(図1)とにおいてフローティングゲートFGa,FGbとの電位差が小さくなり、その領域で量子トンネル効果が発生することなく、フローティングゲートFGa,FGbに電荷が注入され得ない。

【0039】

これに加えて、このとき選択メモリユニット10に配置された第1リードゲート線RGP1および第2リードゲート線RGN1には0[V]のオフ電圧が印加されている。これにより選択メモリユニット10において第1選択セル2aのスイッチトランジスタSWaは、第1リードゲート線RGP1からゲートに0[V]のオフ電圧が印加されることでオフ動作し、第1ビット線BLP1の電圧が遮断され、リードトランジスタ4aに第1ビット線BLP1の電圧が印加され得ない。同様に、選択メモリユニット10において第2セル2bのスイッチトランジスタSWbも、第2リードゲート線RGN1からゲートに0[V]のオフ電圧が印加されることでオフ動作し、第2ビット線BLN1の電圧が遮断され、リードトランジスタ4bに第2ビット線BLN1の電圧が印加され得ない。30

【0040】

この場合、イレースゲート線EGは、複数のメモリユニットUN1,UN2,UN3,UN4で共通化されており、各メモリユニットUN1,UN2,UN3,UN4のイレーストランジスタ3a,3bに所定の電圧を一括して印加し得るようになされている。また、ソース線SLも、複数のメモリユニットUN1,UN2,UN3,UN4で共通化されており、各メモリユニットUN1,UN2,UN3,UN4のリードトランジスタ4a,4bに所定の電圧を一括して印加し得るようになされている。40

【0041】

因みに、非選択メモリユニット11となるメモリユニットUN2では、選択メモリユニット10と共有化しているコントロールゲート線PG1に12[V]の書き込みゲート電圧が印加されるものの、非選択ビット線BL2たる第1ビット線BLP2および第2ビット線BLN2に6[V]の書き込み禁止電圧が印加されていることから、フローティングゲートFGa,FGbとプログラム

トランジスタ5a,5bとの間の電位差が小さく、その領域で量子トンネル効果が発生することなく、フローティングゲートFGa,FGbに電荷が注入され得ない。

#### 【0042】

また、非選択メモリユニット11となるメモリユニットUN3でも、選択メモリユニット10と共有化している第2ビット線BLN1に書き込み電圧が印加されるものの、コントロールゲート線PG2に0[V]の書き込み禁止ゲート電圧が印加されていることから、フローティングゲートFGa,FGbとプログラムトランジスタ5a,5bとの間の電位差がなく、その領域で量子トンネル効果が発生することなく、フローティングゲートFGa,FGbに電荷が注入され得ない。

#### 【0043】

かくして、この不揮発性半導体記憶装置1では、リードトランジスタ4aを電荷移動経路として用いずにプログラムトランジスタ5aのみによって、選択メモリユニット10の第1セル2aに設けたフローティングゲートFGaにだけ電荷を注入し得、選択メモリユニット10の第2セル2bや、他の非選択メモリユニット11の第1セル2aおよび第2セル2bに設けたフローティングゲートFGa,FGbには電荷を注入させることなく、選択メモリユニット10の第1セル2aにのみデータ書き込みを行い得る。

#### 【0044】

##### (3) データの消去動作

次に、この不揮発性半導体記憶装置1において、メモリユニットUN1,UN2,UN3,UN4のデータを消去する際の電圧印加について以下説明する。図3との対応部分に同一符号を付して示す図4は、メモリユニットUN1,UN2,UN3,UN4のデータを消去する際の各部位の電圧値を示している。

#### 【0045】

この場合、不揮発性半導体記憶装置1では、イレースゲート線EGに12[V]のイレース電圧が印加され、ソース線SL、コントロールゲート線PG1,PG2に0[V]が印加され得る。また、この際、不揮発性半導体記憶装置1は、第1リードゲート線RGP1,RGP2および第2リードゲート線RGN1,RGN2に0[V]が印加されることでスイッチトランジスタSWa,SWbがオフ動作し、第1ビット線BLP1およびリードトランジスタ4a間と、第2ビット線BLN1およびリードトランジスタ4b間の電気的な接続を遮断し得る。

#### 【0046】

不揮発性半導体記憶装置1は、第1ビット線BLP1および第2ビット線BLN1をオープンすることで、イレースゲート線EGに接続されたイレーストランジスタ3a,3bのゲート絶縁膜G11にのみ強い電界が印加される。これにより、イレーストランジスタ3a,3bは、チャネルにフローティングゲートFGa,FGb中の電荷を引き抜き、マット一括処理でメモリユニットUN1,UN2,UN3,UN4のデータ消去を行い得る。

#### 【0047】

かくして、不揮発性半導体記憶装置1では、データ消去時、メモリユニットUN1,UN2,UN3,UN4におけるリードトランジスタ4a,4bの領域を電荷の移動経路として用いることなく、イレーストランジスタ3a,3bの領域のみを用いてフローティングゲートFGa,FGbから電荷を引き抜くことができ、データのマット一括消去を行える。

#### 【0048】

##### (4) データの読み出し動作

次に、不揮発性半導体記憶装置1において、データを読み出す際の電圧印加について以下説明する。図3との対応部分に同一符号を付して示す図5は、メモリユニットUN1,UN2,UN3,UN4のうち、メモリユニットUN1のデータを読み出す際の各部位の電圧値を示している。なお、ここでは、メモリユニットUN1,UN2,UN3,UN4のうちメモリユニットUN1の第1セル2aにだけデータが書き込まれ、メモリユニットUN1の第2セル2bにはデータが書き込まれていないものとする。また、ここでは、フローティングゲートFGaに電荷が蓄積された状態を例えれば「0」とし、フローティングゲートFGbに電荷が蓄積されてない状態を「1」とする。

10

20

30

40

50

**【 0 0 4 9 】**

この場合、不揮発性半導体記憶装置1は、第1リードゲート線RGP1および第2リードゲート線RGN1に3[V]のオン電圧が印加され、スイッチトランジスタSWa, SWbをいずれもオン動作させる。このとき、ソース線SLには0[V]が印加され、第1ビット線BLP1, BLP2および第2ビット線BLN1, BLN2には読み出し電圧としてVCCが印加され得る。

**【 0 0 5 0 】**

ここで、フローティングゲートFGaに電荷が蓄積された第1セル2aでは、リードトランジスタ4aのソースに0[V]が印加されると、当該リードトランジスタ4aがオフ動作し、リードトランジスタ4aおよび第1ビット線BLP1間の電気的な接続が遮断され、第1ビット線BLP1での電圧がVCCのままとなる。一方、フローティングゲートFGbに電荷が蓄積されていない他方の第2セル2b（リードトランジスタ4a, 4bの閾値電圧Vthはデブリート状態と仮定する）では、リードトランジスタ4bのソースに0[V]が印加されるとオン動作し、リードトランジスタ4bおよび第2ビット線BLN1間が電気的に接続され、第2ビット線BLN1の電圧が変化しVCCよりも低くなる。10

**【 0 0 5 1 】**

不揮発性半導体記憶装置1は、第1ビット線BLP1に比べて第2ビット線BLN1が低電位となり、これら第1ビット線BLP1および第2ビット線BLN1の電位差を、図示しないラッチ回路でラッチすることにより、第1ビット線BLP1がVCCに固定されるとともに、第2ビット線BLN1が0Vに固定され、読み出し情報が確定し得る。20

**【 0 0 5 2 】**

なお、この実施の形態の場合、不揮発性半導体記憶装置1では、イレースゲート線EGおよびコントロールゲート線PG1, PG2に0[V]が印加され、イレーストランジスタ3a, 3bおよびコントロールキャパシタ6a, 6bによるデータ読み出し時ににおけるフローティングゲートFGa, FGbでの電荷移動を防止し得るようになされている。20

**【 0 0 5 3 】**

因みに、この実施の形態の場合においては、イレースゲート線EGおよびコントロールゲート線PG1, PG2に0[V]を印加するようにした場合について述べたが、本発明はこれに限らず、イレースゲート線EGまたはコントロールゲート線PG1, PG2に例えれば所定電圧のVCCを印加してもよい。この場合、例えばコントロールゲート線PG1, PG2にVCCを印加することで、例えばコントロールキャパシタ6bとフローティングゲートFGbとの容量結合によりフローティングゲートFGbの電位が上昇し、その結果、リードトランジスタ4bから出力されるオン電流が増加することとなり、データをラッチするまでの時間短縮を図ることができる。30

**【 0 0 5 4 】**

因みに、この実施の形態の場合、データ読み出しを行わないメモリユニットUN3, UN4では、第1リードゲート線RGP2および第2リードゲート線RGN2に0[V]のオフ電圧が印加され、スイッチトランジスタSWa, SWbがオフ動作し、フローティングゲートのデータ読み出しが行われず、かくしてメモリユニットUN1のデータのみを読み出すことができる。

**【 0 0 5 5 】****( 5 ) 動作及び効果**

以上の構成において、不揮発性半導体記憶装置1では、フローティングゲートFGa, FGb内の電荷の有無に応じた電圧を読み出すためのリードトランジスタ4a, 4bと、フローティングゲートFGa, FGbに電荷を注入するプログラムトランジスタ5a, 5bと、フローティングゲートFGa, FGbから電荷を引き抜くイレーストランジスタ3a, 3bと、フローティングゲートFGa, FGbの電位を調整するコントロールキャパシタ6a, 6bとを備え、これらリードトランジスタ4a (4b)、プログラムトランジスタ5a (5b)、イレーストランジスタ3a (3b)、およびコントロールキャパシタ6a (6b)の各活性領域上にフローティングゲートFGa (FGb)を延在させた。40

**【 0 0 5 6 】**

また、第1セル2aでは、第1ビット線BLP1をスイッチトランジスタSWaを介してリードト

50

ランジスタ4aに接続させ、第2ビット線BLN1をプログラムトランジスタ5aに直接接続させた。一方、第1セル2aと対をなす第2セル2bでは、第2ビット線BLN1をスイッチトランジスタSWbを介してリードトランジスタ4bに接続させ、第1ビット線BLP1をプログラムトランジスタ5bに直接接続させた。

#### 【0057】

これにより、不揮発性半導体記憶装置1では、フローティングゲートFGa, FGbのデータを読み出すためのリードトランジスタ4a, 4bが、データの書き込みや消去の際に電荷の移動経路とならず、リードトランジスタ4a, 4bのゲート酸化膜への印加電界やホットキャリアのストレスによるダメージを防止でき、かくしてデータの書き込みや消去によって読み出し電流が劣化することもなく誤動作を防止できる。

10

#### 【0058】

また、この不揮発性半導体記憶装置1では、リードトランジスタ4a, 4bがデータの書き込みや消去の際に電荷の移動経路とならないため、リードトランジスタ4a, 4bのサイドウォール領域に電荷の一部が注入されることもなく、データの書き換えを繰り返しても、リードトランジスタ4a, 4bのV<sub>th</sub>もシフトせず誤動作を防止できる。

#### 【0059】

さらに、この不揮発性半導体記憶装置1では、第1ビット線BLP1および第2ビット線BLN1が設けられビット線本数が2本であるにもかかわらず、一方の第1セル2aにて書き込み用となる第2ビット線BLN1が、他方の第2セル2bにて読み出し用のビット線を兼ねるように構成されているため、全体ではビット線本数とセル数とが同じとなり、実効的なビット線本数がセル当たり1本となることから装置全体として小型化を図ることができる。

20

#### 【0060】

以上の構成によれば、不揮発性半導体記憶装置1では、スイッチトランジスタSWa, SWbの切り替えによって、第1セル2aのプログラムトランジスタ5aに接続されてデータ書き込み用となる第2ビット線BLN1が、他方の第2セル2bにて読み出し用のビット線を兼ねつつ、データの書き込み時および消去時に電荷移動経路となるプログラムトランジスタ5a, 5bおよびイレーストランジスタ3a, 3bを設けたことにより、ビット線本数を増やすことなく、データ書き込みや消去に用いられることにより生じてしまうリードトランジスタ4a, 4bの誤作動を確実に防止し得る。

#### 【0061】

30

##### (6) 相補型の第1セルおよび第2セルのV<sub>th</sub>モニターについて

メモリユニットUN1のテストにおいて、上述した実施の形態のような相補型セルではなく、例えば1セル/1ビットとした場合には、単にコントロールゲート線PGに印加する電圧を制御することで、リードトランジスタ4a, 4bのV<sub>th</sub>（閾値電圧）をモニターすることができる。

#### 【0062】

しかしながら、上述した実施の形態のように、第1セル2aおよび第2セル2bにより、2セル/1ビットの相補型セルを構成する場合には、リードゲート線RG1に接続された各スイッチトランジスタSWa, SWbを双方ともオン動作させると、相補側のセルの状態によって相補側のビット線の電位が変化することから、図示しないラッチ回路によって、例えば、より早く電圧が下がった側の第1ビット線BLP1を「1」とし、これに伴い他方の第2ビット線BLN1側を強制的に「0」としてしまい、正常なモニターを行えないという問題がある。

40

#### 【0063】

そこで、本発明では、図6に示すように、相補型セルを構成するメモリユニットUN1において、メモリユニットUN1内にあるリードゲート線RG1を第1リードゲート線RGP1および第2リードゲート線RGN1で構成し、これら第1リードゲート線RGP1および第2リードゲート線RGN1を独立に制御することで、スイッチトランジスタSWa, SWbを個別にオンオフ動作させ、第1セル2aおよび第2セル2bのV<sub>th</sub>を個別にモニターし得るようになされている。

#### 【0064】

ここで、図6は、図1に示したメモリユニットUN1において、第1セルのV<sub>th</sub>をモニター

50

する際の各部位の電圧値を示したものである。この場合、メモリユニットUN1では、イレースゲート線EGおよびソース線SLに0[V]が印加され、V<sub>th</sub>をモニターする第1セル2aに接続された第1リードゲート線RGP1に所定電圧のVCCが印加され、V<sub>th</sub>をモニターしない第2セル2bに接続された第2リードゲート線RGN1に0[V]が印加され得る。このようにメモリユニットUN1では、第2リードゲート線RGN1に0[V]を印加することでスイッチトランジスタSW<sub>b</sub>を強制的にオフ動作させ、当該スイッチトランジスタSW<sub>b</sub>によってフローティングゲートFG<sub>b</sub>および第2ビット線BLN1間の電気的な接続を遮断し、第2ビット線BLN1に第2セル2bの電位状態が関与することなく、第2ビット線BLN1の電圧を一定に維持し得る。

#### 【0065】

この状態で、メモリユニットUN1では、第2ビット線BLN1に所定の電圧、例えばVCC/2を与える、第1ビット線BLP1にV<sub>th</sub>を決める基準電流I<sub>basis</sub>を流し、コントロールゲート線PG1にモニター電圧V<sub>monitor</sub>を印加するとともに、当該コントロールゲート線PG1に印加するモニター電圧V<sub>monitor</sub>の電圧値を変えてゆく。これにより、メモリユニットUN1では、コントロールゲート線PG1に印加するモニター電圧V<sub>monitor</sub>の電圧値に応じて、コントロールキャパシタ6aおよびフローティングゲートFGa間に生じる容量結合によって当該フローティングゲートFGaの電圧が上昇し、リードトランジスタ4aを流れるオン電流が変化し得る。

#### 【0066】

この際、メモリユニットUN1では、第1セル2aにおいてリードトランジスタ4aから流れるオン電流が基準電流I<sub>basis</sub>以上となれば、第1ビット線BLP1が第2ビット線BLN1より低電位となって0[V]にラッチされ、第1セル2aのV<sub>th</sub>がモニター電圧V<sub>monitor</sub>以下と判断できる。これに対して、第1セル2aにおいて基準電流I<sub>basis</sub>以下のオン電流しかリードトランジスタ4aから流れない場合には、所定の時間の後に第1ビット線BLP1が第2ビット線BLN1よりも高電位となってVCCにラッチされ、第1セル2aのV<sub>th</sub>がモニター電圧V<sub>monitor</sub>以上と判断できる。

#### 【0067】

なお、上述した実施の形態においては、第1セル2aにおけるリードトランジスタ4aのV<sub>th</sub>をモニターする場合について述べたが、第2セル2bのリードトランジスタ4bについても、上述した実施の形態と同様の原理でV<sub>th</sub>をモニターすることができる。具体的には、V<sub>th</sub>をモニターする第2セル2bに接続された第2リードゲート線RGN1に所定電圧のVCCを印加し、V<sub>th</sub>をモニターしない第1セル2aに接続された第1リードゲート線RGP1に0[V]を印加することで、スイッチトランジスタSW<sub>a</sub>をオフ動作させ、当該スイッチトランジスタSW<sub>a</sub>によってフローティングゲートFG<sub>a</sub>および第1ビット線BLP1間の電気的な接続を遮断し、第1ビット線BLP1を一定の電圧に維持し得る。

#### 【0068】

また、この状態で、メモリユニットUN1では、第2ビット線BLN1にV<sub>th</sub>を決める基準電流I<sub>basis</sub>を流し、コントロールゲート線PG1にモニター電圧V<sub>monitor</sub>を印加するとともに、当該コントロールゲート線PG1に印加するモニター電圧V<sub>monitor</sub>の電圧値を変えてゆき、リードトランジスタ4bから流れるオン電流が基準電流I<sub>basis</sub>以上であるか否かを判断することになる。

#### 【0069】

##### (7) 他の実施の形態

次にS R A M (Static Random Access Memory) セルと組み合わせたメモリユニットについて以下説明する。図1との対応部分に同一符号を付して示す図7は、本発明による不揮発性半導体記憶装置を構成する1つのメモリユニットUN30を示す。なお、この他の実施の形態による不揮発性半導体記憶装置は、複数のメモリユニットが行列状に配置された構成を有するが、ここでは1つのメモリユニットUN30に着目して以下この構成について説明する。図7に示すように、このメモリユニットUN30は、第1セル2aおよび第2セル2bからなる不揮発メモリ部31にS R A M セル30が接続されている点に特徴を有する。

#### 【0070】

10

20

30

40

50

ここでS R A Mセル30は、N型M O Sトランジスタからなるアクセストランジスタ21a, 21bと、P型M O Sトランジスタからなるロードトランジスタ22a, 22bと、N型M O Sトランジスタからなるドライブトランジスタ23a, 23bとを備え、合計6個のM O Sトランジスタで構成されている。ロードトランジスタ22a, 22bは、ドレインがドライブトランジスタ23a, 23bのドレインに接続され、ソースが電源線Vppに接続されており、さらにゲートがドライブトランジスタ23a, 23bのゲートに接続されている。また、ドライブトランジスタ23a, 23bはソースがグランド線GNDに接続されている。

#### 【 0 0 7 1 】

アクセストランジスタ21aは、相補型第1ビット線BLTにドレインが接続され、ロードトランジスタ22aおよびドライブトランジスタ23a間のストレージノードCaと、ロードトランジスタ22bおよびドライブトランジスタ23bのゲートとにソースが接続されている。一方、他方のアクセストランジスタ21bも同様に、相補型第2ビット線BLBにドレインが接続され、ロードトランジスタ22bおよびドライブトランジスタ23b間のストレージノードCbと、ロードトランジスタ22aおよびドライブトランジスタ23aのゲートとにソースが接続されている。さらに、これらアクセストランジスタ21a, 21bはゲートが共通のワード線WLに接続され、相補型第1ビット線BLTおよび相補型第2ビット線BLB間には、図示しないラッチタイプのセンスアンプが接続されている。

#### 【 0 0 7 2 】

かかる構成に加えてS R A Mセル30には、一方のストレージノードCaに第1セル2aの第1ビット線BLPが接続されるとともに、他方のストレージノードCbに第2セル2bの第2ビット線BLNが接続されている。なお、ここで不揮発メモリ部31は、上述した実施の形態で説明した図1に示すメモリユニットUN1とほぼ同一構成を有するが、ここではリードゲート線RGを1本にし、スイッチトランジスタSWa, SWbを一括してオンオフ制御し得るように構成されている。

#### 【 0 0 7 3 】

このような構成を有するメモリユニットUN30は、外部からのデータの書き込みや読み出しをS R A Mセル30で行うようになされている。ここで、図8は、メモリユニットUN30におけるS R A Mセル30へのデータ書き込み時（図8中、「書き込み」と表記）、S R A Mセル30からのデータ読み出し時（図8中、「読み出し」と表記）、S R A Mセル30から不揮発メモリ部31へデータを取り込むプログラム時（図8中、「プログラム」と表記）、不揮発メモリ部31でのデータ消去時（図8中、「消去」と表記）、不揮発メモリ部31からS R A Mセル30へのデータを再び取り込むデータロード時（図8中、「データロード」と表記）の各部位の電圧値を示す。なお、図8中、任意の電圧値に設定できる部位には「Don't care」と表記している。

#### 【 0 0 7 4 】

##### （ 7 1 ） S R A Mへのデータ書き込み

この場合、S R A Mセル30へのデータ書き込みは、ワード線WLにVccの所定電圧が印加され、ワード線WLに接続されたアクセストランジスタ21a, 21bを双方ともオン動作させる。また、この際、電源線VppにもVccの所定電圧が印加され得る。S R A Mセル30は、例えば一方の相補型第1ビット線BLTに書き込み電圧としてVccが印加されると、他方の相補型第2ビット線BLBに書き込み禁止電圧として0[V]が印加され得る。

#### 【 0 0 7 5 】

これにより、一方のロードトランジスタ22aおよびドライブトランジスタ23aには、他方のアクセストランジスタ21bを介して相補型第2ビット線BLBとゲートが電気的に接続することによりゲートがLowとなり、その結果、ロードトランジスタ22aがオン動作するとともに、ドライブトランジスタ23aがオフ動作する。かくして、これらロードトランジスタ22aおよびドライブトランジスタ23a間のストレージノードCaは、ロードトランジスタ22aを介して電源線Vppと電気的に接続して電圧がHighとなる。

#### 【 0 0 7 6 】

このとき、他方のロードトランジスタ22bおよびドライブトランジスタ23bには、一方の

10

20

30

40

50

アクセストランジスタ21aを介して相補型第1ビット線BLTとゲートが電気的に接続することによりゲートがHighとなり、その結果、ロードトランジスタ22bがオフ動作するとともに、ドライブトランジスタ23bがオン動作する。かくして、これらロードトランジスタ22bおよびドライブトランジスタ23b間のストレージノードCbは、ドライブトランジスタ23bを介してグランド線GNDと電気的に接続して電圧がLowとなる。以上によりS R A Mセル30はデータが書き込まれた状態となる。

#### 【0077】

##### (7 2) S R A Mセルからのデータ読み出し

S R A Mセル30のデータを読み出す際は、ワード線WLにVccの所定電圧が印加され、ワード線WLに接続されたアクセストランジスタ21a, 21bを双方ともオン動作する。これによりメモリユニットUN30では、相補型第1ビット線BLTを介して一方のストレージノードCaの電位を読み出すとともに、相補型第2ビット線BLBを介して他方のストレージノードCbの電位を読み出すことで、センサアンプによってストレージノードに記録されたデータの「0」「1」を判定し得る。10

#### 【0078】

##### (7 3) 不揮発メモリ部へのプログラム

本発明では、上述したS R A Mセルに記録したデータを、上述した「(2)データの書き込み動作」の原理を基に、マット一括処理で不揮発メモリ部31に取り込むことができる。なお、ここでの説明では、S R A Mセル30において一方のストレージノードCaの電位が高いHigh状態にあり、他方のストレージノードCbの電位が低いLow状態にあるとする。20

#### 【0079】

この場合、不揮発メモリ部31には、イレースゲート線EGに6[V]が印加され、コントロールゲート線PGに12[V]が印加され得る。不揮発メモリ部31は、データが書き込まれた一方のストレージノードCaに、第1ビット線BLPを介して第2セル2bのプログラムトランジスタ5bが電気的に接続されていることから、当該プログラムトランジスタ5bのチャネル電位がストレージノードCaと同じHighの電位になって、コントロールゲート線PGの書き込みゲート電圧(12[V])との電位差が小さくなり、その結果、量子トンネル効果が発生することなく、フローティングゲートFGbに電荷が注入され得ない。

#### 【0080】

一方、この不揮発メモリ部31は、データが書き込まれていない他方のストレージノードCbに、第2ビット線BLNを介して第1セル2aのプログラムトランジスタ5aが電気的に接続されていることから、当該プログラムトランジスタ5aのチャネル電位がストレージノードCbと同じLowの電位になって、コントロールゲート線PGの書き込みゲート電圧(12[V])との電位差が大きくなり、その結果、量子トンネル効果が発生し、フローティングゲートFGaに電荷が注入され得る。メモリユニットUN30では、S R A Mセル30に記録したデータを、マット一括処理で不揮発メモリ部31に取り込むことができ、かくして周辺回路の制御を簡素化させることもできる。30

#### 【0081】

また、このような不揮発メモリ部31でも、S R A Mセル30のデータのプログラム時、上述した実施の形態と同様に、イレーストランジスタ3aおよびリードトランジスタ4aを電荷の移動経路とせずに、プログラムトランジスタ5aのみによってフローティングゲートFGaに電荷を注入し得、かくして、電荷移動経路となることにより生じてしまうリードトランジスタ4a, 4bの誤作動を確実に防止し得る。40

#### 【0082】

##### (7 4) 不揮発メモリ部からのデータロード

また、本発明では、上述したように不揮発メモリ部31に一旦取り込んだデータを、上述した「(4)データの読み出し動作」の原理を基に、マット一括処理でS R A Mセル30に再び書き込むことができる。ここでは、不揮発メモリ部31において一方の第1セル2aのフローティングゲートFGaに電荷が蓄積してデータが書き込まれた状態とし、他方の第2セル2bのフローティングゲートFGbに電荷が蓄積されておらずデータが書き込まれていない状50

態とする。この場合、不揮発メモリ部31には、イレースゲート線EGに0[V]が印加され、コントロールゲート線PGにも0[V]が印加され得る。

#### 【0083】

また、不揮発メモリ部31では、リードゲート線RGに所定電圧のVccが印加されることにより、第1セル2aおよび第2セル2bの各スイッチトランジスタSWa,SWbがオン動作するとともに、リードトランジスタ4a,4bのソースに0[V]が印加されることにより、リードトランジスタ4a,4bがオン動作する。これにより不揮発メモリ部31は、リードトランジスタ4aおよび第1ビット線BLP間が電気的に接続され、フローティングゲートFGaの高電位に伴ってS R A Mセル30の一方のストレージノードCaを高電位にしてデータが書き込まれた状態に復元し得る。

10

#### 【0084】

また、不揮発メモリ部31は、リードトランジスタ4bおよび第2ビット線BLN間も電気的に接続され、フローティングゲートFGbの低電位に伴ってS R A Mセル30の他方のストレージノードCbを低電位にしてデータが書き込まれない状態に復元し得る。さらに、この不揮発メモリ部31では、S R A Mセル30へのデータロードをマット一括処理で行うことができるところから、周辺回路の制御も簡素化させることができる。

#### 【0085】

##### (7 5) 不揮発メモリ部におけるデータ消去

さらに、本発明では、上述した「(3)データの消去動作」の原理を基に、不揮発メモリ部31においてデータを消去させることもできる。この場合、不揮発メモリ部31では、イレースゲート線EGに12[V]のイレース電圧が印加され、ソース線SL、コントロールゲート線PGに0[V]が印加され得る。不揮発メモリ部31は、イレースゲート線EGに接続されたイレーストランジスタ3a,3bのゲート絶縁膜にのみ強い電界が印加されることで、イレーストランジスタ3a,3bのチャネル層によってフローティングゲートFGa,FGb中の電荷を引き抜き、マット一括処理で不揮発メモリ部31のデータ消去を行い得る。

20

#### 【0086】

なお、本発明は、本実施の形態に限定されるものではなく、本発明の要旨の範囲内で種々の変形実施が可能であり、例えば図3～図5、図8において、データ書き込み時や、データ消去時、データ読み出し時等における電圧値をそれぞれ明記しているが、本発明はこれに限らず、種々の電圧値を適用してもよい。

30

#### 【0087】

さらに、上述した実施の形態においては、イレーストランジスタ3aをN型ウェルに形成し、コントロールキャパシタ6aを当該N型ウェルと異なるN型ウェルに形成し、さらにリードトランジスタ4a、スイッチトランジスタSWaおよびプログラムトランジスタ5aをP型ウェルに形成した場合について述べたが、本発明はこれに限らず、イレーストランジスタ3aをP型ウェルに形成し、コントロールキャパシタ6aを当該P型ウェルと異なるP型ウェルに形成し、さらにリードトランジスタ4a、スイッチトランジスタSWaおよびプログラムトランジスタ5aをN型ウェルに形成するようにしてもよい。

#### 【符号の説明】

#### 【0088】

40

1 不揮発性半導体記憶装置

2a 第1セル(セル)

2b 第2セル(セル)

3a,3b イレーストランジスタ

4a,4b リードトランジスタ

5a,5b プログラムトランジスタ

6a,6b コントロールキャパシタ

SWa,SWb スイッチトランジスタ

BLP1,BLP2,BLP 第1ビット線

BLN1,BLN2,BLN 第2ビット線

50

## FGa, FGb フローティングゲート

【図1】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図8】

|                            | EG         | RG  | SL         | PG         | Vpp | WL    |

|----------------------------|------------|-----|------------|------------|-----|-------|

| プログラム<br>(SRAMから不揮発メモリ部へ)  | 6          | 0   | 6          | 12         | 6   | 0     |

| 消去<br>(不揮発メモリ部でのデータ消去)     | 12         | 0   | 0          | 0          | Vcc | 0     |

| データロード<br>(不揮発メモリ部からSRAMへ) | 0          | Vcc | 0          | 0          | Vcc | 0     |

| 書き込み<br>(SRAMへの書き込み)       | Don't care | 0   | Don't care | Don't care | Vcc | Vcc/0 |

| 読み出し<br>(SRAMから読み出し)       | Don't care | 0   | Don't care | Don't care | Vcc | Vcc/0 |

---

フロントページの続き

|         |        | F I       |         |       |

|---------|--------|-----------|---------|-------|

| H 0 1 L | 27/11  | (2006.01) | G 1 1 C | 17/00 |

| G 1 1 C | 16/04  | (2006.01) | G 1 1 C | 11/40 |

| G 1 1 C | 11/412 | (2006.01) | G 1 1 C | 11/40 |

| G 1 1 C | 14/00  | (2006.01) |         | 1 0 1 |

(72)発明者 葛西 秀男

東京都小平市小川東町1丁目29番9号 株式会社フローディア内

(72)発明者 品川 裕

東京都小平市小川東町1丁目29番9号 株式会社フローディア内

(72)発明者 奥山 幸祐

東京都小平市小川東町1丁目29番9号 株式会社フローディア内

審査官 小山 満

(56)参考文献 特開2006-196758(JP,A)

特開2011-023567(JP,A)

特開2008-004718(JP,A)

特開2011-123958(JP,A)

特開2007-081299(JP,A)

国際公開第2009/072616(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 1 / 8 2 4 7

G 1 1 C 1 1 / 4 1 2

G 1 1 C 1 4 / 0 0

G 1 1 C 1 6 / 0 4

H 0 1 L 2 1 / 3 3 6

H 0 1 L 2 1 / 8 2 4 4

H 0 1 L 2 7 / 1 1

H 0 1 L 2 7 / 1 1 5

H 0 1 L 2 9 / 7 8 8

H 0 1 L 2 9 / 7 9 2