## MINISTERO DELLO SVILUPPO ECONOMICO DIREZIONE GENERALE PER LA LOTTA ALLA CONTRAFFAZIONE UFFICIO ITALIANO BREVETTI E MARCHI

| DOMANDA DI INVENZIONE NUMERO | 102010901831591 |

|------------------------------|-----------------|

| Data Deposito                | 21/04/2010      |

| Data Pubblicazione           | 21/10/2011      |

Classifiche IPC

Titolo

PROCEDIMENTO PER LA FABBRICAZIONE DI PIASTRINE SEMICONDUTTRICI E PIASTRINA SEMICONDUTTRICE CON TRINCEA DI PROTEZIONE

## DESCRIZIONE

del brevetto per invenzione industriale dal titolo:

"PROCEDIMENTO PER LA FABBRICAZIONE DI PIASTRINE SEMICONDUTTRICI E PIASTRINA SEMICONDUTTRICE CON TRINCEA DI PROTEZIONE"

di STMICROELECTRONICS S.R.L.

di nazionalità italiana

con sede: VIA C. OLIVETTI, 2

AGRATE BRIANZA (MB)

Inventori: PATELMO Matteo, MERLINI Alessandra Piera

\*\*\* \*\*\*\* \*\*\*

La presente invenzione è relativa a un procedimento per la fabbricazione di piastrine semiconduttrici e ad una piastrina semiconduttrice con trincea di protezione.

Come è noto, i dispositivi elettronici integrati sono ottenuti dalla lavorazione di fette semiconduttrici. Numerosi dispositivi, normalmente identici fra loro, sono realizzati simultaneamente nella stessa fetta. Al termine della lavorazione, la fetta deve essere divisa in piastrine, ciascuna delle quali contiene un singolo esemplare del dispositivo.

Il taglio della fetta viene normalmente eseguito con procedimenti meccanici e causa notevoli sollecitazioni. Ciascun dispositivo deve essere perciò adeguatamente protetto, sia per evitare danni strutturali causati dalle

vibrazioni prodotte dagli attrezzi di taglio, sia per prevenire l'assorbimento di umidità neali strati dielettrici superficiali. Tali strati dielettrici, vengono utilizzati per isolare fra loro i diversi livelli di linee di metallizzazione, sono soggetti a particolarmente intensi durante il taglio e, inoltre, possono essere igroscopici. Poiché il taglio richiede l'impiego di getti d'acqua a scopo di raffreddamento, è chiaro che, senza adequati accorgimenti, c'è un rischio che venga assorbita umidità, con consequenti danni per i dispositivi. Il dispositivo rimane inoltre esposto all'atmosfera durante tutta la durata della sua vita e quindi c'è il rischio che venga assorbita umidita' dall'ambiente esterno anche durante il funzionamento.

Ogni esemplare del dispositivo è perciò protetto da un cosiddetto anello di sigillatura (detto "seal ring", "edge of die" oppure "chip outline band"), che circonda completamente l'area della corrispondente piastrina da ottenere mediante il taglio.

Gli anelli di sigillatura in generale comprendono una pluralità di linee metalliche, che si estendono lungo percorsi chiusi (normalmente poligonali) attorno a ciascun dispositivo nella fetta. Le linee metalliche, annegate in strati di materiale dielettrico, sono sovrapposte su diversi livelli e sono reciprocamente collegate da vie di

interconnessione ("interlayer connections") che attraversano il materiale dielettrico fra livelli adiacenti.

Gli anelli di sigillatura hanno larghezza intorno a  $10\text{--}20~\mu\text{m}$  e sono disposti fra rispettivi dispositivi e linee di taglio predisposte sulla fetta per il passaggio dello strumento di taglio.

La protezione offerta dagli anelli di sigillatura non è però del tutto soddisfacente. Durante il taglio, le vibrazioni meccaniche possono facilmente causare delle microcrepe che tendono a propagarsi dalle linee di taglio verso i dispositivi integrati nella fetta. In diversi casi, qli anelli di sigillatura non sono sufficienti ad arrestare la propagazione delle microcrepe, che possono così estendersi fino a raggiungere i dispositivi. Inoltre, le metalliche sono continue е interrompono i 1 dielettrico lungo il loro intero sviluppo. Le vie interconnessione, invece, sono in generale discontinue e definiscono solo una barriera parziale all'assorbimento di umidità ed al propagarsi di eventuali crepe.

Scopo della presente invenzione è mettere a disposizione un procedimento per la fabbricazione di piastrine semiconduttrici e una piastrina semiconduttrice che permettano di superare gli inconvenienti descritti e, in particolare, assicurino efficace protezione contro il

propagarsi di microcrepe e l'assorbimento di umidità durante le fasi di taglio.

Secondo la presente invenzione vengono realizzati un procedimento per la fabbricazione di piastrine semiconduttrici e una piastrina semiconduttrice come definiti rispettivamente nelle rivendicazioni 1 e 9.

Per una migliore comprensione dell'invenzione, ne verranno ora descritte alcune forme di realizzazione, a puro titolo di esempio non limitativo e con riferimento ai disegni allegati, nei quali:

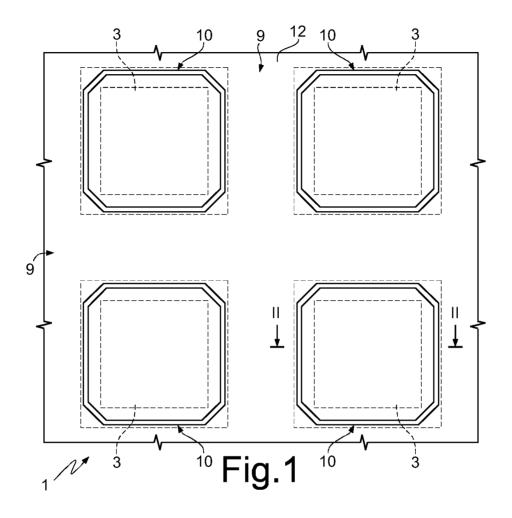

- la figura 1 è una vista in pianta dall'alto di una fetta semiconduttrice in una fase di un procedimento per la fabbricazione di piastrine semiconduttrici in accordo a una forma di realizzazione della presente invenzione;

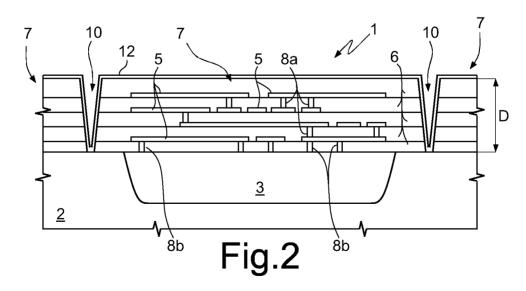

- la figura 2 è una sezione trasversale ingrandita di una porzione della fetta di figura 1, presa lungo la linea II-II di figura 1;

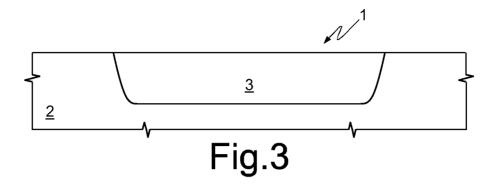

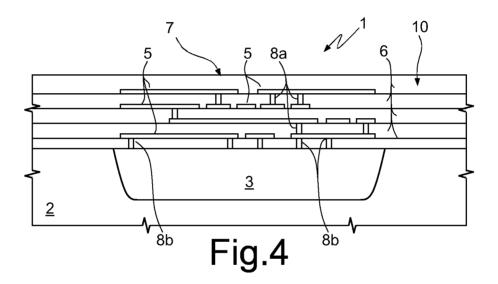

- le figure 3-5 mostrano la sezione di figura 2, in fasi di lavorazione preparatorie;

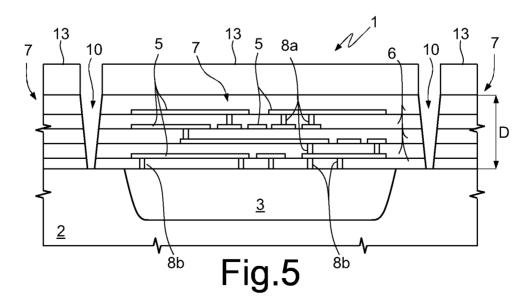

- la figura 6 è una sezione trasversale attraverso una piastrina semiconduttrice in accordo a una forma di realizzazione della presente invenzione, ottenuta dal taglio della fetta di figura 1;

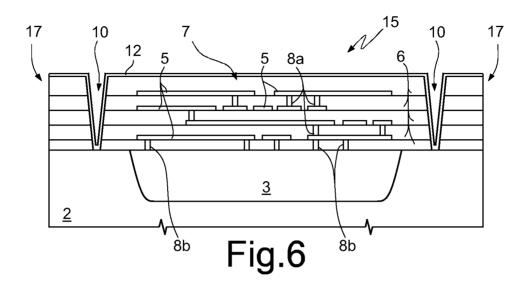

- la figura 7 è una vista in pianta dall'alto della piastrina di figura 6;

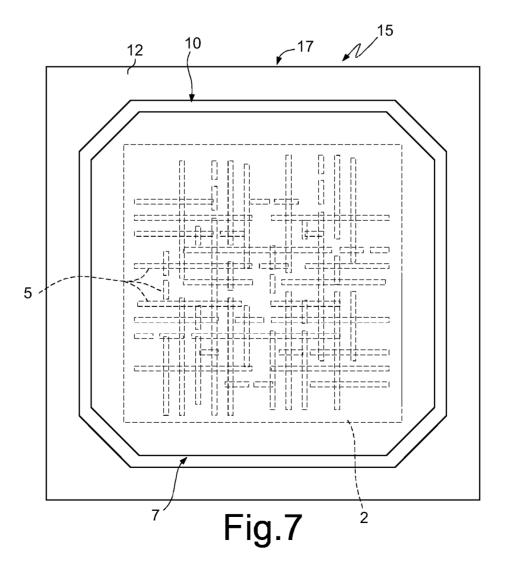

- la figura 8 è una vista in pianta dall'alto di una fetta semiconduttrice in una fase di un procedimento per la fabbricazione di piastrine semiconduttrici in accordo a una diversa forma di realizzazione della presente invenzione;

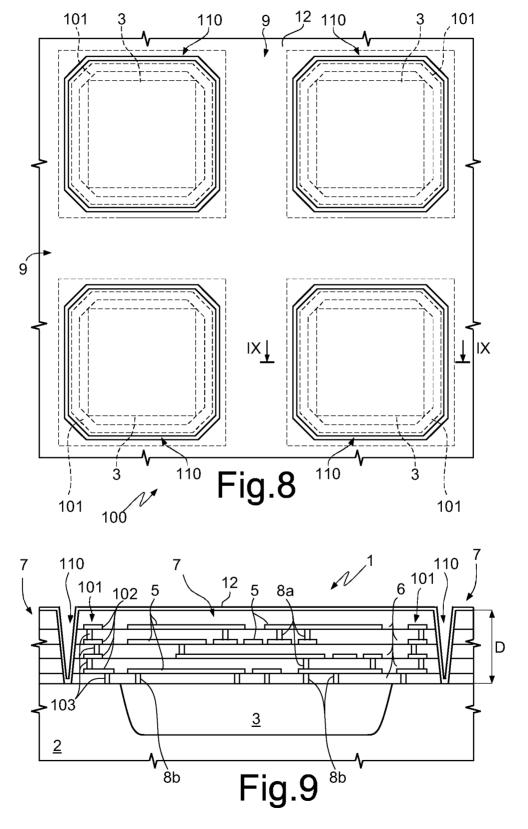

- la figura 9 è una sezione trasversale ingrandita di una porzione della fetta di figura 8, presa lungo la linea IX-IX di figura 8;

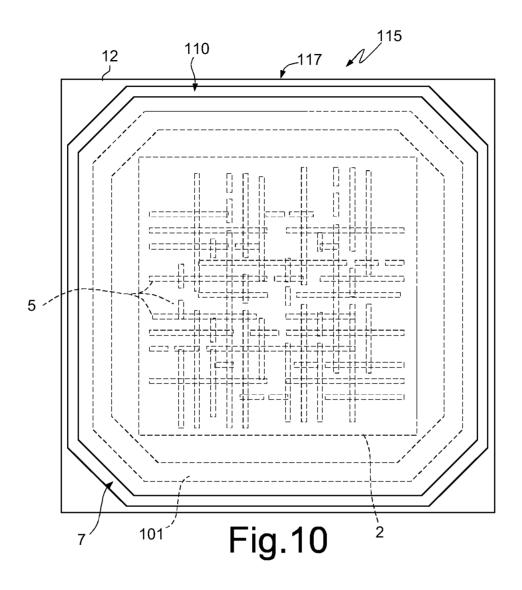

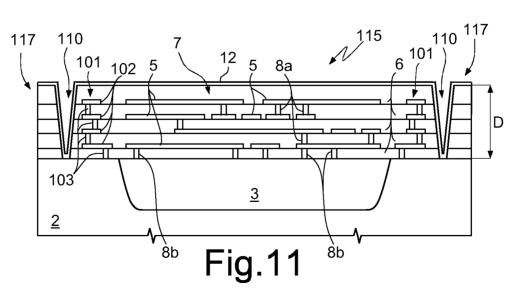

- la figura 10 è una sezione trasversale attraverso una piastrina semiconduttrice in accordo a una forma di realizzazione della presente invenzione, ottenuta dal taglio della fetta di figura 8; e

- la figura 11 è una vista in pianta dall'alto della piastrina di figura 10.

Con riferimento alle figure 1 e 2, una fetta semiconduttrice, indicata nel suo complesso con il numero 1, comprende un substrato 2 in cui sono realizzati una pluralità di dispositivi integrati 3. Per semplicità, nel seguito si farà riferimento al substrato 2 intendendo con ciò indicare tutta la parte della fetta 2 effettivamente contente materiale semiconduttore. In particolare, la definizione include, oltre a un substrato propriamente detto, eventuali strutture semiconduttrici realizzate su o a partire da tale substrato, quali regioni monocristalline connesse al substrato (strati epitassiali) o da esso separate (da strati isolanti, come nei substrati SOI,

Silicon-On-Insulator, o da cavità, come nei substrati SON, Silicon-On-Nothing), regioni policristalline, ottenute con qualunque tecnica (crescita, deposizione). Inoltre, si intende che il substrato 2 può incorporare del tutto o parzialmente elementi isolanti.

I dispositivi integrati 3 possono essere sia circuiti elettronici, di qualsiasi tipo, o anche dispositivi microelettromeccanici (MEMS, MicroElectroMechanical Systems) e sono realizzati con tecniche convenzionali di lavorazione dei semiconduttori. I dispositivi integrati 3 hanno in pianta forma generalmente quadrangolare e, per semplicità, nella forma di realizzazione descritta, si assumerà che siano quadrati.

I dispositivi integrati 3 sono formati nel substrato 2 e sono provvisti di linee di metallizzazione 5 per la connessione dei loro componenti, in modo da assicurare la semplicità, corretta operatività (per le linee metallizzazione 5 sono illustrate solo in modo schematico in figura 2, mentre in figura 1 non sono mostrate). Le linee di metallizzazione 5 si estendono parallelamente alla substrato 2 in direzioni superficie del fra loro perpendicolari, sono disposte su più livelli (quattro, nella forma di realizzazione descritta) e sono separate fra loro da una pluralità di strati dielettrici 6, che formano una struttura isolante 7 sopra il substrato 2. Gli strati dielettrici 6 possono essere dello stesso materiale, ad esempio ossido di silicio, oppure di materiali differenti, secondo le necessità.

Linee di metallizzazione 5 poste su livelli distinti sono collegate, ove richiesto, mediante vie di interconnessione 8a che attraversano uno o più strati dielettrici 6. Contatti 8b assicurano il collegamento fra le linee di metallizzazione 5 del livello più basso con il dispositivo integrato 3.

Dispositivi integrati 3 adiacenti sono separati fra loro da linee di taglio 9, che corrono in direzioni mutuamente perpendicolari.

Inoltre, la struttura isolante 7 è interrotta attorno a ciascun dispositivo integrato 3 da rispettive trincee profonde 10, che raggiungono il substrato 2. Più in dettaglio, le trincee profonde 10 hanno forma di cornici e si estendono lungo linee chiuse (ad esempio ottagonali, come in figura 1), ciascuna circondando un rispettivo dispositivo integrato 3. Le trincee profonde 10 sono pertanto disposte fra i rispettivi dispositivi integrati 3 e le linee di taglio 9 e hanno profondità D tale da attraversare l'intera struttura dielettrica 7, fino a raggiungere il substrato 2. Alla superficie libera della fetta 1, le trincee profonde 10 hanno una larghezza L ad esempio di 2-4  $\mu$ m. La distanza fra il margine esterno di

ciascuna trincea profonda 10 e il rispettivo dispositivo integrato 3 è in questo caso inferiore a 10  $\mu\text{m}\text{.}$

La struttura isolante 7 è ricoperta da uno strato di passivazione 12, che si estende anche sulle pareti delle trincee profonde 10, fino al substrato 2. Lo strato di passivazione 12 è realizzato in un materiale impermeabile, quale ad esempio nitruro di silicio o ossinitruro di silicio, in modo da prevenire l'assorbimento di umidità da parte della struttura isolante 7.

Le porzioni della struttura isolante 7 che ricoprono i dispositivi integrati 3 sono pertanto separate sia le une dalle altre, sia dalle porzioni della struttura isolante 7 che ricoprono le linee di taglio 9. Inoltre, Le porzioni della struttura isolante 7 che ricoprono i dispositivi integrati 3 sono a loro volta protette dallo strato di passivazione 12 e non sono a contatto l'ambiente esterno.

La fetta 1 viene realizzata come descritto di seguito.

Inizialmente (figura 3), i dispositivi integrati 3 vengono fabbricati all'interno di rispettive aree di dispositivo nel substrato 2, utilizzando tecniche convenzionali di lavorazione dei semiconduttori. I dispositivi integrati 3 sono disposti su righe e colonne; fra dispositivi integrati 3 adiacenti sono definite rispettive linee di taglio 9.

Quindi (figura 4), vengono realizzate le linee di

metallizzazione 5 e la struttura dielettrica 7. Più in dettaglio, per ogni livello di metallizzazione viene depositato un rispettivo strato dielettrico 6, in cui vengono aperti passaggi di interconnessione verso il livello sottostante (o verso il substrato 2, nel caso del primo livello di metallizzazione). Viene quindi deposto uno strato metallico (non mostrato per intero nelle figure), che viene sagomato per formare le linee di metallizzazione 5 per il livello in fase di lavorazione.

Una volta terminate le linee di metallizzazione 5 e la struttura dielettrica 7, sulla fetta 1 viene formata una maschera 13 (figura 5), avente aperture 14 che si estendono lungo percorsi chiusi attorno a rispettivi dispositivi integrati 3 (in pratica, lungo il contorno delle trincee profonde 10 che dovranno essere successivamente realizzate).

La struttura isolante 7 viene attaccata attraverso la maschera 13 per aprire le trincee profonde 10. L'attacco è fortemente anisotropo, allo scopo di ottenere pareti ripide, sostanzialmente verticali, e viene terminato quando la superficie del substrato 2 viene raggiunta.

La maschera 13 viene poi rimossa. Lo strato di passivazione 12 viene depositato sull'intera fetta 1 e selettivamente rimosso dai pad (non mostrati) dei dispositivi 3 mediante un attacco mascherato, in modo

convenzionale. Si ottiene così la struttura di figura 2.

La fetta 1 viene poi tagliata lungo le linee di taglio 9 e suddivisa in piastrine ("dice") 15, ciascuno dei quali contiene un rispettivo dispositivo integrato 3. Una delle piastrine 15 è illustrata in figura 6. Più in dettaglio, ogni piastrina 15 comprende una porzione 2' del substrato 2, che include uno dei dispositivi integrati 3 e si estende fino all'interno delle linee di taglio 9 adiacenti, e una porzione della struttura isolante 7, che ricopre dispositivo integrato 3. Inoltre, lungo il margine della porzione 2' del substrato 2 (margine della piastrina) è presente una cornice 17, definita da una porzione della struttura isolante 7 che ricopre porzioni residue delle linee di taglio 9 attorno al dispositivo integrato 3 ed è separata dalla porzione della struttura isolante 7 il dispositivo integrato 3 mediante ricoprente la. rispettiva trincea profonda 10.

Durante il taglio della fetta 1, la struttura isolante 7 rimane esposta soltanto lungo le linee di taglio 9, dove tuttavia non sono presenti elementi strutturali o componenti che possano essere danneggiati. Eventualmente, lungo le linee di taglio 9 possono essere realizzati circuiti per il test dei dispositivi integrati 3 a livello di fetta (EWS, Electrical Wafer Sorting). Tuttavia, tali circuiti non hanno altra utilità e possono essere distrutti

una volta che la fetta 1 è stata validata.

Le porzioni della struttura isolante 7 che ricoprono i dispositivi integrati 3 sono invece separate mediante le trincee profonde 10 e restano protette dallo strato di passivazione 12, che rimane integro al di fuori delle linee di taglio 9.

Anche se la struttura isolante 7 resta esposta lungo le linee di taglio 9, lo strato di passivazione 12, che ricopre le pareti delle trincee profonde 10 fino al substrato 2, impedisce all'umidità di penetrare fino ai dispositivi integrati 3.

La struttura isolante 7 è soggetta a sollecitazioni intense lungo le linee di taglio 9 e l'azione dello strumento di taglio può facilmente causare crepe in queste zone. La propagazione delle crepe viene però arrestata dalle trincee profonde 10, che interrompono la continuità della struttura isolante 7 lungo tutta la sua altezza.

I dispositivi integrati 3 sono quindi efficacemente protetti sia durante tutta la fase di taglio, sia successivamente, durante le fasi di assemblaggio ("packaging") e in tutta la vita utile dei dispositivi integrati 3.

Inoltre, la larghezza delle trincee profonde 10 è molto contenuta (dell'ordine di pochi micron). Il loro impiego in accordo alla forma di realizzazione descritta

permette, quindi, di ottenere un ulteriore importante vantaggio, ossia una considerevole riduzione dell'area complessivamente occupata.

Le figure 7 e 8, in cui parti uguali a quelle già mostrate sono indicate con gli stessi numeri di riferimento, illustrano una diversa forma di realizzazione dell'invenzione.

fetta semiconduttrice questo caso, una 100 Ιn comprende il substrato 2, i dispositivi integrati 3 nel substrato 2, le linee di metallizzazione 5 e la struttura isolante 7. Dispositivi integrati 3 adiacenti sono separati linee di taglio 9. Attorno a ciascun dispositivo integrato 3, la fetta 100 comprende inoltre un rispettivo anello di sigillatura 101, che include una pluralità di anelli metallici 102. Gli anelli metallici 102 sono disposti impilati, ciascuno a un rispettivo livello di metallizzazione, e circondano i rispettivi dispositivi integrati 3. Gli anelli metallici 102 sono mutuamente collegati mediante vie di interconnessione 103, attraversanti rispettivi strati dielettrici 6.

Trincee profonde 110, a forma di cornice, si estendono lungo linee chiuse attorno agli anelli di sigillatura 101 di rispettivi dispositivi integrati 3. Le trincee profonde 110 si estendono in profondità attraverso l'intera struttura isolante 7, fino a raggiungere il substrato 2.

La struttura isolante 7 è inoltre ricoperta da uno strato di passivazione 12 che protegge anche le pareti delle trincee profonde 110 e il substrato 2 al fondo delle trincee profonde 110. Le trincee profonde 110 interrompono la struttura isolante 7, separando porzioni ricoprenti i dispositivi integrati 3 da porzioni ricoprenti le linee di taglio 9. Le porzioni della struttura isolante 7 che proteggono i dispositivi integrati 3 incorporano rispettivi anelli di sigillatura 101 e sono incapsulate dallo strato di passivazione 12.

La fetta 100 viene trattata sostanzialmente come già descritto con riferimento alle figure 3-6. In particolare, gli anelli di sigillatura 101 vengono realizzati per livelli, insieme alle linee di metallizzazione 5. Più precisamente, dagli strati metallici (non mostrati) utilizzate per le linee di metallizzazione 5 vengono ricavati, mediante lo stesso processo di definizione, anche gli anelli metallici 102. Nell'anello di sigillatura 101 possono essere presenti anche solo alcuni degli strati metallici formati altrove nel dispositivo.

Al termine del procedimento, la fetta 100 viene tagliata lungo le linee di taglio 9 e suddivisa così in piastrine 115 (figure 9 e 10), ciascuna delle quali comprende una porzione 2' del substrato 2, in cui è alloggiato un esemplare del dispositivo integrato 3; una

porzione della struttura isolante 7 ricoprente il dispositivo integrato 3; e una cornice 117, che è definita da una porzione della struttura isolante 7 posta al di sopra di porzioni residue delle linee di taglio 9 ed è separata dalla struttura isolante 7 da una rispettiva trincea 110.

La forma di realizzazione descritta offre una doppia protezione sia contro la propagazione di crepe, sia contro l'assorbimento di umidità durante il taglio.

Risulta infine evidente che al procedimento e alla piastrina descritti possono essere apportate modifiche e varianti, senza uscire dall'ambito della presente invenzione, come definita nelle rivendicazioni allegate.

Ad esempio, lo strato di passivazione può essere deposto in più riprese, prima e dopo l'attacco per aprire le trincee profonde. Più precisamente, in questo caso un primo strato di passivazione viene deposto dopo che le linee di metallizzazione e la struttura isolante 7 sono state completate. Quindi, durante una fase di apertura contatti, il primo strato di passivazione viene selettivamente rimosso lungo il percorso dove dovranno poi essere realizzate le trincee profonde. Viene poi effettuato l'attacco anisotropo della struttura isolante per aprire le trincee profonde e, infine, viene deposto un secondo strato di passivazione, che ricopre l'intera fetta e protegge le pareti delle trincee profonde.

## RIVENDICAZIONI

1. Procedimento per la fabbricazione di piastrine semiconduttrici comprendente:

formare dispositivi integrati (3) in un corpo semiconduttore (2) di una fetta semiconduttrice (1; 100); e

formare, sopra al corpo semiconduttore (2), una struttura isolante (7) incorporante linee di metallizzazione (5) per i dispositivi integrati (3);

caratterizzato dal fatto di comprendere:

nella struttura isolante (7), aprire trincee (10; 110) estendentisi lungo linee chiuse attorno a rispettivi dispositivi integrati (3) e aventi profondità tale da raggiungere il corpo semiconduttore (2); e

ricoprire la struttura isolante (7) e pareti delle trincee (10; 110) con uno strato di passivazione (12).

2. Procedimento secondo la rivendicazione 1, comprendente:

disporre i dispositivi integrati (3) su righe e colonne: e

definire linee di taglio (9) fra dispositivi integrati (3) adiacenti;

in cui le trincee (10; 110) sono disposte fra rispettivi dispositivi integrati (3) e le linee di taglio (9) adiacenti ai rispettivi dispositivi integrati (3).

3. Procedimento secondo la rivendicazione 1,

comprendente dividere la fetta (1; 100) lungo le linee di taglio (9) in piastrine (15), ciascuna includente un rispettivo dispositivo integrato (3), una porzione della struttura isolante (7) ricoprente il rispettivo dispositivo integrato (3) e una cornice (17), separata dalla porzione della struttura isolante (7) ricoprente il rispettivo dispositivo integrato (3) mediante la trincea (10; 110) circondante il rispettivo dispositivo integrato (3).

- 4. Procedimento secondo una qualsiasi delle rivendicazioni precedenti, in cui aprire trincee (10; 110) comprende attaccare anisotropicamente la struttura isolante 6).

- 5. Procedimento secondo una qualsiasi delle rivendicazioni precedenti, in cui le trincee (10; 110) sono realizzate in prossimità dei rispettivi dispositivi integrati (3).

- 6. Procedimento secondo una qualsiasi delle rivendicazioni da 1 a 4, comprendente realizzare rispettivi anelli di sigillatura (101) attorno ai dispositivi integrati (3).

- 7. Procedimento secondo la rivendicazione 6, in cui gli anelli di sigillatura (101) sono disposti fra il rispettivo dispositivo integrato (3) e la trincea (10; 110) circondante il rispettivo dispositivo integrato (3).

- 8. Procedimento secondo una qualsiasi delle

rivendicazioni precedenti, in cui formare, sopra al corpo semiconduttore (2), la struttura isolante (7) incorporante linee di metallizzazione (5) per i dispositivi integrati (3) comprende:

formare una pluralità di strati dielettrici (6) sulla fetta (1);

formare un livello di linee di metallizzazione (5) per ogni strato dielettrico (6); e

collegare linee di metallizzazione (5) di livelli distinti attraverso almeno uno strato dielettrico (6).

9. Piastrina semiconduttrice comprendente:

un corpo semiconduttore (2');

un dispositivo integrato (3) nel corpo semiconduttore (2'); e

una struttura isolante (7), disposta sopra al corpo semiconduttore (2') e incorporante linee di metallizzazione (5) per il dispositivo integrato (3);

caratterizzata dal fatto di comprendere:

una cornice isolante (17), disposta lungo margini del corpo semiconduttore (2') e separata dalla struttura isolante (7) mediante una trincea (10; 110), che si estende lungo una linea chiusa attorno al dispositivo integrato (3) e ha profondità tale da raggiungere il corpo semiconduttore (2'); e

uno strato di passivazione (12), ricoprente la

struttura isolante (7) e pareti della trincea (10; 110).

- 10. Piastrina secondo la rivendicazione 9, in cui la trincea (10; 110) è realizzata in prossimità del dispositivo integrato (3).

- 11. Piastrina secondo la rivendicazione 9, comprendente un anello di sigillatura (101) attorno al dispositivo integrato (3).

- 12. Piastrina secondo la rivendicazione 11, in cui l'anello di sigillatura (101) è disposto fra il dispositivo integrato (3) e la trincea (10; 110).

- 13. Piastrina secondo la rivendicazione 11 o 12, in cui l'anello di sigillatura (101) comprende una pluralità di anelli metallici (102) impilati, disposti attorno al dispositivo integrato (2) ed elettricamente connessi fra loro.

p.i.: STMICROELECTRONICS S.R.L.

**Elena CERBARO**

p.i.: STMICROELECTRONICS S.R.L.

p.i.: STMICROELECTRONICS S.R.L.

p.i.: STMICROELECTRONICS S.R.L.

p.i.: STMICROELECTRONICS S.R.L.

p.i.: STMICROELECTRONICS S.R.L.