(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6045567号

(P6045567)

(45) 発行日 平成28年12月14日(2016.12.14)

(24) 登録日 平成28年11月25日(2016.11.25)

(51) Int.Cl.

F 1

G06F 12/02 (2006.01)

G06F 12/00 (2006.01)G06F 12/02 510A

G06F 12/00 597U

請求項の数 20 (全 44 頁)

(21) 出願番号 特願2014-508453 (P2014-508453)

(86) (22) 出願日 平成24年4月22日 (2012.4.22)

(65) 公表番号 特表2014-513356 (P2014-513356A)

(43) 公表日 平成26年5月29日 (2014.5.29)

(86) 國際出願番号 PCT/US2012/034601

(87) 國際公開番号 WO2012/148828

(87) 國際公開日 平成24年11月1日 (2012.11.1)

審査請求日 平成27年4月22日 (2015.4.22)

(31) 優先権主張番号 61/479,249

(32) 優先日 平成23年4月26日 (2011.4.26)

(33) 優先権主張国 米国(US)

(73) 特許権者 500373758

シーゲイト テクノロジー エルエルシー

Seagate Technology

LLC

アメリカ合衆国、95014 カリフォルニア州、クバチーノ、サウス・ディ・アンザ・ブールバード、10200

10200 South De Anza

Blvd Cupertino CA

95014 United States

of America

(74) 代理人 110001195

特許業務法人深見特許事務所

最終頁に続く

(54) 【発明の名称】不揮発性記憶のための可変オーバープロビジョニング

## (57) 【特許請求の範囲】

## 【請求項 1】

システムであって、

1. 若しくはそれ以上のフラッシュメモリの全部または任意の部分を、ホストデータ、システムデータ、システムオーバープロビジョニング (over-provisioning : O.P.)、およびホストオーバープロビジョニングにそれぞれ専用で用いられる分割された 4 つの割り当て領域 (allocation) として動作させる手段と、

1. 若しくはそれ以上のイベントに応答してシステムオーバープロビジョニング割り当て領域およびホストオーバープロビジョニング割り当て領域のうちの任意の 1 若しくは両方のサイズを動的に決定する手段と

を有し、

前記動作させる手段および前記動的に決定する手段は、ソリッドステートディスク (Solid-State Disk : SSD) のコントローラに含まれ、前記フラッシュメモリは前記ソリッドステートディスクに含まれるものであり、

前記イベントは、ホストデータ割り当て領域に記憶されたホストデータの圧縮の変化に少なくとも部分的に起因する前記ホストデータ割り当て領域の使用量の変化を含むものである

システム。

## 【請求項 2】

請求項 1 記載のシステムにおいて、前記動的に決定する手段は、前記ホストデータ割り

当て領域の使用量の圧縮の改善に起因する前記ホストデータ割り当て領域の使用量の低減に応答して、前記システムオーバープロビジョニング割り当て領域のサイズを増加させるものであるシステム。

【請求項 3】

請求項 1 記載のシステムにおいて、前記動的に決定する手段は、前記ホストデータ割り当て領域の使用量の圧縮の改善に起因する前記ホストデータ割り当て領域の使用量の低減に応答して、前記システムオーバープロビジョニング割り当て領域および前記ホストオーバープロビジョニング割り当て領域のうちの任意の 1若しくは両方のサイズを増加させるものであるシステム。

【請求項 4】

請求項 3 記載のシステムにおいて、前記動的に決定する手段は、システムデータ割り当て領域および前記ホストデータ割り当て領域への書き込み帯域幅に少なくとも部分的に基づいて、前記システムオーバープロビジョニング割り当て領域と前記ホストオーバープロビジョニング割り当て領域との間で割り当てを行うものであるシステム。

【請求項 5】

請求項 1 記載のシステムにおいて、前記ホストデータ割り当て領域の前記使用量は、前記ホストデータの圧縮の変化によって少なくとも部分的に決定されるシステム。

【請求項 6】

請求項 1 記載のシステムにおいて、前記ホストデータ割り当て領域の前記使用量の変化は、前記記憶されたホストデータの重複排除の変化に少なくとも部分的に起因するものであるシステム。

【請求項 7】

請求項 1 記載のシステムにおいて、前記ホストデータ割り当て領域の前記使用量の変化は、前記記憶されたホストデータの全部または任意の部分を明示的に割り当て解除するホストコマンドに少なくとも部分的に起因するものであるシステム。

【請求項 8】

請求項 1 記載のシステムにおいて、前記システムオーバープロビジョニング割り当て領域および前記ホストオーバープロビジョニング割り当て領域のうちの任意の 1若しくは両方のサイズの変更は、ガーベジコレクションの直後、再利用の直後、および消去の直後の任意の 1若しくはそれ以上において有効であるシステム。

【請求項 9】

請求項 1 記載のシステムにおいて、さらに、

ホストとインターフェースする手段であって、前記コントローラに具備されており、前記ホストからデータを受け取ることができるようとした前記インターフェースする手段を有するものであるシステム。

【請求項 10】

方法であって、

1 若しくはそれ以上のフラッシュメモリの全部または任意の部分を、ホストデータ、システムデータ、システムオーバープロビジョニング (OP)、およびホストオーバープロビジョニングにそれぞれ専用で用いられる分割された 4 つの割り当て領域として動作させる工程と、

1 若しくはそれ以上のイベントに応答してシステムオーバープロビジョニング割り当て領域およびホストオーバープロビジョニング割り当て領域のうちの任意の 1若しくは両方のサイズを動的に決定する工程と

を有し、

前記動作させる工程および前記動的に決定する工程は、ソリッドステートディスク (SSD) に含まれるコントローラによって実行され、

前記イベントは、ホストデータ割り当て領域に記憶されたホストデータの圧縮の変化に少なくとも部分的に起因する前記ホストデータ割り当て領域の使用量の変化を含むものである

10

20

30

40

50

方法。

【請求項 1 1】

請求項 1 0 記載の方法において、前記動的に決定する工程は、前記ホストデータ割り当て領域の使用量の圧縮の改善に起因する前記ホストデータ割り当て領域の使用量の低減に応答して、前記システムオーバープロビジョニング割り当て領域のサイズを増加させる工程を含むものである方法。

【請求項 1 2】

請求項 1 0 記載の方法において、前記動的に決定する工程は、

前記ホストデータ割り当て領域の使用量の圧縮の改善に起因する前記ホストデータ割り当て領域の使用量の低減に応答して、前記システムオーバープロビジョニング割り当て領域および前記ホストオーバープロビジョニング割り当て領域のうちの任意の 1若しくは両方のサイズを増加させる工程と、

システムデータ割り当て領域および前記ホストデータ割り当て領域への書き込み帯域幅に少なくとも部分的に基づいて、前記システムオーバープロビジョニング割り当て領域と前記ホストオーバープロビジョニング割り当て領域との間で割り当てを行う工程とを含むものである

方法。

【請求項 1 3】

請求項 1 0 記載の方法において、前記ホストデータ割り当て領域の前記使用量は、前記ホストデータの圧縮の変化によって少なくとも部分的に決定される方法。

【請求項 1 4】

請求項 1 0 記載の方法において、前記ホストデータ割り当て領域の前記使用量の変化は、前記記憶されたホストデータの重複排除の変化、および前記記憶されたホストデータの全部または任意の部分を明示的に割り当て解除するホストコマンドのうちの 1 若しくはそれ以上に少なくとも部分的に起因するものである方法。

【請求項 1 5】

請求項 1 0 記載の方法において、前記システムオーバープロビジョニング割り当て領域および前記ホストオーバープロビジョニング割り当て領域のうちの任意の 1若しくは両方のサイズの変更は、ガーベジコレクションの直後、再利用の直後、および消去の直後の任意の 1 若しくはそれ以上において有効である方法。

【請求項 1 6】

処理要素に動作を実行させる命令のセットが記憶されている有形のコンピュータ可読媒体であって、前記動作は、

1 若しくはそれ以上のフラッシュメモリの全部または任意の部分を、ホストデータ、システムデータ、システムオーバープロビジョニング ( O P )、およびホストオーバープロビジョニングにそれぞれ専用で用いられる分割された 4 つの割り当て領域として管理する動作と、

1 若しくはそれ以上のイベントに応答してシステムオーバープロビジョニング割り当て領域およびホストオーバープロビジョニング割り当て領域のうちの任意の 1若しくは両方のサイズを動的に決定する動作と

を有し、

前記有形のコンピュータ可読媒体および前記処理要素はソリッドステートディスク ( S S D ) に具備されており、

前記イベントは、ホストデータ割り当て領域に記憶されたホストデータの圧縮の変化に少なくとも部分的に起因する前記ホストデータ割り当て領域の使用量の変化を含むものである

有形のコンピュータ可読媒体。

【請求項 1 7】

請求項 1 6 記載の有形のコンピュータ可読媒体において、前記動的に決定する動作は、前記ホストデータ割り当て領域の前記使用量の圧縮の改善に起因する前記ホストデータ割

10

20

30

40

50

り當て領域の前記使用量の低減に応答して、前記システムオーバープロビジョニング割り當て領域および前記ホストオーバープロビジョニング割り當て領域のうちの1若しくは両方のサイズを増やし、システムデータ割り當て領域および前記ホストデータ割り當て領域への書き込みのそれぞれの帯域幅に少なくとも部分的に基づいて、前記システムオーバープロビジョニング割り當て領域と前記ホストオーバープロビジョニング割り當て領域との間で割り當てるものである有形のコンピュータ可読媒体。

【請求項18】

請求項16記載の有形のコンピュータ可読媒体において、前記ホストデータ割り當て領域の前記使用量は、前記ホストデータの圧縮の変化によって少なくとも部分的に決定される有形のコンピュータ可読媒体。

10

【請求項19】

請求項16記載の有形のコンピュータ可読媒体において、前記ホストデータ割り當て領域の前記使用量の前記変化は、前記記憶されたホストデータの重複排除の変化、および前記記憶されたホストデータの全部または任意の部分を明示的に割り當て解除するホストコマンドのうちの1若しくはそれ以上に少なくとも部分的に起因するものである有形のコンピュータ可読媒体。

【請求項20】

請求項16記載の有形のコンピュータ可読媒体において、前記システムオーバープロビジョニング割り當て領域および前記ホストオーバープロビジョニング割り當て領域のうちの任意の1若しくは両方のサイズの変更は、ガーベジコレクションの直後、再利用の直後、および消去の直後の任意の1若しくはそれ以上において有効である有形のコンピュータ可読媒体。

20

【発明の詳細な説明】

【技術分野】

【0001】

関連出願の相互参照

本出願の優先権利益の主張を、（それがある場合には、適宜）添付の出願データシート、請求、または送達状において行う。本出願の種類によって許容される範囲内で、本出願はこの参照によりあらゆる目的で以下の出願を組み込むものであり、以下の出願はすべて、発明がなされた時点において本出願と所有者を同じくするものである。

30

【0002】

2011年4月26日付で出願された、Andrew John Tomlinを筆頭発明者とする、「Variable Over-Provisioning for Non-Volatile Storage」という名称の、米国仮出願（整理番号第SF-11-04号および出願番号第61/479249号）。

【背景技術】

【0003】

分野：不揮発性格納技術の進歩が、使用の性能、効率、及び有用性の改善を提供するために必要とされる。

【0004】

関連技術：公知である、または周知であるものとして明記されない限り、コンテキスト、定義、または比較を目的とするものを含む本明細書における技法および概念の言及は、そのような技法または概念が以前から公知であり、あるいは先行技術の一部であることの容認と解釈すべきではない。特許、特許出願、および出版物を含む、本明細書で引用されるあらゆる参照文献は（それがある場合には）、具体的に組み込まれているか否かを問わず、あらゆる目的で、この参照によりその全体が本明細書に組み込まれるものである。

40

この出願の発明に関連する先行技術文献情報としては、以下のものがある（国際出願日以降国際段階で引用された文献及び他国に国内移行した際に引用された文献を含む）。

（先行技術文献）

（特許文献）

50

|         |                           |

|---------|---------------------------|

| (特許文献1) | 特開2007-226557号公報          |

| (特許文献2) | 特開平07-160602号公報           |

| (特許文献3) | 米国特許出願公開第2009/0249022号明細書 |

| (特許文献4) | 米国特許出願公開第2004/0250026号明細書 |

**【発明の概要】****【課題を解決するための手段】****【0005】**

本発明は多くの仕方で実施されてよく、これには、プロセス、製造品、装置、システム、組成物としての仕方、ならびに、コンピュータ可読記憶媒体（ディスクといった光学的大容量記憶装置および／または磁気的大容量記憶装置、フラッシュストレージといった不揮発性記憶を有する集積回路など）や、プログラム命令が光通信リンクまたは電子通信リンク上で送られるコンピュータネットワークといったコンピュータ可読媒体としての仕方が含まれうる。本明細書では、これらの実施態様、または本発明が取りうる任意の他の形態を、技法と呼ぶ場合もある。詳細な説明では、上記の分野における使用の性能、効率、および有用性の改善を可能にする本発明の1若しくはそれ以上の実施形態の説明を提供する。詳細な説明は、詳細な説明の残りの部分のより迅速な理解を容易にするための導入部を含む。導入部は、本明細書で説明する概念に従うシステム、方法、製造品、およびコンピュータ可読媒体のうちの1若しくはそれ以上の例示的実施形態を含む。結論の項でより詳細に論じるように、本発明は、発行される特許請求の範囲内のあらゆる可能な改変形態および変形形態を包含するものである。

10

**【図面の簡単な説明】****【0006】**

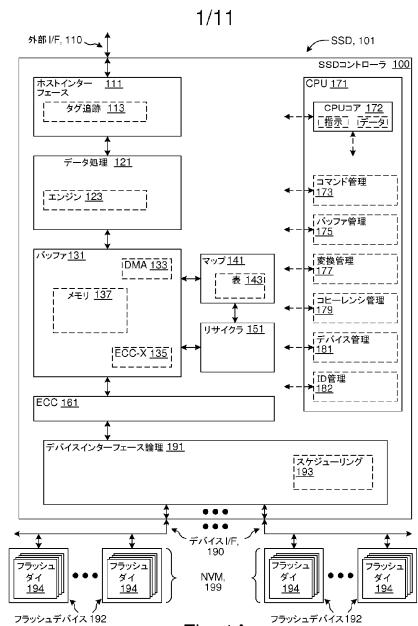

【図1A】図1Aは、不揮発性メモリ（Non-Volatile Memory: NV M）要素（フラッシュメモリなど）によって実施されるような不揮発性記憶を管理するための可変オーバープロビジョニング（Over-Provisioning: OP）を使用するSSDコントローラを含むソリッドステートディスク（Solid-State Disk: SSD）の実施形態の選択された詳細を示す図である。

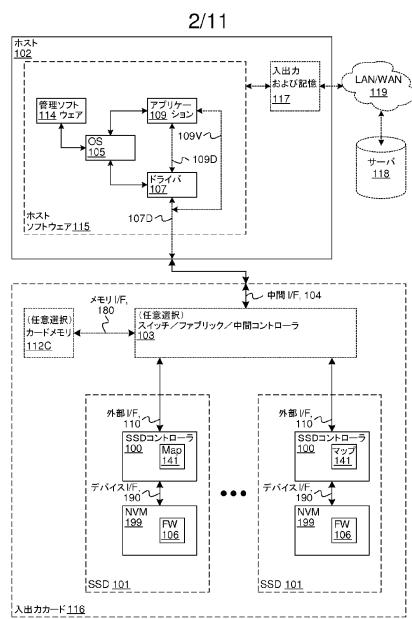

【図1B】図1Bは、図1AのSSDの1つ若しくはそれ以上のインスタンスを含むシステムの様々な実施形態の選択された詳細を示す図である。

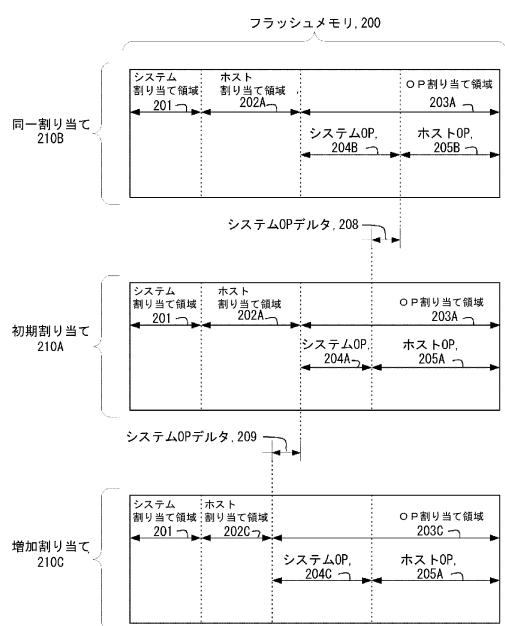

【図2】図2は、NVMを管理するために可変OPを使用するシステムの様々な実施形態による、OP用途を含む、フラッシュメモリのホスト割り当て領域およびシステム割り当て領域の選択的な詳細を示す図である。

20

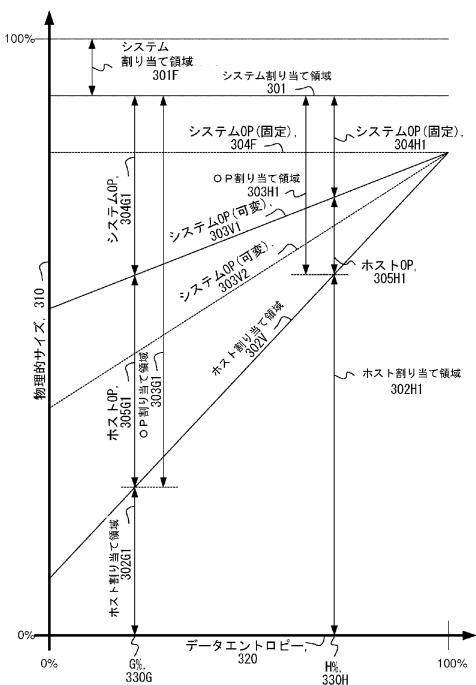

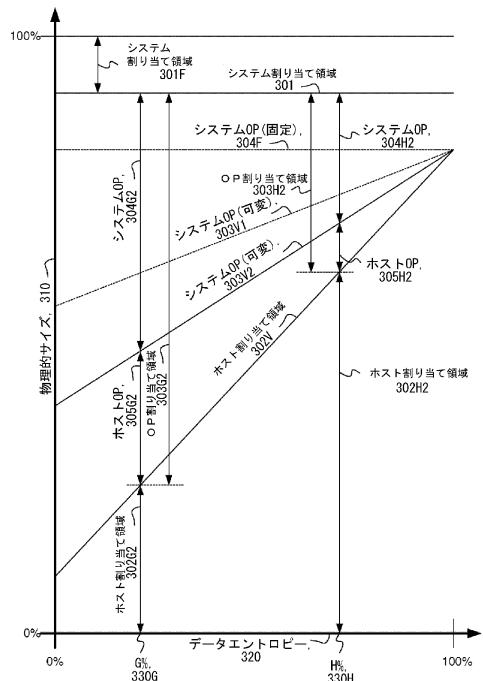

【図3A】図3Aおよび図3Bは、動的に変動するデータエントロピーに関連するものとしての動的に変動するホストOPおよびシステムOPの様々な実施形態の選択された詳細を示す図である。

【図3B】図3Aおよび図3Bは、動的に変動するデータエントロピーに関連するものとしての動的に変動するホストOPおよびシステムOPの様々な実施形態の選択された詳細を示す図である。

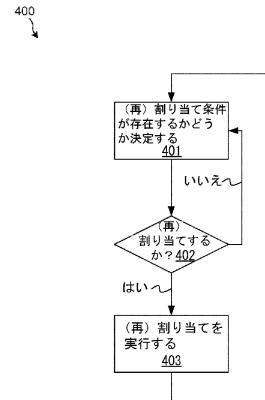

【図4】図4は、NVMを管理するための可変OPのコンテキストにおけるOPリソースの（再）割り当ての実施形態を示す流れ図である。

30

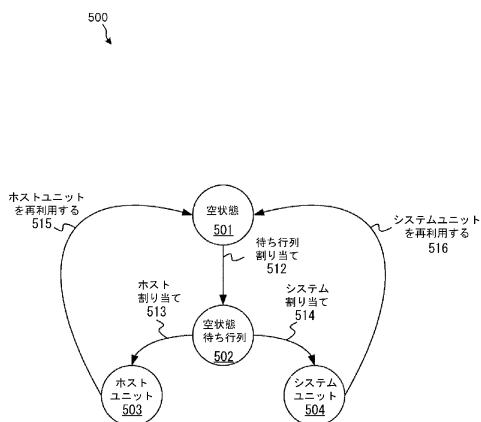

【図5】図5は、フラッシュメモリの被管理ユニットのライフサイクルの実施形態を示す流れ図である。

**【0007】**

40

【表1】

図面の参照符号の一覧

| 参照符号    | 要素名                              |    |

|---------|----------------------------------|----|

| 1 0 0   | S S Dコントローラ                      |    |

| 1 0 1   | S S D                            |    |

| 1 0 2   | ホスト                              |    |

| 1 0 3   | (任意選択の)スイッチ/ファブリック/中間コントローラ      | 10 |

| 1 0 4   | 中間インターフェース                       |    |

| 1 0 5   | O S                              |    |

| 1 0 6   | ファームウェア (F i r mW a r e : F W)   |    |

| 1 0 7   | ドライバ                             |    |

| 1 0 7 D | 点線矢印 (ホストソフトウェア←→入出力装置通信)        |    |

| 1 0 9   | アプリケーション                         |    |

| 1 0 9 D | 点線矢印 (ドライバを介したアプリケーション←→入出力装置通信) |    |

| 1 0 9 V | 点線矢印 (V Fを介したアプリケーション←→入出力装置通信)  |    |

| 1 1 0   | 外部インターフェース                       |    |

| 1 1 1   | ホストインターフェース                      |    |

| 1 1 2 C | (任意選択の)カードメモリ                    |    |

| 1 1 3   | タグ追跡                             |    |

| 1 1 4   | マルチデバイス管理ソフトウェア                  |    |

| 1 1 5   | ホストソフトウェア                        |    |

| 1 1 6   | 入出力カード                           | 20 |

| 1 1 7   | 入出力装置および記憶装置/リソース                |    |

| 1 1 8   | サーバ                              |    |

| 1 1 9   | LAN/WAN                          |    |

| 1 2 1   | データ処理                            |    |

| 1 2 3   | エンジン                             |    |

| 1 3 1   | バッファ                             |    |

| 1 3 3   | D M A                            |    |

| 1 3 5   | E C C - X                        |    |

| 1 3 7   | メモリ                              |    |

| 1 4 1   | マップ                              |    |

| 1 4 3   | 表                                |    |

| 1 5 1   | リサイクル                            |    |

| 1 6 1   | E C C                            | 30 |

| 1 7 1   | C P U                            |    |

| 1 7 2   | C P Uコア                          |    |

| 1 7 3   | コマンド管理                           |    |

| 1 7 5   | バッファ管理                           |    |

| 1 7 7   | 変換管理                             |    |

| 1 7 9   | コピーレンジ管理                         |    |

| 1 8 0   | メモリインターフェース                      |    |

| 1 8 1   | デバイス管理                           |    |

| 1 8 2   | 識別情報管理                           |    |

| 1 9 0   | デバイスインターフェース                     |    |

| 1 9 1   | デバイスインターフェース論理                   |    |

| 1 9 2   | フラッシュデバイス                        |    |

| 1 9 3   | スケジューリング                         | 40 |

| 参照符号  | 要素名                     |

|-------|-------------------------|

| 194   | フラッシュディ                 |

| 199   | NVM                     |

| 200   | フラッシュメモリ                |

| 201   | システム割り当て領域              |

| 202A  | ホスト割り当て領域               |

| 202C  | ホスト割り当て領域               |

| 203A  | OP割り当て領域                |

| 203C  | OP割り当て領域                |

| 204A  | システムOP割り当て領域            |

| 204B  | システムOP割り当て領域            |

| 204C  | システムOP割り当て領域            |

| 205A  | ホストOP割り当て領域             |

| 205B  | ホストOP割り当て領域             |

| 208   | システムOP割り当て領域デルタ         |

| 209   | システムOP割り当て領域デルタ         |

| 210A  | 初期割り当て                  |

| 210B  | 同一割り当て                  |

| 210C  | 増加割り当て                  |

| 301   | システム割り当て領域              |

| 301F  | システム割り当て領域 (固定)         |

| 302G1 | ホスト割り当て領域               |

| 302G2 | ホスト割り当て領域               |

| 302H1 | ホスト割り当て領域               |

| 302H2 | ホスト割り当て領域               |

| 302V  | ホスト割り当て領域               |

| 303G1 | (組み合わせ) OP割り当て領域        |

| 303G2 | (組み合わせ) OP割り当て領域        |

| 303H1 | (組み合わせ) OP割り当て領域        |

| 303H2 | (組み合わせ) OP割り当て領域        |

| 303V1 | システムOP割り当て領域 (可変)       |

| 303V2 | システムOP割り当て領域 (可変)       |

| 304F  | システムOP割り当て領域 (固定)       |

| 304G1 | システムOP割り当て領域            |

| 304G2 | システムOP割り当て領域            |

| 304H1 | システムOP割り当て領域            |

| 304H2 | システムOP割り当て領域            |

| 305G1 | ホストOP割り当て領域             |

| 305G2 | ホストOP割り当て領域             |

| 305H1 | ホストOP割り当て領域             |

| 305H2 | ホストOP割り当て領域             |

| 310   | 物理的サイズ                  |

| 320   | データエントロピー               |

| 330G  | G%                      |

| 330H  | H%                      |

| 400   | 流れ図                     |

| 401   | (再) 割り当て条件が存在するかどうか決定する |

| 402   | (再) 割り当てるか?             |

| 参照符号 | 要素名            |

|------|----------------|

| 403  | (再) 割り当てを実行する  |

| 500  | 流れ図            |

| 501  | 空いている          |

| 502  | 空いている待ち行列      |

| 503  | ホスト単位          |

| 504  | システム単位         |

| 512  | 待ち行列割り当て       |

| 513  | ホスト割り当て領域      |

| 514  | システム割り当て領域     |

| 515  | ホストユニットを再利用する  |

| 516  | システムユニットを再利用する |

10

20

30

40

50

**【発明を実施するための形態】****【0008】**

本発明の1つ若しくはそれ以上の実施形態の詳細な説明を、以下で、本発明の選択された詳細を図示する添付の図を併用して行う。本発明を実施形態との関連で説明する。実施形態は、本明細書では、単なる例示であると理解されるものであり、本発明は、明確に、本明細書中の実施形態のいずれか若しくは全部に、またはいずれか若しくは全部によって限定されるものではなく、本発明は、多数の代替形態、改変形態、および均等物を包含するものである。説明が単調にならないように、様々な言葉によるラベル（これに限定されるものではないが、最初の、最後の、ある一定の、様々な、別の、他の、特定の、選択の、いくつかの、目立ったなど）が実施形態のセットを区別するために適用される場合がある。本明細書で使用する場合、そのようなラベルは、明確に、質を伝えるためのものでも、いかなる形の好みや先入観を伝えるためのものでもなく、単に、別々のセットを都合よく区別するためのものにすぎない。開示するプロセスのいくつかの動作の順序は本発明の範囲内で変更可能である。多様な実施形態がプロセス、方法、および／またはプログラム命令の各特徴の差異を説明するのに使用される場合は常に、所定の、または動的に決定される基準に従って、複数の多様な実施形態にそれぞれ対応する複数の動作モードの1つの静的選択および／または動的選択を行う他の実施形態が企図されている。以下の説明では、本発明の十分な理解を提供するために、多数の具体的な詳細を示す。それらの詳細は例として示すものであり、本発明は、それらの詳細の一部または全部がなくても、特許請求の範囲に従って実施されうる。わかりやすくするために、本発明に関連した技術分野で公知の技術資料は、本発明が必要に曖昧になることのないように詳細に説明していない。

**【0009】****概説**

この概説は、詳細な説明のより迅速な理解を助けるために含まれるにすぎず、本発明は、（それがある場合には、明示的な例を含む）この概説で提示される概念だけに限定されるものではなく、どんな概説の段落も、必然的に、主題全体の縮約された見方であり、網羅的な、または限定的な記述であることを意味するものではない。例えば、以下の概説は、スペースおよび編成によりある一定の実施形態だけに限定される概要情報を提供するものである。特許請求の範囲が究極的にそこに導かれることになる実施形態を含む多くの他の実施形態があり、それらを本明細書の残りの部分にわたって論じる。

**【0010】****頭字語**

ここで定義される様々な縮めた表現の略語（例えば、頭字語）の少なくとも一部が本明細書において使用される特定の要素を指す。

**【0011】**

【表 2】

| 頭字語   | 説明                                                                               |

|-------|----------------------------------------------------------------------------------|

| AHCI  | Advanced Host Controller Interface (アドバンスド・ホスト・コントローラ・インターフェース)                  |

| API   | Application Program Interface (アプリケーション・プログラム・インターフェース)                          |

| BCH   | Bose Chaudhuri Hocquenghem (ボーズ・チャドヒ・オッケンジエム)                                    |

| ATA   | Advanced Technology Attachment (AT Attachment) (アドバンスド・テクノロジ・アタッチメント(ATアタッチメント)) |

| CD    | Compact Disk (コンパクトディスク)                                                         |

| CF    | Compact Flash (コンパクトフラッシュ)                                                       |

| CPU   | Central Processing Unit (中央処理装置)                                                 |

| CRC   | Cyclic Redundancy Check (巡回冗長検査)                                                 |

| DAS   | Direct Attached Storage (ダイレクト・アタッチト・ストレージ)                                      |

| DDR   | Double-Data-Rate (ダブルデータレート)                                                     |

| DES   | Data Encryption Standard (データ暗号化規格)                                              |

| DMA   | Direct Memory Access (直接メモリアクセス)                                                 |

| DNA   | Direct NAND Access (直接NANDアクセス)                                                  |

| DRAM  | Dynamic Random Access Memory (ダイナミック・ランダム・アクセス・メモリ)                              |

| DVD   | Digital Versatile/Video Disk (デジタル多用途/ビデオディスク)                                   |

| DVR   | Digital Video Recorder (デジタル・ビデオ・レコーダ)                                           |

| ECC   | Error-Correcting Code (誤り訂正符号)                                                   |

| eMMC  | Embedded MultiMedia Card (組み込みマルチメディアカード)                                        |

| eSATA | External Serial Advanced Technology Attachment (外部シリアル・アドバンスド・テクノロジ・アタッチメント)     |

| GPS   | Global Positioning System (全地球測位システム)                                            |

| I/O   | Input/Output (入出力)                                                               |

| IC    | Integrated Circuit (集積回路)                                                        |

| IDE   | Integrated Drive Electronics (統合ドライブエレクトロニクス)                                    |

| LAN   | Local Area Network (ローカル・エリア)                                                    |

10

20

30

40

| 頭字語    | 説明                                                                                                     |

|--------|--------------------------------------------------------------------------------------------------------|

|        | ア・ネットワーク)                                                                                              |

| LB     | Logical Block (論理ブロック)                                                                                 |

| LBA    | Logical Block Address (論理ブロックアドレス)                                                                     |

| LDPC   | Low-Density Parity-Check (低密度パリティ検査)                                                                   |

| LPN    | Logical Page Number (論理ページ番号)                                                                          |

| MLC    | Multi-Level Cell (マルチレベルセル)                                                                            |

| MMC    | MultiMediaCard (マルチメディアカード)                                                                            |

| NAS    | Network Attached Storage (ネットワーク・アタッチト・ストレージ)                                                          |

| NCQ    | Native Command Queuing (ネイティブ・コマンド・キューイング)                                                             |

| NVM    | Non-Volatile Memory (不揮発性メモリ)                                                                          |

| ONA    | Optimized NAND Access (最適化NANDアクセス)                                                                    |

| ONFI   | Open NAND Flash Interface (オープンNANDフラッシュインターフェース)                                                      |

| OP     | Over-Provisioning (オーバープロビジョニング)                                                                       |

| OS     | Operating System (オペレーティングシステム)                                                                        |

| PC     | Personal Computer (パーソナルコンピュータ)                                                                        |

| PCIe   | Peripheral Component Interconnect express (PCI express) (周辺装置相互接続エクスプレス (PCIエクスプレス) )                  |

| PDA    | Personal Digital Assistant (携帯情報端末)                                                                    |

| POS    | Point Of Sale (販売時点)                                                                                   |

| RAID   | Redundant Array of Inexpensive/Independent Disks (安価なディスク/独立ディスクの冗長アレイ)                                |

| R eRAM | Resistive Random Access Memory (抵抗変化メモリ)                                                               |

| RS     | Reed-Solomon (リード-ソロモン)                                                                                |

| SAN    | Storage Attached Network (ストレージ・アタッチト・ネットワーク)                                                          |

| SAS    | Serial Attached Small Computer System Interface (Serial SCSI) (シリアル小型コンピュータ・システム・インターフェイス (シリアルSCSI) ) |

| SATA   | Serial Advanced Technology Attachment (Serial ATA) (シリアル・アドバンスド・テクノロジ・アタッチメント                          |

10

20

30

40

| 頭字語   | 説明                                                                 |

|-------|--------------------------------------------------------------------|

|       | (シリアルATA))                                                         |

| SCSI  | Small Computer System Interface (小型コンピュータ・システム・インターフェイス)           |

| SD    | Secure Digital (セキュアデジタル)                                          |

| SDR   | Single-Data-Rate (シングルデータレート)                                      |

| SLC   | Single-Level Cell (シングルレベルセル)                                      |

| SMART | Self-Monitoring Analysis and Reporting Technology (自己モニタリング分析報告技術) |

| SSD   | Solid-State Disk/Drive (ソリッドステートディスク/ドライブ)                         |

| UFS   | Unified Flash Storage (ユニファイド・フラッシュ・ストレージ)                         |

| USB   | Universal Serial Bus (ユニバーサル・シリアル・バス)                              |

| VF    | Virtual Function (仮想関数)                                            |

| WAN   | Wide Area Network (広域ネットワーク)                                       |

10

20

## 【0012】

概念的には、SSDデータの不揮発性記憶に使用されるようなNVM用の可変OPを提供するSSDコントローラは、様々な状況において、より長い寿命、高度な信頼性、および/または改善された性能を可能にする。概念的には、NVMは、ホストデータの記憶とシステムデータの記憶とOP用途との間で動的に割り当てられ、OP用途割り当て領域は、ホストデータOPとシステムデータOPとの間で動的に割り当てられる。割り当ては、SSD、SSDコントローラ、および/またはNVMの様々な動作特性および/またはコンテキストに基づいて動的に変化する。

## 【0013】

SSDに結合されたホストはSSDにより新しいデータを書き込む。より新しいホストデータがより古いホストデータよりもランダム性の低いものである（よってより効果的に圧縮可能である）場合には、ホストデータのエントロピーは減少している。これに応答して、SSDのSSDコントローラは、NVM（フラッシュメモリなど）の割り当てを動的に変更し、ホスト割り当て領域を減らすと同時にOP割り当て領域を増やし、NVMへのシステムデータ書き込みおよびホストデータ書き込みの帯域幅の比率に従って比例的に、システムOPとホストOPとの間でOP割り当て領域を動的に割り当てる。より新しいホストデータがよりランダム性の高いものである（よってあまり効果的に圧縮できない）場合には、ホスト割り当て領域は増加され、また、OP割り当て領域は減少され、比率に従ってシステムOPとホストOPとの間で割り当てられる。

30

40

## 【0014】

例えば、NVMの「空き領域」が（ホストデータ記憶空間またはシステムデータ記憶空間の低減/増加などが原因で）増/減する際に、OPに使用される割り当て領域は、（任意選択で、ガーベジコレクション、再利用、および/または消去に適応するための遅延の後で）増加/減少される。別の例では、システムデータOPとホストデータOPとの間のOPに使用される割り当て領域は、動的に変動する値に比例し、動的に変動する値は、NVMへのシステムデータ書き込みの帯域幅をNVMへのホストデータ書き込みの帯域幅で割ったものである。ホストデータ記憶空間は少なくとも、ホストデータの変動するエントロピー（例えば、圧縮性および/または重複排除によるサイズ低減への応答性）ならびに以前に記憶されたホストデータを明示的に割り当て解除するホストコマンドに従って変動

50

する。

【0015】

第1の例として、OPに利用可能なNVMが所定の量だけ減少する（増加する）場合には、システムデータOPおよびホストデータOPは、システムデータOPとホストデータOPとの間の同じ比率を維持しながら当該の量だけひとまとめにして減らされる（増やされる）。第2の例として、システムデータ転送速度対ホストデータ転送速度の比率が変化する場合には、システムデータOPおよびホストデータOPは、比率の変化に従って調整される。システムデータ転送速度の一例はNVMへのシステムデータ書き込みの帯域幅であり、ホストデータ転送速度の一例はNVMへのホストデータ書き込み（例えば、システムデータ書き込みではない書き込みなど）の帯域幅であり、そのため、システムデータ書き込みは、ホストデータを書き込むNVM書き込みを除いたすべてのNVM書き込みに対応する。ホストデータの書き込みは、任意選択で、かつ／または選択的に、ホストデータおよび／またはホストデータに対応するECC情報を識別するのに使用できるヘッダの書き込みを含む。第3の例として、システムデータOPおよびホストデータOPは、例えば、NVMのユニットが割り当てられるときや、（一部が使用されたNVMユニットを再利用するためなどの）ガーベジコレクションが実行されるときに、それぞれのデータ転送速度に従って（例えば、データ転送速度の比率に従って直線的に）割り当てられる。

【0016】

第4の例では、第1の例および第2（または第3の）例は組み合わされ、そのため、OPに利用可能なNVMの変化およびシステム対ホストデータ転送速度比率の変化が、対応するシステムデータOPおよびホストデータOPの割り当てに変更をもたらす。さらに別の例は前述の例のいずれかを含み、システムデータOPおよび／またはホストデータOPは、NVMのユニットの割り当てと関連付けられたイベントや、NVMの一部分のガーベジコレクションや、NVMのユニットがある種類の用途（ホストデータなど）から別の種類の用途（システムデータなど）への再割り当てに利用可能な任意の他のイベントといったイベントに基づいて動的に再割り当てされる。

【0017】

ある実施形態では、システム用途とホスト用途との間でのOPリソースの割り当ては、それぞれの最小値／最大値および／または粒度に従う。例えば、システムOP割り当て領域および／またはホストOP割り当て領域は、ホスト割り当て領域および／またはシステムデータ転送速度対ホストデータ転送速度の比率とは無関係な、所定数のユニットの最小値である。別の例では、システムOP割り当て領域および／またはホストOP割り当て領域は、所定数のユニットと一致する粒度を有する。

【0018】

様々な実施形態において、NVM（フラッシュメモリなど）は、（フラッシュメモリ）の（被管理）ユニットと呼ばれる、また、本明細書では、「被管理ユニット（managed units）」若しくは「ユニット」とも呼ばれる部分として管理される。（フラッシュメモリ）の（被管理）ユニットの例は、フラッシュメモリの1若しくはそれ以上の連続部分および／または非連続部分であり、例えば、フラッシュメモリの1若しくはそれ以上の連続／非連続ページ／ブロック、フラッシュメモリの（本明細書の別の個所で説明する）1若しくはそれ以上のR-ブロック、あるいは（割り当て領域といった）管理操作に適したフラッシュメモリの任意の下位部分（sub-portions）である。ある実施形態では、フラッシュメモリの割り当て領域は、フラッシュメモリ管理ユニットの整数量子に一致する粒度を有する。

【0019】

R-ブロックの一例は、フラッシュメモリのすべてのダイに及ぶ論理スライスまたはセクションである。例えば、R個のフラッシュダイを有し、各フラッシュダイがN個のブロックを有するフラッシュメモリにおいて、各R-ブロックは、合計でN個のR-ブロックについて、全部合わせたフラッシュダイの各々からの第iのブロックである。別の例では、R個のフラッシュダイを有し、各々がN個のブロックを有するフラッシュメモリにおいて

て、各 R - ブロックは、合計で  $N / 2$  個の R - ブロックについて、フラッシュメモリの各々からの第  $i$  および第  $(i + 1)$  のブロックである。さらに別の例では、複数のデュアル・プレーン・デバイスを有するフラッシュメモリにおいて、各 R - ブロックは、デュアル・プレーン・デバイスの各々からの第  $i$  の偶数ブロックおよび第  $i$  の奇数ブロックである。

#### 【 0 0 2 0 】

ある状況では、特定のサイズのホストストレージ書き込みが SSD のフラッシュメモリへの（各々が、例えば、その特定のサイズの倍数などのサイズを有する）複数の書き込みを生じるときに、書き込み増幅が生じる。複数の書き込みは、例えば、フラッシュメモリのある部分を書き込む（例えばプログラムする）前の当該部分の消去、ウェアアレベリング、ガーベジコレクション、およびシステムデータ書き込みを生じるフラッシュメモリ管理操作などから生じる。書き込み増幅の計算の一例は、（例えば、ホスト書き込みと関連付けられたホストデータの書き込みを完了するためのシステム書き込みなどを含む）ホスト書き込みの特定の集まりの代わりにフラッシュメモリに書き込まれたデータの量を、ホスト書き込みのその特定の集まりによって書き込まれたデータの量で割ったものである。

10

#### 【 0 0 2 1 】

ある実施形態および / または使用シナリオでは、書き込み増幅は比較的低く、これは例えば、ガーベジコレクションおよび / または他の操作が、フラッシュメモリの比較的大きい部分を消去させ、書き込み（プログラミングなど）に容易に利用できるようにしたときの連続したアドレスへのホスト書き込みの比較的長いシーケンスなどである。ある実施形態および / または使用シナリオでは、書き込み増幅は比較的高く、これは例えば、フラッシュメモリの比較的小さい部分が消去され、書き込みに容易に利用できるときのランダムなアドレスへのホスト書き込みの比較的長いシーケンスなどである。

20

#### 【 0 0 2 2 】

SSD 用のコントローラによって、SSD のフラッシュメモリは、ホストデータの記憶領域とシステムデータの記憶領域との間で割り当てられる。ホストデータは SSD に結合されたホストと関連付けられており、システムデータはコントローラと関連付けられている。コントローラは、フラッシュメモリの全体の空き領域に従って割り当てを動的に制御する。ある実施形態および / または使用シナリオでは、システムデータへの割り当てを増やすこと（およびホストデータへの割り当てを減らすこと）によるシステムデータの OP の増加は、書き込み増幅の低減ならびに SSD および / またはフラッシュメモリの性能、信頼性、および / または寿命の改善を可能にする。フラッシュメモリの全体の空き領域は、ホストデータ割り当て領域の空き領域およびシステムデータ割り当て領域の空き領域である。

30

#### 【 0 0 2 3 】

動的割り当て制御は、様々な実施形態において、例えば、ホストデータが圧縮され、重複排除され、または何らかの方法で変換されて、様々なサイズの論理ユニットを生じることになるといった、ホストデータが様々なサイズの論理ユニットを含む場合に使用される。動的割り当て制御は、様々な実施形態において、例えば、ホストデータが比較的高度に圧縮可能であり、または重複排除によって比較的高度にコンパクト化可能であるといった、ホストデータが比較的高度に縮減可能である場合に使用される。

40

#### 【 0 0 2 4 】

ホストデータは、1 若しくはそれ以上のホスト（コンピュータホストなど）から受け取られた（若しくはホストに提供された）データ、または（圧縮、重複排除、暗号化、任意の可逆変換などによって）ホストから（若しくはホストへ）のデータから導出されたデータを含む。ホストデータの例には、ユーザデータおよび / またはファイル、アプリケーションデータおよび / またはファイル、ドライバデータおよび / またはファイル、OS データ、データ構造、および / またはファイル、ならびに SSD とホストとの間のインターフェースを介してホストによって提供される他の情報が含まれる。NVM に書き込まれるホストデータは、任意選択で、かつ / または選択的に、ホストデータおよび / またはホストデータに対応する ECC 情報を識別するのに使用されるヘッダといった、SSD コントロ

50

ーラによって付加され、ホストデータと一緒に書き込まれるメタデータを含む。システムデータは、コントローラ、SSD、および/またはフラッシュメモリ、またはこれらの任意の部分の管理または操作に関連したデータを含む。システムデータの例には、LBAからフラッシュ・メモリ・ロックへのマッピング情報および誤動作（例えばクラッシュや電源障害）が発生した場合の正しい状態の復元を可能にするためのチェックポイント情報が含まれる。システムデータの他の例には、ホストデータに特有ではないが、SSD、SSDコントローラ、および/若しくはNVM（フラッシュメモリなど）によるホストデータの記憶管理、またはSSD、SSDコントローラ、および/若しくはNVMの動作管理に役立つ情報が含まれる。

【0025】

10

様々な状況において、使用されるホストデータ空間対使用されるシステムデータ空間の比率は100:1から500:1までの比率である。様々な状況、例えば、比較的多数のランダムな書き込みを有する状況では、システムデータ書き込み帯域幅対ホストデータ書き込み帯域幅の比率は2:1から5:1までの比率である。

【0026】

本明細書の別の箇所では、フラッシュメモリへのホストデータ書き込みの帯域幅をホストデータ書き込みの帯域幅、あるいはホスト書き込み帯域幅と呼ぶこともあり、フラッシュメモリへのシステムデータ書き込みを、システムデータ書き込みの帯域幅、あるいはシステム書き込み帯域幅と呼ぶこともある。

【0027】

20

一部の実施形態では、NVM内の様々なサイズの量の圧縮データにアクセスすることにより、ある使用シナリオでは記憶効率が改善される。例えば、SSDコントローラは、コンピューティングホストから（例えばディスク書き込みコマンドに関連した）（圧縮されていない）データを受け取り、データを圧縮し、データをフラッシュメモリへ記憶する。コンピューティングホストからの（例えばディスク読み出しこマンドに関連した）その後の要求に応答して、SSDコントローラはフラッシュメモリから圧縮データを読み出し、圧縮データを解凍し、解凍されたデータをコンピューティングホストに提供する。圧縮データは、様々なサイズの量に従ってフラッシュメモリに記憶され、各量のサイズは、例えば、圧縮アルゴリズム、動作モード、様々なデータに関する圧縮有効性により変動する。SSDコントローラは、一部は、含まれるマップ表を調べて（1つまたは複数の）ヘッダがフラッシュメモリのどこに記憶されているか確認することによってデータを解凍する。SSDコントローラは、適切な（圧縮）データがフラッシュメモリのどこに記憶されているか確認するためにフラッシュメモリから得た（1つまたは複数の）ヘッダをパースする。SSDコントローラは、コンピューティングホストに提供すべき解凍データを生成するために、フラッシュメモリからの適切なデータを解凍する。

30

【0028】

様々な実施形態では、SSDコントローラは、コンピューティングホストとインターフェースするためのホストインターフェースと、フラッシュメモリといったNVMとインターフェースするためのインターフェースと、各インターフェースを制御し、圧縮および解凍と共に、低レベル誤り訂正、高レベル誤り訂正、ならびに独立シリコン素子を用いた動的高レベル冗長性モード管理を行う（かつ/または行うことの様々な態様を制御する）ための回路とを含む。

40

【0029】

様々な実施形態によれば、あるホストインターフェースは、USBインターフェース規格、CFインターフェース規格、MMCインターフェース規格、eMMCインターフェース規格、サンダーボルトインターフェース規格、UFSインターフェース規格、SDインターフェース規格、メモリ・スティック・インターフェース規格、xDピクチャ・カード・インターフェース規格、IDEインターフェース規格、SATAインターフェース規格、SCSIインターフェース規格、SASインターフェース規格、およびPCIeインターフェース規格のうちの1つ若しくはそれ以上と適合する。様々な実施形態によれば、コ

50

コンピューティングホストは、コンピュータ、ワークステーションコンピュータ、サーバコンピュータ、ストレージサーバ、S A N、N A Sデバイス、D A Sデバイス、ストレージアプライアンス、P C、ラップトップコンピュータ、ノートブックコンピュータ、ネットブックコンピュータ、タブレット機器またはタブレットコンピュータ、ウルトラブックコンピュータ、電子読み出し装置（e - r e a d e rなど）、P D A、ナビゲーションシステム、（ハンドヘルド型）G P S機器、自動通信路制御システム、自動車媒体制御システムまたはコンピュータ、プリンタ、コピー機またはファックス機またはオールインワン機器、P O S機器、金銭登録機、メディアプレーヤ、テレビ、メディアレコーダ、D V R、ディジタルカメラ、セルラハンドセット、コードレス電話機ハンドセット、および電子ゲームのうちの全部または任意の部分である。一部の実施形態では、インターフェースホスト（S A S / S A T Aブリッジなど）は、コンピューティングホストおよび／またはコンピューティングホストへのブリッジとして動作する。10

#### 【0030】

様々な実施形態では、S S Dコントローラは、1つ若しくはそれ以上のプロセッサを含む。プロセッサは、S S Dコントローラの動作を制御し、かつ／または行うためにファームウェアを実行する。S S Dコントローラは、コマンドおよび／または状況ならびにデータを送り、受け取るためにコンピューティングホストと通信する。コンピューティングホストは、オペレーティングシステム、ドライバ、およびアプリケーションのうちの1つ若しくはそれ以上を実行する。コンピューティングホストによるS S Dコントローラとの通信は、任意選択で、かつ／または選択的に、ドライバおよび／またはアプリケーションによるものである。第1の例では、S S Dコントローラへのすべての通信がドライバによるものであり、アプリケーションは、ドライバに高レベルコマンドを提供し、ドライバがそれをS S Dコントローラのための特定のコマンドに変換する。第2の例では、ドライバはバイパスモードを実施し、アプリケーションは、ドライバを介してS S Dコントローラに特定のコマンドを送ることができるようになっている。第3の例では、P C I e S S Dコントローラが1つ若しくはそれ以上の仮想機能（V i r t u a l F u n c t i o n s : V F s）をサポートし、アプリケーションが、一度構成されると、ドライバをバイパスしてS S Dコントローラを直接通信することを可能にする。20

#### 【0031】

様々な実施形態によれば、あるS S Dは、H D D、C Dドライブ、D V Dドライブといった磁気的不揮発性記憶および／または光学的不揮発性記憶によって使用されるフォームファクタ、電気的インターフェース、および／またはプロトコルと適合する。様々な実施形態では、S S Dは、0以上のパリティ符号、0以上のR S符号、0以上のB C H符号、0以上のビタビ符号または他のトレリス符号、および0以上のL D P C符号の様々な組み合わせを使用する。30

#### 【0032】

##### 例示的実施形態

詳細な説明の概説を終えるにあたり、以下に、例示的実施形態をまとめて示す。これらの例示的実施形態は、少なくとも一部は「E C」（E x a m p l e C o m b i n a t i o n s : E C s）として明示的に列挙されたものを有し、本明細書で説明する概念に従った様々な種類の実施形態の詳細な説明を提供するものである。これらの例は、相互排他的であることも、網羅的であることも、限定的であることも意図されておらず、本発明は、これらの例示的実施形態だけに限定されるものではなく、発行される特許請求の範囲およびその均等物の範囲内のすべての可能な改変形態および変形形態を包含するものである。40

#### 【0033】

##### E C 1 )システムであって、

1若しくはそれ以上のフラッシュメモリの全部または任意の部分を、ホストデータ、システムデータ、システムオーバープロビジョニング（o v e r - p r o v i s i o n i n g : O P）、およびホストオーバープロビジョニングにそれぞれ専用の割り当て領域として動作させる手段と、50

1若しくはそれ以上のイベントに応答して前記割り当て領域のうちの任意の1若しくはそれ以上を動的に決定する手段と

を有するシステム。

【0034】

E C 2 ) E C 1 記載のシステムにおいて、前記イベントは、前記割り当て領域のうちの任意の1若しくはそれ以上の使用量の変化を含むものであるシステム。

【0035】

E C 3 ) E C 1 記載のシステムにおいて、イベントは、フラッシュメモリに記憶された情報の圧縮、重複排除、および変換のうち任意の1若しくはそれ以上の有効性の変更の決定を有するシステム。

10

【0036】

E C 4 ) E C 3 記載のシステムにおいて、前記有効性の変更は、少なくとも部分的に前記それぞれの割り当て領域のうちの特定の1つで使用された特定の空間の量によって測定されるシステム。

【0037】

E C 5 ) E C 3 記載のシステムにおいて、前記有効性の変更は、少なくとも部分的に前記それぞれの割り当て領域のうちの特定の1つで利用可能な特定の空き領域の量によって測定されるシステム。

【0038】

E C 6 ) E C 1 記載のシステムにおいて、前記イベントは、前記ホストデータ割り当て領域に記憶された情報の圧縮および重複排除のうち任意の1若しくはそれ以上の有効性の増加の決定を有するシステム。

20

【0039】

E C 7 ) E C 6 記載のシステムにおいて、前記有効性の増加は、少なくとも部分的に前記ホストデータ割り当て領域に使用される空間の量の低減によって測定されるシステム。

【0040】

E C 8 ) E C 6 記載のシステムにおいて、前記有効性の増加は、少なくとも部分的に前記ホストデータ割り当て領域で利用可能な空き領域の量の増加によって測定されるシステム。

30

【0041】

E C 9 ) E C 6 記載のシステムにおいて、前記動的に決定する手段は、前記有効性の増加の決定に応答して、前記ホストデータ割り当て領域および前記ホストオーバープロビジョニング割り当て領域のうち任意の1若しくはそれ以上を動的に低減させるシステム。

【0042】

E C 10 ) E C 6 記載のシステムにおいて、前記動的に決定する手段は、前記有効性の増加の決定に応答して、前記システムデータ割り当て領域および前記システムオーバープロビジョニング割り当て領域のうち任意の1若しくはそれ以上を動的に増加させるシステム。

【0043】

E C 11 ) E C 1 記載のシステムにおいて、前記動作させる手段および前記動的に決定する手段は、ソリッドステートディスク ( S S D ) のコントローラに含まれ、前記フラッシュメモリは S S D に含まれるものであるシステム。

40

【0044】

E C 12 ) 方法であって、

ソリッドステートディスク ( S S D ) の1若しくはそれ以上のフラッシュメモリを、それぞれホストデータ割り当て領域、システムデータ割り当て領域、および組み合わせオーバープロビジョニング ( O P ) 割り当て領域として動作させる工程と、

前記組み合わせオーバープロビジョニング割り当て領域をシステムオーバープロビジョニング割り当て領域およびホストオーバープロビジョニング割り当て領域のそれぞれとして動作させる工程と、

50

前記システムオーバープロビジョニング割り当て領域の新しい値をシステムデータ転送速度対ホストデータ転送速度の比率の線形関数として動的に決定する工程と、

前記新しい値の変化に応答して前記システムオーバープロビジョニング割り当て領域を動的に変更する工程と

を有し、

前記動的に決定する工程は、イベントに応答するものである方法。

【0045】

E C 1 3 ) E C 1 2 記載の方法において、さらに、

ソリッドステートディスクに接続されたホストからデータを受け取る工程と、

前記ホストから受け取ったデータから情報を特定する工程と、

10

前記ホストデータ割り当て領域に基づいてフラッシュメモリに情報を記憶する工程と

を有するものである方法。

【0046】

E C 1 4 ) E C 1 3 記載の方法において、さらに、

前記ホストから受け取ったデータを圧縮することによって情報を計算する工程を有する

ものである方法。

【0047】

E C 1 5 ) E C 1 3 記載の方法において、さらに、

前記ホストから受け取ったデータを重複排除することによって情報を計算する工程を有する

ものである方法。

20

【0048】

E C 1 6 ) E C 1 2 記載の方法において、さらに、

前記システムデータ割り当て領域に基づいてフラッシュメモリに、ホストアドレス対フ

ラッシュメモリアドレスの対応関係情報を記憶する工程を有するものである方法。

【0049】

E C 1 7 ) E C 1 2 記載の方法において、前記イベントは、少なくとも部分的に再利用

のためにフラッシュメモリのユニットの選択することに基づくものである方法。

【0050】

E C 1 8 ) E C 1 7 記載の方法において、前記再利用は、

30

ガーベジコレクション、

ガーベジコレクションのための選択、

再利用、

再利用のための選択、

消去、および

消去のための選択

のうちの 1 若しくはそれ以上を有する方法。

【0051】

E C 1 9 ) システムであって、

1 若しくはそれ以上のフラッシュメモリを、それぞれホストデータ割り当て領域、シス

テムデータ割り当て領域、および組み合わせオーバープロビジョニング ( O P ) 割り当て

領域として動作させる手段と、

40

前記組み合わせオーバープロビジョニング割り当て領域をシステムオーバープロビジョ

ニング割り当て領域およびホストオーバープロビジョニング割り当て領域のそれぞれとし

て動作させる手段と、

1 若しくはそれ以上のイベントに応答して、前記システムオーバープロビジョニング割

り当て領域の新しい値を動的に決定する手段と

を有するシステム。

【0052】

E C 2 0 ) E C 1 9 記載のシステムにおいて、さらに、

前記新しい値の変化に応答して、前記システムオーバープロビジョニング割り当て領域

50

を動的に変更する手段を有するものであるシステム。

【0053】

EC21) EC19記載のシステムにおいて、前記新しい値を動的に決定する手段は、システムデータ転送速度とホストデータ転送速度との関数に従って新しい値を決定するものであるシステム。

【0054】

EC22) EC21記載のシステムにおいて、前記新しい値を動的に決定する手段は、前記システムデータ転送速度対前記ホストデータ転送速度の比率に従って新しい値を決定するものであるシステム。

【0055】

EC23) EC22記載のシステムにおいて、前記新しい値を動的に決定する手段は新しい値を、前記システムデータ転送速度を前記ホストデータ転送速度で割った値に比例するものとして決定するものであるシステム。

【0056】

EC24) EC21記載のシステムにおいて、前記手段は、ソリッドステートディスク(SSD)のコントローラにより実行されるものであり、前記フラッシュメモリはSSDに含まれるものであるシステム。

【0057】

EC25) EC24記載のシステムにおいて、当該システムは、さらに、

ホストにインターフェースする手段

を有するものであり、前記ホストにインターフェースする手段はSSDに含まれてあり、前記ホストデータ割り当て領域は、少なくとも部分的に前記ホストにインターフェースする手段を介して伝達されたデータの少なくとも一部分を表す情報を記憶するのに使用されるシステム。

【0058】

EC26) EC25記載のシステムにおいて、さらに、

伝達されたデータの少なくとも一部分の圧縮により情報の少なくとも一部分を決定する手段を有するものであるシステム。

【0059】

EC27) EC25記載のシステムにおいて、さらに、

前記伝達されたデータの少なくとも一部分の重複排除により情報の少なくとも一部分を決定する手段を有するものであるシステム。

【0060】

EC28) EC25記載のシステムにおいて、さらに、

前記伝達されたデータの少なくとも一部分のエントロピーを減少させる可逆変換により情報の少なくとも一部分を決定する手段を有するものであるシステム。

【0061】

EC29) EC24記載のシステムにおいて、前記システムデータ割り当て領域は、少なくとも部分的にマップデータの少なくとも一部分を記憶するためにコントローラによって使用されるシステム。

【0062】

EC30) EC24記載のシステムにおいて、前記システムデータ割り当て領域は、少なくとも部分的にチェックポイントデータの少なくとも一部分を記憶するためにコントローラによって使用されるシステム。

【0063】

EC31) EC21記載のシステムにおいて、前記システムデータ転送速度は、少なくとも部分的に、

前記フラッシュメモリに記憶するためにソリッドステートディスク(SSD)コントローラから提供されるシステムデータの転送速度、

前記フラッシュメモリに書き込まれるシステムデータの転送速度、および

10

20

30

40

50

前記フラッシュメモリへのシステムデータ書き込み帯域幅のうちの1若しくはそれ以上に基づくものであるシステム。

【0064】

EC32) EC21記載のシステムにおいて、前記ホストデータ転送速度は、少なくとも部分的に、

前記フラッシュメモリに記憶するためにホストから提供されるデータの転送速度、

前記フラッシュメモリに書き込まれるホストデータの転送速度、および

前記フラッシュメモリへのホストデータ書き込み帯域幅

のうちの1若しくはそれ以上に基づくものであるシステム。

【0065】

10

EC33) EC19記載のシステムにおいて、前記イベントは、

前記フラッシュメモリのユニットの割り当て、

前記フラッシュメモリの1若しくはそれ以上の部分のガーベジコレクション、

前記フラッシュメモリの1若しくはそれ以上の部分の再利用、および

前記フラッシュメモリの1若しくはそれ以上の部分の消去

のうちの1若しくはそれ以上について開始すること、完了すること、要求すること、および/または選択することを含むものであるシステム。

【0066】

20

EC34) EC19記載のシステムにおいて、さらに、

少なくとも部分的にコンピューティングホストからの要求に応答して、前記ホストデータ割り当て領域の少なくとも一部に記憶された情報により表されたホストデータの少なくとも一部分を伝達する手段を有するものであるシステム。

【0067】

EC35) EC34記載のシステムにおいて、さらに、

要求をコンピューティングホストとインターフェースさせる手段を有するものであるシステム。

【0068】

30

EC36) EC35記載のシステムにおいて、前記要求をコンピューティングホストとインターフェースさせる手段は、ストレージインターフェース規格に適合したものであるシステム。

【0069】

EC37) EC36記載のシステムにおいて、前記ストレージインターフェース規格は

、

ユニバーサル・シリアル・バス (Universal Serial Bus: USB)

)インターフェース規格と、

コンパクトフラッシュ (登録商標) (Compact Flash: CF) インターフェース規格と、

マルチメディアカード (MultiMedia Card: MMC) インターフェース規格と、

組み込み型MMC (eMMC) インターフェース規格と、

40

サンダーボルトインターフェース規格と、

UFSインターフェース規格と、

セキュアデジタル (Secure Digital: SD) インターフェース規格と、

メモリ・スティック・インターフェース規格と、

xDピクチャ・カード・インターフェース規格と、

内蔵ドライブエレクトロニクス (Integrated Drive Electronics: IDE) インターフェース規格と、

シリアル・アドバンスト・テクノロジー・アタッチメント (Serial Advanced Technology Attachment: SATA) インターフェース規格と、

50

エクステナナルS A T A ( e S A T A ) インターフェース規格と、

スモール・コンピュータ・システム・インターフェース ( S C S I ) インターフェース規格と、

シリアル接続スモール・コンピュータ・システム・インターフェース ( S A S ) インターフェース規格と、

ファイバー・チャンネル・インターフェース規格と、

イーサネット ( 登録商標 ) インターフェース規格と、

ペリフェラル・コンポーネント・インターフェース ( P e r i p h e r a l C o m p o n e n t I n t e r c o n n e c t e x p r e s s : P C I e ) インターフェース規格と

のうちの 1 若しくはそれ以上のものを有するものであるシステム。

【 0 0 7 0 】

E C 3 8 ) E C 3 4 記載のシステムにおいて、さらに、

コンピューティングホストの全部または任意の部分を有するものであるシステム。

【 0 0 7 1 】

E C 3 9 ) E C 3 8 記載のシステムにおいて、前記計算ホストは、

コンピュータと、

ワークステーションコンピュータと、

サーバコンピュータと、

ストレージサーバと、

ストレージ・アタッチト・ネットワーク ( S t o r a g e A t t a c h e d N e t w o r k : S A N ) と、

ネットワーク・アタッチト・ストレージ ( N e t w o r k A t t a c h e d S t o r a g e : N A S ) デバイスと、

ダイレクト・アタッチト・ストレージ ( D i r e c t A t t a c h e d S t o r a g e : D A S ) デバイスと、

ストレージアプライアンスと、

パーソナルコンピュータ ( P e r s o n a l C o m p u t e r : P C ) と、

ラップトップコンピュータと、

ノートブックコンピュータと、

ネットブックコンピュータと、

タブレットデバイス又はタブレットコンピュータと、

ウルトラブックコンピュータと、

電子書籍端末 ( 電子読み出し機 ) と、

携帯端末 ( P e r s o n a l D i g i t a l A s s i s t a n t : P D A ) と、

ナビゲーションシステムと、

( ハンドヘルド ) グローバル・ポジショニング・システム ( G l o b a l P o s i t i o n i n g S y s t e m : G P S ) デバイスと、

自動車制御システムと、

自動車媒体制御システム及び自動車媒体制御コンピュータと、

プリンタ、コピー機、若しくは F A X 機、又はオールインワンデバイスと、

販売時点情報管理 P O S デバイスと、

金銭登録機と、

メディアプレイヤと、

テレビと、

メディアレコーダと、

デジタル・ビデオ・レコーダ ( D i g i t a l V i d e o R e c o r d e r : D V R ) と、

デジタルカメラと、

セル方式送受話器と、

10

20

30

40

50

コードレス電話の送受話器と、

電子ゲームと

のうちの 1 若しくはそれ以上のものを有するものであるシステム。

## 【0072】

E C 4 0 ) E C 1 9 記載のシステムにおいて、さらに、

フラッシュメモリとインターフェースする手段を有するものであるシステム。

## 【0073】

E C 4 1 ) E C 4 0 記載のシステムにおいて、フラッシュメモリとインターフェースする手段は、フラッシュ・メモリ・インターフェースを有するシステム。

## 【0074】

E C 4 2 ) E C 4 1 記載のシステムにおいて、フラッシュ・メモリ・インターフェースは、

オープンNAND フラッシュインターフェース (ONFI)、

トグルモードインターフェース、

ダブルデータレート (DDR) 同期インターフェース、

DDR2 同期インターフェース、

同期インターフェース、および

非同期インターフェース

のうちの 1 若しくはそれ以上と適合するシステム。

## 【0075】

E C 4 3 ) E C 1 9 記載のシステムにおいて、さらに、

フラッシュメモリのうちの少なくとも 1 つを有するものであるシステム。

## 【0076】

E C 4 4 ) E C 4 3 記載のシステムにおいて、少なくとも 1 つのフラッシュメモリは、

NAND フラッシュ技術記憶セル、および

NOR フラッシュ技術記憶セル

のうちの 1 若しくはそれ以上を有するシステム。

## 【0077】

E C 4 5 ) E C 4 3 記載のシステムにおいて、少なくとも 1 つのフラッシュメモリは、

シングルレベルセル (SLC) フラッシュ技術記憶セル、および

マルチレベルセル (MLC) フラッシュ技術記憶セル

のうちの 1 若しくはそれ以上を有するシステム。

## 【0078】

E C 4 6 ) E C 4 3 記載のシステムにおいて、少なくとも 1 つのフラッシュメモリは、

多結晶シリコン技術ベースの電荷蓄積セル、および

窒化ケイ素技術ベースの電荷蓄積セル

のうちの 1 若しくはそれ以上を有するシステム。

## 【0079】

E C 4 7 ) E C 4 3 記載のシステムにおいて、少なくとも 1 つのフラッシュメモリは、

2 次元技術ベースのフラッシュメモリ技術、および

3 次元技術ベースのフラッシュメモリ技術

のうちの 1 若しくはそれ以上を有するシステム。

## 【0080】

E C 4 8 ) E C 1 9 記載のシステムにおいて、さらに、

コンピューティングホストからの要求をインターフェースする手段であって、要求はフラッシュメモリに記憶された情報に関するものである、インターフェースする手段と、

フラッシュメモリにインターフェースする手段と

を有するものであるシステム。

## 【0081】

E C 4 9 ) E C 4 8 記載のシステムにおいて、手段は单一の集積回路 (IC) において

10

20

30

40

50

集合的に実施されているシステム。

【0082】

E C 5 0 ) E C 4 8 記載のシステムにおいて、手段はソリッドステートディスク ( S S D ) に具備されているシステム。

【0083】

システム

図 1 A は、 N V M 要素 ( フラッシュメモリなど ) によって実施されるような不揮発性記憶を管理するための可変 O P を使用する S S D コントローラを含む S S D ( 1 0 1 ) の実施形態の選択された詳細を図示する。 S S D コントローラは N V M 要素 ( 例えば、フラッシュメモリ ) を介して実装される不揮発性ストレージなどの不揮発性ストレージを管理するためのものである。 S S D コントローラ 1 0 0 は 1 若しくはそれ以上の外部インターフェース 1 1 0 を介してホスト ( 図示せず ) に通信するように結合される。様々な実施形態に従って、外部インターフェース 1 1 0 は、 S A T A インターフェース、 S A S インターフェース、 P I C e インターフェース、ファイバー・チャンネル・インターフェース、イーサネット ( 登録商標 ) インターフェース ( 例えば、 1 0 ギガビットのイーサネット ( 登録商標 ) ) 、上記のインターフェースのうちのいずれかの規格外版、若しくは特注のインターフェース、又はストレージ及び / 又は通信機器及び / 又は計算デバイスを相互接続するために使用されるその他任意の種類のインターフェースのうちの 1 若しくはそれ以上である。例えば、一部の実施形態において、 S S D コントローラ 1 0 0 は S A T A インターフェースと P C I e インターフェースとを含む。

10

【0084】

S S D コントローラ 1 0 0 は、さらに、 1 つ若しくはそれ以上のデバイスインターフェース 1 9 0 を介して、 1 つ若しくはそれ以上のフラッシュデバイス 1 9 2 といった、 1 つ若しくはそれ以上の記憶デバイスを含む N V M 1 9 9 に通信可能に結合されている。様々な実施形態によれば、デバイスインターフェース 1 9 0 は、非同期インターフェース、同期インターフェース、シングルデータレート ( S D R ) インターフェース、ダブルデータレート ( D D R ) インターフェース、 D R A M 互換 D D R 若しくは D D R 2 同期インターフェース、 O N F I 2 . 2 や O N F I 3 . 0 互換インターフェースといった O N F I 互換インターフェース、トグルモード互換フラッシュインターフェース、上記のインターフェースのいずれかの非標準バージョン、カスタムインターフェース、または記憶デバイスに接続するのに使用される任意の他の種類のインターフェースのうちの 1 つ若しくはそれ以上である。

20

【0085】

各フラッシュデバイス 1 9 2 は、一部の実施形態では、 1 つ若しくはそれ以上の個々のフラッシュダイ 1 9 4 を有する。フラッシュデバイス 1 9 2 のうちの特定のフラッシュデバイスの種類に従って、特定のフラッシュデバイス 1 9 2 内の複数のフラッシュダイ 1 9 4 に、並列に、任意選択で、かつ / または選択的にアクセスすることができる。フラッシュデバイス 1 9 2 は、単に、 S S D コントローラ 1 0 0 に通信可能に結合することができるようとした記憶デバイスの一種を表しているにすぎない。様々な実施形態では、 S L C N A N D フラッシュメモリ、 M L C N A N D フラッシュメモリ、 N O R フラッシュメモリ、多結晶シリコン若しくはシリコン窒化膜技術ベースの電荷蓄積セルを使用したフラッシュメモリ、 2 次元若しくは 3 次元技術ベースのフラッシュメモリ、読み出し専用メモリ、スタティック・ランダム・アクセス・メモリ、ダイナミック・ランダム・アクセス・メモリ、強磁性メモリ、相変化メモリ、レーストラックメモリ、 R e R A M 、または任意の他の種類のメモリデバイス若しくは記憶媒体といった、任意の種類の記憶デバイスを使用することができる。

30

【0086】

様々な実施形態によれば、デバイスインターフェース 1 9 0 は、 1 つのバスにつき 1 つ若しくはそれ以上のフラッシュデバイス 1 9 2 を有する 1 つ若しくはそれ以上のバス ; グループ内のバスにおおむね並列にアクセスさせる、 1 つのバスにつき 1 つ若しくはそれ以

40

50

上のフラッシュデバイス 192 を有する 1 つ若しくはそれ以上のバスグループ；またはデバイスインターフェース 190 上へのフラッシュデバイス 192 の 1 つ若しくはそれ以上のインスタンスの任意の他の編成として編成される。

#### 【 0087 】

引き続き図 1A において、SSDコントローラ 100 は、ホストインターフェース 111、データ処理 121、バッファ 131、マップ 141、リサイクラ 151、ECC 161、デバイスインターフェース論理 191、CPU 171 といった 1 つ若しくはそれ以上のモジュールを有する。図 1A に図示する具体的なモジュールおよび相互接続は、単に、一実施形態を表すにすぎず、これらのモジュールの一部または全部、および図示されていないさらに別のモジュールの多くの配置および相互接続が考えられる。第 1 の例として、一部の実施形態では、デュアルポーティングを提供するための 2 つ以上のホストインターフェース 111 がある。第 2 の例として、一部の実施形態では、データ処理 121 および / または ECC 161 がバッファ 131 と組み合わされている。第 3 の例として、一部の実施形態では、ホストインターフェース 111 がバッファ 131 に直接結合されており、データ処理 121 が、バッファ 131 に記憶されたデータに任意選択で、かつ / または選択的に作用する。第 4 の例として、一部の実施形態では、デバイスインターフェース論理 191 がバッファ 131 に直接結合されており、ECC 161 が、バッファ 131 に記憶されたデータに任意選択で、かつ / または選択的に作用する。

#### 【 0088 】

ホストインターフェース 111 は、外部インターフェース 110 を介してコマンドおよび / またはデータを送受信し、一部の実施形態では、タグ追跡 113 によって個々のコマンドの進捗を追跡する。例えば、コマンドは、読み出すべきアドレス (LBA など) およびデータの量 (LBA 量、例えばセクタの数など) を指定する読み出しコマンドを含み、これに応答して SSD は、読み出し状況および / または読み出しデータを提供する。別の例として、コマンドは、書き込むべきアドレス (LBA など) およびデータの量 (LBA 量、例えばセクタの数など) を指定する書き込みコマンドを含み、これに応答して SSD は、書き込み状況を提供し、かつ / または書き込みデータを要求し、任意選択でその後に書き込み状況を提供する。さらに別の例として、コマンドは、もはや割り当てられる必要ななくなった 1 つ若しくはそれ以上のアドレス (1 つ若しくはそれ以上の LBA など) を指定する割り当て解除コマンド (trim コマンドなど) を含み、これに応答して SSD は、マップをしかるべき変更し、任意選択で割り当て解除状況を提供する。あるコンテキストでは、ATA 互換 TRIM コマンドが割り当て解除コマンドの例である。さらに別の例として、コマンドは、超コンデンサ・テスト・コマンドまたはデータハーデニング成功問い合わせを含み、これに応答して SSD は、適切な状況を提供する。一部の実施形態では、ホストインターフェース 111 は、SATA プロトコルと適合し、NCQ コマンドを使用して、最高 32 までの未処理のコマンドを有することができるようになっており、各コマンドは 0 から 31 までの数として表された一意のタグを有する。一部の実施形態では、タグ追跡 113 は、外部インターフェース 110 を介して受け取ったコマンドのための外部タグを、SSD コントローラ 100 による処理の間にコマンドを追跡するのに使用される内部タグと関連付けることができるようになっている。

#### 【 0089 】

様々な実施形態によれば、データ処理 121 は、任意選択で、かつ / または選択的に、バッファ 131 と外部インターフェース 110 との間で送られる一部または全部のデータを処理する、およびデータ処理 121 は、任意選択で、かつ / または選択的に、バッファ 131 に記憶されたデータを処理する、以下のうちの 1 つ若しくはそれ以上が行われる。一部の実施形態では、データ処理 121 は、1 つ若しくはそれ以上のエンジン 123 を使用して、書式設定、書式設定の変更、符号変換、ならびに他のデータ処理および / または操作タスクのうちの 1 つ若しくはそれ以上を行う。

#### 【 0090 】

バッファ 131 は、外部インターフェース 110 からデバイスインターフェース 190

10

20

30

40

50

ヘ / デバイスインターフェース 190 から外部インターフェース 110 へ送られたデータを記憶する。一部の実施形態では、バッファ 131 は、さらに、SSD コントローラ 100 によって 1つ若しくはそれ以上のフラッシュデバイス 192 を管理するのに使用される、一部または全部のマップ表といったシステムデータも記憶する。様々な実施形態では、バッファ 131 は、データの一時記憶に使用されるメモリ 137、バッファ 131 への、かつ / またはバッファ 131 からのデータの移動を制御するのに使用される DMA 133、ならびに高レベル誤り訂正および / または冗長性機能と、他のデータ移動および / または操作機能とを提供するのに使用される ECC-X 135 のうちの 1つ若しくはそれ以上を有する。高レベル冗長性機能の一例が RAID 様の能力であり、ディスクレベルではなく、フラッシュ・デバイス（フラッシュデバイス 192 のうちの複数のものなど）レベルおよび / またはフラッシュダイ（フラッシュダイ 194 など）レベルの冗長性を備える。10

#### 【0091】

様々な実施形態によれば、以下のうちの 1つ若しくはそれ以上である。ECC 161 は、任意選択で、かつ / または選択的に、バッファ 131 とデバイスインターフェース 190 との間で送られる一部または全部のデータを処理する；および ECC 161 は、任意選択で、かつ / または選択的に、バッファ 131 に記憶されたデータを処理する。一部の実施形態では、ECC 161 は、例えば 1つ若しくはそれ以上の ECC 技法に従った低レベル誤り訂正および / または冗長性機能を提供するのに使用される。一部の実施形態では、ECC 161 は、CRC 符号、ハミング符号、RS 符号、BCH 符号、LDP C 符号、ビタビ符号、トレリス符号、硬判定符号、軟判定符号、消去ベースの符号、任意の誤り検出および / または訂正符号、ならびに上記の任意の組み合わせのうちの 1つ若しくはそれ以上を実施する。一部の実施形態では、ECC 161 は、1つ若しくはそれ以上の復号器（LDP C 復号器など）を含む。20

#### 【0092】

デバイスインターフェース論理 191 は、デバイスインターフェース 190 を介してフラッシュデバイス 192 のインスタンスを制御する。デバイスインターフェース論理 191 は、フラッシュデバイス 192 のプロトコルに従ってフラッシュデバイス 192 のインスタンスへ / からデータを送ることができるようになっている。デバイスインターフェース論理 191 は、デバイスインターフェース 190 を介したフラッシュデバイス 192 のインスタンスの制御を選択的に配列するスケジューリング 193 を含む。例えば、一部の実施形態では、スケジューリング 193 は、フラッシュデバイス 192 のインスタンスへの操作を待ち行列に入れ、フラッシュデバイス 192（またはフラッシュダイ 194）のインスタンスの個々のインスタンスへの操作を、フラッシュデバイス 192（またはフラッシュダイ 194）のインスタンスの個々のインスタンスが利用可能になるに従って選択的に送ることができるようになっている。30

#### 【0093】

マップ 141 は、外部インターフェース 110 上で使用されるデータアドレス指定と、デバイスインターフェース 190 上で使用されるデータアドレス指定との間の変換を行い、表 143 を使用して外部データアドレスから NVM 199 内の位置へマップする。例えば、一部の実施形態では、マップ 141 は、外部インターフェース 110 上で使用される LBA を、表 143 によって提供されるマッピングにより、1つ若しくはそれ以上のフラッシュダイ 194 を対象とするロックおよび / またはページアドレスに変換する。ドライブ製造または割り当て解除以来一度も書き込まれていない LBA では、マップは、LBA が読み取出された場合に返すべきデフォルト値を指示する。例えば、割り当て解除コマンドを処理するときに、マップは、割り当て解除された LBA に対応するエントリがデフォルト値のうちの 1つを指示するように変更される。様々な実施形態では、様々なデフォルト値があり、各々が対応するポインタを有する。複数のデフォルト値は、ある（例えば第 1 の範囲内の）割り当て解除された LBA を 1つのデフォルト値として読み出し、ある（例えば第 2 の範囲内の）割り当て解除された LBA を別のデフォルト値として読み出すことを可能にする。デフォルト値は、様々な実施形態では、フラッシュメモリ、ハードウ40

エア、ファームウェア、コマンドおよび／若しくはプリミティブ引数および／若しくはパラメータ、プログラマブルレジスタ、またはそれらの様々な組み合わせによって定義される。

#### 【0094】

一部の実施形態では、マップ141は、表143を使用して、外部インターフェース110上で使用されるアドレスと、デバイスインターフェース190上で使用されるデータアドレス指定との間の変換を行い、かつ／またはルックアップする。様々な実施形態によれば、表143は、1レベルマップ、2レベルマップ、マルチレベルマップ、マップキャッシュ、圧縮マップ、あるアドレス空間から別のアドレス空間への任意の種類のマッピング、および上記の任意の組み合わせのうちの1つ若しくはそれ以上である。様々な実施形態によれば、表143は、スタティック・ランダム・アクセス・メモリ、ダイナミック・ランダム・アクセス・メモリ、NVM（フラッシュメモリなど）、キャッシュメモリ、オンチップメモリ、オフチップメモリ、および上記の任意の組み合わせのうちの1つ若しくはそれ以上を含む。10

#### 【0095】

一部の実施形態では、リサイクラ151は、ガーベジコレクションを行う。例えば、一部の実施形態では、フラッシュデバイス192のインスタンスは、ロックが書き換え可能になる前に消去されなければならないロックを含む。リサイクラ151は、例えば、マップ141によって維持されるマップをスキャンすることによって、フラッシュデバイス192のインスタンスのどの部分が実際に使用されているか（例えば、割り当て解除されているのではなく割り当てられていること）を決定し、フラッシュデバイス192のインスタンスの未使用の（例えば割り当て解除された）部分を消去することによって書き込みに利用できるようになることができるようになっている。別の実施形態では、リサイクラ151は、フラッシュデバイス192のインスタンスのより大きい連続した部分を書き込みに利用できるようにするために、フラッシュデバイス192のインスタンス内に記憶されたデータを移動することができるようになっている。20

#### 【0096】

一部の実施形態では、フラッシュデバイス192のインスタンスは、異なる種類および／または属性のデータを記憶するための1つ若しくはそれ以上のバンドを保持するよう、選択的に、かつ／または動的に構成され、管理され、かつ／または使用される。バンドの数、配置、サイズ、および種類は、動的に変更可能である。例えば、コンピューティングホストからのデータはホット（アクティブな）バンドに書き込まれ、リサイクラ151からのデータはコールド（あまりアクティブではない）バンドに書き込まれる。ある使用シナリオでは、コンピューティングホストが長い順次のストリームを書き込む場合には、ホットバンドのサイズが増加し、コンピューティングホストがランダムな書き込みを行い、またはわずかな書き込みしか行わない場合には、コールドバンドのサイズが増加する。30

#### 【0097】

CPU171は、SSDコントローラ100の様々な部分を制御する。CPU171は、CPUコア172を含む。CPUコア172は、様々な実施形態によれば、1つ若しくはそれ以上のシングルコアプロセッサまたはマルチコアプロセッサである。CPUコア172内の個々のプロセッサコアは、一部の実施形態では、マルチスレッド化されている。CPUコア172は、命令および／またはデータのキャッシュおよび／またはメモリを含む。例えば、命令メモリは、CPUコア172が、SSDコントローラ100を制御するためのプログラム（ファームウェアとも呼ばれるソフトウェアなど）を実行することを可能にする命令を含む。一部の実施形態では、CPUコア172によって実行されるファームウェアの一部または全部が、（例えば、図1BのNVM199のファームウェア106として図示されている）フラッシュデバイス192のインスタンス上に記憶される。40

#### 【0098】

様々な実施形態では、CPU171は、外部インターフェース110を介して受け取られるコマンドを、コマンドが進行している間に追跡し、制御するコマンド管理173、バ50

ツファ 131 の割り当ておよび使用を制御するバッファ管理 175、マップ 141 を制御する変換管理 177、データアドレス指定の整合性を制御し、例えば、外部データアクセスと再利用データアクセスとの間の矛盾を回避するコヒーレンシ管理 179、デバイスインターフェース論理 191 を制御するデバイス管理 181、識別情報の変更および通信を制御する識別情報管理 182、ならびに、任意選択で、他の管理部をさらに含む。CPU 171 によって果たされる管理機能は、そのいずれか、若しくは全部が、ハードウェア、ソフトウェア (CPU コア 172 上や、外部インターフェース 110 を介して接続されたホスト上で実行されるファームウェアなど)、またはそれらの任意の実施形態によって制御され、かつ / または管理され、あるいは、そのどれも、制御も管理もされないものである。

10

#### 【0099】

一部の実施形態では、CPU 171 は、性能統計の収集および / または報告、SMART の実施、電源逐次開閉機構の制御、電力消費の制御および / または調整、電源障害への応答、クロック速度の制御および / またはモニタリングおよび / または調整、ならびに他の管理タスクのうちの 1 つ若しくはそれ以上といった、他の管理タスクを行うことができるようになっている。

#### 【0100】

様々な実施形態は、SSD コントローラ 100 と同様の、例えば、ホストインターフェース 111 および / または外部インターフェース 110 の適応による、様々なコンピューティングホストを用いた動作と適合するコンピューティングホスト・フラッシュ・メモリ・コントローラを含む。様々なコンピューティングホストは、コンピュータ、ワークステーションコンピュータ、サーバコンピュータ、ストレージサーバ、SAN、NAS デバイス、DAS デバイス、ストレージアプライアンス、PC、ラップトップコンピュータ、ノートブックコンピュータ、ネットブックコンピュータ、タブレット機器またはタブレットコンピュータ、ウルトラブックコンピュータ、電子読み出し装置 (e-reader など)、PDA、ナビゲーションシステム、(ハンドヘルド型) GPS 機器、自動通信路制御システム、自動車媒体制御システムまたはコンピュータ、プリンタ、コピー機またはファックス機またはオールインワン機器、POS 機器、金銭登録機、メディアプレーヤ、テレビ、メディアレコーダ、DVR、デジタルカメラ、セルラハンドセット、コードレス電話機ハンドセット、および電子ゲームのうちの 1 つまたはそれらの任意の組み合わせを含む。

20

#### 【0101】

様々な実施形態では、SSD コントローラ (またはコンピューティングホスト・フラッシュ・メモリ・コントローラ) の全部または任意の部分が、単一の I C、マルチダイ I C の単一のダイ、マルチダイ I C の複数のダイ、または複数の I C 上で実施される。例えば、バッファ 131 は、SSD コントローラ 100 の他の要素と同じダイ上に実施される。別の例では、バッファ 131 は、SSD コントローラ 100 の他の要素と異なるダイ上に実施される。

30

#### 【0102】

図 1B に、図 1A の SSD の 1 つ若しくはそれ以上のインスタンスを含むシステムの様々な実施形態の選択された詳細を図示する。SSD 101 は、デバイスインターフェース 190 を介して NVMe 199 に結合された SSD コントローラ 100 を含む。図には、様々な種別の実施形態、すなわち、ホストに直接結合された単一の SSD、各々がそれぞれの外部インターフェースを介してホストに直接それぞれ結合されている複数の SSD、および様々な相互接続要素を介してホストに間接的に結合された 1 つ若しくはそれ以上の SSD が示されている。

40

#### 【0103】

ホストに直接結合された単一の SSD の例示的実施形態としては、SSD 101 の 1 つのインスタンスが、外部インターフェース 110 を介してホスト 102 に直接結合される (例えば、スイッチ / ファブリック / 中間コントローラ 103 が省かれ、バイパスされ、

50

またはパススルーされる）。各々がそれぞれの外部インターフェースを介してホストに直接結合されている複数のSSDの例示的実施形態としては、SSD101の複数のインスタンスの各々が、外部インターフェース110のそれぞれのインスタンスを介してホスト102に直接それぞれ結合される（例えば、スイッチ／ファブリック／中間コントローラ103が省かれ、バイパスされ、またはパススルーされる）。様々な相互接続要素を介してホストに間接的に結合された1つ若しくはそれ以上のSSDの例示的実施形態としては、SSD101の1つ若しくはそれ以上のインスタンスの各々が、ホスト102に間接的にそれぞれ結合される。各間接結合は、スイッチ／ファブリック／中間コントローラ103に結合された外部インターフェース110のそれぞれのインスタンス、およびホスト102に結合する中間インターフェース104を介したものである。

10

#### 【0104】

スイッチ／ファブリック／中間コントローラ103を含む実施形態の一部は、メモリインターフェース180を介して結合された、SSDによってアクセス可能なカードメモリ112Cも含む。様々な実施形態では、SSD、スイッチ／ファブリック／中間コントローラ、および／またはカードメモリのうちの1つ若しくはそれ以上が、物理的に識別可能なモジュール、カード、または差し込み可能な要素（入出力カード116など）上に含まれる。一部の実施形態では、SSD101（またはその変形）は、ホスト102として動作するイニシエータ（開始プログラム）に結合されたSASドライブまたはSATAドライブに対応する。

#### 【0105】

ホスト102は、OS105、ドライバ107、アプリケーション109、マルチデバイス管理ソフトウェア114の様々な組み合わせといった、ホストソフトウェア115の様々な要素を実行することができるようになっている。点線矢印107Dは、ホストソフトウェア 入出力装置通信、例えば、SSD101のインスタンスのうちの1つ若しくはそれ以上から／へ、ドライバ107を介したOS105、ドライバ107、および、ドライバ107を介して、またはVFとして直接アプリケーション109のうちの任意の1つ若しくはそれ以上へ／から送られ／受け取られるデータを表す。

20

#### 【0106】

OS105は、SSDとインターフェースするための（概念的にはドライバ107によって図示されている）ドライバを含み、かつ／またはそのようなドライバを用いて動作することができるようになっている。Windows（登録商標）の様々なバージョン（95、98、ME、NT、XP、2000、サーバ、Vista、および7など）、Linux（登録商標）の様々なバージョン（Red Hat、Debian、およびUbuntuなど）、ならびにMac OSの様々なバージョン（8、9およびXなど）がOS105の例である。様々な実施形態では、ドライバは、SATA、AHCI、NVM Expressといった標準のインターフェースおよび／またはプロトコルを用いて動作する標準のドライバおよび／または汎用のドライバ（「シュリンクラップされた（市販の）」または「プリインストールされた」ともいう）であり、あるいは、任意選択で、SSD101に特有のコマンドの使用を可能にするようにカスタマイズされており、かつ／またはベンダ特有のものである。あるドライブおよび／またはドライバは、アプリケーションレベルのプログラム、例えば最適化NANDアクセス（Optimized NAND Access）（ONAともいう）または直接NANDアクセス（Direct NAND Access）（DNAともいう）の各技法によるアプリケーション109などが、コマンドをSSD101に直接伝えることを可能にするパススルーモードを有し、カスタマイズされたアプリケーションが、汎用ドライバとでさえもSSD101に特有のコマンドを使用することを可能にする。ONAの技法は、非標準変更子（hints）の使用、ベンダ特有のコマンドの使用、非標準の統計の通信、例えば圧縮可能性に従った実際のNVMの使用、および他の技法のうちの1つ若しくはそれ以上を含む。DNAの技法は、NVMへのマップされていない読み出し、書き込み、および／または消去アクセスを提供する非標準のコマンドまたはベンダ特有の（コマンド）の使用、例えば、入出力装置が通常は行

30

40

50

うはずのデータの書式設定をバイパスすることによる、NVMへのより直接的なアクセスを提供する非標準の、またはベンダ特有のコマンドの使用、および他の技法のうちの1つ若しくはそれ以上を含む。ドライバの例は、ONAまたはDNAサポートなしのドライバ、ONA使用可能ドライバ、DNA使用可能ドライバ、ONA/DNA使用可能ドライバである。ドライバの別の例は、ベンダ提供ドライバ、ベンダ開発ドライバ、および/またはベンダ拡張ドライバ、ならびにクライアント提供ドライバ、クライアント開発ドライバ、および/またはクライアント拡張ドライバである。

#### 【0107】

アプリケーションレベルのプログラムの例は、ONAまたはDNAサポートなしのアプリケーション、ONA使用可能アプリケーション、DNA使用可能アプリケーション、およびONA/DNA使用可能アプリケーションである。点線矢印109Dは、アプリケーション 入出力装置通信（ドライバによるバイパスや、アプリケーションのためのVFによるバイパスなど）、例えば、OSを仲介として使用するアプリケーションなしでSSDと通信するONA使用可能アプリケーションおよびONA使用可能ドライバなどを表す。点線矢印109Vは、アプリケーション 入出力装置通信（アプリケーションのためのVFによるバイパスなど）、例えば、OSまたはドライバを仲介として使用するアプリケーションなしでSSDと通信するDNA使用可能アプリケーションおよびDNA使用可能ドライバなどを表す。

#### 【0108】

NVM199の1つ若しくはそれ以上の部分が、一部の実施形態では、ファームウェア記憶、例えばファームウェア106に使用される。ファームウェア記憶は、1つ若しくはそれ以上のファームウェアイメージ（またはその部分）を含む。ファームウェアイメージは、例えばSSDコントローラ100のCPUコア172によって実行される、例えばファームウェアの1つ若しくはそれ以上のイメージを有する。ファームウェアイメージは、別の例では、例えばファームウェア実行時にCPUコアによって参照される、定数、パラメータ値、NVMデバイス情報の1つ若しくはそれ以上のイメージを有する。ファームウェアのイメージは、例えば、現在のファームウェアイメージおよび0以上の（ファームウェア更新に対して）前のファームウェアイメージに対応する。様々な実施形態では、ファームウェアは、汎用動作モード、標準動作モード、ONA動作モード、および/またはDNA動作モードを提供する。一部の実施形態では、ファームウェア動作モードのうちの1つ若しくはそれ以上が、ドライバによって任意選択で伝えられ、かつ/または提供される、鍵または様々なソフトウェア技法によって使用可能とされる（例えば、1つ若しくはそれ以上のAPIが「ロック解除」される）。

#### 【0109】

スイッチ/ファブリック/中間コントローラを欠く一部の実施形態では、SSDは、外部インターフェース110を介して直接ホストに結合される。様々な実施形態では、SSDコントローラ100は、RAIDコントローラといった他のコントローラの1つ若しくはそれ以上の中間レベルを介してホストに結合される。一部の実施形態では、SSD101（またはその変形）は、SASドライブまたはSATADライブに対応し、スイッチ/ファブリック/中間コントローラ103は、イニシエータにさらに結合されたエキスパンダに対応し、あるいは、スイッチ/ファブリック/中間コントローラ103は、エキスパンダを介してイニシエータに間接的に結合されたブリッジに対応する。一部の実施形態では、スイッチ/ファブリック/中間コントローラ103は、1つ若しくはそれ以上のPCIeスイッチおよび/またはファブリックを含む。

#### 【0110】

様々な実施形態、例えば、コンピューティングホストとしてのホスト102（コンピュータ、ワークステーションコンピュータ、サーバコンピュータ、ストレージサーバ、SAN、NASデバイス、DASデバイス、ストレージアプライアンス、PC、ラップトップコンピュータ、ノートブックコンピュータ、および/またはネットブックコンピュータなど）を有する実施形態のあるものでは、コンピューティングホストは、任意選択で、1つ

10

20

30

40

50

若しくはそれ以上のローカルサーバおよび／またはリモートサーバ（例えば、任意選択のサーバ118）と（例えば、任意選択の入出力装置／リソースおよび記憶装置／リソース117および任意選択のLAN／WAN119を介して）通信することができるようになっている。通信は、例えば、SSD101要素のうちの任意の1つ若しくはそれ以上のローカルおよび／またはリモートのアクセス、管理、および／または使用を可能にする。一部の実施形態では、通信は、全部または一部がイーサネット（登録商標）（Ethernet（登録商標））によるものである。一部の実施形態では、通信は、全部または一部がファイバチャネルによるものである。LAN／WAN119は、様々な実施形態では、1つ若しくはそれ以上のローカル・エリア・ネットワークおよび／または広域ネットワーク、例えば、サーバファーム内のネットワーク、サーバファームを結合するネットワーク、メトロエリアネットワーク、およびインターネットのうちの任意の1つ若しくはそれ以上を表す。10

#### 【0111】

様々な実施形態では、1つ若しくはそれ以上のNVMと組み合わされたSSDコントローラおよび／またはコンピューティングホスト・フラッシュ・メモリ・コントローラが、USB記憶コンポーネント、CF記憶コンポーネント、MMC記憶コンポーネント、eMMC記憶コンポーネント、サンダーボルト記憶コンポーネント、UFS記憶コンポーネント、SD記憶コンポーネント、メモリスティック記憶コンポーネント、xDピクチャカード記憶コンポーネントといった不揮発性記憶コンポーネントとして実施される。20

#### 【0112】

様々な実施形態では、SSDコントローラ（またはコンピューティングホスト・フラッシュ・メモリ・コントローラ）の全部またはいずれかの部分、またはその機能が、コントローラが結合されるべきホスト（図1Bのホスト102など）において実施される。様々な実施形態では、SSDコントローラ（若しくはコンピューティングホスト・フラッシュ・メモリ・コントローラ）の全部またはいずれかの部分、またはその機能が、ハードウェア（論理回路など）、ソフトウェアおよび／若しくはファームウェア（ドライバソフトウェア若しくはSSD制御ファームウェアなど）、またはそれらの任意の組み合わせによって実施される。例えば、（例えば図1AのECC161および／またはECC-X135と同様の）ECC部の、またはECC部と関連付けられた機能が、一部はホスト上のソフトウェアによって、一部はSSDコントローラ内のファームウェアとハードウェアとの組み合わせによって実施される。別の例として、（例えば図1Aのリサイクラ151と同様の）リサイクラ部の、またはリサイクラ部と関連付けられた機能が、一部はホスト上のソフトウェアによって、一部はコンピューティングホスト・フラッシュ・メモリ・コントローラ内のハードウェアによって実施される。30

#### 【0113】

##### 可変オーバープロビジョニング（OP）

図2に、NVMを管理するために可変OPを使用するシステムの様々な実施形態による、OP用途のためのものを含む、フラッシュメモリ200の様々なホスト割り当て領域およびシステム割り当て領域の選択された詳細を示す。ホスト割り当て領域は、不揮発性記憶にフラッシュメモリを使用するSSDに結合されたホストから受け取られる／に提供されるデータといったホストデータを記憶するのに使用される。システム割り当て領域（システム割り当て領域201など）は、SSDコントローラ（図1Aのマップ141内の情報の全部または部分の周期的コピーなど）、SSD、フラッシュメモリ、またはこれらの任意の部分の管理または操作に関連するものといった、システムデータを記憶するのに使用される。40

#### 【0114】

図には、3つの割り当てのシナリオ（それぞれ、初期割り当て210A、同一割り当て210B、および増加割り当て210C）に従って使用されたフラッシュメモリ200が図示されている。割り当てのシナリオの各々には、最高の詳細レベルで、割り当ての3要素、すなわち、ホスト、システム、およびOPが図示されている。初期割り当て210A50

および同一割り当て 210B では、ホスト割り当て領域、システム割り当て領域、および OP 割り当て領域は、それぞれ、ホスト割り当て領域 202A、システム割り当て領域 201、および OP (システム + ホスト) 割り当て領域 203A として図示されている。増加割り当て 210C では、ホスト割り当て領域、システム割り当て領域、および OP 割り当て領域は、それぞれ、ホスト割り当て領域 202C、システム割り当て領域 201、および OP (システム + ホスト) 割り当て領域 203C として図示されている。別の詳細レベルでは、様々な割り当ては、ホスト OP 割り当て領域とシステム OP 割り当て領域との間での割り当てに従って異なり、これを、ホスト OP 割り当て領域 205A および 205B、ならびにシステム OP 割り当て領域 204A、204B、および 204C として図示し、以下で説明する。

10

#### 【0115】

動作に際して、割り当ては、開始状態（初期割り当て 210A など）に従って開始する。イベントに応答して、エージェントは割り当てを異なる状態（同一割り当て 210B や増加割り当て 210C など）に変更する。様々な実施形態は様々な動作モードによるものである。第1の動作モードでは、ホスト割り当て領域は不变のままであり、OP (システム + ホスト) 割り当て領域は不变のままであるが、システム OP 割り当て領域とホスト OP 割り当て領域との間で再分配される。第2の動作モードでは、ホスト割り当て領域は変更され、対応する OP (システム + ホスト) 割り当て領域の変更が可能となり、当該割り当て領域はシステム OP 割り当て領域とホスト OP 割り当て領域との間で再分配される。

20

#### 【0116】

第1の動作モードでは、割り当てが初期割り当て 210A に従って開始した後で、割り当ては次いで、同一割り当て 210B に動的に変更される。最高の詳細レベルでは、割り当ての3要素は不变のままである。具体的には、ホスト割り当て領域、システム割り当て領域、および OP 割り当て領域は、それぞれ、ホスト割り当て領域 202A、システム割り当て領域 201、および OP (システム + ホスト) 割り当て領域 203A で不变のままである。しかし、別の詳細レベルでは、OP 割り当て領域は、内部で、ホスト OP 割り当て領域を所定量だけ減らし、システム OP 割り当て領域を当該所定量だけ増やすことによって変更される。具体的には、ホスト OP 割り当て領域はホスト OP 割り当て領域 205A からホスト OP 割り当て領域 205B へシステム OP 割り当て領域 デルタ 208 の量だけ減少し、システム OP 割り当て領域はシステム OP 割り当て領域 204A からシステム OP 割り当て領域 204B へシステム OP 割り当て領域 デルタ 208 の量だけ増加する。

30

#### 【0117】

さらなる動作の後で、割り当ては次いで初期割り当て 210A に戻るように動的に変更され、これは、ホスト OP 割り当て領域をホスト OP 割り当て領域 205A とし、システム OP 割り当て領域をシステム OP 割り当て領域 204A とすることを含む。第1の動作モードに適用可能な他の動作シナリオには、図に示す特定の割り当てのいずれにも制約されることなく、（ホスト割り当て領域およびシステム割り当て領域は不变のままで）ホスト OP 用途とシステム OP 用途との間での OP 割り当て領域の任意の割り当て変更が含まれる。

40

#### 【0118】

第2の動作モードでは、割り当てが初期割り当て 210A に従って開始した後で、割り当ては次いで、増加割り当て 210C に動的に変更される。最高の詳細レベルでは、割り当ての3要素は、ホスト割り当て領域が所定の量だけ減らされ、OP 割り当て領域が当該所定の量だけ増やされるように変更される。別の詳細レベルでは、ホスト OP 割り当て領域は不变のままであり、システム OP 割り当て領域は当該量だけ増加する。具体的には、ホスト割り当て領域はホスト割り当て領域 202A からホスト割り当て領域 202C へシステム OP 割り当て領域 デルタ 209 の量だけ減少し、OP 割り当て領域は OP 割り当て領域 203A から OP 割り当て領域 203C へシステム OP 割り当て領域 デルタ 209 の量だけ増加する。別の詳細レベルでは、ホスト OP 割り当て領域はホスト OP 割り当て領域 205A で不变のままであり、システム OP 割り当て領域は、システム OP 割り当て領域

50

域 204A からシステム OP 割り当て領域 204C へシステム OP 割り当て領域 デルタ 209 の量だけ増加する。

【0119】

さらなる動作の後で、割り当ては次いで初期割り当て 210A に戻るように動的に変更され、これは、ホスト OP 割り当て領域をホスト OP 割り当て領域 205A とし、システム OP 割り当て領域をシステム OP 割り当て領域 204A とすることを含む。第 2 の動作モードに適用可能な他の動作シナリオには、図に示す特定の割り当てのいずれにも制約されることなく、（ホスト割り当て領域を増やす / 減らすことと併せて）ホスト OP 用途とシステム OP 用途との間での OP 割り当て領域の任意の割り当ての変更が含まれる。

【0120】

第 3 の動作モード（図示せず）では、（第 2 の動作モードの場合と同様に）OP 割り当て領域の変化に適応するようにホスト割り当て領域を変更する代わりに（かつ / またはこれに加えて）、システム割り当て領域が変更される。よって、システム割り当て領域の増 / 減はシステム OP 割り当て領域の増 / 減を可能にし、あるいは、システム割り当て領域の増 / 減と組み合わせたホスト割り当て領域の増 / 減は、ホスト OP 割り当て領域および / またはシステム OP 割り当て領域の増 / 減を可能にする。第 1 の動作モードから第 3 の動作モードの任意の組み合わせである他の動作モードも企図されており、これには、様々な動作基準および / または特性に従って、第 1 の動作モードから第 3 の動作モードのいずれかに動的に切り換わる動作モードが含まれる。

【0121】

割り当て状態変更につながるいくつかのイベントおよび割り当て状態変更を実施する対応するエージェントがある。例えば、SSD コントローラ（図 1A の SSD コントローラ 100 など）は、圧縮、重複排除、または変換の変更による使用量の増加（または減少）などに起因して、ホストデータを記憶するのに增量させた（または減量させた）フラッシュメモリ（図 1A の NVMe 199 など）が使用されるべきであると決定する。これに応答して、SSD コントローラは、（例えば、図 2 のシステム OP 割り当て領域 204A からシステム OP 割り当て領域 204C へ）システム OP 割り当て領域を増加する（または減少させる）。別の例では、フラッシュメモリベースの記憶サブシステム（図 1B の SSD 101 など）内のプロセッサ（図 1A の CPU 171 など）は、記憶サブシステムの記憶インターフェース（図 1B の外部インターフェース 110 など）を介してコマンドを受け取る。コマンド（ATA 互換 TRIM コマンドなど）は、記憶サブシステムの特定の部分が未使用状態（空状態など）であり、そこに記憶された任意のデータがもはや不要であることを指定する。これに応答して、プロセッサは、ホストデータおよび / またはホスト OP へのフラッシュメモリの割り当て領域を減らし、システム OP へのフラッシュメモリの割り当て領域を増やす。様々な実施形態において、ホストデータおよび / またはホスト OP への割り当て領域の減少（ならびに任意選択でかつ / 若しくは選択的にシステム OP への割り当て領域の増加）は、未使用部分が整理され、再利用され、かつ / または消去されるまで延期される。

【0122】

さらに別の例では、SSD コントローラ内のモニタリングサブシステム（図 1A のスケジューリング 193 の全部または任意の部分など）は、システム書き込み対ホスト書き込みの帯域幅の現在の比率が前の比率に変化したと決定する。これに応答して、モニタリングサブシステムは、SSD コントローラの割り当てエージェント（図 1A のリサイクル 151 の全部または任意の部分など）が現在の比率に従ってシステム OP とホスト OP との間で割り当てを変更するよう要求する。例えば、現在の比率が増加（減少）した場合には、割り当てエージェントは、システム OP を増やす（減らす）よう、かつ / またはホスト OP を減らす（増やす）ように要求される。様々な実施形態において、増加（減少）は、現在の比率の線形関数、現在の比率と前の比率との比率の線形関数、現在の比率の逆関数、現在の比率と前の比率との逆関数、現在の比率および / 若しくは現在の比率と前の比率との比率の非線形関数、これらの任意の組み合わせ、またはこれらの任意の（1 若しくは

10

20

30

40

50

それ以上の ) 近似である。

【 0 1 2 3 】

動的可変オーバープロビジョニング ( O P ) およびデータエントロピー

図 3 A および図 3 B に、動的に変動するデータエントロピーに関連するものとしての動的に変動するホスト O P およびシステム O P の様々な実施形態の選択された詳細を示す。ホスト O P およびシステム O P は、( 動的に変動する ) ホスト割り当て領域の 1 若しくはそれ以上のホスト割り当て関数として、ならびに ( 例えば、ホストデータおよびシステムデータの ) ( 動的に変動する ) データ転送速度の 1 若しくはそれ以上のデータ転送速度割り当て関数として動的に変動する。ホスト割り当て領域の変動は、説明の都合上、データエントロピーに対して線形であるものとして図示されている。

10

【 0 1 2 4 】

例えば、ホスト割り当て領域が所定の量だけ増加 / 減少する場合には、その量は、組み合わせ O P に / から割り当てられ、結果として生じる組み合わせ O P は、1 若しくはそれ以上のデータ転送速度の 1 若しくはそれ以上のデータ転送速度割り当て関数に従って、ホスト O P とシステム O P との間で動的に割り当てられる。データ転送速度割り当て関数の例は、線形関数、逆関数、非線形関数、またはこれらの任意の組み合わせである。データ転送速度の例は、ホストデータ転送速度、システムデータ転送速度、フラッシュメモリへのホストデータ書き込みの帯域幅、フラッシュメモリへのシステムデータ書き込みの帯域幅、フラッシュメモリへの全書き込みの帯域幅、またはこれらの任意の組み合わせである。

20

【 0 1 2 5 】

図 3 A および図 3 B に示されているように、( 組み合わせ ) O P 割り当て領域は、対応するホスト割り当て領域の動的変動により動的に変動する。動的に変動する ( 組み合わせ ) O P 割り当て領域は、その場合、例えば、フラッシュメモリへのシステムデータ書き込みの帯域幅とフラッシュメモリへのホストデータ書き込みの帯域幅との比率に従って、システム O P とホスト O P との間で動的に可変的に割り当てられる。したがって、ホスト割り当て領域の特定の部分的減少 / 増加について ( 同じ比率で ) 、システム O P 割り当て領域は、その特定の部分に従って増加 / 減少する。様々な実施形態において、比率は任意選択で増減され、かつ / またはホスト O P とシステム O P との間の割り当て領域にオフセットが含まれる。ある実施形態では、割り当てはさらに、それぞれの最小値 / 最大値および / またはそれぞれの割り当て量のうちの 1 若しくはそれ以上に従う。

30

【 0 1 2 6 】

両図に共通して、横軸はデータエントロピー 3 2 0 を表し、左 ( 0 % ) から右 ( 1 0 0 % ) へ増加する。より低いデータエントロピーは、例えば、相対的に圧縮性が高く、相対的に重複排除によるコンパクト性が高く、かつ / または相対的にランダム性の低いホストデータに対応する。より高いデータエントロピーは、例えば、相対的に非圧縮性が高く、相対的に重複性が低く ( よって、重複排除によるコンパクト性が高くなく ) 、かつ / または相対的にランダム性が高いホストデータに対応する。2 つの特定のデータエントロピー値が、G % 3 3 0 G および H % 3 3 0 H として図示されている。

40

【 0 1 2 7 】

様々な実施形態において、データエントロピーは概念的なものであり、例えば、データエントロピーの明示的な測定は行われない。そうではなく、データエントロピーは、ホストデータのサイズが様々な圧縮、重複排除、またはホストデータを記憶するのに使用されるフラッシュメモリの量を変更する他の変換と共にどのように変動するかの表現である。例えば、ホストデータを記憶するのに使用されるフラッシュメモリは、データエントロピーが増加する ( 減少する ) に従って増加する ( 減少する )。例えば、データエントロピーとホストデータのサイズとの関係を ( 例えばホストデータ割り当て領域として ) 図示するときに、データエントロピーのための尺度は、線形、対数、二乗、任意に可変、またはこれらの任意の組み合わせとして解釈される。

【 0 1 2 8 】

50

縦軸は物理的サイズ 310 を表し、下(0%)から上(100%)へ増加する。縦軸に沿った長さは、使用される、かつ/または使用されるように割り当てられるフラッシュメモリに対応し、例えば、より短い/より長い長さは、所与の種類の情報(ホストデータやシステムデータなど)を記憶するのに使用されるより少ない/より多いフラッシュメモリに対応する。ある実施形態では、特定の長さは、特定の用途に(例えば、ホストデータ、システムデータ、またはOPに)割り当てられたフラッシュメモリのユニット数に対応する。

#### 【0129】

データエントロピーに対して変動するホスト割り当て関数は、ホスト割り当て領域 302V として図示されている。データエントロピーが増加するに従って、対応するホストデータを記憶するのに使用されるフラッシュメモリの物理的サイズは(例えば直線的に)増加し、逆もまた同様である。データエントロピーが増加する(減少する)際に固定されたままである不变システム割り当て関数は、システム割り当て領域 301 として図示されている。システム割り当て領域がデータエントロピーに従って変動する、例えば、データエントロピー(またはシステムデータのサイズおよび/若しくはホストデータのサイズと関連付けられた 1 若しくはそれ以上のメトリック)が増加する(減少する)に従って増加する(減少する)実施形態(図示せず)も企図されている。

#### 【0130】

図 3A には、比率の第 1 の値の線形関数に対応するシステム OP 割り当て領域(可変) 303V1 の第 1 の動的に変動する割り当ての 2 つの「動作点」(一方は G%330G に対応し、もう一方は H%330H に対応する)が例示されている。図 3B には、比率の第 2 の値の線形関数に対応するシステム OP 割り当て領域(可変) 303V2 の第 2 の動的に変動する割り当ての 2 つの「動作点」(一方は G%330G に対応し、もう一方は H%330H に対応する)が例示されている。比較のために、図 3A は(図 3B に詳述される 2 つの動作点を有する)システム OP 割り当て領域(可変) 303V2 の破線を含み、図 3B は(図 3A に詳述される 2 つの動作点を有する)システム OP 割り当て領域(可変) 303V1 の破線を含む。

#### 【0131】

様々な実施形態において、比率は、システム転送速度対ホスト転送速度の比率である。様々な実施形態において、システム転送速度および/またはホスト転送速度は、現在のデータ転送速度および/若しくは書き込み帯域幅ならびに/または前のデータ転送速度および/若しくは書き込み帯域幅の関数である。例えば、比率は、ある時間間隔にわたって平均されたシステム書き込みデータ帯域幅を、その時間間隔にわたって平均されたホスト書き込みデータ帯域幅で割ったものである。別の例では、比率は、前のある時点でのシステムデータ転送速度をその前のある時点でのホストデータ転送速度で割ったものである。

#### 【0132】

図 3A で、(G%330G に対応する)第 1 の動作点は、ホスト割り当て領域 302V とシステム OP 割り当て領域(可変) 303V1 との G% データエントロピーの交点に対するものである。第 1 の動作点は、ホスト割り当て領域 302G1、およびホスト OP 割り当て領域 305G1 とシステム OP 割り当て領域 304G1 との間で割り当てられた(組み合わせ)OP 割り当て領域 303G1 を含む。(H%330H に対応する)第 2 の動作点は、ホスト割り当て領域 302V とシステム OP 割り当て領域(可変) 303V1 との H% データエントロピーの交点に対するものである。第 2 の動作点は、ホスト割り当て領域 302H1、およびホスト OP 割り当て領域 305H1 とシステム OP 割り当て領域 304H1 との間で割り当てられた(組み合わせ)OP 割り当て領域 303H1 を含む。

#### 【0133】

第 1 の動作点と第 2 の動作点とを比較すると、データエントロピーが G% から H% へ増加するにつれて、ホストデータを記憶するのに使用されるフラッシュメモリは、ホスト割り当て領域 302G1 からホスト割り当て領域 302H1 へと増加する。OP 用途に利用できるフラッシュメモリがより少なくなるため、これに応答して(組み合わせ)OP 割り

10

20

30

40

50

当て領域も（組み合わせ）OP割り当て領域303G1から（組み合わせ）OP割り当て領域303H1へと減少し、対応するホストOPおよびシステムOPの割り当て領域も減少する。具体的には、ホストOP割り当て領域305G1はホストOP割り当て領域305H1まで減少し、システムOP割り当て領域304G1はシステムOP割り当て領域304H1まで減少する。ホストOPおよびシステムOPに対する減少は、システム書き込み帯域幅対ホスト書き込み帯域幅の比率といった比率の第1の値に従ったホストOPとシステムOPとの間でのOPリソースの割り当てと一致したものである。割り当ては、概念的に、システムOP割り当て領域（可変）303V1で表され、ホスト割り当て領域302Vの線形関数として図示されている。

【0134】

10

図3Bに、図3Aで図示した技法と同様の技法を示す。第1の動作点および第2の動作点は、ホスト割り当て領域302VおよびシステムOP割り当て領域（可変）303V2とのG%データエントロピーおよびH%データエントロピーのそれぞれの交点に対するものである。第1の動作点は、ホスト割り当て領域302G2、およびホストOP割り当て領域305G2とシステムOP割り当て領域304G2との間で割り当てられた（組み合わせ）OP割り当て領域303G2を含む。第2の動作点は、ホスト割り当て領域302H2、およびホストOP割り当て領域305H2とシステムOP割り当て領域304H2との間で割り当てられた（組み合わせ）OP割り当て領域303H2を含む。

【0135】

20

図3Aと同様に、図3Bに示すように、（例えばG%からH%への）データエントロピーの増加は、（例えばホスト割り当て領域302G2からホスト割り当て領域302H2への）ホスト割り当て領域の増加をもたらし、さらには、（例えば（組み合わせ）OP割り当て領域303G2から（組み合わせ）OP割り当て領域303H2への）（組み合わせ）OP割り当て領域の減少をもたらし、OP割り当て領域はさらに、システムOP割り当て領域（例えばシステムOP割り当て領域304G2からシステムOP割り当て領域304H2へ）とホストOP割り当て領域（例えばホストOP305G2からホストOP割り当て領域305H2へ）との間で再割り当てされる。システムOP割り当て領域およびホストOP割り当て領域の減少は、図3Aと関連付けられた比率の第2の値に従ったシステムOPとホストOPとの間でのOPリソースの割り当てと一致したものである。

【0136】

30

図3Aと図3Bとを比較すると、システムOP割り当て領域（可変）303V1の傾きはシステムOP割り当て領域（可変）303V2の傾きよりも小さく、これは、比率の第1の値が比率の第2の値より小さいことに対応する。比率が、システムデータ転送速度をホストデータ転送速度で割ったものである実施形態を考察する。ホストデータ転送速度が不变である間にシステムデータ転送速度が動的に変動する使用シナリオにおいて、システムOP割り当て領域（可変）303V1はシステムOP割り当て領域（可変）303V2よりも低いシステムデータ転送速度に対応する。よって、システムデータ転送速度は（一定のホストデータ転送速度に対して）動的に増加し、システムOP割り当て領域は、システムOP割り当て領域304G1からシステムOP割り当て領域304G2へと（あるいは、システムOP304H1からシステムOP304H2へと）増加する。これに対応して、ホストOP割り当て領域は、ホストOP割り当て領域305G1からホストOP割り当て領域305G2へと（またはホストOP割り当て領域305H1からホストOP割り当て領域305H2へと）減少する。一方、システムデータ転送速度が不变である間にホストデータ転送速度が動的に変動する使用シナリオにおいては、前述のシステムOP割り当て領域およびホストOP割り当て領域の変化は同様に生じる（システムOP割り当て領域（可変）303V1はシステムOP割り当て領域（可変）303V2よりも高いホストデータ転送速度に対応する）。

【0137】

40

（図3Aおよび図3Bの）第1の動作点および第2の動作点、ならびにG%からH%へと増加する前述のデータエントロピーの前述の説明は例にすぎない。別の例として、ある

50

使用シナリオにおいて、データエントロピーは、H %からG %へと減少し、フラッシュメモリ割り当ては、システムOP用途へのフラッシュメモリの割り当てが増加するよう、第2の動作点と一致したもの(H %)から第1の動作点と一致したもの(G %)へと変更される。さらに、データエントロピー軸に沿った複数の可能な動作点が可能であり(図示せず)、これらは実施詳細によってのみ制限される。さらに、ある状況では、動作シナリオは、様々な動作シナリオの間で動的に切り換わり、対応する動作点は動的に、例えば、SSDおよび/またはSSDコントローラの様々な動作特性に基づくものである。

#### 【0138】

比較および参照のために、図3Aおよび図3Bには、固定された(例えば、データエントロピーに対して不变である)システム割り当て領域(固定)301Fが全く同様に図示されている。ある実施形態および/または使用シナリオは動作モードおよび/または動作サブモードを含み、これらのモードでは、システムOPリソースは、システムOP割り当て領域(固定)304Fで概念的に図示するように、固定されている(例えば、データエントロピーに対して不变である)。ある実施形態では、システムOP割り当て領域(固定)304Fは、最小システムOP割り当て領域の全部または一部分を表す。

10

#### 【0139】

図3Aおよび図3Bには、データエントロピーの動的変動の影響をさらに受けるホスト割り当て領域の動的変動の結果として(例えば、ホストOPとシステムOPとの間でのOPリソースの動的割り当てによって)動的に変動するシステムOPのいくつかの例の態様が示されている。態様のあるものは、図のどちらかだけに関して概念的に表されており、態様のあるものは、両図の組み合わせに関して概念的に表されている。

20

#### 【0140】

図3Aのみ(または図3Bのみ)に関しては、動的に変動するシステムOPは、(様々なデータエントロピー動作点に対応する)様々なホスト割り当て領域間の動的変化に関して概念的に表されており、システムデータ転送速度対ホストデータ転送速度の比率は固定されたままである。ホスト割り当て領域302VおよびシステムOP割り当て領域(可変)303V1で表されたシステムOP割り当て関数との交点といった、G %エントロピーに対応するホスト割り当てでの動作を開始すると考える。続いてH %エントロピーに対応するホスト割り当てでの動作に遷移し、引き続きシステムOP割り当て領域(可変)303V1で表された関数に従って割り当てを行い、かつ/またはシステムOPリソースの割り当てを行う。続いてG %エントロピーに対応するホスト割り当てでの動作に戻り、引き続きシステムOP割り当て領域(可変)303V1で表された関数に従って割り当てを行い、かつ/またはシステムOPリソースの割り当てを行う。システムOPは、データエントロピー動作点の変化にさらに関連したものであるホスト割り当て領域の変化に応答して、システムOP割り当て領域304G1からシステムOP割り当て領域304H1へと動的に変更され、次いでシステムOP割り当て領域304G1に戻される。

30

#### 【0141】

図3Aと図3Bとの組み合わせに関しては、動的に変動するシステムOPは、システムのデータ転送速度および/若しくは書き込み帯域幅ならびに/またはホストのデータ転送速度および/若しくは書き込み帯域幅、割り当てを決定するのに使用される1若しくはそれ以上の関数、またはこれらの任意の組み合わせの差異および/または変化に基づくホストOP用途とシステムOP用途との間でのOPリソースの割り当て間の動的変更に関して概念的に表されている。G %データエントロピーおよびシステムOP割り当て領域(可変)303V1の図3Aに示すコンテキストで動作を開始すると考える。続いてG %データエントロピーおよびシステムOP割り当て領域(可変)303V2の図3Bで示されるコンテキストでの動作に遷移する。続いてG %データエントロピーおよびシステムOP割り当て領域(可変)303V1の図3Aで示されるコンテキストでの動作に戻る。システムOPは、例えば、システムデータ書き込み帯域幅、ホストデータ書き込み帯域幅、および/またはこれらの(1若しくはそれ以上の)比率などの変化に応答して、システムOP割り当て領域304G1からシステムOP割り当て領域304G2へと動的に変更され、次

40

50

いでシステムOP割り当て領域304G1に戻される。

【0142】

また、図3Aと図3Bとの組み合わせに関しては、動的に変動するシステムOPは、システムのデータ転送速度および／若しくは書き込み帯域幅ならびに／またはホストのデータ転送速度および／若しくは書き込み帯域幅、および／またはこれらの比率の差異および／または変化に基づくホストOP用途とシステムOP用途との間でのOPリソースの割り当て領域間の動的変更と組み合わせた（様々なデータエントロピー動作点に対応する）様々なホスト割り当て領域間の動的変更に関する概念的に表されている。G%データエントロピーおよびシステムOP割り当て領域（可変）303V1の図3Aに示すコンテキストで動作を開始すると考える。続いてH%データエントロピーおよびシステムOP割り当て領域（可変）303V2の図3Bで示されるコンテキストでの動作に遷移する。続いてG%データエントロピーおよびシステムOP割り当て領域（可変）303V1の図3Aで示されるコンテキストでの動作に戻る。システムOPは、例えば、（例えばデータエントロピーに関連した）ホスト割り当て領域、システムデータ書き込み帯域幅、ホストデータ書き込み帯域幅、および／またはこれらの比率などの変化に応答して、システムOP割り当て領域304G1からシステムOP割り当て領域304H2へと動的に変更され、次いでシステムOP割り当て領域304G1に戻される。

【0143】

ホストOP用途とシステムOP用途との間でのOPリソースの割り当て領域がホストから受け取られるデータパターンに基づくものである他の実施形態が企図されている。例えば、ホストが連続したアドレスへの一連の書き込みを行っている場合には、ホストOP用途とシステムOP用途との間の割り当ては、測定されたホストデータ転送速度の（1未満の）部分である低減されたホストデータ転送速度を使用して計算され、そのため、測定されたホストデータ転送速度がその割り当てに使用された場合よりも少ないホストデータOPが割り当てられる。別の例では、ホストがランダムなアドレスへの一連の書き込みを行っている場合には、ホストOP用途とシステムOP用途との間の割り当ては、測定されたシステムデータ転送速度の倍数である増加させたシステムデータ転送速度を使用して計算され、そのため、測定されたシステムデータ転送速度がその割り当てに使用された場合よりも多いシステムデータOPが割り当てられる。倍数は1より大きいが、必ずしも整数であるとは限らない。

【0144】

ホストOP用途とシステムOP用途との間でのOPリソースの割り当て領域がフラッシュメモリのユニットの瞬間的使用状況に基づくものである他の実施形態が企図されている。例えば、ユニットのバーストがシステム（あるいはホスト）データを記憶するのに使用される場合には、システム（あるいはホスト）OPの割り当て領域は一時的に引き上げられる。

【0145】

図3Aおよび図3B（ならびに図2）で表されたいいくつかの実施形態のいくつかの態様は、概念的に図示されている。前述の図では、様々な割り当ては、連続的であるか否かにかかわらず、割り当てられたフラッシュメモリの記憶のそれぞれの総量を表すものである。例えば、システム割り当て領域201は、フラッシュメモリの複数の非連続ユニットである。別の例として、ホスト割り当て領域302G1および（組み合わせ）OP割り当て領域303G1は、各々、フラッシュメモリのそれぞれの複数の非連続ユニットである。

【0146】

（図2、図3A、および／または図3Bで一部図示されているような）ある実施形態では、OPを増やすためのリソースとして追加のフラッシュメモリ（図示せず）を利用することができ、あるいは、フラッシュメモリのうちの1若しくはそれ以上の部分が故障すると結果的にOPが減ることになる。ある実施形態では、フラッシュメモリは図示しない用途のために確保されている。例えば、フラッシュメモリの1若しくはそれ以上のフラッシュメモリのうちの1若しくはそれ以上の部分は、フラッシュメモリの故障した部分の交換の

ために予約されている。

#### 【0147】

(図2、図3A、および/または図3Bで一部図示されているような)ある実施形態では、ホストデータおよび/またはシステムデータの全部または任意の部分は、不变のまま、圧縮されて、重複排除されて、暗号化されて、任意の形の可逆変換を施されて、またはこれらの任意の組み合わせを適用されてフラッシュメモリに記憶される。ある実施形態では、フラッシュメモリに記憶された情報は、ある実施形態では、低レベルおよび/または高レベルの冗長情報によって保護された情報に加えて、低レベルの冗長情報(ページごとのECCなど)および/または高レベルの冗長情報(RAID様の冗長情報など)を含む。

10

#### 【0148】

オーバープロビジョニング(OP)リソースユニットの(再)割り当ておよびライフサイクル

図4に、例えば、図2、図3A、および図3Bのいずれかに関連した1若しくはそれ以上のコンテキストにおける、NVMを管理するための可変OPのコンテキストにおけるOPリソースの割り当ておよび/または(再)割り当ての実施形態の流れ図を示す。流れではまず、状況が再割り当ての実行に対応するかどうか計算する(続けて(再)割り当てを行う402ための(再)割り当て条件が存在するかどうか決定する401)。状況が存在しない場合には、流れは折り返し戻って計算を繰り返す。状況が存在する場合には、様々な実施形態に従って(再)割り当てが要求され、待ち行列に入れられ、または即座に実行される((再)割り当てを実行する403)。

20

#### 【0149】

様々な実施形態において、割り当て条件および/または(再)割り当て条件が存在するかどうかの計算((再)割り当て条件が存在するかどうか決定する401および/または(再)割り当てを実行する403)は、様々な特定の時点の任意の1若しくはそれ以上において実行される。様々な特定の時点の例は、1若しくはそれ以上のフラッシュメモリユニットが特定の用途のためのものとして(例えば、システムOP用途やホストOP用途のためのものとして)割り当てられ、またはマークされるときである。他の例は、ユニットが、ガーベジコレクション、再利用、消去といった様々な操作を終了し、開始し、またはそのために選択されるときである。他の例は、ユニットがホストユニット状態、システムユニット状態、若しくは空状態待ち行列になるとき、またはユニットがある管理状態から別の管理状態に遷移するときである。他の例は、特定の用途(例えばシステム用途やホスト用途)に利用可能なユニットの数がそれぞれの所定の、かつ/またはプログラムで決定された閾値(例えば最高水準や最低水準)に達したときである。

30

#### 【0150】

図2、図3A、図3B、および図4のうちのいずれか1若しくはそれ以上で概念的に表された様々な実施形態において、割り当て条件および/または(再)割り当て条件が存在するかどうかの計算(例えば、(再)割り当て条件が存在するかどうか決定する401など)は、ユニットが特定の用途(ホストやシステムなど)のためのものとしてマークされるときに実施される。

40

#### 【0151】

図2、図3A、図3B、および図4のうちのいずれか1若しくはそれ以上で概念的に表された様々な実施形態において、割り当て変更、例えば、割り当ておよび/または(再)割り当て)は、フラッシュメモリの未使用の、かつ/または空のユニットを特定の用途のためにマークするとき、例えば、ガーベジコレクションを終了するフラッシュメモリユニットをシステムOP用途に対するホストOP用途のためのものとしてマークするときや、空状態待ち行列に入る時点のフラッシュメモリユニットをシステムOP用途に対するホストOP用途のためのものとしてマークするときなどに、ターゲットとして実施される。例えば、図4で表されたある実施形態では、再割り当ての実行は多段階プロセスである。ターゲット(再)割り当ては、決定され、記憶され、次いで、フラッシュメモリユニットが

50

ガーベジコレクションを終了する際に、終了するユニットは、記憶された（再）割り当てに従って使用可能とマークされる。

#### 【0152】

図5に、R-ブロックといった、フラッシュメモリの被管理ユニットのライフサイクルの実施形態の流れ図500を示す。フラッシュメモリの全部または任意の部分はユニットの集合として管理され、流れ図は、フラッシュユニット管理エージェントがユニットの各々の状態をどのようにして管理するかを表すものである。概念的には、流れ図500は、管理されるユニットの各々についてインスタンス化された状態機械を表すものである。簡単にするために以下の説明では、ユニットを特定の状態に「設定する」、ユニットを特定の状態であるものとして「マークする」といった用語法を、ユニットと関連付けられた管理状態を特定の状態に（または特定の状態を示す1若しくはそれ以上の値に）設定することの略記とする。

10

#### 【0153】

説明を続けて、初期設定時に（例えば、電源オンリセット、リセットコマンドの受け取り、またはこれらの任意の組み合わせに応答して）、フラッシュメモリのユニットのすべてが、ユニットが使用できることを示す初期状態に設定される（空き状態501）。イベントに起因する割り当てに備えるよう求める要求に応答して、所定のユニットは、（例えば、少なくとも部分的にガーベジコレクション、再利用、および／または消去によって）割り当てに備えられ、即座の割り当てに利用可能性であることを示すように設定される（空状態待ち行列502）。ある実施形態では、即座の割り当ての利用可能性は、割り当て遷移マーキング（待ち行列割り当て512）で概念的に示されるように、ユニットが1若しくはそれ以上の空状態待ち行列のうちの1つに入っていることに対応する。

20

#### 【0154】

空状態待ち行列のうちの1つに入ると、ユニットは、ホスト用途（ホスト割り当て領域513）として、またはシステム用途（システム割り当て領域514）としての用途に従ってマークされる。ユニットは次いで、ホスト用途（ホストユニット503）のための、またはシステム用途（システムユニット504）のためのマーキングに従って使用される。再利用またはガーベジコレクションによる再利用のための特定のユニットの選択に応答して、その特定のユニットは、再利用され、その特定のユニットが使用できることを示すように設定される（空状態501）。利用可能性を指示するための設定は、ユニットが再利用のために選択される前にホスト用途に使用されていたにせよ（ホストユニット515を再利用する）、ユニットが再利用のために選択される前にシステム用途に使用されていたにせよ（システムユニット516を再利用する）、行われる。

30

#### 【0155】

ある実施形態では、再利用のためのユニットの選択は、概念的には2段階プロセスである。第1に、（ホストユニット503などに対応する）ホストデータを記憶するのに使用されるユニットや、（システムユニット504などに対応する）システムデータを記憶するのに使用されるユニットといった、再利用すべきユニットの種類の選択が行われる。選択は、図2、図3A、または図3Bに関連して説明したような（動的に）可変のOPに基づくものである。第2に、選択されたカテゴリのユニットの少なくとも一部分のうちで、再利用すべきユニットの選択が行われる。

40

#### 【0156】

ある代替の実施形態では、空状態待ち行列がなく、ユニットは、使用できる状態（空状態501）から、中間の待ち行列に入れられた状態（空状態待ち行列502）を通らずに、ホストユニット（ホストユニット503）として、またはシステムユニット（システムユニット504）としての用途に従って使用される状態へ即座に遷移するものとしてマークされる。ある代替の実施形態では、ホストユニットまたはシステムユニットとして使用されるべきユニットに従った2つのカテゴリの待ち行列があり、ユニットがホストユニットとして使用されるべきか、それともシステムユニットとして使用されるべきかに関する判断は、そのユニットが、使用できる状態（空状態501）から、ホスト分類またはス

50

テム分類を有する待ち行列に従った即座の割り当てに利用可能である状態へ即座に遷移するものとしてマークされるときに行われる。

【0157】

様々な実施形態および／または使用シナリオにおいて、図2、図3A、図3B、および図4のうちのいずれか1若しくはそれ以上に関連した様々な操作は、図5（または図5に関連して説明した代替の実施形態）に示す様々な遷移に応答して、かつ／またはこれらと協働して実行される。様々な操作には、（1若しくはそれ以上の）（動的）割り当て、（1若しくはそれ以上の）（動的）再割り当て、ならびに割り当て／再割り当てに関連した計算および決定が含まれる。

【0158】

例えば、図2のホスト割り当て領域202Aとホスト割り当て領域202Cとの間に示されるようなホスト割り当て領域の動的変更は、ユニットが、ホストユニット（ホスト割り当て領域513）として使用されるべき空状態待ち行列のうちの1つを出るものとしてマークされるときに実行される。別の例として、図2のシステムOP割り当て領域204AとシステムOP割り当て領域204Bとの間に示されるような、ホストOP割り当て領域とシステムOP割り当て領域との間でのOPリソースの割り当て領域の動的変更は、ユニットが、システム分類を有する空状態待ち行列に入るものとしてマークされるときに実行される。さらに別の例として、図3AのシステムOP割り当て領域304G1と図3BのシステムOP割り当て領域304G2との間に示されるような、ホストOP割り当て領域とシステムOP割り当て領域との間でのOPリソースの割り当て領域の動的変更は、ユニットが、空状態待ち行列のうちの1つを出ると同時にホスト用途（ホストユニット503）またはシステム用途（システムユニット504）のためのものとしてマークされるときに実行される。

10

【0159】

さらに別の例では、再割り当てすべきか否かの計算（図4の（再）割り当て条件が存在するかどうか決定する401など）は、ユニットが再利用のために選択され、再利用されるよう求める要求（ホストユニットを再利用する515またはシステムユニットを再利用する516）と協働して実行される。ある実施形態では、再利用のために選択されるユニットの分類は、（再）割り当て（例えば、（再）割り当てを実行する403）の結果とは無関係であり、例えば、ホストユニットまたはシステムユニットは再割り当ての結果にかかわらず選択される。他の実施形態では、再利用のために選択されるユニットの分類は、少なくとも部分的に（再）割り当て（例えば、（再）割り当てを実行する403）の結果に基づくものであり、例えば、ホストユニットは、再割り当て結果が、ホストOP用途により少ないホストユニットが割り当てられるべきであることを示すときに選択される。

20

【0160】

様々な実施形態において、図2、図3A、図3B、および図4の1若しくはそれ以上の要素は、図1Aの1若しくはそれ以上の要素に対応し、またはこれらに関連したものである。例えば、図2のフラッシュメモリ200はNVM199に対応する。別の例として、図3Aおよび図3Bの物理的サイズ310に沿った長さは、NVM199の記憶の量に対応する。さらに別の例として、図2、図3A、図3B、および／または図4に関連して述べた割り当て操作または割り当て関連の操作のうちの1若しくはそれ以上は、リサイクル151およびCPU171のうちの1若しくはそれ以上の1若しくはそれ以上の部分によって、またはこれらの制御の下で実行される。さらに別の例として、図5の状態遷移のうちの1若しくはそれ以上は、マップ141、リサイクル151、およびCPU171のうちの1若しくはそれ以上の1若しくはそれ以上の部分によって、またはこれらの制御の下で実行される。さらに別の例として、図2、図3A、または図3Bに関連して言及したような、（1若しくはそれ以上の）ホストデータ転送速度の測定は、ホストインターフェース111の全部または任意の（1若しくはそれ以上の）部分を介して実行される。さらに別の例として、図2、図3A、または図3Bに関連して言及したような、（1若しくはそれ以上の）ホストデータ転送速度および／または（1若しくはそれ以上の）システムデー

30

40

50

タ転送速度の測定は、デバイスインターフェース論理 191 および / またはスケジューリング 193 の全部または任意の ( 1 若しくはそれ以上の ) 部分を介して実行される。

#### 【 0161 】

##### 実施技法の例

ある実施形態では、( 例えはフラッシュメモリを有する ) 不揮発性記憶、コンピューティングホスト・フラッシュ・メモリ・コントローラ、および / または SSD コントローラ ( 例えは図 1A の SSD コントローラ 100 ) 、ならびにプロセッサ、マイクロプロセッサ、システム・オン・チップ、特定用途向け集積回路、ハードウェアアクセラレータ、または前述の動作の全部または部分を提供する他の回路を管理するための自己ジャーナリングおよび階層的整合性を実施するシステムによって行われる動作の全部またはいずれかの部分の様々な組み合わせが、コンピュータシステムによる処理と適合する仕様によって指定される。仕様は、様々な記述、例えは、ハードウェア記述言語、回路記述、ネットリスト記述、マスク記述、またはレイアウト記述に従つたものである。記述の例には、 Verilog 、 VHDL 、 SPICE 、 SPICE の変形、例えは、 PSpice 、 I BIS 、 LEF 、 DEF 、 GDS - II 、 OASIS 、または他の記述が含まれる。様々な実施形態では、処理は、 1 若しくはそれ以上の集積回路上に含めるのに適する論理および / または回路を生成し、検証し、または指定するための解釈、コンパイル、シミュレーション、および合成の任意の組み合わせを含む。各集積回路は、様々な実施形態によれば、様々な技法に従つて設計することができ、かつ / または製造することができる。技法には、プログラマブルな技法 ( 例えは、フィールド若しくはマスク・プログラマブル・ゲート・アレイ集積回路 ) 、セミカスタムの技法 ( 例えは、全部若しくは一部がセルベースの集積回路 ) 、およびフルカスタムの技法 ( 例えは、実質的に専門化された集積回路 ) 、それらの任意の組み合わせ、または集積回路の設計および / 若しくは製造と適合する任意の他の技法が含まれる。

10

#### 【 0162 】

ある実施形態では、命令のセットを記憶しているコンピュータ可読媒体によって記述される動作の全部または部分の様々な組み合わせが、 1 若しくはそれ以上のプログラム命令の実行および / 若しくは解釈によって、 1 若しくはそれ以上のソースおよび / 若しくはスクリプト言語命令文の解釈および / 若しくはコンパイルによって、または、プログラミングおよび / 若しくはスクリプティング言語命令文で表現された情報をコンパイルし、変換し、かつ / または解釈することによって生成されるバイナリ命令の実行によって実行される。命令文は任意の標準のプログラミングまたはスクリプティング言語 ( 例えは、 C 、 C ++ 、 Fortran 、 Pascal 、 Ada 、 Java ( 登録商標 ) 、 VBscript 、 Shell ) と適合する。プログラム命令、言語命令文、またはバイナリ命令のうち 1 若しくはそれ以上が、任意選択で、 1 若しくはそれ以上のコンピュータ可読記憶媒体要素上に記憶される。様々な実施形態では、プログラム命令の一部、全部、または様々な部分が、 1 若しくはそれ以上の関数、ルーチン、サブルーチン、インラインルーチン、プロシージャ、マクロ、またはそれらの部分として実現される。

20

#### 【 0163 】

##### 結論

ある特定の選択が、説明において、テキストおよび図面を作成するに際の単なる便宜のためになされており、別の指示がない限り、それらの選択は、それ自体で、前述の実施形態の構造または動作に関する追加情報を伝えるものと解釈すべきではない。選択の例には、図の符番に使用される呼称の特定の編成または割り当て、および実施形態の特徴および要素を識別し、参照するのに使用される要素識別子 ( コールアウトや数値識別子など ) の特定の編成または割り当てが含まれる。

30

#### 【 0164 】

「 includes 」または「 including 」という語は、開放型範囲の論理集合を記述する抽象概念として解釈されるべきことが明確に意図されており、後に続けて「 within 」という語が明示されない限り物理的包含を伝えるためのものではない。

40

50

**【 0 1 6 5 】**

前述の実施形態は、説明および理解の明確さのためにある程度詳細に説明されているが、本発明は提示した詳細だけに限定されるものではない。本発明の多くの実施形態がある。開示の実施形態は例示であり、限定ではない。

**【 0 1 6 6 】**

説明と整合性を有する、構成、配置、および使用における多くの変形が可能であり、それらの変形は、発行される特許の特許請求の範囲内にあることが理解されるであろう。例えば、相互接続および機能ユニットのピット幅、クロック速度、および使用される技術の種類は、各構成要素ブロックにおける様々な実施形態に従って変わりうる。相互接続および論理に与えられた名称は、単なる例であり、説明した概念を限定するものと解釈すべきではない。フローチャートおよび流れ図のプロセス、動作、および機能要素の順序および配置は、様々な実施形態に従って変わりうる。また、特に別に指定しない限り、指定される値範囲、使用される最大値および最小値、または他の特定の仕様（例えば、フラッシュメモリ技術の種類、レジスタおよびバッファ内のエントリまたは段の数）は、単に前述の実施形態のものにすぎず、実施技術の改善および変更を追跡することが見込まれるものであり、限定として解釈すべきではない。

10

**【 0 1 6 7 】**

当分野で公知の機能的に等価の技法を、様々なコンポーネント、サブシステム、動作、関数、ルーチン、サブルーチン、インラインルーチン、プロシージャ、マクロ、またはそれらの部分を実施するのに、前述の技法の代わりに用いることができる。また、実施形態の多くの機能的態様を、より高速な処理（以前にハードウェアにあった機能のソフトウェアへの移行を円滑化する）およびより高い集積密度（以前にソフトウェアにあった機能のハードウェアへの移行を円滑化する）の実施形態に依存する設計制約条件および技術傾向に応じて、選択的に、ハードウェア（おおむね専用の回路など）で、またはソフトウェアで（例えば、プログラムされたコントローラ若しくはプロセッサのある方式によって）実現できることも理解される。様々な実施形態の具体的な変形は、これに限定されるものではないが、分割の違い、フォームファクタおよび構成の違い、異なるオペレーティングシステムおよび他のシステムソフトウェアの使用、異なるインターフェース規格、ネットワークプロトコル、または通信リンクの使用、本明細書で説明した概念を、特定の用途の固有の技術的業務的制約条件に従って実施するときに予期されるべき他の変形を含む。

20

**【 0 1 6 8 】**

各実施形態は、前述の各実施形態の多くの態様の最小限の実施に必要とされるものを大きく超えた詳細および環境的コンテキストと共に説明されている。ある実施形態は、残りの要素間での基本的協働を変更せずに開示の構成要素または機能を割愛することを当業者は理解するであろう。よって、開示の詳細の多くが前述の実施形態の様々な態様を実施するのに必要ではないことが理解される。残りの要素が先行技術と区別できる範囲内で、割愛される構成要素および特徴は本明細書で説明した概念を限定するものではない。

30

**【 0 1 6 9 】**

設計におけるすべてのそのような変形は、前述の実施形態によって伝えられる教示に対する実質的な変更ではない。また、本明細書で説明した実施形態は、他のコンピューティング用途およびネットワーキング用途に幅広い適用性を有し、前述の実施形態の特定の用途または産業だけに限定されるものではないことも理解される。よって本発明は、発行される特許の特許請求の範囲内に包含されるあらゆる可能な改変形態および変形形態を含むものと解釈すべきである。

40

【図 1 A】

Fig. 1A

【 図 1 B 】

Fig. 1B

〔 2 〕

Fig. 2

Fig. 3A

【図3B】

Fig. 3B

【図4】

Fig. 4

【図5】

Fig. 5

---

フロントページの続き

(72)発明者 トムリン、アンドリュー ジョン

アメリカ合衆国、95132 カリフォルニア州、サンノゼ、2824 モンテ クレスタ ウエイ

審査官 酒井 恭信

(56)参考文献 特開2010-152516 (JP, A)

米国特許出願公開第2010/0161884 (US, A1)

特開2008-102900 (JP, A)

特表2011-505046 (JP, A)

米国特許出願公開第2011/0264843 (US, A1)

(58)調査した分野(Int.Cl., DB名)

G06F 12/00 - 12/06