(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

23 June 2011 (23.06.2011)

(10) International Publication Number

**WO 2011/074506 A1**

(51) International Patent Classification:

**H01L 21/336** (2006.01)   **H01L 29/786** (2006.01)

**H01L 21/20** (2006.01)

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(21) International Application Number:

PCT/JP2010/072304

(22) International Filing Date:

6 December 2010 (06.12.2010)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

2009-288494 18 December 2009 (18.12.2009) JP

(71) Applicant (for all designated States except US): SEMICONDUCTOR ENERGY LABORATORY CO., LTD. [JP/JP]; 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

(72) Inventors; and

(75) Inventors/Applicants (for US only): YAMAZAKI, Shunpei [JP/JP]; c/o SEMICONDUCTOR ENERGY LABORATORY CO., LTD., 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP). HIROHASHI, Takuya. TAKAHASHI, Masahiro. SHIMAZU, Takashi.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

— with international search report (Art. 21(3))

(54) Title: SEMICONDUCTOR DEVICE AND METHOD FOR MANUFACTURING THE SAME

**FIG. 3D**

**WO 2011/074506 A1**

(57) Abstract: A larger substrate can be used, and a transistor having a desirably high field-effect mobility can be manufactured through formation of an oxide semiconductor layer having a high degree of crystallinity, whereby a large-sized display device, a high-performance semiconductor device, or the like can be put into practical use. A single-component oxide semiconductor layer is formed over a substrate; then, crystal growth is carried out from a surface to an inside by performing heat treatment at 500 °C to 1000 °C inclusive, preferably 550 °C to 750 °C inclusive so that a single-component oxide semiconductor layer including single crystal regions is formed; and a multi-component oxide semiconductor layer including single crystal regions is stacked over the single-component oxide semiconductor layer including single crystal regions.

## DESCRIPTION

SEMICONDUCTOR DEVICE AND METHOD FOR MANUFACTURING THE

SAME

5

## TECHNICAL FIELD

[0001]

The present invention relates to a semiconductor device which includes a circuit including at least a semiconductor element such as a transistor as an element, and a manufacturing method thereof. For example, the present invention relates to an electronic device which includes, as a component, any of a power device mounted in a power circuit, a semiconductor integrated circuit including a memory, a thyristor, a converter, an image sensor, or the like, an electro-optical device typified by a liquid crystal display panel, and a light-emitting display device including a light-emitting element.

15

[0002]

In this specification, a semiconductor device generally means a device which can function by utilizing semiconductor characteristics, and an electro-optical device, a semiconductor circuit, and an electronic device are all semiconductor devices.

20

## BACKGROUND ART

[0003]

A transistor formed over a glass substrate or the like is manufactured using amorphous silicon, polycrystalline silicon, or the like, as typically seen in a liquid crystal display device. Although a transistor manufactured using amorphous silicon has low field-effect mobility, it has an advantage of being able to be formed over a larger glass substrate. On the other hand, although a transistor manufactured using polycrystalline silicon has high field-effect mobility, it has a disadvantage of not being suitable for a larger glass substrate.

30

[0004]

In contrast to a transistor manufactured using silicon, a technique in which a transistor is manufactured using an oxide semiconductor and applied to an electronic

device or an optical device has attracted attention. For example, Patent Document 1 and Patent Document 2 disclose a technique in which a transistor is manufactured using zinc oxide or an In-Ga-Zn-O-based oxide as an oxide semiconductor and such a transistor is used as a switching element or the like of a pixel of a display device.

5 [Reference]

[Patent Document]

[0005]

[Patent Document 1] Japanese Published Patent Application No. 2007-123861

[Patent Document 2] Japanese Published Patent Application No. 2007-096055

10

## DISCLOSURE OF INVENTION

[0006]

Further, large-sized display devices have increasingly become popular. Home-use televisions with a display screen diagonal of 40 inches to 50 inches have started to spread.

15 [0007]

The field-effect mobility of a transistor manufactured using a conventional oxide semiconductor is  $10 \text{ cm}^2/\text{Vs}$  to  $20 \text{ cm}^2/\text{Vs}$ . Since the field-effect mobility of a transistor manufactured using an oxide semiconductor is ten times or more as high as that of a transistor manufactured using amorphous silicon, the transistor manufactured using an oxide semiconductor can provide a performance sufficient as a pixel switching element even in a large-sized display device.

20 [0008]

However, there has been a limitation on the transistor manufactured using an oxide semiconductor when being used as a switching element in a driving device of a semiconductor device, for example, in a driver circuit of a large-sized display device.

25 [0009]

It is an object of an embodiment of the present invention to enable the use of a larger substrate and the manufacture of a transistor having a desirably high field-effect mobility through formation of an oxide semiconductor layer having a high degree of crystallinity, and also to put a large-sized display device, a high-performance semiconductor device, or the like into practical use.

## [0010]

According to an embodiment of the present invention, a single-component oxide semiconductor layer is formed over a substrate; then, crystal growth is carried out from a surface to an inside by performing heat treatment at 500 °C to 1000 °C inclusive, 5 preferably 550 °C to 750 °C inclusive, so that a single-component oxide semiconductor layer including single crystal regions is formed; and a multi-component oxide semiconductor layer including single crystal regions is stacked over the single-component oxide semiconductor layer including single crystal regions. Note that single crystal regions of each of the single-component oxide semiconductor layer 10 including single crystal regions and the multi-component oxide semiconductor layer including single crystal regions are flat-plate-shaped single crystal regions having uniform crystal direction with respect to the surface thereof. The flat-plate-shaped single crystal regions have the a-b plane parallel to the surface thereof and the c-axis in a direction perpendicular to the surfaces of the single-component oxide semiconductor 15 layer including single crystal regions and the multi-component oxide semiconductor layer including single crystal regions. The c-axis directions of the single-component oxide semiconductor layer including single crystal regions and the multi-component oxide semiconductor layer including single crystal regions correspond to the depth direction.

## 20 [0011]

The multi-component oxide semiconductor layer including single crystal regions can be formed in the following manner: a multi-component oxide semiconductor layer is formed over the single-component oxide semiconductor layer including single crystal regions, and then, heat treatment at 100 °C to 500 °C inclusive, 25 preferably 150 °C to 400 °C inclusive is performed, so that crystal growth is carried out toward the surface of the multi-component oxide semiconductor layer which is in an upper level than the surface of the single-component oxide semiconductor layer including single crystal regions. That is, the single-component oxide semiconductor layer including single crystal regions is a seed crystal for the multi-component oxide 30 semiconductor layer.

## [0012]

In addition, the multi-component oxide semiconductor layer including single crystal regions can be formed in the following manner: the multi-component oxide semiconductor layer is deposited over the single-component oxide semiconductor layer including single crystal regions typically by a sputtering method while heating is 5 performed at 200 °C to 600 °C inclusive, preferably 200 °C to 550 °C inclusive, so that epitaxial growth or axial growth from the surface of the single-component oxide semiconductor layer including single crystal regions is carried out and the multi-component oxide semiconductor layer including single crystal regions can be formed. That is, the single-component oxide semiconductor layer including single 10 crystal regions is a seed crystal for the multi-component oxide semiconductor layer including single crystal regions.

[0013]

Since the crystal growth is carried out with the use of the single-component oxide semiconductor layer including single crystal regions as a seed crystal, the 15 multi-component oxide semiconductor layer including single crystal regions has substantially the same crystal direction as the single-component oxide semiconductor layer including single crystal regions.

[0014]

In addition, according to an embodiment of the present invention, crystal 20 growth of the multi-component oxide semiconductor layer is carried out using the single-component oxide semiconductor layer including single crystal regions formed over a substrate as a seed crystal to form the multi-component oxide semiconductor layer including single crystal regions.

[0015]

25 In addition, according to an embodiment of the present invention, the single-component oxide semiconductor layer including single crystal regions is formed over the substrate, and then, the multi-component oxide semiconductor layer including single crystal regions is formed using the single-component oxide semiconductor layer including single crystal regions as a seed crystal.

30 [0016]

After that, the single-component oxide semiconductor layer including single crystal regions and the multi-component oxide semiconductor layer including single

crystal regions are etched into island-shapes, a source electrode and a drain electrode are formed over the multi-component oxide semiconductor layer including single crystal regions which has an island-shape, and a gate insulating layer and a gate electrode are formed, whereby a top-gate transistor can be manufactured.

5 [0017]

Alternatively, a gate electrode and a gate insulating layer are formed over a substrate, a single-component oxide semiconductor layer including single crystal regions and a multi-component oxide semiconductor layer including single crystal regions are formed, the single-component oxide semiconductor layer including single crystal regions and the multi-component oxide semiconductor layer including single crystal regions are etched into island-shapes, and a source electrode and a drain electrode are formed, whereby a bottom-gate transistor can be manufactured.

10 [0018]

In addition, according to an embodiment of the present invention, a semiconductor device includes a thin film transistor which has the following: an oxide semiconductor stack including a single-component oxide semiconductor layer including single crystal regions and a multi-component oxide semiconductor layer including single crystal regions, a gate electrode, a gate insulating layer provided between the oxide semiconductor stack and the gate electrode, and a wiring electrically connected to 20 the oxide semiconductor stack.

25 [0019]

Heat treatment for forming the single-component oxide semiconductor layer including single crystal regions and heat treatment for forming the multi-component oxide semiconductor layer including single crystal regions are preferably performed in an atmosphere containing almost no hydrogen and moisture (e.g., a nitrogen atmosphere, an oxygen atmosphere, or a dry-air atmosphere). Through the heat treatment, dehydration or dehydrogenation for eliminating hydrogen, water, hydroxyl group, hydride, or the like from the single-component oxide semiconductor layer and the multi-component oxide semiconductor layer can be performed, whereby the 30 single-component oxide semiconductor layer including single crystal regions and the multi-component oxide semiconductor layer including single crystal regions can be highly purified. The heat treatment can be performed in the following manner: the

temperature is increased in an inert gas atmosphere and then the atmosphere is switched during the process to an atmosphere containing oxygen. In the case where the heat treatment is performed in an oxygen atmosphere, the oxide semiconductor layer is oxidized, whereby an oxygen defect can be repaired. Even when measurement using 5 thermal desorption spectroscopy (TDS) is performed at up to 450 °C on the oxide semiconductor layer including single crystal regions subjected to the heat treatment, at least a peak of water at around 300 °C among two peaks of water is not detected.

[0020]

When the multi-component oxide semiconductor layer including single crystal regions contains In, in flat-plate-shaped single crystal regions, electron clouds of In overlap with each other to be connected to each other, whereby electrical conductivity  $\sigma$  is increased. Therefore, field-effect mobility of the transistor can be increased.

[0021]

The single crystal regions which are formed at the surface of the single-component oxide semiconductor layer and in which crystals are aligned in the same crystal direction is formed in such a manner that crystal growth is carried out from the surface in a depth direction; accordingly, the single crystal regions can be formed without being influenced by a base component of the single-component oxide semiconductor layer.

[0022]

In the highly purified single-component oxide semiconductor including single crystal regions and the highly purified multi-component oxide semiconductor including single crystal regions, the hydrogen concentration is lower than or equal to  $1 \times 10^{18}$  cm<sup>-3</sup>, preferably lower than or equal to  $1 \times 10^{16}$  cm<sup>-3</sup>, more preferably substantially 0; 25 the carrier density is lower than  $1 \times 10^{14}$  cm<sup>-3</sup>, preferably lower than  $1 \times 10^{12}$  cm<sup>-3</sup>, more preferably lower than  $1.45 \times 10^{10}$  cm<sup>-3</sup>, which is lower than or equal to the lower limit of measurement; and the band gap is greater than or equal to 2 eV, preferably greater than or equal to 2.5 eV, more preferably greater than or equal to 3 eV.

[0023]

30 Note that a transistor according to an embodiment of the present invention includes an insulated-gate field-effect transistor (IGFET) and a thin film transistor

(TFT) in its category.

[0024]

A transistor having high field-effect mobility can be manufactured and a large-sized display device, a high-performance semiconductor device, and the like are realized even when a material of a substrate serving as a base is any material such as an oxide, a nitride, or metal.

#### BRIEF DESCRIPTION OF DRAWINGS

[0025]

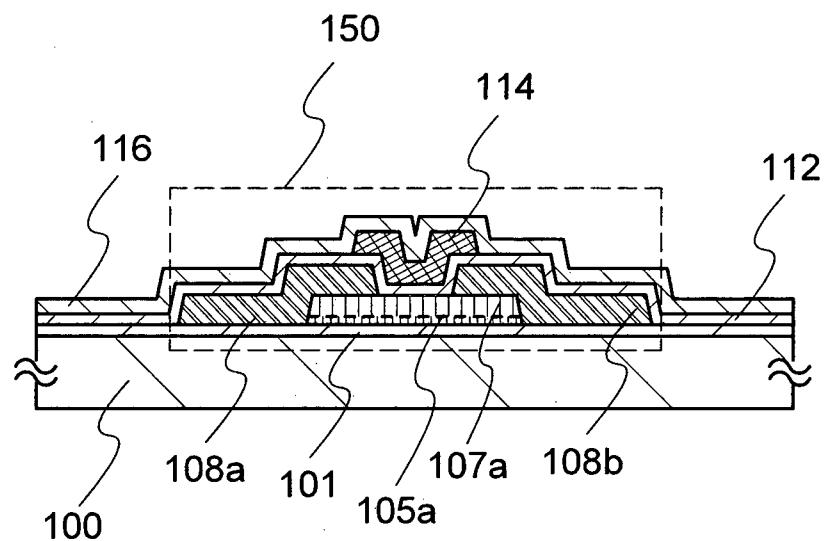

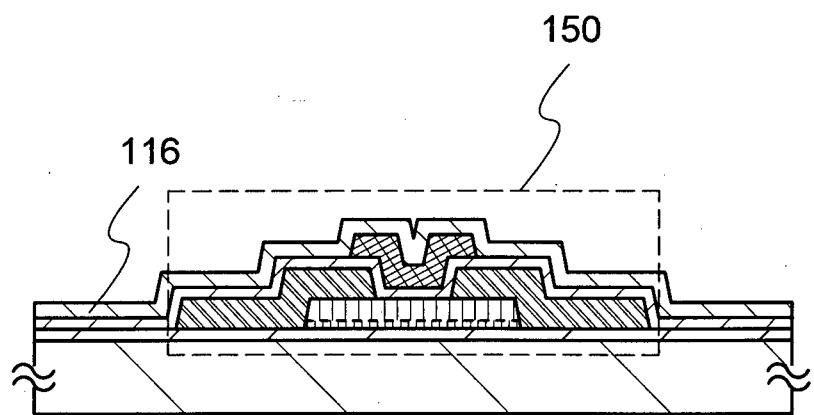

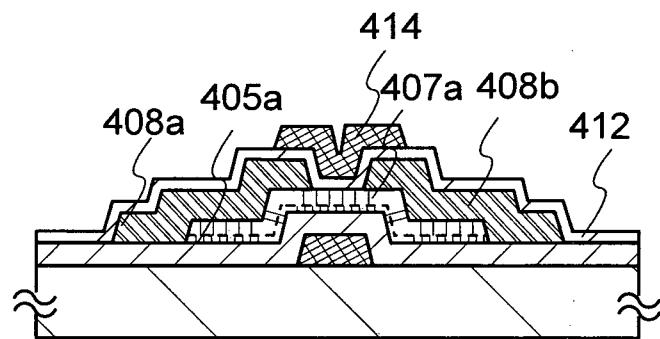

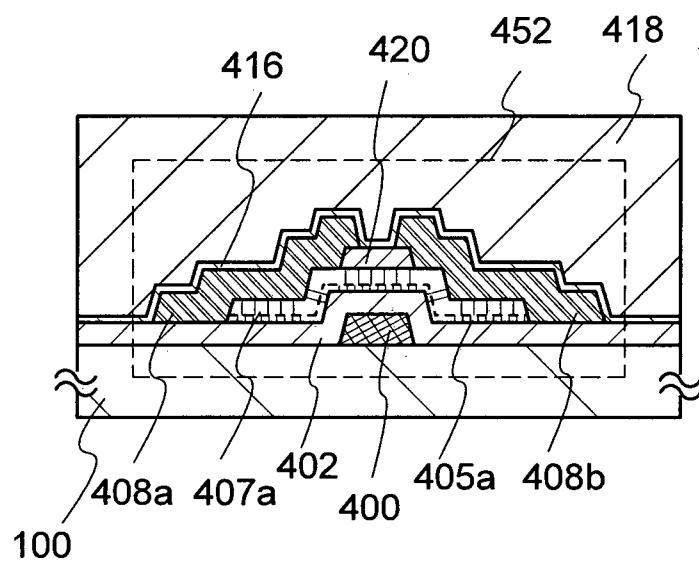

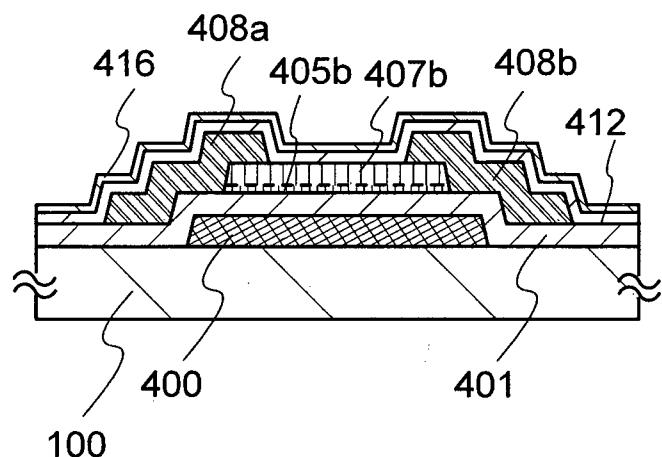

10 FIG. 1 is a cross-sectional view illustrating a semiconductor device according to an embodiment of the present invention.

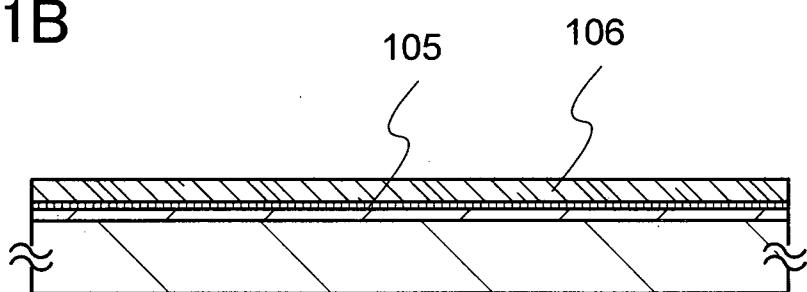

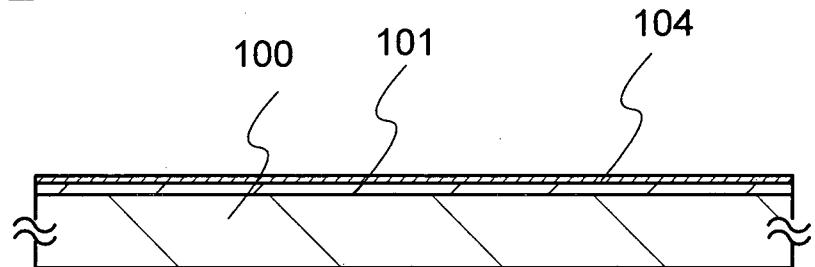

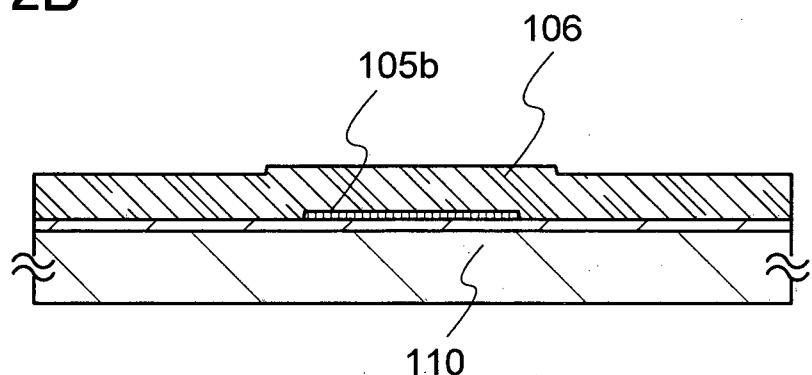

FIGS. 2A to 2E are cross-sectional views illustrating a process for manufacturing a semiconductor device according to an embodiment of the present invention.

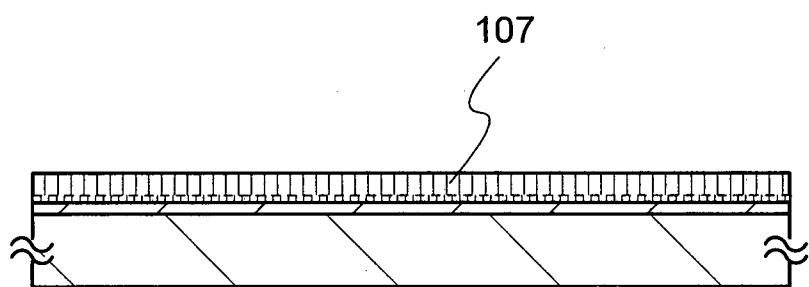

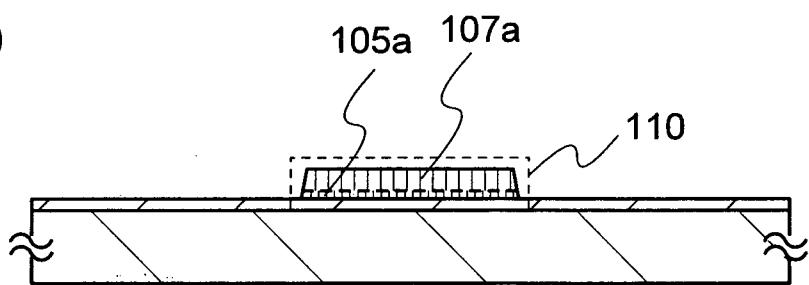

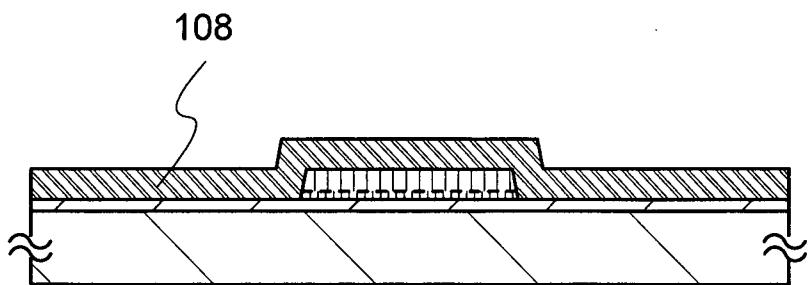

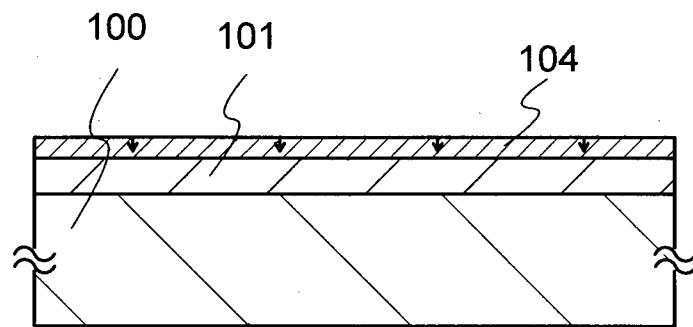

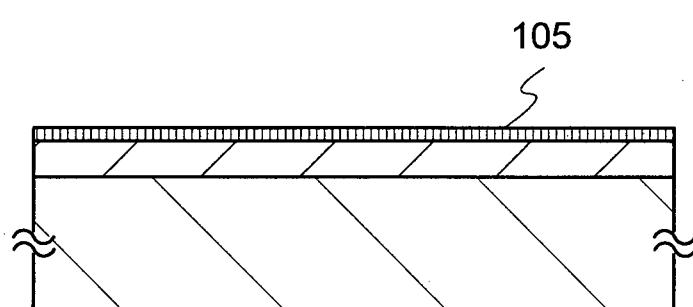

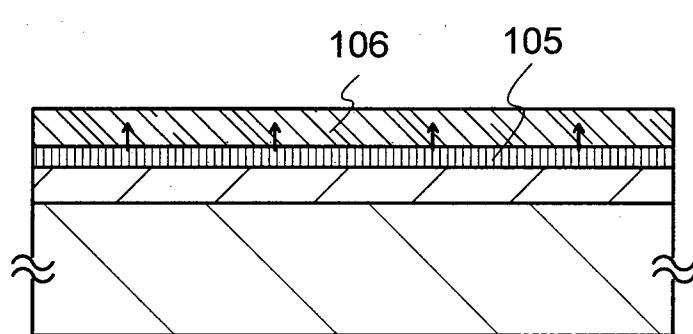

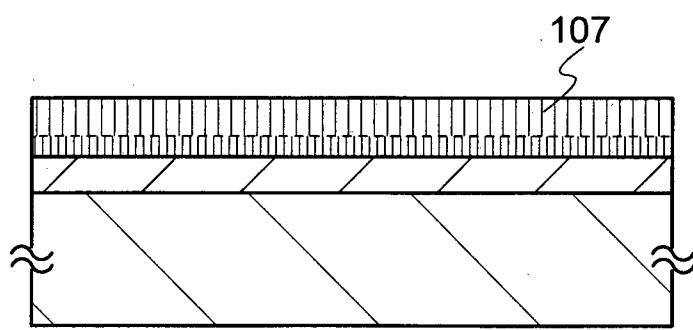

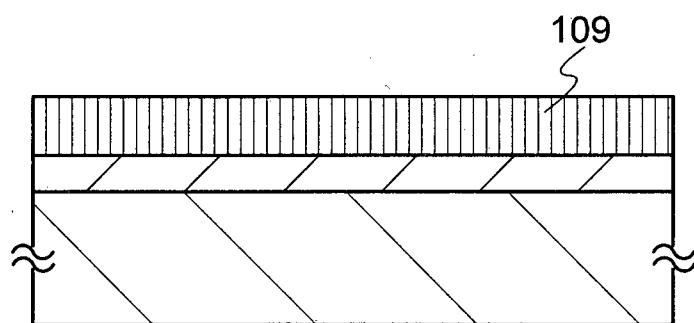

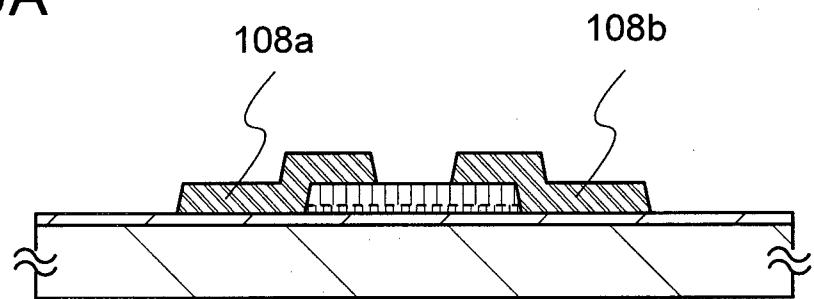

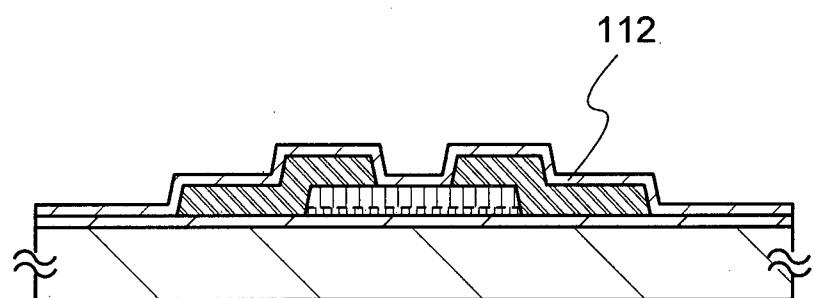

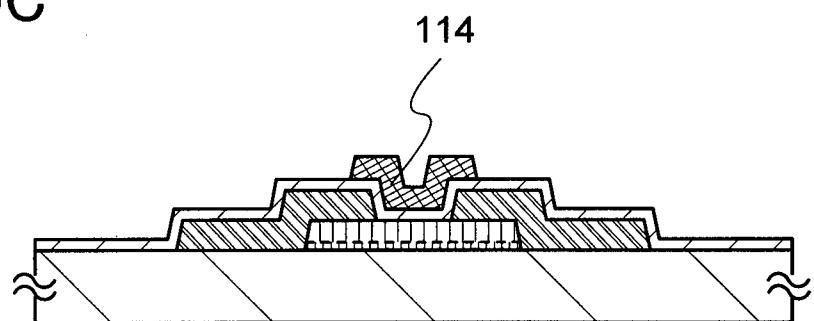

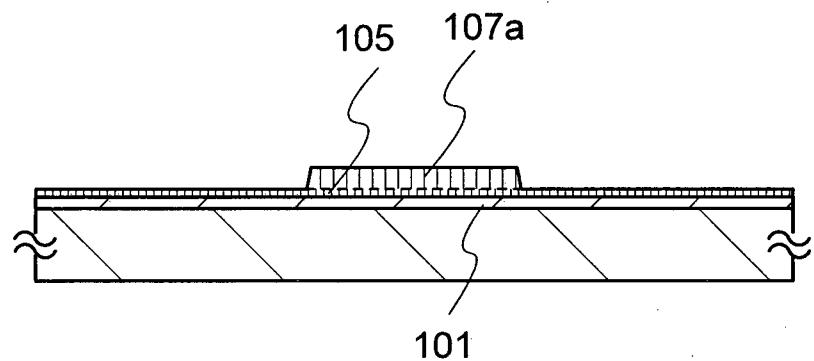

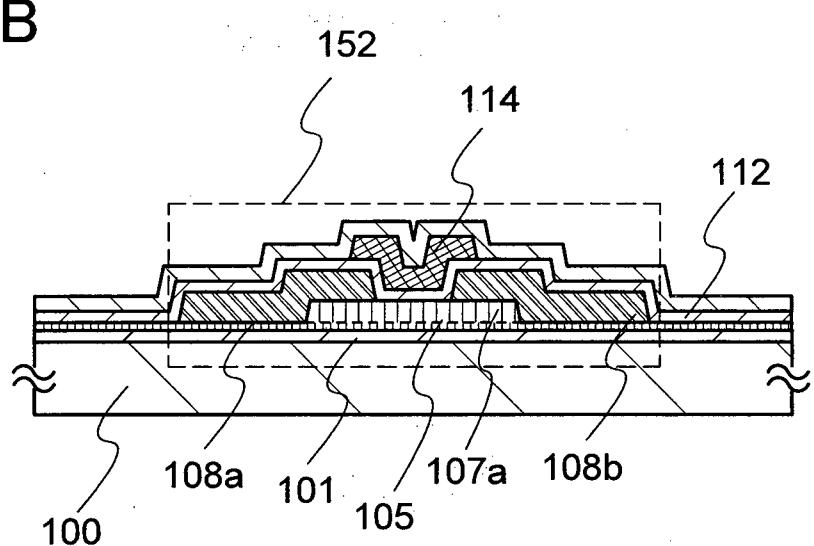

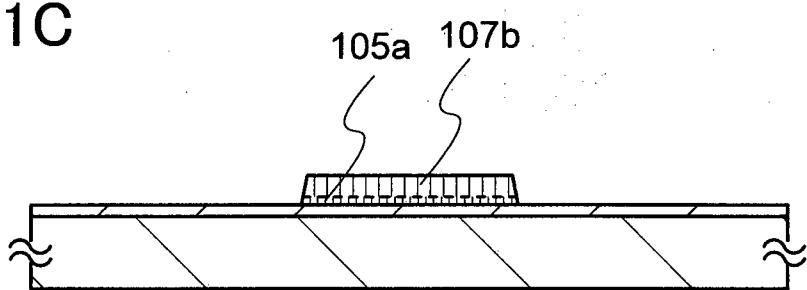

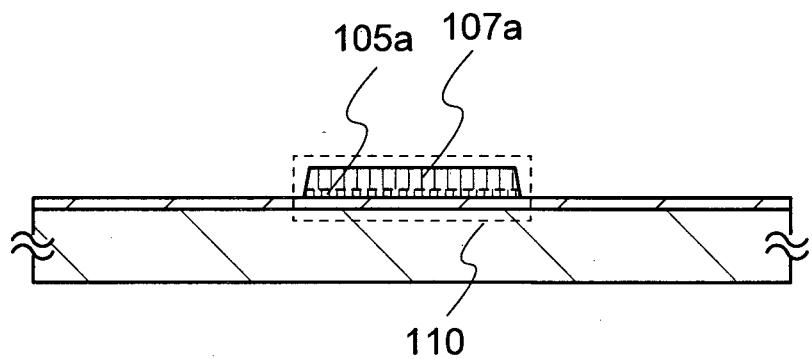

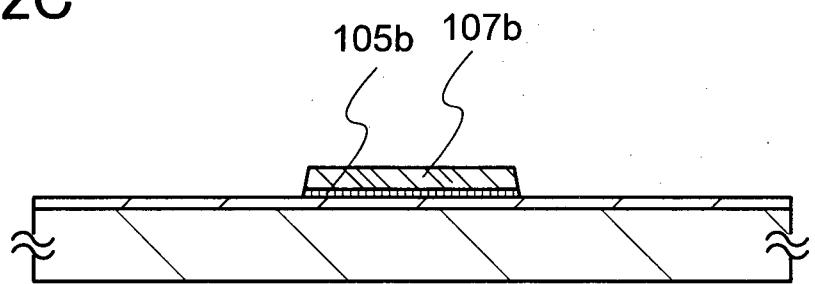

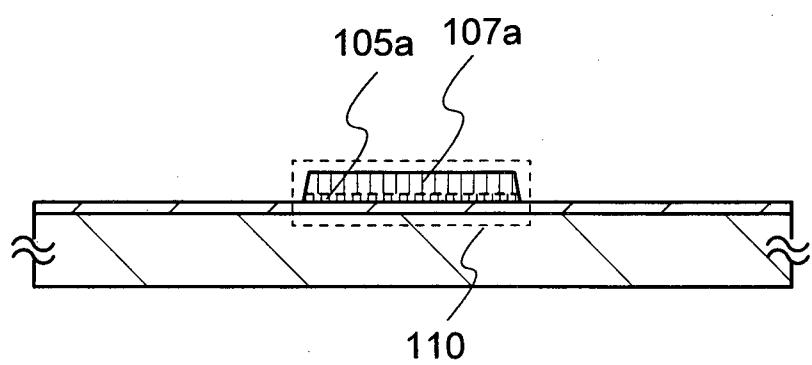

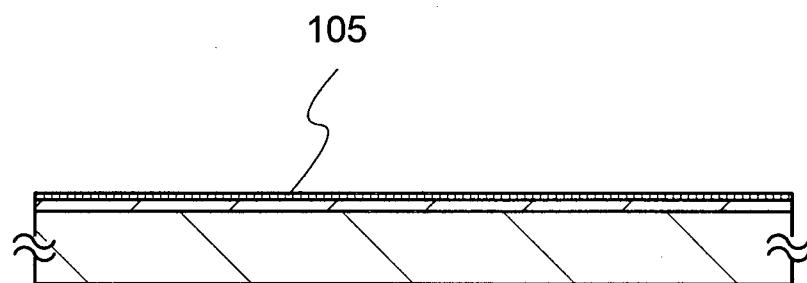

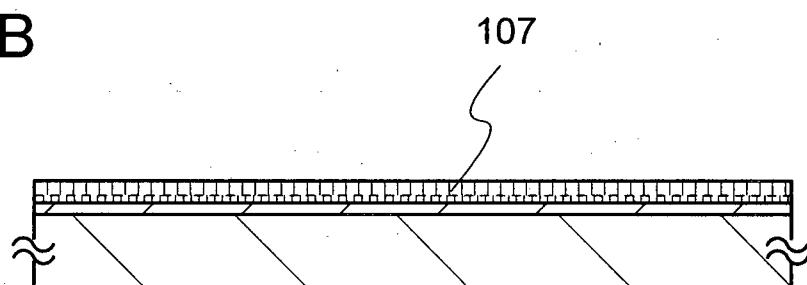

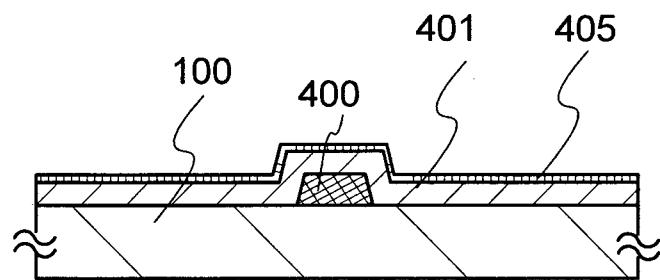

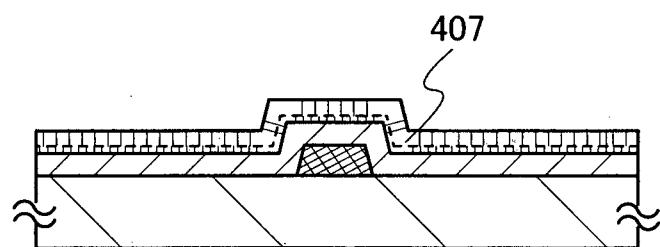

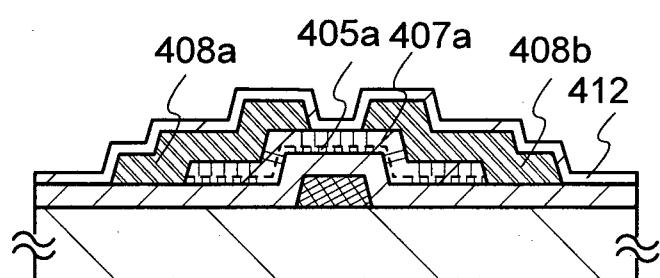

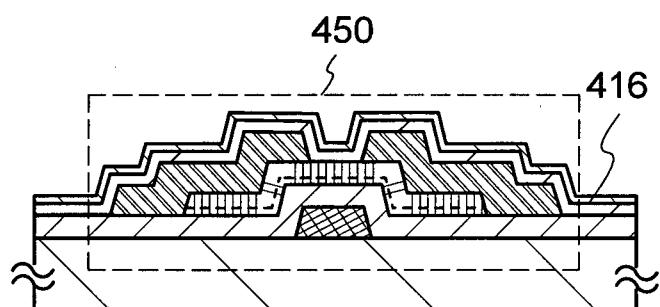

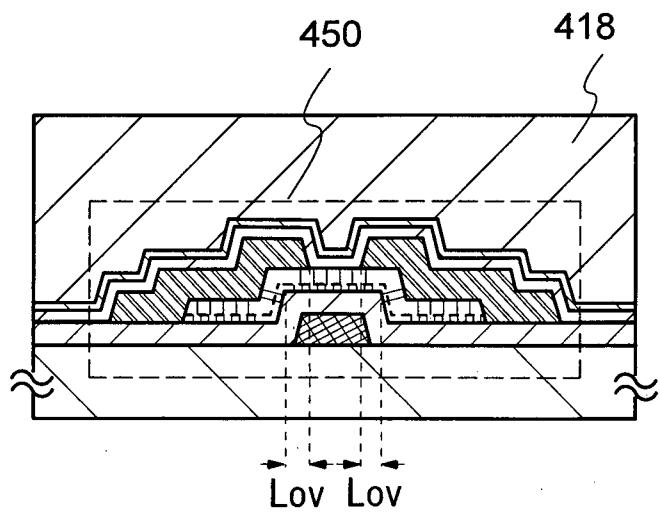

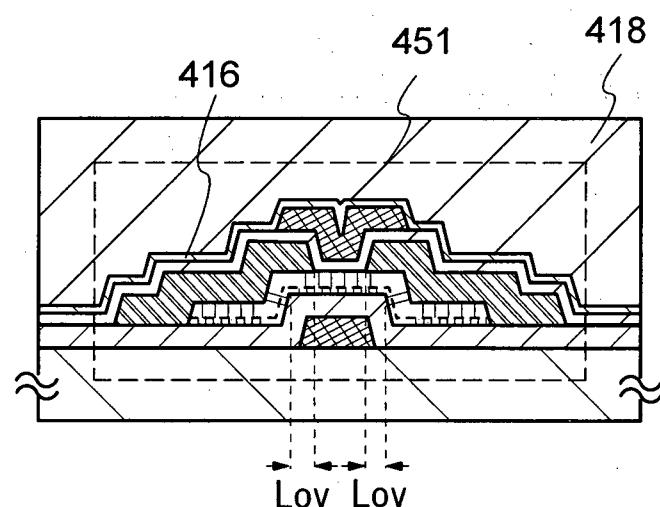

15 FIGS. 3A to 3D are cross-sectional views illustrating a process for manufacturing a semiconductor device according to an embodiment of the present invention.

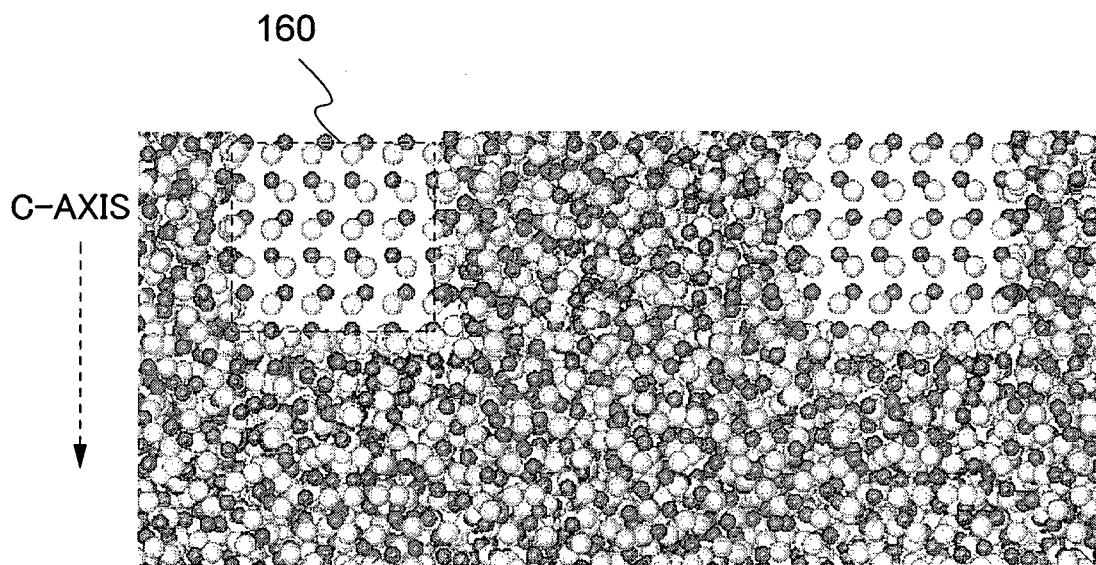

FIG. 4 is a diagram illustrating a process of crystal growth of an oxide semiconductor layer.

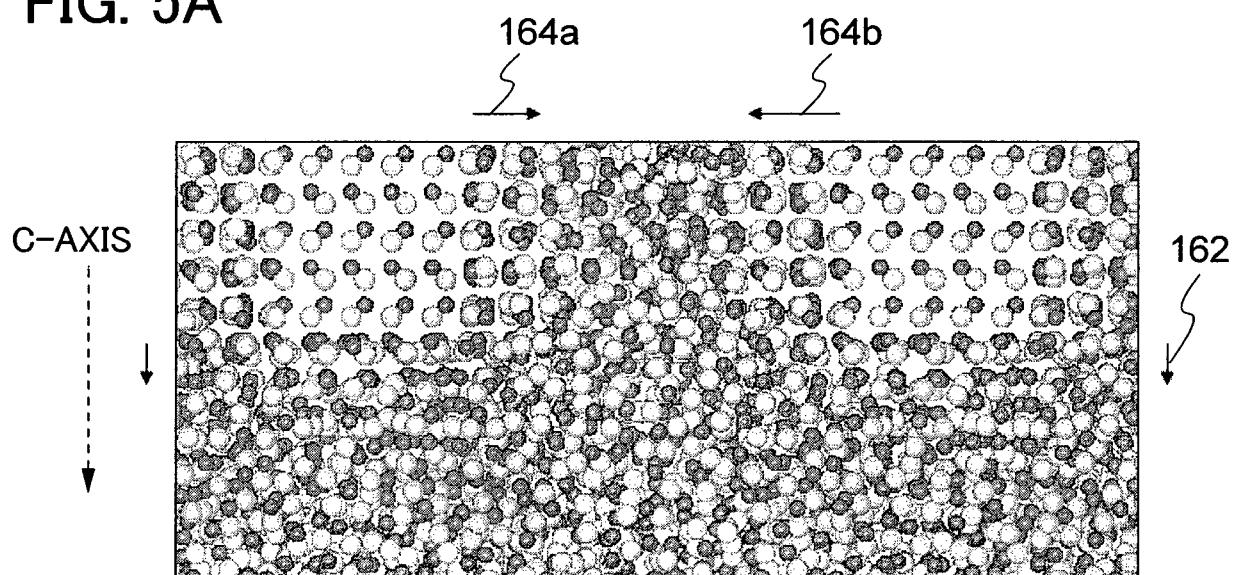

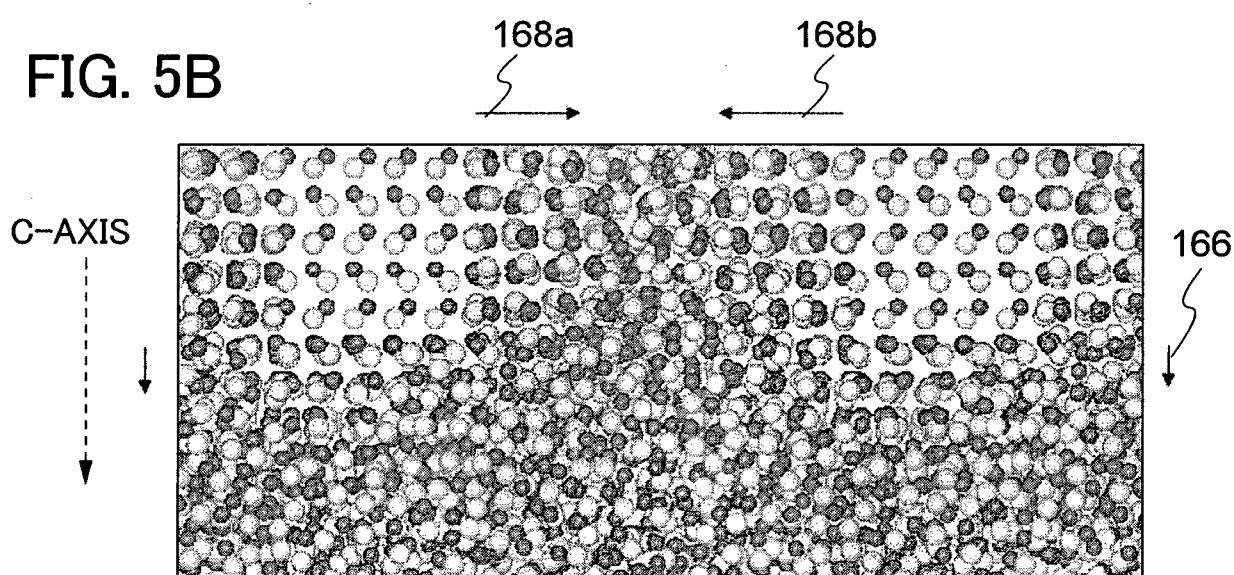

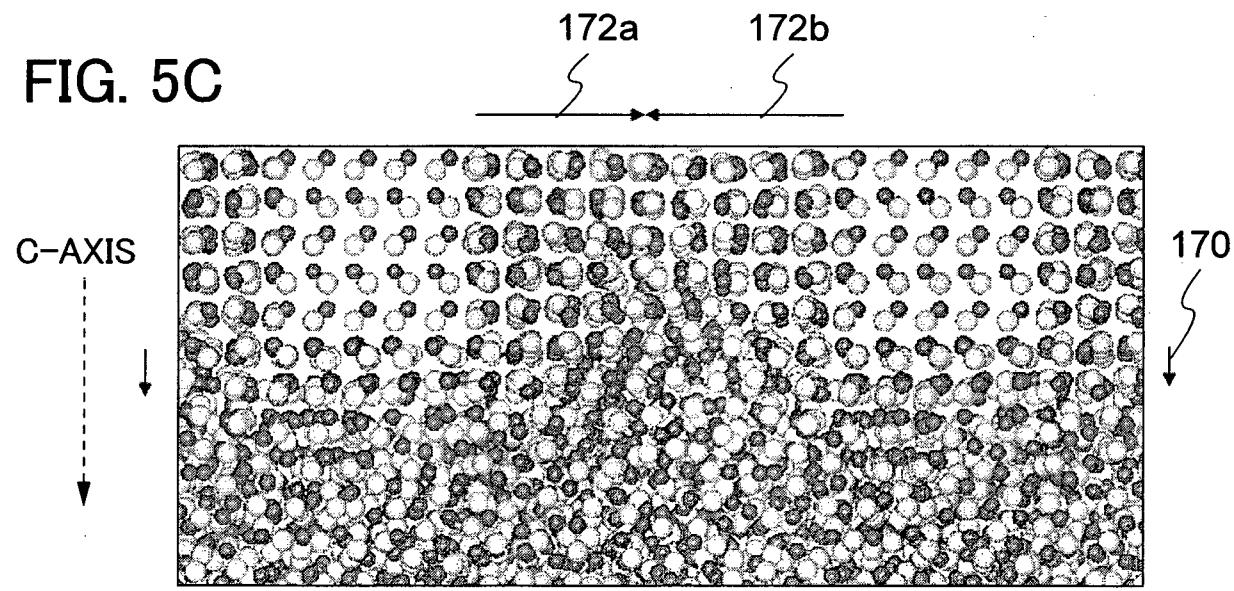

20 FIGS. 5A to 5C are diagrams each illustrating a process of crystal growth of an oxide semiconductor layer.

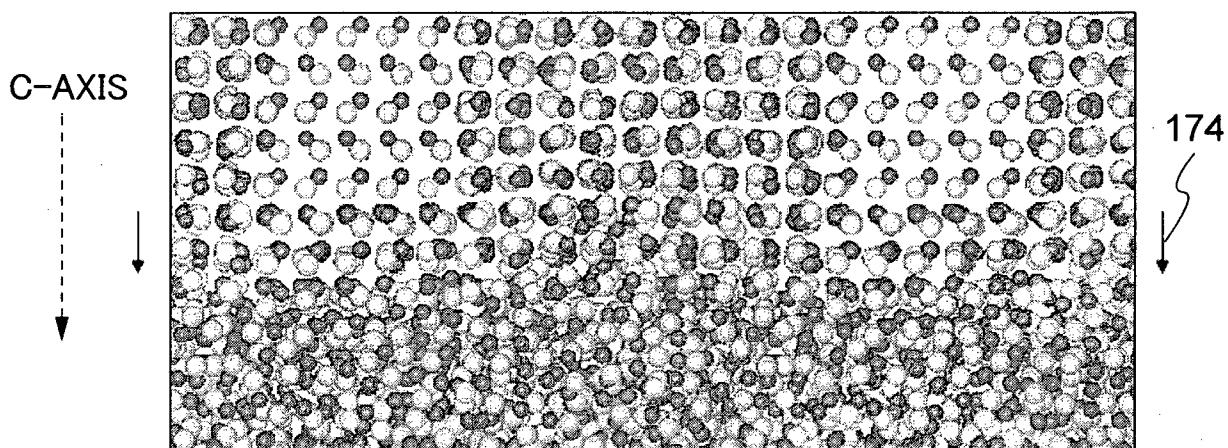

FIGS. 6A and 6B are diagrams each illustrating a process of crystal growth of an oxide semiconductor layer.

25 FIGS. 7A to 7C are diagrams each illustrating a crystal structure of an oxide semiconductor.

FIG. 8 is a cross-sectional view illustrating a process for manufacturing a semiconductor device according to an embodiment of the present invention.

30 FIGS. 9A to 9D are cross-sectional views illustrating a process for manufacturing a semiconductor device according to an embodiment of the present invention.

FIGS. 10A and 10B are cross-sectional views illustrating a semiconductor device according to an embodiment of the present invention.

FIGS. 11A to 11D are cross-sectional views illustrating a process for manufacturing a semiconductor device according to an embodiment of the present invention.

5 FIGS. 12A to 12D are cross-sectional views illustrating a process for manufacturing a semiconductor device according to an embodiment of the present invention.

FIGS. 13A and 13B are cross-sectional views illustrating a process for manufacturing a semiconductor device according to an embodiment of the present invention.

10 FIGS. 14A to 14E are cross-sectional views illustrating a process for manufacturing a semiconductor device according to an embodiment of the present invention.

15 FIGS. 15A and 15B are cross-sectional views illustrating a process for manufacturing a semiconductor device according to an embodiment of the present invention.

FIG. 16 is a cross-sectional view illustrating a process for manufacturing a semiconductor device according to an embodiment of the present invention.

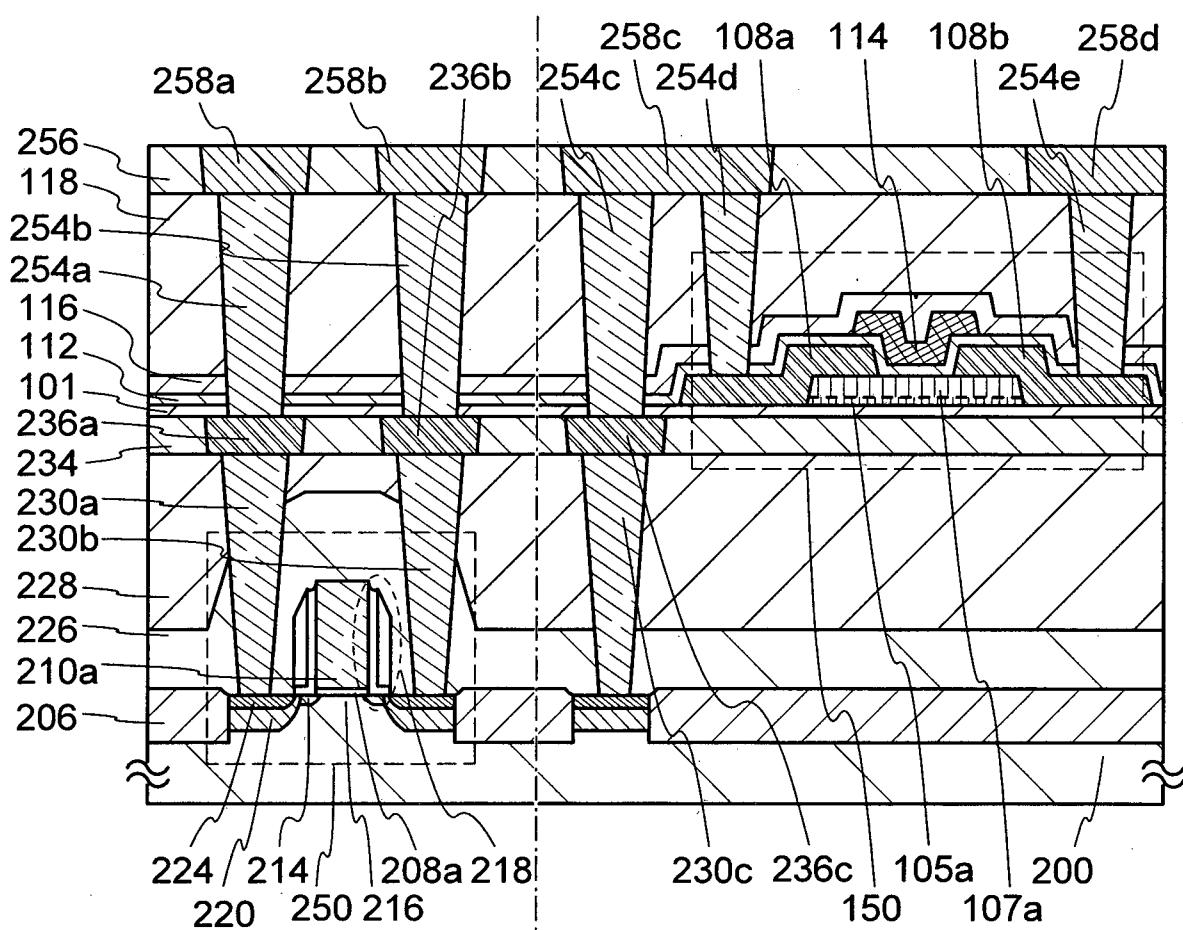

FIG. 17 is a cross-sectional view illustrating a semiconductor device according to an embodiment of the present invention.

20 FIG. 18 is a cross-sectional view illustrating a semiconductor device according to an embodiment of the present invention.

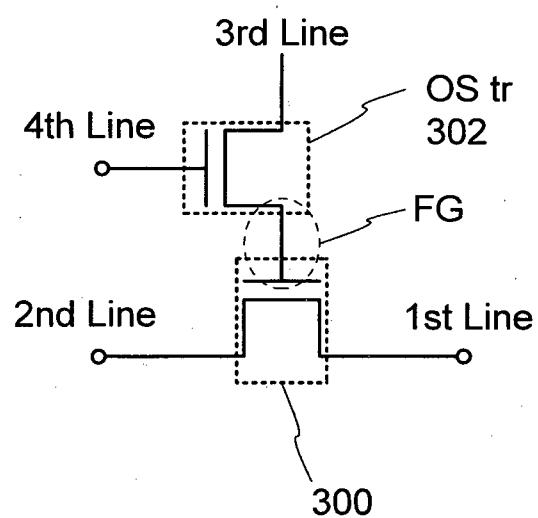

FIG. 19 is an equivalent circuit diagram illustrating a semiconductor device according to an embodiment of the present invention.

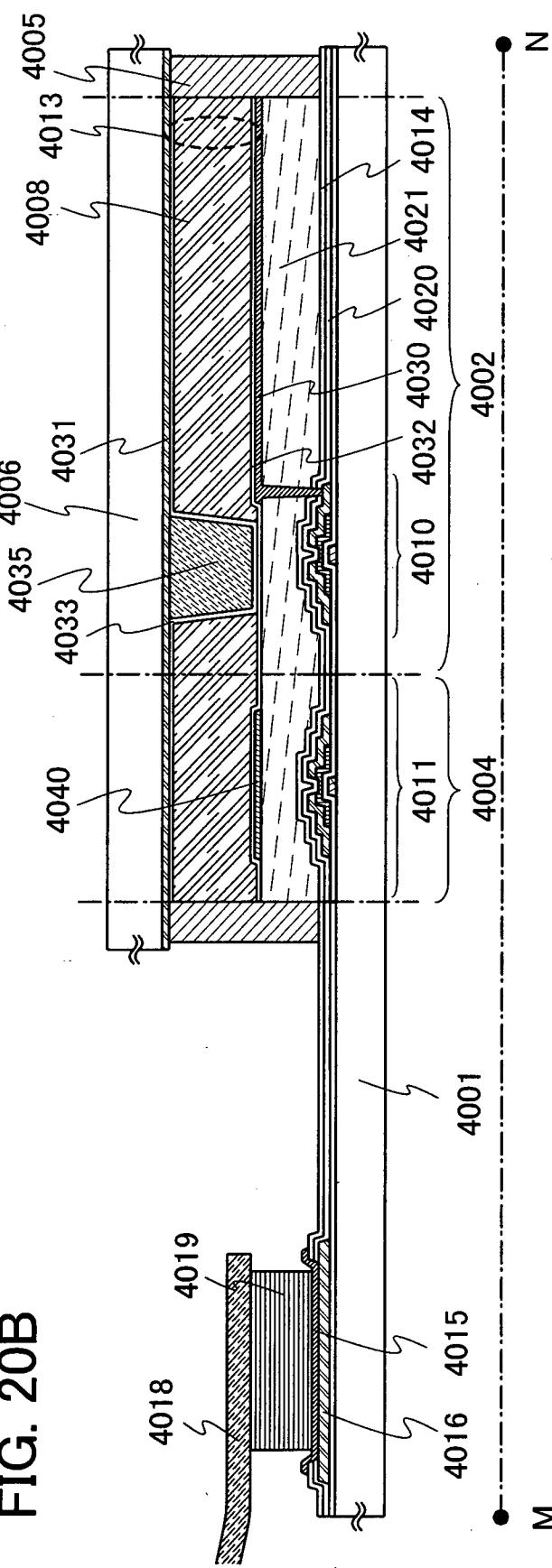

25 FIGS. 20A and 20B are a top view and a cross-sectional view illustrating a semiconductor device according to an embodiment of the present invention.

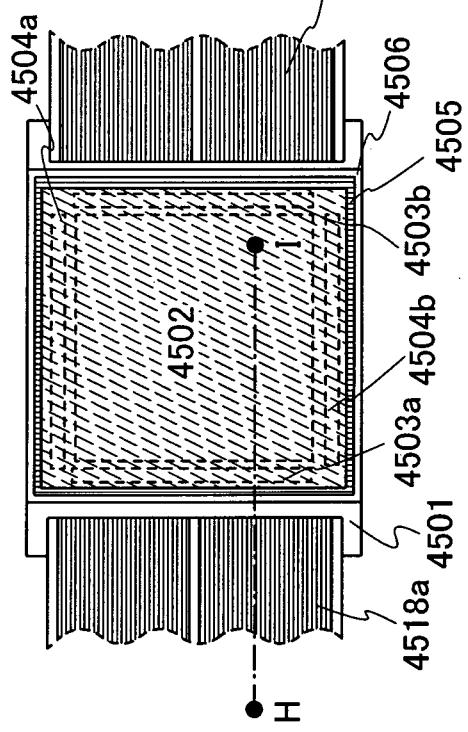

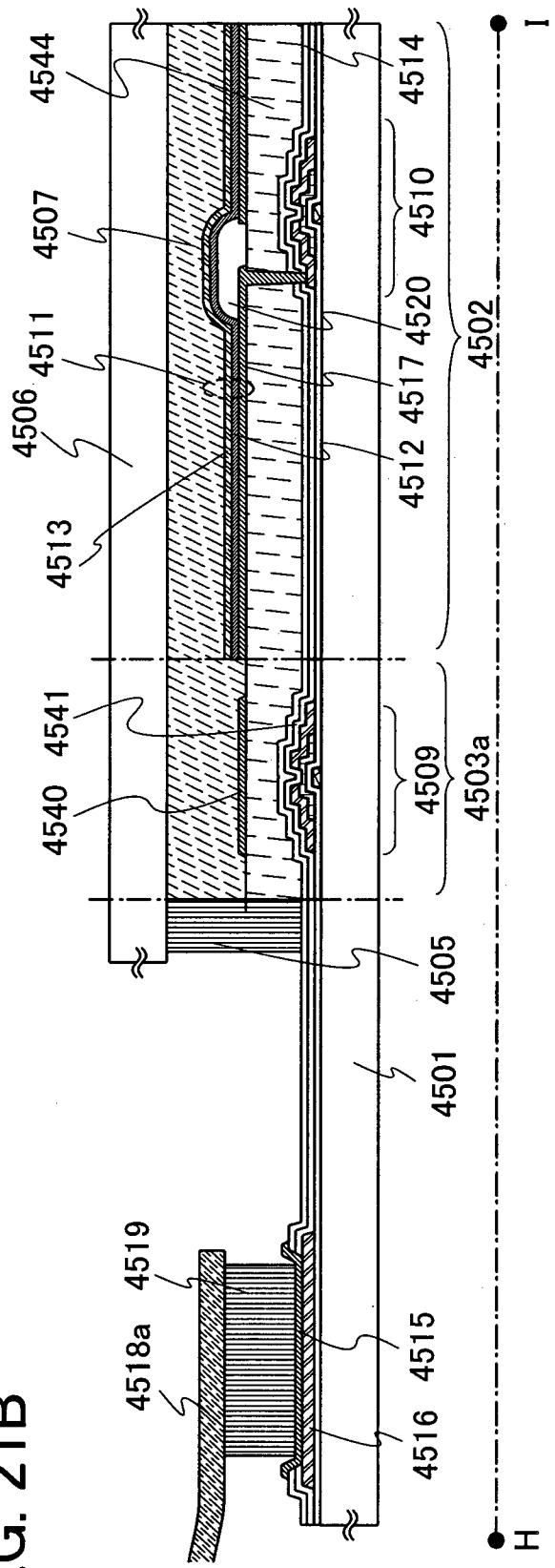

FIGS. 21A and 21B are a top view and a cross-sectional view illustrating a semiconductor device according to an embodiment of the present invention.

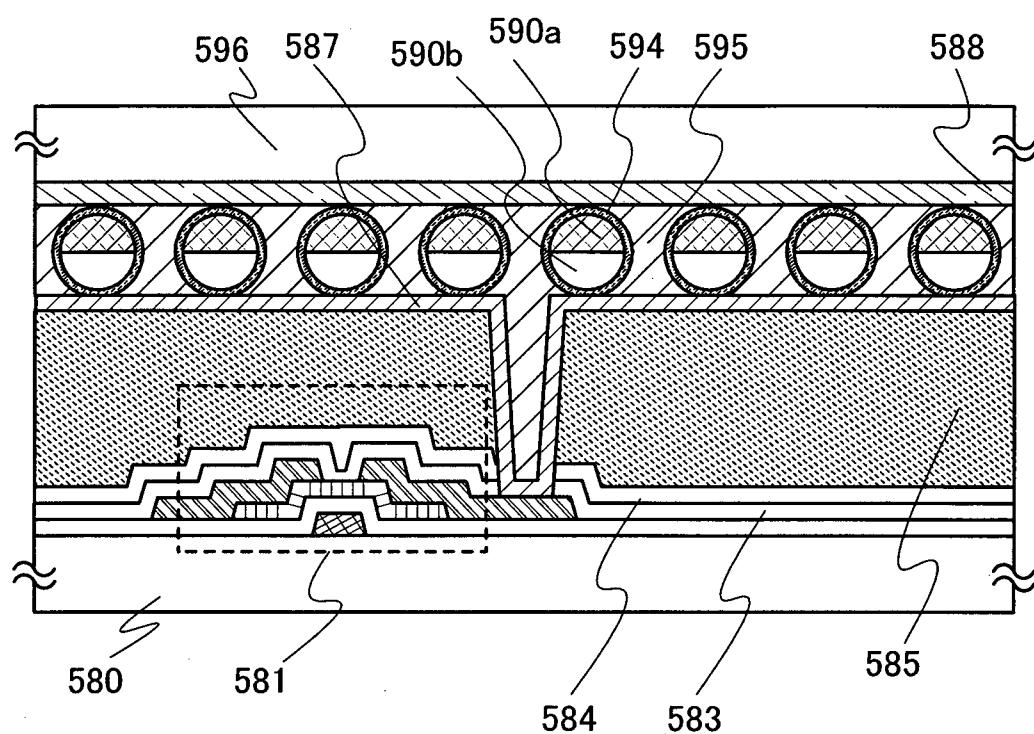

FIG. 22 is a cross-sectional view illustrating a semiconductor device according to an embodiment of the present invention.

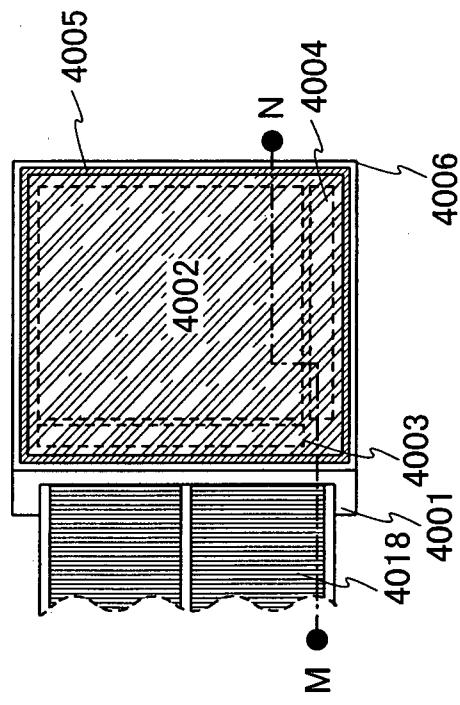

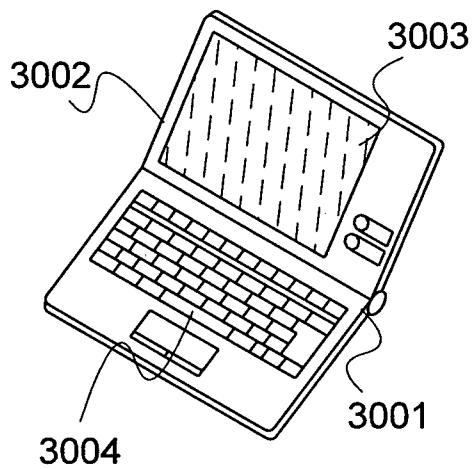

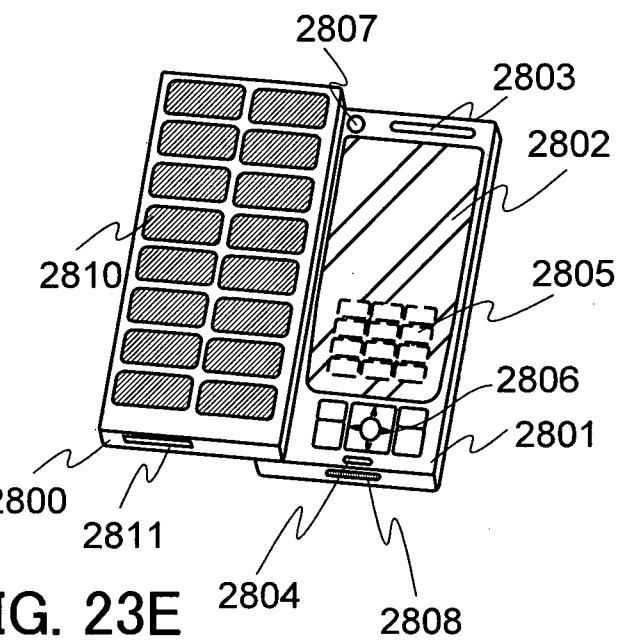

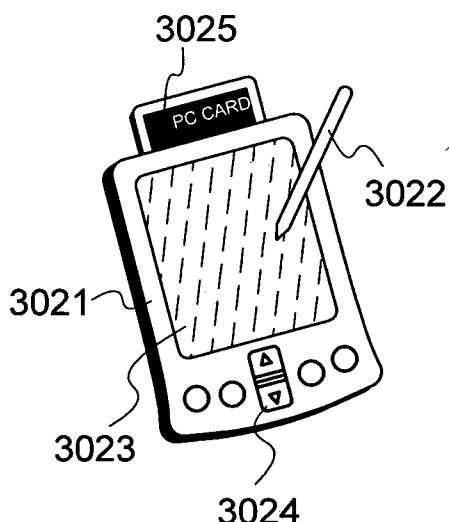

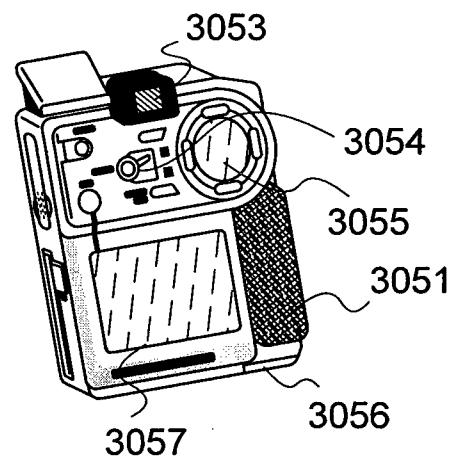

30 FIGS. 23A to 23E are diagrams each illustrating an embodiment of an electronic device.

FIG. 24 is a diagram illustrating an embodiment of an electronic device.

## BEST MODE FOR CARRYING OUT THE INVENTION

## [0026]

5 Embodiments of the present invention will be described in detail with reference to the accompanying drawings. Note that the present invention is not limited to the following description, and it will be easily understood by those skilled in the art that modes and details thereof can be changed in various ways without departing from the spirit and the scope of the present invention. Therefore, the present invention should not be construed as being limited to the description of the following embodiments.

10 Note that in the structures of the present invention described hereinafter, the same portions or portions having similar functions are denoted by the same reference numerals in different drawings, and description thereof is not repeated.

## [0027]

15 Note that in each drawing described in this specification, the size of each component or the thickness of each layer or the area is exaggerated in some cases for clarification. Therefore, embodiments of the present invention are not always limited to such scales.

## [0028]

20 Note that terms such as "first", "second", and "third" in this specification are used in order to avoid confusion between components and do not set a limitation on number. Therefore, for example, description can be made even when "first" is replaced with "second" or "third", as appropriate.

## [0029]

25 Note that "voltage" indicates a difference between potentials of two points, and "potential" indicates electrostatic energy (electrical potential energy) of a unit charge at a given point in an electrostatic field. Note that in general, a difference between a potential of one point and a reference potential (such as a ground potential) is merely called a potential or a voltage, and a potential and a voltage are used as synonymous words in many cases. Thus, in this specification, a potential may be rephrased as a voltage and a voltage may be rephrased as a potential unless otherwise specified.

## [0030]

(Embodiment 1)

In this embodiment, a structure and a manufacturing method of a semiconductor device according to an embodiment of the invention disclosed herein will be described with reference to FIG. 1, FIGS. 2A to 2E, FIGS. 3A to 3D, FIG. 4, FIGS. 5A to 5C, FIGS. 6A and 6B, FIGS. 7A to 7C, FIG. 8, and FIGS. 9A to 9D.

5 [0031]

FIG. 1 is a cross-sectional view illustrating a transistor 150 which is an embodiment of a structure of a semiconductor device. Note that although the transistor 150 described here is an n-channel IGFET (insulated-gate field-effect transistor) whose carriers are electrons, the transistor 150 may be a p-channel IGFET.

10 In this embodiment, the transistor 150 having a top gate structure is described.

[0032]

In the transistor 150 illustrated in FIG. 1, a single-component oxide semiconductor layer 105a including single crystal regions and a multi-component oxide semiconductor layer 107a including single crystal regions are stacked over an insulating layer 101 formed over a substrate 100, and wirings 108a and 108b functioning as a source electrode and a drain electrode are formed thereover. In addition, a gate insulating layer 112 is formed over the multi-component oxide semiconductor layer 107a including single crystal regions and the wirings 108a and 108b, and a gate electrode 114 is formed in a region over the gate insulating layer 112 so as to face the single-component oxide semiconductor layer 105a including single crystal regions and the multi-component oxide semiconductor layer 107a including single crystal regions with the gate insulating layer 112 provided therebetween. An insulating layer 116 is formed over the gate insulating layer 112 and the gate electrode 114.

[0033]

25 A method for manufacturing the transistor 150 illustrated in FIG. 1 is described with reference to FIGS. 2A to 2E, FIGS. 3A to 3D, FIG. 4, FIGS. 5A to 5C, FIGS. 6A and 6B, FIGS. 7A to 7C, and FIG. 8.

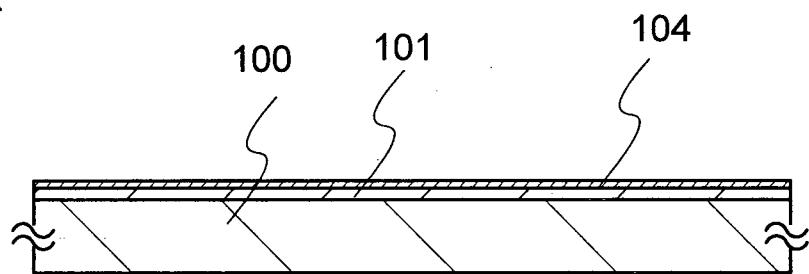

[0034]

30 The insulating layer 101 is formed over the substrate 100. Then, a single-component oxide semiconductor layer 104 is formed over the insulating layer 101 (see FIG. 2A).

[0035]

It is necessary that the substrate 100 at least has enough heat resistance to heat treatment performed later. When a glass substrate is used as the substrate 100, a glass substrate whose strain point is higher than or equal to 730 °C is preferably used. As the glass substrate, for example, a glass material such as aluminosilicate glass, 5 aluminoborosilicate glass, or barium borosilicate glass is used. Note that a glass substrate containing BaO and B<sub>2</sub>O<sub>3</sub> so that the amount of BaO is larger than that of B<sub>2</sub>O<sub>3</sub> is preferably used.

[0036]

Instead of the glass substrate, a substrate formed of an insulator, such as a 10 ceramic substrate, a quartz substrate, or a sapphire substrate can be used. Alternatively, crystallized glass or the like can be used. Further alternatively, a substrate obtained by forming an insulating layer over a surface of a semiconductor substrate such as a silicon wafer or a surface of a conductive substrate formed of a metal material can be used.

[0037]

15 The insulating layer 101 is provided so as to reduce entry of an impurity into a layer formed over the substrate 100 and to enhance adhesion to the layer formed over the substrate 100. The insulating layer 101 is formed using an oxide insulating layer such as a silicon oxide layer or a silicon oxynitride layer, or a nitride insulating layer such as a silicon nitride layer, a silicon nitride oxide layer, an aluminum nitride layer, or 20 an aluminum nitride oxide layer. In addition, the insulating layer 101 may have a stacked structure, for example, a stacked structure in which one or more of the above nitride insulating layers and one or more of the above oxide insulating layers are stacked in that order over the substrate 100. There is no particular limitation on the thickness of the insulating layer 101; the insulating layer 101 can have a thickness of 10 nm to 25 500 nm inclusive, for example. The insulating layer 101 is not an essential component; therefore, a structure in which the insulating layer 101 is not provided is also possible.

[0038]

30 The insulating layer 101 can be formed by a sputtering method, a CVD method, a coating method, a printing method, or the like.

[0039]

Note that when the insulating layer 101 is formed by a sputtering method, the

insulating layer 101 is preferably formed while hydrogen, water, hydroxyl group, hydride, or the like remaining in a treatment chamber is removed. This is for preventing hydrogen, water, hydroxyl group, hydride, or the like from being contained in the insulating layer 101. It is preferable to use an entrapment vacuum pump in order 5 to remove hydrogen, water, hydroxyl group, hydride, or the like remaining in the treatment chamber. As the entrapment vacuum pump, for example, a cryopump, an ion pump, or a titanium sublimation pump is preferably used. An evacuation unit may be a turbo pump provided with a cold trap. Hydrogen, water, hydroxyl group, hydride, or the like is removed from the treatment chamber which is evacuated with a cryopump; 10 thus, when the insulating layer 101 is formed in the treatment chamber, the concentration of impurities contained in the insulating layer 101 can be reduced.

[0040]

In addition, it is preferable to use a high-purity gas from which impurities such 15 as hydrogen, water, hydroxyl group, or hydride are removed to a concentration of several ppm or several ppb, as a sputtering gas which is used when the insulating layer 101 is formed.

[0041]

Examples of a sputtering method include an RF sputtering method in which a high-frequency power source is used as a sputtering power source, a DC sputtering 20 method, and a pulsed DC sputtering method in which a bias is applied in a pulsed manner. An RF sputtering method is mainly used in the case where an insulating layer is formed, and a DC sputtering method is mainly used in the case where a metal layer is formed.

[0042]

25 In this embodiment, the substrate 100 is transferred to the treatment chamber, a sputtering gas containing high-purity oxygen, from which hydrogen, water, hydroxyl group, hydride, or the like is removed, is introduced into the treatment chamber, and a silicon oxide layer is formed as the insulating layer 101 over the substrate 100 using a silicon target. Note that when the insulating layer 101 is formed, the substrate 100 30 may be heated.

[0043]

The single-component oxide semiconductor layer 104 is formed over the

substrate 100 and the insulating layer 101 by a sputtering method or the like.

[0044]

The single-component oxide semiconductor layer 104 can be formed by a sputtering method in a rare gas (typically argon) atmosphere, an oxygen atmosphere, or 5 an atmosphere containing a rare gas (typically argon) and oxygen.

[0045]

In addition, in a manner similar to that of the insulating layer 101, hydrogen, water, hydroxyl group, hydride, or the like remaining in a sputtering apparatus is preferably removed before, during, or after the formation of the single-component oxide 10 semiconductor layer 104. In order to remove residual moisture from the sputtering apparatus, an entrapment vacuum pump is preferably used. As a result, hydrogen, water, hydroxyl group, hydride, or the like is removed, so that the concentration of impurities contained in the single-component oxide semiconductor layer 104 can be reduced.

15 [0046]

Preheat treatment is preferably performed before the single-component oxide semiconductor layer 104 is formed, in order to remove hydrogen, water, hydroxyl group, hydride, or the like which remains on the inner wall of the sputtering apparatus, on a surface of a target, or inside a target material. As the preheat treatment, a method in 20 which the inside of the chamber is heated to 200 °C to 600 °C under reduced pressure, a method in which introduction and removal of nitrogen or an inert gas are repeated, and the like can be given. After the preheat treatment, the substrate or the sputtering apparatus is cooled. Then, the single-component oxide semiconductor layer 104 is formed without exposure to the air. In this case, not water but oil or the like is 25 preferably used as a coolant for the target. Although a certain level of effect can be obtained when introduction and removal of nitrogen or an inert gas are repeated without performing heating, it is more preferable to perform the above treatment while performing heating.

[0047]

30 When the single-component oxide semiconductor layer 104 is formed by a sputtering method, by setting the substrate temperature to 100 °C to 600 °C inclusive,

preferably 200 °C to 400 °C inclusive, impurities such as hydrogen, water, hydroxyl group, or hydride contained in the single-component oxide semiconductor layer 104 can be reduced, and crystal growth can be promoted in first heat treatment performed later.

[0048]

5 The relative density of an oxide semiconductor in an oxide semiconductor target is greater than or equal to 80 %, preferably greater than or equal to 95 %, more preferably greater than or equal to 99.9 %. By using a target having high relative density, the impurity concentration in the single-component oxide semiconductor layer 104 which is formed can be reduced, and a transistor having excellent electric

10 characteristics or high reliability can be obtained.

[0049]

The single-component oxide semiconductor layer 104 is preferably formed using a single-component oxide semiconductor which can have a wurtzite crystal structure that is a hexagonal crystal structure by heating, typically, zinc oxide. Here,

15 the single-component oxide semiconductor means an oxide semiconductor including an oxide of one kind of metal. Note that the single-component oxide semiconductor may contain, as an impurity, an element other than the metal oxide at 1 %, preferably at 0.1 %. The single-component oxide semiconductor is more easily crystallized than the multi-component oxide semiconductor and the crystallinity can be enhanced. The

20 single-component oxide semiconductor layer 104 can be used as a seed crystal for crystal growth of a multi-component oxide semiconductor layer 106 formed later. Therefore, the single-component oxide semiconductor layer 104 may have a thickness with which crystal growth is possible, typically greater than or equal to a thickness of one atomic layer and less than or equal to 10 nm, preferably 2 nm to 5 nm inclusive.

25 When the single-component oxide semiconductor layer 104 is thin, throughput in deposition treatment and heat treatment can be improved.

[0050]

Next, the first heat treatment is performed. The temperature of the first heat treatment is 500 °C to 1000 °C inclusive, preferably 600 °C to 850 °C inclusive. In

30 addition, heating time is one minute to twenty four hours inclusive.

[0051]

After the temperature of the first heat treatment performed on the single-component oxide semiconductor layer 104 is gradually increased, the temperature may be set constant. When the speed for increasing the temperature from a temperature of higher than or equal to 500 °C is 0.5 °C/h to 3 °C/h inclusive, crystal growth of the single-component oxide semiconductor layer 104 is gradually carried out to form a single-component oxide semiconductor layer 105 including single crystal regions; thus, the crystallinity can be further enhanced. Note that the single-component oxide semiconductor layer 105 including single crystal regions has a wurtzite crystal structure that is a hexagonal crystal structure.

10 [0052]

The first heat treatment is preferably performed in a rare gas (typically, argon) atmosphere, an oxygen atmosphere, a nitrogen atmosphere, a dry air atmosphere, an atmosphere containing a rare gas (typically, argon) and oxygen, or an atmosphere containing a rare gas and nitrogen. Specifically, a high-purity gas atmosphere is preferably used, in which the concentration of impurities such as hydrogen, water, hydroxyl group, or hydride are reduced to several ppm or several ppb.

[0053]

In this embodiment, heat treatment in a dry air atmosphere at 700 °C for one hour is performed as the first heat treatment.

20 [0054]

Note that a heat treatment apparatus used for the first heat treatment is not limited to a particular apparatus, and the apparatus may be provided with a device for heating an object to be processed by heat radiation or heat conduction from a heating element such as a resistance heating element. For example, an electric furnace, or a rapid thermal annealing (RTA) apparatus such as a gas rapid thermal annealing (GRTA) apparatus or a lamp rapid thermal annealing (LRTA) apparatus can be used. An LRTA apparatus is an apparatus for heating an object to be processed by radiation of light (an electromagnetic wave) emitted from a lamp such as a halogen lamp, a metal halide lamp, a xenon arc lamp, a carbon arc lamp, a high pressure sodium lamp, or a high pressure mercury lamp. A GRTA apparatus is an apparatus for heat treatment using a high-temperature gas.

## [0055]

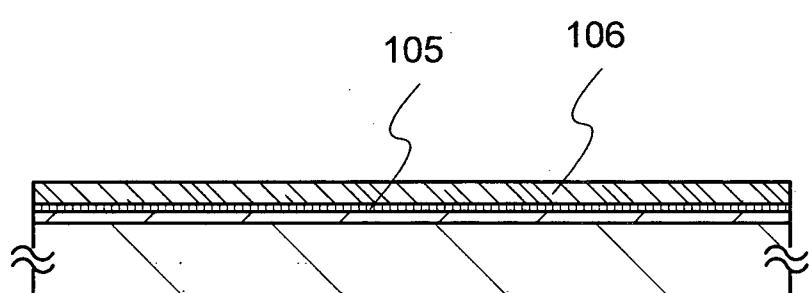

Next, as illustrated in FIG. 2B, the multi-component oxide semiconductor layer 106 is formed over the single-component oxide semiconductor layer 105 including single crystal regions. The multi-component oxide semiconductor layer 106 can have a non-wurtzite crystal structure that is a hexagonal crystal structure by heating. The non-wurtzite crystal structure that is a hexagonal crystal structure is also called a homologous structure. Note that the non-wurtzite crystal structure is a crystal structure which is not a wurtzite type. The multi-component oxide semiconductor layer 106 can be formed by a method similar to that of the single-component oxide semiconductor layer 104. Note that the thickness of the multi-component oxide semiconductor layer 106 may be determined as appropriate in accordance with a device to be manufactured, by a practitioner. For example, the total thickness of the single-component oxide semiconductor layer 104 and the multi-component oxide semiconductor layer 106 is 10 nm to 200 nm inclusive.

## [0056]

As the multi-component oxide semiconductor layer 106, any of the following oxide semiconductor layers can be used: an In-Sn-Ga-Zn-O-based oxide semiconductor layer which is a four-component metal oxide layer; an In-Ga-Zn-O-based oxide semiconductor layer, an In-Sn-Zn-O-based oxide semiconductor layer, an In-Al-Zn-O-based oxide semiconductor layer, a Sn-Ga-Zn-O-based oxide semiconductor layer, an Al-Ga-Zn-O-based oxide semiconductor layer, and a Sn-Al-Zn-O-based oxide semiconductor layer which are three-component metal oxide layers; an In-Zn-O-based oxide semiconductor layer, a Sn-Zn-O-based oxide semiconductor layer, an Al-Zn-O-based oxide semiconductor layer, a Zn-Mg-O-based oxide semiconductor layer, a Sn-Mg-O-based oxide semiconductor layer, and an In-Mg-O-based oxide semiconductor layer which are two-component metal oxide layers; and the like. In this specification, the multi-component oxide semiconductor includes an oxide of plural kinds of metals, and *n*-component metal oxide includes an oxide of *n* kinds of metals. Note that the multi-component oxide semiconductor may contain, as an impurity, an element other than the metal oxide at 1 %, preferably at 0.1 %.

## [0057]

The multi-component oxide semiconductor layer 106 may be formed using a three-component metal oxide, and an oxide semiconductor material represented by  $\text{In}_x\text{Zn}_y\text{O}_z$  ( $Y = 0.5$  to  $5$ ) may be used. Here,  $M$  represents one or more kinds of elements selected from Group 13 elements such as gallium (Ga), aluminum (Al), and boron (B). Note that the contents of In,  $M$ , Zn, and O can be set freely, and the case where the  $M$  content is zero (that is,  $x = 0$ ) is included. The contents of In and Zn are not zero. In other words, the above-described expression includes an In-Ga-Zn-O-based oxide semiconductor, an In-Zn-O-based oxide semiconductor, and the like.

## [0058]

As a target used for forming the multi-component oxide semiconductor layer 106 by a sputtering method, a metal oxide target containing zinc can be used. For example, an oxide semiconductor target containing In, Ga, and Zn has a composition ratio of  $\text{In:Ga:Zn} = 1:x:y$  ( $x$  is greater than or equal to 0, and  $y$  is greater than or equal to 0.5 and less than or equal to 5). Specifically, a target having a composition ratio of  $\text{In:Ga:Zn} = 1:1:0.5$  [atomic ratio], a target having a composition ratio of  $\text{In:Ga:Zn} = 1:1:1$  [atomic ratio], a target having a composition ratio of  $\text{In:Ga:Zn} = 1:1:2$  [atomic ratio], or a target having a composition ratio of  $\text{In:Ga:Zn} = 1:0.5:2$  [atomic ratio] can be used. In this embodiment, since crystallization is intentionally caused by performing heat treatment in a later step, it is preferable to use an oxide semiconductor target by which crystallization is easily caused.

## [0059]

When the multi-component oxide semiconductor layer 106 is formed by a sputtering method, by heating the substrate, impurities such as hydrogen, water, hydroxyl group, or hydride contained in the multi-component oxide semiconductor layer 106 can be reduced, and crystal growth can be promoted in second heat treatment performed later.

## [0060]

The relative density of an oxide semiconductor in an oxide semiconductor target is greater than or equal to 80 %, preferably greater than or equal to 95 %, more

preferably greater than or equal to 99.9 %. By using a target having high relative density, the impurity concentration in the multi-component oxide semiconductor layer 106 which is formed can be reduced, and a transistor having excellent electric characteristics or high reliability can be obtained.

5 [0061]

Further, preheat treatment is preferably performed before the multi-component oxide semiconductor layer 106 is formed, in order to remove hydrogen, water, hydroxyl group, hydride, or the like which remains on the inner wall of the sputtering apparatus, on a surface of a target, or inside a target material. As the preheat treatment, a method 10 in which the inside of the chamber is heated to 200 °C to 600 °C under reduced pressure, a method in which introduction and removal of nitrogen or an inert gas are repeated, and the like can be given. After the preheat treatment, the substrate or the sputtering apparatus is cooled. Then, the multi-component oxide semiconductor layer 106 is formed without exposure to the air. In this case, not water but oil or the like is 15 preferably used as a coolant for the target. Although a certain level of effect can be obtained when introduction and removal of nitrogen or an inert gas are repeated without performing heating, it is more preferable to perform the above treatment while performing heating.

[0062]

20 Next, the second heat treatment is performed. The temperature of the second heat treatment is 100 °C to 500 °C inclusive, preferably 150 °C to 400 °C inclusive. The heating time is set to 1 minute to 100 hours inclusive, preferably 5 hours to 20 hours inclusive, typically 10 hours. Through the second heat treatment, a multi-component oxide semiconductor layer 107 including single crystal regions can be 25 formed. The multi-component oxide semiconductor layer 107 including single crystal regions has a hexagonal crystal structure which is not a wurtzite crystal structure.

[0063]

30 In the first heat treatment and the second heat treatment, not only is crystal growth carried out in the single-component oxide semiconductor layer 104 and the multi-component oxide semiconductor layer 106, but impurities that are not main components of the oxide semiconductor, typically, hydrogen, water, hydroxyl group, or

hydride are removed, so that the oxide semiconductor layers can be highly purified.

[0064]

Note that the second heat treatment can be performed in an atmosphere similar to that of the first heat treatment. In addition, a heating apparatus similar to that of the first heat treatment can be used as appropriate for the second heat treatment.

[0065]

Here, an interface between the single-component oxide semiconductor layer 105 including single crystal regions and the multi-component oxide semiconductor layer 107 including single crystal regions is denoted by a dotted line. However, when the single-component oxide semiconductor layer 105 including single crystal regions is ZnO and the multi-component oxide semiconductor layer 107 including single crystal regions is an In-Ga-Zn-O-based oxide semiconductor, zinc contained in ZnO or the In-Ga-Zn-O-based oxide semiconductor is diffused due to the pressure and temperature of the heat treatment. Diffusion of zinc is recognized because, when TDS is performed at a temperature up to 450 °C, a peak of In or Ga is not detected but a peak of zinc is detected particularly at around 300 °C under vacuum heating conditions. Note that TDS is performed in vacuum, and it is found that zinc is detected from a temperature of about 200 °C. Accordingly, as illustrated in FIG. 8, there is also the case where a boundary between the single-component oxide semiconductor layer including single crystal regions and the multi-component oxide semiconductor layer including single crystal regions is not clear and these layers can be regarded as one layer, i.e., a layer 109.

[0066]

At the time of increasing the temperature in the first heat treatment and the second heat treatment, an atmosphere in a furnace may be a nitrogen atmosphere, and the atmosphere may be switched to an oxygen atmosphere at the time of performing cooling. The inside of the oxide semiconductor layer can be supplied with oxygen so as to be an i-type oxide semiconductor layer by switching the nitrogen atmosphere in which dehydration or dehydrogenation is performed to the oxygen atmosphere after the dehydration or dehydrogenation.

[0067]

Through the above process, the single-component oxide semiconductor layer 105 including single crystal regions and the multi-component oxide semiconductor layer 107 including single crystal regions can be formed (see FIG. 2C).

[0068]

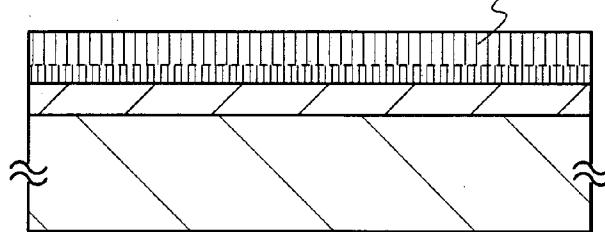

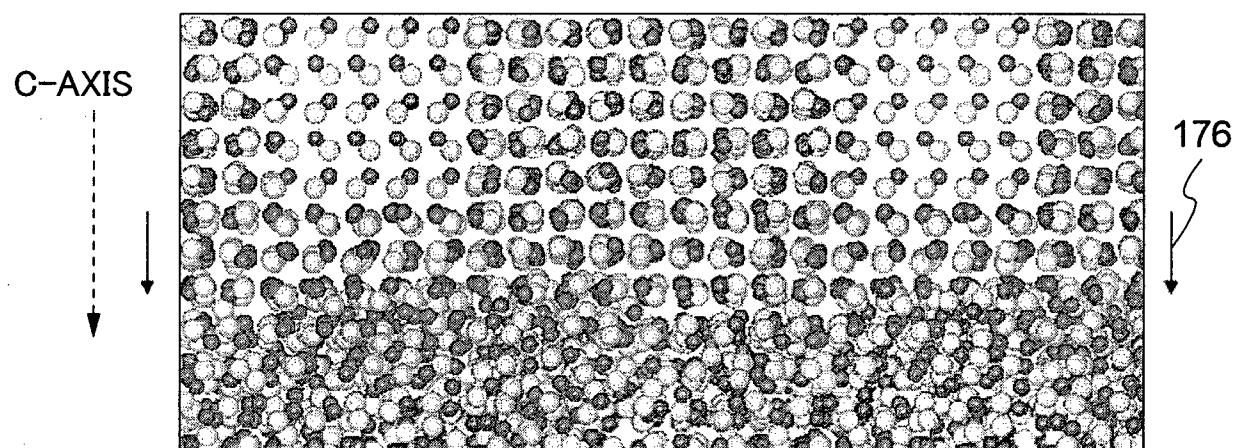

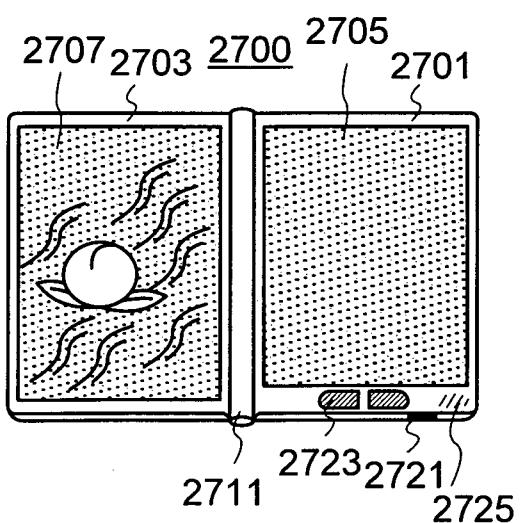

5 Now, details of the crystallization process for achieving the single-component oxide semiconductor layer 105 including single crystal regions and the multi-component oxide semiconductor layer 107 including single crystal regions are described with reference to FIGS. 3A to 3D.

[0069]

10 By the first heat treatment after the formation of the single-component oxide semiconductor layer 104, crystal growth begins from the surface of the single-component oxide semiconductor layer 104 toward the insulating layer 101 as indicated by arrows in FIG. 3A. Since the single-component oxide semiconductor layer 104 is easily crystallized, the entire single-component oxide semiconductor layer 15 104 is crystallized, so that the single-component oxide semiconductor layer 105 including single crystal regions is formed (see FIG. 3B).

[0070]

20 By the first heat treatment, crystal growth is carried out from the surface of the single-component oxide semiconductor layer 104, so that single crystal regions are formed. The single crystal regions are plate-shaped crystal regions obtained by crystal growth from the surface to the inside and have an average thickness of greater than or equal to a thickness of one atomic layer and less than or equal to 10 nm, preferably 2 nm to 5 nm inclusive. The single crystal regions have the a-b plane parallel to the surface and the c-axis perpendicular to the surface. In this embodiment, most part of 25 the single-component oxide semiconductor layer 104 is made to contain crystals (also referred to as co-growing (CG) crystals) by the first heat treatment. Since crystal growth is carried out from the surface in a depth direction, the single crystal regions having relatively uniform crystal direction with respect to the surface of the single-component oxide semiconductor layer 104 can be formed without being 30 influenced by a base component.

[0071]

Next, after the formation of the multi-component oxide semiconductor layer

106 over the single-component oxide semiconductor layer 105 including single crystal regions, the second heat treatment is performed, whereby crystal growth begins from the single-component oxide semiconductor layer 105 including single crystal regions toward the surface of the multi-component oxide semiconductor layer 106 as indicated 5 by arrows in FIG. 3C. The single-component oxide semiconductor layer 105 including single crystal regions is c-axis aligned perpendicularly to the surface. By using the single-component oxide semiconductor layer 105 including single crystal regions as a seed crystal, crystal growth (epitaxial growth or axial growth) of the multi-component oxide semiconductor layer 106 can be carried out such that substantially the same 10 crystal axis as the single-component oxide semiconductor layer 105 including single crystal regions is obtained. That is, crystal growth can be carried out while the multi-component oxide semiconductor layer 106 is c-axis aligned. Through the above process, the multi-component oxide semiconductor layer 107 including single crystal regions can be formed (see FIG. 3D).

15 [0072]

For example, in the case where an In-Ga-Zn-O-based oxide semiconductor material is used for the multi-component oxide semiconductor layer including single crystal regions, the single crystal regions can include crystals represented by  $\text{InGaO}_3(\text{ZnO})_m$  such as  $\text{InGaZnO}_4$  or  $\text{InGaZn}_5\text{O}_8$ , crystals represented by  $\text{In}_2\text{Ga}_2\text{ZnO}_7$ , 20 or the like. Such crystals have hexagonal crystal structures and their c-axes are substantially perpendicular to the surface of the multi-component oxide semiconductor layer through the second heat treatment.

[0073]

Here, a crystal in which the c-axis is substantially perpendicular to the surface 25 of the multi-component oxide semiconductor layer has a layered structure which contains any of In, Ga, and Zn, parallel to the a-axis and b-axis. Specifically, a crystal of  $\text{In}_2\text{Ga}_2\text{ZnO}_7$ ,  $\text{InGaZnO}_4$ , or  $\text{InGaZn}_5\text{O}_8$  has a structure in which a layer that contains In and a layer that does not contain In (a layer that contains Ga or Zn) are stacked in a c-axis direction.

30 [0074]

In the In-Ga-Zn-O-based oxide semiconductor, the conductivity of the layer that contains In in a direction of the a-b plane is favorable. This is due to the fact that

electrical conductivity is mainly controlled by In in the In-Ga-Zn-O-based oxide semiconductor and the fact that the 5s orbital of one In atom overlaps with the 5s orbital of an adjacent In atom and thereby a carrier path is formed. Further, since the multi-component oxide semiconductor layer including single crystal regions described in this embodiment is highly crystallized, there are fewer impurities and defects than in an amorphous, microcrystalline, or polycrystalline oxide semiconductor layer. Accordingly, carrier mobility of the multi-component oxide semiconductor layer including single crystal regions can be improved, whereby on-state current and field-effect mobility of the transistor can be enhanced.

10 [0075]

Now, a mechanism for forming plate-shaped crystal regions in the single-component oxide semiconductor layer 104 through the first heat treatment will be described with reference to FIG. 4, FIGS. 5A to 5C, and FIGS. 6A and 6B.

[0076]

15 Motion of atoms in the first heat treatment was examined by a classical molecular dynamics method. An empirical potential which characterizes the interaction between atoms is defined in a classical molecular dynamics method, so that force that acts on each atom can be evaluated. Here, a law of classical mechanics was applied to each atom and Newton's equation of motion was numerically solved, whereby motion (time-dependent change) of each atom was examined. In this 20 calculation, a Born-Mayer-Huggins potential was used as the empirical potential.

[0077]

A model in which crystal nuclei 160 that are single crystal zinc oxide (hereinafter referred to as c-ZnO) having a width of 1 nm are provided at equal intervals 25 in amorphous zinc oxide (hereinafter referred to as a-ZnO) was formed as illustrated in FIG. 4. Note that the density of a-ZnO and c-ZnO was 5.5 g/cm<sup>3</sup>. The vertical direction was a c-axis direction.

[0078]

30 Next, the model in FIG. 4 was subjected to classical molecular dynamics simulation at 700 °C for 100 psec (0.2 fsec × 500,000 steps) while fixing c-ZnO under three-dimensional periodic boundary conditions. Results thereof are shown in FIGS.

5A to 5C and FIGS. 6A and 6B.

[0079]

FIGS. 5A, 5B, and 5C respectively show the changes of atomic positions after 20 psec, 40 psec, and 60 psec. FIGS. 6A and 6B respectively show the changes of 5 atomic positions after 80 psec and 100 psec. In each drawing, the distance and direction of crystal growth are denoted by the length and pointing direction of arrows.

[0080]

Table 1 shows crystal growth rates in a vertical direction (c-axis [0001]) and a horizontal direction perpendicular to the vertical direction.

10 [0081]

[Table 1]

| DIRECTION  | CRYSTAL GROWTH RATE<br>(nm/psec) |

|------------|----------------------------------|

| VERTICAL   | $6.1 \times 10^{-3}$             |

| HORIZONTAL | $3.0 \times 10^{-2}$             |

[0082]

15 In FIGS. 5A to 5C, arrows 164a, 164b, 168a, 168b, 172a, and 172b in a horizontal direction (a direction perpendicular to a c-axis direction) are longer than arrows 162, 166, and 170 in a vertical direction (the c-axis direction). Therefore, it is found that crystal growth in a horizontal direction is preferential and that the crystal growth is finished between adjacent crystal nuclei in FIG. 5C.

[0083]

20 In FIGS. 6A and 6B, it is found that crystal growth is carried out in a vertical direction (the c-axis direction) using crystal regions formed at the surface as seed crystals as indicated by arrows 174 and 176.

[0084]

25 In addition, according to Table 1, it is found that the crystal growth rate in the horizontal direction perpendicular to the vertical direction (c-axis [0001]) is about 4.9 times higher than that in the vertical direction. Therefore, crystal growth first proceeds in a direction parallel to the surface (the a-b plane) in ZnO. At this time, in the a-b plane, crystal growth proceeds in the horizontal direction to form plate-shaped single crystal regions. Next, using the plate-shaped single crystal regions formed at the

surface (the a-b plane) as seed crystals, crystal growth proceeds in the c-axis direction perpendicular to the surface (the a-b plane). Therefore, it is assumed that ZnO is likely to be c-axis aligned. As described above, after the crystal growth preferentially proceeds in the direction parallel to the surface (the a-b plane), crystal growth (also referred to as epitaxial growth or axial growth) proceeds in the c-axis direction perpendicular to the surface, whereby the plate-shaped single crystal regions are formed.

[0085]

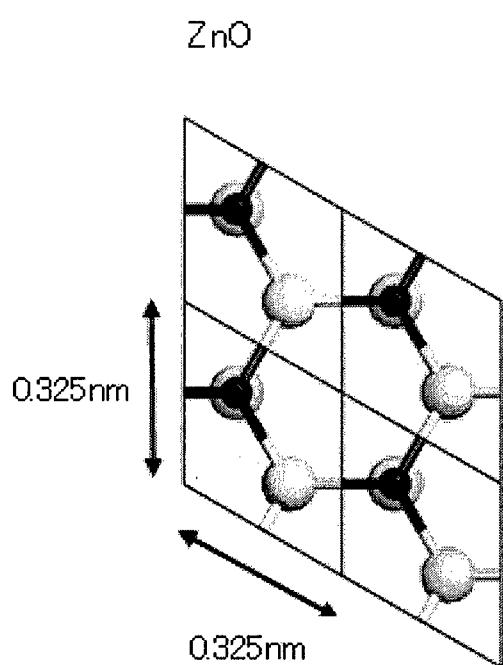

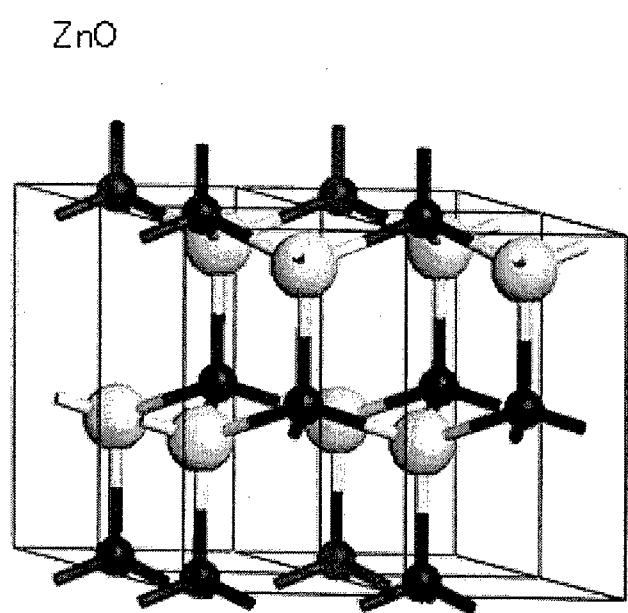

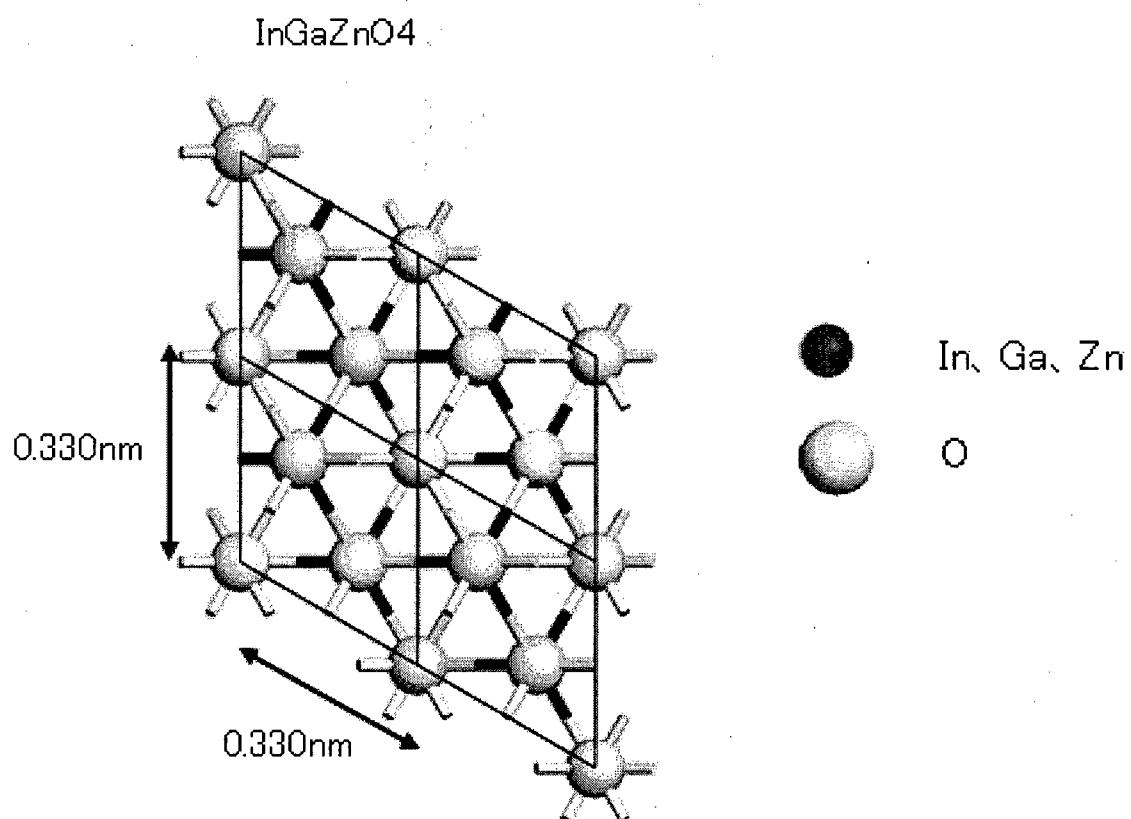

Next, a mechanism of crystal growth in which the crystal axis of the multi-component oxide semiconductor layer 107 including single crystal regions is substantially equal to the crystal axis of the single-component oxide semiconductor layer 105 including single crystal regions is described with reference to FIGS. 7A to 7C.

[0086]

FIG. 7A shows the structure of a unit cell in the a-b plane in which zinc oxide (ZnO) having a hexagonal crystal structure that is a typical example of the single-component oxide semiconductor layer is observed from the c-axis direction. FIG. 7B shows the crystal structure in which the c-axis direction is a vertical direction.

[0087]

FIG. 7C shows the structure in the a-b plane in which InGaZnO<sub>4</sub> that is a typical example of the multi-component oxide semiconductor layer is observed from the c-axis direction.

[0088]

According to FIGS. 7A and 7C, lattice constants of ZnO and InGaZnO<sub>4</sub> are substantially the same, and ZnO and InGaZnO<sub>4</sub> have high consistency with each other in the a-b plane. In addition, ZnO and InGaZnO<sub>4</sub> have a hexagonal crystal structure and ZnO has a bond parallel to the c-axis direction; therefore, crystal growth can be carried out in the c-axis direction with high consistency in InGaZnO<sub>4</sub> that is a typical example of the multi-component oxide semiconductor layer. Accordingly, crystal growth is carried out such that the crystal axis of the multi-component oxide semiconductor layer 107 including single crystal regions is substantially equal to the crystal axis of the single-component oxide semiconductor layer 105 including single crystal regions.

## [0089]

Then, a resist mask is formed by a photolithography step over the multi-component oxide semiconductor layer 107 including single crystal regions illustrated in FIG. 2C. After that, the single-component oxide semiconductor layer 105 including single crystal regions and the multi-component oxide semiconductor layer 107 including single crystal regions are etched by using the resist mask, whereby the island-shaped single-component oxide semiconductor layer 105a including single crystal regions and the island-shaped multi-component oxide semiconductor layer 107a including single crystal regions are formed (FIG. 2D). The resist mask may be formed by an ink-jet method. Formation of the resist mask by an ink-jet method needs no photomask; thus, manufacturing cost can be reduced. Hereinafter, the single-component oxide semiconductor layer 105a including single crystal regions and the multi-component oxide semiconductor layer 107a including single crystal regions are also referred to as an oxide semiconductor stack 110.

## 15 [0090]

In the etching, a dry etching method or a wet etching method can be used. As an etchant used for wet etching, a solution obtained by mixing phosphoric acid, acetic acid, and nitric acid, an ammonia hydrogen peroxide (hydrogen peroxide at 31 wt%: ammonia water at 28 wt%: water = 5:2:2), or the like can be used. In addition, 20 ITO07N (produced by KANTO CHEMICAL CO., INC.) may be used.

## [0091]

The etchant after the wet etching is removed together with the material etched off by cleaning. The waste liquid including the etchant and the material etched off may be purified and the material may be reused. When a material such as indium is 25 collected from the waste liquid after the etching and reused, the resources can be efficiently used and the cost can be reduced.

## [0092]

As an etching gas for dry etching, a gas containing chlorine (chlorine-based gas such as chlorine (Cl<sub>2</sub>), boron trichloride (BCl<sub>3</sub>), silicon tetrachloride (SiCl<sub>4</sub>), or carbon 30 tetrachloride (CCl<sub>4</sub>)) is preferably used.

## [0093]

Alternatively, a gas containing fluorine (fluorine-based gas such as carbon tetrafluoride (CF<sub>4</sub>), sulfur hexafluoride (SF<sub>6</sub>), nitrogen trifluoride (NF<sub>3</sub>), or trifluoromethane (CHF<sub>3</sub>)); hydrogen bromide (HBr); oxygen (O<sub>2</sub>); any of these gases to which a rare gas such as helium (He) or argon (Ar) is added; or the like can be used.

5 [0094]

As a dry etching method, a parallel plate RIE (reactive ion etching) method or an ICP (inductively coupled plasma) etching method can be used. In order to etch the layer into a desired shape, the etching condition (the amount of electric power applied to a coil-shaped electrode, the amount of electric power applied to an electrode on a substrate side, the temperature of the electrode on the substrate side, or the like) is 10 adjusted as appropriate.

[0095]

Next, a conductive layer 108 is formed over the insulating layer 101 and the island-shaped oxide semiconductor layers (see FIG. 2E). The conductive layer 108 is 15 formed into the wirings 108a and 108b later.

[0096]

The conductive layer 108 can be formed using a metal element selected from aluminum, chromium, copper, tantalum, titanium, molybdenum, and tungsten, an alloy containing any of these metal elements as a component, an alloy containing any of these 20 metal elements in combination, or the like. Alternatively, one or more metal elements selected from manganese, magnesium, zirconium, and beryllium may be used. In addition, the conductive layer 108 can have a single-layer structure or a stacked structure having two or more layers. For example, a single-layer structure of an aluminum layer containing silicon, a two-layer structure in which a titanium layer is 25 stacked over an aluminum layer, a two-layer structure in which a titanium layer is stacked over a titanium nitride layer, a two-layer structure in which a tungsten layer is stacked over a titanium nitride layer, a two-layer structure in which a tungsten layer is stacked over a tantalum nitride layer, a three-layer structure in which a titanium layer, an aluminum layer, and a titanium layer are stacked in this order, and the like can be given. Alternatively, a layer, an alloy layer, or a nitride layer which contains 30 aluminum and one or more of elements selected from titanium, tantalum, tungsten, molybdenum, chromium, neodymium, and scandium may be used.

[0097]

Alternatively, as the conductive layer 108, a light-transmitting conductive material such as indium tin oxide, indium oxide containing tungsten oxide, indium zinc oxide containing tungsten oxide, indium oxide containing titanium oxide, indium tin oxide containing titanium oxide, indium zinc oxide, or indium tin oxide to which silicon oxide is added, can be used. It is also possible to have a stacked structure formed using the above light-transmitting conductive material and the above metal element.

[0098]

The conductive layer 108 is formed by a sputtering method, a CVD method, or a vacuum evaporation method. In this embodiment, as the conductive layer 108, a metal layer including three layers of a titanium layer with a thickness of 50 nm, an aluminum layer with a thickness of 100 nm, and a titanium layer with a thickness of 50 nm, each formed by a sputtering method, is used.

[0099]

Next, a resist mask is formed over the conductive layer 108 by a photolithography step, and the conductive layer 108 is etched with the use of the resist mask, so that the wirings 108a and 108b functioning as a source electrode and a drain electrode are formed (see FIG. 9A). Alternatively, when the wirings 108a and 108b are formed by a printing method or an ink-jet method without using a photolithography step, the number of steps can be reduced.

[0100]

In light exposure performed on a resist for forming a resist mask that is used in etching, it is preferable to use ultraviolet light, a KrF laser beam, or an ArF laser beam. Particularly for light exposure in the case where the channel length (L) is shorter than 25 nm, a resist is preferably exposed to extreme ultraviolet light whose wavelength is several nanometers to several tens of nanometers, which is extremely short. In light exposure using extreme ultraviolet light, resolution is high and the depth of focus is large. Therefore, the channel length (L) of a transistor, which is formed later, can be 10 nm to 1000 nm (1  $\mu$ m) inclusive. By a decrease in channel length by such a method, operation speed of the transistor can be improved. In addition, off-state current of a transistor including the above-described oxide semiconductor is very small; thus, an increase in power consumption due to miniaturization of the transistor can be

suppressed.

[0101]

The material of the oxide semiconductor stack 110 and the material and etching conditions of the conductive layer 108 are adjusted as appropriate so that the oxide semiconductor stack 110 is not removed at the time of etching the conductive layer 108. Note that in some cases, the oxide semiconductor stack 110 is partly etched in the etching step and thus has a groove portion (a recessed portion) depending on the materials and the etching conditions.

[0102]

In addition, a crystal region on the side surface of the oxide semiconductor stack 110 which is in contact with the wiring 108a or 108b is in an amorphous state in some cases.

[0103]

Note that the etching of the conductive layer 108 may be performed using either dry etching or wet etching, or using both dry etching and wet etching. In order to form the wirings 108a and 108b having a desired shape, an etching condition (etchant, etching time, temperature, or the like) is adjusted as appropriate in accordance with the material.

[0104]

In this embodiment, ammonia hydrogen peroxide (a mixed solution of ammonia, water, and hydrogen peroxide) is used as an etchant and the conductive layer 108 is etched, so that the wirings 108a and 108b are formed.

[0105]

Next, as illustrated in FIG. 9B, the gate insulating layer 112 is formed over the insulating layer 101, the oxide semiconductor stack 110, and the wirings 108a and 108b.

[0106]

The gate insulating layer 112 can be formed with a single layer or a stacked layer using one or more of a silicon oxide layer, a silicon nitride layer, a silicon oxynitride layer, a silicon nitride oxide layer, and an aluminum oxide layer. A portion of the gate insulating layer 112 which is in contact with the oxide semiconductor stack 110 preferably contains oxygen, and in particular, the portion of the gate insulating layer 112 is preferably formed using a silicon oxide layer. The use of a silicon oxide layer

makes it possible to supply oxygen to the oxide semiconductor stack 110; thus, favorable characteristics can be obtained.

[0107]

When the gate insulating layer 112 is formed using a high-k material such as 5 hafnium silicate ( $\text{HfSiO}_x$ ), hafnium silicate to which nitrogen is added ( $\text{HfSi}_x\text{O}_y\text{N}_z$ ), hafnium aluminate to which nitrogen is added ( $\text{HfAl}_x\text{O}_y\text{N}_z$ ), hafnium oxide, or yttrium oxide, gate leakage current can be reduced. Further, a stacked structure in which a high-k material and one or more of a silicon oxide layer, a silicon nitride layer, a silicon oxynitride layer, a silicon nitride oxide layer, and an aluminum oxide layer are stacked 10 can be used. The thickness of the gate insulating layer 112 may be 50 nm to 500 nm inclusive. When the thickness of the gate insulating layer 112 is large, gate leakage current can be reduced.

[0108]

15 The i-type or substantially i-type oxide semiconductor layer (the highly purified oxide semiconductor layer whose hydrogen concentration is reduced) obtained by removal of impurities is extremely sensitive to an interface state and interface charge; therefore, the interface between the oxide semiconductor stack and the gate insulating layer 112 is important. Thus, the gate insulating layer 112 that is to be in contact with the highly purified oxide semiconductor stack 110 needs to have high 20 quality.

[0109]

For example, high-density plasma CVD using microwaves (e.g., with a 25 frequency of 2.45 GHz) is preferably adopted because an insulating layer can be dense and have high withstand voltage and high quality. This is because when the highly purified oxide semiconductor layer whose hydrogen concentration is reduced and the high-quality gate insulating layer are in close contact with each other, the interface state can be reduced and the interface characteristics can be favorable. In addition, since the insulating layer formed using high-density plasma CVD can have a uniform thickness, the insulating layer has excellent step coverage. Further, as for the insulating layer 30 formed using high-density plasma CVD, the thickness can be controlled precisely.

[0110]

It is needless to say that other film formation methods such as a sputtering

method or a plasma CVD method can be employed as long as a high-quality insulating layer can be formed as the gate insulating layer. When a silicon oxide layer is formed by a sputtering method, a silicon target or a quartz target is used as a target, and oxygen or a mixed gas of oxygen and argon is used as a sputtering gas. In addition, as the gate insulating layer, an insulating layer whose characteristics of an interface with the oxide semiconductor stack 110 are improved or whose film quality is improved by heat treatment after the formation may be used. In any case, an insulating layer which can reduce the interface state density with the oxide semiconductor stack 110 and can form a favorable interface, in addition to having good film quality as the gate insulating layer, 5 may be used.

10

[0111]

For example, in a gate bias-temperature stress test (BT test) at 85 °C at  $2 \times 10^6$  V/cm for 12 hours, when impurities are added to the oxide semiconductor stack 110, bonds between impurities and a main component of the oxide semiconductor stack 110 are cut by an intense electric field (B: bias) and high temperature (T: temperature), and 15 generated dangling bonds cause a shift in threshold voltage (V<sub>th</sub>).

[0112]

On the other hand, when impurities in the oxide semiconductor stack 110, in particular, hydrogen, water, hydroxyl group, hydride, or the like, are removed as much 20 as possible, and characteristics of an interface between the oxide semiconductor stack and the gate insulating layer are improved as described above, a transistor which is stable to the BT test can be obtained.

[0113]

Note that a halogen element (e.g. fluorine or chlorine) may be contained in an 25 insulating layer provided in contact with the oxide semiconductor stack 110, or a halogen element may be contained in the oxide semiconductor stack 110 by plasma treatment in a gas atmosphere containing a halogen element in a state that the oxide semiconductor stack 110 is exposed, whereby impurities such as hydrogen, water, hydroxyl group, or hydride existing in the oxide semiconductor stack 110 or at the 30 interface between the oxide semiconductor stack 110 and the insulating layer which is provided in contact with the oxide semiconductor stack 110 may be removed. When the insulating layer is made to contain a halogen element, the halogen element

concentration in the insulating layer may be approximately  $5 \times 10^{17} \text{ cm}^{-3}$  to  $1 \times 10^{20} \text{ cm}^{-3}$ .

[0114]

As described above, in the case where a halogen element is contained in the 5 oxide semiconductor stack 110 or at the interface between the oxide semiconductor stack 110 and the insulating layer which is in contact with the oxide semiconductor stack 110 and the insulating layer which is provided in contact with the oxide semiconductor stack 110 is an oxide insulating layer, the side of the oxide insulating layer which is not in contact with the oxide semiconductor stack 110 is preferably 10 covered with a nitride insulating layer. That is, a silicon nitride layer or the like may be provided on and in contact with the oxide insulating layer which is in contact with the oxide semiconductor stack 110. With such a structure, entry of an impurity such as hydrogen, water, hydroxyl group, or hydride into the oxide semiconductor stack 110 can be reduced.

15 [0115]

Further, preheat treatment is preferably performed before the gate insulating layer 112 is formed in order to remove moisture or hydrogen which remains on the inner wall of the sputtering apparatus, on a surface of a target, or inside a target material. After the preheat treatment, the substrate or the sputtering apparatus is cooled. Then, 20 the gate insulating layer 112 is formed without exposure to the air. In this case, not water but oil or the like is preferably used as a coolant for the target.

[0116]

Next, the gate electrode 114 is formed over the gate insulating layer 112 in a region overlapping with the oxide semiconductor stack 110 (see FIG. 9C). The gate 25 electrode 114 can be formed in such a way that a conductive layer is formed over the gate insulating layer 112 by a sputtering method, a CVD method, or a vacuum evaporation method, a resist mask is formed by a photolithography step over the conductive layer, and the conductive layer is etched using the resist mask.

[0117]

30 The gate electrode 114 can be formed using a metal element selected from aluminum, chromium, copper, tantalum, titanium, molybdenum, and tungsten, an alloy

containing any of these metal elements as a component, an alloy containing any of these metal elements in combination, or the like. Alternatively, one or more metal elements selected from manganese, magnesium, zirconium, and beryllium may be used. Further, the gate electrode 114 may have a single-layer structure or a stacked-layer structure of 5 two or more layers. For example, a single-layer structure of an aluminum layer containing silicon, a two-layer structure in which a titanium layer is stacked over an aluminum layer, a two-layer structure in which a titanium layer is stacked over a titanium nitride layer, a two-layer structure in which a tungsten layer is stacked over a titanium nitride layer, a two-layer structure in which a tungsten layer is stacked over a tantalum nitride layer, a three-layer structure in which a titanium layer, an aluminum layer, and a titanium layer are stacked in this order, and the like can be given. Alternatively, a layer, an alloy layer, or a nitride layer which contains aluminum and one 10 or more elements selected from titanium, tantalum, tungsten, molybdenum, chromium, neodymium, and scandium may be used.

15 [0118]

Alternatively, a light-transmitting conductive material such as indium tin oxide, indium oxide containing tungsten oxide, indium zinc oxide containing tungsten oxide, indium oxide containing titanium oxide, indium tin oxide containing titanium oxide, indium zinc oxide, or indium tin oxide to which silicon oxide is added, can be used as 20 the gate electrode 114. It is also possible to have a stacked structure formed using the above light-transmitting conductive material and the above metal element.

[0119]

Next, third heat treatment may be performed in an inert gas atmosphere or an oxygen gas atmosphere (preferably, at 200 °C to 450 °C inclusive, for example, 250 °C 25 to 350 °C inclusive). By the heat treatment, oxygen is supplied to oxygen defects generated by the first and second heat treatment, so that it is possible to further reduce the oxygen defects which serve as donors, satisfy the stoichiometric proportion, and make the oxide semiconductor stack 110 closer to an i-type oxide semiconductor or a substantially i-type oxide semiconductor. Note that the third heat treatment may be 30 performed before formation of the gate electrode 114 or after formation of the insulating layer 116 which is formed later.

[0120]

Next, the insulating layer 116 is formed over the gate insulating layer 112 and the gate electrode 114 (see FIG. 9D). The insulating layer 116 may contain hydrogen. The insulating layer 116 can be formed by a sputtering method, a CVD method, or the like. In this embodiment, a nitride silicon layer which is one of nitride insulating layers obtained by a CVD method is used.

[0121]

The third heat treatment is performed in a nitrogen atmosphere at 150 °C to 450 °C inclusive, preferably 250 °C to 440 °C inclusive. In addition, the third heat treatment may be performed in an oxygen atmosphere, a rare gas atmosphere, or a dry air atmosphere without limitation to a nitrogen atmosphere.

[0122]

Through the above process, the transistor 150 having the oxide semiconductor stack which is highly purified and has single crystal regions and in which the hydrogen concentration is reduced can be formed.

[0123]

After the step in FIG. 2C, in some cases, the multi-component oxide semiconductor layer 107 including single crystal regions is etched into an island-shape but the single-component oxide semiconductor layer 105 including single crystal regions is not etched into an island-shape depending on the etching condition, and the single-component oxide semiconductor layer 105 including single crystal regions remains over the entire surface of the insulating layer 101 as illustrated in FIG. 10A. After that, through the steps illustrated in FIG. 2E and FIGS. 9A to 9D, a transistor 152 as illustrated in FIG. 10B is obtained, in which the single-component oxide semiconductor layer 105 including single crystal regions is formed over the insulating layer 101, the multi-component oxide semiconductor layer 107a including single crystal regions, the wirings 108a and 108b, and the gate insulating layer 112 are formed over the single-component oxide semiconductor layer 105 including single crystal regions, and the gate electrode 114 is formed over the gate insulating layer 112.

30 [0124]

A conventional oxide semiconductor is generally an n-type semiconductor and

current tends to flow between source and drain electrodes even when a gate voltage is 0 V in a transistor using a conventional oxide semiconductor; that is, the transistor tends to be normally on. In the case where the transistor is normally on, it is difficult to control a circuit even when the field-effect mobility is high. It is known that hydrogen is a donor in an oxide semiconductor and is one factor causing an oxide semiconductor to be an n-type semiconductor. Further, an oxygen defect is known as one factor causing an oxide semiconductor to be an n-type semiconductor.

5 [0125]

Therefore, in order to make the oxide semiconductor be an i-type oxide semiconductor, the oxide semiconductor is highly purified by removing hydrogen, water, hydroxyl group, hydride, or the like that is an n-type impurity along with the crystal growth in the first heat treatment and the second heat treatment so as to contain an impurity that is not a main component of the oxide semiconductor as little as possible and is made to be an intrinsic oxide semiconductor by removing oxygen defects in the third heat treatment. In other words, this embodiment has a feature that the oxide semiconductor is made to be a highly purified i-type (intrinsic) oxide semiconductor or an oxide semiconductor close thereto not by addition of an impurity but by removal of an impurity such as hydrogen, water, hydroxyl group, or hydride or oxygen defects as much as possible. In particular, since the oxide semiconductor described in this embodiment is crystallized to a high degree, it is characterized by having fewer impurities or defects than an amorphous, microcrystalline, or polycrystalline oxide semiconductor. By highly purifying the oxide semiconductor as described above, the threshold voltage of the transistor can be positive, so that a so-called normally-off switching element can be achieved.

10 20 25 [0126]

The hydrogen concentration of the oxide semiconductor at this time is lower than or equal to  $1 \times 10^{18} \text{ cm}^{-3}$ , preferably lower than or equal to  $1 \times 10^{16} \text{ cm}^{-3}$ , more preferably substantially 0. Moreover, the carrier density of the oxide semiconductor is lower than  $1 \times 10^{14} \text{ cm}^{-3}$ , preferably lower than  $1 \times 10^{12} \text{ cm}^{-3}$ , more preferably lower than  $1.45 \times 10^{10} \text{ cm}^{-3}$ . That is, the carrier density of the oxide semiconductor is as close to zero as possible. Furthermore, the band gap of the oxide semiconductor is

greater than or equal to 2 eV, preferably greater than or equal to 2.5 eV, more preferably greater than or equal to 3 eV. The hydrogen concentration in the oxide semiconductor is measured by secondary ion mass spectroscopy (SIMS). The carrier density can be measured by the Hall effect measurement. Lower carrier density can be calculated with the use of measurement results of capacitance-voltage (CV) measurement.

5 [0127]

In the oxide semiconductor, the carrier concentration is sufficiently low (e.g., lower than  $1 \times 10^{12} /cm^3$ , preferably lower than  $1.45 \times 10^{10} /cm^3$ ) as compared with the minimum carrier concentration (approximately  $1 \times 10^{14} /cm^3$ ) of a general silicon wafer.