(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5599181号

(P5599181)

(45) 発行日 平成26年10月1日(2014.10.1)

(24) 登録日 平成26年8月22日(2014.8.22)

(51) Int.Cl.

F 1

|                    |                  |             |      |

|--------------------|------------------|-------------|------|

| <b>H01L 29/786</b> | <b>(2006.01)</b> | H01L 29/78  | 617U |

| <b>H01L 21/312</b> | <b>(2006.01)</b> | H01L 29/78  | 617T |

| <b>H01L 51/05</b>  | <b>(2006.01)</b> | H01L 29/78  | 618B |

| <b>H01L 51/30</b>  | <b>(2006.01)</b> | H01L 21/312 | A    |

|                    |                  | H01L 29/28  | 100A |

請求項の数 2 (全 13 頁) 最終頁に続く

(21) 出願番号

特願2009-274818 (P2009-274818)

(22) 出願日

平成21年12月2日 (2009.12.2)

(65) 公開番号

特開2010-135793 (P2010-135793A)

(43) 公開日

平成22年6月17日 (2010.6.17)

審査請求日 平成24年11月28日 (2012.11.28)

審判番号 不服2013-16169 (P2013-16169/J1)

審判請求日 平成25年8月21日 (2013.8.21)

(31) 優先権主張番号 12/328,849

(32) 優先日 平成20年12月5日 (2008.12.5)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 596170170

ゼロックス コーポレイション

XEROX CORPORATION

アメリカ合衆国、コネチカット州 06856、ノーウォーク、ピーオーボックス 4505、グローバー・アヴェニュー 45

(74) 代理人 110001210

特許業務法人 YKI 国際特許事務所

(72) 発明者 イーリアン ウー

カナダ オンタリオ オークヴィル ティラーウッド ドライブ 2394

ポール エフ スミス

カナダ オンタリオ オークヴィル ゲートストーン アベニュー 24

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ

## (57) 【特許請求の範囲】

## 【請求項 1】

トップゲート薄膜トランジスタであって、

(a) 基板と、

(b) ゲート電極と、

(c) 有機半導体層と、

(d) 多量の低 k 誘電体ポリマー / 少量の高 k 誘電体ポリマー の第 1 の層、及び、多量の高 k 誘電体ポリマー / 少量の低 k 誘電体ポリマー の第 2 の層を含み、相分離した誘電体構造物からなるゲート絶縁膜と、

を含み、

10

前記第 2 の層は、前記半導体層に最も近い前記ゲート絶縁膜の領域にあり、

当該第 2 の層において、前記低 k 誘電体ポリマーと前記高 k 誘電体ポリマーとを合わせた重量を基準として、

前記低 k 誘電体ポリマーは、40% ~ 10% の範囲の濃度であり、

前記高 k 誘電体ポリマーは、60% ~ 90% の範囲の濃度である薄膜トランジスタ。

## 【請求項 2】

請求項 1 に記載の薄膜トランジスタにおいて、

前記低 k 誘電体ポリマーは、4.0 未満の誘電率を有する薄膜トランジスタ。

## 【発明の詳細な説明】

## 【技術分野】

20

## 【0001】

本発明は、電子デバイス及び当該デバイスにおいて使用される好適な材料、さらには電子デバイス及びそれらの構成要素の作製プロセスに関する。さらに詳しくは、本発明は、相分離した誘電体構造物を含む電子デバイス、さらには当該電子デバイス及び相分離された誘電体構造物の作製プロセスに関する。

## 【背景技術】

## 【0002】

従来のフォトリソグラフィプロセスを使用してシリコンベースの薄膜トランジスタ（TFT）回路を作製することのコスト及び複雑さの問題から、液相ベースのパターン成形及び析出技術、例えば、スピンドルコート法、溶液キャスト法、ディップコート法、ステンシル／スクリーン印刷法、フレキソ印刷法、グラビア印刷法、オフセット印刷法、インキジェット印刷法、ミクロコンタクト印刷法など、又はそれらのプロセスを組み合わせたものを使用して作製することができるプラスチック／有機薄膜トランジスタに大きな関心が寄せられてきた。一般的に、そのようなプロセスは、シリコンベースの薄膜トランジスタ回路の作製に使用される複雑なフォトリソグラフィプロセスと比較して、より単純かつより低コストである。そのため、液相加工される薄膜トランジスタ回路を作製するために、液相加工可能な材料が必要とされている。

10

## 【先行技術文献】

## 【特許文献】

## 【0003】

20

【特許文献1】米国特許第6528409号明細書

【特許文献2】米国特許第6706464号明細書

【特許文献3】米国特許第5883219号明細書

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0004】

プラスチック薄膜トランジスタに好適な誘電体材料としては、例えば、(1)良好な電気絶縁性、及び(2)半導体材料との良好な適合性、を有しているものが望ましい。従来のゲート絶縁膜(ゲート誘電体)における問題点は、簡単なプロセスで、その誘電体材料に対して所望の特質を全て備えることが困難であるということである。

30

本発明の目的は、(1)良好な電気絶縁性、及び(2)半導体材料との良好な適合性を有する電子デバイス用の誘電体材料を提供することである。

## 【課題を解決するための手段】

## 【0005】

本発明に係る薄膜トランジスタは、トップゲート薄膜トランジスタであって、(a)基板と、(b)ゲート電極と、(c)有機半導体層と、(d)多量の低k誘電体ポリマー／少量の高k誘電体ポリマーの第1の層、及び、多量の高k誘電体ポリマー／少量の低k誘電体ポリマーの第2の層を含み、相分離した誘電体構造物からなるゲート絶縁膜と、を含み、前記第2の層は、前記半導体層に最も近い前記ゲート絶縁膜の領域にあり、当該第2の層において、前記低k誘電体ポリマーと前記高k誘電体ポリマーとを合わせた重量を基準として、前記低k誘電体ポリマーは、40%～10%の範囲の濃度であり、前記高k誘電体ポリマーは、60%～90%の範囲の濃度であることを特徴とする。

40

ここで、低k誘電体ポリマーは、4.0未満の誘電率を有することが好ましい。

## 【図面の簡単な説明】

## 【0008】

【図1】本発明に係る第1の実施態様であるTFTの形態を示す図である。

【図2】本発明に係る第2の実施態様であるTFTの形態を示す図である。

【図3】本発明に係る第3の実施態様であるTFTの形態を示す図である。

【図4】本発明に係る第4の実施態様であるTFTの形態を示す図である。

## 【0009】

50

なお、特に断らない限り、各図において、同一又は類似の構成には、同一の符号を付する。

**【発明を実施するための形態】**

**【0010】**

本発明の開示の態様は、相分離した誘電体構造物を含む電子デバイス（例えば、薄膜トランジスタ）に関する。薄膜トランジスタの文脈においては、その誘電体構造物を「ゲート絶縁膜」と称する場合がある。誘電体構造物は、各種適切な電子デバイスにおいて使用することができる。薄膜トランジスタの他の電子デバイスとしては、例えば、埋め込みコンデンサ、エレクトロルミネセントランプが挙げられる。

**【0011】**

本発明の誘電体構造物の作製において、低k誘電体材料（低k誘電体材料：low k誘電体材料）と、高k誘電体材料（高k誘電体材料：high k誘電体）と、液体とを含む誘電体組成物が調製されるが、低k誘電体材料と高k誘電体材料とは、液相析出させるまで相分離しない。

**【0012】**

実施態様において、「低k誘電体材料」と「高k誘電体材料」という用語は、誘電体組成物中及び誘電体構造物中において、（誘電率を基準にして）二つのタイプの誘電体材料を区別するために使用される。したがって、各種適切な誘電体材料を、低k誘電体材料とすることが可能であり、その低k誘電体材料よりも高い誘電率を有する各種適切な誘電体材料を、高k誘電体材料とすることができます。「低k誘電体材料」には、1種、2種又はそれ以上の適切な材料を含むことができる。「高k誘電体材料」には、1種、2種又はそれ以上の適切な材料を含むことができる。

**【0013】**

実施態様において、低k誘電体材料は、デバイスの半導体層に適合可能であるか、又は良好な適合性を有する電気絶縁材料である。「適合可能」（又は「適合性」）という用語は、低k誘電体材料が多い表面に隣接させたときに、半導体層が電気的な性能を良好に発揮できることを意味する。例えば、ポリチオフェン半導体の場合には、一般的に、疎水性表面が好ましい。いくつかの実施態様においては、低k誘電体材料が疎水性表面を有するので、ポリチオフェン半導体に対して優れた適合性を示すことができる。

**【0014】**

いくつかの実施態様において、低k誘電体材料は、例えば、4.0未満、又は約3.5未満、特には約3.0未満の誘電率を有する。いくつかの実施態様において、低k誘電体材料は、例えばメチル基、フェニレン基、エチレン基、Si-C、Si-O-Siなどの非極性又は弱極性基を有する。いくつかの実施態様において、低k誘電体材料は、低k誘電体ポリマー（kがより低い誘電体ポリマー）である。代表的な低k誘電体ポリマーとして以下のものが挙げられるが、これらに限定される訳ではない。例えば、ポリスチレン、ポリ(4-メチルスチレン)、ポリ(クロロスチレン)、ポリ(-メチルスチレン)、ポリシロキサン、例えば、ポリ(ジメチルシロキサン)及びポリ(ジフェニルシロキサン)、ポリシリセスキオキサン、例えば、ポリ(エチルシリセスキオキサン)、ポリ(メチルシリセスキオキサン)、及びポリ(フェニルシリセスキオキサン)、ポリフェニレン、ポリ(1,3-ブタジエン)、ポリ(-ビニルナフタレン)、ポリプロピレン、ポリイソブレン、ポリイソブチレン、ポリエチレン、ポリ(4-メチル-1-ペンテン)、ポリ(p-キシレン)、ポリ(メタクリル酸シクロヘキシル)、ポリ(プロピルメタクリルPOSS-co-メチルメタクリレート)、ポリ(プロピルメタクリルPOSS-co-スチレン)、ポリ(スチリルPOSS-co-スチレン)、ポリ(ビニルシンナメート)など、ならびにそれらの混合物が挙げられる。「POSS」という用語は、ポリヘドラルオリゴメリックシリセスキオキサンを指す。いくつかの実施態様において、低k誘電体材料には、ポリシリセスキオキサン、特にポリ(メチルシリセスキオキサン)を含む。なお、誘電率は、室温、1kHzの周波数で測定したものである。

**【0015】**

10

20

30

40

50

いくつかの実施態様において、低 k 誘電体材料の表面は、膜としてキャストしたとき、低い表面エネルギーを有している。表面エネルギーの性質を表すために、前進水接触角を使用することができる。接触角が高いということは、表面エネルギーが低いということを意味する。いくつかの実施態様においては、その接触角が 80° 以上、又は約 90°。よりも高く、特には約 95°。よりも高い。

#### 【0016】

いくつかの実施態様において、高 k 誘電体材料は、例えば、ヒドロキシル基、アミノ基、シアノ基、ニトロ基、C=O 基などの極性基を含む電気絶縁材料である。いくつかの実施態様において、高 k 誘電体材料は、4.0 以上、又は約 5.0 を超える、特には約 6.0 を超える誘電率を有している。いくつかの実施態様において、高 k 誘電体材料は、高 k 誘電体ポリマー (k がより高い誘電体ポリマー) である。高 k 誘電体ポリマーとしては、例えば、ポリイミド、ポリエステル、ポリエーテル、ポリアクリレート、ポリビニル、ポリケトン、及びポリスルホンを使用することができる。代表的な高 k 誘電体ポリマーとしては、以下のものが挙げられるが、これらに限定される訳ではない。例えば、ポリ(4-ビニルフェノール) (PVP)、ポリビニルアルコール、及びポリ(2-ヒドロキシルエチルメタクリレート) (PHEMA)、シアノエチル化ポリビニルアルコール、シアノエチル化セルロース、ポリフッ化ビニリデン (PVDF)、ポリ(ビニルピリジン)、それらのコポリマーなどが挙げられる。いくつかの実施態様において、高 k 誘電体材料は、PVP 及び / 又は PHEMA である。

#### 【0017】

いくつかの実施態様において、高 k 誘電体材料は、膜としてキャストしたとき、高い表面エネルギーを有している。前進水接触角で言えば、その角度が、例えば、80° 未満、又は約 60° 未満、又は約 50° 未満である。

#### 【0018】

いくつかの実施態様において、高 k 誘電体材料の誘電率と低 k 誘電体材料の誘電率との差は、少なくとも約 0.5、又は少なくとも約 1.0、又は少なくとも約 2.0 であって、例えば、約 0.5 ~ 約 200 である。

#### 【0019】

いくつかの実施態様において、相分離した本発明の誘電体構造物は、内部に生成した細孔 (ボイドや開口部と呼ばれることがある) を含む。他の実施態様においては、本発明の誘電体構造物が、そのような内部に生成した細孔を含まない (ただし、いくつかの実施態様においては、ピンホールが存在している可能性があるが、それらは意図的に生成させたものではなく、むしろ、本発明のプロセスにおける望ましくない副生物である)。いくつかの実施態様におけるピンホール密度は、例えば、50 個 / mm² 未満、又は 10 個 / mm²、又は 5 個 / mm² である。いくつかの実施態様においては、本発明の誘電体構造物がピンホールをまったく含まない。いくつかの実施態様においては、誘電体組成物が光画像化不能である。いくつかの実施態様においては、誘電体構造物中に細孔を生成させる工程を含まない。

#### 【0020】

いくつかの実施態様において、誘電体構造物は、約 4.0 を超える、又は約 5.0 を超える、特には約 6.0 を超える総合誘電率を有する。総合誘電率は、金属 / 誘電体構造物 / 金属コンデンサにより決定される。薄膜トランジスタ用途においては、特に、いくつかの実施態様においては、高い総合誘電率が望ましく、それによって、比較的低い電圧でそのデバイスを動作させることが可能である。

#### 【0021】

1種、2種又はそれ以上の適切な流動体が、液相析出を容易とさせる液体として使用することができる。いくつかの実施態様において、その液体は、低 k 誘電体材料及び高 k 誘電体材料を溶解させることができる。代表的な液体としては、以下のものが挙げられるが、これらに限定される訳ではない。例えば、水、アルコール、例えば、メタノール、エタノール、プロパノール、ブタノール及びメトキシエタノール、酢酸エステル、例えば、酢

10

20

30

40

50

酸エチル及びプロピレングリコールモノエチルエーテルアセテート、ケトン、例えば、メチルイソブチルケトン、メチルイソアミルケトン、アセトン、メチルエチルケトン及びメチルプロピルケトン、エーテル、例えば、石油エーテル、テトラヒドロフラン及びメチルt-ブチルエーテル、炭化水素、例えば、ヘキサン、シクロヘキサン、シクロペンタン、ヘキサデカン、イソオクタン、芳香族炭化水素、例えば、トルエン、キシレン、エチルベンゼン及びメシチレン、塩素系溶媒、例えば、クロロホルム、ジクロロメタン、ジクロロエタン、クロロベンゼン、ジクロロベンゼン及びトリクロロベンゼン、ならびに他の溶媒、例えば、ジメチルスルホキシド、トリフルオロ酢酸、アセトニトリル、ジメチルホルムアミド、ジメチルアセトアミド、ピリジン、n-メチル-アルファ-ピロリジノンが挙げられる。

10

## 【0022】

誘電体組成物中にその他の材料を添加することも可能である。代表的な材料としては、低k誘電体材料に係る及び/又は高k誘電体材料に係る架橋剤、例えば、ポリ(メラミン-c o -ホルムアルデヒド)が挙げられる。また、架橋触媒、例えば、トルエンスルホン酸を添加してもよいし、誘電率を高めるために使用される無機ナノ粒子、例えば、Al<sub>2</sub>O<sub>3</sub>、TiO<sub>2</sub>を添加してもよい。

## 【0023】

誘電体組成物中における上記成分のそれぞれの濃度は、約0.001～約99重量パーセントの間で変動する。低k誘電体材料の濃度は、例えば、約0.1～約30重量%、又は約1～約20重量%である。高k誘電体材料の濃度は、例えば、約0.1～約50重量%、又は約5～約30重量%である。架橋反応のための架橋剤及び触媒の濃度は、誘電体材料の濃度に依存する。架橋剤の誘電体材料に対する重量比率は、例えば、約1：99～約50：50、又は約5：95～約30：70である。触媒の誘電体材料に対する重量比率は、例えば、約1：9999～約5：95、又は約1：999～約1：99である。無機ナノ粒子は、例えば、約0.5～約30重量%、又は約1～約10重量%で添加することもできる。

20

## 【0024】

いくつかの実施態様において、低k誘電体材料と高k誘電体材料とは、誘電体組成物中で相分離していない。いくつかの実施態様において、「相分離していない」という表現は、例えば、低k誘電体材料と高k誘電体材料とが液体中に溶解していることを意味する。いくつかの実施態様において、「溶解している」という用語は、低k誘電体材料と高k誘電体材料とが液体の中に完全に溶解しているか、又は部分的に溶解していることを示している。いくつかの実施態様において、「相分離していない」という表現は、例えば、低k誘電体材料、高k誘電体材料、及び液体が混和性であって、ある範囲の温度、圧力、組成では単一相を形成していることを意味する。その温度範囲は、例えば、0～150、特にはほぼ室温である。その圧力は、例えば、約1気圧である。液相析出させる前の誘電体組成物中では、低k誘電体材料と高k誘電体材料とが、低k誘電体材料、高k誘電体材料及び液体を合計した重量を基準にして、例えば約0.1～約90重量パーセント、又は約0.5～約50重量パーセントの割合で存在することができる。低k誘電体材料と高k誘電体材料との比率は、例えば、約1：99～99：1、又は約5：95～約95：5まで、特には約10：90～約40：60とすることができます(最初の数値が、低k誘電体材料を表す)。

30

## 【0025】

低k誘電体材料、高k誘電体材料及び液体が混和性であって、液相析出する前には単一相(典型的には透明溶液)を形成しているいくつかの実施態様において、その単一相は、光散乱法によって確認するか、或いは器具を一切使用することなく人の目で視覚的に検出することが可能である。

40

## 【0026】

液相析出する前には、いくつかの実施態様において、誘電体組成物には、低k誘電体材料及び/又は高k誘電体材料の凝集物が含まれていてもよい。それらの凝集物は、例えば

50

、そのスケールが、可視光線の波長より短い、又は 100 nm 未満、特には 50 nm 未満であることが好ましい。本発明の目的に関して、それらの凝集物が、誘電体組成物中に存在している場合、それらが相分離した結果であるとか又は相分離されているとは考えられないし、さらにはこれらの凝集物が「第 1 の相」及び / 又は「第 2 の相」であるとは考えられない。

#### 【 0 0 2 7 】

誘電体組成物は、基板上に液相析出される。なお、各種適切な液相析出法を採用することができる。いくつかの実施態様において、液相析出法としては、ブランケットコーティング、例えば、スピンドルコーティング法、ブレードコーティング法、ロッドコーティング法、ディップコーティング法など、プリンティング（印刷法）、例えば、スクリーン印刷、インクジェット印刷、スタンプ、孔版印刷、スクリーン印刷、グラビア印刷、フレキソ印刷などが挙げられる。

#### 【 0 0 2 8 】

いくつかの実施態様において、液相析出は、单一工程で実施することができる。「单一工程」という用語は、1種の誘電体組成物から、第 1 及び第 2 の両方の誘電体材料を同時に液相析出させることを意味する。これは、2種の異なった誘電体材料が2種の異なった誘電体組成物から別々に液相析出する従来の2重層誘電体構造物を作製するためのプロセスとは異なる。「单一工程」における「工程」は、「パス」という用語とは異なる。いくつかの実施態様においては、誘電体構造物の厚みを増大させる目的で、誘電体組成物の单一工程析出の際に、2パス以上を実施することもできる。

#### 【 0 0 2 9 】

誘電体構造物を作製する場合、いくつかの実施態様において、本発明のプロセスには、低 k 誘電体材料及び高 k 誘電体材料の相分離を起こさせて、低 k 誘電体材料（多量）/高 k 誘電体材料（少量）の第 1 の相と、高 k 誘電体材料（多量）/低 k 誘電体材料（少量）の第 2 の相とを含む誘電体構造物を形成させることが含まれる。「起こさせる」という用語には、液体を蒸発させて液相析出する際に、相分離が自発的に起きることが含まれる。「起こさせる」という用語には、さらに、液相析出の途中又は後に、相分離を容易とするための外部的な支援が含まれ、いくつかの実施態様においては、例えば、加熱アニーリング及び / 又は溶媒アニーリングによって相分離を起こさせる。加熱アニーリングは、各種適切な温度、例えば、1つの誘電体材料のガラス転移温度又は融点よりも高い温度で実施することもできる。加熱アニーリングの時間は、具体的な誘電体の組合せに依存するが、例えば、約 1 分 ~ 約 1 日、又は約 1 分 ~ 1 時間とすることができる。溶媒アニーリングは、各種の温度、例えば、室温又は高温下で、1種又は複数の溶媒の蒸気に析出した誘電体構造物を暴露されることによって、実施することができる。代表的な溶媒は、例えば、本明細書の液相析出のところで述べたような液体から選択することができる。溶媒アニーリングの時間は、具体的な誘電体の組合せに依存するが、例えば、約数秒 ~ 約 1 週間、又は約 1 分 ~ 2 時間とすることができます。

#### 【 0 0 3 0 】

いくつかの実施態様において、「第 1 の相」及び「第 2 の相」における「相」という用語は、化学的組成のような性質が比較的均質であるような材料の單一又は複数のドメインを意味する。したがって、「中間相」という用語は、相分離された誘電体構造物の中の第 1 の相と第 2 の相との間の領域を指し、その中では、組成の傾斜が存在する。いくつかの実施態様において、誘電体構造物は、第 1 の相、任意の中間相、及び第 2 の相を有している。

#### 【 0 0 3 1 】

いくつかの実施態様において、本発明の相分離された誘電体構造物の「相分離された」状態は、以下に示すような第 1 の相と第 2 の相との代表的モルホロジーによって表わされる。

: (1) (層の形態にある) 第 1 の相と (層の形態にある) 第 2 の相との間に (層の形態にある) 中間相が存在する；

(2) 1 つの相が、他の相の連続マトリックスの中に複数の「ドット」を形成する；

(3) 1 つの相が、他の相の連続マトリックスの中に複数の

10

20

30

40

50

棒状の要素（例えば、円筒）を形成する；（4）1つの相が、他の相の中に相互貫入して、両連続ドメインを形成する。いくつかの実施態様においては、モルホロジー（2）、（3）、又は（4）が存在するが、（1）が存在しないこともある。

#### 【0032】

第1の相と第2の相とのモルホロジーに関連した「相分離された」状態は、各種の分析法、例えば、以下のような手段によって求めることができる。：誘電体構造物の表面及び断面の走査型電子顕微鏡法（SEM）及び原子間力顕微鏡法（AFM）分析；ならびに誘電体構造物の断面の透過型電子顕微鏡法（TEM）分析。その他の手法、例えば、光散乱法及びX線（広角及び小角X線）散乱法も使用可能である。

#### 【0033】

いくつかの実施態様において、中間相を含むモルホロジー（1）は、従来からの2層ゲート絶縁膜（中間相が傾斜した組成変化を含む境界層を有する）とは異なって、その界面層が傾斜組成変化ではなく、不連続的な組成変化を含む。また、別の違いとしては、本発明の中間相が比較的厚く、約10nm～約50nmの範囲の厚みを有しているが、これは従来からの2層ゲート絶縁膜（約5nm未満、特には約3nm未満の界面層厚みを有する）に見出されるいかななる界面層よりも明らかに厚い。

#### 【0034】

いくつかの実施態様において、第1の相は、多量の低k誘電体材料と、少量の高k誘電体材料とを含む。また、第2の相は、少量の低k誘電体材料と、多量の高k誘電体材料とを含む。「多量」という用語は、相分離された誘電体構造物の相中の低k誘電体材料と高k誘電体材料とを合計した重量の50重量%を超えていていることを意味している。いくつかの実施態様において、「多量」という用語は、誘電体構造物の相の中の51～100重量%、約55～約95重量%、又は約80～100重量%を意味している。

#### 【0035】

「少量」という用語は、誘電体構造物の相中の低k誘電体材料と高k誘電体材料とを合計した重量の50重量%未満であることを意味している。いくつかの実施態様においては、「少量」という用語は、誘電体構造物の相中の49～0重量%、約45～約5重量%、又は約20～0重量%を意味している。

#### 【0036】

いくつかの実施態様において、半導体を含む層に最も近い誘電体構造物の領域における低k誘電体材料の濃度は、高k誘電体材料の濃度よりも低い。

#### 【0037】

「領域」という用語は、半導体層に最も近い誘電体構造物の（その誘電体構造物の表面に平行な）薄層を指している。当該領域を検査して、低k誘電体材料と高k誘電体材料の濃度を求める。いくつかの実施態様において、その領域には、第1の相の一部又は全部と、場合によっては第2の相の一部又は全部とが含まれる。いくつかの実施態様においては、任意の界面層が、誘電体構造物の中に存在していてもよく、その結果、領域に界面層が含まれてもよいが、それは、領域が、第1の相の一部又は全部と、場合によっては第2の相の一部又は全部とを含むのに十分な厚みを有する場合に限られる。領域は、分析に使用できる厚み、例えば、約1nm～約100nm、又は約5nm～約100nm、特には約5nm～約50nmの厚みを有している。第1の誘電体材料及び第2の誘電体材料の濃度を求めるには、種々の方法を使用することができる。例えば、X線光電子分光法（XPS）を使用して、領域中の複数の誘電体材料のそれぞれの原子濃度を分析することができる。AFMを使用すれば、複数の相のドメインサイズを求めることができる。領域の断面部分のTEMを使用しても、複数の相のドメインサイズと、複数の誘電体材料のそれぞれの原子濃度を求めることができる。ある実施態様においては、複数の方法を組み合わせて使用してもよい。複数の方法で結果が大きく異なるような場合には、TEM分析の結果を優先する。

#### 【0038】

「領域」のいくつかの実施態様において、高k誘電体材料は、例えば、約60%～10

10

20

30

40

50

0 %、約 60 %～約 90 %、又は約 80 %～100 %の範囲の濃度であり、低 k 誘電体材料は、約 40 %～0 %、約 40 %～約 10 %、又は約 20 %～0 %の範囲の濃度である。当該濃度は、各種因子によって調節することが可能であって、そのような因子としては、例えば、以下のものが挙げられる。例えば、誘電体組成物中の低 k 誘電体材料と高 k 誘電体材料との初期比、誘電体組成物中の誘電体材料の濃度、誘電体材料の混和性、アニーリング時間及びアニーリング温度のような加工条件が挙げられる。

#### 【0039】

相分離をさせるために、いくつかの実施態様においては、固相状態において非混和性であるか又は部分的にしか混和しない低 k 誘電体材料及び高 k 誘電体材料を選択することができる。2種のポリマー等の2種の誘電体材料の混和性（混合物が单一相を形成する能力）は、それらの相互作用パラメータにより予想することができる。一般的に、ポリマーは、それと類似したポリマーと混和性がある。10

#### 【0040】

いくつかの実施態様において、誘電体構造物が多層構造である場合（モルホロジー（1））には、第1の相の厚みが、例えば、約 1 nm～約 500 nm、又は約 5 nm～約 200 nm、又は約 5 nm～約 50 nm である。第2の相の厚みは、例えば、約 5 nm～約 2 μm（2000 nm）、又は約 10 nm～約 500 nm、又は約 100 nm～約 500 nm である。誘電体構造物全体の厚みは、例えば、約 10 nm～約 2 μm、又は約 200 nm～約 1 μm、又は約 300～約 800 nm である。20

#### 【0041】

いくつかの実施態様において、誘電体構造物中の低 k 誘電体材料は架橋されている。いくつかの実施態様において、誘電体構造物中の低 k 誘電体材料は自己架橋されている。いくつかの実施態様において、誘電体構造物中の低 k 誘電体材料は熱的に自己架橋されている。いくつかの実施態様において、誘電体構造物中の低 k 誘電体材料及び高 k 誘電体材料の両方が架橋されている。20

#### 【0042】

いくつかの実施態様において、相分離する誘電体構造物は、例えば、それぞれ異なったポリマーである低 k 誘電体材料及び高 k 誘電体材料のポリマーブレンド物を含む。いくつかの実施態様において、ポリマーブレンド物は、2成分系ブレンド物である。他の実施態様において、ポリマーブレンド物は、それぞれ第3又は第4の誘電体材料を添加した3成分系ブレンド物又は4成分系ブレンド物である。なお、本明細書では、「ブレンド物」という用語は、2種以上の材料が存在していることを単に示しているのであって、その第1の相及び第2の相における低 k 誘電体材料及び k が高い誘電体材料の濃度や分布を意味している訳ではない。本発明の開示のさらなる態様は、相分離するポリマーブレンドゲート絶縁膜である薄膜トランジスタに関する。30

#### 【0043】

半導体層と誘電体構造物との間には、任意の界面層が存在していてもよい。

#### 【0044】

本発明は、いくつもの利点を有している。第1には、いくつかの実施態様におけるプロセスでは、任意の単一工程の特性を使用することによって、複数の誘電体材料を多段工程で析出させることを回避できる。第2には、いくつかの実施態様において、相分離するポリマーブレンド誘電体は、複数のポリマーの利点を組み合わせることによって、より良好な性質を有することができる。誘電体構造物は、各種適切な方法を用いて形成することができる。いくつかの実施態様において、誘電体構造物は、上記相分離プロセスを使用して形成される。誘電体構造物は、誘電体組成物の単一析出工程により作製され、低 k 誘電体材料及び高 k 誘電体材料は、相分離して異なった相となる。他の実施態様において、誘電体構造物は、誘電体材料の多段工程析出によって形成される。例えば、低 k 誘電体材料を析出させ、次いで、低 k 誘電体材料の上に、高 k 誘電体材料を析出させる。40

#### 【0045】

いくつかの実施態様において、誘電体構造物は、相分離された誘電体構造物である。い50

くつかの実施態様において、トランジスタは、トップゲートトランジスタであり、その誘電体が、誘電体組成物の单一工程析出によって形成される。誘電体構造物は、低k誘電体ポリマー及び高k誘電体ポリマーを含み、トップゲートトランジスタの半導体層に最も近い誘電体構造物の領域において、低k誘電体ポリマーは、高k誘電体ポリマーよりも低濃度である。

#### 【0046】

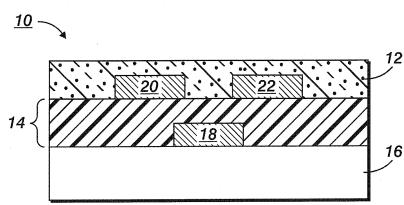

図1において、有機薄膜トランジスタ(「OTFT」)構造10を模式的に示す。OTFT構造10は、基板16、基板16に接触する金属接点18(ゲート電極)及びゲート絶縁膜14、ゲート絶縁膜14上に、2つの金属接点、即ち、ソース電極20及びドレイン電極22を備える。金属接点20及び22の上及び間には、本明細書において説明した有機半導体層12がある。

10

#### 【0047】

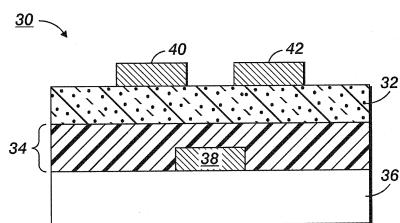

図2は、OTFT構造30を模式的に示す図である。OTFT構造30は、基板36、ゲート電極38、ソース電極40及びドレイン電極42、ゲート絶縁膜34、ならびに有機半導体層32を備える。

#### 【0048】

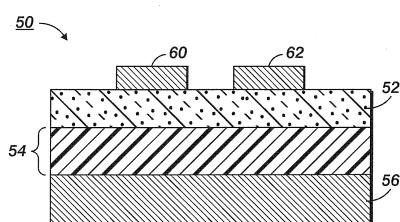

図3は、OTFT構造50を模式的に示す図である。OTFT構造50は、基板及びゲート電極の両方の役割を果たす、重でにnドープしたシリコンウェハ56、ゲート絶縁膜54、及び有機半導体層52を備え、有機半導体層52の上に、ソース電極60及びドレイン電極62が配置されている。

20

#### 【0049】

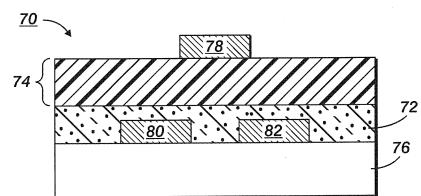

図4は、OTFT構造70を模式的に示す図である。OTFT構造70は、基板76、ゲート電極78、ソース電極80、ドレイン電極82、有機半導体層72、及びゲート絶縁膜74を備える。

#### 【0050】

基板としては、例えば、シリコン、ガラスプレート、プラスチックフィルム又はシートなどを用いることができる。構造的に可撓性のあるデバイスとするためには、プラスチック基板、例えば、ポリエステル、ポリカーボネート、ポリイミドのシートなどを用いることが好ましい。

#### 【0051】

30

ゲート電極は、金属薄膜、導電性ポリマー膜、導電性のインキ又はペーストから作製された導電性膜などであってもよく、或いは、例えば、重でにドープしたシリコンのように、基板そのものをゲート電極とすることができます。ゲート電極層の厚みは、例えば、金属膜の場合で約10～約200nmの範囲、導電性ポリマーの場合で約1～約10μmの範囲である。

#### 【0052】

ソース電極層及びドレイン電極層は、半導体層に対して低抵抗オーム性接触を与える材料から選択して作製することができる。ソース電極及びドレイン電極として好適な材料としては、ゲート電極材料を挙げることができ、例えば、金、ニッケル、アルミニウム、白金、導電性ポリマー及び導電性インキなどが挙げられる。ソース電極及びドレイン電極の厚みは、典型的には、例えば、約40nm～約10nm、より詳しくは約100nm～約400nmである。

40

#### 【0053】

有機半導体層として好適な材料としては、アセン、例えば、アントラセン、テトラセン、ペンタセン、及び置換ペンタセン、ペリレン、フラーん、フタロシアニン、オリゴチオフェン、ポリチオフェン、及びそれらの置換誘導体などが挙げられる。いくつかの実施態様においては、液相加工可能な材料から有機半導体層を形成する。半導体層は、各種好適な手段により形成させることが可能であるが、そのような方法としては、真空蒸発法、スピンドルコート法、溶液キャスト法、ディップコート法、ステンシル／スクリーン印刷法、フレキソ印刷法、グラビア印刷法、オフセット印刷法、インキジェット印刷法、ミクロコ

50

ンタクト印刷法、それらの方法に組合せなどが挙げられるが、これらに限定される訳ではない。いくつかの実施態様において、半導体層の厚みは、約10nm～約1μmである。

#### 【0054】

ゲート絶縁膜の組成と構造については、本明細書に記載されている。いくつかの実施態様においては、ゲート絶縁膜の第1の相と第2の相とが相互に接触しており、他の実施態様においては、第1の相と第2の相との間に中間相が存在している。いくつかの実施態様においては、ゲート絶縁膜の第1の相が半導体層と接触しており、他の実施態様においては、その第1の相と半導体層との間に界面層が存在している。いくつかの実施態様においては、ゲート絶縁膜の第1の相及び第2の相の両方が半導体層と接触している。他の実施態様においては、ゲート絶縁膜の第1の相と第2の相の両方が半導体層と接触しており、その半導体層と第1の相との間の接触面積が、薄膜トランジスタのチャネル領域（電源とドレイン電極との間の領域）における半導体層と第2の相との間の接触面積よりも大きい。10

#### 【0055】

ゲート絶縁膜、ゲート電極、半導体層、ソース電極、及びドレイン電極は、いかなる順で形成されてもよい。いくつかの実施態様においては、ゲート電極及び半導体層が両方ともゲート絶縁膜と接触状態にあり、ソース電極及びドレイン電極が両方とも半導体層と接触状態にある。「いかなる順でもよい」という用語は、順次に形成させていくことと、同時に形成させることの両方を意味している。例えば、ソース電極とドレイン電極とは、同時に形成させることもできるし、或いは順次形成させることもできる。20

#### 【0056】

ここで、本発明の具体的な実施態様例を用いて、本発明を詳細に説明するが、それらの例は説明のためだけのものであり、本明細書に記載する、物質、条件、プロセスパラメータによって本発明が限定を受けることを意図するものではない。特に断らない限り、パーセント及び部はすべて、重量基準である。本明細書において、室温とは、例えば、約20～約25の範囲の温度を指す。20

#### 【0057】

比較例1

#### 【0058】

比較例1において、ゲート絶縁膜は、低k誘電体材料であるポリ(メチルシルセスキオキサン)(PMSSQ)から調製した。PMSSQ溶液は、前駆体としてメチルトリメトキシシランを使用し、以下の手順に従って調製した。0.88gの0.1重量%塩酸水溶液と、5.13gのテトラヒドロフランの混合物とを、氷浴を用いて冷却された3口フラスコの4.08gのメチルトリメトキシシランと、9.24gのメチルイソブチルケトンとの混合物に、乾燥雰囲気下で激しく攪拌しながら30分かけて滴下した。得られた混合物を放置して室温にまで温め、その状態で5分置いてから、60にまで加熱して、その状態で24時間維持した。30

#### 【0059】

PMSSQ絶縁層を用いて、図4に示すようなトップゲートトランジスタを作製した。予め清浄化しておいたガラス基板の上に、ソースドレイン電極を、シャドーマスクを用いた真空蒸着法により設けた。ポリ(3,3'-(ジドデシル-クオーター-チオフェン)(PQT-12)半導体層(PQT-12は、ベン・S.オン(Beng S. On)ら、ジャーナル・オブ・ジ・アメリカン・ケミカル・ソサイエティ(J. Am. Chem. Soc., 2004, 126, 3378~3379に開示されているが、その開示はすべて参考として引用し本明細書に組み入れるものとする)を、スピンドル法によりソースドレイン電極の上に設けた。80で30分間かけて乾燥させてから、半導体層を140

で10～15分間真空炉でアニールさせた。誘電体組成物は、まず、0.2ミクロンのシリジフィルターで濾過し、次いで、2000rpmで半導体層の上にスピンドルコートした。80で10分間かけて乾燥させてから、真空炉で、140で30分間かけて誘電体層(絶縁層)を加熱架橋させた。その絶縁層の上にA1ゲート電極を真空蒸着すること4050

により、O TFT デバイスを完成させた。それらのデバイスは、Keithley 4200 SCS を用いて特性評価した。この誘電体構造を有するO TFT は、絶縁層の漏洩のために極めて低いデバイス収率 (< 10%) を示した。機能デバイスは、0.06 cm<sup>2</sup>/V·s の移動度と、100 ~ 1000 の電流オンオフ比を示した。

#### 【0060】

実施例 1

#### 【0061】

実施例 1においては、低 k 誘電体材料及び高 k 誘電体材料の両方を含む誘電体組成物を使用した。低 k 誘電体材料としては、PMSSQ を使用し、高 k 誘電体材料としては、ポリ(4-ビニルフェノール) (PVP) を使用した。高 k 誘電体材料の PVP には、架橋剤としてポリ(メラミン-co-ホルムアルデヒド)を添加した。なお、表 1 に示す重量の材料を使用して、誘電体組成物の配合を行った。

#### 【0062】

【表 1】

| 材料                                                | 重量 (g) |

|---------------------------------------------------|--------|

| 液体； n-ブタノール                                       | 0.9    |

| 高 k 誘電材料； PVP                                     | 0.077  |

| 低 k 誘電材料； PMSSQ (25 重量% 溶液)                       | 0.116  |

| 架橋剤； ポリ(メラミン-co-ホルムアルデヒド) (メチル化物、n-ブタノール中 84 重量%) | 0.08   |

#### 【0063】

その誘電体組成物を使用して、比較例 1 の記載に従ってトップゲートトランジスタを作製した。予め清浄化しておいたガラス基板の上に、シャドーマスクを用いた真空蒸着法によりソースドレイン電極の対を設けた。次いで、スピンドルコート法により、PQT-12 半導体を設けた。半導体層を乾燥、アニールさせてから、誘電体組成物を 0.2 ミクロンのシリジフィルターを用いて濾過してから、半導体層の上にスピンドルコートした。得られた誘電体層(絶縁層)を、まず、80°で 10 分間かけて乾燥させ、次いで、真空炉で、140°で 30 分間かけて、加熱アニーリングと架橋を行わせた。その絶縁層の上に A1 ゲート電極を真空蒸着させることにより、O TFT デバイスを完成させた。

#### 【0064】

ゲート絶縁膜層の特性評価：水接触角測定では、100°の前進接触角を示し、これは、極めて高い疎水性表面であることを表している。極めて疎水性が高いという特性は、スピンドルコート法及び加熱架橋の間に、PMSSQ 成分が絶縁層の表面に移行して、相分離した誘電体構造物が形成されたことを証明している。

#### 【0065】

相分離が起きたことは、さらに、誘電体構造物の XPS 測定によっても確認された。表面の定量的 XPS 分析から、次のような原子%であることが判った。Si ; 27.8%、O ; 38.7%、C ; 33.4%。表面上の PVP 中に芳香族炭素原子が顕著な量で存在していることを裏付ける強い証拠は無かった。低 k 誘電体材料の PMSSQ だけに存在している Si が、表面領域 (数 nm) で高い原子%となっている。高 k 誘電体材料の架橋剤だけに存在している N 原子が、表面には存在しなかった。相分離した誘電体構造物の XPS 解析の深さ方向分布から、表面上から 40 nm の部分に PMSSQ が分散していることがわかった。表面上から 40 nm の領域において、第 1 の誘電体材料の PMSSQ に由来する O 原子と S 原子が高い濃度で存在することが見出された。なお、N 原子濃度は、表面上より 40 nm 離れた位置から一定であった。

10

20

30

40

50

上記分析結果を総合的に判断すると、誘電体構造物は、PMSQ（低k誘電体材料）の多量相が誘電体構造物のトップにあり、架橋されたPVP（高k誘電体材料）の多量相が、半導体層に最も近い誘電体構造物の底部分にある、相分離構造であることがわかる。

#### 【0066】

OTFTデバイスの特性評価：それらのデバイスは、Keithley 4200 SCS を用いて特性評価した。半導体層に最も近いところに、高kポリマーの多量相を有する誘電体構造のOTFTは、大幅に改良されたデバイス収率(>90%)を示した。これらのデバイスは、 $0.1 \text{ cm}^2 / \text{V} \cdot \text{s}$  の平均移動度と、電流オンオフ比 10,000 を示した。

#### 【0067】

実施例1及び比較例1から、相分離した低k誘電体材料と高k誘電体材料とのブレンド物を有するデバイスは、高い移動度と高い電流オンオフ比の両方を示すということがよくわかる。

#### 【符号の説明】

#### 【0068】

10、30、50、70 有機薄膜トランジスタ(OTFT)構造、12、32、52、72 有機半導体層、14、34、54、74 ゲート絶縁膜(ゲート誘電体)、16 基板、18 金属接点、20、40、60、80 ソース電極、22、42、62、82 ドレイン電極、38、78 ゲート電極、56 シリコンウェハ。

10

【図1】

【図4】

【図2】

【図3】

---

フロントページの続き

(51)Int.Cl.

F I

H 0 1 L 29/28 2 8 0

合議体

審判長 小野田 誠

審判官 恩田 春香

審判官 加藤 浩一

(56)参考文献 特開2005-72569 (JP, A)

特開2008-258609 (JP, A)

特表2005-513818 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L29/786

H01L21/336

H01L51/05-51/40