(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4573863号

(P4573863)

(45) 発行日 平成22年11月4日(2010.11.4)

(24) 登録日 平成22年8月27日(2010.8.27)

(51) Int.Cl.

H01S 5/323 (2006.01)

F 1

H01S 5/323 610

請求項の数 4 (全 24 頁)

(21) 出願番号 特願2007-283225 (P2007-283225)

(22) 出願日 平成19年10月31日 (2007.10.31)

(65) 公開番号 特開2008-160070 (P2008-160070A)

(43) 公開日 平成20年7月10日 (2008.7.10)

審査請求日 平成20年5月22日 (2008.5.22)

(31) 優先権主張番号 特願2006-323582 (P2006-323582)

(32) 優先日 平成18年11月30日 (2006.11.30)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74) 代理人 100104433

弁理士 宮園 博一

(72) 発明者 別所 靖之

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(72) 発明者 野村 康彦

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

(72) 発明者 畑 雅幸

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

最終頁に続く

(54) 【発明の名称】窒化物系半導体素子の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に、第1の方向に延びる光導波路を有する窒化物系半導体層を形成する工程と、前記光導波路の延びる前記第1の方向と交差する第2の方向に沿って、前記窒化物系半導体層が形成された前記基板に対して、第1の分割を行う工程と、

前記第1の分割を行う工程の後、前記第1の分割を行う工程により分割された前記基板の前記窒化物系半導体層が形成された側とは反対側の表面で、かつ、前記第2の方向に延びる前記第1の分割により形成された分割面から所定の距離を隔てた領域に、レーザ光を照射することにより前記第1の方向に延びる素子分割用溝を形成する工程と、

前記素子分割用溝に沿って第2の分割を行うことにより窒化物系半導体素子を形成する工程とを備え、

前記基板は、前記第1の方向に延びるとともに、前記第2の方向に所定の間隔で複数設けられる欠陥集中領域を有し、

前記基板上に第1の方向に延びる光導波路を有する窒化物系半導体層を形成する工程は、前記第1の方向に延びる隣接する前記欠陥集中領域の間に、少なくとも2つの前記光導波路を形成する工程を含み、

前記第1の分割を行う工程は、

前記欠陥集中領域を含み、かつ、前記光導波路を含まない領域に、レーザ光を照射することにより、前記第2の方向に延びるように前記欠陥集中領域毎に設けられる破線状の劈開用溝を形成する工程とを含む、窒化物系半導体素子の製造方法。

10

20

**【請求項 2】**

前記基板に素子分割用溝を形成する工程は、前記欠陥集中領域と、前記光導波路間の中央とに、前記素子分割用溝を形成する工程を含む、請求項1に記載の窒化物系半導体素子の製造方法。

**【請求項 3】**

隣接する前記光導波路間の中央から前記光導波路までの距離は、前記欠陥集中領域から前記光導波路までの距離以下の大きさである、請求項2に記載の窒化物系半導体素子の製造方法。

**【請求項 4】**

前記第1の分割を行う工程と、前記第2の分割を行うことにより窒化物系半導体素子を形成する工程とを行った後に、前記窒化物系半導体層側、または、前記基板側のいずれか一方を、融着層を介して放熱基台に取り付ける工程をさらに備える、請求項1～3のいずれか1項に記載の窒化物系半導体素子の製造方法。 10

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、窒化物系半導体素子の製造方法に関し、特に、素子分割用溝を形成する工程を備えた窒化物系半導体素子の製造方法に関する。 20

**【背景技術】****【0002】**

従来、素子分割用溝を形成する工程を備えた窒化物系半導体素子の製造方法が知られている（たとえば、特許文献1参照）。

**【0003】**

上記特許文献1には、GaN基板上にリッジ部（光導波路）を有する半導体層を形成する工程と、所定の方向に沿って劈開を行うことによりレーザ共振器バーを形成する工程と、スクライバー（ダイヤモンド針）などを用いて、半導体層側からレーザ共振器バーに素子分離溝（素子分割用溝）を形成する工程と、レーザ共振器バーを素子分離溝に沿って分割することにより半導体レーザ素子を形成する工程とを備えた半導体素子の製造方法が開示されている。 30

**【0004】****【特許文献1】特開2005-136093号公報****【発明の開示】****【発明が解決しようとする課題】****【0005】**

しかしながら、上記特許文献1の製造方法では、スクライバー（ダイヤモンド針）などを用いて半導体層側からレーザ共振器バーに素子分離溝（素子分割用溝）を形成するので、素子分離溝を形成する際に、スクライバー（ダイヤモンド針）を半導体層に接触させることに起因して、半導体層に割れや欠けが発生し、リッジ部（光導波路）にダメージを与えるという不都合がある。その結果、リッジ部が損傷する場合があるという問題点がある。 40

**【0006】**

この発明は、上記のような課題を解決するためになされたものであり、この発明の1つの目的は、光導波路が損傷するのを抑制することが可能な窒化物系半導体素子の製造方法を提供することである。

**【課題を解決するための手段】****【0007】**

上記目的を達成するために、この発明の第1の局面による窒化物系半導体素子の製造方法は、基板上に、第1の方向に延びる光導波路を有する窒化物系半導体層を形成する工程と、光導波路の延びる第1の方向と交差する第2の方向に沿って第1の分割を行う工程と 50

、基板の窒化物系半導体層が形成された側とは反対側の表面で、かつ、第2の方向に延びる第1の分割による分割面から所定の距離を隔てた領域に、レーザ光を照射することにより第1の方向に延びる素子分割用溝を形成する工程と、素子分割用溝に沿って第2の分割を行うことにより窒化物系半導体素子を形成する工程とを備えている。

#### 【0008】

この第1の局面による窒化物系半導体素子の製造方法では、上記のように、基板の窒化物系半導体層が形成された側とは反対側の表面に、レーザ光を照射することにより第1の方向に延びる素子分割用溝を形成することによって、レーザ光を用いて非接触の状態で、基板に素子分割用溝を形成することができるので、素子分割用溝を形成する際に窒化物系半導体層に割れや欠けが発生するのを抑制することができる。これにより、窒化物系半導体層の光導波路が損傷するのを抑制することができる。また、基板の第1の分割による分割面から所定の距離を隔てた領域に、レーザ光を照射することにより素子分割用溝を形成することによって、素子分割用溝を光導波路の分割面から離れた位置に形成することができるので、レーザ光を照射することにより素子分割用溝を形成する際に、基板の材料などが蒸発して粉状になったものが光導波路の分割面に付着するのを抑制することができる。これにより、光導波路から出射される光の強度が低下するのを抑制することができる。また、基板の窒化物系半導体層が形成された側とは反対側の表面に、レーザ光を照射することにより素子分割用溝を形成することによって、素子分割用溝を窒化物系半導体層の光導波路からさらに離れた位置に形成することができるので、レーザ光を照射することにより素子分割用溝を形成する際に、基板の材料などが蒸発して粉状になったものが光導波路の分割面に付着するのをより抑制することができる。これにより、光導波路から出射される光の強度が低下するのをより抑制することができる。10

#### 【0009】

上記構成において、好ましくは、基板は、第1の方向に延びるとともに、第2の方向に所定の間隔で複数設けられる欠陥集中領域を有する。このように構成すれば、欠陥集中領域に第1の方向に延びる素子分割用溝を形成すれば、欠陥集中領域を素子端部に形成することができるので、通常、素子の中央部側に配置される光導波路を欠陥集中領域から離れた領域に形成することができる。これにより、光導波路の結晶欠陥が増加するのを抑制することができる。20

#### 【0010】

上記基板が欠陥集中領域を有する構成において、好ましくは、基板上に第1の方向に延びる光導波路を有する窒化物系半導体層を形成する工程は、第1の方向に延びる隣接する欠陥集中領域の間に、少なくとも2つの光導波路を形成する工程を含み、基板に素子分割用溝を形成する工程は、欠陥集中領域と、光導波路間の中央とに、素子分割用溝を形成する工程を含む。このように構成すれば、隣接する欠陥集中領域間に2つ以上の窒化物系半導体素子を形成することができるので、1つの半導体ウェハに対する窒化物系半導体素子の取れ数を多くすることができる。30

#### 【0011】

上記基板上に窒化物系半導体層を形成する工程が隣接する欠陥集中領域間に少なくとも2つの光導波路を形成する工程を含む構成において、好ましくは、隣接する光導波路間の中央から光導波路までの距離は、欠陥集中領域から光導波路までの距離以下の大きさである。このように構成すれば、光導波路を欠陥集中領域から離れた位置に形成することができる。レーザ光を照射することにより素子分割用溝を形成する場合、欠陥集中領域では光の吸収が増大し高温になりやすいので、光導波路を欠陥集中領域から離れた位置に形成することにより、光導波路が高温になりすぎるので抑制することができる。これにより、素子分割用溝を形成する際に、光導波路が損傷するのをより抑制することができる。40

#### 【0012】

上記基板が欠陥集中領域を有する構成において、好ましくは、第1の分割を行う工程は、少なくとも窒化物系半導体層の欠陥集中領域を含み、かつ、光導波路を含まない領域に、レーザ光を照射することにより、第2の方向に延びるように欠陥集中領域毎に設けられ50

る破線状の劈開用溝を形成する工程と、劈開用溝に沿って劈開を行うことにより共振器面を形成する工程とを含む。このように構成すれば、光導波路に劈開用溝を形成することなく、劈開を行うことができるので、光導波路の分割面を、容易に、劈開面とすることができる。

#### 【0013】

上記第1の局面による窒化物系半導体素子の製造方法において、好ましくは、第1の分割を行う工程と、第2の分割を行うことにより窒化物系半導体素子を形成する工程を行った後に、窒化物系半導体層側、または、基板側のいずれか一方を、融着層を介して放熱基台に取り付ける工程をさらに備える。このように構成すれば、融着層が、表面から窪んだ劈開用溝または素子分割用溝にも入り込んで固着するので、窒化物系半導体素子を放熱基台に安定して固定することができる。この結果、レーザ出射光の軸ずれが生じるのを抑制することができる。10

#### 【0014】

上記第1の局面による窒化物系半導体素子の製造方法によって形成された窒化物系半導体素子は、窒化物系半導体からなる基板と、基板上に形成され、第1の方向に延びる光導波路が形成された窒化物系半導体からなる窒化物系半導体層と、少なくとも光導波路の端面近傍を除く領域に、光導波路の延びる第1の方向に沿って基板の窒化物系半導体層が形成された側とは反対側の表面に形成された第1の段差部とを備える。

#### 【0015】

上記第1の局面による窒化物系半導体素子の製造方法によって形成された窒化物系半導体素子では、上記のように、第1の方向に沿って基板の窒化物系半導体層が形成された側とは反対側の表面に形成された第1の段差部を備えることによって、第1の段差部は、基板上の窒化物系半導体層から離れた位置に形成されるので、窒化物系半導体層に割れや欠けが発生するのを抑制することができる。これにより、窒化物系半導体層の光導波路が損傷するのを抑制することができる。また、光導波路の端面近傍を除く領域に第1の段差部を備えることによって、レーザ光を照射することにより第1の段差部（素子分割用溝）を形成する際に、基板の材料などが蒸発して粉状になったものが光導波路の端面（分割面）に付着するのを抑制することができる。これにより、光導波路から出射される光の強度が低下するのを抑制することができる。また、第1の方向に沿って基板の窒化物系半導体層が形成された側とは反対側の表面に形成された第1の段差部を備えることによって、第1の段差部（素子分割用溝）は窒化物系半導体層の光導波路からさらに離れた位置に形成されるので、レーザ光を照射することにより第1の段差部（素子分割用溝）を形成する際に、基板の材料などが蒸発して粉状になったものが光導波路の端面（分割面）に付着するのをより抑制することができる。これにより、光導波路から出射される光の強度が低下するのをより抑制することができる。2030

#### 【0016】

上記第1の局面による窒化物系半導体素子の製造方法によって形成された窒化物系半導体素子において、好ましくは、第1の方向における第1の段差部の長さは、第1の方向における光導波路の端面間距離の5分の1以上である。このように構成すれば、第1の方向に沿って素子分割を行う際に、予め第1の段差部（素子分割用溝）が光導波路の端面間距離の5分の1以上の長い領域に形成されているので、第1の段差部を起点として第1の方向に容易に素子分割を行うことができる。これにより、窒化物系半導体層に割れや欠けが発生するのをより抑制することができる。40

#### 【0017】

上記第1の局面による窒化物系半導体素子の製造方法によって形成された窒化物系半導体素子において、好ましくは、基板は、光導波路の延びる第1の方向に延びるとともに、第1の方向と交差する第2の方向に所定の間隔で複数設けられる欠陥集中領域を有し、少なくとも窒化物系半導体層の欠陥集中領域を含み、かつ、光導波路近傍の端面を含まない領域に、光導波路から所定の距離を隔てて、第2の方向に延びるように欠陥集中領域毎に第2の段差部が形成されている。このように構成すれば、欠陥集中領域に第1の方向に延50

びる第1の段差部(素子分割用溝)を形成した場合、欠陥集中領域を素子端部に形成することができるので、通常、素子の中央部側に配置される光導波路を欠陥集中領域から離れた領域に形成することができる。これにより、光導波路の結晶欠陥が増加するのを抑制することができる。また、少なくとも窒化物系半導体層の欠陥集中領域を含み、かつ、光導波路近傍の端面を含まない領域に、光導波路から所定の距離を隔てて、第2の方向に延びるように欠陥集中領域毎に第2の段差部を形成すれば、光導波路に第2の段差部(劈開用溝)を形成することなく劈開を行うことができるので、光導波路の端面を、容易に、劈開面とすることができます。

#### 【0018】

上記窒化物系半導体層の第2の方向に延びるように欠陥集中領域毎に第2の段差部を形成する構成において、好ましくは、第2の方向における第2の段差部の長さは、第2の方向における光導波路を含む端面の幅の20分の1以上である。このように構成すれば、第2の方向に沿って劈開を行う際に、予め第2の段差部(劈開用溝)が光導波路を含む端面の幅の20分の1以上の長い領域に形成されているので、第2の段差部を起点として第2の方向に、より容易に、劈開することができる。10

#### 【0019】

上記第1の局面による窒化物系半導体素子の製造方法によって形成された窒化物系半導体素子において、好ましくは、窒化物系半導体層側、または、基板側のいずれか一方が、融着層を介して放熱基台に取り付けられている。このように構成すれば、融着層が、表面から窪んだ劈開用溝または素子分割用溝にも入り込んで固着するので、窒化物系半導体素子を放熱基台に安定して固定することができる。この結果、レーザ出射光の軸ずれが生じるのを抑制することができる。20

#### 【発明を実施するための最良の形態】

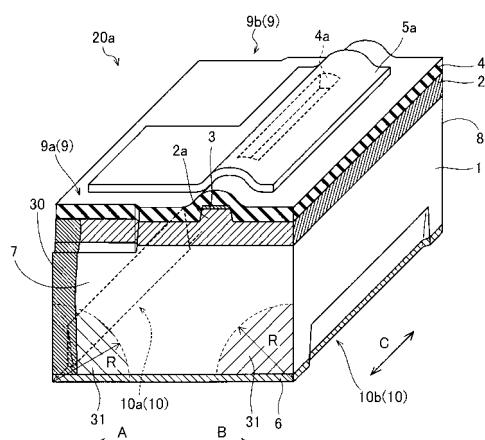

#### 【0020】

##### (第1実施形態)

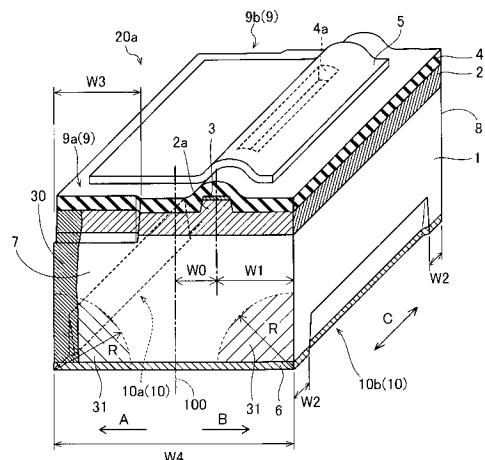

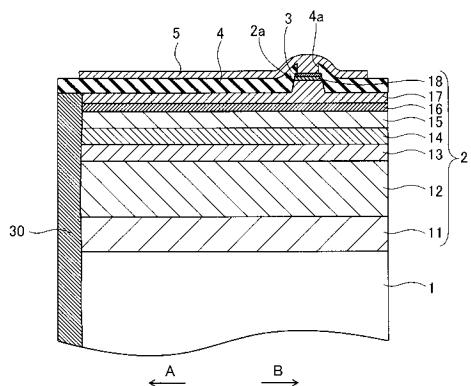

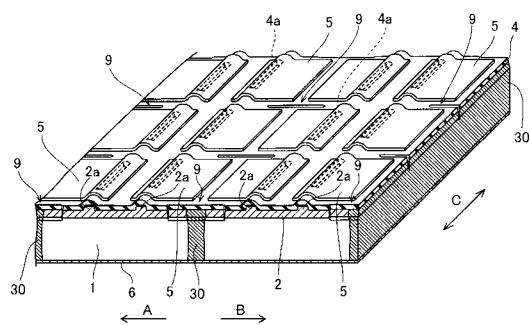

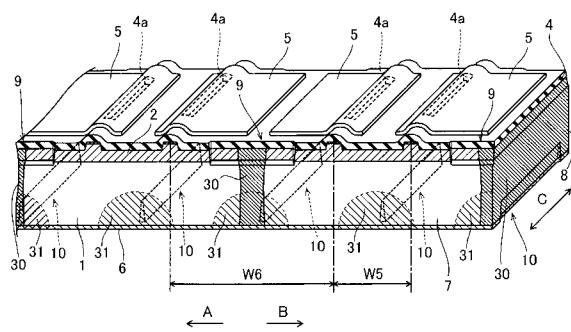

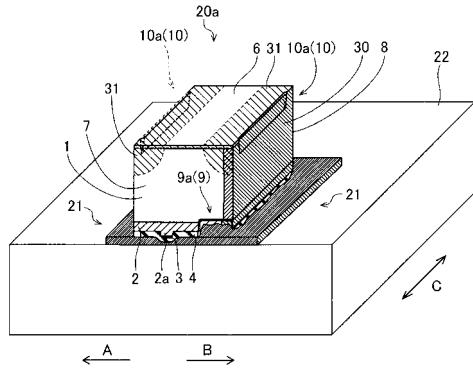

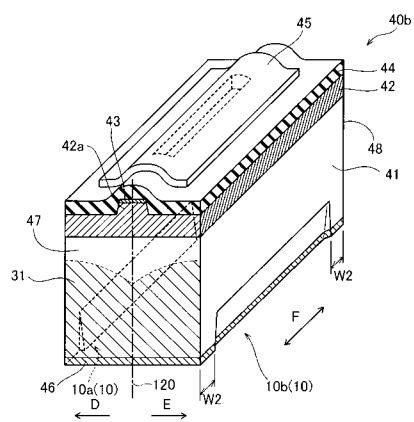

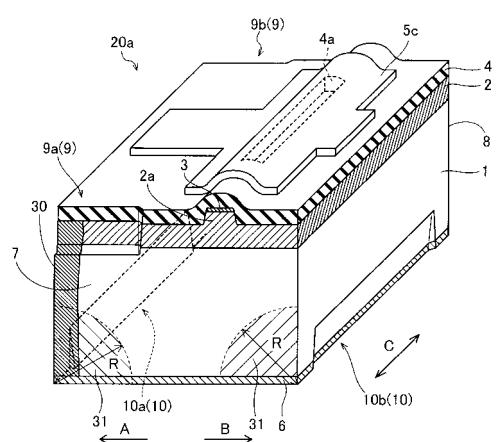

図1は、本発明の第1実施形態によるGaN系半導体レーザチップの製造プロセスにより形成された構造の一例を示した斜視図である。図2は、図1に示したGaN系半導体レーザチップの中央付近の半導体層の詳細構造を示した断面図である。まず、図1および図2を参照して、第1実施形態によるGaN系半導体レーザチップの製造プロセスにより形成された構造の一例(半導体レーザチップ20a)について説明する。なお、第1実施形態によるGaN系半導体レーザチップは、400nm帯域の発振波長を有する半導体レーザチップ(青紫色レーザダイオード)である。30

#### 【0021】

第1実施形態の一例による半導体レーザチップ20aでは、図1に示すように、n型GaN基板1上に、後述する活性層14(図2参照)を含むとともに、pn接合を有する窒化物系の半導体層2が形成されている。なお、n型GaN基板1は、本発明の「基板」の一例である。

#### 【0022】

ここで、第1実施形態の一例による半導体レーザチップ20aでは、図1に示すように、n型GaN基板1および半導体層2の一方側(矢印A方向側)の端部には、結晶欠陥の多い直線状の欠陥集中領域30が形成されている。このn型GaN基板1は、所定の領域(欠陥集中領域30)に結晶欠陥を集中して形成することにより、それ以外の広い領域の結晶欠陥を低減させた基板である。なお、半導体層2は、本発明の「窒化物系半導体層」の一例である。40

#### 【0023】

また、半導体レーザチップ20aの矢印A方向(矢印B方向)の長さ(幅)は、約200μmに形成されるとともに、矢印A方向(矢印B方向)と実質的に直交するC方向の長さ(奥行き)は、約400μmに形成されている。また、劈開方向(後述するリッジ部2aの延びる方向(C方向)と実質的に直交する方向)(矢印A方向(矢印B方向))は、<11-20>方向である。また、レーザ光が出射される面(後述する劈開面7また50

は 8 ) は、 M 面 ( { 1 - 1 0 0 } 面 ) である。

**【 0 0 2 4 】**

また、半導体層 2 は、図 1 に示すように、 C 方向にストライプ状 ( 細長状 ) に延びる光導波路を構成するリッジ部 2 a を含む。このリッジ部 2 a は、第 1 実施形態では、半導体レーザチップ 2 0 a ( n 型 G a N 基板 1 ) の矢印 A 方向 ( 矢印 B 方向 ) の中央部 1 0 0 から他方側 ( 矢印 B 方向側 ) に距離 W 0 ( = 約 2 0  $\mu\text{m}$  ) だけ寄った領域に形成されている。すなわち、リッジ部 2 a は、欠陥集中領域 3 0 から約 1 2 0  $\mu\text{m}$  離れた位置に形成されている。また、リッジ部 2 a は、半導体レーザチップ 2 0 a ( n 型 G a N 基板 1 ) の他方側 ( 矢印 B 方向側 ) の端部から所定の距離 W 1 ( = 約 8 0  $\mu\text{m}$  ) だけ内側に形成されている。このリッジ部 2 a の上面には、リッジ部 2 a 側 ( 下側 ) から順に P t 膜および P d 膜が積層された p 側電極 3 が形成されている。また、半導体層 2 上には、 p 側電極 3 を覆うように、約 3 0 0 nm の厚みを有する S i O <sub>2</sub> 膜からなる電流プロック層 4 が形成されている。この電流プロック層 4 の p 側電極 3 の真上の C 方向の両端部 ( 後述する劈開面 7 および 8 ) 近傍以外の領域には、開口部 4 a が設けられている。

10

**【 0 0 2 5 】**

また、 p 側電極 3 および電流プロック層 4 上の半導体レーザチップ 2 0 a ( n 型 G a N 基板 1 ) の端面 ( 4 辺 ) から約 3 0  $\mu\text{m}$  内側の線によって囲まれる領域には、 p 側電極 3 および電流プロック層 4 側 ( 下側 ) から順に T i 膜および A u 膜が積層された p 側パッド電極 5 が形成されている。すなわち、 p 側パッド電極 5 は、開口部 4 a を介して p 側電極 3 に電気的に接続されている。また、 p 側パッド電極 5 の矢印 A 方向 ( 矢印 B 方向 ) の長さ ( 幅 ) は、約 1 4 0  $\mu\text{m}$  に形成されるとともに、 C 方向の長さ ( 奥行き ) は、約 3 4 0  $\mu\text{m}$  に形成されている。また、半導体レーザチップ 2 0 a ( n 型 G a N 基板 1 ) の裏面上には、 n 型 G a N 基板 1 側 ( 上側 ) から順に T i 膜、 P t 膜および A u 膜が積層された n 側電極 6 が形成されている。

20

**【 0 0 2 6 】**

また、半導体レーザチップ 2 0 a ( 図 1 参照 ) には、光導波路を構成するリッジ部 2 a と直交するように、 2 つの劈開面 7 および 8 が形成されている。なお、劈開面 7 および 8 は、本発明の「第 1 の分割による分割面」の一例である。この 2 つの劈開面 7 および 8 により、共振器面が構成されている。また、劈開面 7 および 8 には、それぞれ、約 1 0 5 nm の厚みを有する S i O <sub>2</sub> 膜からなる端面コート膜 ( 図示せず ) と、約 7 0 nm の厚みを有する S i O <sub>2</sub> 膜および約 4 3 nm の厚みを有する T i O <sub>2</sub> 膜が交互に 5 層ずつ積層された端面コート膜 ( 図示せず ) とが形成されている。

30

**【 0 0 2 7 】**

また、第 1 実施形態の一例による半導体レーザチップ 2 0 a では、 n 型 G a N 基板 1 、半導体層 2 および電流プロック層 4 には、上面側 ( 電流プロック層 4 側 ) から基板 1 の内部に達する約 4 0  $\mu\text{m}$  の深さを有する劈開 ( 第 1 の分割 ) を行うための劈開導入用段差部 9 a および 9 b が形成されている。この劈開導入用段差部 9 a および 9 b は、 p 側パッド電極 5 が形成されていない領域に形成されている。なお、劈開導入用段差部 9 a および 9 b は、それぞれ、本発明の「第 2 の段差部」の一例である。

40

**【 0 0 2 8 】**

また、第 1 実施形態では、半導体レーザチップ 2 0 a の劈開導入用段差部 9 a および 9 b は、結晶欠陥の多い欠陥集中領域 3 0 を含み、かつ、リッジ部 2 a ( 光導波路 ) を含まない領域に形成されている。具体的には、劈開導入用段差部 9 a および 9 b は、図 1 に示すように、リッジ部 2 a の一方側 ( 矢印 A 方向側 ) の領域のみに、半導体レーザチップ 2 0 a ( n 型 G a N 基板 1 ) の一方側 ( 矢印 A 方向側 ) の端部まで延びるように、リッジ部 2 a ( 光導波路 ) と直交する方向 ( 矢印 A 方向 ( 矢印 B 方向 ) ) に沿ってそれぞれ形成されている。また、劈開導入用段差部 9 a および 9 b は、矢印 A 方向 ( 矢印 B 方向 ) の幅 W 3 が、劈開面 7 または 8 の矢印 A 方向 ( 矢印 B 方向 ) の幅 W 4 ( = 約 2 0 0  $\mu\text{m}$  ) の 2 0 分の 1 以上を有するように構成されている。

50

**【 0 0 2 9 】**

また、第1実施形態では、n型GaN基板1およびn側電極6の矢印A方向および矢印B方向の端部には、半導体レーザチップ20a(n型GaN基板1)の裏面側(半導体層2が形成された側とは反対側)から、リッジ部2a(光導波路)の延びる方向(C方向)に沿って、チップ状に分割(第2の分割)を行うための分離導入用段差部10aおよび10bがそれぞれ形成されている。この分離導入用段差部10aおよび10bは、n側電極6側から基板1の内部に達する約40μmの深さを有する。なお、分離導入用段差部10aおよび10bは、それぞれ、本発明の「第1の段差部」の一例である。

#### 【0030】

また、第1実施形態では、図1に示すように、分離導入用段差部10aおよび10bは、矢印A方向(矢印B方向)に延びる劈開面7および8から所定の距離W2(=約20μm)を隔てた領域に形成されている。なお、分離導入用段差部10aおよび10bは、矢印C方向の長さ(=約360μm)が、半導体レーザチップ20aのC方向の長さ(=約400μm)の5分の1以上を有するように形成されている。また、分離導入用段差部10aおよび10bは、レーザ光が照射されることにより形成されており、劈開面7および8の下部には、レーザ光が照射されることによりn型GaN基板1およびn側電極6の材料が蒸発して粉状になったもの(デブリ31)が付着している。このデブリ31は、分離導入用段差部10aおよび10b近傍の劈開面7および8の下部を中心として所定の半径R(=約80μm)を有するように形成されている。

#### 【0031】

また、n型GaN基板1および半導体層2の詳細構造としては、n型GaN基板1は、酸素がドープされるとともに、六方晶構造からなる。また、半導体層2は、GaN面のC面(面方位(0001))からなる表面(上面)を有している。また、半導体層2は、図2に示すように、n型GaN基板1上に配置されるとともに、Siがドープされたn型GaN層からなるバッファ層11が形成されている。このバッファ層11上には、n型Al<sub>0.05</sub>Ga<sub>0.95</sub>Nからなるn型クラッド層12が形成されている。

#### 【0032】

また、n型クラッド層12上には、アンドープGaNからなるn側光ガイド層13が形成されている。このn側光ガイド層13上には、多重量子井戸(MQW)構造を有する活性層14が形成されている。この活性層14は、2つのアンドープGaNからなる障壁層(図示せず)と、3つのアンドープIn<sub>0.1</sub>Ga<sub>0.9</sub>Nからなる井戸層(図示せず)とが交互に積層された構造を有する。

#### 【0033】

また、活性層14上には、アンドープGaNからなるp側光ガイド層15が形成されている。このp側光ガイド層15上には、アンドープAl<sub>0.3</sub>Ga<sub>0.7</sub>Nからなるキャップ層16が形成されている。このキャップ層16は、活性層14のIn原子が脱離するのを抑制することにより、活性層14の結晶品質が劣化するのを抑制する機能を有する。

#### 【0034】

また、キャップ層16上には、Mgがドープされるとともに、p型Al<sub>0.05</sub>Ga<sub>0.95</sub>Nからなるp型クラッド層17が形成されている。このp型クラッド層17は、p型クラッド層17の上面から所定の領域がエッチングされることにより形成された約1.5μmの幅を有するとともにC方向(図1参照)に延びる凸部を有する。また、p型クラッド層17の凸部上には、アンドープIn<sub>0.05</sub>Ga<sub>0.95</sub>Nからなるp側コンタクト層18が形成されている。これらp型クラッド層17の凸部とp側コンタクト層18により、電流注入領域となるとともに、光導波路を構成するリッジ部2aが形成されている。

#### 【0035】

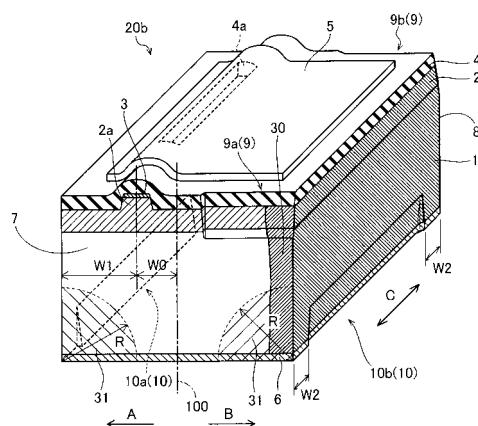

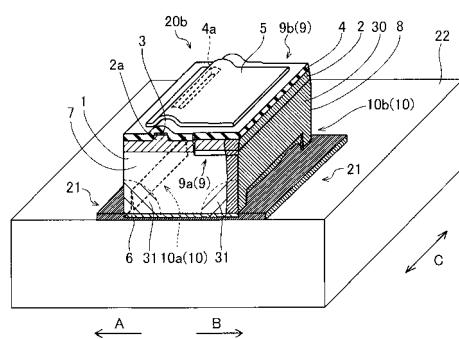

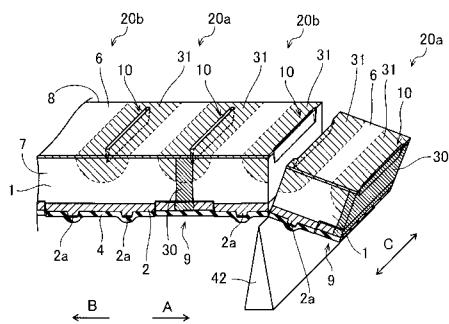

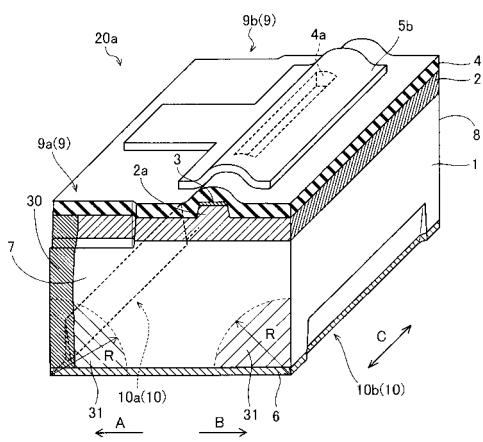

図3は、本発明の第1実施形態によるGaN系半導体レーザチップの製造プロセスにより形成された構造の他の例を示した斜視図である。図4は、図3に示した第1実施形態の他の例によるGaN系半導体レーザチップを放熱基台に取り付けた際の構造を示した斜視図である。次に、図3および図4を参照して、第1実施形態によるGaN系半導体レーザ

10

20

30

40

50

チップの製造プロセスにより形成された構造の他の例（半導体レーザチップ20b）について説明する。

#### 【0036】

ここで、第1実施形態では、後述する製造プロセスにおいて、図1に示した第1実施形態の一例による半導体レーザチップ20aに加えて、図3に示すような第1実施形態の他の例による半導体レーザチップ20bも形成される。この半導体レーザチップ20bは、中央部100を対称軸として半導体レーザチップ20a（図1参照）と矢印A方向（矢印B方向）に対称な形状を有している。

#### 【0037】

また、図4には、第1実施形態の他の例による半導体レーザチップ20b（n型GaN基板1）のn側電極6側がAu-Snなどからなる半田21を介してジャンクションアップ方式によりAlNなどからなる放熱基台（サブマウント）22に固定されている構造が示されている。この際、溶融した半田21は、放熱基台22に対して半導体レーザチップ20bのn側電極6の裏面側のみならず、分離導入用段差部10aおよび10bの形状に合わせて流れ込んで固着するので、半導体レーザチップ20bは放熱基台22に対して確実に融着されている。なお、半田21は、本発明の「融着層」の一例である。

#### 【0038】

なお、図4では、第1実施形態の他の例による半導体レーザチップ20bをジャンクションアップ方式により放熱基台22に融着した例について示したが、第1実施形態の一例による半導体レーザチップ20a（図1参照）についても、上記と同様に、ジャンクションアップ方式により放熱基台22に融着することが可能である。

#### 【0039】

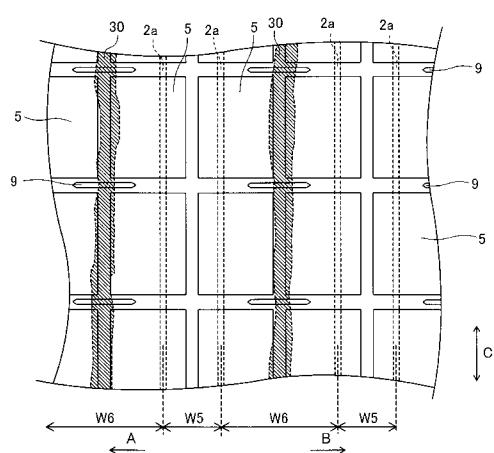

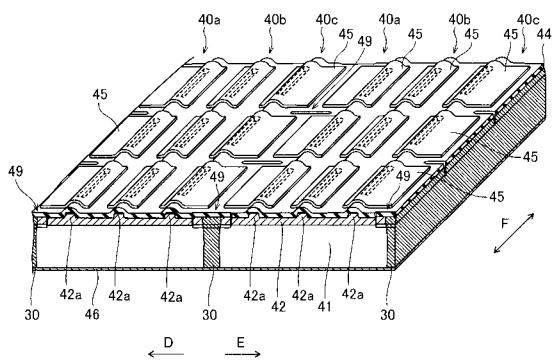

図5および図6は、図1および図3に示した第1実施形態によるGaN系半導体レーザチップのウェハ状態での製造プロセス（ウェハプロセス）を説明するための図である。次に、図1～図6を参照して、第1実施形態による半導体レーザチップ20aおよび20bのウェハ状態での製造プロセス（ウェハプロセス）について説明する。

#### 【0040】

まず、図2に示すように、MOVPE（Metal Organic Vapor Phase Epitaxy：有機金属気相成長）法を用いて、約1150の基板温度で、欠陥集中領域30を有するn型GaN基板1上に、Siがドープされたn型GaN層からなるバッファ層11、n型Al<sub>0.05</sub>Ga<sub>0.95</sub>Nからなるn型クラッド層12、および、アンドープGaNからなるn側光ガイド層13を順次成長させる。

#### 【0041】

ここで、第1実施形態では、n型GaN基板1として、C方向に延びるとともに、矢印A方向（矢印B方向）に約400μmの間隔でストライプ状に配置される欠陥集中領域30が複数設けられた基板を用いる。

#### 【0042】

この後、MOVPE法を用いて、約850の基板温度で、n側光ガイド層13上に、3つのアンドープIn<sub>0.1</sub>Ga<sub>0.9</sub>Nからなる井戸層（図示せず）と、2つのアンドープGaNからなる障壁層（図示せず）とを交互に成長させることにより、活性層14を形成する。続いて、活性層14上に、アンドープGaNからなるp側光ガイド層15と、アンドープAl<sub>0.3</sub>Ga<sub>0.7</sub>Nからなるキャップ層16とを順次形成する。

#### 【0043】

この後、MOVPE法を用いて、約1150の基板温度で、キャップ層16上に、Mgがドープされ、p型Al<sub>0.05</sub>Ga<sub>0.95</sub>Nからなるp型クラッド層17を成長させる。

#### 【0044】

次に、MOVPE法を用いて、約850の基板温度で、p型クラッド層17上に、アンドープIn<sub>0.05</sub>Ga<sub>0.95</sub>Nからなるp側コンタクト層18を形成する。

#### 【0045】

10

20

30

40

50

その後、真空蒸着法およびエッティング技術を用いて、リッジ部 2 a および p 側電極 3 を形成する。具体的には、真空蒸着法を用いて、p 側コンタクト層 1 8 上に、p 側コンタクト層 1 8 側（下側）から順に P t 膜および P d 膜を形成する。次に、エッティング技術を用いて、C 方向（図 1 参照）に延びるレジスト（図示せず）をマスクとして、P t 膜および P d 膜をエッティングするとともに、p 側コンタクト層 1 8 と p 型クラッド層 1 7 の上面から所定の領域とをエッティングする。これにより、p 側コンタクト層 1 8 および p 型クラッド層 1 7 の凸部により構成されるとともに、電流注入領域および光導波路としての機能を有する約 1.5 μm の幅を有するリッジ部 2 a と、リッジ部 2 a 上に配置される p 側電極 3 とが形成される。このとき、リッジ部 2 a は、図 5 および図 6 に示すように、約 200 μm 間隔で劈開方向である <11-20> 方向（矢印 A 方向（矢印 B 方向））と実質的に直交する方向（<1-100> 方向）（C 方向）にストライプ状（細長状）に延びるように形成される。

10

#### 【0046】

また、第 1 実施形態では、リッジ部 2 a は、C 方向に延びる隣接する欠陥集中領域 3 0 と欠陥集中領域 3 0 との間に、2 つずつ形成される。また、リッジ部 2 a は、図 6 に示すように、所定の間隔 W 5 (= 約 160 μm) および W 6 (= 約 240 μm) の異なる 2 つの間隔を交互に有するように形成される。すなわち、第 1 実施形態では、リッジ部（光導波路）2 a 間の中央からリッジ部（光導波路）2 a までの距離（約 80 μm）は、欠陥集中領域 3 0 からリッジ部（光導波路）2 a までの距離（約 120 μm）以下の大きさである。

20

#### 【0047】

このようにして、図 2 に示すように、バッファ層 1 1、n 型クラッド層 1 2、n 側光ガイド層 1 3、活性層 1 4、p 側光ガイド層 1 5、キャップ層 1 6、p 型クラッド層 1 7 および p 側コンタクト層 1 8 からなる半導体層 2 が形成される。このとき、第 1 実施形態では、n 型 GaN 基板 1 の結晶欠陥の多い欠陥集中領域 3 0 上に形成される半導体層 2 の領域も、結晶欠陥の多い欠陥集中領域 3 0 となる。

#### 【0048】

その後、図 1 に示すように、プラズマ CVD 法を用いて、半導体層 2 上に、p 側電極 3 を覆うように、約 300 nm の厚みを有する SiO<sub>2</sub> 膜からなる電流ブロック層 4 を形成する。

30

#### 【0049】

次に、エッティング技術を用いて、フォトレジスト（図示せず）をマスクとして、電流ブロック層 4 をエッティングして、p 側電極 3 の真上の領域のうちの劈開面形成領域近傍以外の電流ブロック層 4 の部分に開口部 4 a を形成する。これにより、p 側電極 3 の上面が露出される。

#### 【0050】

その後、真空蒸着法およびリフトオフ法を用いて、p 側電極 3 および電流ブロック層 4 の所定の領域上に、p 側電極 3 および電流ブロック層 4 側（下側）から順に Ti 膜および Au 膜を積層することにより、p 側パッド電極 5 を形成する。具体的には、電流ブロック層 4 上の GaN 系半導体レーザチップ（n 型 GaN 基板 1）の端面（4 辺）となる位置から約 30 μm 内側の線によって囲まれる領域以外の領域（端面となる位置から約 30 μm までの領域）に、フォトレジスト（図示せず）を形成する。そして、真空蒸着法を用いて、p 側電極 3 および電流ブロック層 4 上に、p 側電極 3 および電流ブロック層 4 側（下側）から順に Ti 膜および Au 膜を形成する。その後、リフトオフ法を用いて、フォトレジスト（図示せず）を除去することにより、p 側電極 3 および電流ブロック層 4 上の GaN 系半導体レーザチップ（n 型 GaN 基板 1）の端面（4 边）となる位置から約 30 μm 内側の線によって囲まれる領域（端面となる位置から約 30 μm までの領域以外の領域）に、p 側パッド電極 5 が形成される。このとき、p 側パッド電極 5 は、図 5 に示すように、p 側パッド電極 5 の矢印 A 方向（矢印 B 方向）の中央部が光導波路を構成するリッジ部 2 a から矢印 A 方向側または矢印 B 方向側に約 20 μm 寄った領域に配置される。なお、各

40

p側パッド電極5は、矢印A方向(矢印B方向)の長さ(幅)が約140μmに形成されるとともに、C方向の長さ(奥行き)が約340μmに形成される。

#### 【0051】

次に、n型GaN基板1の厚みが、たとえば、約130μmになるまで、n型GaN基板1の裏面側を研磨する。

#### 【0052】

その後、真空蒸着法を用いて、n型GaN基板1の裏面上に、n型GaN基板1側(上側)から順にTi膜、Pt膜およびAu膜を積層することにより、n側電極6を形成する。

#### 【0053】

以上のようにして、GaN系半導体レーザチップがマトリクス状に配置されたウェハが完成する。

10

#### 【0054】

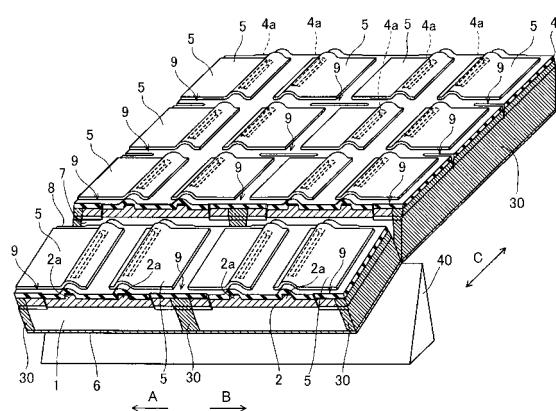

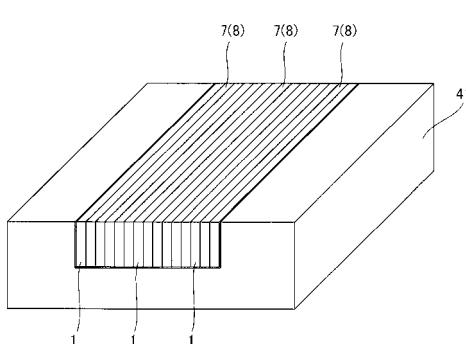

図7～図10は、図1に示した第1実施形態によるGaN系半導体レーザチップのウェハプロセス以降の製造プロセス(チップ化プロセス)を説明するための斜視図である。次に、図1および図5～図10を参照して、第1実施形態によるGaN系半導体レーザチップのウェハプロセス以降の製造プロセス(チップ化プロセス)について説明する。

#### 【0055】

まず、図5に示すように、半導体層2側(上側)から、ストライプ状のリッジ部2aの延びる方向(C方向)に沿って約400μmの間隔を隔てて、レーザ光を用いてリッジ部2aと直交する方向(矢印A方向および矢印B方向)に延びる劈開用溝9を形成する。このとき、異なる2つの間隔のうちの大きい間隔W6(=約240μm)(図6参照)を有するリッジ部(光導波路)2a間に、約100μmの長さを有する劈開用溝9を形成する。すわなち、第1実施形態では、劈開用溝9は、欠陥集中領域30を含み、かつ、リッジ部(光導波路)2aを含まない領域に、矢印A方向(矢印B方向)に延びる破線状に欠陥集中領域30毎に形成される。

20

#### 【0056】

また、劈開用溝9は、約40μmの深さを有するように形成されるとともに、GaN系半導体レーザチップの上面側から、n型GaN基板1、半導体層2および電流ブロック層4に形成される。

30

#### 【0057】

この状態で、図7に示すように、矢印A方向(矢印B方向)に延びる刃状治具40を劈開用溝9に沿って下面側からウェハに当接させるとともに、ウェハの上面側が開くように荷重を印加することによって、ウェハを、劈開用溝9の位置で矢印A方向(矢印B方向)に沿って劈開(第1の分割)する。これにより、ウェハは、半導体レーザチップ20aおよび20bが矢印A方向(矢印B方向)に交互に1列に配置されたバー状に形成される。

#### 【0058】

次に、図8に示すように、バー状に劈開された複数のウェハを、劈開面7が上側になるように、端面コート用治具41に配置する。そして、劈開面7に約105nmの厚みを有するSiO<sub>2</sub>膜からなる端面コート膜(図示せず)を形成する。その後、バー状に劈開された複数のウェハを裏返して、劈開面8が上側になるように、端面コート用治具41に配置する。そして、劈開面8に、約70nmの厚みを有するSiO<sub>2</sub>膜および約43nmの厚みを有するTiO<sub>2</sub>膜が交互に5層ずつ積層された端面コート膜(図示せず)を形成する。このようにして、劈開面7および8に、共振器面が形成される。

40

#### 【0059】

次に、図9に示すように、バー状に劈開されたウェハのn型GaN基板1の裏面側から、約200μmの間隔で、ストライプ状のリッジ部2aの延びる方向(C方向)にレーザ光を用いて非接触の状態で、約40μmの深さを有する素子分割用溝10を形成する。

#### 【0060】

このとき、第1実施形態では、矢印A方向(矢印B方向)に延びる劈開面7および8か

50

ら所定の距離W2（約20μm）（図1参照）を隔てた領域に、素子分割用溝10を形成する。このとき、劈開面7および8の下部には、レーザ光が照射されることにより、所定の半径R（=約80μm）を有するデブリ31（n型GaN基板1およびn側電極6の材料が蒸発して粉状になったもの）が付着する。なお、レーザ光を用いて非接触の状態でn型GaN基板1に素子分割用溝10を形成するので、素子分割用溝10を形成する際に半導体層2に割れや欠けが発生するのが抑制される。

#### 【0061】

また、第1実施形態では、約160μmの間隔W5（図6参照）を有するリッジ部（光導波路）2a間、および、約240μmの間隔W6（図6参照）を有するリッジ部（光導波路）2a間のそれぞれの中間位置に、素子分割用溝10を形成する。すなわち、第1実施形態では、素子分割用溝10は、欠陥集中領域30と、約160μmの間隔W5を有するリッジ部（光導波路）2a間の中央とに形成される。10

#### 【0062】

この状態で、図10示すように、C方向に延びる刃状治具42を素子分割用溝10に沿って上面側（半導体層2側）からバー状のウェハに当接させるとともに、バー状のウェハの下面側（n側電極6側）が開くように荷重を印加することにより、バー状のウェハを、素子分割用溝10の位置でC方向に沿って分割（第2の分割）する。これにより、バー状のウェハが、図1に示すように、約200μmの矢印A方向（矢印B方向）の長さ（幅）および約400μmのC方向の長さ（奥行き）を有するGaN系半導体レーザチップに分割されて、GaN系半導体レーザチップ（半導体レーザチップ20aおよび20b）が多数製造される。20

#### 【0063】

また、図4に示すように、上記の製造プロセスによってチップ化された半導体レーザチップ20bのn側電極6側を下にして、加熱により高温状態となった放熱基台（サブマウント）22に半田21を介して融着する。この際、溶融した半田21は、放熱基台22に対して半導体レーザチップ20bのn側電極6の裏面側のみならず、分離導入用段差部10aおよび10bにも、その形状に合わせるように流れ込んで固着する。これにより、ジャンクションアップ方式によるGaN系半導体レーザチップが形成される。

#### 【0064】

第1実施形態では、上記のように、n型GaN基板1の半導体層2が形成された側とは反対側のn側電極6側に、レーザ光を照射することによりC方向に延びるように形成された分離導入用段差部10aおよび10b（素子分割用溝10）を備えることによって、分離導入用段差部10aおよび10b（素子分割用溝10）は、n型GaN基板1上の半導体層2から離れた位置に形成されるので、半導体層2に割れや欠けが発生するのを抑制することができる。これにより、半導体層2の光導波路を構成するリッジ部2aが損傷するのを抑制することができる。30

#### 【0065】

また、第1実施形態では、n型GaN基板1の劈開面7および8から所定の距離W2（=約20μm）を隔てた領域に、レーザ光を照射することにより形成された分離導入用段差部10aおよび10b（素子分割用溝10）を備えることによって、素子分割用溝10をリッジ部（光導波路）2aの端面を含む劈開面7および8から離れた位置に形成することができるので、レーザ光を照射することにより分離導入用段差部10aおよび10b（素子分割用溝10）を形成する際に、デブリ31（n型GaN基板1およびn側電極6の材料が蒸発して粉状になったもの）がリッジ部2aの端面近傍に付着するのを抑制することができる。これにより、リッジ部2a下の発光部から出射されるレーザ光の強度が低下するのを抑制することができる。また、n型GaN基板1の半導体層2が形成された側とは反対側のn側電極6側に、レーザ光を照射することにより形成された分離導入用段差部10aおよび10b（素子分割用溝10）を備えることによって、分離導入用段差部10aおよび10b（素子分割用溝）は半導体層2のリッジ部2aからさらに離れた位置に形成されるので、レーザ光を照射することにより分離導入用段差部10aおよび10b（素40

50

子分割用溝 10 ) を形成する際に、デブリ 31 がリッジ部 2a の端面近傍に付着するのをより抑制することができる。これにより、リッジ部 2a 下の発光部から出射される光の強度が低下するのをより抑制することができる。

#### 【 0 0 6 6 】

また、第 1 実施形態では、リッジ部（光導波路）2a 間の中央からリッジ部 2a までの距離 W1 (= 約 80 μm) を、欠陥集中領域 30 からリッジ部 2a までの距離（約 120 μm）以下の大きさにすることによって、リッジ部 2a を欠陥集中領域 30 から離れた位置に形成することができる。レーザ光を照射することにより分離導入用段差部 10a および 10b (素子分割用溝 10 ) を形成する場合、欠陥集中領域 30 では光の吸収が増大し高温になりやすいので、リッジ部 2a を欠陥集中領域 30 から離れた位置に形成することにより、リッジ部 2a が高温になりすぎることを抑制することができる。これにより、分離導入用段差部 10a および 10b (素子分割用溝 10 ) を形成する際に、リッジ部（光導波路）2a が損傷するのをより抑制することができる。10

#### 【 0 0 6 7 】

また、第 1 実施形態では、矢印 C 方向における分離導入用段差部 10a および 10b (素子分割用溝 10 ) の長さを、矢印 C 方向におけるリッジ部（光導波路）2a の端面間距離 (= 約 400 μm) の 5 分の 1 以上であるように構成することによって、矢印 C 方向に沿って素子分割を行う際に、予め素子分割用溝 10 がリッジ部 2a の端面間距離の 5 分の 1 以上の長い領域に形成されているので、素子分割用溝 10 を起点として矢印 C 方向に容易に素子分割を行うことができる。これにより、半導体層 2 に割れや欠けが発生するのをより抑制することができる。20

#### 【 0 0 6 8 】

また、第 1 実施形態では、半導体層 2 の欠陥集中領域 30 を含み、かつ、リッジ部（光導波路）2a を含まない領域に、レーザ光を照射することにより、矢印 A 方向（矢印 B 方向）に延びるように欠陥集中領域 30 每に、破線状の劈開導入用段差部 9a および 9b (劈開用溝 9 ) を形成することによって、リッジ部 2a に劈開導入用段差部 9a および 9b (劈開用溝 9 ) を形成することなく、劈開を行うことができるので、リッジ部 2a の分割面を、容易に、劈開面とすることができます。

#### 【 0 0 6 9 】

また、第 1 実施形態では、矢印 A 方向（矢印 B 方向）における劈開導入用段差部 9a および 9b (劈開用溝 9 ) の幅 W3 を、矢印 A 方向（矢印 B 方向）における劈開面 7 および 8 の幅 W4 (= 約 200 μm) の 20 分の 1 以上であるように構成することによって、矢印 A 方向（矢印 B 方向）に沿って劈開を行う際に、予め劈開用溝 9 が劈開面 7 および 8 の幅 W4 の 20 分の 1 以上の長い領域に形成されているので、劈開用溝 9 を起点として矢印 A 方向（矢印 B 方向）に、より容易に、劈開することができる。30

#### 【 0 0 7 0 】

また、第 1 実施形態では、n 型 GaN 基板 1 の n 側電極 6 側を、Au - Sn などからなる半田 21 を介して放熱基台 22 に取り付けるように構成することによって、半田 21 が、n 側電極 6 の裏面上のみならず、裏面から窪んだ分離導入用段差部 10a および 10b にも入り込んで固定するので、半導体レーザチップ 20b を放熱基台 22 に安定して固定することができる。この結果、レーザ出射光の軸ずれが生じるのを抑制することができる。なお、半導体レーザチップ 20a (図 1 参照) をジャンクションアップ方式により放熱基台 22 に融着する場合も、上記と同様の効果が得られる。40

#### 【 0 0 7 1 】

( 第 1 実施形態の第 1 変形例 )

図 11 は、本発明の第 1 実施形態の第 1 変形例による GaN 系半導体レーザチップを放熱基台に取り付けた際の構造を示した斜視図である。この第 1 実施形態の第 1 変形例による GaN 系半導体レーザチップでは、上記第 1 実施形態と異なり、上記第 1 実施形態の一例による半導体レーザチップ 20a をジャンクションダウン方式により放熱基台 22 に固定する場合について説明する。50

## 【0072】

ここで、第1実施形態の第1変形例では、図11に示すように、半導体レーザチップ20a(n型GaN基板1)のp側パッド電極5側がAu-Snなどからなる半田21を介してジャンクションダウン方式によりAlNなどからなる放熱基台22に固定されている。この場合、溶融した半田21は、放熱基台22に対して半導体レーザチップ20aのp側パッド電極5の表面のみならず劈開面7および8の半導体層2側に形成された劈開導入用段差部9aおよび9bの形状に合わせて流れ込んで固着するので、半導体レーザチップ20aは放熱基台22に対して確実に融着されている。

## 【0073】

第1実施形態の第1変形例では、上記のように、n型GaN基板1の半導体層2が形成されたp側パッド電極5側を、Au-Snなどからなる半田21を介して放熱基台22に取り付けるように構成することによって、半田21が、p側パッド電極5の表面のみならず、表面から窪んだ劈開導入用段差部9aおよび9bにも入り込んで固着するので、半導体レーザチップ20aを放熱基台22に安定して固定することができる。この結果、レーザ出射光の軸ずれが生じるのを抑制することができる。また、溶融した半田21が劈開導入用段差部9a(図11参照)に入り込んで固着するので、共振器面(劈開面7)のリッジ部(光導波路)2a近傍に、はみ出ない。これにより、半田21がリッジ部2aからのレーザ出射光を妨げるのを抑制することができる。

## 【0074】

なお、第1実施形態の第1変形例のその他の効果は、上記第1実施形態と同様である。

また、上記第1実施形態の他の例による半導体レーザチップ20b(図3参照)をジャンクションダウン方式により放熱基台22に融着する場合も、上記と同様の効果が得られる。

## 【0075】

## (第2実施形態)

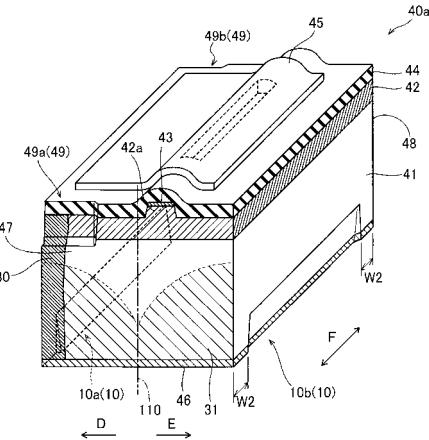

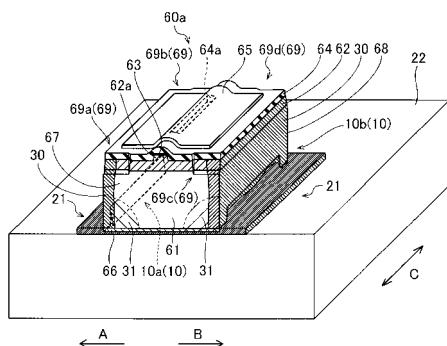

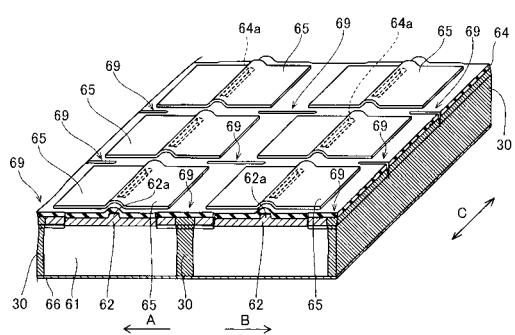

図12および図13は、本発明の第2実施形態によるGaN系半導体レーザチップの製造プロセスにより形成された構造を示した斜視図である。図14は、図12および図13に示した第2実施形態によるGaN系半導体レーザチップの製造プロセスを説明するための斜視図である。図12～図14を参照して、この第2実施形態では、上記第1実施形態と異なり、隣接する欠陥集中領域と欠陥集中領域との間に3つのGaN系半導体レーザチップを形成する場合について説明する。

## 【0076】

第2実施形態では、GaN系半導体レーザチップは、図12および図13に示すように、n型GaN基板41の一方側(矢印D方向側または矢印E方向側)に結晶欠陥の多い欠陥集中領域30を有する半導体レーザチップ40aと、n型GaN基板41に結晶欠陥の多い欠陥集中領域30を有さない半導体レーザチップ40bとにより構成されている。なお、後述する製造プロセスにおいて、図12に示した第2実施形態による半導体レーザチップ40aに加えて、図14に示すような半導体レーザチップ40cも形成される。この半導体レーザチップ40cは、第1実施形態で示した半導体レーザチップ20aに対する半導体レーザチップ20bと同様に、中央部110を対称軸として半導体レーザチップ40a(図12参照)と矢印D方向(矢印E方向)に対称な形状を有している。

## 【0077】

この半導体レーザチップ40a(40c)および40bは、図12および図13に示すように、矢印D方向(矢印E方向)に沿って、それぞれ、約150μmおよび約100μmの長さを有するように形成されている。なお、n型GaN基板41は、本発明の「基板」の一例である。

## 【0078】

また、半導体レーザチップ40a(40c)および40bには、上記第1実施形態と同様、n型GaN基板41上に、F方向にストライプ状(細長状)に延びる光導波路を構成するリッジ部42aを含む窒化物系の半導体層42が形成されている。なお、半導体層4

10

20

30

40

50

2は、本発明の「窒化物系半導体層」の一例である。また、半導体層42上には、p側電極43を覆うように、約300nmの厚みを有するSiO<sub>2</sub>膜からなる電流ブロック層44およびp側パッド電極45が形成されている。また、n型GaN基板41の裏面上には、n側電極46が形成されている。また、光導波路を構成するリッジ部42aと直交するように、共振器面を構成する2つの劈開面47および48が形成されている。なお、劈開面47および48は、本発明の「第1の分割による分割面」の一例である。

#### 【0079】

また、第2実施形態では、図12に示すように、半導体レーザチップ40aには、上記第1実施形態と同様、劈開導入用段差部49aおよび49b(劈開用溝49)が一方側に形成されるとともに、リッジ部42aが半導体レーザチップ40a(n型GaN基板41)の矢印D方向(矢印E方向)の中央部110から他方側に寄った領域に形成されている。また、半導体レーザチップ40bには、図13に示すように、上記第1実施形態と異なり、劈開導入用段差部49aおよび49b(劈開用溝49)が形成されていないとともに、リッジ部42aが半導体レーザチップ40b(n型GaN基板41)の矢印D方向(矢印E方向)の中央部120に形成されている。

#### 【0080】

なお、第2実施形態のその他の構造は、上記第1実施形態と同様である。

#### 【0081】

次に、図12～図14を参照して、第2実施形態によるGaN系半導体レーザチップのウェハ状態での製造プロセス(ウェハプロセス)について説明する。

#### 【0082】

まず、図12および図13に示すように、上記第1実施形態と同様のプロセスを用いて、n型GaN基板41上に、p側コンタクト層(図示せず)までを形成する。その後、真空蒸着法およびエッチング技術を用いて、リッジ部(光導波路)42aおよびp側電極43を形成する。

#### 【0083】

このとき、第2実施形態では、図14に示すように、隣接する欠陥集中領域30と欠陥集中領域30との間に3つのリッジ部42aを形成する。

#### 【0084】

なお、第2実施形態のその他のウェハ状態での製造プロセス(ウェハプロセス)は、上記第1実施形態のウェハ状態での製造プロセスと同様である。

#### 【0085】

次に、図12～図14を参照して、第2実施形態によるGaN系半導体レーザチップのウェハプロセス以降の製造プロセス(チップ化プロセス)について説明する。

#### 【0086】

まず、上記第1実施形態と同様のプロセスを用いて、図14に示すように、欠陥集中領域30を含み、かつ、リッジ部(光導波路)42aを含まない領域に、矢印D方向(矢印E方向)に延びる破線状に欠陥集中領域30毎に劈開用溝49を形成する。この状態で、上記第1実施形態と同様のプロセスを用いて、ウェハを、劈開用溝49の位置で矢印D方向(矢印E方向)に沿って劈開(第1の分割)する。これにより、ウェハは、GaN系半導体レーザチップが矢印D方向(矢印E方向)に1列に配置されたバー状に形成される。

#### 【0087】

そして、上記第1実施形態と同様のプロセスを用いて、バー状に劈開されたウェハのn型GaN基板41の裏面側から、ストライプ状のリッジ部42aの延びる方向(F方向)に素子分割用溝10(図12および図13参照)を形成する。

#### 【0088】

このとき、第2実施形態では、図12および図13に示すように、上記第1実施形態と同様、矢印D方向(矢印E方向)に延びる劈開面47および48から所定の距離W2(約20μm)を隔てた領域に、素子分割用溝10を形成する。

#### 【0089】

10

20

30

40

50

また、第2実施形態では、素子分割用溝10は、欠陥集中領域30と、欠陥集中領域30から約150μm離れた部分とに形成される。この状態で、上記第1実施形態と同様のプロセスを用いて、バー状のウェハを、素子分割用溝10の位置でF方向に沿って分割(第2の分割)することにより、図12および図13に示したGaN系半導体レーザチップ(3つの半導体レーザチップ40a(40c)および40b)が多数製造される。

#### 【0090】

なお、第2実施形態のその他のウェハプロセス以降の製造プロセス(チップ化プロセス)は、上記第1実施形態のウェハプロセス以降の製造プロセスと同様である。

#### 【0091】

また、第2実施形態の効果は、上記第1実施形態と同様である。なお、半導体レーザチップ40aおよび40c(図12参照)を融着層(半田21など)を介して放熱基台に固定する際は、上記第1実施形態と同様にジャンクションアップ方式およびジャンクションダウン方式のいずれの方法によっても融着層が分離導入用段差部10a(10b)または劈開導入用段差部49a(49b)に入り込んで固着するので、半導体レーザチップ40aを放熱基台に安定して固定することができる。その一方、半導体レーザチップ40b(図13参照)を融着層を介して放熱基台に固定する際は、ジャンクションダウン方式の場合のみ、融着層が分離導入用段差部10a(10b)に入り込んで固着するので、上記と同様の効果が得られる。

#### 【0092】

##### (第3参考形態)

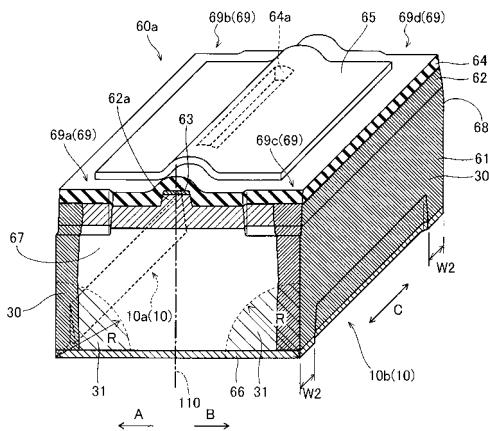

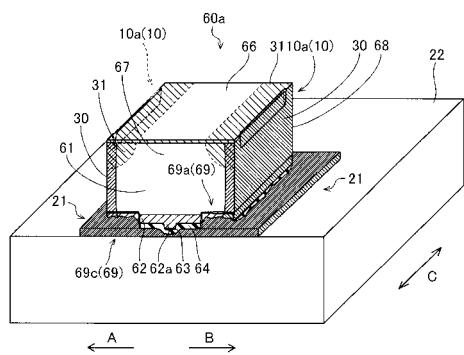

図15は、本発明の第3参考形態によるGaN系半導体レーザチップの製造プロセスにより形成された構造を示した斜視図である。図16は、図15に示した第3参考形態によるGaN系半導体レーザチップを放熱基台に取り付けた際の構造を示した斜視図である。図15および図16を参照して、この第3参考形態では、上記第1および第2実施形態と異なり、隣接する欠陥集中領域と欠陥集中領域との間に1つのGaN系半導体レーザチップを形成する場合について説明する。

#### 【0093】

第3参考形態による半導体レーザチップ60aでは、図15に示すように、n型GaN基板61の両側(矢印A方向側および矢印B方向側)に結晶欠陥の多い欠陥集中領域30を有している。この半導体レーザチップ60aは、矢印A方向(矢印B方向)に沿って、約400μmの長さ(幅)を有するように形成されている。なお、n型GaN基板61は、本発明の「基板」の一例である。

#### 【0094】

また、半導体レーザチップ60aには、上記第1実施形態と同様、n型GaN基板61上に、C方向にストライプ状(細長状)に延びる光導波路を構成するリッジ部62aを含む窒化物系の半導体層62が形成されている。なお、半導体層62は、本発明の「窒化物系半導体層」の一例である。また、半導体層62上には、p側電極63を覆うように、約300nmの厚みを有するSiO<sub>2</sub>膜からなる電流ブロック層64およびp側パッド電極65が形成されている。また、n型GaN基板61の裏面上には、n側電極66が形成されている。また、光導波路を構成するリッジ部62aと直交するように、共振器面を構成する2つの劈開面67および68が形成されている。なお、劈開面67および68は、本発明の「第1の分割による分割面」の一例である。

#### 【0095】

ここで、第3参考形態では、図15に示すように、半導体レーザチップ60aには、上記第1実施形態と異なり、劈開導入用段差部69aおよび69bが一方側(矢印A方向側)に形成されているとともに、劈開導入用段差部69cおよび69dが他方側(矢印B方向側)に形成されている。また、リッジ部62aは、半導体レーザチップ60a(n型GaN基板61)の矢印A方向(矢印B方向)の中央部110から若干A方向側に寄った領域に形成されている。なお、劈開導入用段差部69a、69b、69cおよび69dは、それぞれ、本発明の「第2の段差部」の一例である。

10

20

30

40

50

**【0096】**

なお、第3参考形態のGaN系半導体レーザチップ（半導体レーザチップ60a）のその他の構造は、上記第1実施形態と同様である。

**【0097】**

また、第3参考形態では、図16に示すように、半導体レーザチップ60a（n型GaN基板61）のn側電極66側がAu-Snなどからなる半田21を介してジャンクションアップ方式によりAlNなどからなる放熱基台（サブマウント）22に固定されている。この際、溶融した半田21は、放熱基台22に対して半導体レーザチップ60aのn側電極66の裏面側のみならず分離導入用段差部10aおよび10bの形状に合わせるように流れ込んで固着する。これにより、半導体レーザチップ60aは放熱基台22に対して確実に固定されている。10

**【0098】**

図17は、図15および図16に示した第3参考形態によるGaN系半導体レーザチップの製造プロセスを説明するための斜視図である。次に、図15～図17を参照して、第3参考形態によるGaN系半導体レーザチップのウェハ状態での製造プロセス（ウェハプロセス）について説明する。

**【0099】**

まず、図15に示すように、上記第1実施形態と同様のプロセスを用いて、n型GaN基板61上に、p側コンタクト層（図示せず）までを形成する。その後、真空蒸着法およびエッティング技術を用いて、リッジ部（光導波路）62aおよびp側電極63を形成する。20

**【0100】**

このとき、第3参考形態では、図17に示すように、隣接する欠陥集中領域30と欠陥集中領域30との間に1つのリッジ部62aを形成する。

**【0101】**

なお、第3参考形態の他のウェハ状態での製造プロセス（ウェハプロセス）は、上記第1実施形態のウェハ状態での製造プロセスと同様である。

**【0102】**

次に、図15～図17を参照して、第3参考形態によるGaN系半導体レーザチップのウェハプロセス以降の製造プロセス（チップ化プロセス）について説明する。30

**【0103】**

まず、上記第1実施形態と同様のプロセスを用いて、図17に示すように、欠陥集中領域30を含み、かつ、リッジ部（光導波路）62aを含まない領域に、矢印A方向（矢印B方向）に延びる破線状に欠陥集中領域30毎に劈開用溝69を形成する。この状態で、上記第1実施形態と同様のプロセスを用いて、ウェハを、劈開用溝69の位置で矢印A方向（矢印B方向）に沿って劈開（第1の分割）する。これにより、ウェハは、GaN系半導体レーザチップが矢印A方向（矢印B方向）に1列に配置されたバー状に形成される。

**【0104】**

そして、上記第1実施形態と同様のプロセスを用いて、バー状に劈開されたウェハのn型GaN基板61の裏面側から、ストライプ状のリッジ部62aの延びる方向（C方向）に素子分割用溝10（図15参照）を形成する。40

**【0105】**

このとき、第3参考形態では、図15に示すように、上記第1実施形態と同様、矢印A方向（矢印B方向）に延びる劈開面67および68からC方向に所定の距離W2（約20μm）を隔てた領域に、素子分割用溝10を形成する。

**【0106】**

また、第3実施形態では、素子分割用溝10は、欠陥集中領域30の部分（図15参照）に形成される。この状態で、上記第1実施形態と同様のプロセスを用いて、バー状のウェハを、素子分割用溝10の位置でC方向に沿って分割（第2の分割）することにより、図15に示したGaN系半導体レーザチップ（半導体レーザチップ60a）が多数製造さ50

れる。

#### 【0107】

なお、第3実施形態のその他のウェハプロセス以降の製造プロセス（チップ化プロセス）は、上記第1実施形態のウェハプロセス以降の製造プロセスと同様である。

#### 【0108】

そして、第3参考形態では、図16に示すように、上記チップ化された半導体レーザチップ60aのn側電極66側を下にして、加熱により高温状態となった放熱基台（サブマウント）22に半田21を介して融着する。この際、溶融した半田21は、放熱基台22に対して半導体レーザチップ60aのn側電極66の裏面側のみならず、分離導入用段差部10aおよび10bの形状に合わせて流れ込んで固着する。これにより、第1実施形態と同様に、ジャンクションアップ方式によるGaN系半導体レーザチップが形成される。10

#### 【0109】

第3参考形態では、上記第1実施形態と同様に、n型GaN基板61の半導体層62が形成された側とは反対側のn側電極66側を、Au-Snなどからなる半田21を介して放熱基台22に取り付けるように構成することによって、半田21が、n側電極66の裏面上のみならず、裏面から窟んだ分離導入用段差部10aおよび10bにも入り込んで固着するので、半導体レーザチップ60aを放熱基台22に安定して固定することができる。この結果、レーザ出射光の軸ずれが生じるのを抑制することができる。なお、第3参考形態のその他の効果は、上記第1実施形態と同様である。20

#### 【0110】

##### （第3参考形態の変形例）

図18は、本発明の第3参考形態の変形例によるGaN系半導体レーザチップを放熱基台に取り付けた際の構造を示した斜視図である。この第3参考形態の変形例によるGaN系半導体レーザチップでは、上記第3参考形態と異なり、半導体レーザチップ60aをジャンクションダウン方式により放熱基台22に固定する場合について説明する。

#### 【0111】

ここで、第3参考形態の変形例では、図18に示すように、半導体レーザチップ60a（n型GaN基板61）のp側パッド電極65側がAu-Snなどからなる半田21を介してジャンクションダウン方式によりAlNなどからなる放熱基台（サブマウント）22に固定されている。この場合、溶融した半田21は、放熱基台22に対して半導体レーザチップ60aのp側パッド電極65の表面のみならず劈開面67および68の半導体層62側に形成された4つの劈開導入用段差部69a、69b、69cおよび69dの形状に合わせて流れ込んで固着するので、半導体レーザチップ60aは放熱基台22に対して確実に固定されている。30

#### 【0112】

第3参考形態の変形例では、上記のように、n型GaN基板61の半導体層62が形成されたp側パッド電極65側を、Au-Snなどからなる半田21を介して放熱基台22に取り付けるように構成することによって、半田21が、p側パッド電極65の表面のみならず、表面から窟んだ劈開導入用段差部69a、69b、69cおよび69d（4箇所）にも入り込んで固着するので、半導体レーザチップ60aを放熱基台22に安定して固定することができる。この結果、レーザ出射光の軸ずれが生じるのを抑制することができる。また、溶融した半田21が劈開導入用段差部69aおよび69c（図18参照）に入り込んで固着するので、共振器面（劈開面67）のリッジ部（光導波路）62a近傍にはみ出ない。これにより、半田21がリッジ部62aからのレーザ出射光を妨げるのを抑制することができる。なお、第3参考形態の変形例のその他の効果は、上記第1実施形態と同様である。40

#### 【0113】

なお、今回開示された実施形態および実施例は、すべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は、上記した実施形態および実施例の説明ではなく特許請求の範囲によって示され、さらに特許請求の範囲と均等の意味および50

範囲内でのすべての変更が含まれる。

**【0114】**

たとえば、上記実施形態では、GaN系半導体レーザチップに本発明を適用する例を示したが、本発明はこれに限らず、GaN系以外の窒化物系半導体素子にも適用可能である。

**【0115】**

また、上記実施形態では、素子分割用溝を、劈開面から約20μm隔てた領域に形成した例を示したが、本発明はこれに限らず、素子分割用溝を、劈開面から約20μm以外の距離を隔てた領域に形成してもよい。たとえば、素子分割用溝を、劈開面から約20μmよりも大きい距離を隔てた領域に形成する場合、素子分割用溝を形成する際のデブリがリッジ部（光導波路）に付着するのをより抑制することができるので、ウェハ（n型GaN基板）をより薄くすることができる。

**【0116】**

また、上記実施形態では、結晶欠陥の多い領域が直線状に形成されたn型GaN基板を用いた例について示したが、本発明はこれに限らず、結晶欠陥の多い領域が直線状以外の、たとえば、網目状に形成されたn型GaN基板を用いてもよい。

**【0117】**

また、上記実施形態では、刃状治具を用いて、ウェハを劈開または分割した例について示したが、本発明はこれに限らず、刃状治具以外の、たとえば、ローラなどを用いて、ウェハを劈開または分割してもよい。

**【0118】**

また、上記実施形態では、端面コート材料として、SiO<sub>2</sub>およびTiO<sub>2</sub>を用いた例について示したが、本発明はこれに限らず、端面コート材料として、SiO<sub>2</sub>およびTiO<sub>2</sub>以外の、たとえば、Al<sub>2</sub>O<sub>3</sub>、ZrO<sub>2</sub>、Ta<sub>2</sub>O<sub>5</sub>、Nb<sub>2</sub>O<sub>5</sub>、La<sub>2</sub>O<sub>3</sub>、SiN、AlNまたはBNなどを用いてもよいし、これらの組成比の異なる材料であるTi<sub>3</sub>O<sub>5</sub>やNb<sub>2</sub>O<sub>3</sub>などを用いてもよい。

**【0119】**

また、上記実施形態では、ウェハ（n型GaN基板）の厚みを約130μmに形成した例について示したが、本発明はこれに限らず、ウェハ（n型GaN基板）の厚みを約130μm以外の厚みに形成してもよい。

**【0120】**

また、上記実施形態では、p側パッド電極を、半導体レーザチップの端面（4辺）となる位置から均等な距離だけ内側の領域に形成したが、本発明はこれに限らず、均等な距離でなくてもよいし、形状も他のものでも構わない。たとえば、p側パッド電極を、円形、多角形、または、図19～図21にそれぞれ示した本発明の第1実施形態の第2変形例～第4変形例のような形状にしてもよい。この場合、第2変形例～第4変形例では、p側パッド電極5a～5cの面積を小さくすることができる。これにより、半導体レーザチップの容量を小さくすることができる。これにより、半導体レーザチップの応答特性（高周波特性）を向上させることができる。また、第2変形例～第4変形例（特に第2変形例）では、半導体レーザチップ（p側パッド電極5a～5c）を上方から見るだけで、半導体レーザチップの方向を容易に識別することができるので、レーザ光の出射方向を容易に識別することができる。

**【0121】**

また、上記実施形態では、隣接する欠陥集中領域と欠陥集中領域との間に、1つまたは2つまたは3つのGaN系半導体レーザチップを形成した例について示したが、本発明はこれに限らず、隣接する欠陥集中領域と欠陥集中領域との間に、4つ以上のGaN系半導体レーザチップを形成してもよい。

**【0122】**

また、第2実施形態では、隣接する欠陥集中領域と欠陥集中領域との間に、約150μm、約100μmおよび約150μmの幅をそれぞれ有する3つのGaN系半導体レーザ

10

20

30

40

50

チップを形成した例について示したが、本発明はこれに限らず、隣接する欠陥集中領域と欠陥集中領域との間に、同じ幅の3つのGaN系半導体レーザチップを形成してもよい。

### 【0123】

また、第2実施形態では、隣接する欠陥集中領域と欠陥集中領域との間に、3つのGaN系半導体レーザチップを形成し、中央のレーザチップのリッジ部（光導波路）を、レーザチップの中央部に位置するように形成した例について示したが、本発明はこれに限らず、中央のレーザチップのリッジ部（光導波路）を、一方側に寄った位置に形成してもよい。

### 【0124】

また、上記実施形態では、基板の裏面側に形成される素子分割用溝および基板の半導体層側に形成される劈開用溝の深さとともに約40μmとした例について示したが、本発明はこれに限らず、素子分割用溝および劈開用溝の深さを3μm以上100μm以下の範囲で形成してもよい。

### 【0125】

また、上記実施形態では、半導体レーザチップを固定するためのサブマウントとしてAlNからなる放熱基台を用いた例について示したが、本発明はこれに限らず、SiC、Si、BN、ダイヤモンド、Cu、CuWおよびAlなどの他の材料からなる放熱基台を用いてもよい。また、レーザチップを放熱基台に固定する際の融着層としてAu-Snからなる半田を用いたが、本発明はこれに限らず、Ag-Sn、Pb-SnおよびIn-Snなどの他の材料からなる融着層を用いてもよい。

### 【図面の簡単な説明】

### 【0126】

【図1】本発明の第1実施形態によるGaN系半導体レーザチップの製造プロセスにより形成された構造の一例を示した斜視図である。

【図2】図1に示したGaN系半導体レーザチップの中央付近の半導体層の詳細構造を示した断面図である。

【図3】本発明の第1実施形態によるGaN系半導体レーザチップの製造プロセスにより形成された構造の他の例を示した斜視図である。

【図4】図3に示した第1実施形態の他の例によるGaN系半導体レーザチップを放熱基台に取り付けた際の構造を示した斜視図である。

【図5】図1に示した第1実施形態によるGaN系半導体レーザチップのウェハ状態での製造プロセス（ウェハプロセス）を説明するための斜視図である。

【図6】図1に示した第1実施形態によるGaN系半導体レーザチップのウェハ状態での製造プロセス（ウェハプロセス）を説明するための平面図である。

【図7】図1に示した第1実施形態によるGaN系半導体レーザチップのウェハプロセス以降の製造プロセス（チップ化プロセス）を説明するための斜視図である。

【図8】図1に示した第1実施形態によるGaN系半導体レーザチップのウェハプロセス以降の製造プロセス（チップ化プロセス）を説明するための斜視図である。

【図9】図1に示した第1実施形態によるGaN系半導体レーザチップのウェハプロセス以降の製造プロセス（チップ化プロセス）を説明するための斜視図である。

【図10】図1に示した第1実施形態によるGaN系半導体レーザチップのウェハプロセス以降の製造プロセス（チップ化プロセス）を説明するための斜視図である。

【図11】本発明の第1実施形態の第1変形例によるGaN系半導体レーザチップを放熱基台に取り付けた際の構造を示した斜視図である。

【図12】本発明の第2実施形態によるGaN系半導体レーザチップの構造を示した斜視図である。

【図13】本発明の第2実施形態によるGaN系半導体レーザチップの構造を示した斜視図である。

【図14】図12および図13に示した第2実施形態によるGaN系半導体レーザチップの製造プロセスを説明するための斜視図である。

10

20

30

40

50

【図15】本発明の第3参考形態によるGaN系半導体レーザチップの構造を示した斜視図である。

【図16】図15に示した第3参考形態によるGaN系半導体レーザチップを放熱基台に取り付けた際の構造を示した斜視図である。

【図17】図15および図16に示した第3参考形態によるGaN系半導体レーザチップの製造プロセスを説明するための斜視図である。

【図18】本発明の第3参考形態の変形例によるGaN系半導体レーザチップを放熱基台に取り付けた際の構造を示した斜視図である。

【図19】本発明の第1実施形態の第2変形例によるGaN系半導体レーザチップの構造を示した斜視図である。 10

【図20】本発明の第1実施形態の第3変形例によるGaN系半導体レーザチップの構造を示した斜視図である。

【図21】本発明の第1実施形態の第4変形例によるGaN系半導体レーザチップの構造を示した斜視図である。

【符号の説明】

【0127】

- 1、41、61 n型GaN基板(基板)

- 2、42、62 半導体層(窒化物系半導体層)

- 7、8、47、48、67、68 剥開面(第1の分割による分割面)

- 9、49、69 剥開用溝

- 9a、9b、49、49b、69a、69b、69c、69d 剥開導入用段差部(第2の段差部) 20

- 10 素子分割用溝

- 10a、10b 分離導入用段差部(第1の段差部)

- 21 半田(融着層)

- 30 欠陥集中領域

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【 図 9 】

【図11】

【 図 1 0 】

【図12】

【図13】

【図15】

【図14】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

審査官 小林 和幸

(56)参考文献 特開2003-017791(JP,A)

特開2004-179350(JP,A)

特開昭60-123086(JP,A)

特開平11-233893(JP,A)

特開2003-069152(JP,A)

特開2002-246698(JP,A)

特開平01-280388(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01S 5/00 - 5/50