**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) . Int. Cl.<sup>6</sup>

G06F 1/12

(45) 공고일자 2005년07월29일

(11) 등록번호 10-0472292

(24) 등록일자 2005년02월04일

|             |                   |             |                 |

|-------------|-------------------|-------------|-----------------|

| (21) 출원번호   | 10-1998-0705103   | (65) 공개번호   | 10-1999-0076975 |

| (22) 출원일자   | 1998년07월02일       | (43) 공개일자   | 1999년10월25일     |

| 번역문 제출일자    | 1998년07월02일       |             |                 |

| (86) 국제출원번호 | PCT/US1996/019446 | (87) 국제공개번호 | WO 1997/25664   |

| 국제출원일자      | 1996년12월05일       | 국제공개일자      | 1997년07월17일     |

(81) 지정국

국내특허 : 아일랜드, 일본,

EP 유럽특허 : 오스트리아, 벨기에, 스위스, 독일, 덴마크, 스페인, 프랑스, 영국, 그리스, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투칼, 스웨덴,

(30) 우선권주장 08/582,448 1996년01월03일 미국(US)

(73) 특허권자 크레던스 시스템스 코포레이션

미합중국 캘리포니아주 프레몬트 포리어 애비뉴 215(72) 발명자 밀러 찰스 에이.

미합중국 씨에이 94539 프레몬트 세둠 로드 48705(74) 대리인 김재만

유미특허법인**심사관 : 허영한****(54) 동기식논리회로의신호디스큐시스템****요약**

글로벌 클록 신호(CLKG)는 유사한 길이를 가지며 유사하지 않은 신호 전파속도를 가지는 2개의 개별적인 전송 라인(18A, 18B)을 통해 분산된 동기식 논리 회로의 각 모듈(16(1)-16(N))로 분배된다. 각 모듈에 도달하는 글로벌 클록 신호의 해당 펄스의 위상차는 전송 라인의 길이에 비례하며, 양 전송 라인의 고유 클록 신호 지연에 비례한다. 각 모듈의 디스큐 회로(18(1)-18(N))는 글로벌 클록 신호가 모듈에 도달한 후 이 신호를 지연하여 로컬 클록 신호(CLK(1)-CLK(N))를 생성한다. 디스큐 회로는 모듈에 도달한 글로벌 클록 신호 펄스의 위상차를 검출하여, 제1 전송 라인의 고유 지연을 결정한 후, 로컬 클록 지연을 조정하여 고유 지연의 총합 및 로컬 클록 지연이 평균 지연과 일치하도록 한다.

**대표도**

도 1

명세서

## 기술분야

본 발명은 디지털 시스템의 신호원(signal source)와 면 거리의 동작 모듈 사이에 전송된 신호를 디스큐(deskew)하고 또 는 시간을 보상하기 위한 시스템에 관한 것이다.

## 배경기술

하나의 세트의 상호 연결된 동작 모듈로 구성된 동기식 디지털 논리회로에서는, 각 모듈로 분배된 여러 신호 중 하나의 신호는 모듈간 동작의 타이밍을 제어하는 클록 신호이다. 예를 들어 컴퓨터는, 액시에 탑재되고 백플레인 배선(backplane wiring)에 의해 중앙 프로세서 및 클록 신호원을 포함하는 마더 보드(mother board)와 상호 연결된 복수의 회로기판(circuit board)을 포함할 수 있다. 일반적으로 백플레인 내의 도체 중 하나는 클록 신호를 각각의 회로 기판으로 전송한다. 동기식 시스템에서는 기준 신호를 상대적 시간에 동기화하여, 기준 신호 경로 지연이 상기 시스템에 타이밍 대기시간(latency)(신호 스큐(skew))을 유도하지 않도록 하는 것이 바람직하다.

또한 신호 스큐는 동기식으로 함께 동작해야 하는 분산된 구성 요소를 가지는 전자 장치의 경우 문제가 될 수 있다. 예를 들어, 집적회로(IC) 검사기는 호스트 유닛 및 상기 호스트 유닛과 연결된 다중 동작 모듈을 포함할 수 있다. 각 동작 모듈은 테스트 중인 IC의 개별 핀과 인터페이스 할 수 있다. 서로 다른 시간에, 동작 모듈은 테스트 신호를 IC 핀으로 전송할 수 있으며, IC의 상기 핀에 의해 발생된 출력 데이터를 획득할 수 있다. 호스트 유닛의 기능 중 하나는 동작 모듈의 동작을 조정하는 것이다. 테스트 중인 장치(Device Under Test; DUT)에 도달하는 신호의 도달 시간을 동기화하기 위해, 모듈간의 신호 스큐를 제거해야 한다. 예를 들어, 테스트 개시를 신호하기 위해 호스트 유닛이 "시작(start)" 신호를 각 동작 모듈로 전송할 수 있다. 또한 호스트 유닛은 클록 신호를 각 동작 모듈로 전송하여, 테스트가 진행되는 동안 동작 모듈의 동작을 동기화하고 테스트가 진행되는 동안 호스트와 모듈간의 통신을 동기화한다. 클록 및 다른 제어 신호가 서로 다른 거리를 이동하여 동작 모듈에 도달하는 경우, 이들 신호는 서로 다른 시간에 서로 다른 모듈에 도달한다. 이러한 다양한 제어 및 클록 신호의 스큐가 테스터의 동작 주파수에 비해 충분히 크다면 모듈 작동간에 타이밍 부정합(mismatch)이 발생할 수 있으며 모듈을 출발하여 DUT에 도달하는 신호를 동기화하는데 있어 역효과를 미칠 수 있다.

1994년 11월 29일, Watson 등에게 허여된 미합중국 특허번호 5,369,640은 개별 전송 라인을 소스로부터 각 동작 모듈로 제공함으로써 그리고 이들 전송 라인이 모두 동일한 길이를 가지도록 조정함으로써, 면 거리의 동작 모듈로 전송된 신호의 스큐를 감소하는 시스템에 대하여 서술하고 있다. 그러나 신호 스큐 문제를 해결하기 위한 이러한 "스타 버스(star bus)" 방법은 많은 수의 전송 라인이 신호원과 연결되어야 하기 때문에 복수의 동작 모듈을 가지는 시스템에서는 다소 다루기 힘들 수 있다.

신호 스큐를 제거하기 위한 다른 방법이 1984년 5월 8일, Tague 등에게 허여된 미합중국 특허번호 4,447,870에 개시되어 있다. 여기에서는 각 동작 모듈에 도달한 후 클록 신호를 더 지연시키는 조정 가능한 지연 회로(delay circuit)를 각 동작 모듈에 제공한다. 각 동작 모듈의 지연 회로를 조정하여, 클록 신호 전송 라인 및 조정 가능한 지연 회로에 의해 제공된 지연의 합을 표준 지연과 일치시킨다. 이러한 방법은 클록 신호가 백플레인에 의해 모든 동작 모듈과 연결되어 있는 단일 전송 라인을 통해 동작 모듈로 전송되도록 한다. 그러나 이 방법은 각 동작 모듈에서의 지연 회로를 수동으로 조정해야 하기 때문에 시간 소비적이며, 어려운 과정을 요구한다. 또한 동작 모듈이 전송 라인을 따라 새로운 위치로 이동할 때마다, 클록 지연 회로를 재조정해야 한다.

## 발명의 상세한 설명

본 발명에 따른 디스큐 시스템(deskewing system)은 단일 신호원에 의해 발생된 글로벌(global) 기준 신호에 응답하여 디지털 시스템의 각 분산된 모듈에 로컬 클록 신호를 제공한다. 글로벌 신호는 유사한 길이를 가지지만 상이한 신호 전파 속도(velocity of signal propagation)를 가지는 2개의 개별적인 전송 라인을 통해 신호원로부터 각 모듈로 전송된다. 2개의 전송 라인을 통해 각 모듈에 도달하는 2개의 글로벌 신호의 위상차는 전송 라인의 길이에 비례하며, 따라서 양 전송 라인의 고유한 클록 신호 지연에 비례한다. 각 모듈의 디스큐 회로는 글로벌 클록 신호가 2개의 전송 라인 중 제1 전송 라인을 통해 모듈에 도달하면 이 신호를 더 지연하여 모듈의 로컬 클록 신호를 생성한다. 디스큐 회로는 2개의 전송 라인을 통해 모듈에 도달하는 해당 글로벌 기준 신호의 위상차를 검출하여 제1 전송 라인의 고유 지연을 결정한다. 디스큐 회로는 그후 로컬 클록 지연을 조정하여 전송 라인의 고유 지연 및 로컬 클록 지연의 합이 표준 지연과 일치하도록 한다. 모든 모듈에 대하여 표준 지연만큼 동일하게 지연시키기 때문에, 모든 모듈에서 생성된 로컬 클록 신호는 모두 위상 동기된다.

따라서 본 발명의 목적은 동기식 논리 회로 시스템의 개별적인 모듈의 동작을 밀접하게 동기시키는 시스템을 제공하는 것이다.

본 명세서의 결론부는 본 발명의 요지를 구체적으로 지적하고 명확하게 청구한다. 그러나 당업자는 동일한 참조 번호가 동일한 구성요소를 가리키는 다음의 도면을 참조하여 명세서의 나머지 부분을 읽음으로써, 본 발명의 작동 방법 및 구성과 본 발명의 이점과 목적을 잘 이해하게 될 것이다.

### 도면의 간단한 설명

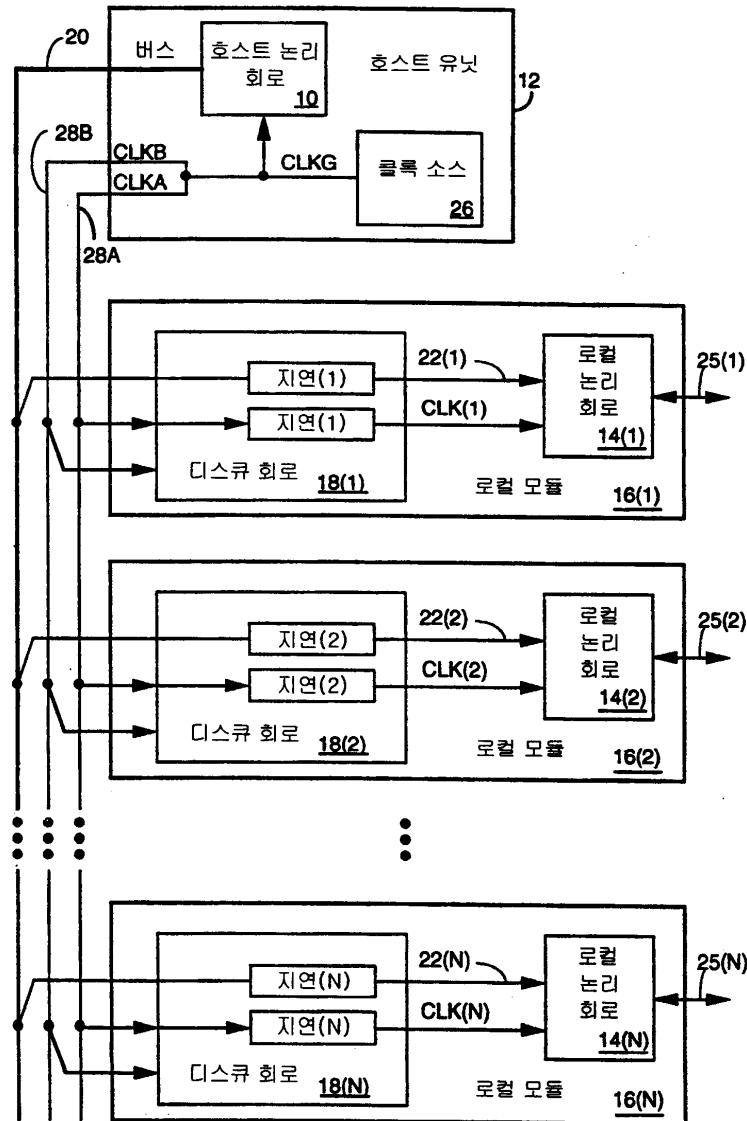

도 1은 본 발명에 따른 신호 디스큐 시스템을 사용하는 모듈의 동기식 논리 회로를 도시하는 블록도이며;

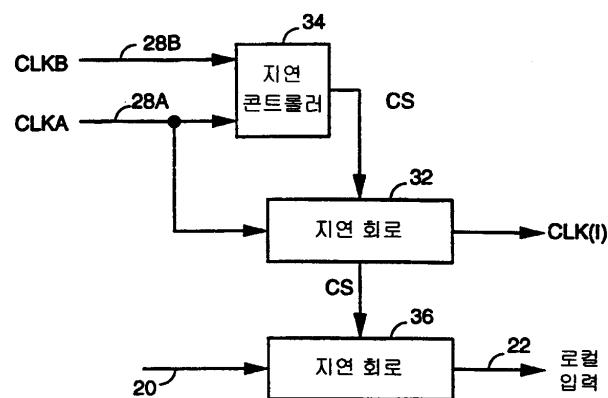

도 2는 도 1의 디스큐 회로를 보다 상세한 형태로 도시하는 블록도이며;

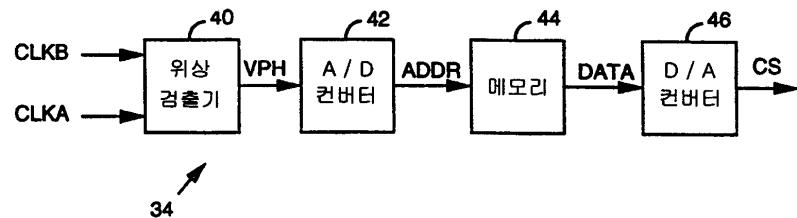

도 3은 도 2의 지연 제어 회로를 보다 상세한 형태로 도시하는 블록도이며;

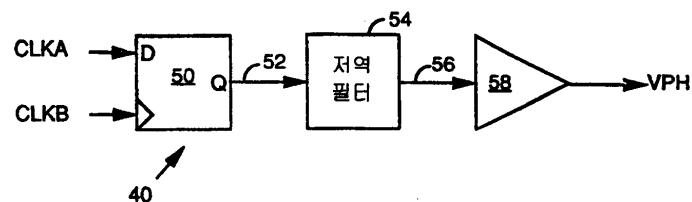

도 4는 도 2의 위상 검출기 회로로 사용하기에 적합한 종래 기술의 회로를 도시하는 블록도이며;

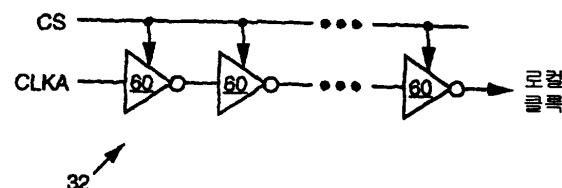

도 5는 종래 기술의 지연 회로를 도시하는 블록도이며;

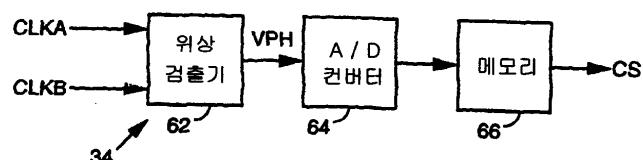

도 6은 도 2의 지연 제어 회로의 다른 실시예를 도시하는 블록도이며;

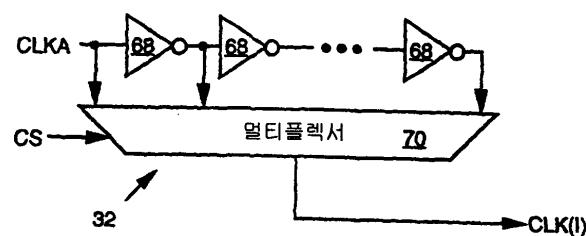

도 7은 종래 기술의 지연 회로를 도시하는 블록도이며;

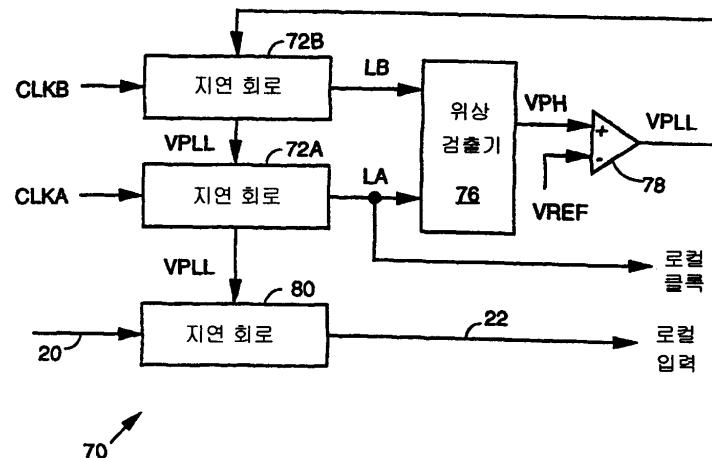

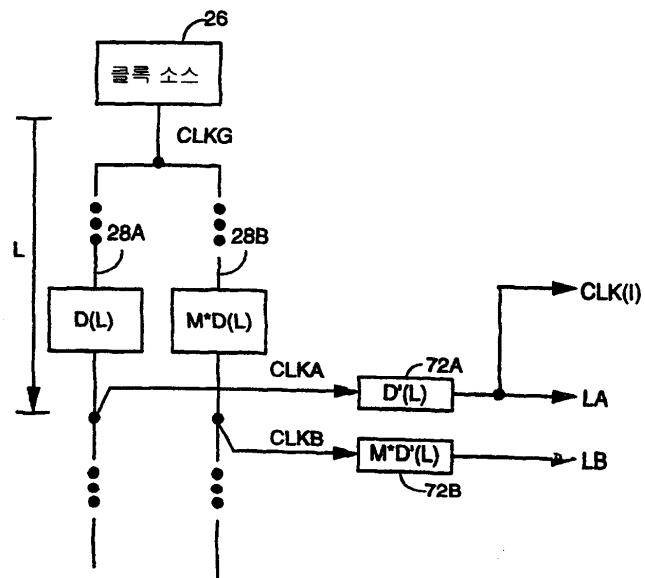

도 8은 도 1의 디스큐 회로의 다른 실시예를 도시하는 블록도이며;

도 9는 도 7의 디스큐 시스템의 클록 신호 지연을 도시하는 블록도이며;

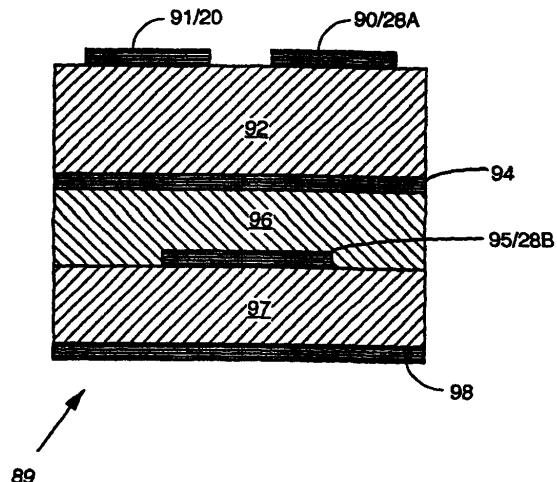

도 10은 서로 다른 신호 전파 속도를 가지는 전송 라인을 제공하는 회로 기판의 단면을 도시한다.

### 실시예

도 1을 참조하여 설명하면, 본 발명은 동기식 논리 시스템의 호스트 유닛(12) 내의 호스트 논리 회로(host logic circuit, 10)와 동작 모듈(16(1)-16(N))내의 분산된 N개의 로컬 논리 회로(local logic circuit, 14(1)-14(N)) 세트 사이에 전송된 신호를 디스큐하는 시스템에 관한 것이다. 동작 모듈(16)은 호스트 논리 회로(10)로부터 서로 다른 간격으로 위치한다. 호스트 논리 회로(10) 및 로컬 논리 회로(14)는 종속적인 요소이다. 예를 들어 논리 시스템은 컴퓨터일 수 있으며, 호스트 논리 회로(10)는 종래의 마이크로프로세서이며 로컬 논리 회로(18)는 메모리, 주변 I/O 콘트롤러 또는 컴퓨터 프로세서와 동기식 방식으로 통신하는 다른 소자일 수 있다. 예를 들어, 시스템(10)은 또한 집적 회로 테스터 구조물로 분산될 수 있으며, 각 로컬 논리 회로(14)는 테스트 중인 집적 회로 소자의 개별적인 핀에 인터페이스를 제공한다. 테스트가 진행되는 동안의 서로 다른 시간에 동작 모듈은 테스트 신호를 테스트 중인 소자의 단자(25(1)-25(N))로 전송할 수 있으며, IC의 핀에서 생성된 출력 데이터를 획득할 수 있다. 호스트 유닛은 제어 신호 및 명령어를 동작 모듈로 제공한다.

일반적인 동기식 논리 시스템에서는 시스템의 동작을 동기화하는 글로벌 클록 신호가 각 로컬 논리 회로로 동시에 전송된다. 로컬 논리 회로가 공간적으로 분산되어 있으므로, 공통 클록 신호원에서 시작하는 클록 신호의 펄스가 로컬 논리 회로에 동시에 도달하지 않을 수 있다. 특히 로컬 논리회로가 서로 다른 위치에서 공통 전송 라인을 탭(tap)하여 글로벌 클록 신호를 획득하는 경우에 더더욱 그러하다. 클록 신호 펄스가 클록 소스를 떠나는 시간과 상기 펄스가 다양한 로컬 논리 회로에 도달하는 시간의 차이("스퀴")는 그들이 서로 동기식으로 동작하는 성능에 영향을 미친다. 본 발명은 클록 신호 스퀴를 보상하여 모두 위상 동기된 로컬 클록 신호를 각 로컬 논리 회로(14)에 제공한다. 상기 신호 분배 시스템은 또한 신호 경로 길이의 차에 기인하여 발생하는 호스트 논리 회로(10)와 로컬 논리 회로(14) 사이에 전송된 제어 및 통신 신호의 스퀴를 보상한다.

따라서 본 발명의 디스큐 시스템은 동작 모듈(16(1)-16(N)) 중에서 해당하는 모듈 내에 각각 탑재된 N개의 디스큐 회로(18(1)-18(N)) 세트를 포함한다. 상기 디스큐 시스템은 또한 호스트 논리 회로(10)와 각 디스큐 회로(18) 사이에서 통신 및/또는 제어 신호를 운송하는 제어 신호 버스(20)를 포함한다. 버스(20)는 CLKA(28A) 송신 경로와 동일한 전파 속도를

가지는 전송 경로를 사용한다. I번째의 디스큐 회로(18(I))는 I번째의 해당 로컬 논리 회로(14(I))와 버스(20) 사이에 인터페이스를 제공하며, 이때 "I"는 1부터 N까지의 모든 수이다. 호스트 논리 회로(10)에 의해 생성된 출력 신호는 버스(20)를 통해 각 디스큐 회로(18(I))로 전송되며, 이 신호는 상기 디스큐 회로의 조정 가능한 지연 DELAY(I)를 통과하여 입력 신호(22)로서 해당 로컬 논리 회로(14(I))로 전송된다.

또한 본 발명의 신호 분배 시스템은 클록 소스(26) 및 상기 클록 소스(26)와 함께 묶여 있는 한 쌍의 전송 라인(28A, 28B)을 포함하며, 각 클록 소스(26)는 디스큐 회로(18)와 상호 접속되어 있다. 클록 소스(26)는 주기적 글로벌 클록 신호 CLKG를 각 전송 라인(28A, 28B)에 동시에 위치시킨다. 전송 라인(28A, 28B)은 글로벌 클록 신호를 개별적인 클록 신호 CLKA 및 CLKB로서 각각 디스큐 회로(18)로 전송한다. 각 디스큐 회로(18)는 전송 라인(28A, 28B)을 따라 유사한 간격으로 전송 라인(28A, 28B)을 텁한다. CLKA 및 CLKB 신호는 소정의(I번째) 디스큐 회로(18(I))에 도달한 후, 디스큐 회로(18(I+1))에 도달한다. 그러나 클록 소스(26)와 I번째 디스큐 회로(18(I)) 사이를 이동하는 동안, CLKA 신호는 CLKB 신호가 전송 라인(28B)을 따라 이동하는 것과 실질적으로 동일한 간격으로 전송 라인(28A)을 따라 이동한다.

본 발명에 따라, 전송 라인(28A, 28B)은 서로 다른 신호 전파 속도를 가진다. 구체적으로, 전송 라인(28A) 상의 CLKA 신호의 전파 속도는 전송 라인(28B) 상의 CLKB 신호 전파 속도보다 M배 빠르며, 이때 M은 1보다 큰 수이다. 따라서 이들이 동일한 거리를 이동함에도 불구하고, CLKA 신호의 펄스는 CLKB 신호의 대응 펄스보다 더 빨리 I번째 디스큐 회로에 도달한다. 디스큐 회로(18(I))에 도달하는 CLKA 신호 및 CLKB 신호의 해당 펄스의 도달 시간 지연은 클록 소스(20)와 디스큐 회로(18(I)) 사이의 전송 라인(28A, 28B)의 길이에 비례한다. 따라서 CLKA와 CLKB의 위상차는 소스(26)로부터 전송 라인(28A, 28B)을 따라 디스큐 회로(18(I))가 CLKA 및 CLKB 신호를 검출하는 지점까지의 전송 라인의 길이이다.

버스(20)는 전송 라인(28A)과 유사한 전파 속도를 가지는 하나 이상의 전송 라인을 포함한다. 버스(20) 상의 호스트 논리 회로(10)와 모든 디스큐 회로(18(I)) 사이의 거리는 전송 라인(28A) 상의 클록 소스(26)와 디스큐 회로(18(I)) 사이의 거리와 실질적으로 동등하다. 신호 펄스가 버스(20)를 통해 논리 회로(10)를 출발하는 시간과 전송 라인(28)을 통해 클록 소스(26)를 출발하는 시간이 동시에 동일한 경우에, 이들 신호가 동일한 거리를 이동하며 동일한 전파 속도를 가지기 때문에 디스큐 회로(18(I))에 동시에 도달한다.

각 디스큐 회로(18(I))는 CLKA 및 CLKB 신호로부터 로컬 클록 신호 CLK(I)를 도출하고 로컬 클록 신호 CLK(I)를 해당 로컬 논리 회로(14(I))에 입력으로서 공급한다. 디스큐 회로(18)는 로컬 클록 신호 CLK(1)-CLK(N)가 실질적으로 모두 위상 동기되도록 한다. 로컬 논리 회로(14(I)-14(N))는 이들 신호를 로컬 입력 신호(22(I)-22(N))를 수신하는 것을 포함하여 그들의 동작을 동기화하는 타이밍 신호로서 사용한다.

각 디스큐 회로(18(I))는 조정 가능한 지연 시간 DELAY(I)만큼 입력 CLKA 신호를 지연함으로써 로컬 클록 신호 CLK(I)를 생성한다. 디스큐 회로(18(I))가 클록 소스(26)와 가까워질수록, 디스큐 회로(18(I))는 CLKA 신호를 더 길게 지연시켜 로컬 클록 신호 CLK(I) 출력을 생성한다. 구체적으로 각 디스큐 회로(18(I))는 모든 로컬 클록 신호 CLKL(I)-CLKL(N)을 모두 위상 동기하기에 충분한 시간만큼 CLKA를 지연한다.

각 디스큐 회로(18(I))는 우선 CLKA 및 CLKB 신호의 해당 펄스가 도달하는 시간차를 측정함으로써 CLKA 신호를 지연 할 시간을 결정한다. 이러한 측정된 시간차는 클록 소스(26)로부터 디스큐 회로(18(I))까지의 전송선(28A, 또는 28B)의 길이에 비례하며, 따라서 CLKA 신호가 클록 소스(26)로부터 디스큐 회로(18(I))로 이동하는데 필요한 시간 D(I)에 비례한다. DELAY(I)를 조정하여, D(I) 및 DELAY(I)의 합을 다음과 같이 일정한 전체 지연(constant total delay) TD와 일치시키며, 여기에서 SKEW(I)는 소스(26)의 글로벌 클록 신호에 대한 로컬 클록 신호 CLK(I)의 스케일 의미한다.

$$\text{SKEW}(I) = TD$$

$$= D(I) + \text{DELAY}(I)$$

$$= \text{CONSTANT}$$

또한 각 디스큐 회로(18(I))는 로컬 입력 신호(22(I))를 동일 지연 DELAY(I)를 통해 버스(20)의 선으로부터 로컬 논리 회로(14(I))로 전달한다. 따라서 호스트 논리 회로(10)에서 시작하는 신호는 로컬 입력 신호(22(I))로서 모든 로컬 논리 회로(14(I))에 동시에 도달한다.

도 2를 참조로 하여 설명하면, 본 발명의 바람직한 실시예에 따라, 도 1의 디스큐 회로(18(I))는 DELAY(I)에 의해 CLKA 신호를 조정 가능하게 지연하여 로컬 클록 신호 CLK(I) 신호를 발생하는 지연 회로(32)를 포함한다. 지연 콘트롤러(34)는

이 위상차를 측정하고 지연 회로(32)의 지연, DELAY(I)를 적당하게 조정하는 출력 신호 CS를 생성한다. CS 신호는 또한 지연 회로(36)에 지연 제어 입력으로서 인가되며, 지연 회로(36)는 지연 회로(32)와 유사한 구성을 가지며 CS 신호에 응답하여 유사한 지연 DELAY(I)를 제공한다. 지연 회로(36)는 버스(20)의 선에 도달하는 신호의 도달 시간을 지연하여 로컬 입력 신호(22(I))를 도1의 로컬 논리 회로(14(I))로 제공한다. 설명의 편의를 위해, 단지 하나의 지연 회로(36)가 도 2에 도시되어 있으며, 필요하다면, 버스(20)의 각 선을 로컬 논리 회로의 입력단 및/또는 출력단과 연결하기 위해 CS 신호에 의해 제어되는 유사한 지연 회로를 제공할 수 있다.

도 3은 지연 콘트롤러(34)의 하나의 실시예를 도시한다. 지연 콘트롤러(34)는 CLKA 및 CLKB 신호를 수신하고 그들로부터 CLKA와 CLKB의 위상차에 비례하는 전압을 가지는 출력 신호 VPH를 생성하는 위상 검출기(phase detector, 40)를 포함한다. A/D 컨버터(analog-to-digital converter, 42)는 상기 VPH 신호를 유사한 크기를 갖는 디지털 값 ADDR로 변환한다. 상기 ADDR은 제어 데이터(DATA)를 각 주소에 기억시키고 현재 주소 지정된 DATA를 D/A 컨버터(digital-to-analog converter, 46)에 공급하는 주소 지정 가능 메모리(addressable memory, 22)에 주소 저장한다. D/A 컨버터(46)는 DATA의 크기에 비례하는 크기를 갖는 CS 신호를 생성한다. 메모리(44)의 각 어드레스에 기억된 데이터를 조정하여, CLKA와 CLKB의 모든 주어진 위상차에 대하여 CS 신호가 적당한 지연을 지연 회로(32)에 제공하는 크기를 가지도록 한다. 오실로스코프 또는 다른 위상 검출 장치를 사용하여 클로벌 클록 신호 CLKG와 로컬 클록 신호 CLK(I)의 위상 관계를 모니터하고, CLK(I) 및 CLKG가 각 ADDR 값에 대하여 바람직한 위상 관계를 가질 때까지 DATA를 반복하여 조정함으로써 이러한 저장된 DATA 값을 결정할 수 있다.

도 4는 도 2의 위상 검출기(40)로 사용하기에 적합한 잘 알려진 종래 기술의 위상 검출기 회로를 도시한다. D형 플립플롭(50)은 CLKA가 CLKB를 앞서는 경우에는 출력 신호(52)를 하이(high)로 구동하고, CLKA가 CLKB보다 뒤쳐지는 경우에는 로우(low)로 구동한다. 저역 필터(54)는 신호(52)를 필터하여 입력을 증폭기(58)에 제공한다. 증폭기(58)는 입력 신호(56)에 응답하여 VPH 신호 출력을 발생한다. VPH의 크기는 CLKA와 CLKB 신호의 위상차에 비례한다.

도 5는 도 1의 지연 회로(32)로 사용하기에 적합한 잘 알려진 종래 기술의 지연 회로를 도시한다. 지연 회로(32)는 직렬로 연결된 인버터(60) 세트를 포함하며, CLKA 신호는 직렬로 연결된 첫 번째 인버터의 입력단에 공급되며, 로컬 클록 신호 CLK(I)는 직렬로 연결된 최종 인버터의 출력단에서 발생한다. CS 신호는 인버터에 전원을 공급한다. CS 신호의 크기가 증가함에 따라 각 인버터(60)의 신호 전파속도 또한 증가하며, 그 결과로 지연 회로(32)의 지연을 감소시킨다.

도 6 및 도 7은 지연 콘트롤러(34) 및 지연 회로(32)의 다른 실시예를 도시한다. 도 5를 참조하여 설명하면, 지연 콘트롤러(34)는 도 2의 위상 검출기(40), A/D 컨버터(42) 및 메모리(44)와 유사한 위상 검출기(62), A/D 컨버터(64) 및 메모리(66)를 포함한다. 그러나 이 실시예에서, 지연 회로(32)에 공급된 CS 신호는 도 2의 메모리(44)가 출력 DATA 신호를 생성하는 방식과 동일한 방식으로 메모리(64)에 의해 생성된 디지털 데이터 신호이다. 도 7을 참조하여 설명하면, 다른 지연 회로(32)는 직렬로 연결된 인버터(68) 세트를 포함하며, CLKA 신호는 상기 직렬로 연결된 첫 번째 인버터에 입력으로서 공급된다. 도 6의 메모리(66)의 디지털 CS 출력에 의해 제어되는 멀티플렉서(70)는 하나의 인버터(68)의 출력을 로컬 클록 신호 CLK(I)로 선택한다. 도 2의 메모리(44)에 기억될 변환 데이터의 값을 확정하는 상기 방식으로 메모리(64)에 저장된 변환 데이터 값을 실험적으로 구축할 수 있다. 도 7에 도시된 지연 회로(32)의 실시예는 당업자에게 잘 알려져 있다.

도 8은 도 1의 디스큐 회로(30(I))의 다른 실시예의 디스큐 회로(70)를 도시한다. 디스큐 회로(70)는 한 쌍의 지연 회로(72A, 72B)를 포함한다. 지연 회로(72A)는 CLKA를 지연시켜 제1 로컬 클록 LA(클록 LA는 출력 로컬 클록 신호 CLK(I)로서 사용됨)를 생성한다. 지연 회로(72B)는 CLKB를 지연하여 제2 로컬 클록 신호 LB를 생성한다. LA 및 LB 신호는 LA와 LB의 위상차에 비례하는 전압을 가지는 출력 신호 VPH를 생성하며 도 4의 위상검출기(40)와 유사한 위상 검출기(76)에 입력으로서 공급된다. 차동 증폭기(78)는 VPH 신호를 고정 전압 기준 신호 VREF와 비교하고 VPH와 VREF의 차에 비례하는 크기를 가지는 출력 신호 VPML을 생성한다. VPML 신호를 지연 회로(72A, 72B)의 제어 입력으로서 공통적으로 공급한다.

지연 회로(72A, 72B)는 유사한 방식으로 변화한다. VPML이 증가함에 따라, 지연 회로(72A, 72B)에 의해 제공된 지연은 감소된다. 그러나 모든 주어진 크기의 VPML에 대하여, 지연 회로(72B)에 의해 제공된 지연은 지연 회로(72A)에 의해 제공된 지연에 비해 M배 길다. 상기한 바와 같이, 도 1의 전송 라인(28A)의 신호 전파 속도는 전송 라인(28B)의 신호 전파 속도에 비해 M배 빠르다. 따라서 클록 소스와 모든 디스큐 회로 사이의 전송 라인(28B)에 의해 제공된 신호 지연은 전송 라인(28A)의 지연 보다 M배 길다. 지연 회로(72A, 72B)가 도 5의 회로(32)와 유사한 경우에, 예를 들어 2개의 지연 회로의 인버터 단의 개수를 서로 다르게 하여 2개의 지연 회로의 지연비(delay ratio) M을 구축할 수 있다. 예를 들어 인버터 단이 CMOS 트랜지스터에 의해 구현되는 경우에, 당업자에게 잘 알려진 방식으로 인버터(56)를 구성하는 CMOS 트랜지스터의 채널 폭을 다르게 함으로써 지연율 M을 미세하게 조정할 수 있다.

도 9는 도 8의 회로의 신호 지연을 도시한다. 로컬 모듈은 클록 소스(26)로부터 가변적인 거리(L)로 전송 라인(28A, 28B)을 텁(tap)하여, CLKA 및 CLKB 신호를 획득한다. 텁과 클록 소스(26) 사이의 전송 라인(28A)의 고유 신호 지연  $D(L)$ 는 L과 직선 비례한다. 전송 라인(28A)의 신호 전파 속도가 전송 라인(28B)의 신호 전파 속도보다 M배 빠르기 때문에, 전송 라인(28B)의 고유 신호 지연  $M*D(L)$ 은 전송 라인(28A)의 고유 신호 지연  $D(L)$ 보다 M배 길다.(여기에서 "\*" 표시는 곱셈을 의미한다) 또한 지연 회로(72A)에 의해 제공된 지연은 L과 상관관계(function)가 있으며, 도 9에서는  $D'(L)$ 로 표시된다. 모든 주어진 크기의 VPPLL에 대하여, 도 7의 지연 회로(72B)에 의해 제공된 지연이 지연 회로(72A)에 의해 제공된 지연보다 M배 길기 때문에 회로(72B)의 지연은  $M*D'(L)$ 가 된다.

도 9를 검토하면 알 수 있듯이, 글로벌 클록 CLKG는 클록 소스(26)의 출력단을 출발하여 전송 라인(28A) 및 지연 회로(72A)의 지연  $D(L)$  및  $D'(L)$ 의 합만큼 지연되어 로컬 클록 LA가 된다. 따라서 CLKG에 대한 로컬 클록 LA의 위상은 다음과 같다.

$$\text{PHASE(LA)} = [D(L)] + [D'(L)] \quad (1)$$

유사하게 글로벌 클록 CLKG에 대한 로컬 클록 LB의 위상은 다음과 같다.

$$\text{PHASE(LB)} = [M*D(L) + M*D'(L)] \quad (2)$$

따라서 도 7의 위상 검출기(76)에 의해 검출된 LA와 LB의 위상차는 다음과 같다.

$$\text{PHASE(B:A)} = \text{PHASE(LB)} - \text{PHASE(LA)}$$

$$\text{PHASE(B:A)} = [M*D(L) + M*D'(L)] - [D(L) + D'(L)]$$

$$\text{PHASE(B:A)} = (M-1) * [D(L) + D'(L)] \quad (3)$$

상기 방정식 (1)과 (3)를 통해 우리는 다음 공식을 얻을 수 있다.

$$\text{PHASE(LA)} = D(L) + D'(L) = \text{PHASE(B:A)} / (M-1) \quad (4)$$

위상 검출기 (76) 및 차동 증폭기(78)에 의해 제공되는 피드백 제어 VPPLL은 로컬 클록 LB와 LA의 위상차 PHASE(B:A)를 증폭기(78)에 공급된 기준 신호 VREF의 전압에 의해 결정된 일정한 값으로 유지한다. 피드백 루프는 VREF와 동등한 VPH를 요구한다. VPH가 PHASE(B:A)와 비례하기 때문에, PHASE(B:A)는 VPH를 VREF와 일치시키는데 필요한 모든 값을 고정된다.

PHASE(B:A) 및 M이 L과는 상관없는 독립 상수이기 때문에, 방정식(4)으로부터 클록 소스(26)의 출력단의 글로벌 클록 신호 CLKG에 대한 로컬 클록 LA의 위상인 PHASE(LA) 또한 L로부터 독립적이라는 것을 알 수 있다. 이것은 유사한 크기를 갖는 VREF 신호가 모든 디스큐 회로 내의 차동 증폭기(78)에 공급되는 경우에, 이 시스템의 모든 디스큐 회로에서 발생한 로컬 클록 신호 LA는 클록 소스(26) 출력단의 글로벌 클록 신호 CLKG와 동일한 위상을 가진다는 것을 의미한다. LA 신호가 로컬 논리 회로로 출력되는 로컬 클록 신호 CLK(I)로서 사용되기 때문에, 도 1의 모든 로컬 클록 신호 CLK(1)-CLK(N)가 모두 위상 동기되며, 로컬 논리 회로 14(1)-14(N)의 동작은 밀접하게 동기화된다.

로컬 클록 신호 LA와 LB의 일정한 위상차 PHASE(B:A)가  $(M-1)*D(LMAX)$ 와 일치하도록 도 8의 VREF의 크기를 선택하여야 한다. LMAX는 전송 라인(28)을 따라 클록 소스(26)로부터 가장 먼 거리의 로컬 모듈 전송 라인 텁보다 더 먼 거리의 어느 한 지점까지의 거리이다. 따라서  $D(LMAX)$ 는 클록 소스(26)와 상기 먼 거리의 지점 사이의 전송 라인(28A)의 전체 고유 신호 지연이다. 최종 지연  $\text{DELAY}(1) - \text{DELAY}(N)$ 이 양(positive)의 수이며, 디스큐 회로(18(1)-18(N)) 내의 고유 지연 회로의 성능 범위 안이 되도록 VREF의 값을 선택해야 한다.

우리는 방정식(4)으로부터 2개의 전송 라인의 전파속도비인 M값이 1보다 커야 한다는 것을 알 수 있다. 전송 라인이 백플레인 회로 기판 위에서 구현된 경우에, 이렇게 하는 방법 중 하나는 하나의 전송 라인용 마이크로스트립(microstrip) 도체 및 다른 전송 라인용 스트립라인(stripline) 도체를 사용하는 것이다. 마이크로스트립 도체는 회로 기판의 상부에 형성되며, 스트립라인 도체는 회로 기판의 층 사이에 위치한다. 예를 들어 비교 유전율(dielectric constant) 5.0을 가지는 G-

10 유리섬유(Fiberglass) 기판의 경우, 마이크로스트립 도체의 전파 속도는 565 ps/ft(picoseconds/foot)가 되며, 스트립 라인 도체의 전파 속도는 442 ps/ft가 된다. 따라서 속도비는 1.28이 된다. 2개의 도체의 신호 지연 차는 전송 라인 1인치 길이당 68ps이다.

M을 증가시켜, 서로 다른 유전율을 가지는 회로 기판 층을 사용하여 디스큐 분해능을 개선할 수 있다. 도 10은 다중 층 회로 기판(89)의 단면을 도시하며, 전송 라인(28A) 및 버스 라인(20)을 제공하는 마이크로스트립 도체(90, 91)는 접지 평면 도체(94) 위의 FR4 절연층(dielectric layer, 92) (비교 유전율 = 4.8)의 상부에 구성된다. 전송 라인(28B)을 제공하는 스트립라인(95)은 2개의 듀로이드(Duroid) 절연층(96, 97) (비교 유전율 = 10) 사이에 위치하며, 제2 접지 평면(98)은 회로 기판의 바닥 위에 위치한다. 이러한 배열은 1.82의 전파속도비 M을 발생시킨다. 2개의 도체의 신호 지연 차는 전송선 1인치 길이당 120ps이다.

분산된 동기식 논리 회로의 신호 디스큐 시스템에 대하여 설명하였다. 전술한 명세서가 본 발명의 바람직한 실시예에 대하여 서술하고 있지만, 당업자는 보다 큰 관점에서 본 발명을 일탈하지 않고 바람직한 실시예에 대하여 복수의 변형을 실시할 수 있다. 다음의 청구항은 따라서 본 발명의 범위와 사상 내에서 이러한 모든 변경을 포괄할 것을 의도한다.

### (57) 청구의 범위

#### 청구항 1.

클록 신호원에 의해 발생된 글로벌 클록 신호(global clock signal)에 응답하여 분산된 동기식 논리 회로의 복수의 모듈 각각에서 실질적으로 서로 위상 동기하는 개별적인 로컬 클록 신호(local clock signal)를 생성하는 방법으로서,

전송 라인을 통해 상기 클록 신호원으로부터 상기 각 모듈로 상기 글로벌 클록 신호를 전송하는 동시에 상기 클록 신호원과 각 모듈 사이의 상기 전송 라인에 대한 길이를 감지하는 단계, 그리고

상기 전송 라인을 통해 상기 각 모듈에 도달하는 상기 글로벌 클록 신호를 상기 클록 신호원과 상기 모듈 사이의 상기 감지된 전송 라인과 상관관계가 있는 지연 시간만큼 지연시켜, 각 모듈에서 개별적인 로컬 클록 신호를 생성하는 단계

을 포함하는 로컬 클록 신호 생성 방법.

#### 청구항 2.

제1항에 있어서,

상기 지연 시간은 상기 감지된 전송 라인의 길이와 반비례 관계에 있는 로컬 클록 신호 생성 방법.

#### 청구항 3.

클록 신호원에 의해 생성된 글로벌 클록 신호에 응답하여 분산된 동기식 논리 시스템의 복수의 모듈 각각에서 실질적으로 서로 위상 동기하는 개별적인 로컬 클록 신호를 생성하는 방법으로서,

상기 클록 신호원과 상기 모듈 사이에서 실질적으로 동일한 길이를 갖지만 실질적으로 서로 상이한 신호 전파 속도를 가지는 상기 제1 및 제2 전송 라인 각각을 통해 상기 클록 신호원으로부터 상기 각 모듈로 상기 글로벌 클록 신호를 전송하는 단계,

상기 클록 신호원과 상기 각 모듈 사이의 상기 제1 및 제2 전송 라인에 대한 길이를 감지하는 단계, 그리고

상기 제1 및 제2 전송 라인 중 하나의 라인을 통해 상기 각 모듈에 도달하는 상기 글로벌 클록 신호를 상기 모듈과 상기 클록 신호원 사이의 상기 감지된 전송 라인과 상관관계가 있는 지연 시간만큼 지연시켜, 각 모듈에서 개별적인 로컬 클록 신호를 생성하는 단계

을 포함하는 로컬 클록 신호 생성 방법.

#### 청구항 4.

제3항에 있어서,

상기 지연 시간은 상기 감지된 전송 라인의 길이와 반비례 관계에 있는 로컬 클록 신호 생성 방법.

#### 청구항 5.

제3항에 있어서,

상기 클록 신호원과 각 모듈 사이의 상기 제1 및 제2 전송 라인의 길이를 감지하는 단계는 상기 제1 전송 라인을 통해 상기 각 모듈에 도달하는 상기 글로벌 클록 신호의 위상을 상기 제2 전송 라인을 통해 상기 각 모듈에 도달하는 상기 글로벌 클록 신호의 위상과 비교하는 단계를 포함하는 로컬 클록 신호 생성 방법.

#### 청구항 6.

제3항에 있어서,

상기 제1 및 제2 전송 라인의 길이를 감지하고 상기 글로벌 클록 신호를 지연하는 단계는,

상기 제1 전송 라인을 통해 상기 각 모듈에 도달하는 상기 글로벌 클록 신호의 위상을 상기 제2 전송 라인을 통해 상기 각 모듈에 도달하는 상기 글로벌 클록 신호의 위상과 비교하여, 상기 길이를 나타내는 크기를 갖는 제1 신호를 생성하는 단계,

상기 제1 신호에 응답하여 제2 신호를 생성하는 단계, 그리고

상기 글로벌 클록 신호가 상기 제1 및 제2 전송 라인 중 하나를 통해 상기 모듈에 도달한 후 상기 글로벌 클록 신호가 지연 회로를 통과하도록 하여 상기 로컬 클록 신호를 생성하는 단계

를 포함하고,

상기 제2 신호의 크기는 상기 제1 신호의 크기와 소정의 상관 관계가 있고,

상기 지연 회로는 상기 지연 시간만큼 상기 글로벌 클록 신호를 지연하며, 상기 지연 시간은 상기 지연 회로의 제어 입력으로서 공급되는 상기 제2 신호의 크기에 따라 제어되는

로컬 클록 신호 생성 방법.

#### 청구항 7.

제6항에 있어서,

상기 제2 신호를 발생하는 단계는,

주소 지정 가능 메모리의 개별적인 어드레스에 데이터 값을 기억하는 단계,

상기 주소 지정 가능 메모리가 상기 저장된 데이터 값 중 하나의 값을 판독하도록 상기 제1 신호의 크기에 따라 상기 주소 지정 가능 메모리를 주소 지정하는 단계, 그리고

상기 판독된 데이터 값에 따른 크기를 갖는 상기 제2 신호를 생성하는 단계

를 포함하는 로컬 클록 신호 생성 방법.

### 청구항 8.

클록 신호원에 의해 생성된 글로벌 클록 신호에 응답하여 동기식 논리 시스템의 복수의 모듈 각각에서 개별적인 로컬 클록 신호를 생성하는 방법으로서,

제1 및 제2 전송 라인 각각을 통해 상기 클록 신호원으로부터 각 모듈로 상기 글로벌 클록 신호를 전송하는 단계,

상기 제1 전송 라인을 통해 각 모듈에 도달하는 상기 글로벌 클록 신호를 조정 가능한 제1 지연 시간만큼 지연시켜, 상기 모듈에서 제1 로컬 클록 신호를 생성하는 단계,

상기 제2 전송 라인을 통해 각 모듈에 도달하는 상기 글로벌 클록 신호를 조정 가능한 제2 지연 시간만큼 지연시켜, 상기 모듈에서 제2 로컬 클록 신호를 생성하는 단계, 그리고

각 모듈의 상기 제1 및 제2 지연 시간을 조정하여, 각 모듈에서 생성된 제1 및 제2 로컬 클록 신호 사이에 소정의 위상 관계를 제공하는 단계

를 포함하는 로컬 클록 신호 생성 방법.

### 청구항 9.

제8항에 있어서,

상기 제1 및 제2 전송 라인은 상기 클록 신호원과 각 모듈 사이에서 실질적으로 동일한 길이를 가지며, 상기 제1 전송 라인에 대한 글로벌 클록 신호의 전파 속도는 상기 제2 전송 라인에 대한 글로벌 클록 신호의 전파속도의 M배이며, 상기 M은 1 이외의 숫자인 로컬 클록 신호 생성 방법.

### 청구항 10.

제9항에 있어서,

상기 제2 지연 시간 대 상기 제1 지연 시간의 비율은 각 모듈에 대한 상기 M과 실질적으로 동일한 로컬 클록 신호 생성 방법.

### 청구항 11.

클록 신호원에 의해 발생된 글로벌 클록 신호에 응답하여 동기식 논리 시스템의 복수의 모듈 각각에서 개별적인 로컬 클록 신호를 생성하는 장치로서,

상기 클록 신호원으로부터 각 모듈로 상기 글로벌 클록 신호를 전송하는 전송 라인, 그리고

상기 클록 신호원과 각 모듈 사이의 상기 전송 라인에 대한 길이를 감지하고 상기 전송 라인을 통해 각 모듈에 도달하는 상기 글로벌 클록 신호를 상기 모듈과 상기 클록 신호원 사이의 상기 감지된 전송 라인과 상관관계가 있는지연 시간만큼 지연시켜, 상기 모듈에서 상기 로컬 클록 신호를 생성하는 디스큐 수단(deskewing means)

을 포함하는 로컬 클록 신호 생성 장치.

### 청구항 12.

제11항에 있어서,

각 모듈의 상기 지연 시간은 상기 클록 신호원과 상기 모듈 사이의 상기 감지된 전송 라인의 길이와 반비례 관계에 있는 로컬 클록 신호 생성 장치.

### 청구항 13.

클록 신호원에 의해 발생된 글로벌 클록 신호에 응답하여 동기식 논리 시스템의 복수의 모듈에서 실질적으로 서로 위상 동기하는 개별적인 로컬 클록 신호를 생성하는 장치로서,

상기 클록 신호원로부터 각 모듈로 상기 글로벌 클록 신호를 전송하는 제1 전송 라인,

상기 클록 신호원로부터 각 모듈로 상기 글로벌 클록 신호를 전송하는 제2 전송 라인, 그리고

상기 각 모듈과 연관되어 있으며, 상기 클록 신호원과 이것과 연관된 모듈 사이의 상기 제1 및 제2 전송 라인에 대한 길이를 감지하고 상기 제1 및 제2 전송 라인 중 하나의 라인을 통해 상기 연관된 모듈에 도달하는 상기 글로벌 클록 신호를 상기 감지된 전송 라인의 길이와 상관관계가 있는지연 시간만큼 지연하는 디스큐 수단,

을 포함하며

상기 제1 및 제2 전송 라인은 상기 클록 신호원과 각 모듈 사이에 실질적으로 동일한 길이를 갖지만, 실질적으로 서로 상이한 글로벌 클록 신호 전파 속도를 갖는

로컬 클록 신호 생성 장치.

### 청구항 14.

제13항에 있어서,

상기 지연 시간은 상기 감지된 전송 라인의 길이와 반비례 관계에 있는 로컬 클록 신호 생성 장치.

### 청구항 15.

제13항에 있어서,

상기 디스큐 수단은 상기 제1 전송 라인을 통해 상기 연관 모듈에 도달하는 상기 글로벌 클록 신호의 위상을 상기 제2 전송 라인을 통해 상기 연관된 모듈에 도달하는 상기 글로벌 클록 신호의 위상과 비교하는 수단을 포함하는 로컬 클록 신호 생성 장치.

## 청구항 16.

제13항에 있어서,

상기 디스큐 수단은

상기 제1 전송 라인을 통해 상기 연관 모듈에 도달하는 상기 글로벌 클록 신호의 위상을 상기 제2 전송 라인을 통해 상기 연관된 각 모듈에 도달하는 상기 글로벌 클록 신호의 위상과 비교하여, 상기 길이를 나타내는 크기를 가지는 제1 신호를 생성하는 수단,

상기 제1 신호에 응답하여 상기 제1 신호의 크기와 소정의 상관관계가 있는 크기의 제2 신호를 생성하는 수단, 그리고

상기 글로벌 클록 신호가 상기 제1 및 제2 전송 라인 중 하나를 통해 상기 모듈에 도달한 후 상기 글로벌 클록 신호를 상기 지연 시간만큼 지연하여 상기 로컬 클록 신호를 생성하는 지연 수단

을 포함하고,

상기 지연 시간은 상기 지연 수단의 입력으로서 인가되는 상기 제2 신호의 크기에 따라 제어되는

로컬 클록 신호 생성 장치.

## 청구항 17.

제16항에 있어서,

상기 제2 신호를 생성하는 상기 수단은

개별적인 어드레스에 데이터 값은 기억하는 주소 지정 가능 메모리,

상기 주소 지정 가능 메모리가 상기 기억된 데이터 값 중 주소 지정된 하나의 값을 판독하도록 상기 제1 신호의 크기에 따라 상기 주소 지정 가능 메모리를 주소 지정하는 수단, 그리고

상기 판독된 데이터 값에 따른 크기를 갖는 상기 제2 신호를 생성하는 수단

을 포함하는 로컬 클록 신호 생성 장치.

## 청구항 18.

클록 신호원에 의해 생성된 글로벌 클록 신호에 응답하여 동기식 논리 시스템의 복수의 모듈 각각에서 실질적으로 서로 위상 동기하는 개별적인 로컬 클록 신호를 생성하는 장치로서,

상기 클록 신호원로부터 각 모듈로 상기 글로벌 클록 신호를 전송하는 제1 전송 라인,

각 모듈과 연관되어 있으며, 상기 제1 전송 라인을 통해 각 모듈에 도달하는 상기 글로벌 클록 신호를 조정 가능한 제1 지연 시간만큼 지연시켜, 상기 연관된 모듈에 대한 제1 로컬 클록 신호를 생성하는 제1 지연 수단,

각 모듈과 연관되어 있으며, 상기 제2 전송 라인을 통해 각 모듈에 도달하는 상기 글로벌 클록 신호를 조정 가능한 제2 지연 시간만큼 지연시켜, 상기 모듈에서 제2 로컬 클록 신호를 생성하는 제2 지연 수단, 그리고

각 모듈과 연관되어 있으며, 상기 모듈과 연관된 상기 제1 및 제2 지연 수단의 상기 제1 및 제2 지연 시간을 조정하여 상기 연관 모듈의 상기 제1 및 제2 로컬 클록 신호 사이에 소정의 위상 관계를 제공하는 수단

을 포함하는 로컬 클록 신호 생성 장치.

### 청구항 19.

제18항에 있어서,

상기 제1 전송 라인에 대한 글로벌 클록 신호의 전파속도는 상기 제2 전송 라인에 대한 글로벌 클록 신호의 전파속도의 M배이며, 상기 M은 실질적으로 1로부터 변화하는 숫자인 로컬 클록 신호 생성 장치.

### 청구항 20.

제19항에 있어서,

상기 제2 지연 수단에 대한 상기 제2 지연 시간 대 상기 제1 지연 수단에 대한 상기 제1 지연 시간의 비율은 실질적으로 M과 동일한 로컬 클록 신호 생성 장치.

### 청구항 21.

글로벌 클록 신호를 생성하는 클록 신호원을 포함하는 호스트 유닛 및 상기 호스트 유닛으로부터 멀리 떨어져 위치하는 복수의 논리 모듈을 포함하는 동기식 논리 시스템에 대하여, 각 모듈에서 개별적인 로컬 클록 신호를 생성하고 상기 호스트 유닛과 각 모듈 사이에서 데이터 신호를 전송하는 방법으로서,

전송 라인을 통해 상기 클록 신호원으로부터 각 모듈로 상기 글로벌 클록 신호를 전송하는 단계,

상기 클록 신호원과 각 모듈 사이의 상기 전송 라인에 대한 길이를 감지하는 단계,

상기 전송 라인을 통해 각 모듈에 도달하는 상기 글로벌 클록 신호를 상기 클록 신호원과 상기 모듈 사이의 상기 감지된 전송 라인의 길이와 상관관계가 있는 지연 시간만큼 지연시켜, 상기 모듈에서 로컬 클록 신호를 생성하는 단계,

데이터 라인을 통해 상기 호스트 유닛과 상기 각 모듈 사이에서 데이터 신호를 전송하는 단계, 그리고

상기 각 모듈에서 상기 데이터 신호를 상기 클록 신호원과 상기 모듈 사이의 상기 감지된 전송 라인의 길이와 상관관계가 있는 상기 지연 시간만큼 지연시키는 단계

를 포함하는 데이터 신호 전송 방법.

### 청구항 22.

동기식 논리 시스템의 호스트 유닛 내에 위치하는 클록 신호원에 의해 발생된 글로벌 클록 신호에 응답하여 동기식 논리 시스템의 복수의 모듈에서 개별적인 로컬 클록 신호를 생성하고, 상기 호스트 유닛과 상기 각 모듈 사이에서 데이터 신호를 전송하는 장치로서,

상기 클록 신호원로부터 각 모듈로 상기 글로벌 클록 신호를 전송하는 제1 전송 라인;

상기 클록 신호원로부터 각 모듈로 상기 글로벌 클록 신호를 전송하는 제2 전송 라인;

상기 호스트 유닛과 상기 각 모듈 사이에서 상기 데이터 신호를 전송하는 데이터 라인, 그리고

각 모듈과 연관되어 있으며, 상기 제1 및 제2 전송 라인을 통해 상기 연관된 모듈에 도달하는 상기 글로벌 클록 신호의 위상차를 감지하며, 상기 제1 및 제2 전송 라인 중 하나를 통해 상기 연관 모듈에 도달하는 상기 글로벌 클록 신호를 상기 감지된 위상차와 상관관계가 있는 지연 시간만큼 지연시켜 상기 연관된 모듈에서 로컬 클록 신호를 생성하고, 상기 데이터 신호를 상기 지연 시간과 동일하게 지연하여 상기 데이터 라인과 상기 연관된 모듈 사이에서 전송하는 디스큐 수단

을 포함하는 데이터 신호 전송 장치.

### 청구항 23.

제22항에 있어서,

상기 제1 및 제2 전송 라인 그리고 상기 데이터 라인은 상기 클록 신호원과 각 모듈 사이에서 실질적으로 동등한 길이를 가지며, 상기 제1 전송 라인에 대한 글로벌 클록 신호의 전파속도는 상기 제2 전송 라인에 대한 글로벌 클록 신호의 전파속도의 M배이며, 상기 M은 1 이외의 다른 숫자이며, 상기 데이터 라인의 데이터 신호 전파 속도는 상기 제1 전송 라인의 전파속도와 실질적으로 동등한 데이터 신호 전송 장치.

### 청구항 24.

클록 신호원에 의해 생성된 글로벌 클록 신호에 응답하여 동기식 논리 시스템의 복수의 모듈 각각에서 개별적인 로컬 클록 신호를 생성하고, 상기 호스트 유닛과 상기 각 모듈 사이에서 데이터 신호를 전송하는 장치로서,

상기 클록 신호원로부터 각 모듈로 상기 글로벌 클록 신호를 전송하는 제1 전송 라인,

상기 클록 신호원로부터 각 모듈로 상기 글로벌 클록 신호를 전송하는 제2 전송 라인,

각 모듈과 연관되어 있으며, 상기 제1 전송 라인을 통해 각 모듈에 도달하는 상기 글로벌 클록 신호를 조정 가능한 제1 지연 시간만큼 지연시켜, 상기 연관된 모듈에 대한 제1 로컬 클록 신호를 생성하는 제1 지연 수단,

각 모듈과 연관되어 있으며, 상기 제2 전송 라인을 통해 각 모듈에 도달하는 상기 글로벌 클록 신호를 조정 가능한 제2 지연 시간만큼 지연시켜, 상기 모듈에서 제2 로컬 클록 신호를 생성하는 제2 지연 수단,

각 모듈과 연관되어 있으며, 상기 데이터 라인과 상기 연관 모듈 사이에서 상기 데이터 신호를 상기 조정 가능한 제1 지연 시간만큼 지연하는 제3 지연 수단, 그리고

각 모듈과 연관되어 있으며, 상기 제1 및 제2 지연 시간을 조정하여 상기 연관 모듈의 상기 제1 및 제2 로컬 클록 신호 사이에 소정의 위상 관계를 제공하는 수단

을 포함하며,

상기 제1 전송 라인에 대한 글로벌 클록 신호의 전파속도는 상기 제2 전송 라인에 대한 글로벌 클록 신호의 전파속도의 M배이며, 상기 M은 실질적으로 1로부터 변화하는 숫자이며, 상기 데이터 라인에 대한 데이터 신호의 전파 속도는 상기 제1 전송 라인의 전파속도와 실질적으로 동일하며, 각 모듈의 상기 제2 지연 시간 대 상기 제1 지연 시간의 비는 실질적으로 M과 동일한

데이터 신호 전송 장치.

### 청구항 25.

제1 전송 라인의 신호 스케우(signal skew)의 크기를 나타내는 출력 신호를 생성하는 장치로서,

전기 펄스를 발생하는 펄스 발생기,

위상 검출기, 그리고

상기 펄스 발생기 회로로부터 상기 위상 검출기로 상기 펄스를 개별적으로 전송하는 제2 전송 라인

을 포함하며,

상기 제1 전송 라인은 상기 펄스 발생기로부터 상기 위상 검출기로 상기 펄스를 전송하고,

상기 제1 및 제2 전송 라인은 상기 펄스 발생기와 상기 위상 검출기 사이에서 유사한 길이를 갖지만 서로 상이한 전파속도를 가지며,

상기 위상 검출기는 상기 제1 및 제2 전송 라인을 통해 도달하는 상기 펄스의 도달 시간의 위상차를 나타내는 출력 신호를 생성하며,

상기 위상차는 상기 펄스 발생기와 상기 위상 검출기 사이의 상기 제1 전송 라인의 신호 스케일 크기에 비례하는 출력 신호 생성장치.

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10