(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6914010号

(P6914010)

(45) 発行日 令和3年8月4日(2021.8.4)

(24) 登録日 令和3年7月15日(2021.7.15)

(51) Int.Cl.

H01S 5/0683 (2006.01)

H03K 17/78 (2006.01)

F 1

H01S 5/0683

H03K 17/78

E

請求項の数 14 (全 17 頁)

(21) 出願番号 特願2016-104553 (P2016-104553)

(22) 出願日 平成28年5月25日 (2016.5.25)

(65) 公開番号 特開2017-212334 (P2017-212334A)

(43) 公開日 平成29年11月30日 (2017.11.30)

審査請求日 令和1年5月9日 (2019.5.9)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 110003281

特許業務法人大塚国際特許事務所

(72) 発明者 遠藤 航

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

(72) 発明者 塙道 寛貴

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 高椋 健司

最終頁に続く

(54) 【発明の名称】駆動装置

## (57) 【特許請求の範囲】

## 【請求項 1】

発光素子と、前記発光素子が発生した光を受光する受光素子と、前記発光素子が発生するべき光の光量を示す目標値と前記受光素子によって検出された光の光量とを比較し比較結果に応じた制御信号を発生する比較回路と、変更可能なゲインを有し前記制御信号に前記ゲインを乗じた信号である駆動信号を前記発光素子に供給する駆動回路とを備える駆動装置であって、

前記駆動回路は、前記ゲインを前記目標値に応じて変更するためのゲイン変更スイッチを有し、前記目標値が基準値より小さい場合の前記ゲインは、前記目標値が前記基準値より大きい場合の前記ゲインより小さい、

ことを特徴とする駆動装置。

## 【請求項 2】

前記駆動回路は、前記制御信号に応じて、容量が接続されたノードの充放電を行う充放電回路と、前記ノードの電圧に応じた電流を前記発光素子に供給する電流供給回路とを含み、

前記ゲイン変更スイッチは、前記目標値に応じて前記駆動回路の前記ゲインが変更されるように前記電流供給回路のゲインを変更するためのスイッチを含む、

ことを特徴とする請求項 1 に記載の駆動装置。

## 【請求項 3】

前記電流供給回路は、前記ノードの電圧を電流に変換する電圧電流変換回路と、前記電

圧電流変換回路から出力される電流に応じた電流を出力する電流電流変換回路とを含み、前記スイッチは、前記電流電流変換回路の出力する電流の、前記電圧電流変換回路から出力される電流に対するゲインを変更する、ことを特徴とする請求項2に記載の駆動装置。

**【請求項4】**

前記電流電流変換回路は、前記電圧電流変換回路から出力される電流を受けて第1のミラー電流を発生する第1のカレントミラーレ路と、前記第1のミラー電流を受けて第2のミラー電流を発生する第2のカレントミラーレ路とを含み、

前記スイッチは、前記第2のカレントミラーレ路に含まれる複数のトランジスタのうち、前記第2のミラー電流を発生させるために動作させるトランジスタの個数を決定する、ことを特徴とする請求項3に記載の駆動装置。 10

**【請求項5】**

前記スイッチは、前記複数のトランジスタのゲートを互いに接続する、ことを特徴とする請求項4に記載の駆動装置。

**【請求項6】**

前記電流電流変換回路は、前記電圧電流変換回路から出力される電流のミラー電流を発生する複数のミラーレ路を含み、

前記スイッチは、前記複数のミラーレ路のうち前記駆動信号の発生のために動作させるミラーレ路の個数を決定する、ことを特徴とする請求項3乃至5のいずれか1項に記載の駆動装置。 20

**【請求項7】**

前記目標値が基準値より小さい場合の前記電流供給回路の前記ゲインは、前記目標値が前記基準値より大きい場合の前記電流供給回路の前記ゲインより小さい、

ことを特徴とする請求項2乃至6のいずれか1項に記載の駆動装置。

**【請求項8】**

前記駆動回路は、前記制御信号に応じて、容量が接続されたノードの充放電を行う充放電回路と、前記ノードの電圧に応じた電流を発生する電圧電流変換回路と、前記電圧電流変換回路が発生した電流の大きさをシフトさせたシフト電流を発生するシフト回路と、を含み、前記ゲイン変更スイッチは、前記シフト回路の活性化および非活性化を制御するためのスイッチを含み、 30

前記シフト回路が活性化されている場合は、前記電圧電流変換回路が発生した電流の大きさを前記シフト回路がシフトさせたシフト電流に応じた駆動電流が前記発光素子に供給され、前記シフト回路が非活性化されている場合は、前記電圧電流変換回路が発生した電流に応じた駆動電流が前記発光素子に供給される、

ことを特徴とする請求項1に記載の駆動装置。

**【請求項9】**

前記シフト電流は、前記電圧電流変換回路が発生した電流より小さい、ことを特徴とする請求項8に記載の駆動装置。

**【請求項10】**

前記目標値が前記基準値より小さい場合に前記シフト回路が活性化され、前記目標値が前記基準値より大きい場合に前記シフト回路が非活性化される、 40

ことを特徴とする請求項8又は9に記載の駆動装置。

**【請求項11】**

前記シフト回路は、前記電圧電流変換回路の出力ノードと基準電位との間の経路に配置された電流源を含み、前記スイッチは、前記経路に設けられている、

ことを特徴とする請求項8乃至10のいずれか1項に記載の駆動装置。

**【請求項12】**

前記駆動回路は、前記制御信号に応じて、容量が接続されたノードの充放電を行う充放電回路と、前記ノードの電圧に応じた電流を前記発光素子に供給する電流供給回路とを含み、 50

前記ゲイン変更スイッチは、前記目標値に応じて前記ゲインが変更されるように前記充放電回路が前記容量を充放電させる電流の大きさを変更するためのスイッチを含む、ことを特徴とする請求項1に記載の駆動装置。

#### 【請求項13】

前記充放電回路は、サンプルモードでは前記容量の充放電を行い、ホールドモードでは前記容量の充放電を行わない、

ことを特徴とする請求項2乃至12のいずれか1項に記載の駆動装置。

#### 【請求項14】

前記目標値、および、前記目標値に応じて前記ゲインを変更するように前記ゲイン変更スイッチを制御するためのゲイン制御信号を発生する制御部を更に備える、

10

ことを特徴とする請求項1乃至13のいずれか1項に記載の駆動装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、発光素子を駆動する駆動装置に関する。

##### 【背景技術】

##### 【0002】

半導体レーザ等の発光素子を駆動する駆動装置がプリンタなどにおいて使用されている。特許文献1には、一定の光出力を得るためのAPC(Automatic Power Control)機能を有する半導体レーザ駆動装置が記載されている。特許文献1に記載された半導体レーザ駆動装置は、フォトダイオード、演算増幅器、アナログスイッチ、ホールドコンデンサ、電圧-電流変換回路、スイッチ回路、可変抵抗および基準電位発生回路を有する。フォトダイオードは、レーザダイオードの発光量に比例した電流を可変抵抗に流す。その電流は、可変抵抗によって電圧に変換され、演算増幅器の反転入力端に供給される。演算増幅器の非反転入力端には、基準電位発生回路から基準電位が供給される。演算増幅器の出力端は、アナログスイッチの一端に接続され、アナログスイッチの他端は、電圧-電流変換回路に接続されている。アナログスイッチの他端と接地電位との間にはホールドコンデンサが接続されている。電圧-電流変換回路は、入力電圧をレーザダイオードの駆動電流に変換する。スイッチ回路は、DATA信号に応じてスイッチングを行う。半導体レーザ駆動装置は、上記の構成により、フォトダイオードを使って検出された電圧が基準電位に等しくなるように、レーザダイオードに供給する電流をフィードバック制御する。

20

##### 【先行技術文献】

##### 【特許文献】

##### 【0003】

##### 【特許文献1】特開2004-165444号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0004】

APC機能を実現するためのフィードバックループの動作は、光量の制御範囲を大きくしようとすると、該フィードバックループの構成要素の応答特性が悪い領域において不安定性になりうる。例えば、発光素子に発生させるべき光の光量が特定の領域においては、電圧-電流変換回路等の構成要素の応答特性が低く、フィードバックループの遅延が増大しうる。この遅延が大きくなり過ぎると、発振が起こりうる。

30

##### 【0005】

本発明は、上記の課題認識を契機としてなされたものであり、駆動装置の安定性を向上させるために有利な技術を提供することを目的とする。

##### 【課題を解決するための手段】

##### 【0006】

本発明の1つの側面は、駆動装置に係り、前記駆動装置は、発光素子と、前記発光素子

40

50

が発生した光を受光する受光素子と、前記発光素子が発生するべき光の光量を示す目標値と前記受光素子によって検出された光の光量とを比較し比較結果に応じた制御信号を発生する比較回路と、変更可能なゲインを有し前記制御信号に前記ゲインを乗じた信号である駆動信号を前記発光素子に供給する駆動回路とを備える駆動装置であって、前記駆動回路は、前記ゲインを前記目標値に応じて変更するためのゲイン変更スイッチを有し、前記目標値が基準値より小さい場合の前記ゲインは、前記目標値が前記基準値より大きい場合の前記ゲインより小さい。

**【発明の効果】**

**【0007】**

本発明によれば、駆動装置の安定性を向上させるために有利な技術が提供される。 10

**【図面の簡単な説明】**

**【0008】**

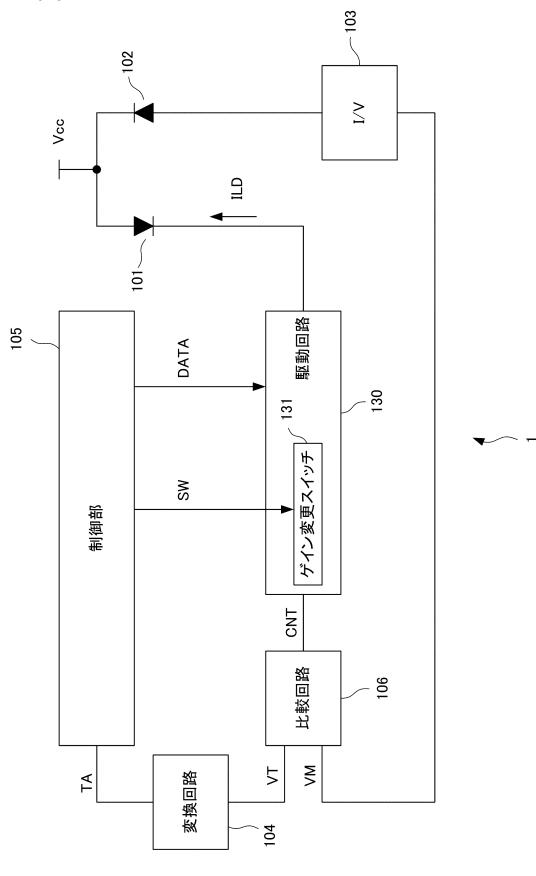

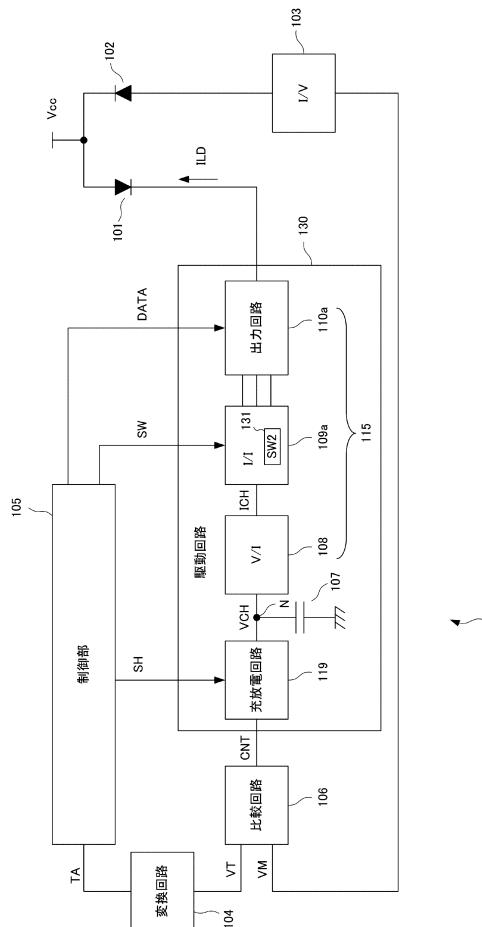

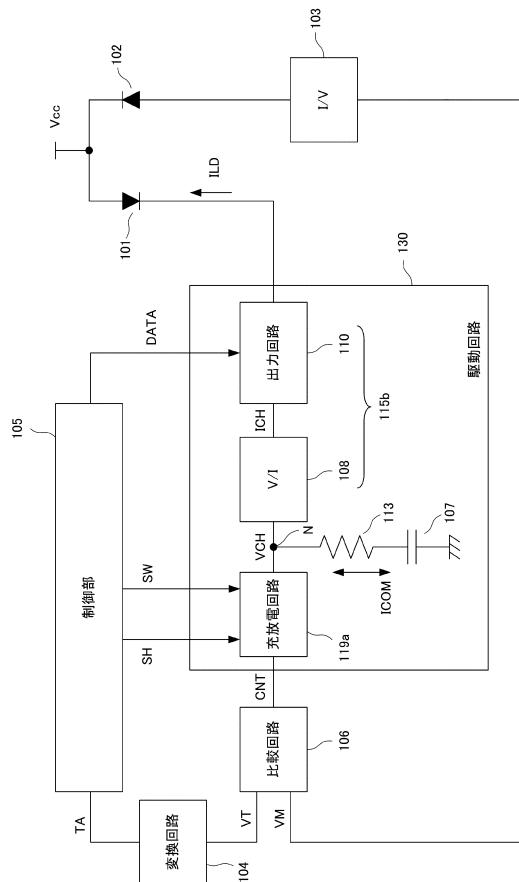

**【図1】**本発明の第1実施形態の駆動装置の構成を示す図。

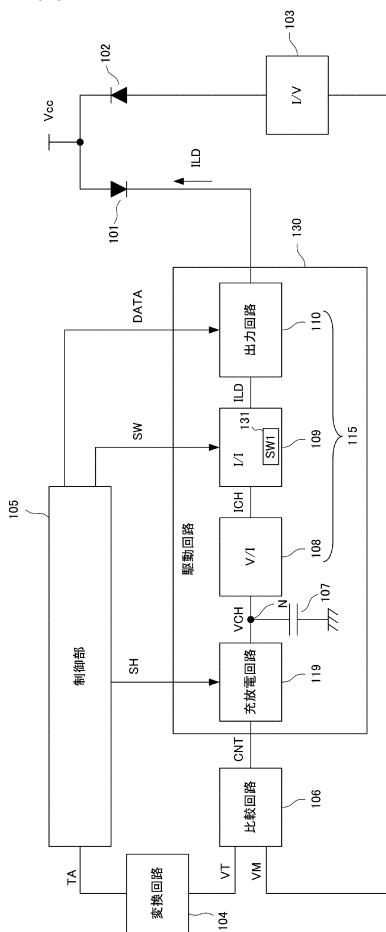

**【図2】**本発明の第2実施形態の駆動装置の構成を示す図。

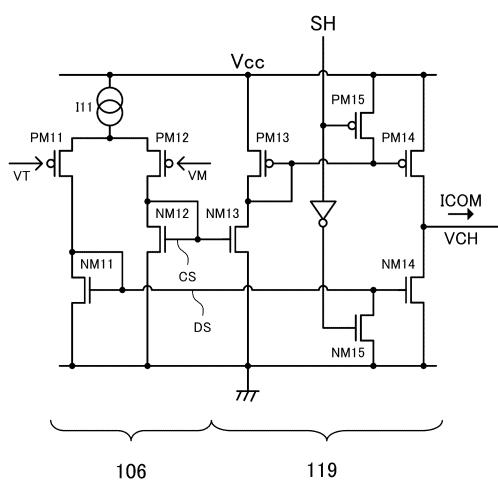

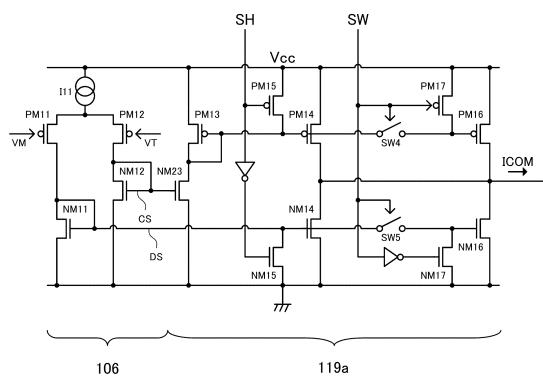

**【図3】**本発明の第2実施形態の駆動装置における比較回路および充放電回路の構成例を示す図。

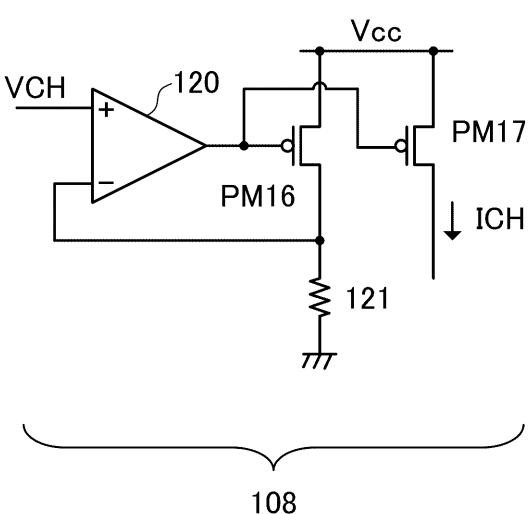

**【図4】**電圧電流変換回路の構成例を示す図。

**【図5】**電流電圧変換回路の構成例を示す図。

**【図6】**電圧電流変換回路の入出力特性を例示する図。

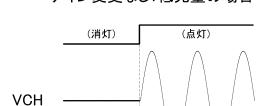

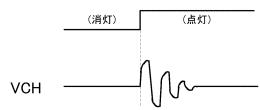

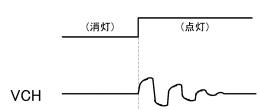

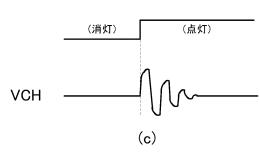

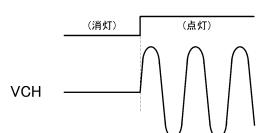

**【図7】**本発明の第2実施形態の駆動装置における電圧VCHの波形を例示する図。 20

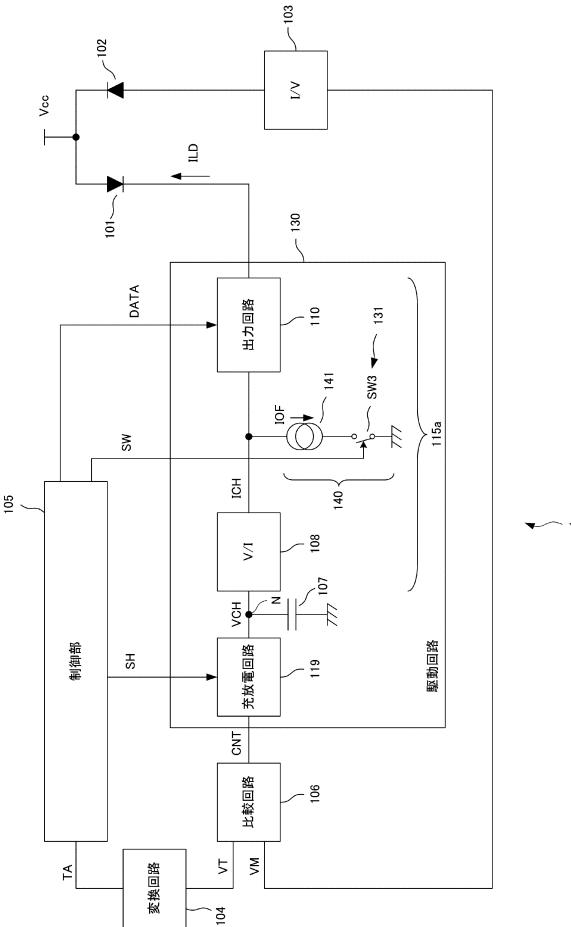

**【図8】**本発明の第3実施形態の駆動装置の構成を示す図。

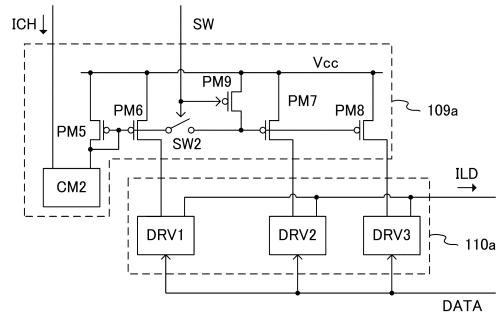

**【図9】**本発明の第3実施形態における電流電圧変換回路および出力回路の構成例を示す図。

**【図10】**本発明の第4実施形態の駆動装置の構成を示す図。

**【図11】**本発明の第5実施形態の駆動装置の構成を示す図。

**【図12】**本発明の第5実施形態の駆動装置における比較回路および充放電回路の構成例を示す図。

**【図13】**本発明の第5実施形態の駆動装置における電圧VCHの波形を例示する図。

**【発明を実施するための形態】**

**【0009】**

30

以下、添付図面を参照しながら本発明のその例示的な実施形態を通して説明する。

**【0010】**

図1には、本発明の第1実施形態の駆動装置1の構成が示されている。駆動装置1は、発光素子101、受光素子102、比較回路106および駆動回路130を備えうる。比較回路106、駆動回路130、発光素子101、受光素子102および電流電圧変換回路103によってフィードバックループが構成されている。フィードバックループにより、光量自動調整(APC)機能が提供される。フィードバックループは、APCループとも呼ばれうる。具体的には、フィードバックループにより、発光素子101が発生する光の光量が目標値(目標光量)に一致するように発光素子101が駆動されうる。発光素子101は、例えば、発光ダイオード(LED)またはレーザダイオードでありうる。駆動装置1は、例えば、レーザービームプリンタまたはLEDプリンタのようなプリンタに組み込まれうる。受光素子102は、例えば、フォトダイオード等の光電変換素子でありうる。発光素子101のアノード端子、および、受光素子102のカソード端子は、電源Vccに接続されうる。 40

**【0011】**

比較回路106は、発光素子101が発生するべき光の強度を示す目標値と受光素子102によって検出された光の光量とを比較し比較結果に応じた制御信号CNTを発生する。一例において、比較回路106は、発光素子101が発生するべき光の光量を示す目標値としての目標電圧VTと受光素子102によって検出された光の光量を示すモニタ電圧VMとを比較し比較結果に応じて制御信号CNTを発生する。制御信号CNTは、例えば

50

、モニタ電圧  $V_M$  が目標電圧  $V_T$  より小さい場合には、発光素子 101 を駆動電流の増加を要求し、モニタ電圧  $V_M$  が目標電圧  $V_T$  より大きい場合には、発光素子 101 を駆動電流の減少を要求する信号でありうる。

#### 【0012】

図 1 に示された例では、駆動装置 1 は、第 1 尺度において規定される第 1 目標値  $T_A$  を第 2 尺度において規定される第 2 目標値としての目標電圧  $V_T$  に変換する変換回路 104 を備え、目標電圧  $V_T$  が比較回路 106 に供給される。第 1 目標値  $T_A$  は、発光素子 101 が発生するべき光の光量を示す値であればよく、それを示す尺度は、無次元数であってもよいし、光束、光度、輝度等の物理量であってもよい。図 1 に示された例では、発光素子 101 から受光した光の光量に応じた電流が受光素子 102 によって生成され、その電流が電流電圧変換回路 103 によって電圧に変換されることによってモニタ電圧  $V_M$  が生成される。

10

#### 【0013】

駆動回路 130 は、比較回路 106 から供給される制御信号  $CNT$  に応じた駆動信号としての駆動電流  $ILD$  を発光素子 101 に供給する。ここで、駆動電流  $ILD$  は、制御信号  $CNT$  を入力とし駆動電流  $ILD$  を出力とする駆動回路 130 のゲインを制御信号  $CNT$  に乗じた信号として理解することができる。駆動回路 130 は、目標値  $T_A$  に応じて駆動回路 130 のゲインを変更するためのゲイン変更スイッチ 131 を有する。駆動回路 130 のゲインは、駆動回路 130 の出力である駆動電流  $ILD$  と駆動回路 130 の入力である制御信号  $CNT$  との比 ( $ILD / CNT$ ) として定義されうる。例えば、駆動電流  $ILD$  のラプラス変換を  $ILD(s)$  とし、制御信号  $CNT$  のラプラス変換を  $CNT(s)$  とすると、駆動回路 130 のゲイン  $G(s)$  は、 $ILD(s) / CNT(s)$  で与えられうる。あるいは、駆動電流を時間  $t$  の関数である  $ILD(t)$ 、制御信号を時間  $t$  の関数である  $CNT(t)$  とすると、駆動回路 130 のゲイン  $G(t)$  は、 $ILD(t) / CNT(t)$  で与えられうる。ゲイン変更スイッチ 131 は、目標値  $T_A$  に応じて駆動回路 130 の回路構成を変更するためのスイッチとして理解されうる。

20

#### 【0014】

目標値  $T_A$  に応じてゲイン変更スイッチ 131 によって駆動回路 130 のゲインを変更する構成は、駆動装置 1 のフィードバックループの安定性を向上させるために有利である。

30

#### 【0015】

駆動装置 1 は、目標値  $T_A$ 、および、目標値  $T_A$  に応じて駆動回路 130 のゲインを変更するようにゲイン変更スイッチ 131 を制御するためのゲイン制御信号  $SW$  を発生する制御部 105 を備えうる。制御部 105 は、発光素子 101 に対する電流  $ILD$  の供給および非供給（つまり、点灯および消灯）を制御するための制御データ  $DATA$  を駆動回路 130 に供給するように構成されうる。制御データ  $DATA$  は、例えば、パルス幅変調されたデータでありうる。駆動回路 130 は、制御データ  $DATA$  に応じて発光素子 101 に対する電流  $ILD$  の供給および非供給を制御するように構成されうる。例えば、駆動回路 130 は、制御データ  $DATA$  が第 1 の値を有するときは発光素子 101 に電流  $ILD$  を供給し、制御データ  $DATA$  が第 2 の値を有するときは発光素子 101 に電流  $ILD$  を供給しないように構成されうる。

40

#### 【0016】

以下、第 1 実施形態を具体化した第 2 ~ 第 5 実施形態を説明する。図 2 には、本発明の第 2 実施形態の駆動装置 1 の構成が示されている。第 2 実施形態として言及されない事項は、第 1 実施形態に従いうる。第 2 実施形態では、駆動回路 130 は、制御信号  $CNT$  に応じて、容量（キャパシタ）107 が接続されたノード N の充放電を行う充放電回路 119 と、ノード N の電圧  $VCH$  に応じた電流  $ILD$  を発光素子 101 に供給する電流供給回路 115 とを含む。容量 107 は、ノード N と基準電位（例えば、接地電位）との間に配置されうる。充放電回路 119 は、比較回路 106 から供給される制御信号  $CNT$  に基づいて容量 107 の充放電を行う。充放電回路 119 は、サンプルホールド機能を有するよ

50

うに構成されうる。この場合、充放電回路 119 は、サンプルモードでは、容量 107 の充放電を行い、ホールドモードでは、容量 107 の充放電を行わず、サンプルモードからホールドモードに切り替わる直前における容量 107 の電圧 VCH をホールドする。

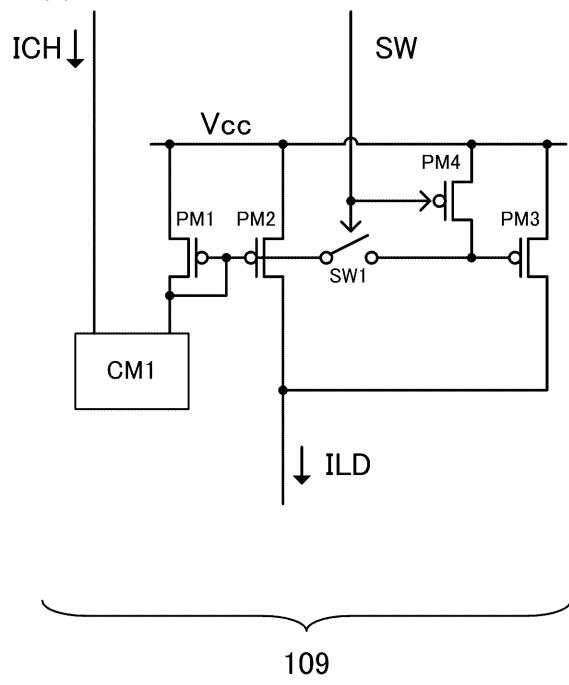

#### 【0017】

電流供給回路 115 は、電圧電流変換回路 108 と、電流電流変換回路 109 と、出力回路 110 とを含みうる。電圧電流変換回路 108 は、ノード N の電圧 VCH を電流 ICH に変換する。電流電流変換回路 109 は、電流 ICH を増幅して、電流 ICH に応じた電流 ILD を出力する。出力回路 110 は、制御データ DATA に応じて発光素子 101 に対する電流 ILD の供給および非供給を制御する。ゲイン変更スイッチ 131 は、目標値 TA に応じて駆動回路 130 のゲインが変更されるように電流供給回路 115 のゲイン (より詳しくは、電流電流変換回路 109 のゲイン) を変更するためのスイッチ SW1 を含みうる。スイッチ SW1 を有する電流電流変換回路 109 の構成については後述する。目標値 TA が基準値より小さい場合の電流供給回路 115 のゲイン (より詳しくは電流電流変換回路 109 のゲイン) は、目標値 TA が当該基準値より大きい場合の電流供給回路 115 のゲイン (より詳しくは電流電流変換回路 109 のゲイン) より小さくされうる。

#### 【0018】

図 3 には、比較回路 106 および充放電回路 119 の具体的な構成例が示されている。比較回路 106 は、電流源 I11、PMOS トランジスタ PM11、PM12、NMOS トランジスタ NM11、NM12 を含みうる。充放電回路 119 は、PMOS トランジスタ PM13、PM14、PM15、NMOS トランジスタ NM13、NM14、NM15 を含みうる。

#### 【0019】

電流源 I11 の一端は電源 Vcc 接続され、電流源 I11 他端は PMOS トランジスタ PM11、PM12 のソースに接続されている。PMOS トランジスタ PM11 のゲートには、目標電圧 (目標値) VT が供給され、PMOS トランジスタ PM12 のゲートには、モニタ電圧 VM が供給される。PMOS トランジスタ PM11 のドレインは、NMOS トランジスタ NM11 のゲートおよびドレインに接続されている。PMOS トランジスタ PM12 のドレインは、NMOS トランジスタ NM12、NM13 のゲートおよび NMOS トランジスタ NM12 のドレインに接続されている。NMOS トランジスタ NM11 のゲートおよびドレインは、NMOS トランジスタ NM14 のゲートおよび NM15 のドレインに接続されている。NMOS トランジスタ NM13 のドレインは、PMOS トランジスタ PM13、PM14 のゲートおよび PMOS トランジスタ PM13、PM15 のドレインに接続されている。PMOS トランジスタ PM14 のドレインは、NMOS トランジスタ NM14 のドレインに接続され、容量 107 に対して電流 ICOM を出力する。また、PMOS トランジスタ PM15 のゲートにはサンプルホールド信号 SH が供給され、NMOS トランジスタ NM15 のゲートにはサンプルホールド信号 SH の反転信号が供給される。

#### 【0020】

図 3 に示された例において、NMOS トランジスタ NM11 のゲートおよびドレインに現れる信号 DS、および、NMOS トランジスタ NM12 のゲートおよびドレインに現れる信号 CS は、前述の制御信号 CNT の例である。

#### 【0021】

容量 107 に流れる電流 ICOM は、PMOS トランジスタ PM14 が出力する電流の値から NMOS トランジスタ NM14 が出力する電流の値を差し引いた値を有する電流である。モニタ電圧 VM が目標電圧 VT よりも低い場合、電流源 I11 の電流は、PMOS トランジスタ PM12 に支配的に流れ、そのミラー電流が PMOS トランジスタ PM14 から容量 107 に流れる。これにより、ノード N の電圧 VCH が上昇するよう、容量 107 に対する充電動作がなされる。一方で、モニタ電圧 VM が目標電圧 VT よりも高い場合は、電流源 I11 の電流は PMOS トランジスタ PM11 に支配的に流れ、そのミラー電流が容量 107 から NMOS トランジスタ NM14 に流れる。これにより、ノード N の

電圧 V C H が下降するように、容量 107 からの放電動作がなされる。

#### 【0022】

また、サンプルホールド信号 S H が “H” の場合（サンプルモード）は、PMOSトランジスタ PM15 および NMOSトランジスタ NM15 はオフとなるため、上記のような充放電動作が行われる。一方で、サンプルホールド信号が “L” の場合（ホールドモード）、PMOSトランジスタ PM15 および NMOSトランジスタ NM15 はオンとなる。これにより PMOSトランジスタ PM14 および NMOSトランジスタ NM14 がオフされるので、サンプルホールド信号が “H” から “L” に変化する直前における容量 107 の電圧 V C H がホールドされる。

#### 【0023】

図 4 には、電圧電流変換回路 108 の具体的な構成例が示されている。電圧電流変換回路 108 は、オペアンプ（演算増幅器）120、PMOSトランジスタ PM16、PM17 および抵抗 121 で構成されうる。オペアンプ 120 の正極入力端子には電圧 V C H が供給され、負極入力端子は PMOSトランジスタ PM16 のドレインおよび抵抗 121 の一端に接続されている。オペアンプ 120 の出力は PMOSトランジスタ PM16、PM17 のゲートに接続されている。抵抗 121 の他端は接地電位に接続され、PMOSトランジスタ PM16、PM17 のソースは電源 V c c に接続されている。オペアンプ 120 の正極入力端子および負極入力端子が仮想短絡されていることから、抵抗 121 に電圧 V C H が印加されて電流に変換され、そのミラー電流である電流 I C H が PMOSトランジスタ PM17 により電流電流変換回路 109 へ出力される。

#### 【0024】

図 5 には、電流電流変換回路 109 の具体的な構成例が示されている。電流電流変換回路 109 は、カレントミラー回路 CM1、PMOSトランジスタ PM1、PM2、PM3、PM4 およびスイッチ SW1 を含みうる。スイッチ SW1 は、ゲイン変更スイッチ 131 を構成する。カレントミラー回路 CM1 には、電圧電流変換回路 108 から電流 I C H が供給される。カレントミラー回路 CM1 は、電流 I C H のミラー電流を PMOSトランジスタ PM1 に出力する。カレントミラー回路 CM1 の出力は、PMOSトランジスタ PM1 のゲートおよびドレイン、PMOSトランジスタ PM2 のゲートおよびスイッチ SW1 の一端に接続されている。スイッチ SW1 の他端には、PMOSトランジスタ PM3 のゲートおよび PM4 のドレインが接続され、PMOSトランジスタ PM1 ~ PM4 のソースは電源 V c c に接続されている。ゲイン制御信号 SW は、スイッチ SW1 および PMOSトランジスタ PM4 のゲートに供給される。

#### 【0025】

PMOSトランジスタ PM1 ~ PM3 は、カレントミラー回路を構成する。ゲイン制御信号 SW が “H”（ハイレベル）である場合、スイッチ SW1 がオンし、PMOSトランジスタ PM1 を流れる電流が PMOSトランジスタ PM2、PM3 によってミラーされる。そして、PMOSトランジスタ PM2、PM3 を流れるミラー電流の合計が電流 I LD として出力回路 110 に供給される。一方で、ゲイン制御 SW が “L”（ローレベル）である場合、スイッチ SW1 がオフし、PMOSトランジスタ PM4 がオンする。PMOSトランジスタ PM4 がオンすることによって PMOSトランジスタ PM3 のゲート電圧が V c c 電圧になり、これによって PMOSトランジスタ PM3 がオフする。この場合、PMOSトランジスタ PM1 を流れる電流が PMOSトランジスタ PM2 のみによってミラーされ、PMOSトランジスタ PM2 を流れるミラー電流が電流 I LD として出力回路 110 に供給される。したがって、ゲイン制御信号 SW によって制御されるスイッチ SW1 により、電流 I C H のミラー電流を発生する複数のトランジスタ（ミラー回路）のうち駆動電流 I LD の生成のために動作させるトランジスタの個数が決定される。ここで、駆動電流 I LD の生成のために動作させるトランジスタの個数によって駆動電流 I LD の大きさが定まる。つまり、ゲイン制御信号 SW に応じて駆動電流 I LD の生成のために動作させるトランジスタの個数を決定することによって、ゲイン制御信号 SW に応じて電圧電流変換回路 108 のゲインを変更することができる。ここで、電圧電流変換回路 108 のゲ

10

20

30

40

50

インを変更することによって電流供給回路 115、更には駆動回路 130 のゲインを変更することができる。ゲイン制御信号 SW によって電流供給回路 115、更には駆動回路 130 のゲインを変更することができる。

#### 【0026】

発光素子 101 が発生する光の光量の範囲を拡大するために（つまり、電流 ILD の範囲を拡大するために）、電圧電流変換回路 108 を構成するオペアンプ 120 として、広いダイナミックレンジを有するオペアンプが使用される。しかしながら、オペアンプ 120 に供給される電圧 VCH が小さくなるとオペアンプ 120 の応答性が低下し、電圧電流変換回路 108 における遅延量が大きくなってしまう。したがって、電圧 VCH が小さくなるとフィードバックループ全体の遅延量が大きくなり、フィードバックループが不安定になり、場合によっては発振現象が起こりうる。10

#### 【0027】

そこで、第 2 実施形態では、制御部 105 が出力するゲイン制御信号 SW に応じて、電流電流変換回路 109 のゲインが変更される。電流 ILD は、式（1）で与えられる。ここで、R は、電圧電流変換回路 108 の抵抗 121 の抵抗値であり、Gain は、電流電流変換回路 109 のゲインである。式（1）より明らかなように、Gain を小さくすることにより、電圧 VCH を小さくすることなく、電流 ILD を小さくすることができる。したがって、発光素子 101 が発生する光の光量範囲を拡大しながらフィードバックループの安定性を向上させることができる。20

#### 【0028】

$$ILD = Gain \times VCH / R \quad \dots \quad (1)$$

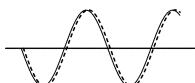

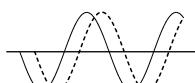

図 6 (a)、(b) には、電圧電流変換回路 108 の入出力特性が例示されている。実線は、電圧電流変換回路 108 に対する入力を示し、点線は、電圧電流変換回路 108 からの出力を示している。図 6 (a) は、高光量の場合（目標値 TA が基準値より大きい場合）の入出力特性を示し、図 6 (b) は、低光量の場合（目標値 TA が基準値より小さい場合）の入出力特性を示している。高光量の場合は、制御部 105 は、ゲイン制御信号 SW を "H" とし、低光量の場合は、制御部 105 は、ゲイン制御信号 SW を "L" とする。これにより、低光量の場合の電圧電流変換回路 108 のゲイン Gain は、高光量の場合の電圧電流変換回路 108 のゲイン Gain より小さくされる。図 6 (a)、(b) に例示されるように、目標値 TA に応じて駆動回路 130 のゲインが変更されるように電流供給回路 115 のゲインを変更するにより、光量の目標値 TA が小さくなることによる電圧電流変換回路 108 の遅延を低減することができる。30

#### 【0029】

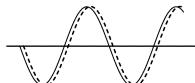

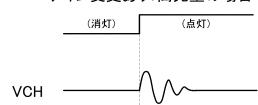

図 6 (c)、(d) には、比較例として、ゲイン制御信号 SW を "H" に固定した場合の電圧電流変換回路 108 の入出力特性が例示されている。実線は、電圧電流変換回路 108 に対する入力を示し、点線は、電圧電流変換回路 108 からの出力を示している。図 6 (c) は、高光量の場合（目標値 TA が基準値より大きい場合）の入出力特性を示し、図 6 (d) は、低光量の場合（目標値 TA が基準値より小さい場合）の入出力特性を示している。図 6 (d) に例示されているように、光量の目標値 TA が小さくなると、電圧電流変換回路 108 の応答性が低下し、遅延量が大きくなる。これは、フィードバックループの発振を引き起こしうる。図 7 (a) ~ (d) には、それぞれ図 6 (a) ~ (d) に対応する電圧 VCH の波形が例示されている。ゲイン制御信号 SW が "H" に固定された場合の電圧電流変換回路 108 では、低光量の場合に、電圧 VCH が発振し、フィードバックループが発振している。40

#### 【0030】

式（1）より明らかなように、ゲイン制御信号 SW に応じて抵抗値 R を変更する構成においても、電流電流変換回路 109 のゲインを変更する構成と同様の効果が得られる。例えば、抵抗 121 として、互いに抵抗値が異なる 2 つの抵抗を並列に設けておき、ゲイン制御信号 SW に応じて、使用する抵抗を選択する構成を採用することができる。ここで、電流電流変換回路 109 のゲインを変更することも、電圧電流変換回路 108 の抵抗 12 50

1の抵抗値を変更することも、電流供給回路115のゲインを変更するものである。

#### 【0031】

第2実施形態では、アノード駆動タイプの発光素子の駆動を例示しているが、カソード駆動タイプの発光素子を採用してもよい。これは、以下の実施形態についても同様である。

#### 【0032】

図8には、本発明の第3実施形態の駆動装置1の構成が示されている。第3実施形態として言及されない事項は、第1又は第2実施形態に従う。第3実施形態の駆動回路130は、制御信号CNTに応じて、容量107が接続されたノードNの充放電を行う充放電回路119と、ノードNの電圧VCHに応じた電流ILDを発光素子101に供給する電流供給回路115とを含む。電流供給回路115は、電圧電流変換回路108と、電流電流変換回路109aと、出力回路110aとを含みうる。電圧電流変換回路108は、ノードNの電圧VCHを電流ICHに変換する。電流電流変換回路109aは、電流ICHを増幅する。出力回路110aは、制御データDATAに応じて発光素子101に対する電流ILDの供給および非供給を制御する。ゲイン変更スイッチ131は、目標値TAに応じて駆動回路130のゲインが変更されるように電流供給回路115のゲイン(より詳しくは、電流電流変換回路109aおよび出力回路110aで構成される回路のゲイン)を変更するためのスイッチSW2を含みうる。

#### 【0033】

図9には、第3実施形態における電流電流変換回路109aおよび出力回路110aの構成例が示されている。電流電流変換回路109aは、カレントミラー回路CM2、PMOSトランジスタPM5～PM9およびスイッチSW2を含みうる。カレントミラー回路CM2には、電圧電流変換回路108から電流ICHが供給される。カレントミラー回路CM2は、電流ICHのミラー電流をPMOSトランジスタPM5に出力する。カレントミラー回路CM2の出力は、PMOSトランジスタPM5のゲートおよびドレイン、PMOSトランジスタPM6のゲートおよびスイッチSW2の一端に接続されている。スイッチSW2の他端には、PMOSトランジスタPM7、PM8のゲートおよびPMOSトランジスタPM9のドレインが接続されている。PMOSトランジスタPM5～PM9のソースは、電源VCCに接続されている。ゲイン制御SWは、スイッチSW2およびPMOSトランジスタPM9のゲートに供給される。

#### 【0034】

ゲイン制御信号SWが“H”である場合、スイッチSW2がオンし、PMOSトランジスタPM5を流れる電流がPMOSトランジスタPM6～PM8によってミラーされる。そして、PMOSトランジスタPM6～PM8を流れるミラー電流が出力回路110aに供給される。一方で、ゲイン制御信号SWが“L”である場合、スイッチSW2がオフし、PMOSトランジスタPM9がオンする。PMOSトランジスタPM9がオンすることによってPMOSトランジスタPM7、PM8のゲート電圧がVCC電圧になり、これによってPMOSトランジスタPM7、PM8がオフする。この場合、PMOSトランジスタPM5を流れる電流がPMOSトランジスタPM6のみによってミラーされ、PMOSトランジスタPM6を流れるミラー電流が出力回路110aに供給される。

#### 【0035】

出力回路110aは、ドライバDRV1～DRV3を含む。ドライバDRV1には、PMOSトランジスタPM6のドレインが接続され、ドライバDRV2にはPMOSトランジスタPM7のドレインが接続され、ドライバDRV3にはPMOSトランジスタPM8のドレインが接続されている。ドライバDRV1～DRV3の出力は、電流ILDの出力端子に接続されている。ゲイン制御信号SWが“H”である場合、ドライバDRV1～DRV3のそれぞれは、PMOSトランジスタPM6～PM8がそれぞれ出力する電流に所定の倍率を乗じた値を有する電流を制御データDATAに従って出力する。そして、ドライバDRV1～DRV3がそれぞれ出力する電流を合計した電流ILDが発光素子101に供給される。一方で、ゲイン制御信号SWが“L”である場合、PMOSトランジスタ

10

20

30

40

50

P M 7、P M 8はオフとなり、ドライバDRV1は、PMOSトランジスタP M 6が出力する電流に所定の倍率を乗じた値の電流をDATA信号に従って出力する。そして、ドライバDRV1が出力する電流が電流ILDとして発光素子101に供給される。ゲインの変更による電流ILDの波形の変化を小さくするためには、ドライバDRV1～DRV3は、互いに同一の回路構成を有することが望ましい。

#### 【0036】

一般的に、出力回路110aが電流ILDを広範囲にわたって高速に制御することを可能にするためには、図9に例示されているように、複数のドライバが設けられることが多い。その理由として、大きな電流ILDを流すためにサイズの大きなMOSトランジスタを用いると、ゲート容量が大きくなり、応答性が悪くなるためである。電流電流変換回路109aおよび出力回路110aの組み合わせは、出力回路110aが電流ILDを広範囲にわたって高速に制御するために有利である。10

#### 【0037】

図10には、本発明の第4実施形態の駆動装置1の構成が示されている。第4実施形態として言及されない事項は、第1乃至第3実施形態に従う。第4実施形態の駆動回路130は、制御信号CNTに応じて、容量107が接続されたノードNの充放電を行う充放電回路119と、ノードNの電圧VCHに応じた電流ILDを発光素子101に供給する電流供給回路115aとを含む。電流供給回路115aは、電圧電流変換回路108と、シフト回路140と、出力回路110とを含みうる。電圧電流変換回路108は、ノードNの電圧VCHを電流ICHに変換する。シフト回路140は、電圧電流変換回路108が発生した電流ICHの大きさをシフトさせたシフト電流が出力回路110に供給されるように、電流ICHの大きさをシフトさせる。出力回路110は、制御データDATAに応じて発光素子101に対する電流ILDの供給および非供給を制御する。シフト回路140は、電圧電流変換回路108の出力ノードと基準電位(例えば、接地電位)との間の経路に配置された電流源141を含む。ゲイン変更スイッチ131は、電圧電流変換回路108の出力ノードと基準電位との間の経路に、電流源141と直列に接続されたスイッチSW3を含みうる。20

#### 【0038】

第4実施形態では、目標値TAが基準値より小さい場合にゲイン制御信号SWが“H”にされ、目標値TAが当該基準値より大きい場合にゲイン制御信号SWが“L”にされる。ゲイン制御信号SWが“L”である場合、スイッチSW3がオフすることによってシフト回路140が非活性化され、電圧電流変換回路108が発生した電流ICHがそのまま出力回路110に供給される。この場合、出力回路110は、電流ICHに所定の倍率を乗じた値を有する電流ILDを制御データDATAに応じて発光素子101に供給する。一方で、ゲイン制御信号SWが“H”である場合、スイッチSW3がオンすることによってシフト回路140が活性化される。これにより、電圧電流変換回路108が発生した電流ICHからオフセット電流IOFが差し引かれたシフト電流(ICH - IOF)が出力回路110に供給される。この場合、出力回路110は、シフト電流(ICH - IOF)に所定の倍率を乗じた値の電流ILDを制御データDATAに応じて発光素子101に供給する。この例では、シフト電流(ICH - IOF)は、電流ICHより小さい電流である。3040

#### 【0039】

よって、目標値TAが基準値より小さい場合(ゲイン制御信号SWが“H”)は、電流IDLは、(2)式で示され、目標値TAが当該基準値より大きい場合(ゲイン制御信号SWが“L”)は、電流IDLは、(3)式で示される。

#### 【0040】

$$IDL = (ICH - IOF) \times = (VCH / R - IOF) \times \dots \quad (2)$$

$$IDL = ICH \times = (VCH / R) \times \dots \quad (3)$$

第4実施形態においても、ゲイン制御信号SWにより電流供給回路115のゲインを変更することができる。具体的には、目標値TAが基準値より小さい場合の電流供給回路150

15のゲインを目標値TAが当該基準値より大きい場合の電流供給回路115aのゲインより小さくすることができる。

#### 【0041】

図11には、本発明の第5実施形態の駆動装置1の構成が示されている。第5実施形態として言及されない事項は、第1乃至第4実施形態に従う。第5実施形態では、駆動回路130は、制御信号CNTに応じて、容量107が接続されたノードNの充放電を行う充放電回路119aと、ノードNの電圧VCHに応じた電流ILDを発光素子101に供給する電流供給回路115bとを含む。電流供給回路115bは、電圧電流変換回路108と、出力回路110とを含みうる。電圧電流変換回路108は、ノードNの電圧VCHを電流ICHに変換する。出力回路110は、電流ICHに所定の倍率を乗じた値を有する電流ILDを制御データDATAに応じて発光素子101に供給する。

10

#### 【0042】

図12には、比較回路106および充放電回路119aの構成例が示されている。比較回路106は、第2実施形態と同様であり、電流源I11、PMOSトランジスタPM11、PM12、NMOSトランジスタNM11、NM12を含みうる。充放電回路119は、第2実施形態と同様の構成要素として、PMOSトランジスタPM13、PM14、PM15、NMOSトランジスタNM13、NM14、NM15を含みうる。充放電回路119は、更に、PMOSトランジスタPM16、PM17、NMOSトランジスタNM16、NM17を含みうる。また、充放電回路119は、ゲイン変更スイッチ131として、充放電回路119が容量107を充放電させる電流ICOMの大きさ(充放電回路119のゲイン)を変更するスイッチSW4、SW5を含む。

20

#### 【0043】

スイッチSW4の一端は、PMOSトランジスタPM14のゲートに接続され、スイッチSW5の一端は、NMOSトランジスタNM14のゲートに接続されている。更に、スイッチSW4の他端は、PMOSトランジスタPM16のゲートおよびPMOSトランジスタPM17のドレインに接続されている。スイッチSW5の他端は、NMOSトランジスタNM16のゲートおよびNMOSトランジスタNM17のドレインに接続されている。PMOSトランジスタPM13～PM17のソースは電源Vccに接続され、NMOSトランジスタNM11～NM17のソースは接地電位に接続されている。PMOSトランジスタPM14、PM16およびNMOSトランジスタNM14、NM16のドレインは共通に接続され、電流ICOMを出力する。PMOSトランジスタPM17のゲートおよびスイッチSW4、SW5には、ゲイン制御信号SWが供給され、NMOSトランジスタNM17のゲートには、ゲイン制御信号SWの反転信号が供給される。

30

#### 【0044】

第2実施形態で説明したように、サンプルホールド信号SHが“H”である場合にサンプルモードとなり、目標電圧VTとモニタ電圧VMとの比較結果に応じた電流ICOMが充放電回路119aから出力される。ここで、ゲイン制御信号SWが“H”である場合、スイッチSW4、SW5がオンするので、PMOSトランジスタPM14、PM16、NMOSトランジスタNM14、NM16が動作状態となって電流ICOMが出力され、容量107の充放電がなされる。一方で、ゲイン制御信号が“L”的場合、スイッチSW4、SW5がオフし、PMOSトランジスタPM14、NMOSトランジスタNM14のみが動作状態となって電流ICOMが出力され、容量107の充放電がなされる。つまり、ゲイン制御信号SWによってサンプルモードにおける充放電回路119のゲインが決定される。これにより、目標値TAの全域において、フィードバックループを安定化することができる。ここで、上記のように、充電電流および放電電流の双方を調整可能な構成とするのがより好ましいが、いずれか一方のみの電流量を調整可能な構成でもよく、この場合には、フィードバックループを安定化する効果を得ることができる。

40

#### 【0045】

サンプルホールド信号SHが“L”である場合は、PMOSトランジスタPM14、PM16およびNMOSトランジスタNM14、NM16がオフし、充放電回路119aは

50

、ホールドモードとなって充放電を停止する。よって、サンプルホールド信号が”H”から”L”に変化する直前における容量107の電圧VCHがホールドされる。

#### 【0046】

一般的に、容量107の容量値は大きいので、容量107は、駆動装置1が作りこまれたICの外に配置されうる。充放電回路119aの出力端子と容量107との間には、IC内部の配線抵抗や実装基板上の抵抗、容量107の等価直列抵抗(ESR)などの寄生のCH抵抗113が存在し、これによる影響が無視できなくなる。つまり、APC動作時に電流ICOMが充電から放電、放電から充電に切り替る際、電圧VCHに電圧変動が生じることによりフィードバックループ(APCループ)の安定性が害されうる。寄生のCH抵抗113の値によっては、フィードバックループの安定性が低下するので、充放電回路119aの出力端子と容量107との間には、フィードバックループの安定性向上させる抵抗値を有する抵抗が意図的に挿入されうる。10

#### 【0047】

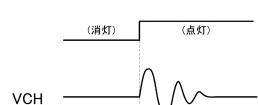

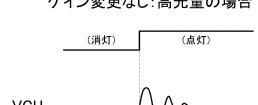

図13(a)、(b)には、第5実施形態の駆動装置1における電圧VCHの波形が例示されている。図13(a)は、高光量の場合(目標値TAが基準値より大きい場合)の電圧VCHの波形を示し、図13(b)は、低光量の場合(目標値TAが基準値より小さい場合)の電圧VCHの波形を示している。図13(a)、(b)に例示されるように、充放電回路119aのゲインを目標値TAに応じて調整することによって電圧VCHを安定させ、フィードバックループを安定させることができる。図13(c)、(d)には、比較例として、ゲイン制御信号SWを”H”に固定した場合の電圧VCHの波形が例示されている。ゲイン制御信号SWが”H”に固定された場合、低光量の場合に、電圧VCHが発振し、フィードバックループが発振している。20

#### 【符号の説明】

#### 【0048】

101：発光素子、102：受光素子、TA：目標値、VT：目標電圧(目標値)、VM：モニタ電圧、ゲイン制御信号SW、CNT：制御信号

【図1】

【図2】

【図3】

【図4】

【 四 5 】

109

【図6】

#### ゲイン変更あり: 高光量の場合

(a)

#### ゲイン変更あり: 低光量の場合

(b)

#### ゲイン変更なし: 高光量の場合

(c)

### ゲイン変更なし: 低光量の場合

(d)

【 四 7 】

ゲイン変更あり:高光量の場合

(a)

#### ゲイン変更あり: 低光量の場合

(b)

#### ゲイン変更なし・高光量の場合

(c)

### ゲイン変更なし: 低光量の場合

【 四 8 】

【図 9】

【図 10】

【図 11】

【図 12】

## 【図 1 3】

ゲイン変更あり:高光量の場合

(a)

ゲイン変更あり:低光量の場合

(b)

ゲイン変更なし:高光量の場合

(c)

ゲイン変更なし:低光量の場合

(d)

---

フロントページの続き

(56)参考文献 特開平01-182819(JP,A)

特開2012-128909(JP,A)

特開2004-014754(JP,A)

特開2007-287274(JP,A)

特開2005-183657(JP,A)

特開2012-009123(JP,A)

特開2000-216487(JP,A)

特開2003-008139(JP,A)

米国特許出願公開第2005/0073268(US,A1)

(58)調査した分野(Int.Cl., DB名)

H01S 5/00 - 5/50

G11B 7/12 - 7/22

H03K 7/74 - 17/98