(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3896204号

(P3896204)

(45) 発行日 平成19年3月22日(2007.3.22)

(24) 登録日 平成18年12月22日(2006.12.22)

(51) Int.C1.

F 1

G O 6 F 12/00 (2006.01)

G O 6 F 12/00 5 9 5

請求項の数 5 (全 15 頁)

(21) 出願番号 特願平9-338054

(22) 出願日 平成9年11月21日(1997.11.21)

(65) 公開番号 特開平10-198597

(43) 公開日 平成10年7月31日(1998.7.31)

審査請求日 平成16年11月17日(2004.11.17)

(31) 優先権主張番号 08/757,606

(32) 優先日 平成8年11月29日(1996.11.29)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 78735 テキサス州

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100083574

弁理士 池内 義明

(74) 代理人 100116322

弁理士 桑垣 衛

(72) 発明者 デイビッド・シリル・バビン

アメリカ合衆国テキサス州78748、オ

ースチン、キングフィッシャー・クリーク

・ドライブ 509

最終頁に続く

(54) 【発明の名称】直列的に提供されるデータストリームのためのレジスタ格納先を選択する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

直列的に提供されるデータストリームのためのレジスタ格納先を選択する方法であって、

第1の組のレジスタ(54, 55, 56)を提供する段階であって、該第1の組のレジスタはNを有限の正の整数としてビット長さNの第1のレジスタおよびMを有限の正の整数でありかつNがMに等しくないものとしてビット長さMの第2のレジスタを備えるもの、

第2の組のレジスタ(51, 52, 53)を提供する段階であって、前記第2の組のレジスタはビット長さNの第1のレジスタおよびビット長さMの第2のレジスタを備えるもの、

イネーブル信号(14)を提供する段階であって、該イネーブル信号は選択的にパルス化されて前記第1の組のレジスタ(57)または前記第2の組のレジスタ(59)のいずれか1つを選択可能であり、前記第1の組のレジスタまたは前記第2の組のレジスタの内の選択されたいずれか1つは選択された組のレジスタであり、そして

直列的に提供されるデータストリーム(16)を提供する段階であって、前記直列的に提供されるデータストリーム内のビットの数が検出され、前記直列的に提供されるデータストリーム内のビットの数は前記直列的に提供されるデータストリームを含めるために書き込まれるべき前記選択された組のレジスタ内の選択されたレジスタを識別する(72)もの、

を具備することを特徴とする直列的に提供されるデータストリームのためのレジスタ格納先を選択する方法。

**【請求項 2】**

前記直列的に提供されるデータストリームを提供する段階は、

巡回シフトレジスタ(20)を使用することにより前記直列的に提供されるデータストリーム内のビットの数を監視し、それによって前記直列的に提供されるデータストリームの入力シフトの後に、前記巡回シフトレジスタにおけるイネーブルされたビットの数が前記選択された組のレジスタ内の選択されたレジスタを決定する段階、

を具備することを特徴とする請求項1に記載の方法。

**【請求項 3】**

直列的に提供されるデータストリームのためのレジスタ格納先を選択する方法であって

、複数のレジスタ(57, 59)を提供する段階、

イネーブル信号(14)を提供する段階であって、該イネーブル信号はある期間の間選択的にパルス化されて前記直列的に提供されるデータストリームが提供される前に2進シーケンスを提供するもの、

前記2進シーケンス(72)を処理して前記複数のレジスタの内の選択されたレジスタ(51~56)を決定する段階、

前記直列的に提供されるデータストリーム(16)を提供する段階であって、前記イネーブル信号は前記直列的に提供されるデータストリームの受信を可能にするもの、そして

前記直列的に提供されるデータストリームを前記2進シーケンスによって選択される選択されたレジスタへと格納する段階、

を具備することを特徴とする直列的に提供されるデータストリームのためのレジスタ格納先を選択する方法。

**【請求項 4】**

クロック信号(12)を受けるための第1の入力、イネーブル信号(14)を受けるための第2の入力、およびレジスタ選択信号を提供するための出力を有する監視回路(72)、

前記イネーブル信号(14)を受信しかつ少なくとも1つのバンク選択信号を提供するためのバンク選択回路(74)であって、該バンク選択回路は複数のビット格納要素を備えるもの、

1つまたはそれ以上のバンク(57, 59)へと構成された複数のレジスタ(51~56)であって、該複数のレジスタにおける各レジスタは前記イネーブル信号、前記バンク選択回路からの前記少なくとも1つのバンク選択信号、および前記監視回路からの前記レジスタ選択信号の組合せによって選択されるもの、

データの直列ストリームを受けるためのデータ入力(16)に結合されたデータ直列シフトレジスタ(40)、そして

前記少なくとも1つのバンク選択信号および前記レジスタ選択信号を受けかつ少なくとも1つの格納制御信号を前記複数のレジスタに提供するための回路(36~38)であって、前記複数のレジスタの内の1つのレジスタが前記データ直列シフトレジスタによって提供されるデータを格納するために選択されるもの、

を具備することを特徴とする回路。

**【請求項 5】**

イネーブル信号(14)を受けるためのレジスタ選択回路(72)であって、前記イネーブル信号はデータ入力(16)によってシリアルデータが提供される前に論理“1”および論理“0”的時間シリアルな2進シーケンスを提供し、前記論理“1”および論理“0”的時間シリアルな2進シーケンスは前記レジスタ選択回路によって処理されて複数のレジスタ格納イネーブル信号(30の出力)を提供するもの、

データ入力に結合されて論理“1”および論理“0”的前記時間シリアルな2進シーケンスの後に生じる前記イネーブル信号のアクティブ状態に応じて前記データ入力からデー

10

20

30

40

50

タの直列ストリームを受けるためのシリアルシフトレジスタ(40)、そして

前記シリアルシフトレジスタからデータを受けるよう結合されかつ前記複数のレジスタ格納イネーブル信号を受けるよう結合された複数のレジスタ(51～56)であって、前記複数のレジスタ格納イネーブル信号の1つは論理“1”および論理“0”的時間シリアルな2進シーケンスに応答して前記レジスタ選択回路からイネーブルされそれによって前記シリアルシフトレジスタに格納されたデータの直列ストリームが前記複数のレジスタの内の選択されたレジスタに提供されるもの、

を具備することを特徴とする回路。

【発明の詳細な説明】

【0001】

10

【発明の属する技術分野】

本発明は一般的には集積回路に関し、かつより特定的には時間およびスペース効率のよい方法でレジスタにシリアルまたは直列データを提供することに関する。

【0002】

【従来の技術】

集積回路のピンのカウント数、パッケージングの寸法、およびコストを低減するためには、シリアルインタフェースを使用して集積回路の間でデータを提供することが好都合である。しかしながら、シリアルインタフェースは通常アドレスおよびデータ2進値の双方が集積回路内におけるかなりの量の性能を消費する時間順次的な方法で提供されることを必要とする。従って、シリアル周辺インタフェースにおけるアドレスビットの必要性を除去してシリアル通信期間のより大きな部分がオーバヘッドよりはデータを通信するのに消費されるようにするステップが取られてきた。

20

【0003】

シリアル周辺インタフェース(SPI)においてアドレスビットを避けるための1つの従来の技術はバビン(Babin)による米国特許第5,146,577号に教示されている。この特許においては、データはシリアルデータ入力ポートによって提供される。シリアルデータ入力ポートによって提供されるこのシリアルデータはデータシリアル・シフトレジスタに直列的にシフトされる。データが該データシリアル・シフトレジスタにシフトされている間に、シリアルデータ全体を前記データシリアル・シフトレジスタにシフト入力するのに必要なクロックの数がリップルカウンタによってカウントされる。リップルカウンタの最終的なカウント値はもしシステム内のすべてのレジスタが異なるサイズであればどのレジスタが直列的にシフトされたデータを受けるかを決定するために使用することができる。例えば、もしリップルカウンタがデータシフトシーケンスの終りに8の値を含んでおれば、かつシステム内に8ビットのレジスタのみが配置されておれば、前記シリアルシフトレジスタに提供されるデータは該8ビットの内部レジスタに提供されるべきことが容易に決定できる。もしリップルカウンタが16ビットを検出しつつシステムにおける唯一のレジスタが16ビット幅であれば、データは正確に導くことができ、それによってデータビットのカウントがアドレスビットの必要性を置き換えることになる。各レジスタは独自の数のデータビット容量を有するから、データビットをカウントすることはシリアル通信される付加的なアドレスビットの必要性なしに書き込まれるべきレジスタを決定する。

30

【0004】

【発明が解決しようとする課題】

しかしながら、システムがより複雑になりかつ、例えば、2つの8ビットのレジスタ(または任意の同じサイズの任意の2つのレジスタ)を含む場合には、このクロックカウント方法は問題のあるものとなる。もし2つまたはそれ以上のレジスタあるいは2つまたはそれ以上の組のレジスタが同じサイズを有していれば、システムにシフト入力されるデータビットの数が知られていても、複数の同じサイズのレジスタのどれがデータを受けるべきかに関して依然として明確ではない。例えば、シリアルデータ入力と通信することを必要とする4つの8ビットレジスタがある場合、リップルカウンタが8のカウントを生成する

40

50

という事実は前記 4 つの 8 ビットレジスタのどれがデータを受けるべきかを決定するための適切な指示ではない。

#### 【0005】

さらに、シリアルデータ通信の前に、途中で、あるいは後にシリアルアドレス通信を使用することは有利ではない。数多くのシリアル通信インターフェース（S C I）およびシリアル周辺インターフェース（S P I）はビットがシリアル入力に固定された量またはパケットのビットで提供されることを要求する。例えば、あるインターフェースは機能するために 8 ビットのセグメントがデータ入力へとユニット全体で直列的に提供されることを要求するかもしれない。これは  $2^8$  のレジスタをアドレスするために 8 ビットが必要とされる限り問題はない。しかしながら、もし 2 つのレジスタのみがシステム内にあり、従ってたった 1 ビットのアドレシングのみが必要であれば、依然としてアドレシングのために 8 ビットが提供されなければならず、それによって大部分のデータプロセッサの並列の高周波動作と比較した場合すでに低速であるインターフェースにおいて 8 ビットの内の 7 ビットを浪費する。従って、通信ごとにセットされたパケットまたはセットされた数のビットを必要とするデータライン上のシリアルアドレスデコードを避けることが性能を改善することになる。10

#### 【0006】

従って、より多くのレジスタが単一の集積回路に集積され、これらのレジスタが同じサイズでありますかつシリアルデータインターフェースへのジョイントまたは合同のアクセスを必要とするため、どのレジスタがシリアルなシフトデータを受けるかを決定する新しい方法が開発される必要がある。この新しい方法は付加的なアドレスピンなしに機能しあつシリアル周辺インターフェース（S P I）の制約および改善された性能の要求のためにデータターミナル上にアドレス値を直列的に提供する必要性を避けることが必要である。20

#### 【0007】

##### 【課題を解決するための手段】

一般に、本発明は集積回路内で適切なレジスタにデータビットを含むデータのシリアルストリーム（serial stream）を提供する装置および方法に関するものである。ここに教示されるシリアルデータインターフェースはシリアル情報をシリアルデータが提供される前または後にデータ入力に添って通信される直列的に送信されるアドレスビットの必要性なしに適切な格納レジスタに通信することができる。集積回路内の格納レジスタへの直列的に提供されるデータの適切なルーティングは好みの 2 レベルデコード手順を使用して達成される。この 2 レベルデコード方法においては、第 1 のレベルのデコードがイネーブル信号またはチップ選択ライン上に直列的に提供される 2 進シーケンスを監視することにより達成される。2 レベルまたは 2 次元デコードの第 2 のレベルはシフトレジスタにシフト入力されるデータエレメントの数をカウントすることにより達成される。シリアルシフトレジスタヘデータを入力するために使用されるクロック（またはデータビット）をカウントする間にイネーブル信号におけるデコードを行うことにより、複数のレジスタの内の 1 つが入力データストリームを受けるために独自的に選択できる。前記複数のレジスタにおけるこれらのレジスタは同じサイズのものであってもよくかつそれでもデコードのチップ選択 / イネーブル信号レベルを介して適切なデータ格納のために選択される。さらに、チップ選択またはイネーブル信号における符号化（encoding）は特定のサイズ（前記発明の背景で説明した 8 ビットのような）に限定されず、従ってオーバヘッドが低減される。3040

#### 【0008】

さらに他の形式では、どのレジスタがシリアルシフトデータを格納するかの決定はシリアル周辺インターフェース（S P I）のイネーブルラインまたはチップ選択ライン上に直列的に提供される 2 進シーケンスを監視するのみで行うことができる。この実施形態では、データ入力に提供されるデータは時間効率のよい方法で選択されたレジスタに導かれ、この場合レジスタは到来ストリームのクロックカウントまたはデータビットのカウントを行わなくても同じデータサイズのものとすることができます。いくつかの実施形態では、イネー

ブル端子またはチップ選択端子のデコード信号はその部分に到来する実際のデータストリームと並列に生じることができ、それによって転送において観察される唯一の時間はそれがシリアルデータを転送するために必要とする時間となる。この構成においては、フルデータの捕捉を可能にするためにエッジが検出される場合に第1の装置によってイネーブルがローにラッチされる必要があり、一方他の装置はデスティネイションを捕捉しかつデコードするために変化するイネーブルを監視し続けるために使用される。

#### 【0009】

##### 【発明の実施の形態】

説明の簡略化および明瞭化のために、図面に示された各要素は必ずしも比例した大きさで描かれていなかることが理解されるであろう。例えば、いくつかの要素の寸法は明瞭化のために他の要素に対して誇張されている。さらに、適切と考えられる場合には、各図面の間で参照数字が反復されて対応するまたは同様の要素を示している。10

#### 【0010】

本発明は図1～図9を参照することによりさらに明瞭に理解することができる。

#### 【0011】

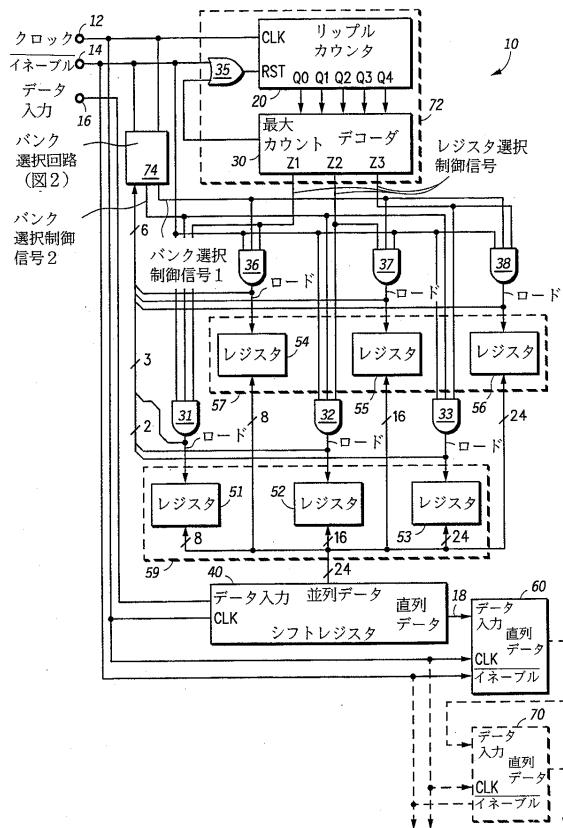

図1は、ブロック図形式で、集積回路（I C）内で直列的にシフトされるデータを導くために使用できる電気的システムを示している。図1は、上部左手コーナに示されるように、3つの主要な入力信号を備えている。システムクロックは図1におけるクロック端子12を介して提供され、これはシステム内のラッチ、レジスタ、フリップフロップ、その他を制御するためにクロック信号を提供する。データの直列ストリームはデータ入力端子16を介して時間的に直列様式で提供することができる。データイネーブル信号はイネーブル端子14を介して提供され、従って集積回路はいつ有効なデータが端子16上に提供されているかを通知されるようになる。20

#### 【0012】

クロック端子12およびイネーブル端子14はバンク選択回路74に結合されている。さらに、クロック12およびイネーブル端子14は図1のモニタまたは監視回路72に結合されている。バンク選択回路74および監視回路72は2レベルまたは2次元デコードを提供し、これはデータ入力端子16によって提供される直列シフトデータがどこに最終的に格納されるべきかを決定する（始めに、I Cへと到来するすべてのデータは直列的に図1のレジスタ40に格納され、次に引き続く動作によって該データを並列インターフェースを介して前記2レベルデコードによって決定される最終のデスティネイションレジスタ51～56に格納されることになる）。バンク選択回路74はイネーブル端子14によって直列的に提供される2進シーケンスを検出しかつデコードする。短い2進シーケンスの1つの例は図7のシーケンス200によって示されている。イネーブル端子14によって提供されるこの2進シーケンスはバンク選択回路74によって検出されかつ処理されて図1に示される1つまたはそれ以上のバンク選択制御信号を提供する。イネーブル端子14上に2進シーケンスを提供した後、シリアルデータがデータ入力端子16を介して提供される。このデータはイネーブル14が活性化されあるいはアクティベイトされている限りクロック信号12を使用してレジスタ40へとクロック入力される（イネーブルは図1および図7においてはアクティブローであるが、他の実施形態ではアクティブハイとすることもできる）。データが端子16を通して転送されているこの活性化された状態の間に、レジスタ40へとデータを転送するために使用される端子12上のクロックサイクルの数が回路72によって監視される。30

#### 【0013】

第1の実施形態では、前記監視回路72は端子16上のデータの直列ストリームをレジスタ40へと完全に格納するために必要とされるすべてのクロックサイクルをカウントする。言い換れば、イネーブル信号がアクティブローである限り、クロックの数はカウンタ20へとカウントされる。例えば、データ端子上に提供されるデータが8ビットのデータである場合は、前記イネーブルはデータの8ビット全体が端子16上に提供されるまで活性化される。データの8ビットの各々はクロック12からの単一のクロックサイクルによ40

ってクロッキングまたは刻時される。従って、イネーブルが活性化されている間に生じるクロックサイクルの数をカウントすることにより、監視回路 72 はデータ入力端子 16 を介して提供されるデータビットの数を決定することができる。

#### 【0014】

1つの形式で、リップルカウンタはデータクロックサイクルのみをカウントするように構成できるが、直列シーケンスクロックサイクルもまたかつ依然として適切な格納先またはデスティネイションレジスタを決定することに注目することが重要である。例えば、イネーブル 14 によって提供される2進シーケンスは2つのクロックサイクルでありかつ提供されるデータ部分は8ビット、16ビットまたは24ビットの内の1つであると仮定する。カウンタ 20 は 10, 18 または 26 の値を格納するよう設計することができ（これはデータとデコードシーケンス長さを加えたものである）、または2進デコードシーケンスが提供される場合に時間期間を無視することにより 8, 16 または 24 を格納するために使用できる。いずれの場合も、デコーダからの最終的な結果は同じであり、カウントされたビットはデコーダ論理 30 がデータを受信すべきレジスタのサイズを決定できるようにする。

10

#### 【0015】

リップルカウンタ 20 によってカウントされるクロックサイクルの数は図 1 のデコーダ 30 に提供される。デコーダ 30 は次にリップルカウンタ 20 からの 5 ビットのカウント値をデコードしあつカウンタ 20 によって提供されたカウント値に応じてデコーダ出力信号 Z1, Z2 または Z3 の1つを活性化する。イネーブルされたとき、Z1 信号はデータが 8 ビットレジスタに提供されたことを示す。イネーブルされたとき、Z2 信号はデータが 16 ビットレジスタに提供されたことを示す。イネーブルされたとき、Z3 信号はデータが 24 ビットレジスタに提供されたことを示す。従って、監視回路 72 は1つのアクティブな出力を提供し、前記レジスタ選択制御信号の1つがターミナル 16 を通るデータの転送の完了に応じて活性化される。バンク選択制御信号およびレジスタ選択制御信号も、いっしょに、複数の AND ゲート 31 ~ 33、および 36 ~ 38 に提供されてレジスタ 51 ~ 56 ヘロード信号を提供する。AND ゲート 36 ~ 37 は第 1 のバンクまたは第 1 の組のレジスタ 57 に結合されている。AND ゲート 31 ~ 33 は第 2 のバンクまたは第 2 の組のレジスタ 59 に結合されている。第 1 のバンクのレジスタ 57 は 3 個のレジスタ 54, 55 および 56 を含んでいる（3 個は一例として使用されかつより多いあるいはより少ないレジスタを他の実施形態において使用することができる）。レジスタ 54 は 8 ビットのデータを格納する容量を有するレジスタである。図 1 のレジスタ 55 は 16 ビットのデータを格納する容量を有するレジスタである。図 1 のレジスタ 56 は 24 ビットのデータを格納する容量を有するレジスタである。

20

#### 【0016】

1 実施形態では、レジスタ 54 は集積回路 10 内の第 1 の位相同期ループ（PLL）（図示せず）のための制御レジスタである 8 ビットのレジスタである。この実施形態では、コードレジスタ 55 は集積回路 10 内の前記第 1 の位相同期ループ（PLL）（図示せず）の動作を制御する基準レジスタである。また、この実施形態において、レジスタ 56 は集積回路 10 に配置された前記第 1 の位相同期ループ（PLL）の動作を制御するための電圧制御発振器（VCO）の分周器レジスタである。従って、3 つのレジスタ 54 ~ 56 の集まりは 1 実施形態において IC 内の第 1 の PLL の動作を集合的に制御するために使用される。

30

#### 【0017】

レジスタ 51 ~ 53 はレジスタ 54 ~ 56 と同様のものである。例えば、レジスタ 51 はレジスタ 54 と同様に 8 ビットのデータを格納する容量を有する。レジスタ 52 はレジスタ 55 と同様に 16 ビットのデータを格納する容量を有する。レジスタ 53 はレジスタ 56 と同様に 24 ビットのデータを格納する容量を有する。従って、1 実施形態では、レジスタ 51 ~ 53 は集積回路 10 内の前記第 1 の位相同期ループ回路（図 1 には示されていない）と共に配置された第 2 の位相同期ループ（PLL）回路（図 1 には示されていない）

40

50

)を制御するために使用することができる。

**【0018】**

図1は、データ入力(data in)と名付けられたシリアル入力および24ビットを有する並列出力を有するシリアルシフトレジスタ40を示している(より大きなレジスタに対しては24ビットより多くを必要とする)。このシフトレジスタ40はターミナル12におけるクロックサイクルに応答してデータ入力16からの到来する時間シリアルなデータストリームを格納する。イネーブルが活性化されている間に、シリアルデータは端子16を介してレジスタ40に提供され、かつ監視回路72は前に述べたようにクロックのカウントを行ってイネーブルが不活性にされた(deactivated)ことによりデータシフトが完了した後にデータシフトレジスタ40内に格納されるデータビットの数を決定する。

10

**【0019】**

図1はシフトレジスタ50と直列に結合された付加的なシリアルデータ装置60および70を示している。装置60および70は数多くのシリアルシフト装置がシフトレジスタ40と直列に結合できあるいは直列に継続接続できる(cascaded)ことを示している。ゲート35およびデコーダ30の最大カウント信号はこのシリアル動作を行うことができるようになる。

**【0020】**

図1の回路の動作は次の通りである。ターミナルまたは端子16からレジスタ51～56の1つにデータ転送を開始するために、イネーブル信号が使用されて該転送を開始する。

20 始めに、該イネーブル信号は短い時間シリアルな2進シーケンスによってパルス化または肯定されあるいはトグルされる(図7を参照)。この時間シリアルな2進シーケンスはバンク選択回路74によって検知され、該バンク選択回路74は図2を参照してさらに詳細に説明する。この2進シーケンスは図1のバンク選択制御信号を介して図1におけるバンク59またはバンク57のいずれか1つを選択する。図1には2つのバンクが示されているが、イネーブル端子14におけるより長い2進シーケンスを使用することにより2つより多くのバンクのレジスタの間で選択するためにバンク選択回路を拡張することも可能なことに注意を要する。2進シーケンスがCPUのビットセットおよびピットクリア命令を介してイネーブル信号14上に提供された後、イネーブル信号は完全に活性化され(すなわち、以後は2進シーケンスを提供せずデータ入力の期間の間常にアクティブローとする)

30 )かつデータは端子16を介して受信される。

**【0021】**

データはクロック12からのクロックサイクルを介してシフトレジスタ40へとクロック入力される。データ16をシフトレジスタ60へとシフトするために使用されるこれらのクロックサイクル12はリップルカウンタ20によってカウントされる。いったんイネーブルが不活性にされると、カウンタ20のカウント値はデコードされて図1におけるデコーダ30からレジスタ選択制御信号出力を提供し、かつリップルカウンタはNORゲート35を介してリセットされる。この時点で、データは完全にレジスタ40内にシフトされかつ並列インタフェースを介してレジスタ51～56の入力において利用可能である。前記バンク選択制御信号およびレジスタ選択制御信号を提供することはゲート31～33および36～38の1つが活性化されて図1の6個のレジスタの内の1つにアクティブなコード信号を提供できるようにする。従って、図1におけるデコードプロセスは2次元的または2レベルのデコードプロセスであり、それはバンク選択回路74は2つのバンク57および59の内の1つを選択し、一方監視回路72は選択されたバンク内のどのレジスタがレジスタ40に格納されたデータによって書き込まれるかを選択するからである。

40

**【0022】**

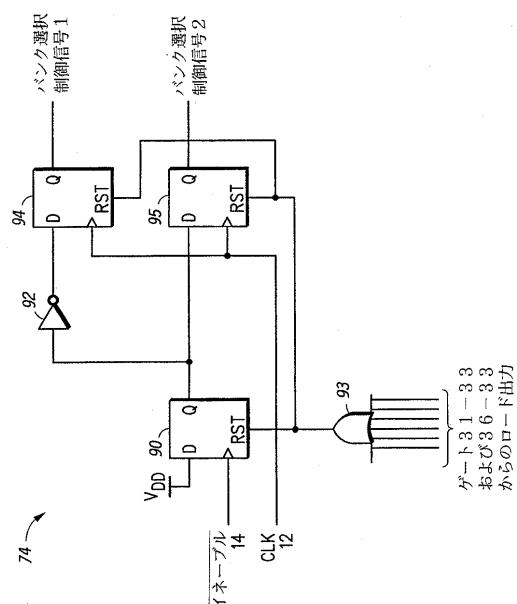

図2は、図1のバンク選択回路74をより詳細に示す。バンク選択回路74はDフリップフロップ90および1対のDフリップフロップ94および95を備えている。図2は図1のゲート31～33および36～38の出力のすべてをORゲート入力として受信しあつリセット信号をフリップフロップ90, 94および95に提供するリセットORゲート9

50

3を示している。

#### 【0023】

図6のイネーブルシーケンスは図2の回路において使用されてバンク2(図1のバンク59)を非選択に保つ一方でバンク1(図1のバンク57)を選択する。始めに、図6においてイネーブル信号はインアクティブハイ(inactive high)でありかつどのような方法であれトグルはしていない。さらに、フリップフロップ90, 94および95はすべてリセットされ(ゲート93はパワーアップに応じてリセットされるよう設計できる)、従って双方のバンク選択制御信号1および2はローでありかつ不活性である。図6の左側部分において、イネーブルはアクティブローに移行する。しかしながら、フリップフロップ90はフリップフロップ90へのクロック入力の立上りエッジにおいてのみD入力に際してVDD値をラッチする。従って、フリップフロップ90の出力Qはイネーブル14の立下りエッジにおいて(前のリセットのため)ローに留まっている。その後のバンク選択をイネーブルするためにイネーブル14において短時間のオールゼロ2進シーケンスが提供された後に(バンク1はその後デフォールトにより選択されるが、それはフリップフロップ90が変更されないからである)、クロック12は図6に示されるようにトグルを開始する。クロック12がトグルを開始したとき、論理“1”がフリップフロップ94にラッチされ、一方論理“0”がインバータ92のためフリップフロップ95にラッチされ、それによってバンク1を選択する(図1のバンク57)。従って、図1のレジスタ40へとデータをクロッキングする作用はまたどのバンクが直列的に提供されるデータによって書き込まれるべきかを選択する。バンクが今や選択されているにもかかわらず、データは図1のゲート31～33および36～38からの肯定された信号に応じてレジスタ51～56の1つにのみ書き込まれ、これらの信号はイネーブルがハイに移行し(不活性にされ)、バンク選択がハイであり、かつデコーダ30の1つの出力Z1～Z3がハイである場合にのみイネーブルされる。イネーブル14は図6におけるデータのクロッキングの間ローであるから、バンク信号が活性化されても、図1のレジスタ40へのシリアルシフトデータ入力動作の間は図1のレジスタ51～56のいずれにもデータはラッチされない。レジスタ40への入力データへのCLK12のトグルの反復もまたフリップフロップ94および95への安定した値をクロッキングするために続けられる。従って、バンク選択制御信号は図1のレジスタ40へのデータシフト動作に関連する反復されるクロックの間に逆にまたは不利に変更されることはない。

#### 【0024】

いったんデータが完全に図1のレジスタ40にシフトされると、CLKはトグルを停止する。さらに、クロックがトグルを停止した後、イネーブルが図6の右側部分においてインアクティブハイにされる。この時点で、イネーブルはハイでありバンクの1つがフリップフロップ94～95を介して選択され、かつデコーダ30の1つの出力がアクティブかつ安定になる。従って、図1のレジスタ54～56の1つが該レジスタ54～56の1つの「ロード」入力においてポジティブゴーイングエッジを介してレジスタ40の内容を含むよう書き込まれる。

#### 【0025】

図7のイネーブルシーケンスは図2の回路において使用されバンク1(図1のバンク57)を非選択に保つ一方でバンク2(図1のバンク59)を選択する。始めに、イネーブル信号は図7においてインアクティブハイでありかついずれの方法でもトグルしていない。さらに、フリップフロップ90, 94および95は全てリセットされ(ゲート93はパワーアップに応じてリセットされるよう設計できる)、したがって両方のバンク選択制御信号1および2はローでありかつ不活性状態とされまたはデアクティベイトされている。図7の左手部分において、イネーブルはアクティブローに移行する。しかしながら、フリップフロップ90はフリップフロップ90へのクロック入力の立上りエッジにおいてのみD入力におけるVDD値をラッチする。したがって、フリップフロップ90の出力Qはポイント203においてイネーブル14の立下りエッジに際して(前のリセットにより)ローに留まっている。ポイント203からポイント204への立上りエッジは図7のイネーブル

10

20

30

40

50

ル 1 4において遭遇する。この立上りエッジはフリップフロップ 9 0 に論理“1”を格納する。図 7 のポイント 2 0 4 からポイント 2 0 5 への立下りエッジはフリップフロップ 9 0 の Q 出力において提供される論理“1”を変更しない。クロック 1 2 は今やデータをレジスタ 4 0 へと捕捉するためにトグルを始める。クロック 1 2 がトグルを始めた時、論理“1”がフリップフロップ 9 5 へとラッチされ、一方論理“0”がインバータ 9 2 を介してフリップフロップ 9 4 へラッチされ、それによってバンク 2 (図 1 のバンク 5 9 ) を選択する。したがって、データを図 1 のレジスタ 4 0 へとクロッキングする作用はまた直列に提供されるデータとともにどのバンクが書き込まれるべきかを選択する。バンクがいまや選択されても、データは図 1 のゲート 3 1 ~ 3 3 および 3 6 ~ 3 8 からの肯定された信号に応じてレジスタ 5 1 ~ 5 6 の 1 つに書き込まれるのみであり、これらの信号はイネーブルがハイに移行し(不活性とされ)、バンク選択がハイであり、かつデコーダ 3 0 の 1 つの出力 Z 1 ~ Z 3 がハイである場合にのみイネーブルされる。イネーブル 1 4 は図 6 のデータのクロッキングの間ローであるから、バンク信号が活性化またはアクティベイトされていなくても図 1 のレジスタ 4 0 への直列シフトデータ入力動作の間に図 1 のレジスタ 5 1 ~ 5 6 のいずれにもデータはラッチされない。レジスタ 4 0 への入力データに対する C L K 1 2 の反復されるトグルはまた安定な値をフリップフロップ 9 4 および 9 5 へとクロッキングし続ける。したがって、バンク選択制御信号は図 1 のレジスタ 4 0 へのデータシフト動作に関連する反復されたクロックの間に逆に変更されることはない。

#### 【0026】

いったんデータが完全に図 1 のレジスタ 4 0 へとシフトされると、C L K 1 2 はトグルを停止する。さらに、クロック 1 2 がトグルを停止した後、イネーブルが図 6 の右側部分においてインアクティブハイにされる。このポイントで、イネーブルはハイであり、バンクの 1 つがフリップフロップ 9 4 ~ 9 5 を介して選択され、かつデコーダ 3 0 の 1 つの出力がアクティブでありかつ安定してする。したがって、図 1 のレジスタ 5 1 ~ 5 3 の 1 つがレジスタ 5 1 ~ 5 3 の 1 つの「ロード」入力においてポジティブゴーイング・エッジを介してレジスタ 4 0 の内容を含むよう書き込まれる。ゲート 3 1 ~ 3 3 および 3 6 ~ 3 8 の出力が前記ポジティブゴーイングのレジスタ書き込みエッジの後にバンク選択回路 7 4 を通るフィードバック経路により短い時間の間のみハイに留まっていることに注目することが重要である。図 1 のゲート 3 1 ~ 3 3 および 3 6 ~ 3 8 の出力は図 2 の OR ゲート 9 3 に提供され、該 OR ゲート 9 3 は図 1 のゲート 3 1 ~ 3 3 および 3 6 ~ 3 8 の 1 つから立ち上りまたはポジティブゴーイング・エッジが提供された後に図 2 のフリップフロップを急速にリセットする。したがって、図 2 は 2 つのバンクのレジスタの間で選択を行なう回路を示している。

#### 【0027】

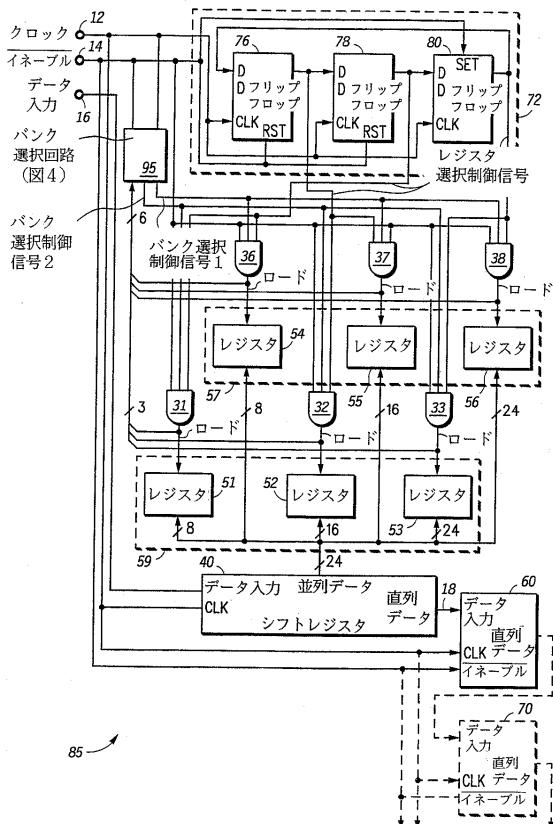

図 3 は、図 1 に示されるシステムの別の実施形態を示す。図 3 における回路の全ては監視回路 7 2 の内容を除き図 1 に示されたものと同じである。図 3 の監視回路 7 2 内にはジョンソンカウンタ (Johnson counter) を形成する複数のフリップフロップ 7 6 ~ 8 0 が示されている。ジョンソンカウンタは図 1 の回路 7 2 に示されるリップルカウンタ 2 0 、デコーダ 3 0 およびゲート 3 5 を置換える。イネーブル 1 4 がインアクティブハイである場合、フリップフロップ 7 6 および 7 8 はクリアされ、一方フリップフロップ 8 0 はセットされる。いったんイネーブルがアクティブローに移行すると、データ 1 6 をレジスタ 4 0 内へラッチし、かつ回路 7 2 内のジョンソンカウンタをクロッキングするクロックサイクルが端子 1 2 上に生じるに応じて、フリップフロップはセットビットをフリップフロップ 8 0 からフリップフロップ 7 6 を通り 8 0 へと巡回して回転させ始める。バンク選択 2 進シーケンスがイネーブル 1 4 によって提供されている間に、図 3 の回路 7 2 のジョンソンカウンタはイネーブルライン上の 2 進シーケンスの進行の間に 1 回またはそれ以上スタートされかつリセットされる。2 進シーケンスの間のこのスタートおよびリセットは不安定な (erratic) データをロードゲート 3 1 ~ 3 3 および 3 6 ~ 3 8 に送ることになる。しかしながら、バンク選択回路 7 4 からの信号は不活性とされこの不安定なデータが N A N D ゲート 3 1 ~ 3 3 および 3 6 ~ 3 8 を通って進むのを防止するか

10

20

30

40

50

ら、この不安定なデータは問題にはならない。回路 7 2 が到来するデータビットを処理しかつ状態を変えている間は、イネーブルはローになるであろう。したがって、バンク選択が決定されかつセットされた後に、データを入力するためのローのイネーブル信号は回路 7 2 がデータを入力するために使用するクロック信号を処理している間に N A N D ゲート 3 1 ~ 3 3 および 3 6 ~ 3 8 が悪いロード信号を受け渡すのを防止する。したがって、イネーブルがローである限り、バンク選択の 1 つが活性化されかつ回路 7 2 からの 3 つの出力の内の 1 つが活性化されることによりイネーブルがハイに移行するまで図 3 のレジスタ 5 1 ~ 5 6 においてはラッチは生じない。したがって、レジスタ 5 1 ~ 5 6 の 1 つは図 7 のポイント 2 0 1 においてラッチされることになる。

## 【0028】

10

レジスタ 4 0 内に 2 進ビットをラッチするために使用される各々のクロックサイクルに対し、レジスタ 8 0 において始めに生成されたセットビットはフリップフロップ 7 6 ~ 8 0 の巡回ループ内の次のレジスタに巡回的に移動される。例えば、ターミナル 1 6 から最初のデータ要素をクロッキングする第 1 のクロックサイクルはレジスタ 8 0 における論理 “1” をレジスタ 7 6 にシフトする。データ 1 6 をレジスタ 4 0 にラッチするターミナル 1 2 上で遭遇する第 2 のクロックはこのセットビットをフリップフロップ 7 6 からフリップフロップ 7 8 へとシフトする。このプロセスは図 3 のレジスタ 4 0 内にデータビットをラッチするために使用されるそれぞれのクロックに対して繰り返される。

## 【0029】

20

8 ビットのデータ値がターミナル 1 6 によって提供されかつ 8 つのクロックを介してレジスタ 4 0 にラッチされた時、始めにフリップフロップ 8 0 において生成されたセットビットは図 3 のフリップフロップ 7 8 内で巡回を停止する（すなわち、8 / 3 の余りは 2 である）。したがって、フリップフロップ 7 8 の出力はバンク選択回路 7 4 によって選択された 8 ビットのレジスタ 5 1 および 5 4 の内の 1 つの中での格納をイネーブルするために使用される。フリップフロップ 8 0 において生成させたセットビットは 1 6 ビットのデータ値がシフトレジスタ 4 0 にシフト入力された時にフリップフロップ 7 6 内で巡回を停止する（すなわち、1 6 / 3 の余りは 1 である）。したがって、フリップフロップ 7 6 の出力はバンク選択回路 7 4 によって選択された 1 6 ビットのレジスタ 5 2 または 5 5 の内の 1 つへの格納をイネーブルするために使用される。最後に、始めにフリップフロップ 8 0 にあったセットビットは一連の 2 4 のデータビットがシフトレジスタ 4 0 へシフトされた後に同じフリップフロップ 8 0 内に最終的に存在することになる（すなわち、2 4 / 3 の余りは 0 である）。したがって、フリップフロップ 8 0 の出力はバンク選択回路 7 4 によって選択されるレジスタ 5 3 および 5 6 の内の 1 つの中にデータをラッチするために使用される。したがって、図 3 の回路はカウンタおよびイネーブル - 出力 - ラッチドデコーダを使用して図 1 において導入された 2 次元デコード機構に対しややよりコンパクトな解決を与える。

30

## 【0030】

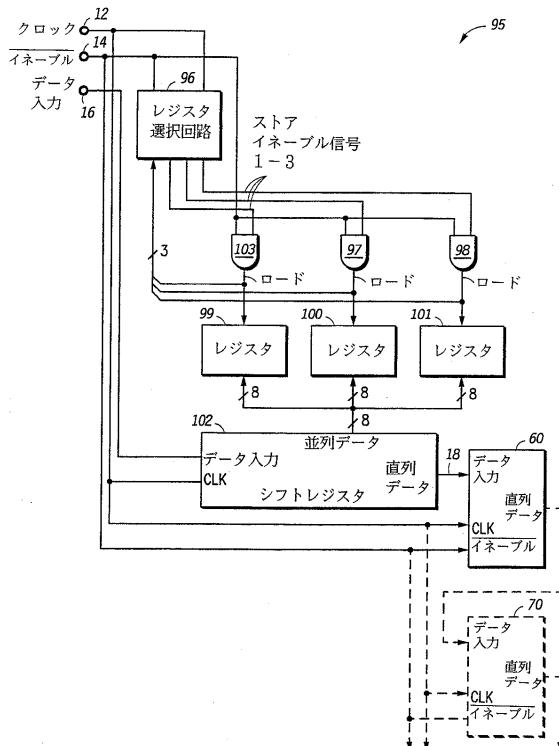

図 4 は、図 1 ~ 図 3 に示されたものに対しさらに別の実施形態を示す。図 1 ~ 図 3 に示されたバンク選択およびレジスタ選択を使用する上で 2 次元デコードシーケンスを行なう代りに、図 4 は 1 次元選択プロセスを示している。言い換えれば、図 4 は複数のレジスタの内の 1 つがイネーブル 1 4 において直列的に提供される 2 進コードシーケンスを監視することによってのみ選択されそれによって図 4 の回路はデータクロックまたはシフトレジスタにシフトされるデータエレメントをカウントするために何等の回路も要求しない。したがって、図 4 においては図 1 および図 3 の監視回路 7 2 と類似する回路は無い（この回路は図 4 では必要とされない）。

40

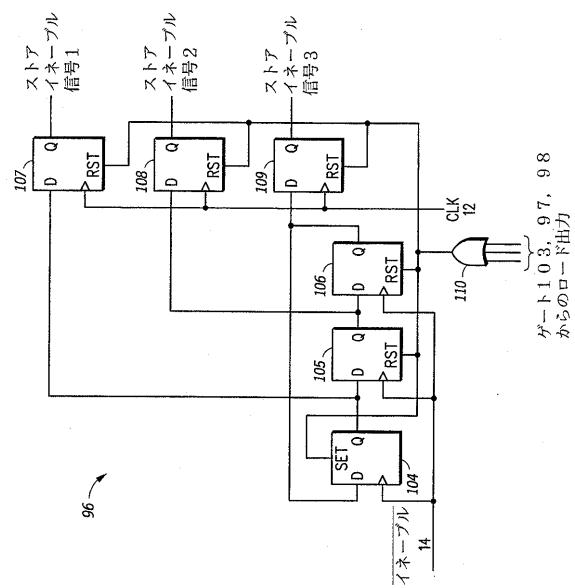

## 【0031】

図 4 は、図 1 および図 3 に示されるのと同じクロック 1 2 、イネーブル 1 4 およびデータ入力 1 6 の各入力を含んでいる。しかしながら、図 1 および図 3 の監視回路 7 2 および 7 4 は図 4 では単一のレジスタ選択回路 9 6 に置換えられている。レジスタ選択回路 9 6 は複数のレジスタ選択制御信号を複数のレジスタの各々に提供する（図 4 では 3 つが示され

50

ているが、イネーブル 14 に到来する 2 進シーケンスを長くすることにより数多くのレジスタを設けることができる）。これらの制御信号は複数のANDゲート 103.97 および 98 に提供される。ゲート 103.97 および 98 はロード信号を複数のロードレジスタ 99～101 に提供する。入力データターミナル 16 は図 1 および図 3 に示されたのと同様の方法でシフトレジスタ 102 に直列的に結合されている。さらに、同じ直列的に結合された装置 60 および 70 が図 1 および図 3 に示されているように図 4 に示されている。

#### 【0032】

前に述べたように、図 4 は複数のレジスタ 99～101 の内のどのレジスタがシフトレジスタ 102 に提供されるデータを格納すべきかを決定する 1 次元デコードプロセスを示している。どのロードレジスタが選択されるかの決定はレジスタ選択回路 96 によって排他的に行なわれる。

#### 【0033】

レジスタ選択回路 96 はさらに図 5 に示されている。該レジスタ選択回路 96 はイネーブル信号 14 を監視して該イネーブル 14 の立上りエッジの特定の数を検出することによりデータ転送を開始する。データ転送を始めるためにイネーブル信号 14 はデータがデータ入力 16 に提供される前に 2 進シーケンスを提供する。この 2 進シーケンスは立上りエッジを含み、該立上りエッジは回路 96 で監視されて図 4 に示されるレジスタ選択制御信号を提供する。図 5 の回路は図 4 に示されるように 3 つまでのレジスタ 99～101 の選択を可能にする。

#### 【0034】

回路 96 はジョンソンカウンタとして構成された第 1 の組のレジスタ 104～106 を有する。始めに、イネーブル 14 はアイドルまたはオフ状態であり、この場合、イネーブルは非肯定値 (deasserted value) または論理 “1” を絶えず提供する。したがって、フリップフロップ 105～106 はリセット状態にあり、一方フリップフロップ 104 はセット状態にあり、この場合この 100 状態はイネーブル 14 によって提供される一定の論理 “1” によって乱されることはない。エンコーディングを開始するため、エンコードライン 14 にゼロが始めに提供される。このゼロに続きゼロ～2 の立上りエッジが続く。もしイネーブル 14 におけるゼロの立上りが検出されれば、フリップフロップ 104 は論理 “1” を保持する。もし 1 の立上りエッジが検出されれば、フリップフロップ 105 は 3 つのフリップフロップ 104～106 の間で論理 “1” のみを含むことになる。もし 2 つの立上りエッジが検出されれば、フリップフロップ 106 は 3 つのフリップフロップ 104～106 の間で論理 “1” のみを含むことになる。論理 “1” を含むフリップフロップは図 4 の 3 つのレジスタ 99～101 の内のどれが、図 2 フリップフロップ 94～95 と同様のフリップフロップ 107～109 へと 1 をイネーブルした論理 “1” をラッチすることにより、書き込みのために選択されるかを決定する。

#### 【0035】

したがって、図 5 はデータを図 4 の 3 つのレジスタ 99～101 に選択的にロードするために使用できるあるいはより多くのフリップフロップを使用することによって図 4 よりさらに複雑な回路のために使用することができる回路を示している。一般にイネーブル 14 によって始めに提供される 2 進シーケンス（立上りエッジ）はどのレジスタがシフトレジスタ 102 に直列的にシフトされる最終的なデータを格納するかを選択する。

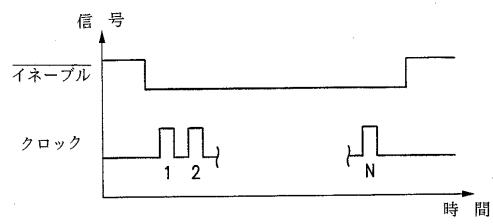

#### 【0036】

図 6 にはイネーブル 14 およびクロック 12 を含むタイミング図が示されている。イネーブル 14 はここで示されたシフトレジスタに適切な長さのデータ値を提供するために必要な N クロックサイクルの期間全体の間ローに留まっている。例えば、8 ビットのデータ値に対しては N = 8 であり、24 ビットのデータ値に対しては N = 24 であるなどとなる。図 6 は図 1～図 5 の内の 1 つまたはそれ以上の動作を説明するために前に使用された。

#### 【0037】

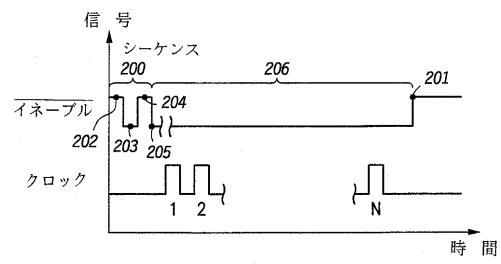

図 7 にはイネーブル 14 およびクロック 12 を含むタイミング図が示されている。データ

10

20

30

40

50

ライン上のシリアルアドレシングは多くのS P IおよびS C Iの制約があると可能ではないから、データ受信フェーズ206の前にイネーブルライン14上にエンコーディングシーケンス200が設けられている。イネーブルシーケンス200の発生の間に、1つまたはそれ以上のポイント202, 203, 204, 205等に位置する値は図1～2、図3、または図4～図5に示された3つの実施形態の1つで示されたように、ラッチされかつ処理される。図7は図1～図5の回路を説明するために前に使用されている。

### 【0038】

#### 【発明の効果】

したがって、本発明によれば、I C内へとデータを直列的に走査する(scanning)ための方法および装置が提供されたことが明らかである。本発明が特定の実施形態に関して説明されかつ示されたが、本発明はこれらの例示的な実施形態に限定されるものでないと考える。当業者は本発明の精神および範囲から離れることなく修正および変更を行うことが可能なことを認識するであろう。例えば、ここでは8ビット、16ビットおよび24ビットのレジスタが説明されたが、任意のサイズのレジスタを使用できることは明らかである。ここで示されたレジスタは任意の機能のために使用できる。ここで示されたレジスタは任意の数のバンクその他に構成することができる。ここではジョンソンカウンタが示されたが、このカウンタはグレイコードカウンタ、2進カウンタ、状態マシン、または他の回路と置換えることができる。したがって、この発明は添付の特許請求の範囲に含まれる全ての変更および修正を含むものと考える。

#### 【図面の簡単な説明】

【図1】本発明に係わる、2つまたはそれ以上のレジスタが同じサイズである複数のレジスタの内の1つにデータを直列的に提供するためのシステムを示すブロック図である。

【図2】本発明に係わる、図1のバンク選択回路のより詳細な構成を示すブロック図である。

【図3】本発明に係わる、図1に示された回路の別の実施形態を示すブロック図である。

【図4】本発明に係わる、図1および図3に示されたシステムのさらに他の実施形態を示すブロック図である。

【図5】本発明に係わる、図4のレジスタ選択回路を示すブロック図である。

【図6】本発明に係わる、図1、図3および図4の内の1つまたはそれ以上において示されたシステムの動作方法を示すタイミング図である。

【図7】本発明に係わる、図1、図3および図4の内の1つまたはそれ以上において示されたシステムの動作方法を示すタイミング図である。

#### 【符号の説明】

12 クロック端子

14 イネーブル端子

16 データ入力端子

20 リップルカウンタ

30 デコーダ

40 シフトレジスタ

31, 32, 33, 36, 37, 38 ANDゲート

35 ORゲート

51, 52, ..., 56 レジスタ

60, 70 付加的なシリアルデータ装置

72 監視回路

74 バンク選択回路

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

審査官 多賀 実

(56)参考文献 特開昭55-012573(JP,A)

特開平03-137712(JP,A)

特開平08-212154(JP,A)

特開昭55-033246(JP,A)

特開昭52-146135(JP,A)

米国特許第5146577(US,A)

米国特許第5454097(US,A)

(58)調査した分野(Int.Cl., DB名)

G06F12/00-06,

G06F13/16-18,

G06F13/38,

G06F7/00,

G06F9/30-36,

G06F1/24,

G11C7/00