**ФЕДЕРАЛЬНАЯ СЛУЖБА

ПО ИНТЕЛЛЕКТУАЛЬНОЙ СОБСТВЕННОСТИ,

ПАТЕНТАМ И ТОВАРНЫМ ЗНАКАМ**

**(12) ОПИСАНИЕ ИЗОБРЕТЕНИЯ К ПАТЕНТУ**

(21)(22) Заявка: 2010129098/28, 13.07.2010

(24) Дата начала отсчета срока действия патента:

13.07.2010

Приоритет(ы):

(22) Дата подачи заявки: 13.07.2010

(45) Опубликовано: 10.11.2011 Бюл. № 31

(56) Список документов, цитированных в отчете о

поиске: RU 2388110 С1, 27.04.2010. Low-Bias CTIA

Multiplexer for 1024 Element InGaAs Line

Sensors. Walter F. Kosonocky et all. SPIE,

v.2226, 1994, p.152. RU 2005308 С1, 30.12.1993.

RU 2073254 С1, 10.02.1997. US 6275059 B1,

14.08.2001. US 2007216439 A1, 20.09.2007.

Адрес для переписки:

111123, Москва, ш. Энтузиастов, 46/2,

ФГУП "НПО \"Орион"

(72) Автор(ы):

Акимов Владимир Михайлович (RU),

Васильева Лариса Александровна (RU),

Демидов Станислав Стефанович (RU),

Лисейкин Виктор Петрович (RU)

(73) Патентообладатель(и):

Российская Федерация, от имени которой

выступает Министерство промышленности и

торговли Российской Федерации (RU)

R U 2 4 3 3 5 0 3 C 1

C 1

C 0 3

C 3 3 4 2 R U**(54) СПОСОБ ОБНАРУЖЕНИЯ СКРЫТЫХ ДЕФЕКТОВ КРЕМНИЕВЫХ МОП

МУЛЬТИПЛЕКСОРОВ**

(57) Реферат:

Изобретение относится к технологии изготовления и способам тестирования МОП мультиплексоров. Сущность изобретения: в способе обнаружения скрытых дефектов кремниевых МОП мультиплексоров на кремниевой пластине с годными кристаллами МОП мультиплексоров вскрывают окна в защитном слое окисла к металлизированным площадкам истоков МОП транзисторов и подложке, наносят слой индия, формируют область индия, которая закорачивает все истоки МОП транзисторов на подложку в

каждом кристалле. При этом область индия, которая закорачивает все истоки МОП транзисторов на подложку, выполняют в виде полос, расположенных только над истоками МОП транзисторов. Затем проводят контроль годных кристаллов с обнаружением скрытых дефектов и проводят формирование In столбиков. Способ позволяет увеличить надежность метода обнаружения скрытых дефектов кремниевых МОП мультиплексоров за счет исключения прямых закороток стоковых областей на подложку. 4 ил.

R U 2 4 3 3 5 0 3 C 1

Фиг.3

R U 2 4 3 3 5 0 3 C 1

R U 2 4 3 3 5 0 3 C 1

RUSSIAN FEDERATION

(19) RU<sup>(11)</sup> 2 433 503<sup>(13)</sup> C1

(51) Int. Cl.

*H01L 21/66* (2006.01)

FEDERAL SERVICE

FOR INTELLECTUAL PROPERTY,

PATENTS AND TRADEMARKS

## (12) ABSTRACT OF INVENTION

(21)(22) Application: 2010129098/28, 13.07.2010

(24) Effective date for property rights:

13.07.2010

Priority:

(22) Date of filing: 13.07.2010

(45) Date of publication: 10.11.2011 Bull. 31

Mail address:

111123, Moskva, sh. Ehntuziastov, 46/2, FGUP

"NPO "Orion"

(72) Inventor(s):

Akimov Vladimir Mikhajlovich (RU),

Vasil'eva Larisa Aleksandrovna (RU),

Demidov Stanislav Stefanovich (RU),

Lisejkin Viktor Petrovich (RU)

(73) Proprietor(s):

Rossijskaja Federatsija, ot imeni kotoroj

vystupaet Ministerstvo promyshlennosti i

torgovli Rossijskoj Federatsii (RU)

## (54) METHOD OF HIDDEN FAULT LOCATION OF SILICON-GATE MOS MULTIPLEXERS

(57) Abstract:

FIELD: electricity.

SUBSTANCE: method of hidden fault location of silicon-gate MOS multiplexers on a silicon wafer with suitable MOS crystals of multiplexers involves opening windows in a field oxide layer to metallised areas of MOS sources of transistors and a substrate, coating with an indium layer, forming an indium area which short-circuits all the MOS sources of the transistors on the substrate in each crystal. The indium area which short-circuits all the MOS sources of the transistors on the substrate is stripped only over the MOS sources of the transistors. It is followed with known-good chip check to locate hidden faults and to form In stubs.

EFFECT: method allows providing higher reliability of hidden fault location of the silicon-gate MOS multiplexers due to elimination of direct short-circuits of the stock areas on the substrate.

4 dwg

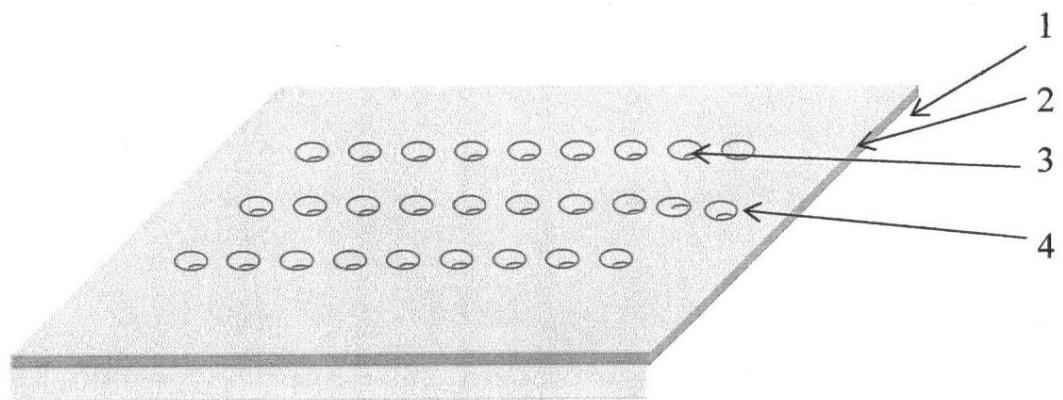

Фиг.3

R U 2 4 3 3 5 0 3 C 1

Изобретение относится к технологии изготовления и способам тестирования МОП мультиплексоров.

В настоящее время широко используется способ изготовления гибридных ИК матричных фотоприемных устройств (МФПУ) методом перевернутого монтажа фоточувствительных элементов с МОП мультиплексором при помощи индивидуальных столбиков. Послестыковки часто обнаруживаются электрические дефекты МОП мультиплексора, определить которые без специальных мер тестирования достыковки невозможно, например электрическое короткое замыкание между входными контактами и выходными шинами МОП мультиплексора (исток - шина стока ключевого МОП транзистора) в ячейке матрицы считывания фотосигнала.

Известно, что для выявления упомянутого выше дефекта используется сплошной слой In толщиной не менее толщины окисного слоя, закорачивающий все истоки МОП транзисторов слоем индия на подложку [RU, патент на изобретение №2388110 С1].

Путь тока при этом: стоковая шина-дефект-исток-слой индия-подложка.

Указанный метод обнаружения дефектов имеет следующие недостатки: наличие слоя индия над металлизированными шинами стоков может приводить к их закоротке на подложку слоем индия напрямую через дефект (пору) в защитном окисле над стоком, миную область истока, что можно назвать «ложной тревогой», так как в рабочей структуре слоя индия над стоковыми шинами нет. Путь тока в этом случае: стоковая шина-дефект-слой индия-подложка.

Задачей изобретения является увеличение надежности (достоверности) метода обнаружения скрытых дефектов кремниевых МОП мультиплексоров за счет исключения прямых закороток стоковых областей на подложку путем формирования в каждом кристалле МОП мультиплексора слоя индия в виде полос только над истоками МОП транзисторов.

Технический результат достигается тем, что:

- на металлизированные площадки истоков, вскрытые в окисле, наносят слой индия толщиной, равной необходимой высоте In столбика;

- при помощи фотолитографической обработки формируют в каждом кристалле область индия в виде полос, которые располагаются только над истоками МОП транзисторов и закорачивают их на подложку;

- контролируют функционирование мультиплексоров и фиксируют наличие дефектов, в том числе электрические закоротки исток-сток, которые не проявлялись при контроле функционирования без индия;

- далее методом фотолитографии формируют индивидуальные столбики высотой, равной толщине напыленной пленки индия.

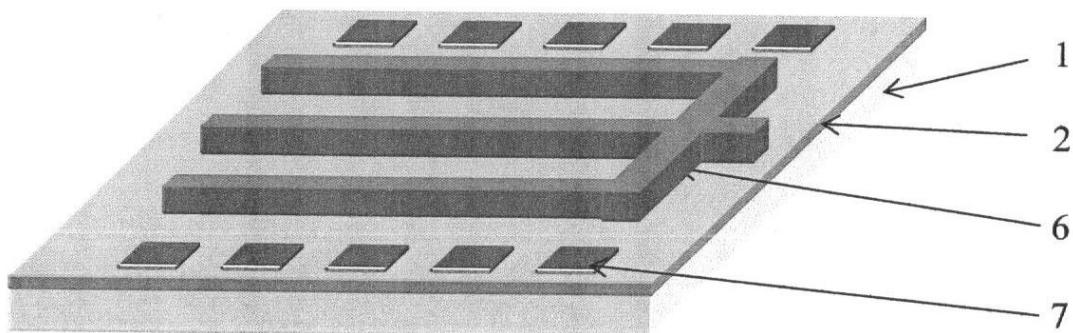

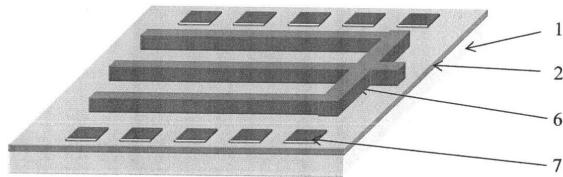

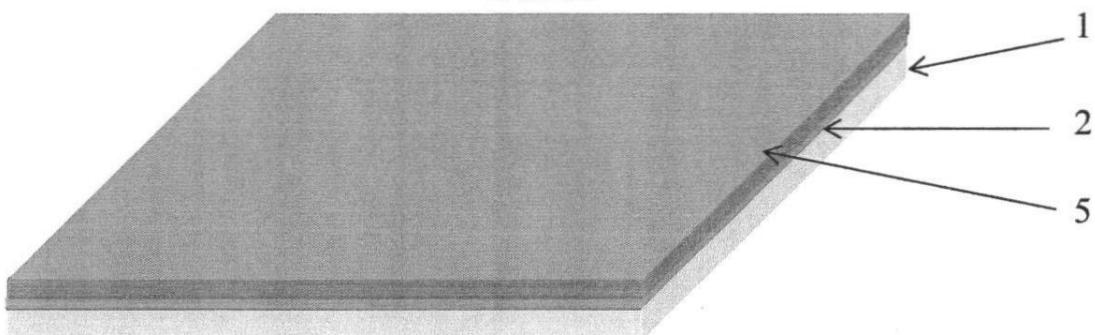

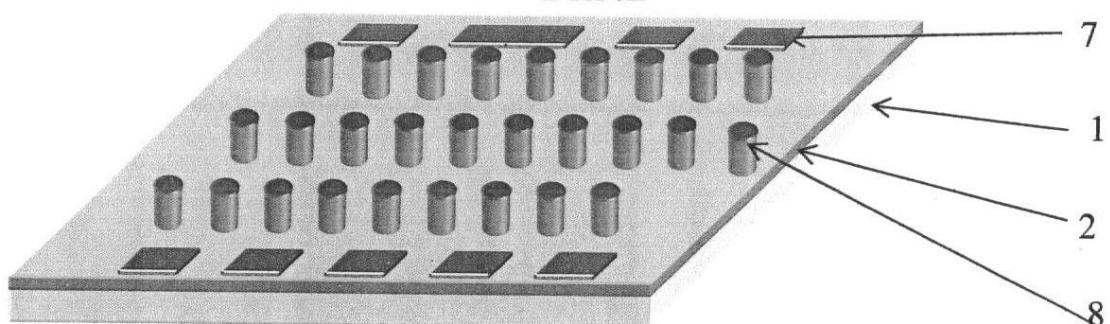

Последовательность технологической цепочки предлагаемого способа иллюстрируется на фиг.1-4, где:

- 1 - годный кристалл МОП мультиплексора, являющийся частью пластины;

- 2 - слой защитного окисла;

- 3 - контактные окна к металлизированным площадкам истоков МОП транзисторов;

- 4 - контактное окно к подложке;

- 5 - слой индия;

- 6 - область индия в виде полос, сформированная только над истоками МОП транзисторов мультиплексора и закорачивающая их на подложку;

- 7 - контактные площадки для контроля функционирования МОП мультиплексора;

- 8 - индивидуальные столбики.

Способ обнаружения скрытых дефектов МОП мультиплексоров осуществляется в

следующей последовательности:

- на кремниевой пластине с годными кристаллами МОП мультиплексоров вскрывают окна в защитном слое окисла к металлизированным площадкам истоков МОП транзисторов и подложке (фиг.1);

<sup>5</sup> - напыляют слой индия толщиной, равной необходимой высоте In столбиков (фиг.2);

- проводят фотолитографическую обработку по слою индия для получения области индия в виде полос, расположенных только над истоками МОП транзисторов, которая закорачивает все истоки МОП транзисторов на подложку (фиг.3);

<sup>10</sup> - проводят контроль функционирования годных МОП мультиплексоров с выявлением скрытых дефектов - закороток исток-сток;

- проводят фотолитографическую обработку по слою индия для формирования столбиков, режут пластину на кристаллы, осуществляют травление индия для формирования столбиков (фиг.4).

<sup>15</sup> Предлагаемый способ обнаружения дефектов гармонично вписывается в технологию изготовления МОП мультиплексоров.

Изготовлены экспериментальные образцы кремниевых МОП мультиплексоров с проведением тестирования на предмет обнаружения скрытых дефектов методом <sup>20</sup> закорачивания истоков МОП транзисторов на подложку слоем индия с рельефом 3...4 мкм и с последующей фотолитографией для получения однородных столбиков высотой 9...10 мкм.

#### Формула изобретения

<sup>25</sup> Способ обнаружения скрытых дефектов кремниевых МОП мультиплексоров, заключающийся в том, что на кремниевой пластине с годными кристаллами МОП мультиплексоров вскрывают окна в защитном слое окисла к металлизированным площадкам истоков МОП транзисторов и подложке, наносят слой индия, формируют <sup>30</sup> область индия, которая закорачивает все истоки МОП транзисторов на подложку в каждом кристалле, проводят контроль годных кристаллов с обнаружением скрытых дефектов, проводят формирование In столбиков, отличающийся тем, что область индия, которая закорачивает все истоки МОП транзисторов на подложку выполняют в виде полос, расположенных только над истоками МОП транзисторов.

<sup>35</sup>

<sup>40</sup>

<sup>45</sup>

<sup>50</sup>

Фиг.1

Фиг.2

Фиг.4