(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-99547

(P2014-99547A)

(43) 公開日 平成26年5月29日(2014.5.29)

(51) Int.Cl.

|                   |                  |

|-------------------|------------------|

| <b>H01L 25/07</b> | <b>(2006.01)</b> |

| <b>H01L 25/18</b> | <b>(2006.01)</b> |

| <b>H01L 21/60</b> | <b>(2006.01)</b> |

| <b>H01L 23/48</b> | <b>(2006.01)</b> |

F 1

|            |      |

|------------|------|

| H01L 25/04 | C    |

| H01L 21/60 | 301A |

| H01L 23/48 | G    |

テーマコード(参考)

5 F 0 4 4

審査請求 未請求 請求項の数 10 O L (全 12 頁)

(21) 出願番号

特願2012-251225 (P2012-251225)

(22) 出願日

平成24年11月15日 (2012.11.15)

(71) 出願人 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

110001195

特許業務法人深見特許事務所

白水 政孝

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

商 明

東京都千代田区丸の内二丁目7番3号

三菱電機株式会社内

F ターム(参考) 5F044 AA01 AA12 FF04 FF05

(54) 【発明の名称】電力半導体モジュールおよびその製造方法

## (57) 【要約】

【課題】ワイヤのループ安定化を図ることによりワイヤの断線や短絡を抑制可能な電力半導体装置およびその製造方法を提供する。

【解決手段】電力半導体モジュール10は、第1のフレーム部5と、電力半導体素子1と、第2のフレーム部6と、制御用集積回路2と、ワイヤ7aと、絶縁体部4とを有している。電力半導体素子1は、第1のフレーム部5の第1の表面5aに搭載されている。制御用集積回路2は、第2のフレーム部6の第3の表面6aに搭載され、かつ電力半導体素子1を制御するためのものである。

ワイヤ7aは、一端が電力半導体素子1に接続され、かつ他端が制御用集積回路2に接続されている。第1のフレーム部5の第1の表面5aに垂直な方向において、第1のフレーム部5の第1の表面5aと第2のフレーム部6の第3の表面6aと同じ高さに位置している。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

互いに対向する第1の表面および第2の表面を有する第1のフレーム部と、

前記第1のフレーム部の前記第1の表面に搭載された電力半導体素子と、

互いに対向する第3の表面および第4の表面を有する第2のフレーム部と、

前記第2のフレーム部の前記第3の表面に搭載され、かつ前記電力半導体素子を制御するための制御用集積回路と、

一端および他端を有し、前記一端が前記電力半導体素子に接続され、かつ前記他端が前記制御用集積回路に接続されたワイヤと、

前記電力半導体素子、前記第1のフレーム部、前記制御用集積回路、前記第2のフレーム部および前記ワイヤを封止する絶縁体部とを備え、

前記第1のフレーム部の前記第1の表面に垂直な方向において、前記第1のフレーム部の前記第1の表面と前記第2のフレーム部の前記第3の表面とが同じ高さに位置している、電力半導体モジュール。

**【請求項 2】**

前記第1のフレーム部の前記第2の表面および前記第2のフレーム部の前記第4の表面に接する絶縁シートをさらに備えた、請求項1に記載の電力半導体モジュール。

**【請求項 3】**

前記第1のフレーム部の前記第2の表面と接するブロック部をさらに備えた、請求項1に記載の電力半導体モジュール。

**【請求項 4】**

前記ブロック部の材料は銅を含む、請求項3に記載の電力半導体モジュール。

**【請求項 5】**

前記ブロック部の材料はセラミックを含む、請求項3に記載の電力半導体モジュール。

**【請求項 6】**

前記第1のフレーム部および前記第2のフレーム部の少なくとも一方は、前記第1の表面と対面する側に位置する前記絶縁体部の面から前記絶縁体部の外部に出る、請求項1～5のいずれか1項に記載の電力半導体モジュール。

**【請求項 7】**

前記第1のフレーム部および前記第2のフレーム部の少なくとも一方は、前記絶縁体部から前記外部に露出した位置にコネクタピンを有している、請求項6に記載の電力半導体モジュール。

**【請求項 8】**

前記ワイヤの材質はアルミニウムを含む、請求項1～7のいずれか1項に記載の電力半導体モジュール。

**【請求項 9】**

互いに対向する第1の表面および第2の表面を有する第1のフレーム部と、

前記第1のフレーム部の前記第1の表面に搭載された電力半導体素子と、

互いに対向する第3の表面および第4の表面を有する第2のフレーム部と、

前記第2のフレーム部の前記第3の表面に搭載され、かつ前記電力半導体素子を制御するための制御用集積回路と、

一端および他端を有し、前記一端が前記電力半導体素子に接続され、かつ前記他端が前記制御用集積回路に接続されたワイヤと、

前記電力半導体素子、前記第1のフレーム部、前記制御用集積回路、前記第2のフレーム部および前記ワイヤを封止する絶縁体部とを備え、

前記第2のフレーム部は、前記絶縁体部の内部において前記第1の表面に対して交差する方向に折れ曲がっている、電力半導体モジュール。

**【請求項 10】**

第1の端面を有する第1のフレーム部と、前記第1の端面と隙間をあけて向かい合う第2の端面を有する第2のフレーム部と、前記第1のフレーム部および前記第2のフレーム

10

20

30

40

50

部の双方の側部に間隔をあけて配置され、かつ前記第1のフレーム部と前記第2のフレーム部とをつなぐ第3のフレーム部とを有するフレームを準備する工程と、

前記第3のフレーム部に対して前記第1のフレーム部および前記第2のフレーム部を前記第3のフレーム部の表面に交差する方向に折り曲げるとともに、前記第1の端面および前記第2の端面が向かい合う方向に前記第3のフレーム部を縮ませる工程と、

前記第1のフレーム部に電力半導体素子を搭載する工程と、

前記第2のフレーム部に前記電力半導体素子を制御するための制御用集積回路を搭載する工程と、

一端および他端を有するワイヤによって、前記一端を前記電力半導体素子に接続し、かつ前記他端を前記制御用集積回路に接続する工程とを備えた、電力半導体モジュールの製造方法。10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電力半導体モジュールおよびその製造方法に関し、特に、電力半導体素子と制御用集積回路とを接続するワイヤを有する電力半導体モジュールおよびその製造方法に関するものである。

【背景技術】

【0002】

従来、たとえばIGBT (Insulated Gate Bipolar Transistor)などの電力半導体素子と、当該電力半導体素子を制御する制御用集積回路とがワイヤにより接続された電力半導体モジュールが知られている。たとえば、特開2005-150595号公報(特許文献1)によれば、パワーチップと制御チップとが金を主成分とするワイヤで接続された電力半導体装置が開示されている。当該電力半導体装置によれば、パワーチップの放熱性と端子の絶縁性能とを両立するため、パワーチップが搭載されているフレームをパッケージの外周部に位置している絶縁シートに接触させ、かつ制御チップが搭載されているフレームはパッケージの中央部に位置している。20

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2005-150595号公報30

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上記の構成の電力半導体装置によれば、電力半導体素子と制御用集積回路との間に高い段差があるので、電力半導体素子と制御用集積回路とを接続するワイヤの端部に強い応力がかかるためワイヤの断線や短絡が発生することがあった。

【0005】

本発明は、上記のような課題に鑑みてなされたものであり、ワイヤの端部にかかる応力を緩和してワイヤのループ安定化を図ることによりワイヤの断線や短絡を抑制可能な電力半導体装置およびその製造方法を提供することを目的とする。40

【課題を解決するための手段】

【0006】

本発明に係る電力半導体モジュールは、第1のフレーム部と、電力半導体素子と、第2のフレーム部と、制御用集積回路と、ワイヤと、絶縁体部とを有している。第1のフレーム部は、互いに対向する第1の表面および第2の表面を有する。電力半導体素子は、第1のフレーム部の第1の表面に搭載されている。第2のフレーム部は、互いに対向する第3の表面および第4の表面を有する。制御用集積回路は、第2のフレーム部の第3の表面に搭載され、かつ電力半導体素子を制御するためのものである。ワイヤは、一端および他端を有し、一端が電力半導体素子に接続され、かつ他端が制御用集積回路に接続されている50

。絶縁体部は、電力半導体素子、第1のフレーム部、制御用集積回路、第2のフレーム部およびワイヤを封止する。第1のフレーム部の第1の表面に垂直な方向において、第1のフレーム部の第1の表面と第2のフレーム部の第3の表面とが同じ高さに位置している。ここで、同じ高さとは、第1の表面に垂直な方向において、第1の表面と第2の表面との距離が0.1mm以下であることを意味する。

【発明の効果】

【0007】

本発明によれば、ワイヤの端部にかかる応力を緩和してワイヤのループ安定化を図ることによりワイヤの断線や短絡を抑制可能な電力半導体装置およびその製造方法を提供することができる。

10

【図面の簡単な説明】

【0008】

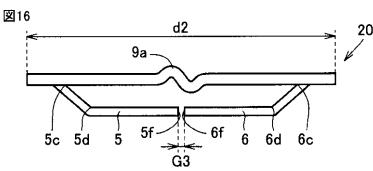

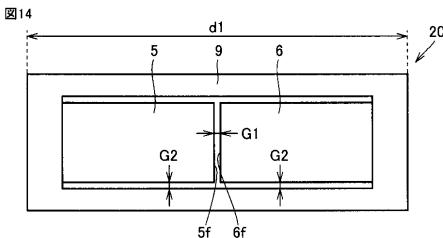

【図1】本発明の実施の形態1に係る電力用半導体装置の構成を概略的に説明するための断面模式図である。

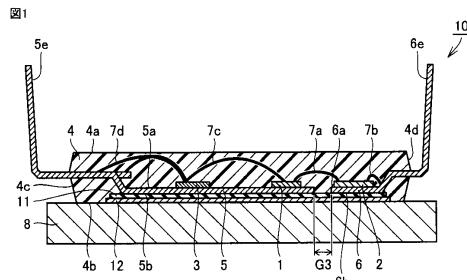

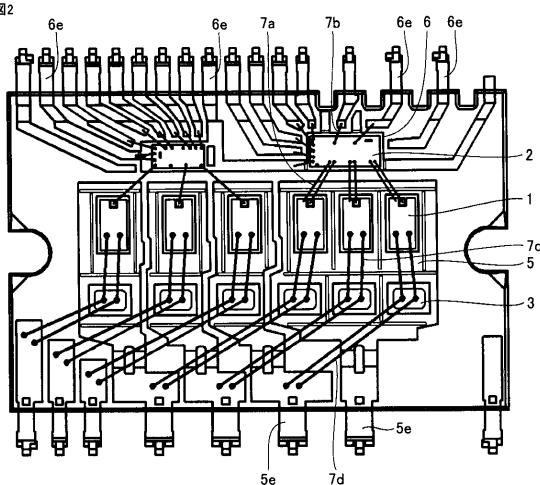

【図2】本発明の実施の形態1に係る電力用半導体装置の構成を概略的に説明するための平面模式図である。

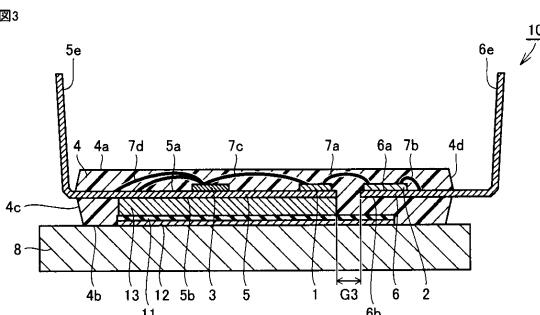

【図3】本発明の実施の形態2に係る電力用半導体装置の構成を概略的に説明するための断面模式図である。

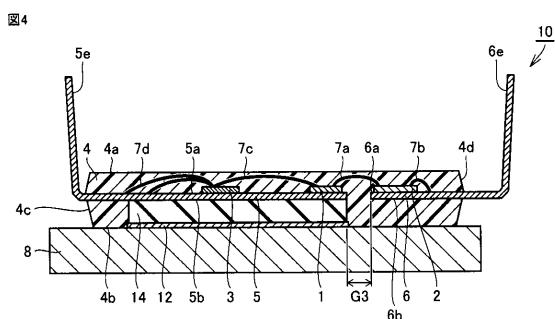

【図4】本発明の実施の形態3に係る電力用半導体装置の構成を概略的に説明するための断面模式図である。

20

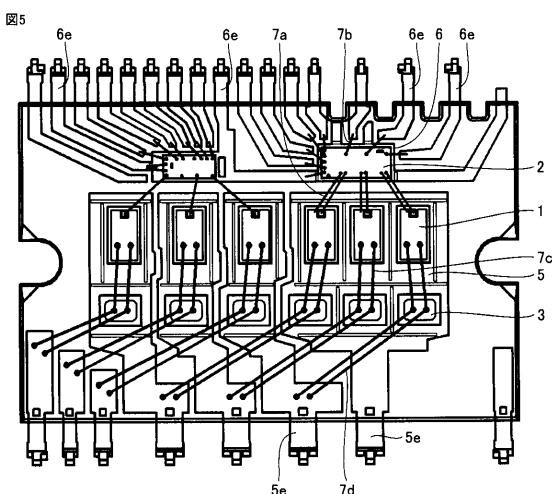

【図5】本発明の実施の形態2および実施の形態3に係る電力用半導体装置の構成を概略的に説明するための平面模式図である。

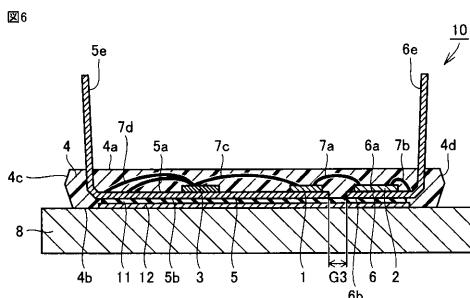

【図6】本発明の実施の形態4に係る電力用半導体装置の構成を概略的に説明するための断面模式図である。

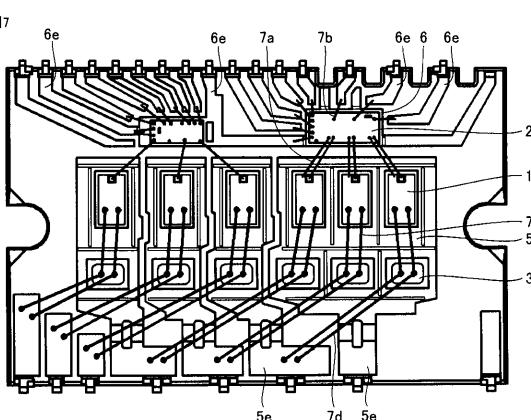

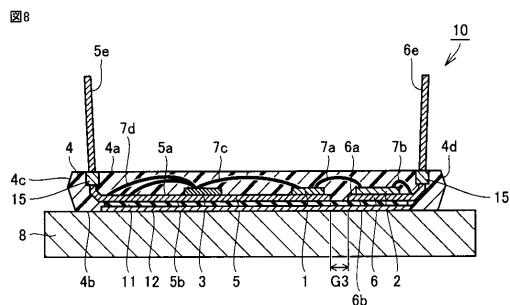

【図7】本発明の実施の形態4に係る電力用半導体装置の構成を概略的に説明するための平面模式図である。

【図8】本発明の実施の形態5に係る電力用半導体装置の構成を概略的に説明するための断面模式図である。

【図9】本発明の実施の形態5に係る電力用半導体装置の構成を概略的に説明するための平面模式図である。

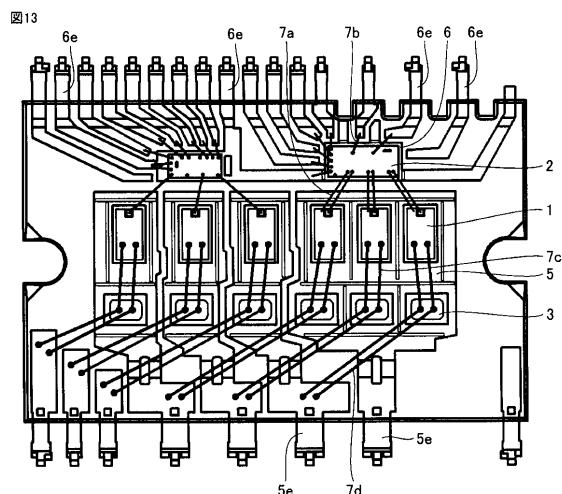

【図10】本発明の実施の形態6に係る電力用半導体装置の構成を概略的に説明するための平面模式図である。

30

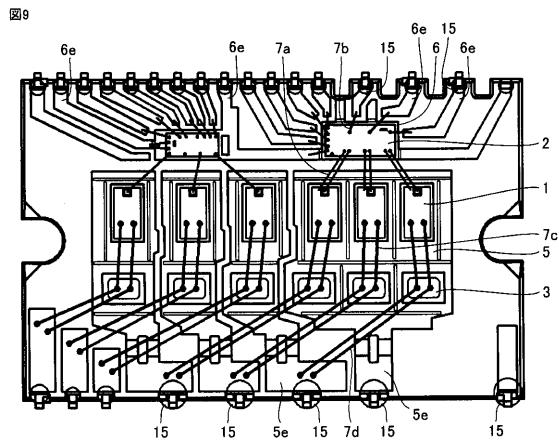

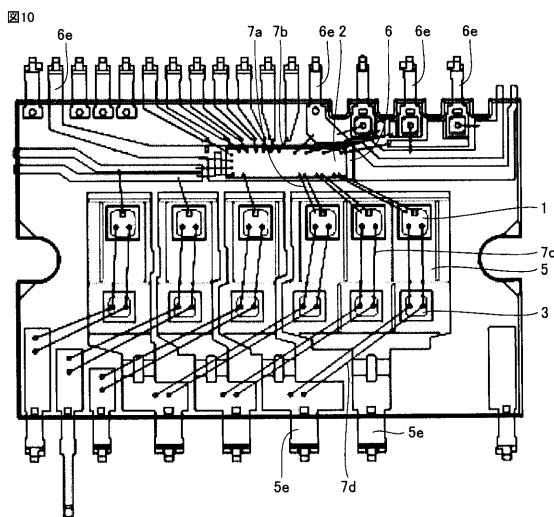

【図11】本発明の実施の形態7に係る電力用半導体装置の構成を概略的に説明するための断面模式図である。

【図12】本発明の実施の形態7に係る電力用半導体装置の構成を概略的に説明するための断面模式図である。

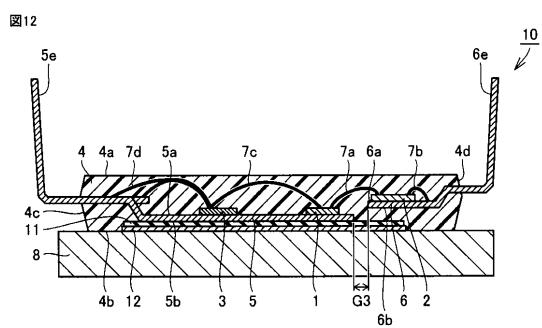

【図13】本発明の実施の形態7に係る電力用半導体装置の構成を概略的に説明するための平面模式図である。

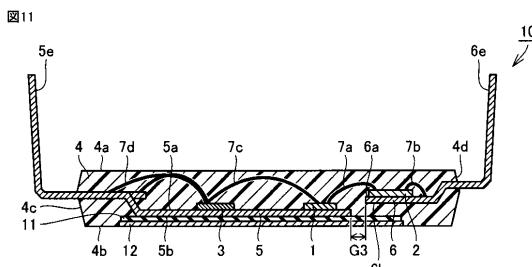

【図14】本発明の実施の形態1に係る電力用半導体装置の製造方法の第1の工程を概略的に説明するための平面模式図である。

40

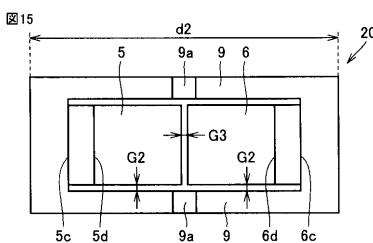

【図15】本発明の実施の形態1に係る電力用半導体装置の製造方法の第2の工程を概略的に説明するための平面模式図である。

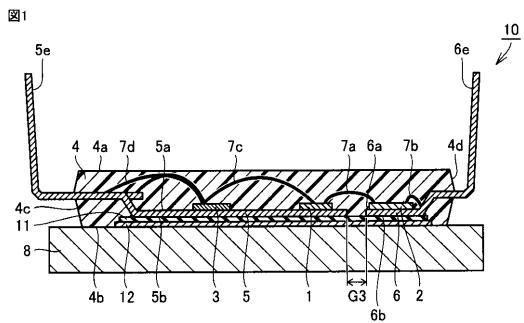

【図16】本発明の実施の形態1に係る電力用半導体装置の製造方法の第2の工程を概略的に説明するための断面模式図である。

【発明を実施するための形態】

【0009】

以下、図面に基づいて本発明の実施の形態について説明する。なお、以下の図面において同一または相当する部分には同一の参照番号を付しその説明は繰返さない。

【0010】

(実施の形態1)

50

図1および図2を参照して、実施の形態1に係る電力半導体モジュールの構成について説明する。実施の形態1に係る電力半導体モジュール10は、IGBT1と、IC(Integrated Circuit)2と、FWDi(Free Wheeling Diode)3と、第1のフレーム部5と、第2のフレーム部6と、ワイヤ7aと、絶縁体部4とを主に有している。

#### 【0011】

第1のフレーム部5は、互いに対向する第1の表面5aおよび第2の表面5bを有しており、第1のフレーム部5の第1の表面5a上にIGBT1やFWDi3などの電力半導体素子が搭載されている。IGBT1およびFWDi3は、たとえばはんだなどの接合部材で第1の表面5aに接合されている。

10

#### 【0012】

第2のフレーム部6は、互いに対向する第3の表面6aおよび第4の表面6bを有しており、第2のフレーム部6の第3の表面6aに電力半導体素子を制御するための制御用集積回路であるIC2が搭載されている。IC2の裏面は、たとえばはんだなどの接合部材で第3の表面6aに接合されている。第2のフレーム部6はグラウンド電位であってもよい。図2に示すように、1つの第2のフレーム部6に2つのIC2が搭載されていてもよい。IC2には、温度センサが内蔵されていてもよい。

#### 【0013】

IGBT1とIC2とはワイヤ7aにより直接電気的に接続されている。ワイヤ7aは一端および他端を有し、一端がIGBT1に接続され、かつ他端がIC2に接続されている。ワイヤ7aは、第1のフレーム部5と第2のフレームとを跨ぐように配置されている。図2に示すように、3つのIGBT1が1つのICにワイヤ7aにより接続されていてもよい。またワイヤ7aは単数でも複数でもよい。またIGBT1とFWDi3とはワイヤ7cにより電気的に接続されている。FWDi3は第1のフレーム部5とワイヤ7dにより電気的に接続されていてもよいし、第1のフレーム部5とは異なるフレームに電気的に接続されていてもよい。さらにIC2は第2のフレーム部6とワイヤ7bにより電気的に接続されていてもよいし、第2のフレーム部6とは異なる他のフレームに電気的に接続されていてもよい。ワイヤ7a～7dはたとえば金を含む材料からなるが、たとえばアルミニウムなどであってもよい。金よりも低コストなアルミニウムを用いることで、電力半導体モジュール10の製造コストを低減することができる。

20

#### 【0014】

絶縁体部4は、IGBT1、FWDi3、IC2、第1のフレーム部5、第2のフレーム部6およびワイヤ7a～7dを封止している。絶縁体部4はたとえば樹脂から成るが、セラミックなどであってもよい。

30

#### 【0015】

図1に示すように、第1のフレーム部5の第1の表面5aに垂直な方向(つまり図1における上下方向)において、第1のフレーム部5の第1の表面5aと第2のフレーム部6の第3の表面6aとが同じ高さに位置している。本発明において同じ高さとは、第1の表面5aに垂直な方向における第1の表面5aと第3の表面6aとの距離が0.1mm以下であることを意味する。つまり、第1の表面5aが第3の表面6aよりも0.1mm以下だけ絶縁シート11に近くに位置してもよく、0.1mm以下だけ絶縁シート11より遠くに位置していてもよい。

40

#### 【0016】

第1のフレーム部5および第2のフレーム部6の各々は、絶縁体部4の内部において第1のフレーム部5の第1の表面5aに対して垂直な方向に折れ曲がっている。第1のフレーム部5は絶縁体部4の左側面部4cから絶縁体部4の外部に出ており、端子部5eと繋がっている。同様に、第2のフレーム部6は絶縁体部4の右側面部4dから絶縁体部4の外部に出ており、端子部6eと繋がっている。第1のフレーム部5と端子部5eとは一体として形成されていてもよいし、別体であってもよい。同様に、第2のフレーム部6と端子部6eとは一体として形成されていてもよいし、別体であってもよい。

50

## 【0017】

本実施の形態に係る電力半導体モジュール10は、第1のフレーム部5の第2の表面5bおよび第2のフレーム部6の第4の表面6bに接する絶縁シート11を有している。絶縁シート11は、第2の表面5bおよび第4の表面6bの全てをカバーしていることが好ましい。絶縁シート11の第1のフレーム部5が接している面と反対側の面に接して金属板12が配置されており、金属板12は絶縁体部4から露出している。放熱フィン8は、絶縁体部4の下面4bおよび金属板12と接して設けられている。

## 【0018】

次に、本実施の形態に係る電力半導体モジュールの製造方法について図1、図2および図14～図16を参照して説明する。

10

## 【0019】

まず図14を参照して、フレーム準備工程が実施される。具体的には、中央にH形状の切欠き部が形成され、かつ金属からなるフレーム20が準備される。当該フレーム20は、第1の端面5fを有する第1のフレーム部5と、当該第1の端面5fと隙間G1をあけて向かい合う第2の端面6fを有する第2のフレーム部6とを有する。当該フレーム20は、第1のフレーム部5および第2のフレーム部6の各々の側部に隙間G2をあけて配置され、かつ第1のフレーム部5と第2のフレーム部6とを繋ぐ第3のフレーム部9を有する。

20

## 【0020】

次に、第1のフレーム部5に電力半導体素子が搭載される工程と、第2のフレーム部6に電力半導体素子を制御するための制御用集積回路が搭載される工程とが実施される。具体的には、IGBT1およびFWDiが第1のフレーム部5の第1の表面5aに搭載され、IC2が第2のフレーム部6の第3の表面6aに搭載される。

20

## 【0021】

図15および図16を参照して、フレーム折り曲げ工程が実施される。具体的には、第3のフレーム部9に対して第1のフレーム部5および第2のフレーム部6を第3のフレーム部9と交差する方向に折り曲げるとともに、第1の端面5fおよび第2の端面6fが向かい合う方向に第3のフレーム部9を縮ませる。第3のフレーム部9を縮ませるとは、フレーム20の幅が幅d1から幅d2に小さくなることである。図16に示すように、第3のフレーム部9を縮めることにより、第3のフレーム部9の中央付近に湾曲部9aが形成されてもよい。

30

## 【0022】

第1のフレーム部5は、第1の折り曲げ部5cで絶縁シート11側に折り曲げられ、第2の折り曲げ部5dにおいて絶縁シート11とは反対側に折り曲げられる。同様に、第2のフレーム部6は、第1の折り曲げ部6cで絶縁シート11側に折り曲げられ、第2の折り曲げ部6dにおいて絶縁シート11とは反対側に折り曲げられる。折り曲げ後の第1のフレーム部5と第2のフレーム部6とは、第1の表面5aの法線方向（つまり図16における上下方向）において同じ高さ位置している。その後、第1のフレーム部5と第2のフレーム部6とを接続する第3のフレーム部9が除去され、第1のフレーム部と第2のフレーム部6とは電気的に絶縁される。

40

## 【0023】

図1を参照して、ワイヤボンディング工程が実施される。具体的には、一端および他端を有するワイヤ7aにより、ワイヤ7aの一端がIGBT1に接続され、かつワイヤ7aの他端がIC2に接続されている。これにより、IGBT1とIC2とがワイヤ7aにより直接電気的に接続される。またIGBT1とFWDi3とがワイヤ7cにより電気的に接続される。FWDi3と第1のフレーム部5とはワイヤ7dにより電気的に接続されてもよい。さらにIC2と第2のフレーム部6とはワイヤ7bにより電気的に接続されてもよい。

## 【0024】

次に、モールド工程が実施される。具体的には、IGBT1、FWDi3、IC2、第

50

1のフレーム部5、第2のフレーム部6およびワイヤ7a～7dが樹脂からなる絶縁体部4によって封止される。

【0025】

なお、上記では、電力半導体素子が搭載される工程および制御用集積回路が搭載される工程の後に、フレーム折り曲げ工程を実施する場合について説明したが、フレーム折り曲げ工程の後に、電力半導体素子が搭載される工程および制御用集積回路が搭載される工程が実施されても構わない。

【0026】

次に、本発明の実施の形態1の作用効果について説明する。

実施の形態1に係る電力半導体モジュール10によれば、電力半導体素子と制御用集積回路とを繋ぐワイヤ7aを有し、かつ電力半導体素子が搭載された第1のフレーム部5の第1の表面5aと、制御用集積回路が搭載された第2のフレーム部6の第3の表面6aとが同じ高さに位置している。これにより、ワイヤ7aの端部にかかる応力を緩和してワイヤ7aのループ安定化を図ることができるので、ワイヤ7aの断線やワイヤ7aが他のフレームと短絡することを抑制することができる。また、絶縁体部4をモールドするときに、ワイヤ7aが流されることを抑制することができる。さらに、制御用集積回路に温度センサが搭載されている場合、温度センサと電力半導体素子との距離が近いので、温度センサの精度を向上することができる。

【0027】

また実施の形態1に係る電力半導体モジュール10は、第1のフレーム部5の第2の表面5bおよび第2のフレーム部6の第4の表面6bに接する絶縁シート11をさらに有する。これにより、第2の表面5bおよび第4の表面6bを通じて効率的に放熱することができる。

【0028】

さらに実施の形態1に係る電力半導体モジュール10の製造方法によれば、第3のフレーム部9に対して第1のフレーム部5および第2のフレーム部6を折り曲げるとともに、第1の端面5fおよび第2の端面6fが向かい合う方向に第3のフレーム部9が縮まる。これにより、第1の表面5aと平行な方向における電力半導体素子および制御用集積回路の距離を可能な限り短くし、かつ第1の表面と垂直な方向における電力半導体素子および制御用集積回路の距離を可能な限り短くすることができる。

【0029】

(実施の形態2)

図3および図5を参照して、実施の形態2に係る電力半導体モジュールの構成について説明する。実施の形態2に係る電力半導体モジュール10の構成は、第1のフレーム部5と絶縁シート11との間に銅からなるブロック部13が配置されている点において実施の形態1に係る電力半導体モジュールの構成と異なっており、他の点については同様である。

【0030】

実施の形態2に係る電力半導体モジュール10によれば、第1のフレーム部5の第2の表面5bおよび絶縁シート11に接して銅からなるブロック部13が配置されている。IGBT1およびFWD13が搭載されている第1のフレーム部5と、IC2が搭載されている第2のフレーム部6とは、第1のフレーム部の第1の表面5aの法線方向において同じ高さに位置している。第2のフレーム部6は絶縁体部4を介して絶縁シート11に接している。

【0031】

実施の形態2に係る電力半導体モジュール10は、第1のフレーム部5の第2の表面5bと接するブロック部13を有する。これにより、第2のフレーム部6を絶縁体部4内で折り曲げることなく、第1の表面5aに垂直な方向における第1のフレーム部5の第1の表面5aと第2のフレーム部6の第3の表面6aとの高さを同じ位置にすることができます。結果として、電力半導体素子および制御用集積回路を繋ぐワイヤ7aのループ安定化を

10

20

30

40

50

図ることができる。

**【0032】**

また実施の形態2に係る電力半導体モジュール10によれば、ブロック部13の材料は銅を含む。これにより、電力半導体素子が発生する熱を効率的に外部に拡散することができる。

**【0033】**

(実施の形態3)

図4および図5を参照して、実施の形態3に係る電力半導体モジュールの構成について説明する。実施の形態3に係る電力半導体モジュールの構成は、ブロック部13はセラミックを含んでいることによりDBC(Direct Bonded Copper)構造を有している点において実施の形態2に係る電力半導体モジュールの構成と異なっており、他の点については同様である。

10

**【0034】**

DBCとは2層の銅板の間にセラミックベースが配置されて当該銅板に接着されたものである。具体的には、実施の形態3に係る電力半導体モジュール10は、銅からなる第1のフレーム部5と銅から成る金属板12との間にブロック部が配置されており、当該ブロック部は、酸化アルミニウム( $Al_2O_3$ )や窒化アルミニウム(AlN)などのセラミックベース14からなる。IGBT1およびFWD13が搭載されている第1のフレーム部5と、IC2が搭載されている第2のフレーム部6とは、第1のフレーム部の第1の表面5aの法線方向において同じ高さに位置している。第2のフレーム部6は絶縁体部4を通して絶縁シート11に接している。

20

**【0035】**

実施の形態3に係る電力半導体モジュール10によれば、ブロック部13の材料はセラミックを含む。これにより、電力半導体モジュール10を軽量化することができる。

**【0036】**

(実施の形態4)

図6および図7を参照して、実施の形態4に係る電力半導体モジュールの構成について説明する。実施の形態4に係る電力半導体モジュールの構成は、第1のフレーム部5および第2のフレーム部6の少なくとも一方は、第1の表面5aと対面する側の絶縁体部4の上面4aから絶縁体部の外部に出ている点において実施の形態1に係る電力半導体モジュールの構成と異なっており、他の点については同様である。

30

**【0037】**

具体的には、実施の形態4に係る電力半導体モジュール10における第1のフレーム部5は絶縁体部4の内部において絶縁体部4の上面4a側に折れ曲がっている。第1のフレーム部5は絶縁体部4の上面4aを通って絶縁体部4の外部に出ている。同様に、第2のフレーム部6は絶縁体部4の内部において絶縁体部4の上面4a側に折れ曲がっている。第2のフレーム部6は絶縁体部4の上面4aを通って絶縁体部4の外部に出ている。なお、図6においては、第1のフレーム部5および第2のフレーム部6の各々が絶縁体部4の上面4aを通って外部に出ているが、本発明は、第1のフレーム部5および第2のフレーム部6のいずれか一方が絶縁体部4の上面4aを通っており、他方が絶縁体部4の左側面部4cまたは右側面部4dを通って絶縁体部4の外部に出ていても構わない。

40

**【0038】**

実施の形態4に係る電力半導体モジュール10によれば、第1のフレーム部5および第2のフレーム部6の少なくとも一方は、第1の表面5aと対面する絶縁体部4の上面4aから絶縁体部4の外部に出る。これにより、第1のフレーム部5および第2のフレーム部6と放熱フィン8との距離を長くすることで、第1のフレーム部5および第2のフレーム部6と放熱フィン8との間の絶縁性能を向上することができる。

**【0039】**

(実施の形態5)

図8および図9を参照して、実施の形態5に係る電力半導体モジュールの構成について

50

説明する。実施の形態 5 に係る電力半導体モジュールの構成は、第 1 のフレーム部 5 および第 2 のフレーム部 6 の少なくとも一方は、絶縁体部 4 から外部に露出した位置にコネクタピン 15 が有している点において実施の形態 1 に係る電力半導体モジュールの構成と異なっており、他の点については同様である。

#### 【 0 0 4 0 】

具体的には、実施の形態 5 に係る電力半導体モジュール 10 は、第 1 のフレーム部 5 および第 2 のフレーム部 6 の各々はコネクタピン 15 を有している。図 8 に示すように、コネクタピン 15 の一部は絶縁体部 4 の上面 4a から露出しており、コネクタピン 15 と端子部 5e とが接続されている。これにより、第 1 のフレーム部 5 と端子部 5e が電気的に接続される。同様に、コネクタピン 15 と端子部 6e とが接続されている。これにより、第 2 のフレーム部 6 と端子部 6e が電気的に接続される。端子部 5e および端子部 6e は絶縁体部 4 の上面 4a と交差する方向に伸長している。なお、図 6 においては、第 1 のフレーム部 5 および第 2 のフレーム部 6 の各々がコネクタピン 15 を有しているが、本発明は、第 1 のフレーム部 5 および第 2 のフレーム部 6 のいずれか一方がコネクタピン 15 を有しており、他方はコネクタピン 15 を有していないなくても構わない。

10

#### 【 0 0 4 1 】

実施の形態 5 に係る電力半導体モジュール 10 によれば、第 1 のフレーム部 5 および第 2 のフレーム部 6 の少なくとも一方は、絶縁体部 4 から外部に露出した位置にコネクタピン 15 を有している。第 1 のフレーム部 5 および第 2 のフレーム部 6 を端子なしフレームとし、後工程においてコネクタピン 15 を介して端子部 5e、6e を取り付けることにより、端子部の形状が異なる電力半導体モジュール 10 を効率的に製造することができる。また、第 1 のフレーム部 5 および第 2 のフレーム部 6 を端子がないフレームにすることと、千鳥配置などの多列フレームの形成が可能となる。

20

#### 【 0 0 4 2 】

##### ( 実施の形態 6 )

図 10 を参照して、実施の形態 6 に係る電力半導体モジュールの構成について説明する。実施の形態 6 に係る電力半導体モジュールの構成は、IC2 が 1 チップ化されている点において実施の形態 1 の構成と異なっており、他の点については同様である。

#### 【 0 0 4 3 】

具体的には、実施の形態 6 に係る電力半導体モジュール 10 は、第 2 のフレーム部 6 に搭載された 1 つの IC2 が複数の IGBT1 を制御可能に設けられている。従来は、上下に配置されている 2 つの IGBT1 を別の IC2 により制御していたため、お互いの動作のタイミングを制御することができなかった。実施の形態 6 に係る電力半導体モジュール 10 においては、上下に配置されている 2 つの IGBT1 を同時に動作させないように IC2 の内部で制御することができるのでインターロック（安全装置）として機能することができる。

30

#### 【 0 0 4 4 】

##### ( 実施の形態 7 )

図 11 ~ 図 13 を参照して、実施の形態 7 に係る電力半導体モジュールの構成について説明する。実施の形態 7 に係る電力半導体モジュールの構成は、第 2 のフレーム部 6 と絶縁シート 11 とが直接接触しておらず、第 2 のフレーム部 6 が第 1 のフレーム部 5 よりも絶縁体部 4 の上面 4a 側に位置する点において実施の形態 1 に係る電力半導体モジュールの構成と異なっており、他の点については同様である。また実施の形態 7 に係る電力半導体モジュールの製造方法は、実施の形態 1 の製造方法と同様である。

40

#### 【 0 0 4 5 】

実施の形態 7 に係る電力半導体モジュール 10 によれば、第 2 のフレーム部 6 の第 4 の表面 6b と絶縁シート 11 との間には絶縁体部 4 が配置されている。第 2 のフレーム部 6 は絶縁体部 4 の内部において第 1 のフレーム部 5 の第 1 の表面 5a に対して交差する方向に折れ曲がっている。IGBT1 および FWD13 が搭載されている第 1 のフレーム部 5 は、IC2 が搭載されている第 2 のフレーム部 6 よりも、絶縁シート 11 の近くに配置

50

れている。つまり、実施の形態 7 に係る電力半導体モジュールにおいては、第 1 の表面 5 a に対して垂直な方向における第 1 のフレーム部 5 の第 1 の表面 5 a と第 2 のフレーム部 6 の第 3 の表面 6 a との距離は同じでなくても構わない。

#### 【 0 0 4 6 】

電力半導体モジュール 10 は、図 11 に示すように絶縁シート 11 と接する金属板 12 は絶縁体部 4 の外部に露出していてもよい。好ましくは、図 12 に示すように当該金属板 12 および絶縁体部 4 の下面 4 b と接して放熱フィン 8 が設けられている。

#### 【 0 0 4 7 】

実施の形態 7 に係る電力半導体モジュール 10 によれば、第 2 のフレーム部 6 は、絶縁体部 4 の内部において第 1 の表面 5 a に対して交差する方向に折れ曲がっている。これにより、第 1 の表面 5 a に対して垂直な方向における第 1 のフレーム部 5 と第 2 のフレーム部 6 との距離を小さくすることができるので、電力半導体素子と制御用集積回路とを繋ぐワイヤ 7 a のループ安定化を図ることができる。結果として、ワイヤ 7 a の断線や短絡を抑制することができる。

10

#### 【 0 0 4 8 】

今回開示された実施の形態および実施例はすべての点で例示であって、制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味、および範囲内でのすべての変更が含まれることが意図される。

20

#### 【 符号の説明 】

#### 【 0 0 4 9 】

1 IGBT、2 IC、3 FWDi、4 絶縁体部、4 a 上面、4 b 下面、4 c, 4 d 側面、5 第 1 のフレーム部、5 a 第 1 の表面、5 b 第 2 の表面、5 e 端子部、5 f 第 1 の端面、6 第 2 のフレーム部、6 a 第 3 の表面、6 b 第 4 の表面、6 e 端子部、6 f 第 2 の端面、7 a, 7 b, 7 c, 7 d ワイヤ、8 放熱フィン、9 第 3 のフレーム、10 電力半導体モジュール、11 絶縁シート、12 金属板、13 ブロック部、14 セラミックベース、15 コネクタピン、20 フレーム。

【図1】

【図2】

【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

【図9】

( 义 1 2 )

【 図 1 3 】

【 図 1 0 】

【 図 1 1 】

【 図 1 4 】

【 図 15 】

【 図 1 6 】