(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5819027号

(P5819027)

(45) 発行日 平成27年11月18日(2015.11.18)

(24) 登録日 平成27年10月9日(2015.10.9)

(51) Int.Cl.

G06F 12/00 (2006.01)

F 1

G 06 F 12/00 5 6 4 D

請求項の数 19 (全 14 頁)

(21) 出願番号 特願2015-514160 (P2015-514160)

(86) (22) 出願日 平成25年5月22日 (2013.5.22)

(65) 公表番号 特表2015-520902 (P2015-520902A)

(43) 公表日 平成27年7月23日 (2015.7.23)

(86) 國際出願番号 PCT/US2013/042281

(87) 國際公開番号 WO2013/177315

(87) 國際公開日 平成25年11月28日 (2013.11.28)

審査請求日 平成27年1月27日 (2015.1.27)

(31) 優先権主張番号 13/477,642

(32) 優先日 平成24年5月22日 (2012.5.22)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVICES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンディベール、ビイ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・プレイス、メイル・ストップ

・68 (番地なし)

(74) 代理人 100108833

弁理士 早川 裕司

(74) 代理人 100111615

弁理士 佐野 良太

最終頁に続く

(54) 【発明の名称】メモリアクセス遅延トレーニングのための方法および装置

## (57) 【特許請求の範囲】

## 【請求項1】

データストローブ信号を受信するように構成されたメモリコントローラを備えるシステムであって、

前記メモリコントローラは、

データ入力の前記データストローブ信号と、クロック入力のイネーブル信号とを受信するように結合された第1の記憶回路と、

前記第1の記憶回路から受信した出力信号に基づき、前記イネーブル信号のアサーションが前記データストローブ信号内のプリアンブル指示と一致するまで、前記イネーブル信号の位相を調整するように構成されたトレーニングユニットと、

を含むトレーニング回路と、

前記データストローブ信号を受信するように結合された第1の入力と、前記イネーブル信号を受信するように結合された第2の入力とを有する論理ゲートであって、前記イネーブル信号がアサートされる場合に、前記データストローブ信号を渡すように構成されている論理ゲートと、を備える、

システム。

## 【請求項2】

前記イネーブル信号を前記第1の記憶回路の前記クロック入力に提供するように結合された第2の記憶回路であって、前記イネーブル信号を前記論理ゲートの前記第2の入力に提供するように結合された第2の記憶回路をさらに備え、前記第1および第2の記憶回路

はフリップフロップである、請求項 1 に記載のシステム。

【請求項 3】

入力クロック信号を受信するように結合された遅延ロックループ ( D L L ) であって、遅延を前記入力クロック信号に提供することに基づいて、出力クロック信号を生成するように構成された D L L をさらに備える、請求項 2 に記載のシステム。

【請求項 4】

前記トレーニングユニットは制御レジスタを含み、前記 D L L は、前記制御レジスタ内に格納された値に基づいて、遅延量を前記入力クロック信号に提供するように構成されている、請求項 3 に記載のシステム。

【請求項 5】

前記トレーニングユニットは、前記データストローブ信号に対する前記イネーブル信号の前記位相を検出するように構成されており、且つ、前記制御レジスタ内に格納された前記値を更新するように構成されている、請求項 4 に記載のシステム。

【請求項 6】

前記プリアンブルは、前記データストローブ信号内に複数の連続した論理ゼロを含み、前記トレーニングユニットは、前記イネーブル信号が前記プリアンブル内でアサートされるように、前記イネーブル信号の前記位相を調整するように構成されている、請求項 1 に記載のシステム。

【請求項 7】

前記トレーニングユニットは、トレーニング手順の開始に応じて、前記データストローブ信号の立ち上がりエッジがいつ受信されるかを判断するように構成されている、請求項 6 に記載のシステム。

【請求項 8】

前記トレーニングユニットは、前記データストローブ信号の立ち上がりエッジがいつ受信されるかの判断に応じて、

前記イネーブル信号の立ち上がりエッジが前記プリアンブルの終端と一致するまで、前記イネーブル信号の前記位相を増加するように調整すること、

調整における増加ごとに、制御レジスタ内に格納された値を更新することと、

前記イネーブル信号の前記立ち上がりエッジが前記プリアンブルの前記終端といつ一致するかの判断に応じて、前記値から所定量を減算すること、

を行うように構成されている、

請求項 7 に記載のシステム。

【請求項 9】

データおよび前記データストローブ信号を前記メモリコントローラに伝達するように結合されたメモリをさらに備え、前記メモリコントローラは、前記メモリから受信したデータを、前記データストローブ信号と同期化するように構成されている、請求項 1 に記載のシステム。

【請求項 10】

第 1 の記憶回路が、データ入力のデータストローブ信号と、クロック入力のイネーブル信号とを受信して、対応する出力信号を生成することと、

メモリから受信した前記データストローブ信号に対する前記イネーブル信号の位相を、前記イネーブル信号のアサーションが前記データストローブ信号内のプリアンブル指示と一致するまで調整することであって、遅延ロックループ ( D L L ) の遅延を調整することを含む、ことと、

前記遅延の指示をレジスタに格納することと、

を含む方法。

【請求項 11】

トレーニングユニットが前記プリアンブルを検出することをさらに含み、前記プリアンブルを検出することは、前記データストローブ信号内の複数の連続した論理ゼロを検出することを含む、請求項 10 に記載の方法。

10

20

30

40

50

**【請求項 1 2】**

前記イネーブル信号が前記プリアンブル内でアサートされるように、前記トレーニングユニットが、前記イネーブル信号の前記位相を調整することをさらに含む、請求項 1 1 に記載の方法。

**【請求項 1 3】**

前記トレーニングユニットが、トレーニング手順の開始に応じて、前記データストローブ信号の第 1 の立ち上がりエッジを検出することをさらに含む、請求項 1 1 に記載の方法。

**【請求項 1 4】**

前記イネーブル信号が、前記プリアンブルの終端で生じる前記データストローブ信号のエッジと一致するまで、前記トレーニングユニットが、前記イネーブル信号の前記位相を增加させるように調整することをさらに含む、請求項 1 3 に記載の方法。 10

**【請求項 1 5】**

前記イネーブル信号の前記位相を前記プリアンブルの前記終端と一致するように調整した後に、前記トレーニングユニットが、前記イネーブル信号の前記位相を前記プリアンブルの前記終端から前記プリアンブル内に調整することをさらに含む、請求項 1 4 に記載の方法。

**【請求項 1 6】**

前記イネーブル信号がアサートされる場合に、論理ゲートが、前記データストローブ信号をメモリコントローラ内の受信器に渡すことと、 20

前記イネーブル信号がアサートされない場合に、前記論理ゲートが、前記データストローブ信号の前記受信器への引き渡しを抑制することと、をさらに含む、請求項 1 0 に記載の方法。

**【請求項 1 7】**

トレーニングユニットが、前記出力信号に基づいて、前記データストローブ信号に対する前記イネーブル信号の前記位相を判断することと、

前記トレーニングユニットが、前記データストローブ信号に対する前記イネーブル信号の前記位相に基づいて、前記 D L L の前記遅延を調整することと、

第 2 の記憶回路が、クロック信号を前記 D L L から受信することと、前記 D L L から受信した前記クロック信号と同期して、前記イネーブル信号をアサートすること、 30

をさらに含む、請求項 1 0 に記載の方法。

**【請求項 1 8】**

前記調整中にメモリからの複数の連続読み取りを実行することをさらに含み、前記データストローブ信号は前記調整中に切り換わり続ける、請求項 1 0 に記載の方法。

**【請求項 1 9】**

メモリコントローラが、読み取り要求をメモリに提供することと、

前記メモリが、前記読み取り要求の受信に応じて、前記データストローブ信号を前記メモリコントローラに提供することと、

前記イネーブル信号を、前記プリアンブル内で生じた時点でアサートすることと、

をさらに含む、請求項 1 0 に記載の方法。 40

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、コンピュータシステムに関し、より詳細には、コンピュータシステム内のメモリの読み取りを同期化するのに用いられる信号に対する遅延時間のトレーニングに関する。

**【背景技術】****【0 0 0 2】**

メモリからデータを適切に読み出すために、データが有効な時間を判断することは重要なファクターである。コンピュータシステムの性能を最適化するために、この値を最小限 50

にすることが望ましい。メモリから受信したデータが読み出され得る最適な時間を判断するために、トレーニング手順が実行され得る。

【0003】

様々なタイプのダブルデータレート (DDR) メモリ (例えば、DDR、DDR2、およびDDR3など) に対して、読み取り操作中に、データストローブ信号がデータと共にメモリから返される場合がある。データストローブ信号は、メモリコントローラ内の受信器でデータを同期化するために使用され得るソース同期クロック信号であることに加えて、そのデータが有効であることを示す。正確なタイミングを確実にするためのデータストローブ信号のトレーニングが、システム動作の開始時に実行され得る。

【0004】

DDRデータストローブのトレーニングを実行するための一つ方法は、シードとして知られている低動作周波数での読み取りの実行で始まる。次いで、トレーニング手順は、シードとして知られている第1の周波数で返されたデータをデータストローブ信号が観察するのを可能にする最適時間を判断するために、一連の読み取りを実行し得る。シードは、コンピュータシステムの設計段階において、研究所で実施された特性評価に基づき判断され得る。トレーニングは、データストローブ信号を有効にする最適時間が判断されるまで、異なる周波数で実施され得る。元の周波数で結果として生じるトレーニングされた最適時間は、次のさらに高い周波数での後続のトレーニングに対するおおよその開始時間を計算するために使用され得る。結果として生じる第2のトレーニングされた値は、第3のさらに高い周波数などでのトレーニングに対するおおよその開始時間を計算するために使用され得る。さらに高い周波数でのトレーニングに対する開始時間を決定するために低周波数でトレーニングされた時間を使用する方法は、通常の操作で使用される全ての周波数がトレーニングされるまで、複数回繰り返され得る。

10

【発明の概要】

【課題を解決するための手段】

【0005】

データストローブ信号を有効にするための遅延をトレーニングする様々な方法および装置の実施形態が開示される。一実施形態では、システムは、データストローブ信号を受信するように構成されたメモリコントローラを含む。メモリコントローラは、トレーニング回路を含む。トレーニング回路は、データ入力のデータストローブ信号とクロック入力のイネーブル信号を受信するように結合された第1の記憶回路と、前記第1の記憶回路から受信した出力信号に基づき、イネーブル信号のアサーションがデータストローブ信号内のプリアンブル指示と一致するまで、イネーブル信号の位相を調整するように構成されたトレーニングユニットと、を含む。

30

【0006】

一実施形態では、方法は、メモリから受信したデータストローブ信号に対するイネーブル信号の位相を調整することを含む。この位相は、イネーブル信号のアサーションがデータストローブ信号内のプリアンブル指示と一致するまで調整され得る。この調整は、遅延ロックループ (DLL) の遅延を調整することによって達成され得る。本方法は、遅延指示をレジスタに格納することをさらに含む。

40

【0007】

メモリサブシステムの一実施形態は、メモリコントローラに結合されたメモリを含む。メモリコントローラは、読み取り要求をメモリに送信するように構成されている。メモリは、読み取り要求に応じて、データとデータストローブ信号とを、メモリコントローラに提供するように構成されている。メモリコントローラは、イネーブル信号のアサーションがデータストローブ信号内のプリアンブル指示と一致するまで、データストローブ信号に対するイネーブル信号の位相を調整するように構成されたトレーニングユニットを含む。前記調整することは、遅延ロックループ (DLL) の遅延を調整することを含む。メモリコントローラは、遅延指示をレジスタに格納するようにさらに構成されている。

【0008】

50

本開示の他の態様は、以下の詳細な説明と、添付の図面とを参照することで明らかになる。添付の図面の簡単な説明を以下に示す。

【図面の簡単な説明】

【0009】

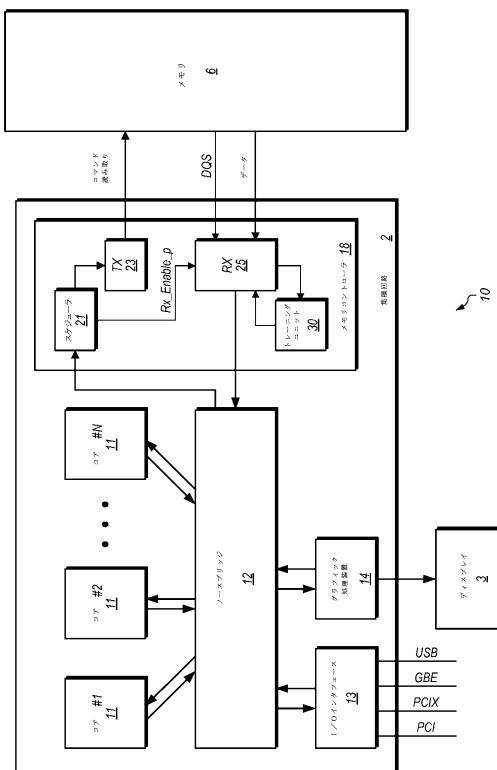

【図1】処理装置と、ディスプレイと、周辺機器用バスと、メモリと、メモリコントローラとを含むシステムのブロック図である。

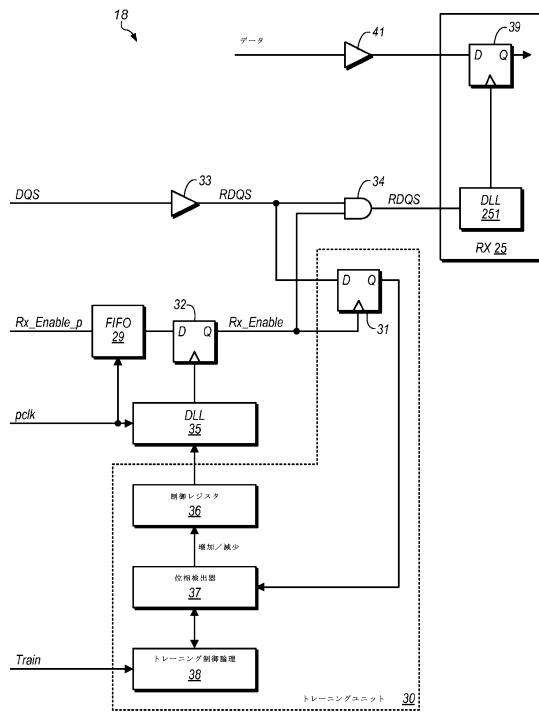

【図2】トレーニングユニットを含むメモリコントローラの一実施形態のブロック図である。

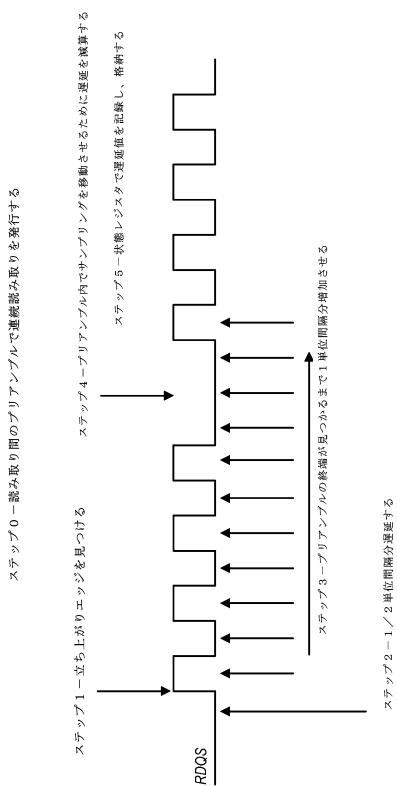

【図3】データストローブ信号に対するイネーブル信号の遅延をトレーニングするための方法の一実施形態を示すタイミング図である。

10

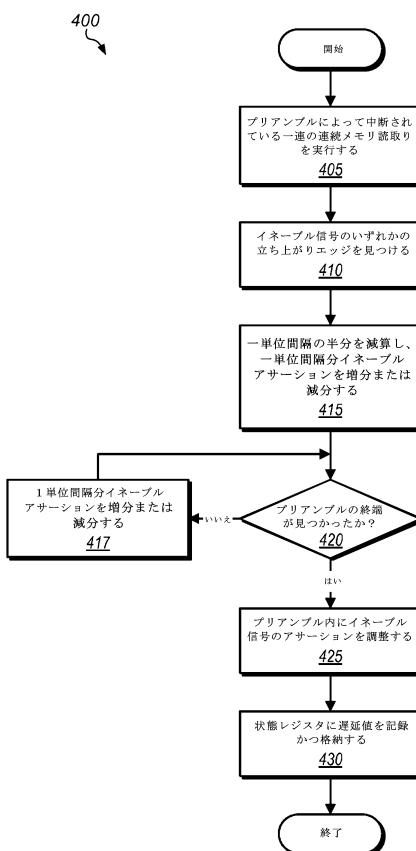

【図4】データストローブ信号に対するイネーブル信号の遅延をトレーニングするための方法の一実施形態を示すフロー図である。

【図5】コンピュータ可読キャリア媒体の一実施形態のブロック図である。

【発明を実施するための形態】

【0010】

本発明は、様々な修正および代替形式を受け入れる余地があるが、図面では、本発明の特定の実施形態を一例として示し、本明細書において詳細に説明する。しかし、図面およびそれに関連する説明は、本発明を開示する特定の形式に限定することを意図しておらず、それとは逆に、本発明は、添付の請求項によって定義されるような本発明の精神ならびに範囲に含まれる、全ての修正、均等物および代替手段を包含することが理解されるべきである。

20

【0011】

図1は、コンピュータシステム10の一実施形態のブロック図である。図示した実施形態では、コンピュータシステム10は、メモリ6に結合された集積回路( I C )2を含む。コンピュータシステム10は、例えばラップトップ、デスクトップまたはサーバーコンピュータなどの従来型のコンピュータシステムや、例えばハンドヘルドコンピューティング装置( 例えば、携帯電話またはスマートフォン )、デジタルテレビ、タブレットコンピューティング装置などの様々な他のタイプのコンピューティング装置を含み得る。図示した実施形態では、I C 2は、いくつかのプロセッサコア11を有するシステムオンチップ( S o C )である。I C 2の実施形態は、中央処理装置( C P U )、グラフィック処理装置( G P U )、加速処理装置( A P U )、アプリケーションプロセッサ、デジタル信号プロセッサ( D S P )などを含み得る。様々な実施形態では、プロセッサコアの数は、わずか1つであってもよいし、I Cダイ上の実装に適するだけの数であってもよい。マルチコアの実施形態では、プロセッサコア11は、互いに同一( すなわち、ホモジニアスマルチコア )であってもよいし、1つ以上のコアが他のコアと異なって( すなわち、ヘテロジニアスマルチコア )いてもよい。各プロセッサコア11は、1つ以上の実行ユニット、キャッシュメモリ、スケジューラ、分岐予測回路などを含んでもよい。さらに、各プロセッサコア11は、メモリ6へのアクセス要求をアサートするように構成されてもよく、メモリ6は、コンピュータシステム10におけるメインメモリとして機能し得る。かかる要求は、読み取り要求および/または書き込み要求を含んでもよく、当初は各プロセッサコア11からノースブリッジ12によって受信され得る。メモリ6へのアクセス要求は、ある命令の実行に応じて開始されてもよく、プリフェッチ操作に応じて開始されてもよい。

30

【0012】

図示した実施形態では、ノースブリッジ12は、I C 2の様々な機能ユニット間の通信の経路指定および制御を提供し得る。このため、ノースブリッジ12は、異なる機能ユニットを互いに結合する( 例えば、メモリアクセス要求中に、何れか1つのプロセッサコア11をメモリコントローラ18に結合する )ように構成された1つ以上のクロスバーユニットを含んでもよい。さらに、ノースブリッジ12は、I C 2の動作中に、電力消費対性能を最適化するために使用される様々な電力管理機能を実装し得る。

40

【0013】

50

図示した実施形態では、I/Oインターフェース13は、ノースブリッジ12に結合されている。I/Oインターフェース13は、コンピュータシステム10におけるサウスブリッジ装置として機能してもよい。いくつかの異なるタイプの周辺機器用バスが、I/Oインターフェース13に結合されてもよい。この特定の実施例では、バスタイプは、Peripheral Component Interconnect (PCI) バス、PCI-Extended (PCI-X)、ギガビットイーサネット (登録商標) (GBE) バスおよびユニバーサルシリアルバス (USB) を含む。しかし、これらのバスタイプは例示であり、多数の他のバスタイプがI/Oインターフェース13に結合されてもよい。周辺機器は、周辺機器用バスの一部または全部に結合されてもよい。かかる周辺機器は、キーボード、マウス、プリンタ、スキャナ、ジョイスティックや他のタイプのゲームコントローラ、媒体記録装置、外部記憶装置、ネットワークインターフェースカードなどを含むが、これらに限定されない。対応する周辺機器用バスを介してI/Oユニット13に結合され得る周辺機器の少なくともいくつかは、直接メモリアクセス (DMA) を用いてメモリアクセス要求をアサートし得る。(読み取りおよび書き込み要求を含み得る)これらの要求は、I/Oインターフェース13を介してノースブリッジ12に伝達され得る。

#### 【0014】

図示した実施形態では、I C 2は、コンピュータシステム10のディスプレイ3に結合されるグラフィック処理装置14を含む。ディスプレイ3は、フラットパネルLCD (液晶ディスプレイ)、プラズマディスプレイ、CRT (ブラウン管) または任意の他の適切なディスプレイタイプであり得る。GPU 14は、様々なビデオ処理機能を実行し、処理情報を、視覚情報としての出力のためにディスプレイ3に提供し得る。

#### 【0015】

図示した実施形態におけるメモリコントローラ18は、ノースブリッジ12に結合されており、いくつかの実施形態では、実際に、ノースブリッジ12の構成要素であってもよい。メモリコントローラ18は、ノースブリッジ12から伝達されたメモリ要求を受信し得る。(プリフェッчを含む)読み取り要求に応じてメモリ6からアクセスされたデータは、メモリコントローラ18によって、ノースブリッジ12を介して要求エージェントに伝達され得る。メモリコントローラ18は、書き込み要求に応じて、要求および書き込まれるデータの両方を、ノースブリッジ12を介して要求エージェントから受信し得る。複数のメモリアクセス要求がある時間において保留中である場合に、メモリコントローラ18は、これらの要求間を調停 (arbitrate) し得る。

#### 【0016】

メモリコントローラ18は、メモリ6へのデータの書き込みをサポートする機能も含むが、その機能については、便宜上、ここでは示していないことに留意されたい。

#### 【0017】

図示した実施形態におけるメモリ6は、一実施形態では、複数のメモリモジュールとして実装され得る。各メモリモジュールは、メモリモジュール上に実装された1つ以上のメモリデバイス (例えば、メモリチップ) を含み得る。別の実施形態では、メモリ6は、I C 2が実装され得るマザーボードまたは他のキャリア上に設けられた1つ以上のメモリデバイスを含み得る。さらに別の実施形態では、メモリ6の少なくとも一部は、I C 2のダイ上に実装され得る。前述した様々な実施態様の組合せを有する実施形態も可能であり、検討され得る。メモリ6は、動作中にI C 2とともに用いられるランダムアクセスメモリ (RAM) を実現するために使用され得る。

#### 【0018】

図示した実施形態では、メモリ6は、いくつかの異なるタイプのダブルデータレート (DDR) ダイナミックRAM (DRAM) のうちの1つとして実装される。かかるタイプのDDR DRAMは、オリジナルDDR標準DRAM、DDR2 DRAMおよびDDR3 DRAMを含む。メモリ6は、将来の規格のDDR DRAMとして実装され得ることも考えられる。特定の規格に関わらず、メモリ6は、メモリコントローラ18からの読み取り要求に応じて、要求されたデータと共に、データストローブ信号、DQSを返し

10

20

30

40

50

得る。データストローブ信号は、事実上、メモリコントローラ 18 の受信器 25 でデータを同期化するために使用されるソース同期クロック信号である。メモリ 6 からデータが返されていない場合には、データストローブ信号は、アイドルであってもよいし、トライステート (tri-state) であってもよい。いくつかの事例では、データストローブ信号は、読み取りが実行されていない場合、トライステート状態にされ得る（すなわち、高インピーダンス状態に置かれる）。トライステート状態の間にデータストローブ信号がサンプリングされる場合には、誤った読み取りや受信器 25 内での遅延ロックループ (DLL) の内部操作の破損を含む、予測できない挙動を引き起こし得る。しかし、以下で説明する方法および装置の実施形態では、データストローブ信号がトライステート状態である場合には、データストローブ信号のサンプリングを回避し得る。

10

#### 【0019】

図示した実施形態では、メモリコントローラ 18 は、読み取りコマンドをノースブリッジ 12 から受信するために結合されたスケジューラ 21 を含む。スケジューラ 21 は、メモリ 6 への伝送のために様々な読み取りコマンドをスケジューリングするように構成されている。いくつかの実施形態では、スケジューラ 21 は、競合する読み取りコマンドの調停を実行するように構成されてもよい。読み取りコマンドは、メモリ 6 への伝送のために送信器 23 に転送され得る。加えて、スケジューラ 21 は、読み取りコマンドに応じてメモリ 6 からのデータの受信を可能にするために、受信イネーブル信号 (Rx\_enable) を受信器 25 に提供し得る。図示した実施形態では、受信器 25 は、データストローブ信号のメモリ 6 からの伝送と合わせるために、イネーブル信号のアサーションを保留するいくつかのバッファリングおよびタイミング回路を含み得る。これにより、誤ったデータが受信器 25 によって受信されるのを防ぎ得る。受信器 25 内のイネーブル信号のアサーションのタイミングは、トレーニングユニット 30 によって実行されるトレーニング手順によって判断され得る。トレーニングユニット 30 および対応するトレーニング手順については、以下でさらに詳細に説明する。

20

#### 【0020】

ここで、図 2 を参照すると、メモリコントローラ 18 の一実施形態のブロック図が示されている。この図では、メモリコントローラ 18 の全ての構成要素が示されておらず、従って、様々な実施形態では（前述のものを含む）他の構成要素が含まれ得ることに留意されたい。

30

#### 【0021】

図示した実施形態では、メモリコントローラ 18 は、メモリ 6 から伝達されたデータを受信するために結合された受信器 25 を含む。データは、メモリ 6 から伝達されたデータストローブ信号に基づいて、受信したデータストローブ信号 (RDQS) と同期化され得る（受信したデータストローブ信号は、メモリ 6 から提供されたデータストローブ信号と実質的に同一の信号であり得るが、ここでは、バッファ 33 の存在のために別々に参照される）。受信したデータストローブ信号は、イネーブル信号 (Rx\_enable) を用いて、（本実施形態において AND ゲートとして実装された）論理ゲート 34 を介してゲートされ得る。イネーブル信号がアサートされる場合には、受信したデータストローブは、受信器 25 の遅延ロックループ (DLL) 251 に渡すために有効にされる。次いで、DLL 251 は、着信データを同期化するために、対応するクロック信号をフリップフロップ 39（またはフリップフロップのグループ）に提供し得る。一方、イネーブル信号がアサートされない場合には、受信したデータストローブは DLL 251 に提供されない。これにより、受信器 25 における意図しないデータの受信を抑制する。イネーブル信号がアサート解除される場合には、トライステートのデータストローブ信号のサンプリングが回避される。このことは、上述したように、誤った動作が発生する可能性を防ぎ得る。従って、イネーブル信号がいつアサートされ、いつアサート解除されるかという制御は、データストローブ信号が、正しい動作を保証する適切なタイミング（すなわち、図 3 に示すパターンのように、データストローブ信号が、高状態と低状態との間でアクティブに切り換わっているタイミング）でサンプリングされることを確実にし得る。

40

50

## 【0022】

イネーブル信号は、D L L 35に提供されたクロック信号(p c l k)と同じ領域から受信したイネーブル信号(R x \_ e n a b l e \_ p)に基づく。図示した実施形態では、受信したイネーブル信号は、先入れ先出しメモリ(F I F O)29に提供される。F I F O 29の読み取りおよび書き込みポインタはp c l k信号と同期化される。p c l k信号は、メモリコントローラ18内の位相ロックループ(P L L)によって生成されてもよく、その内部の動作を同期化するために使用される。F I F O 29の出力は、記憶回路(本実施形態では、フリップフロップ32)に結合される。また、F I F O 29の出力は、クロック信号をD L L 35から受信するために結合される。図示した実施形態では、D L L 35は、p c l k信号を入力クロックとして受信するように結合され、p c l k信号の遅延バージョンをフリップフロップ32に提供するように構成されている。その結果、論理ゲート34に提供されたR x \_ e n a b l e信号は、D L L 35からの出力としてのp c l k信号の遅延バージョンと同期化され得る。10

## 【0023】

読み取り中、イネーブル信号は、特定の時点でアサートされ得る。イネーブル信号があまりにも早くアサートされることにより、受信したデータストローブ信号がD L L 25 1に渡るのを可能にする場合には、受信器25は、誤ったデータを受信する場合がある。イネーブル信号のアサートが遅すぎる場合には、メモリ6から返されるデータは、受信器25に受信されない場合がある。従って、イネーブル信号のアサーションに最適な時間を判断するために、トレーニングが実施され得る。図示した実施形態では、メモリコントローラ18は、トレーニングユニット30を含む。トレーニングユニット30は、フリップフロップ31と、位相検出器37と、トレーニング制御論理38と、を含む。20

## 【0024】

図示した実施形態では、R D Q S信号は、フリップフロップ31のデータ入力で受信される。フリップフロップ31のクロック入力は、フリップフロップ32から出力されたイネーブル信号出力を受信するように結合されている。フリップフロップ31の出力は、位相検出器37に提供される。位相検出器37は、フリップフロップ31から受信した出力信号に基づき、受信したデータストローブ信号、R D Q Sに対する、イネーブル信号、R x \_ e n a b l eの位相を判断し得る。この実施形態では、F I F O 29は、R x \_ e n a b l e信号がプリアンブルに応じてアサートされるように、論理高(logic h)をフリップフロップ32のD入力に提供し得る。したがって、フリップフロップ31によるR D Q S信号のサンプリングを生じさせ得るプリアンブルを生成する読み取りとなる。30

## 【0025】

イネーブル信号のトレーニングは、トレーニング制御論理38の制御下で実施され得る。トレーニングを実施するために、トレーニング制御論理38に提供されたトレーニング信号(T r a i n)がアサートされ得る。トレーニング制御論理38は、トレーニングアルゴリズムの実行中に位相検出器37に指示し得る。位相検出器37によって提供される情報は、トレーニングアルゴリズムにおいて実行される様々なステップの判断において、トレーニング制御論理38によって使用され得る。40

## 【0026】

図示した実施形態における位相検出器37の出力は、制御レジスタ36に格納された値を増加または減少させる1つ以上の信号を含む。制御レジスタ38の出力は、フリップフロップ32に提供されるクロック信号を生成するためにp c l k信号の遅延を設定するのに使用される、D L L 35に提供される指示であってよい。したがって、位相検出器37は、イネーブル信号と、受信したデータストローブ信号との間の位相関係を効果的に制御するのに使用され得る。より詳細には、図示した実施形態における位相検出器37は、制御レジスタ36に格納された値を増加させることにより、D L L 32によって提供される遅延を増加し得る。D L Lによって提供される遅延の減少は、制御レジスタ36に格納された値を減少させる位相検出器37によって実行され得る。一般に、D L L 32に50

よって提供される遅延の変化は、受信したデータストローブ信号と、イネーブル信号との間の位相関係を変化させ得る。トレーニング中、位相検出器 37 は、アルゴリズムのいくつかの部分においてフリップフロップ 31 によって提供される出力信号と、アルゴリズムの他の部分におけるトレーニング制御論理 38 からの直接制御とに基づいて、D L L 32 の遅延を変化させ得る。

#### 【0027】

図 3 は、トレーニングユニット 30 によって実行され得るトレーニングアルゴリズムの一実施形態を示すタイミング図である。トレーニングは、トレーニング制御論理 38 へ train 信号をアサートすることにより開始され得る。また、アルゴリズムのステップ 0 では、連続読み取りが、プリアンブルによって中断されている読み取りとともに、トレーニング手順の実行時に開始され得る。図示の例では、読み取りは、論理 1 と論理 0 との間の受信したデータストローブ信号のサイクルによって示される。図示の例におけるプリアンブルは、論理 1 の間のいくつか（図の例では 3 つ）の連続した論理 0 によって示される。一般に、データ読み取り操作は、限定数のデータビットを受信するバースト内で行われてよく、その後、データストローブ信号は、トライステート状態にされ得る（すなわち、高インピーダンス状態に置かれる）。読み取りバーストごとに準備するために、各読み取り操作は、データストローブが 10w になる期間に先行され得る。この期間はプリアンブルとして知られている。読み取り操作が連続して生じる場合には、着信データストローブは、クロックのように見える波形を示し、プリアンブルは生成されない。より詳細には、バーストは、図に示すように、プリアンブルによって中断される。バーストは、データストローブ信号がトライステート状態になるのを防ぐために、継続期間において十分に短い場合がある。一方、読み取りの間の期間がプリアンブルの継続期間よりも長い場合には、データストローブ信号は、メモリによってトライステート状態にされ得る。

10

#### 【0028】

アルゴリズムのステップ 1 は、受信したデータストローブ信号の立ち上がりエッジを見つけることである（この代わりに、立ち下がりエッジを見つける実施形態も可能であり、検討されることに留意されたい）。これは、イネーブル信号を循環させ、イネーブル信号と（循環している）受信したデータストローブ信号との間の位相差を測定して、位相差がゼロになるまで調整することによって達成され得る。立ち上がりエッジが見つかると、トレーニング制御論理 38 は、位相検出器 37 に対して、データストローブ信号の 2 分の 1 の単位間隔を D L L 36 の遅延から減算するように指示する。本明細書では、単位間隔は、受信したデータストローブ信号の 2 分の 1 の期間であってよい。従って、データストローブ信号が 50% のデューティサイクルを有する場合には、単位間隔は、当該デューティサイクルと同等であり得る。

20

#### 【0029】

受信したデータストローブ信号に対するイネーブル信号の位相をデータストローブ信号の 2 分の 1 の単位間隔だけ調整した後に、トレーニング制御論理 38 は、位相検出器 37 に対して、プリアンブルの終端が見つかるまで、イネーブル信号の位相を 1 単位間隔だけ増加するように調整する（ステップ 3）のを開始するように指示し得る。図の例では、位相調整は、増加によって実行される。しかし、同じ目的を達成するためには、増加の代わりに減少も使用され得る。位相の増加調整ごとに、位相関係が、トレーニング制御論理 38 に報告されてもよく、トレーニング制御論理 38 は、測定値の履歴を保持および監視し得る。その履歴に基づき、トレーニング制御論理 38 は、イネーブル信号が、受信したデータストローブ信号の第 1 のポストプリアンブルサイクルの第 1 の立ち下がりエッジと一致するタイミングを判断し得る。

30

#### 【0030】

トレーニング制御論理 38 は、プリアンブルの終端が検出されたことを判断すると、位相検出器 37 に対して、イネーブル信号の位相がプリアンブル内で生じるまで遅延を減算する（ステップ 4）ように調整することを指示し得る。一実施形態では、イネーブル信号は、プリアンブルのおおよその中間点に位置合わせされ得る。この調整が生じると、位相

40

50

検出器 37 は、受信したデータストローブ信号に対するイネーブル信号の位相の指標を、制御レジスタ 36 に記録し得る。このとき、トレーニングが完了する。ミッション（すなわち、通常）モードでの将来の動作のために、メモリ 6 からのデータの 1 つ以上の連続読み取り中に、イネーブル信号のアサーションが、データストローブ信号の第 1 の立ち上がりエッジよりも前のプリアンブル中に生じ得る。

#### 【 0 0 3 1 】

イネーブル信号の立ち上がりエッジをプリアンブル内の点と一致させることによって、温度および電圧変動に起因したドリフトを許容するためにより多くのマージンが提供され得る。これにより、メモリに対するインターフェースが、より高速な周波数で動作されることを可能にし得る。前述のトレーニングアルゴリズムは、異なる周波数での複数の反復を必要としないこと、および、「シード値」としても知られている、事前特性化された開始条件も必要としないことにさらに留意されたい。これにより、トレーニング手順が、従来の方法よりも確実に、かつ、短時間で実行されることを可能にし得る。

10

#### 【 0 0 3 2 】

ここで図 4 を参照すると、データストローブ信号に対するイネーブル信号の遅延をトレーニングするための方法の一実施形態を示すフロー図が表されている。方法 400 は、図 1 および図 2 に関連して前述したハードウェアの実施形態を使用して実行され得るが、他のハードウェアの実施形態で本方法を実行することも可能であり、検討されることに留意されたい。

20

#### 【 0 0 3 3 】

方法 400 は、プリアンブルによって中断されている読み取りとともに、複数の一連の連続メモリ読み取りを実行すること（ブロック 405）によるトレーニングの開始で始まる。読み取りは、データストローブ信号と同期化されてもよく、データストローブ信号は、プリアンブル（例えば、1 と 0 の交互に入れ替わるサイクル間の複数の連続した 0）を含む。読み取りは、連続、次いでプリアンブル、その後、別の連続などのように実行されてもよい。

20

#### 【 0 0 3 4 】

トレーニング手順中に、データストローブ信号のエッジ（本実施例では、立ち上がりエッジ）が、データストローブの立ち上がりエッジとの位相差がゼロになるまでイネーブル信号の立ち上がりエッジの位相を調整することによって、見つけられ得る（ブロック 410）。この時点でイネーブル信号が調整される立ち上がりエッジは、データストローブ信号の任意の立ち上がりエッジであり得る。

30

#### 【 0 0 3 5 】

データストローブ信号の立ち上がりエッジの位置決めに応じて、イネーブル信号の位相は、2 分の 1 の単位間隔分減算されてもよく、次いで、一単位間隔分増加するように調整され得る（ブロック 415）。調整は、増加または減少を含み得る。プリアンブルの終端が見つからなかった（ブロック 420, いいえ）場合には、ブロック 415 の調整が継続する。プリアンブルの終端が見つかった（ブロック 420, はい）場合には、プリアンブル内のポイントにイネーブル信号のアサーションを置くために、最終位相調整が行われ得る（ブロック 425）。一実施形態では、最終位相調整において、イネーブル信号のアサーションを、プリアンブルの中間点または中間点の近くに置き得る。最終位相調整が完了した後に、対応する遅延値の指示が制御レジスタに格納される（ブロック 430）。この遅延値は、通常動作中に、遅延ロックループの遅延を設定するために使用され得る。

40

#### 【 0 0 3 6 】

次に図 5 を参照すると、システム 10 を表すデータベース 505 を含むコンピュータアクセス可能記憶媒体 500 のブロック図が示されている。一般的に言えば、コンピュータアクセス可能記憶媒体 500 は、命令および / またはデータをコンピュータに提供するために、使用中にコンピュータによってアクセス可能な任意の持続性（non-transitory）記憶媒体を含み得る。例えば、コンピュータアクセス可能記憶媒体 500 は、磁気または光媒体などの記憶媒体（例えば、ディスク（固定もしくは取り外し可能）、

50

テープ、CD-ROM、DVD-ROM、CD-R、CD-RW、DVD-R、DVD-RW、Blu-Rayなど)を含み得る。記憶媒体は、例えばユニバーサルシリアルバス(USB)インターフェースなどの周辺インターフェースを介してアクセス可能な、RAM(例えば、シンクロナスダイナミックRAM(SDRAM)、ダブルデータレート(DDR)、DDR2、DDR3など)SDRAM、低電力DDR(例えばLDDR2など)SDRAM、Rambus DRAM(RDRAM)、スタティックRAM(例えばSRAMなど)など)、ROM、フラッシュメモリ、不揮発性メモリ(例えばフラッシュメモリ)などの、揮発性または不揮発性メモリ媒体をさらに含み得る。記憶媒体は、微小電気機械システム(MEMS)、ならびに、ネットワークおよび/または無線リンクなどの通信媒体を介してアクセス可能な記憶媒体を含み得る。

10

### 【0037】

一般に、コンピュータアクセス可能記憶媒体500で実行される、システム10および/またはその部分を表すデータ505は、システム10を含むハードウェアを製造するために、直接または間接に、プログラムによって読み取られて使用可能なデータベースまたは他のデータ構造であり得る。例えば、データベース505は、VerilogまたはVHDLなどの高水準設計用言語(HDL)でのハードウェア機能性の動作レベル記述またはレジスタ転送レベル(RTL)記述であり得る。記述は、ゲートのリストを含むネットリストを合成ライブラリから生成するために、記述を合成し得る合成ツールによって読み取られ得る。ネットリストは、システム10を含むハードウェアの機能性も表すゲートの組を含む。ネットリストは、次いで、マスクに適用される幾何学形状を記述するデータセットを生成するために、設置され、経路指定され得る。マスクは、次いで、システム10に対応する半導体回路または複数の回路を製造するための様々な半導体製造ステップで使用され得る。あるいは、コンピュータアクセス可能記憶媒体500上のデータベース505は、必要に応じて、ネットリスト(合成ライブラリ有りまたは無し)もしくはデータセット、または、グラフィックデータシステム(GDS)IIデータであり得る。

20

### 【0038】

コンピュータアクセス可能記憶媒体500は、システム10の表現を含むが、他の実施形態では、必要に応じて、I C 2、エージェントの任意の組(例えば、処理コア11、I/Oインターフェース13、ノースブリッジ12など)、または、エージェントの部分を含む、システム10の任意の部分の表現を含み得る。

30

### 【0039】

本発明は、特定の実施形態について説明してきたが、実施形態は例示であること、および、発明の範囲はこのように限定されないことが理解されるであろう。説明した実施形態に対する任意の変形、修正、追加および改善が可能である。これらの変形、修正、追加および改善は、以下の特許請求の範囲内で詳述するように、本発明の範囲内に含まれ得る。

【 図 1 】

## 【図2】

( 3 )

【 4 】

【図5】

---

フロントページの続き

(74)代理人 100162156

弁理士 村雨 圭介

(72)発明者 グレン エイ. デアース

アメリカ合衆国 01450 マサチューセッツ州、グロットン、スクアナコック ドライブ 2

0

(72)発明者 ウォーレン アール. アンダーソン

アメリカ合衆国 01581 マサチューセッツ州、ウェストボロー、チャウンシー ストリート

7

(72)発明者 アンワー ピー. カシェム

アメリカ合衆国 02141 マサチューセッツ州、ケンブリッジ、パークシャー ストリート

100、#2

(72)発明者 リチャード ダブリュ. リーヴス

アメリカ合衆国 01581 マサチューセッツ州、ウェストボロー、ベルクナップ ストリート

9

(72)発明者 エドアルド プレー<sup>テ</sup>

アメリカ合衆国 02474 マサチューセッツ州、アーリントン、ワイマン ストリート 24

(72)発明者 ジェラルド アール. タルボット

アメリカ合衆国 01742 マサチューセッツ州、コンコード、ホールデン ウッド ロード

280

審査官 寺谷 大亮

(56)参考文献 特開2013-065086 (JP, A)

国際公開第2008/000059 (WO, A1)

特開2011-197789 (JP, A)

特開2012-248082 (JP, A)

(58)調査した分野(Int.Cl. , DB名)

G06F 12/00

G11C 11/4076