(19) **日本国特許庁(JP)**

# (12)特 許 公 報(B2)

(11)特許番号

特許第5655655号 (P5655655)

(45) 発行日 平成27年1月21日(2015.1.21)

(24) 登録日 平成26年12月5日(2014.12.5)

(51) Int.Cl. F L

**HO3F** 1/07 (2006.01) HO3F 1/07 **HO3F** 3/24 (2006.01) HO3F 3/24

請求項の数 3 (全 12 頁)

(21) 出願番号 特願2011-61756 (P2011-61756) (22) 出願日 平成23年3月18日 (2011.3.18)

(65) 公開番号 特開2012-199706 (P2012-199706A) (43) 公開日 平成24年10月18日 (2012.10.18)

審査請求日 平成26年1月8日(2014.1.8)

||(73)特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

||(74)代理人 100089118

弁理士 酒井 宏明

(72) 発明者 青木 信久

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 白井 孝治

最終頁に続く

# (54) 【発明の名称】ドハティ増幅装置

## (57)【特許請求の範囲】

# 【請求項1】

電源端子へ印加される電圧に応じてRF入力信号を増幅する主増幅器と、

電源端子へ印加される電圧に応じて前記RF入力信号のピーク成分を増幅する副増幅器と、

前記主増幅器の出力端に接続された伝送線路と、

前記伝送線路の出力端と前記副増幅器の出力端に接続され、前記伝送線路の出力信号と前記副増幅器の出力信号とを合成する合成器と、

前記合成器の出力端に接続された出力負荷と

を備え、

10

前記主増幅器の電源端子へ印加される電圧が前記副増幅器の電源端子へ印加される電圧よりも低く設定されるとともに、前記伝送線路のインピーダンス値が前記出力負荷のインピーダンス値を2倍した値よりも小さく設定されることを特徴とするドハティ増幅装置。

# 【請求項2】

前記主増幅器の物理的サイズを規定するパラメータと前記副増幅器の物理的サイズを規定するパラメータとが同一であることを特徴とする請求項1に記載のドハティ増幅装置。

### 【請求項3】

前記主増幅器の物理的サイズを規定するパラメータが前記副増幅器の物理的サイズを規定するパラメータのm倍又は1/m倍であり、前記主増幅器の電源端子へ印加される電圧が前記副増幅器の電源端子へ印加される電圧のn倍である場合に、mおよびnは、(1+

m・n) / m < 2 の関係が成立するように設定されることを特徴とする請求項 1 に記載のドハティ増幅装置。

【発明の詳細な説明】

### 【技術分野】

## [0001]

本発明は、ドハティ増幅装置に関する。

#### 【背景技術】

# [0002]

近年、周波数の利用効率を向上させるための変調方式として、OFDM(Orthogonal Frequency Division Multiplexing)等の線形変調方式が広く用いられている。OFDM等の線形変調方式により変調された信号は、ピーク電力対平均電力比(PAPR:Peak to Average Power Ratio)が高くなる傾向がある。このため、最近では、PAPRが高い信号を高効率で増幅する増幅装置が種々検討されている。例えば、このような増幅装置として、ドハティ増幅装置が知られている。

#### [0003]

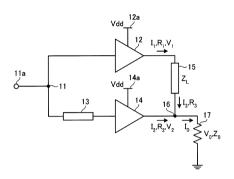

図3は、一般的なドハティ増幅装置の構成例を示す図である。同図に示すように、ドハティ増幅装置は、分配器11、キャリア増幅器12、位相調整器13、ピーク増幅器14、インピーダンス変換器15、合成器16および出力負荷17を有する。

#### [0004]

分配器11は、入力端子11aから入力されるRF(Radio Frequency)信号を2つのRF信号に分岐し、一方のRF信号をキャリア増幅器12へ分配するとともに、他方のRF信号を位相調整器13へ分配する。キャリア増幅器12は、電源端子12aへ印加される電圧に応じて分配器11から入力されるRF信号を増幅し、増幅後のRF信号をインピーダンス変換器15へ出力する。

# [0005]

位相調整器 1 3 は、分配器 1 1 から入力される R F 信号の位相を調整し、調整後の R F 信号をピーク増幅器 1 4 へ出力する。ピーク増幅器 1 4 は、電源端子 1 4 a へ印加される電圧に応じて分配器 1 1 から入力される R F 信号のピーク成分を増幅し、増幅後の R F 信号を合成器 1 6 へ出力する。インピーダンス変換器 1 5 は、 / 4 の電気長を有する伝送線路であり、キャリア増幅器 1 2 の出力端に接続される。合成器 1 6 は、インピーダンス変換器 1 5 の出力端とピーク増幅器 1 4 の出力端とに接続され、インピーダンス変換器 1 5 からの R F 信号とピーク増幅器 1 4 からの R F 信号とを合成する。出力負荷 1 7 は、合成器 1 6 の出力端に接続される。出力負荷 1 7 のインピーダンス値 2 。は固定である。

#### [00006]

図3に示したドハティ増幅装置では、キャリア増幅器12の電源端子12aへ印加される電圧Vddがピーク増幅器14の電源端子14aへ印加される電圧Vddと同一となるように設定される。そして、ドハティ増幅装置では、キャリア増幅器12がAB級又はB級で動作し、ピーク増幅器14がB級又はC級で動作する。すなわち、キャリア増幅器12が飽和状態となるまではキャリア増幅器12のみが主増幅器として動作し、キャリア増幅器12が飽和状態となると、ピーク増幅器14が副増幅器として動作する。

# [0007]

ここで、ドハティ増幅装置の出力電力に対する効率は、それぞれの増幅器が飽和状態で動作した時のインピーダンス変換器15から合成器16へ出力される電流 I3と合成器16から出力負荷17へ出力される電流 I3との比 に応じて変動する。特に、ドハティ増幅装置の効率は、 <0.5のときに良好となることが知られている。

# [0008]

このため、 < 0 . 5 を実現する従来技術として、キャリア増幅器とピーク増幅器とのデバイスサイズを異ならせる手法が提案されている。この従来技術では、例えば、キャリア増幅器のエミッタ面積をピーク増幅器のエミッタ面積よりも小さく設定することによって、キャリア増幅器とピーク増幅器とのデバイスサイズを異ならせる。

10

20

30

40

#### 【先行技術文献】

## 【特許文献】

[0009]

【特許文献1】特開2007-81800号公報

【特許文献 2 】特開 2 0 0 7 - 6 4 5 0 号公報

【特許文献3】特開2005-322993号公報

【特許文献4】特開2006-166141号公報

【発明の概要】

【発明が解決しようとする課題】

[0010]

しかしながら、キャリア増幅器とピーク増幅器とのデバイスサイズを異ならせる従来技術では、インピーダンス変換器のインピーダンスが増大し、その結果、効率が劣化するという問題がある。

## [0011]

開示の技術は、上記に鑑みてなされたものであって、インピーダンス変換器のインピーダンスの増加に起因した効率の劣化を回避することができるドハティ増幅装置を提供することを目的とする。

#### 【課題を解決するための手段】

#### [0012]

本願の開示するドハティ増幅装置は、主増幅器と、副増幅器と、伝送線路と、合成器と、出力負荷とを有する。主増幅器は、電源端子へ印加される電圧に応じてRF入力信号を増幅する。副増幅器は、電源端子へ印加される電圧に応じて前記RF入力信号のピーク成分を増幅する。 伝送線路は、前記主増幅器の出力端に接続される。合成器は、前記伝送線路の出力端と前記副増幅器の出力端に接続され、前記伝送線路の出力信号と前記副増幅器の出力信号とを合成する。そして、前記主増幅器の電源端子へ印加される電圧が前記副増幅器の電源端子へ印加される電圧よりも低く設定されるとともに、前記伝送線路のインピーダンス値が前記出力負荷のインピーダンス値を2倍した値よりも小さく設定される。

#### 【発明の効果】

# [0013]

本願の開示するドハティ増幅装置の一つの態様によれば、インピーダンス変換器のイン ピーダンスの増加に起因した効率の劣化を回避することができるという効果を奏する。

【図面の簡単な説明】

### [0014]

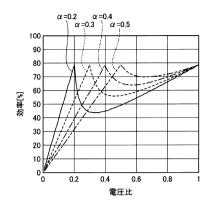

【図1】図1は、一般的なドハティ増幅装置における効率特性を示す図である。

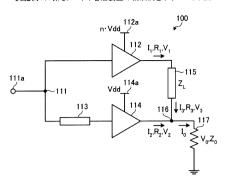

【図2】図2は、実施例1に係るドハティ増幅装置の構成例を示すブロック図である。

【図3】図3は、一般的なドハティ増幅装置の構成例を示す図である。

【発明を実施するための形態】

## [0015]

まず、本願の開示するドハティ増幅装置の実施例を説明する前に、一般的なドハティ増幅装置の問題点について説明する。図 1 は、図 3 に示した一般的なドハティ増幅装置における効率特性を示す図である。図 1 では、横軸が出力負荷 1 7 での、ドハティ増幅器が出力可能な最大電圧と出力電圧の電圧比を表し、縦軸が効率(%)を表す。言い換えると、横軸が出力電力を表し、縦軸が効率(%)を表す。また、図 1 では、ドハティ増幅器が最大電力を出力した時のインピーダンス変換器 1 5 から合成器 1 6 へ出力される電流  $\Gamma_3$  と、合成器 1 6 から出力負荷 1 7 へ出力される電流  $\Gamma_3$  との比 を変化させたときの効率特性を示す。

#### [0016]

図1に示すように、 が0.5であるとき、効率が極大値となる電圧比は0.5である。そして、 が0.5よりも小さくなるに連れて、効率が極大値となる電圧比は小さくなる。これは、 が0.5よりも小さくなるに連れて、PAPRが比較的に高い信号に対す

10

20

30

40

10

20

30

40

50

る増幅の効率が向上することを意味する。例えば、PAPRが比較的に高い信号の電圧比が 0 . 2 であるものとする。この場合には、 が 0 . 5 であるとき、変調波が平均電力を出力した場合の効率は約 3 0 %に留まるが、 が 0 . 2 であるとき、効率は極大値である約 7 9 %まで向上する。このように、ドハティ増幅装置の効率は、 が 0 . 5 よりも小さいときに良好となる。

### [0017]

ここで、 が 0 . 5 よりも小さい状態を実現するために、図 3 に示した従来のドハティ増幅装置におけるキャリア増幅器 1 2 とピーク増幅器 1 4 とのデバイスサイズを異ならせたものとする。例えば、キャリア増幅器 1 5 のエミッタ面積がピーク増幅器 1 4 のエミッタ面積よりも小さく設定されるものとする。すると、インピーダンス変換器 1 5 のインピーダンス Z L が増大することを以下に証明する。

[0018]

ピーク増幅器とキャリア増幅器が飽和動作の状態を考える。まず、 が、次式(1)で 定義される。

$= I_3 / I_0 \cdots (1)$

ただし、I<sub>3</sub>は、インピーダンス変換器 1 5 から合成器 1 6 へ出力される電流 I<sub>0</sub>は、合成器 1 6 から出力負荷 1 7 へ出力される電流

[0019]

出力負荷17では、次式(2)が成立する。

$V_{0} = I_{0} \cdot Z_{0} \cdot \cdot \cdot (2)$

ただし、V。は、出力負荷17の電圧

Z<sub>0</sub>は、出力負荷17のインピーダンス値

[0020]

式(1)および式(2)から次式(3)が求められる。

$I_3 = \cdot V_0 / Z_0 \cdots (3)$

[0021]

インピーダンス変換器 1 5 の入力端の電力と出力端の電力とが等しく、飽和動作状態では、出力電圧はピーク増幅器、キャリア増幅器共等しいと考えられるので、 $V_1 = V_2$ となり、次式(4)が成立する。

$V_{1}^{2}/R_{1} = V_{2}^{2}/R_{1} = I_{3}^{2} \cdot R_{3}$  · · · (4)

ただし、V₁は、キャリア増幅器12の出力端の電圧

V<sub>2</sub>は、ピーク増幅器14の出力端の電圧

R 1 は、キャリア増幅器 1 2 の出力端のインピーダンス

R<sub>3</sub>は、インピーダンス変換器15の出力端のインピーダンス

[0022]

また、インピーダンス変換器15の性質から次式(5)が求められる。

$R_1 \cdot R_3 = Z_L^2 \cdot \cdot \cdot (5)$

[0023]

式(4)および式(5)から次式(6)が求められる。

$Z_L = V_2 / I_3 \cdots (6)$

[0024]

式 (3)、式 (6) および  $V_0 = V_2$  の関係から次式 (7) が求められる。

$Z_{\perp} = 1 / \cdot Z_{0} \cdot \cdot \cdot (7)$

[0025]

[0026]

このように、キャリア増幅器とピーク増幅器とのデバイスサイズを異ならせる従来の手

法では、インピーダンス変換器のインピーダンスが増大する傾向にある。そして、インピーダンス変換器のインピーダンスの増大に伴って、ドハティ増幅装置の効率が劣化する。

#### 【実施例1】

## [0027]

次に、実施例1に係るドハティ増幅装置100の構成について説明する。図2は、実施例1に係るドハティ増幅装置の構成例を示すブロック図である。同図に示すように、実施例1に係るドハティ増幅装置100は、分配器111、キャリア増幅器112、位相調整器113、ピーク増幅器114、インピーダンス変換器115、合成器116および出力負荷117を有する。分配器111は、入力端子111aから入力されるRF信号を2つのRF信号に分岐し、一方のRF信号をキャリア増幅器112へ分配するとともに、他方のRF信号を位相調整器113へ分配する。

#### [0028]

キャリア増幅器 1 1 2 は、増幅素子として電界効果トランジスタ(FET:Field effect transistor)を含む増幅器である。キャリア増幅器 1 1 2 は、電源端子 1 1 2 a へ印加される電圧に応じて分配器 1 1 1 から入力されるRF信号を増幅し、増幅後のRF信号をインピーダンス変換器 1 1 5 へ出力する。キャリア増幅器 1 1 2 の電源端子 1 1 2 a は、直流電源に接続されるとともに、キャリア増幅器 1 1 2 内部のFETに接続される。キャリア増幅器 1 1 2 の電源端子 1 1 2 a へ印加される電圧は、ドレイン電圧とも呼ばれる。また、キャリア増幅器 1 1 2 の電源端子 1 1 2 a へ印加される電圧は、ピーク増幅器 1 1 4 の電源端子 1 1 4 a へ印加される電圧と異なるように設定される。本実施例では、キャリア増幅器 1 1 2 の電源端子 1 1 2 a へ印加される電圧は、ピーク増幅器 1 1 4 の電源端子 1 1 4 a へ印加される電圧 V d d の n 倍に設定される。

#### [0029]

位相調整器 1 1 3 は、分配器 1 1 1 から入力される R F 信号の位相を調整し、調整後の R F 信号をピーク増幅器 1 1 4 へ出力する。

## [0030]

ピーク増幅器 1 1 4 は、キャリア増幅器 1 1 2 と同様に増幅素子としてFETを含む増幅器である。ピーク増幅器 1 1 4 は、電源端子 1 1 4 a へ印加される電圧に応じて分配器 1 1 1 から入力される R F 信号を、 R F 信号の電力が閾値を越えた時に増幅し、増幅後の R F 信号を合成器 1 1 6 へ出力する。また、ピーク増幅器 1 1 4 の電源端子 1 1 4 a は、直流電源に接続されるとともに、ピーク増幅器 1 1 4 内部のFETに接続される。ピーク増幅器 1 1 4 の電源端子 1 1 4 a へ印加される電圧は、ドレイン電圧とも呼ばれる。

#### [0031]

インピーダンス変換器 1 1 5 は、 / 4 の電気長を有する伝送線路であり、キャリア増幅器 1 1 2 の出力端に接続される。

#### [0032]

合成器 1 1 6 は、インピーダンス変換器 1 1 5 の出力端とピーク増幅器 1 1 4 の出力端とに接続され、インピーダンス変換器 1 1 5 からの R F 信号とピーク増幅器 1 1 4 からの R F 信号とを合成する。出力負荷 1 1 7 は、合成器 1 1 6 の出力端に接続される。出力負荷 1 1 7 のインピーダンス Z 。は固定である。

# [0033]

本実施例のドハティ増幅装置100では、キャリア増幅器112がAB級又はB級で動作し、ピーク増幅器114がB級又はC級で動作する。すなわち、キャリア増幅器112が飽和状態となるまではキャリア増幅器112のみが主増幅器として動作し、キャリア増幅器112が飽和状態となると、ピーク増幅器114が副増幅器として動作する。

# [0034]

特に、本実施例のドハティ増幅装置100では、キャリア増幅器112の電源端子11 2aへ印加される電圧がピーク増幅器114の電源端子114aへ印加される電圧よりも低く設定される。これとともに、インピーダンス変換器115のインピーダンス値が出力 負荷117のインピーダンス値を2倍した値よりも小さく設定される。これにより、イン 10

20

30

40

10

20

30

40

50

ピーダンス変換器 1 1 5 のインピーダンス値が不用意に増大することを回避することができ、インピーダンス変換器 1 1 5 のインピーダンス値の増加に起因した効率の劣化を回避することができる。

[0035]

ここで、本実施例のドハティ増幅装置100がインピーダンス変換器115のインピーダンス値の増加に起因した効率の劣化を回避することができる理由について説明する。

[0036]

まず、 が、上記の式(1)と同様に、次式(8)で定義される。

$= I_3 / I_0 \cdots (8)$

ただし、I<sub>3</sub>は、インピーダンス変換器 1 1 5 から合成器 1 1 6 へ出力される電流 I<sub>0</sub>は、合成器 1 1 6 から出力負荷 1 1 7 へ出力される電流

[0037]

出力負荷117では、次式(9)が成立する。

$V_0 = I_0 \cdot Z_0 \cdot \cdot \cdot (9)$

ただし、V。は、出力負荷117の電圧

Zηは、出力負荷117のインピーダンス値

[0038]

式(8)および式(9)から次式(10)が求められる。

$I_{3} = \cdot V_{0} / Z_{0} \qquad \cdot \cdot \cdot \qquad (10)$

[0039]

式 (10) および  $V_0 = V_3$  の関係から次式 (11) が求められる。

$R_3 = V_3 / I_3 = V_0 / (V_0 / Z_0 \cdot ) = 1 / \cdot Z_0 \cdot \cdot \cdot (11)$

ただし、R<sub>3</sub>は、インピーダンス変換器115の出力端のインピーダンス

[0040]

また、インピーダンス変換器115の入力端の電力と出力端の電力とが等しいので、次式(12)が成立する。

$V_{1}^{2}/R_{1} = I_{3} \cdot V_{3} \cdot \cdot \cdot (12)$

[0041]

また、インピーダンス変換器115の性質から次式(13)が求められる。

$R_1 \cdot R_3 = Z_1^2 \cdot \cdot \cdot (13)$

【 0 0 4 2 】 式( 1 3 )に式( 1 1 )を適用することにより、次式( 1 4 )が求められる。

$Z_{\perp}^{2} = R_{1} \cdot (1/) \cdot Z_{0} \cdot \cdot \cdot (14)$

[0043]

式(14)に式(12)を適用することにより、次式(15)が求められる。

$Z_{\perp}^{2} = V_{\perp}^{2} / (I_{3} \cdot V_{3}) \cdot (1/) \cdot Z_{0} \cdot \cdot \cdot (15)$

[0044]

式(15)に式(10)および $V_3 = V_0$ の関係を適用することにより、次式(16)が求められる。

$Z_{\perp}^{2} = (1/2) \cdot Z_{0}^{2} \cdot V_{1}^{2} / V_{0}^{2} \cdot \cdot \cdot (16)$

[ 0 0 4 5 ]

式(16)から次式(17)が求められる。

$Z_L = (1/) \cdot Z_0 \cdot V_1 / V_0 \cdot \cdot \cdot (17)$

[0046]

キャリア増幅器 1 1 2 の出力端の電圧  $V_1$  が電源端子 1 1 2 a へ印加される電圧 n ・  $V_d$  。 に比例すると仮定すると、次式( 1 8 )が成立する。

$V_1 = x \cdot n \cdot V_{d \cdot d} \qquad \cdots \qquad (18)$

ただし、×は、比例定数

[0047]

また、ピーク増幅器114の出力端の電圧が電源端子114aへ印加される電圧Vddd

に比例すると仮定すると、次式(19)が成立する。

$V_2 = x \cdot V_{d \cdot d} \qquad \cdots \qquad (19)$

[0048]

式(18)および式(19)から次式(20)が求められる。

$V_1 = n \cdot V_2 = n \cdot V_0 \qquad \cdot \cdot \cdot \qquad (20)$

[0049]

式(17)に式(20)を適用することにより次式(21)が求められる。

$Z_{\perp} = (1/) \cdot n \cdot Z_{0} \cdot \cdot \cdot (21)$

[0050]

本実施例では、インピーダンス変換器115のインピーダンス値 Z \_ が出力負荷117のインピーダンス値 Z 。を2倍した値よりも小さく設定されるので、次式(22)が成立する。

$Z_{\perp} < 2 Z_{0} \qquad \cdots \qquad (22)$

[0051]

式(21)および式(22)から次式(23)が求められる。

$n < 2 \cdot \cdot \cdot (23)$

[0052]

式(23)から < 0.5のときに次式(24)が求められる。

n < 1 · · · (24)

[0053]

式(24)は、キャリア増幅器 1 1 2 の電源端子 1 1 2 a へ印加される電圧  $n \cdot V_{dd}$  がピーク増幅器 1 1 4 の電源端子 1 1 4 a へ印加される電圧  $V_{dd}$  よりも低く設定された場合に、効率の劣化を回避することができることを意味する。

[0054]

このように、本実施例では、キャリア増幅器112の電源端子112aへ印加される電圧がピーク増幅器114の電源端子114aへ印加される電圧よりも低く設定される。また、インピーダンス変換器115のインピーダンス値が出力負荷117のインピーダンス値を2倍した値よりも小さく設定される。これにより、インピーダンス変換器115のインピーダンス値が不用意に増大することを回避することができ、インピーダンス変換器115のインピーダンス値の増加に起因した効率の劣化を回避することができる。

[0055]

また、本実施例では、キャリア増幅器112の物理的サイズを規定するパラメータとピーク増幅器114の物理的サイズを規定するパラメータとが同一である。本実施例のキャリア増幅器112およびピーク増幅器114は、増幅素子としてFETを含む増幅器である。したがって、キャリア増幅器112のゲート幅、ゲート長、ゲート数またはパッケージ内FET数と、ピーク増幅器114のゲート幅、ゲート長、ゲート数またはパッケージ内FET数とが同一である。言い換えると、キャリア増幅器112のデバイスサイズとピーク増幅器114のデバイスサイズとピーク増幅器114のデバイスサイズとが同一である。本実施例では、キャリア増幅器112のデバイスサイズとピーク増幅器114のデバイスサイズとが同一である場合でもインピーダンス変換器115のインピーダンス値が不用意に増大することを回避することができる。

[0056]

以下、本実施例のドハティ増幅装置100が、キャリア増幅器112のデバイスサイズとピーク増幅器114のデバイスサイズとが同一である場合でも、インピーダンス変換器115のインピーダンス値が不用意に増大することを回避することができる理由について説明する。

[0057]

まず、キャリア増幅器 1 1 2 の電力を求める。キャリア増幅器 1 1 2 の電力 I  $_1$  ・ V  $_1$  は、次式 ( 2 5 )を用いて求められる。

$I_{1} \cdot V_{1} = I_{3} \cdot V_{3} \qquad \cdot \cdot \cdot \qquad (25)$

20

10

30

40

```

[0058]

```

式(10)および $V_3 = V_0$ の関係を式(25)に適用することにより、次式(26)が求められる。

$I_1 \cdot V_1 = (V_0^2 / Z_0) \cdot \cdot \cdot \cdot (26)$

[0059]

次いで、ピーク増幅器 1 1 4 の電力を求める。ピーク増幅器 1 1 4 の電力  $\mathbb{I}_2$  ・  $\mathbb{V}_2$  は、次式 (27)を用いて求められる。

$I_2 \cdot V_2 = I_2 \cdot V_0 \qquad \cdot \cdot \cdot \qquad (27)$

[0060]

また、Ⅰっに関して次式(28)が成立する。

$I_{2} = I_{0} - I_{3} \cdots (28)$

[0061]

式(28)に式(8)を適用することにより次式(29)が求められる。

$I_{2} = (1 - ) \cdot I_{0} \cdot \cdot \cdot (29)$

[0062]

また、 I n は、次式 (30)を用いて求められる。

$I_0 = V_0 / Z_0 \cdots (30)$

[0063]

式(29)および式(30)から次式(31)が求められる。

$I_2 = V_0 / Z_0 \cdot (1 - ) \cdot \cdot \cdot (31)$

[0064]

式(27)に式(31)を適用することにより、次式(32)が求められる。

$I_2 \cdot V_2 = V_0^2 / Z_0 \cdot (1 - ) \cdot \cdot \cdot (32)$

[0065]

式(26)および式(32)からキャリア増幅器112の電力とピーク増幅器114の電力との比を求めると、次式(33)が導出される。

$I_1 \cdot V_1 / (I_2 \cdot V_2) = / (1 - ) \cdot \cdot \cdot (33)$

[0066]

$I_1 \cdot V_1 / (I_2 \cdot V_2) = n \cdot V_{dd} / V_{dd} = n \cdot \cdot \cdot (34)$

[0067]

式(33)および式(34)から次式(35)が求められる。

$/(1 - ) = n \cdot \cdot \cdot (35)$

[0068]

式(21)に式(35)を適用することにより次式(36)が求められる。

$Z_{\perp} = (1 + n) \cdot Z_{0} \qquad \cdots \qquad (36)$

[0069]

式(36)および式(22)から次式(37)が求められる。

n < 1 · · · (37)

[ 0 0 7 0 ]

式(37)は、キャリア増幅器112の電源端子112aへ印加される電圧 $n \cdot V_{dd}$ をピーク増幅器114の電源端子114aへ印加される電圧 $V_{dd}$ よりも低く設定することにより、電源端子112aの物理的サイズを規定するパラメータと電源端子114aの物理的サイズを規定するパラメータとが同一である場合でも、インピーダンス変換器115のインピーダンス値の増大を抑えることができることを示す。

50

10

20

30

# [0071]

なお、本実施例では、キャリア増幅器 1 1 2 およびピーク増幅器 1 1 4 が増幅素子としてFETを含む場合について説明したが、キャリア増幅器 1 1 2 およびピーク増幅器 1 1 4 がFETに代えてバイポーラトランジスタを含んでいてもよい。この場合には、キャリア増幅器 1 1 2 のエミッタ面積またはパッケージ内バイポーラトランジスタ数と、ピーク増幅器 1 1 4 のエミッタ面積またはパッケージ内バイポーラトランジスタ数とが同一となる。また、この場合には、キャリア増幅器 1 1 2 の電源端子 1 1 2 a へ印加される電圧およびキャリア増幅器 1 1 4 の電源端子 1 1 4 a へ印加される電圧は、バイポーラトランジスタのコレクタ端子へ接続されコレクタ電圧とも呼ばれる。

#### [0072]

上述してきたように、本実施例のドハティ増幅装置100では、キャリア増幅器112の電源端子112aへ印加される電圧がピーク増幅器114の電源端子114aへ印加される電圧よりも低く設定される。また、インピーダンス変換器115のインピーダンス値が出力負荷117のインピーダンス値を2倍した値よりも小さく設定される。このため、本実施例によれば、インピーダンス変換器115のインピーダンス値が不用意に増大することを回避することができ、インピーダンス変換器115のインピーダンス値の増加に起因した効率の劣化を回避することができる。

### [0073]

また、本実施例のドハティ増幅装置100では、キャリア増幅器112の物理的サイズを規定するパラメータとピーク増幅器114物理的サイズを規定するパラメータとが同一である。このため、本実施例によれば、キャリア増幅器112の電源端子112aへ印加される電圧n・V d d をピーク増幅器114の電源端子114aへ印加される電圧V d d よりも低く設定することにより、キャリア増幅器112の物理的サイズを規定するパラメータとピーク増幅器114物理的サイズを規定するパラメータとが同一である場合にも、インピーダンス変換器115のインピーダンス値の増大を抑えることができる。その結果、インピーダンス変換器115のインピーダンス値の増加に起因した効率の劣化をより効率的に回避することができる。

#### 【実施例2】

# [0074]

上記実施例1では、キャリア増幅器112の物理的サイズを規定するパラメータとピーク増幅器114の物理的サイズを規定するパラメータとが同一である場合について説明した。しかしながら、キャリア増幅器112の物理的サイズを規定するパラメータとピーク増幅器114の物理的サイズを規定するパラメータとが異なっていてもよい。そこで、以下では、このような場合を実施例2として説明する。

# [0075]

本実施例のドハティ増幅装置では、キャリア増幅器112の電源端子112aへ印加される電圧がピーク増幅器114の電源端子114aへ印加される電圧のn倍に設定される。 これとともに、インピーダンス変換器115のインピーダンス値が出力負荷117のインピーダンス値を2倍した値よりも小さく設定される。

### [0076]

さらに、本実施例のドハティ増幅装置では、実施例1のドハティ増幅装置100と異なり、キャリア増幅器112の物理的サイズを規定するパラメータとピーク増幅器114の物理的サイズを規定するパラメータとが異なる。

# [0077]

具体的には、キャリア増幅器 1 1 2 の物理的サイズを規定するパラメータがピーク増幅器 1 1 4 の物理的サイズを規定するパラメータのm倍である。例えば、キャリア増幅器 1 1 2 のゲート幅、ゲート数またはパッケージ内 F E T 数がピーク増幅器 1 1 4 のゲート幅、ゲート数またはパッケージ内 F E T 数のm倍である。また、物理的サイズを規定するパラメータがゲート長の場合は、キャリア増幅器 1 1 2 のゲート長がピーク増幅器 1 1 4 のゲート長の1/m倍の場合である。このため、キャリア増幅器 1 1 2 における飽和電力およ

10

20

30

40

びピーク増幅器 1 1 4 における飽和電力は、電源端子 1 1 2 a へ印加される電圧 n ・m・V d d および電源端子 1 1 4 a へ印加される電圧 V d d にそれぞれ比例する。すなわち、次式 (38)が成立する。

$I_{1} \cdot V_{1} / (I_{2} \cdot V_{2}) = n \cdot m \cdot V_{dd} / V_{dd} = n \cdot m$  (38)

[0078]

式(33)および式(38)から次式(39)が求められる。

$/(1 - ) = n \cdot m \cdot \cdot \cdot (39)$

[0079]

式(21)に式(39)を適用することにより次式(40)が求められる。

$Z_{\perp} = (1 + n \cdot m) / m \cdot Z_{0} \qquad \cdots \qquad (40)$

[0800]

式(40)および式(22)から次式(41)が求められる。

$(1 + n \cdot m) / m < 2 \cdot \cdot \cdot (41)$

[0081]

式(41)は、キャリア増幅器112の物理的サイズを規定するパラメータとピーク増幅器114の物理的サイズを規定するパラメータとが異なる場合に、インピーダンス変換器115のインピーダンス値が出力負荷117のインピーダンス値を2倍した値よりも小さく設定できるため、インピーダンス変換器115のインピーダンス値の増大を抑えることができることを示す。

[0082]

上述してきたように、本実施例のドハティ増幅装置100では、キャリア増幅器112の物理的サイズを規定するパラメータとピーク増幅器114の物理的サイズを規定するパラメータとが異なる。このため、本実施例によれば、インピーダンス変換器115のインピーダンス値が出力負荷117のインピーダンス値を2倍した値よりも小さく設定できるため、インピーダンス変換器115のインピーダンス値の増大を抑えることができ、インピーダンス変換器115のインピーダンス値の増加に起因した効率の劣化をより効率的に回避することができる。

【符号の説明】

[0083]

100 ドハティ増幅装置

1 1 1 分配器

1 1 1 a 入力端子

1 1 2 キャリア増幅器

1 1 2 a 電源端子

1 1 3 位相調整器

1 1 4 ピーク増幅器

1 1 4 a 電源端子

1 1 5 インピーダンス変換器

1 1 6 合成器

117 出力負荷

20

10

30

# 【図1】

一般的なドハティ増幅装置における効率特性を示す図

# 【図2】

実施例1に係るドハティ増幅装置の構成例を示すブロック図

# 【図3】

一般的なドハティ増幅装置の構成例を示す図

# フロントページの続き

(56)参考文献 特開2007-081800(JP,A)

特表2010-536224(JP,A)

特開2006-166141(JP,A)

米国特許出願公開第2006/0145757(US,A1)

(58)調査した分野(Int.CI., DB名)

H03F 1/00~ 3/72