(12)发明专利申请

(10)申请公布号 CN 110428774 A

(43)申请公布日 2019.11.08

(21)申请号 201910652678.0

(22)申请日 2019.07.19

(71)申请人 深圳市华星光电半导体显示技术有限公司

地址 518132 广东省深圳市光明新区公明

街道塘明大道9-2号

(72)发明人 蔡振飞

(74)专利代理机构 深圳翼盛智成知识产权事务

所(普通合伙) 44300

代理人 黄威

(51)Int.Cl.

G09G 3/3225(2016.01)

权利要求书1页 说明书4页 附图2页

(54)发明名称

像素驱动电路和显示面板

(57)摘要

本申请提供了一种像素驱动电路和显示面板。所述像素驱动电路包括复位单元、补偿单元和驱动单元；所述复位单元的第一输入端接入复位电压，第二输入端接入第一控制信号，输出端连接所述驱动单元，所述复位单元根据所述第一控制信号为驱动单元提供复位信号；所述补偿单元的输入端接入数据信号，输出端连接所述驱动单元，所述补偿单元根据所述数据信号为驱动单元提供补偿信号；所述驱动单元的第一输入端连接所述复位单元，第二输入端连接所述补偿单元，第三输入端接入第二控制信号，输出端连接第二电源电压。本申请提供的像素驱动电路和显示面板能够简化现有技术中的像素驱动电路的结构和时序。

1. 一种像素驱动电路,其特征在于,所述像素驱动电路包括复位单元、补偿单元和驱动单元;其中,

所述复位单元的第一输入端接入复位电压,第二输入端接入第一控制信号,输出端连接所述驱动单元,所述复位单元根据所述第一控制信号为驱动单元提供复位信号;

所述补偿单元的输入端接入数据信号,输出端连接所述驱动单元,所述补偿单元根据所述数据信号为驱动单元提供补偿信号;

所述驱动单元的第一输入端连接所述复位单元,第二输入端连接所述补偿单元,第三输入端接入第二控制信号,输出端连接第二电源电压。

2. 根据权利要求1所述的像素驱动电路,其特征在于,所述驱动单元包括第一薄膜晶体管、第二薄膜晶体管和第三薄膜晶体管;其中,

所述第一薄膜晶体管的源极连接第一电源电压,栅极接入第二控制信号,漏极连接所述第二薄膜晶体管的源极;

所述第二薄膜晶体管的栅极连接所述复位信号,漏极连接所述第三薄膜晶体管的源极;

所述第三薄膜晶体管的栅极接入第二控制信号,漏极连接待驱动的有机发光二极管的输入端。

3. 根据权利要求2所述的像素驱动电路,其特征在于,所述第一薄膜晶体管、第二薄膜晶体管和第三薄膜晶体管为N型薄膜晶体管。

4. 根据权利要求3所述的像素驱动电路,其特征在于,所述补偿单元包括第四薄膜晶体管和存储电容;其中,

所述第四薄膜晶体管的源极连接所述数据信号,栅极连接所述第一控制信号,漏极连接所述存储电容的一个极板和所述第二薄膜晶体管的漏极;

所述存储电容的另一个极板连接所述第二薄膜晶体管的栅极。

5. 根据权利要求4所述的像素驱动电路,其特征在于,所述第四薄膜晶体管为N型薄膜晶体管。

6. 根据权利要求4所述的像素驱动电路,其特征在于,所述第一薄膜晶体管、第二薄膜晶体管和第三薄膜晶体管的宽长比相等且大于所述第四薄膜晶体管的宽长比。

7. 根据权利要求2所述的像素驱动电路,其特征在于,所述复位单元包括第五薄膜晶体管和第六薄膜晶体管;其中,

所述第五薄膜晶体管的源极连接第二薄膜晶体管的源极,栅极连接所述第一控制信号,漏极连接所述第二薄膜晶体管的栅极;

所述第六薄膜晶体管的源极连接所述复位电压,栅极连接所述第一控制信号,漏极连接所述第二薄膜晶体管的栅极。

8. 根据权利要求7所述的像素驱动电路,其特征在于,所述第五薄膜晶体管和第六薄膜晶体管为N型薄膜晶体管。

9. 根据权利要求2所述的像素驱动电路,其特征在于,所述第五薄膜晶体管和第六薄膜晶体管的宽长比相等。

10. 一种显示面板,其特征在于,所述显示面板包括如权利要求1-9中任一项所述的像素驱动电路。

## 像素驱动电路和显示面板

### 技术领域

[0001] 本申请涉及电子显示领域,尤其涉及一种像素驱动电路和显示面板。

### 背景技术

[0002] 现有的显示面板通常使用薄膜晶体管层作为显示面板的驱动电路。受制作工艺、晶体管参数和电路电压的影响,不同薄膜晶体管的阈值电压往往略有差异。同时,在电路工作时,各个节点的电压变化也会导致薄膜晶体管的阈值电压发生漂移。因此,为了消除薄膜晶体管的阈值电压的差异和变化对电路带来的负面影响,通常需要在驱动电路中增加补偿模块。

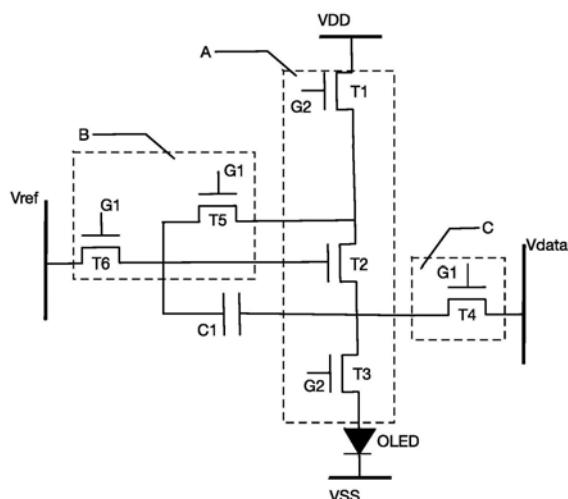

[0003] 图1是现有技术中常用的驱动电路。通过位于驱动电路两侧的复位电路和补偿电路消除了阈值电压和驱动电流的相关性,然而这种电路的晶体管和电容的数量都比较多,且时序复杂,难以保证补偿的准确性。

#### [0004] 申请内容

[0005] 本申请提供了一种像素驱动电路和显示面板,能够简化现有技术中的像素驱动电路的结构和时序。

[0006] 为解决上述问题,本申请提供了一种像素驱动电路,所述像素驱动电路包括复位单元、补偿单元和驱动单元;其中,

[0007] 所述复位单元的第一输入端接入复位电压,第二输入端接入第一控制信号,输出端连接所述驱动单元,所述复位单元根据所述第一控制信号为驱动单元提供复位信号;

[0008] 所述补偿单元的输入端接入数据信号,输出端连接所述驱动单元,所述补偿单元根据所述数据信号为驱动单元提供补偿信号;

[0009] 所述驱动单元的第一输入端连接所述复位单元,第二输入端连接所述补偿单元,第三输入端接入第二控制信号,输出端连接第二电源电压。

[0010] 根据本申请的其中一个方面,所述驱动单元包括第一薄膜晶体管、第二薄膜晶体管和第三薄膜晶体管;其中,

[0011] 所述第一薄膜晶体管的源极连接第一电源电压,栅极接入第二控制信号,漏极连接所述第二薄膜晶体管的源极;

[0012] 所述第二薄膜晶体管的栅极连接所述复位信号,漏极连接所述第三薄膜晶体管的源极;

[0013] 所述第三薄膜晶体管的栅极接入第二控制信号,漏极连接所述待驱动的有机发光二极管的输入端。

[0014] 根据本申请的其中一个方面,所述第一薄膜晶体管、第二薄膜晶体管和第三薄膜晶体管为N型薄膜晶体管。

[0015] 根据本申请的其中一个方面,所述补偿单元包括第四薄膜晶体管和存储电容;其中,

[0016] 所述第四薄膜晶体管的源极连接所述数据信号,栅极连接所述第一控制信号,漏

极连接所述存储电容的一个极板和所述第二薄膜晶体管的漏极；

[0017] 所述存储电容的另一个极板连接所述第二薄膜晶体管的栅极。

[0018] 根据本申请的其中一个方面，所述第四薄膜晶体管为N型薄膜晶体管。

[0019] 根据本申请的其中一个方面，所述第一薄膜晶体管、第二薄膜晶体管和第三薄膜晶体管的宽长比相等且大于所述第四薄膜晶体管的宽长比。

[0020] 根据本申请的其中一个方面，所述复位单元包括第五薄膜晶体管和第六薄膜晶体管；其中，

[0021] 所述第五薄膜晶体管的源极连接第二薄膜晶体管的源极，栅极连接所述第一控制信号，漏极连接所述第二薄膜晶体管的栅极；

[0022] 所述第六薄膜晶体管的源极连接所述复位电压，栅极连接所述第一控制信号，漏极连接所述第二薄膜晶体管的栅极。

[0023] 根据本申请的其中一个方面，所述第五薄膜晶体管和第六薄膜晶体管为N型薄膜晶体管。

[0024] 根据本申请的其中一个方面，所述第五薄膜晶体管和第六薄膜晶体管的宽长比相等。

[0025] 相应的，本申请还提供了一种显示面板，所述显示面板包括如前所述的像素驱动电路。

[0026] 本申请的像素驱动电路使用的薄膜晶体管均为N型薄膜晶体管，相比于采用同时采用N型薄膜晶体管和P型薄膜晶体管的驱动电路，本申请的驱动电路的制备工艺更加简单。同时，本申请只需要一个存储电容，对应的电路时序简单，便于大规模量产。

## 附图说明

[0027] 图1为现有技术中的像素驱动电路的电路图；

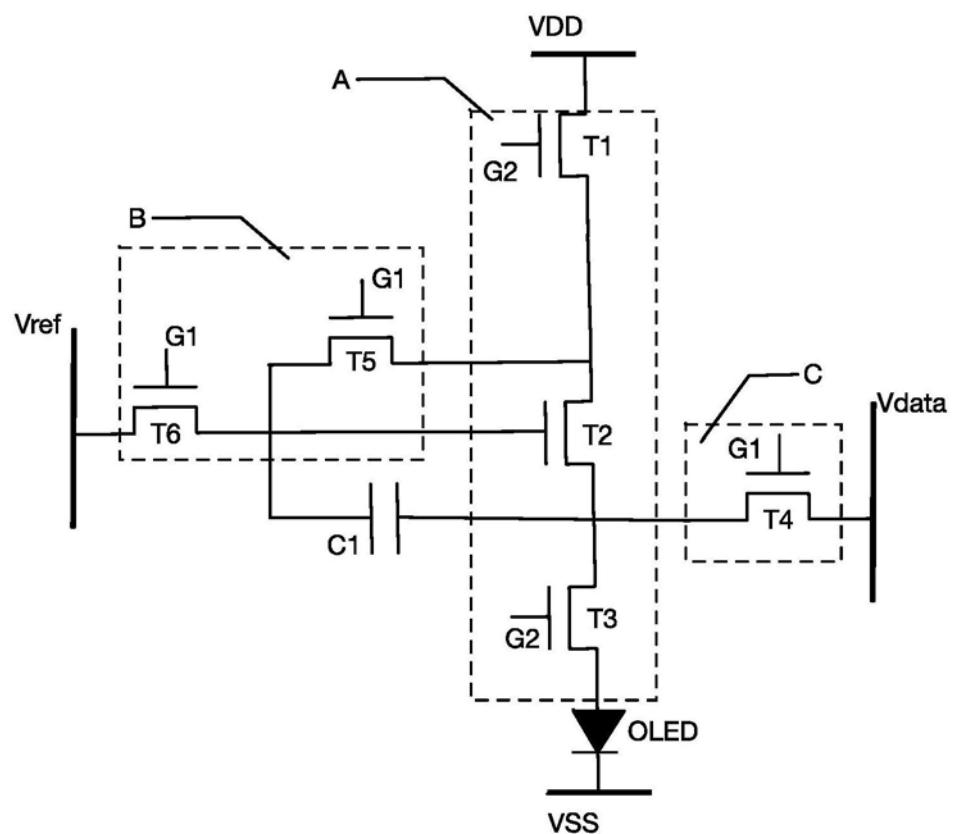

[0028] 图2为本申请的一个具体实施例中的像素驱动电路的电路图；

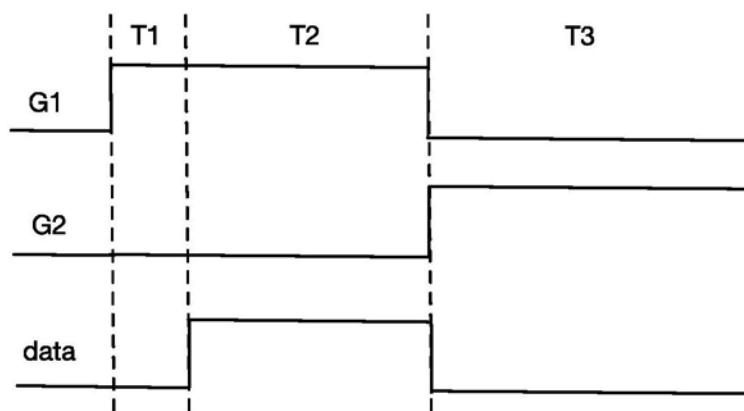

[0029] 图3为图2中的像素驱动电路的时序图。

## 具体实施方式

[0030] 以下各实施例的说明是参考附加的图示，用以示本申请可用以实施的特定实施例。本申请所提到的方向用语，例如[上]、[下]、[前]、[后]、[左]、[右]、[内]、[外]、[侧面]等，仅是参考附加图式的方向。因此，使用的方向用语是用以说明及理解本申请，而非用以限制本申请。在图中，结构相似的单元是用以相同标号表示。

[0031] 首先对现有技术进行简要说明，图1是现有技术中常用的驱动电路。通过位于驱动电路两侧的复位电路和补偿电路消除了阈值电压和驱动电流的相关性，然而这种电路的晶体管和电容的数量都比较多，且时序复杂，难以保证补偿的准确性。

[0032] 因此，本申请提供了一种像素驱动电路和显示面板，能够简化现有技术中的像素驱动电路的结构和时序。

[0033] 参见图2，图2为本申请的一个具体实施例中的像素驱动电路的电路图，所述像素驱动电路包括复位单元B、补偿单元C和驱动单元。

[0034] 在本实施例中，所述驱动单元A的第一输入端连接所述复位单元B，第二输入端连

接所述补偿单元C,第三输入端接入第二控制信号G2,输出端连接第二电源电压VSS。

[0035] 在本实施例中,所述驱动单元A包括第一薄膜晶体管T1、第二薄膜晶体管T2和第三薄膜晶体管T3。其中,所述驱动单元A的第一输入端为所述第二薄膜晶体管T2的栅极,第二输入端为所述第二薄膜晶体管T2的漏极,第三输入端为第一薄膜晶体管T1和第三薄膜晶体管T3栅极。本实施例中待驱动的有机发光二极管OLED连接所述第三薄膜晶体管T3的漏极。

[0036] 具体的,所述第一薄膜晶体管T1的源极连接第一电源电压VDD,栅极接入第二控制信号G2,漏极连接所述第二薄膜晶体管T2的源极。所述第二薄膜晶体管T2的栅极连接所述复位信号,漏极连接所述第三薄膜晶体管T3的源极。所述第三薄膜晶体管T3的栅极接入第二控制信号G2,漏极连接所述有机发光二极管的输入端。所述有机发光二极管OLED的输出端连接所述第二电源电压VSS。

[0037] 在本实施例中,所述第一薄膜晶体管T1、第二薄膜晶体管T2和第三薄膜晶体管T3为N型薄膜晶体管,所述发光二极管为有机发光二极管。所述第一薄膜晶体管T1、第二薄膜晶体管T2和第三薄膜晶体管T3具有相同的宽长比。

[0038] 所述补偿单元C的输入端接入数据信号Vdata,输出端连接所述驱动单元,所述补偿单元C根据所述数据信号Vdata为驱动单元A提供补偿信号。参见图2,所述补偿单元C包括第四薄膜晶体管T4和存储电容C1。其中,所述补偿单元C的输入端为第四薄膜晶体管T4的源极,输出端为第四薄膜晶体管T4的漏极。所述第四薄膜晶体管T4的源极连接所述数据信号Vdata,栅极连接所述第一控制信号G1,漏极连接所述存储电容C1的一个极板和所述第二薄膜晶体管T2的漏极。所述存储电容C1的另一个极板连接所述第二薄膜晶体管T2的栅极。

[0039] 在本实施例中,所述第四薄膜晶体管T4为N型薄膜晶体管。同时,所述第一薄膜晶体管T1、第二薄膜晶体管T2和第三薄膜晶体管T3的宽长比相等且大于所述第四薄膜晶体管T4的宽长比。

[0040] 所述复位单元B的第一输入端接入复位电压Vref,第二输入端接入第一控制信号G1,输出端连接所述驱动单元,所述复位单元B根据所述第一控制信号G1为驱动单元A提供复位信号。所述复位单元B包括第五薄膜晶体管T5和第六薄膜晶体管T6。其中,所述复位单元B的第一输入端为第六薄膜晶体管T6的源极,第二输入端为第五薄膜晶体管T5和第六薄膜晶体管T6的栅极,输出端为第五薄膜晶体管T5的漏极。

[0041] 所述第五薄膜晶体管T5的源极连接第二薄膜晶体管T2源极,栅极连接所述第一控制信号G1,漏极连接所述第二薄膜晶体管T2的栅极。所述第六薄膜晶体管T6的源极连接所述复位电压Vref,栅极连接所述第一控制信号G1,漏极连接所述第二薄膜晶体管T2的栅极。

[0042] 在本实施例中,所述第五薄膜晶体管T5和第六薄膜晶体管T6为N型薄膜晶体管,且所述第五薄膜晶体管T5和第六薄膜晶体管T6的宽长比相等。

[0043] 下面对本申请的像素驱动电路的工作过程进行简要说明。参见图3,图3为图2中的像素驱动电路的时序图。

[0044] 首先,在复位阶段时,第一控制信号G1为高电平。此时第四薄膜晶体管T4、第五薄膜晶体管T5和第六薄膜晶体管T6打开,将复位信号Vref的高电平写入第二薄膜晶体管T2的栅极和漏极,第二薄膜晶体管T2的源极写入低电平,实现对第二薄膜晶体管T2的复位。

[0045] 之后,在补偿阶段时,数据信号Vdata为高电平,第二薄膜晶体管T2由于栅极和漏极短接而打开,持续放电,使栅极和漏极之间的电压逐渐降低。当第二薄膜晶体管T2的栅极

电压Vg等于阈值电压Vth时,第二薄膜晶体管T2截止,此时的栅极电压Vg=Vdata+Vth,实现了对第二薄膜晶体管T2的补偿。

[0046] 最后,在发光阶段时,第一控制信号G1为低电平。此时第四薄膜晶体管T4、第五薄膜晶体管T5和第六薄膜晶体管T6关闭,第二薄膜晶体管T2和第三薄膜晶体管T3打开,驱动管第二薄膜晶体管T2的漏极电流I符合如下公式,实现了对阈值电压的补偿。

$$[0047] I = K (Vgs - Vth)^2$$

$$[0048] = K (Vdata - V_{OLED} + Vth - Vth)^2$$

$$[0049] = K (Vdata - V_{OLED})^2.$$

[0050] 本申请的像素驱动电路使用的薄膜晶体管均为N型薄膜晶体管,相比于采用同时采用N型薄膜晶体管和P型薄膜晶体管的驱动电路,本申请的驱动电路的制备工艺更加简单。同时,本申请只需要一个存储电容,对应的电路时序简单,便于大规模量产。

[0051] 相应的,本申请还提供了一种显示面板,所述显示面板包括如前所述的像素驱动电路。

[0052] 综上所述,虽然本申请已以优选实施例揭露如上,但上述优选实施例并非用以限制本申请,本领域的普通技术人员,在不脱离本申请的精神和范围内,均可作各种更动与润饰,因此本申请的保护范围以权利要求界定的范围为准。

图1

图2

图3