(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-150913

(P2007-150913A)

(43) 公開日 平成19年6月14日(2007.6.14)

| (51) Int.CI.               | F 1        | テーマコード (参考) |

|----------------------------|------------|-------------|

| <b>H04N 7/32</b> (2006.01) | H04N 7/137 | Z 5C059     |

| <b>H04N 7/30</b> (2006.01) | H04N 7/133 | Z 5J064     |

| <b>H03M 7/36</b> (2006.01) | H03M 7/36  |             |

審査請求 未請求 請求項の数 12 O L (全 24 頁)

|           |                              |          |                                             |

|-----------|------------------------------|----------|---------------------------------------------|

| (21) 出願番号 | 特願2005-344739 (P2005-344739) | (71) 出願人 | 000005821<br>松下電器産業株式会社<br>大阪府門真市大字門真1006番地 |

| (22) 出願日  | 平成17年11月29日 (2005.11.29)     | (74) 代理人 | 100109210<br>弁理士 新居 広守                      |

|           |                              | (72) 発明者 | 岡本 和雄<br>大阪府門真市大字門真1006番地 松下電器産業株式会社内       |

|           |                              | (72) 発明者 | 田坂 啓<br>大阪府門真市大字門真1006番地 松下電器産業株式会社内        |

|           |                              | (72) 発明者 | 有村 耕治<br>大阪府門真市大字門真1006番地 松下電器産業株式会社内       |

最終頁に続く

(54) 【発明の名称】画像符号化装置

## (57) 【要約】

【課題】より少ないサイクル数でイントラ予測処理を行なうとともに、H.264の規格に準拠した画像復号化装置が復号化することができる符号化データを生成する画像符号化装置を提供する。

【解決手段】イントラ予測対象のブロックに隣接する左側のブロックの、前記イントラ予測対象のブロックに隣接する右端の垂直方向の原画の画素データを記憶するイントラ予測バッファ2と、イントラ予測バッファ2に記憶されている前記画素データを利用して、前記イントラ予測対象のブロックについてイントラ予測するイントラ予測部4とを備える。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

画像内のマクロブロックを構成する矩形領域についてイントラ予測し、前記画像を符号化する装置であって、

(a) イントラ予測対象の矩形領域に隣接する左側の矩形領域の、前記イントラ予測対象の矩形領域に隣接する右端の垂直方向の原画の画素データと、(b) 前記イントラ予測対象の矩形領域に隣接する上側の矩形領域の、前記イントラ予測対象の矩形領域に隣接する下端の水平方向の原画の画素データとの、少なくとも一方を記憶する記憶手段と、

前記記憶手段に記憶されている前記画素データを利用して、前記イントラ予測対象の矩形領域についてイントラ予測するイントラ予測手段と

を備える画像符号化装置。

10

**【請求項 2】**

前記矩形領域は 4 画素 × 4 ラインのブロックであって、

前記記憶手段は、前記マクロブロックを構成する 16 個のイントラ予測対象のブロックそれぞれについて、前記イントラ予測対象のブロックに隣接する左側のブロックの、前記イントラ予測対象のブロックに隣接する右端の垂直方向の原画の画素データを記憶し、

前記イントラ予測手段は、前記記憶手段に記憶されている前記画素データと、前記イントラ予測対象のブロックに隣接する上側のブロックの、前記イントラ予測対象のブロックに隣接する下端の水平方向の符号化処理された後の画像の画素データとを利用して、前記イントラ予測対象のブロックについてイントラ予測する

20

請求項 1 記載の画像符号化装置。

**【請求項 3】**

更に、

前記イントラ予測対象のブロックに隣接する左側のブロックの原画について直交変換及び量子化することにより得られる量子化値が所定の閾値より大きいか否かを判定する量子化値判定手段と、

前記量子化値判定手段によって、前記量子化値が前記閾値より大きいと判定された場合、前記左側のブロックの原画に対して解像度を低下させるフィルタ処理を行なうフィルタ処理手段とを備え、

前記イントラ予測手段は、前記記憶手段に記憶されている前記画素データにより形成される画素を含む前記左側のブロックの原画に対して、前記フィルタ処理手段によってフィルタ処理された後の画像であるフィルタ処理画の右端の垂直方向の画素データと、前記イントラ予測対象のブロックに隣接する上側のブロックの、前記イントラ予測対象のブロックに隣接する下端の水平方向の符号化処理された後の画像の画素データとを利用して、前記イントラ予測対象のブロックについてイントラ予測する

30

請求項 2 記載の画像符号化装置。

**【請求項 4】**

更に、前記イントラ予測対象のブロックを含む画像がフレームであるのかフィールドであるのかを判定するフレーム判定手段を備え、

前記イントラ予測手段は、

(1) 前記フレーム判定手段によって、前記画像がフレームであると判定された場合、前記記憶手段に記憶されている前記画素データと、前記イントラ予測対象のブロックに隣接する上側のブロックの、前記イントラ予測対象のブロックに隣接する下端の水平方向の符号化処理された後の画像の画素データとを利用して、前記イントラ予測対象のブロックについてイントラ予測し、

40

(2) 前記フレーム判定手段によって、前記画像がフィールドであると判定された場合、前記イントラ予測対象のブロックに隣接する上側のブロックの、前記イントラ予測対象のブロックに隣接する下端の水平方向の符号化処理された後の画像の画素データと、前記イントラ予測対象のブロックに隣接する左側のブロックの、前記イントラ予測対象のブロックに隣接する右端の垂直方向の符号化処理された後の画像の画素データとを利用して

50

、前記イントラ予測対象のブロックについてイントラ予測する

請求項 2 記載の画像符号化装置。

**【請求項 5】**

前記矩形領域は 4 画素 × 4 ラインのブロックであって、

前記記憶手段は、前記マクロブロックを構成する左端の垂直方向の 4 個のイントラ予測対象のブロックのみについて、前記イントラ予測対象のブロックに隣接する左側のブロックの、前記イントラ予測対象のブロックに隣接する右端の垂直方向の原画の画素データを記憶し、

前記イントラ予測手段は、

(1) 前記 4 個のイントラ予測対象のブロックについては、前記記憶手段に記憶されている前記画素データと、前記イントラ予測対象のブロックに隣接する上側のブロックの、前記イントラ予測対象のブロックに隣接する下端の水平方向の符号化処理された後の画像の画素データとを利用して、前記イントラ予測手段は、

(2) 前記マクロブロックを構成する 16 個のブロックのうちの前記 4 個のイントラ予測対象のブロックを除く 12 個のイントラ予測対象のブロックについては、前記イントラ予測対象のブロックに隣接する上側のブロックの、前記イントラ予測対象のブロックに隣接する下端の水平方向の符号化処理された後の画像の画素データと、前記イントラ予測対象のブロックに隣接する左側のブロックの、前記イントラ予測対象のブロックに隣接する右端の垂直方向の符号化処理された後の画像の画素データとを利用して、前記イントラ予測手段は、

、

前記イントラ予測対象のブロックについてイントラ予測する

請求項 1 記載の画像符号化装置。

**【請求項 6】**

前記矩形領域は 4 画素 × 4 ラインのブロックであって、

前記記憶手段は、前記マクロブロックを構成する 16 個のイントラ予測対象のブロックそれぞれについて、前記イントラ予測対象のブロックに隣接する上側のブロックの、前記イントラ予測対象のブロックに隣接する下端の水平方向の原画の画素データを記憶し、

前記イントラ予測手段は、前記記憶手段に記憶されている前記画素データと、前記イントラ予測対象のブロックに隣接する左側のブロックの、前記イントラ予測対象のブロックに隣接する右端の垂直方向の符号化処理された後の画像の画素データとを利用して、前記イントラ予測手段は、

、

前記イントラ予測対象のブロックについてイントラ予測する

請求項 1 記載の画像符号化装置。

**【請求項 7】**

画像内のマクロブロックについてイントラ予測し、前記画像を符号化する装置であって、

、

前記マクロブロックについてイントラ予測するイントラ予測手段と、

前記マクロブロックに対応する色差についてのサブブロックの色差についての予測モードとして、前記マクロブロックの輝度についてイントラ予測されて得られた予測モードの内容と同じ内容の予測モードを割り当てる割り当て手段と

を備える画像符号化装置。

**【請求項 8】**

前記イントラ予測手段は、前記マクロブロックを構成する各サブブロックの輝度についてイントラ予測するとともに、前記マクロブロックに対応する色差についてのサブブロックの特定のブロックの色差についてイントラ予測し、

前記マクロブロックにおいて、前記色差についてのサブブロックにおいて前記特定のブロックが存在する位置と相対的に同じ位置に存在する、前記マクロブロックを構成する特定のサブブロックの輝度についてイントラ予測されて得られた予測モードの内容と、前記特定のブロックの色差についてイントラ予測されて得られた予測モードの内容とが同じ場合、前記割り当て手段は、前記色差についてのサブブロックを構成する一のブロックの色差についての予測モードとして、前記マクロブロックにおける、前記色差についてのサブ

10

20

30

40

50

ブロックにおいて前記一のブロックが存在する位置と相対的に同じ位置に存在する、前記マクロブロックを構成するサブブロックの輝度についてイントラ予測されて得られた予測モードの内容と同じ内容の予測モードを割り当てる

請求項 7 記載の画像符号化装置。

【請求項 9】

画像内のマクロブロックについてイントラ予測し、前記画像を符号化する装置であって

、前記マクロブロックについてイントラ予測するイントラ予測手段と、

第1のマクロブロックを構成する第1の特定のサブブロックの輝度についての予測モードと、前記第1のマクロブロックより後にイントラ予測される、前記第1のマクロブロックに隣接する第2のマクロブロックのブロックにおいて、前記第1のマクロブロックにおいて前記第1の特定のサブブロックが存在する位置と相対的に同じ位置に存在する第2の特定のサブブロックの輝度についてイントラ予測されて得られた予測モードとが同じ場合、前記第2のマクロブロックの色差についての予測モードとして、前記第1のマクロブロックの色差についての予測モードを割り当てる割り当て手段と

を備える画像符号化装置。

【請求項 10】

画像内のマクロブロックを構成する矩形領域についてイントラ予測し、前記画像を符号化する方法であって、

(a) イントラ予測対象の矩形領域に隣接する左側の矩形領域の、前記イントラ予測対象の矩形領域に隣接する右端の垂直方向の原画の画素データと、(b) 前記イントラ予測対象の矩形領域に隣接する上側の矩形領域の、前記イントラ予測対象の矩形領域に隣接する下端の水平方向の原画の画素データとの、少なくとも一方を記憶手段に格納する格納ステップと、

前記記憶手段に記憶されている前記画素データを利用して、前記イントラ予測対象の矩形領域についてイントラ予測するイントラ予測ステップと

を含む画像符号化方法。

【請求項 11】

画像内のマクロブロックについてイントラ予測し、前記画像を符号化する方法であって

、前記マクロブロックについてイントラ予測するイントラ予測ステップと、

前記マクロブロックに対応する色差についてのサブブロックの色差についての予測モードとして、前記マクロブロックの輝度についてイントラ予測されて得られた予測モードの内容と同じ内容の予測モードを割り当てる割り当てステップと

を含む画像符号化方法。

【請求項 12】

画像内のマクロブロックについてイントラ予測し、前記画像を符号化する方法であって

、前記マクロブロックについてイントラ予測するイントラ予測ステップと、

第1のマクロブロックを構成する第1の特定のサブブロックの輝度についての予測モードと、前記第1のマクロブロックより後にイントラ予測される、前記第1のマクロブロックに隣接する第2のマクロブロックのブロックにおいて、前記第1のマクロブロックにおいて前記第1の特定のサブブロックが存在する位置と相対的に同じ位置に存在する第2の特定のサブブロックの輝度についてイントラ予測されて得られた予測モードとが同じ場合、前記第2のマクロブロックの色差についての予測モードとして、前記第1のマクロブロックの色差についての予測モードを割り当てる割り当てステップと

を含む画像符号化方法。

【発明の詳細な説明】

【技術分野】

【0001】

10

20

30

40

50

本発明は、イントラ予測を行なって画像を符号化する画像符号化装置に関する。

#### 【背景技術】

##### 【0002】

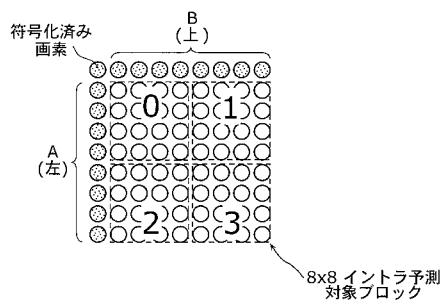

MPEG4 - AVC 規格において「イントラ予測」が定義されている。これを更に進歩させた Joint Video Team (JVT) 方式という符号化方式が提案されている。具体的には、H26L 規格又は H.264 規格において、従来の MPEG2 規格等にはないフレーム内予測である「イントラ予測」が提案されている。イントラ予測は、予測対象ブロックの画素値を、予測対象ブロックに隣接する左側及び上側のブロックの既に符号化された画素値から予測することである。MPEG4 - AVC 規格の場合、8 画素 × 8 ラインのサブブロックを 1 個の単位としてイントラ予測する。他方、H.264 規格のメインプロファイルの場合、4 画素 × 4 ラインのブロック又は 16 画素 × 16 ラインのマクロブロックを 1 個の単位としてイントラ予測する。10

##### 【0003】

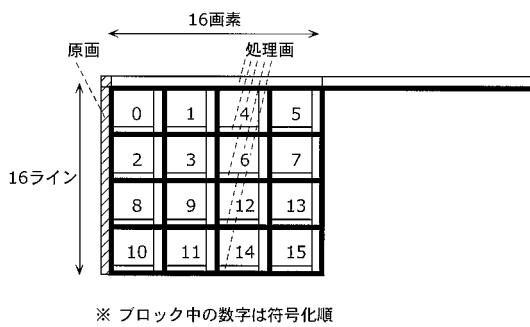

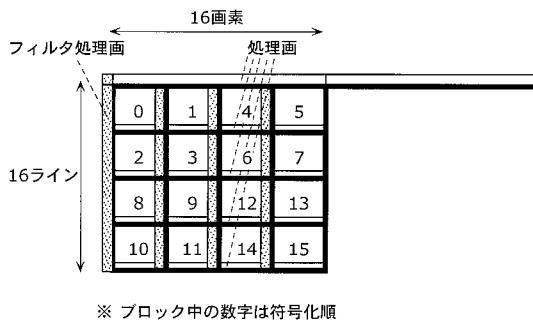

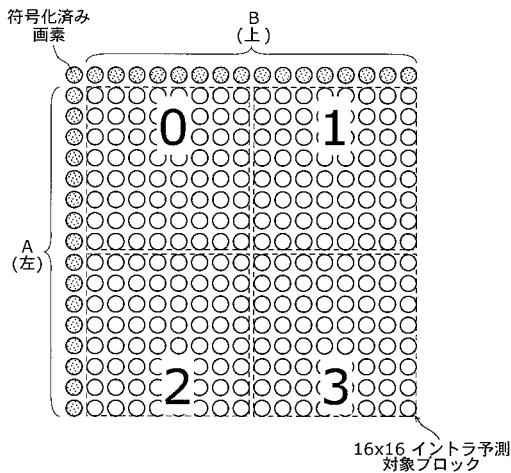

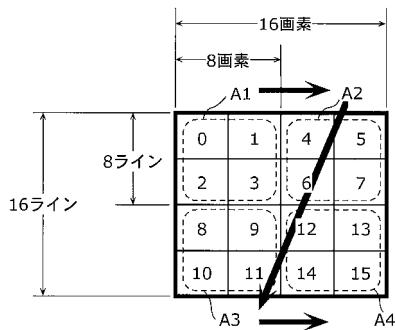

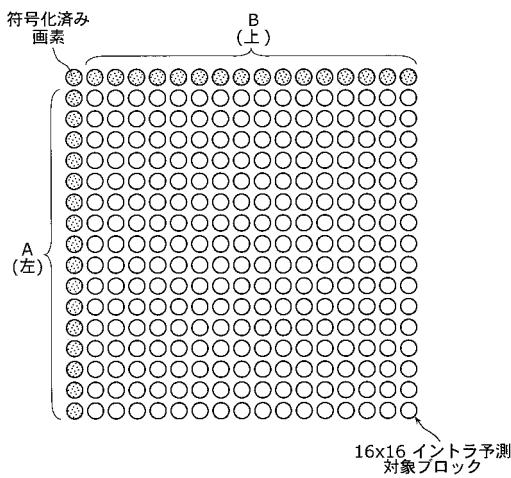

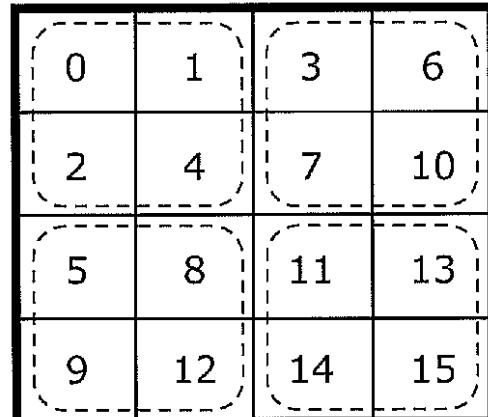

以下に、より高画質の符号化に適している H.264 規格のイントラ予測を説明する。4 画素 × 4 ラインのブロックを 1 個の単位としてイントラ予測する場合、図 13 に示すように、16 画素 × 16 ラインのマクロブロックにおいて、8 画素 × 8 ラインの 4 個のサブブロック A1、A2、A3、及び A4 を、符号 A1、A2、A3、A4 の順にイントラ予測する。更に詳しくは、各サブブロックから 4 画素 × 4 ラインを 1 個の単位として分割された 16 個のブロックを、番号 0、1、2、3、4、5、6、7、8、9、10、11、12、13、14、15 の順（ラスタスキャン順）にイントラ予測する。これはラスタスキャン方式によるイントラ予測と呼ばれている。20

##### 【0004】

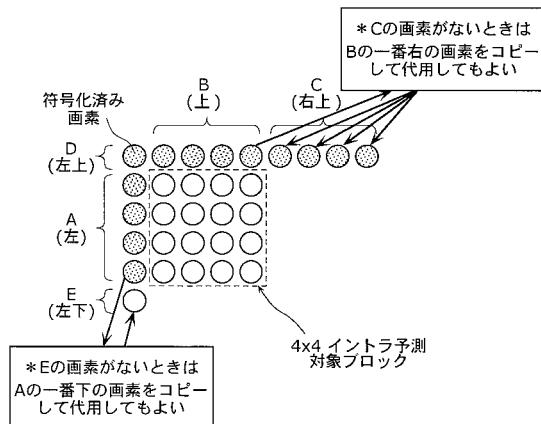

4 画素 × 4 ラインのブロックに対して行なうイントラ予測を説明する。図 14 に示すように、イントラ予測対象の 4 画素 × 4 ラインのブロックの各画素値を、イントラ予測対象のブロックに隣接する上側のブロックの既に符号化された 8 画素と、イントラ予測対象のブロックに隣接する左側のブロックの既に符号化された 5 画素との全部又は一部を利用して予測する。この際、H.264 規格において定義されている 9 個の予測モードのうちの最もパフォーマンスコストの小さい予測モードを、イントラ予測対象のブロックの予測モードと決定する。30

##### 【0005】

4 画素 × 4 ラインのブロックをイントラ予測する場合、上記の通り全部で 9 個の予測モードがあり、発生頻度が高い予測モードに小さい番号が割り当てられている。4 画素 × 4 ラインのブロックをイントラ予測する場合、ブロック毎に、9 個の予測モードの中から、最も適切な予測モードを選択する。もし、隣接ブロックからの予測対象のブロックの予測方向 I と、現実に予測した予測対象のブロックの予測方向 II とが同じ場合、その旨を示す「予測モードフラグ」のみを符号化する。もし、予測方向 I と予測方向 II とが合致しない場合、「予測した予測方向と異なる予測方向のフラグ」と、予測しなかった 8 個の予測モードによる予測を行なうか否かを示す情報を符号化する。

##### 【0006】

9 個の予測モードは以下の通りである。予測モード 0 は垂直予測であり、予測モード 1 は水平予測であり、予測モード 2 は平均値予測であり、予測モード 3 は斜め左下方予測であり、予測モード 4 は斜め右下方予測である。予測モード 5 は垂直右方予測であり、予測モード 6 は水平下方予測であり、予測モード 7 は垂直左方予測であり、予測モード 8 は水平上方予測である。40

##### 【0007】

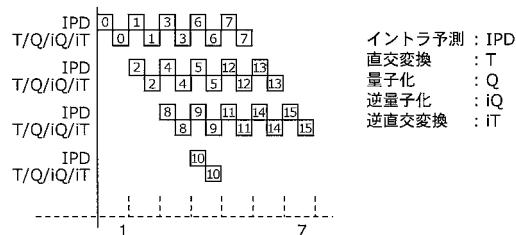

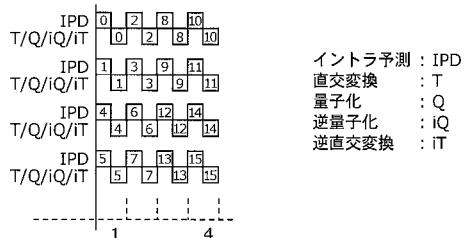

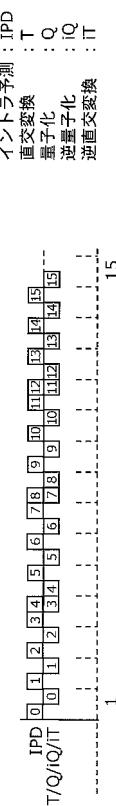

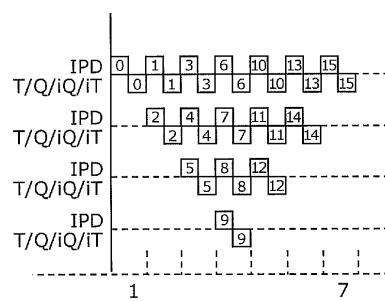

1 個のマクロブロックを構成する 16 個のブロックのイントラ予測処理のタイミングを図 15 に示す。H.264 規格では、イントラ予測（以下、「IPD」ともいう）を行なった後、直交変換（以下、「T」ともいう）と、量子化（以下、「Q」ともいう）と、逆量子化（以下、「iQ」ともいう）と、逆直交変換（以下、「iT」ともいう）とを、順に行なうことにより、16 個のブロックそれぞれを符号化する。各ブロックについて、I50

P D を 1 サイクルで行なうとともに、T と Q と i Q と i T とを順に行なうこと（以下、「T / Q / i Q / i T」ともいう）を 1 サイクルで行なうとすると、1 個のマクロブロックを構成する 16 個のブロックをラスタスキャン順に逐次処理する場合、図 15 に示すように、イントラ予測処理を完了するには、15 サイクルが必要である。

#### 【0008】

次に、H . 264 規格のメインプロファイルで定義されている、16 画素 × 16 ラインのマクロブロックに対して行なうイントラ予測を説明する。

#### 【0009】

輝度のイントラ予測は、図 16 に示すように、16 画素 × 16 ラインのマクロブロック単位で行なわれる。すなわち、イントラ予測対象のマクロブロックの各画素値を、イントラ予測対象のマクロブロックに隣接する上側のマクロブロックの既に符号化された 16 画素と、イントラ予測対象のマクロブロックに隣接する左側のマクロブロックの既に符号化された 16 画素との全部又は一部を利用して予測する。10

#### 【0010】

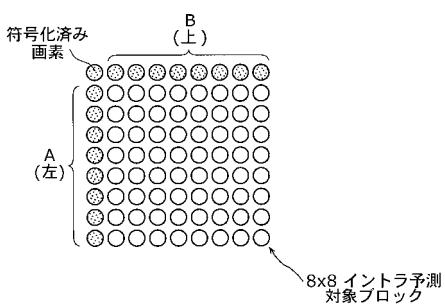

他方、色差のイントラ予測は、図 17 に示すように、8 画素 × 8 ラインのサブブロック単位で行なわれる。すなわち、イントラ予測対象のサブブロックの各画素値を、イントラ予測対象のサブブロックに隣接する上側のマクロブロックの既に符号化された 8 画素と、イントラ予測対象のサブブロックに隣接する左側のマクロブロックの既に符号化された 8 画素との全部又は一部を利用して予測する。

#### 【0011】

なお、輝度のイントラ予測については 4 個の予測モードがあり、予測モード 0 は垂直予測であり、予測モード 1 は水平予測であり、予測モード 2 は平均値予測であり、予測モード 3 は平面予測である。輝度のイントラ予測の場合、4 個の予測モードのいずれかによる予測結果と、マクロブロックタイプとが符号化される。色差のイントラ予測についても 4 個の予測モードがあり、予測モード 0 は平均値予測であり、予測モード 1 は水平予測であり、予測モード 2 は垂直予測であり、予測モード 3 は平面予測である。なお、色差信号には C b と C r とがあるが、予測モードは共通である。また、色差のイントラ予測についての予測モードは、輝度信号のイントラ予測についての予測モードと独立して選択される。20

#### 【0012】

上記のように、JVT 方式によりイントラ予測対象のブロックを符号化するには、イントラ予測対象のブロックの処理の開始時において、イントラ予測対象のブロックに隣接する上側及び左側のブロック（参照ブロック）の画素の値が決定されていなければならない。したがって、1 個のマクロブロックを構成する 16 個のブロックをラスタスキャン順に I P D しその後 T / Q / i Q / i T しようとすると、図 15 に示すように、I P D と T / Q / i Q / i T とを並列化することはできない。つまり、1 個のマクロブロックについてのイントラ予測処理には、多くのサイクルが必要となり、各処理部を I C 化し高速処理させようすると、クロックを高速化する必要が生じ、消費電力が増大するという課題がある。30

#### 【0013】

従来、この課題を解決するために、いろいろな手法が提案されている（例えば、特許文献 1 及び特許文献 2 参照）。40

#### 【0014】

次に、特許文献 1 により開示されている技術（以下、「第 1 の従来技術」という）を説明する。

#### 【0015】

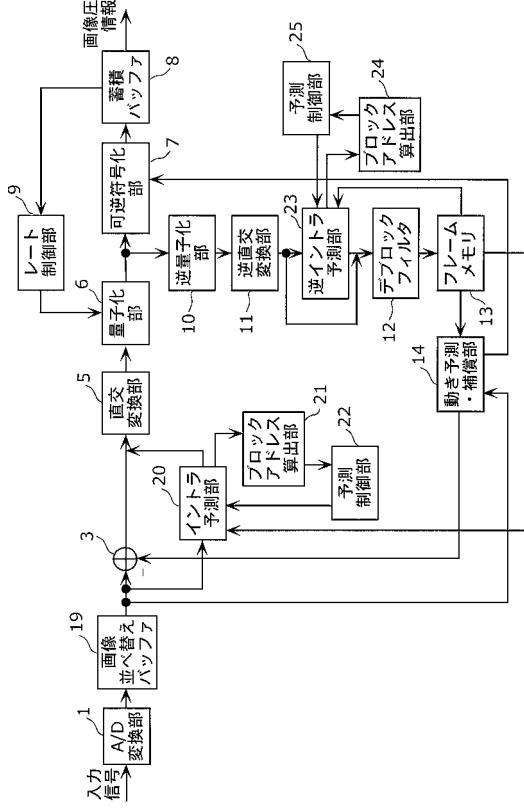

図 18 は、第 1 の従来技術の画像符号化装置の構成を示すブロック図である。第 1 の従来技術の画像符号化装置は、A / D 変換部 1 と、画像並べ替えバッファ 19 と、減算部 3 と、直交変換部 5 と、量子化部 6 と、可逆符号化部 7 と、蓄積バッファ 8 と、レート制御部 9 と、逆量子化部 10 と、逆直交変換部 11 と、デブロックフィルタ 12 と、フレームメモリ 13 と、動き予測・補償部 14 と、イントラ予測部 20 と、ブロックアドレス算出

10

20

30

40

50

部21と、予測制御部22と、逆イントラ予測部23と、予測制御部25と、ブロックアドレス算出部24とを備える。

#### 【0016】

A/D変換部1と、画像並べ替えバッファ19と、減算部3と、直交変換部5と、量子化部6と、可逆符号化部7と、蓄積バッファ8と、レート制御部9と、逆量子化部10と、逆直交変換部11と、デブロックフィルタ12と、フレームメモリ13と、動き予測・補償部14とにより構成される部分は、一般的な画像符号化予測処理部である。

#### 【0017】

次に、第1の従来技術の画像符号化装置の動作を説明する。

A/D変換部1は、入力されたアナログの画像信号をデジタルの画像信号に変換する。次に、画像並べ替えバッファ19は、インタレースの画像をプログレッシブの画像へ変換する。イントラ予測部20はイントラ予測を行なうべきであるか否かを判定する。イントラ予測部20がイントラ予測を行なうべきであると判定すると、ブロックアドレス算出部21は、次に処理可能なブロックのアドレスを算出し、予測制御部22に対してどのブロックを処理すべきかを指示する。第1の従来技術の画像符号化装置は、ラスタスキャン順ではなく、処理条件が整ったブロックから順にイントラ予測を実行する。このため、第1の従来技術の画像符号化装置は、IPDとT/Q/iQ/iTとを並列化すること、つまりパイプライン処理することができる。

#### 【0018】

直交変換部5は、イントラ予測部20によって上記ルールにより得られた予測符号を直交変換し、量子化部6は、直交変換部5によって得られた係数を量子化し、データ量を削減する準備を行なう。その後、可逆符号化部7は量子化部6によって得られた値を可逆符号化する。可逆符号化されたデータは蓄積バッファ8に蓄積された後、画像圧縮情報として画像符号化装置の外部に出力される。

#### 【0019】

レート制御部9は、蓄積バッファ8の空き状態等に基づいて、量子化部6が量子化を実行する際のレート制御を行なう。

#### 【0020】

イントラ予測部20は、既に量子化された、予測対象のブロックに隣接する左側及び上側の画素のデータを使用する。このため、逆量子化部10は量子化部6によって得られた値を逆量子化し、逆直交変換部11は、逆量子化部10によって得られた係数を逆直交変換し、逆イントラ予測部23は逆イントラ予測を行なう。この際、ブロックアドレス算出部24は処理すべきブロックのアドレスを算出し、予測制御部25は逆イントラ予測の制御を行なう。その後、デブロックフィルタ12は、隣接するブロック間の画像を滑らかにしてブロックノイズを目立たなくし、処理した画像の情報をフレームメモリ13に一時的に格納する。フレームメモリ13に格納された画像の情報は、イントラ予測部20に与えられる。これにより、イントラ予測には、常に量子化処理されたいわゆる処理画が用いられる。

#### 【0021】

第1の従来技術においては、ラスタスキャン順とは異なるスキャン順により、各ブロックをイントラ予測する。このため、第1の従来技術には、パイプライン処理が可能となり、処理負荷の大きいイントラ予測を並列に行なえるという長所がある。しかしながら、イントラ予測を行なうには、予測対象ブロックに隣接した上側及び左側のブロックの画素の量子化された処理画が予測対象ブロックを処理する前に得られていなければならないという、時系列的な課題は残存したままである。

#### 【0022】

次に、第1の従来技術の画像復号化装置を説明する。

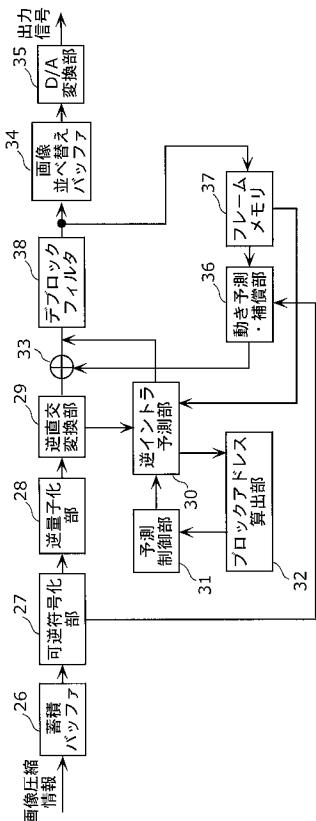

図19は、第1の従来技術の画像復号化装置の構成を示すブロック図である。第1の従来技術の画像復号化装置は、蓄積バッファ26と、可逆符号化部27と、逆量子化部28と、逆直交変換部29と、逆イントラ予測部30と、予測制御部31と、ブロックアドレ

10

20

30

40

50

ス算出部32と、加算部33と、画像並べ替えバッファ34と、D/A変換部35と、動き予測・補償部36と、フレームメモリ37と、デブロックフィルタ38とを備える。

【0023】

第1の従来技術の画像復号化装置の動作は、上記符号化の逆の動作であるので、説明は省略する。

【0024】

第1の従来技術におけるブロックの処理順は、図13に示すH.264規格において定義されている順とは異なり、図20に示す順である。そのため、第1の従来技術では、1個のマクロブロックのイントラ予測におけるIPDとT/Q/iQ/iTとを、図21に示すように、4パイプラインで行なうことができる。この場合、1個のマクロブロックのイントラ予測処理を7サイクルで行なうことができる。つまり、第1の従来技術により、1個のマクロブロックのイントラ予測処理を、H.264規格によると15サイクルが必要であったところから、7サイクルへとサイクル数を減少させることができ、改善されている。10

【0025】

特許文献1には、ブロックの処理順として、H.264規格において定義されている順とは異なる、図22に示す順も開示されている。この場合、1個のマクロブロックのイントラ予測におけるIPDとT/Q/iQ/iTとを、図23に示すように、4パイプラインで行なうことができる。したがって、図23に示すように、1個のマクロブロックのイントラ予測処理のサイクル数を、H.264規格によると15サイクルが必要であったところから、7サイクルへと減少させることができ、改善されている。20

【0026】

次に、特許文献2により開示されている技術（以下、「第2の従来技術」という）を説明する。

【0027】

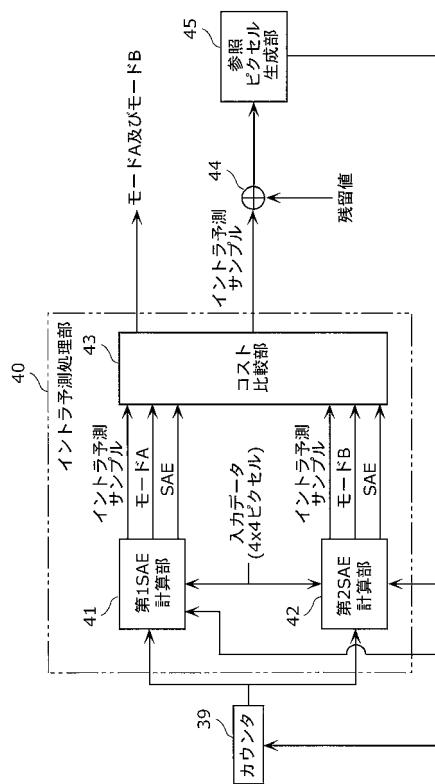

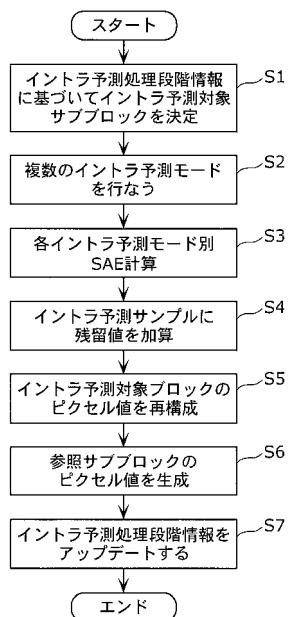

図24は、第2の従来技術のイントラ予測装置の構成を示すブロック図である。第2の従来技術のイントラ予測装置は、マクロブロック毎にイントラ予測処理を行なう装置であって、カウンタ39と、イントラ予測処理部40と、加算部44と、参照ピクセル生成部45とを備える。イントラ予測処理部40は、第1SAE計算部41と、第2SAE計算部42と、コスト比較部43とを有する。30

【0028】

SAEは、Sum Absolute Errorの略であって、検出されたイントラ予測サンプルと、それに対応するサブブロックの現在ピクセル値とを使用することにより得られる、各イントラ予測モードにおけるエラー絶対値の和を意味する。

【0029】

図25は、第2の従来技術のイントラ予測装置の動作手順を示すフローチャートである。

【0030】

次に、図24と図25とを使用して、第2の従来技術のイントラ予測装置の動作を説明する。

【0031】

カウンタ39は、イントラ予測処理段階の情報に基づいて、イントラ予測対象サブブロックを決定する（S1）。次に、イントラ予測処理部40は、複数のイントラ予測モードによりイントラ予測を行なう（S2）。そして、第1SAE計算部41及び第2SAE計算部42は、イントラ予測モード毎にSAE計算を行なう（S3）。コスト比較部43は、第1SAE計算部41によって得られた結果と、第2SAE計算部42によって得られた結果とを比較し、パフォーマンスコストが小さい方をイントラ予測サンプルとして出力し、加算部44はイントラ予測サンプルに残留値を加算する（S4）。その後、参照ピクセル生成部45はイントラ予測対象ブロックのピクセル値を再構成する（S5）。更に、参照ピクセル生成部45は参照サブブロックのピクセル値を生成する（S6）。最後に、40

参照ピクセル生成部 45 はイントラ予測処理段階の情報をアップデートする (S7)。

#### 【0032】

第2の従来技術におけるイントラ予測のブロックの処理順は図26に示す順であって、2個のブロックの処理を同時に行なうことが可能になる。つまり、図27に示すように、1個のマクロブロックのイントラ予測におけるIPDとT/Q/iQ/iTとを、2パイプラインで行なうことができる。したがって、1個のマクロブロックのイントラ予測処理を、H.264規格によると15サイクルが必要であったところから、それより少ない10サイクルで実行することができ、改善されている。

#### 【0033】

第2の従来技術においても、ラスタスキャン順とは異なるスキヤン順により各ブロックをイントラ予測するので、イントラ予測の速度を向上させることができるとなる。つまり、第2の従来技術には、処理負荷の大きいイントラ予測を高速で行なえるという長所がある。

【特許文献1】特開2004-140473号公報

【特許文献2】特開2005-130509号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0034】

特許文献1に記載の方法は、図21及び図23に示すように、各ブロックについて実行すべきIPDとT/Q/iQ/iTとを、4パイプラインで行なう。しかしながら、1個のマクロブロックのイントラ予測処理のサイクル数を、H.264規格による15サイクルから、その約半分の7サイクルへしか減少させることができない。つまり、特許文献1に記載の方法では、パイプラインの使用効率が悪いという課題がある。また、特許文献1に記載の方法では、H.264の規格で定義されているラスタスキャン順でイントラ予測されていないので、画像復号化装置には、ブロックの処理順をラスタスキャン順に変更する手段が必要となる。

#### 【0035】

また、特許文献2に記載の方法は、図27に示すように、各ブロックについて実行すべきIPDとT/Q/iQ/iTとを、2段のパイプラインで行なう。しかしながら、イントラ予測を行なうには、予測対象ブロックに隣接する上側及び左側の画素の量子化された処理画が既に得られていなければならないという、時系列的な課題がある。このため、1個のマクロブロックのイントラ予測処理のサイクル数を、H.264規格による15サイクルから、10サイクルへしか減少させることができない。つまり、特許文献2に記載の方法では、イントラ予測処理の高速化を実現することができない。

#### 【0036】

本発明は、より少ないサイクル数でイントラ予測処理を行なうとともに、H.264の規格に準拠した画像復号化装置が復号化することができる符号化データを生成する画像符号化装置を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0037】

上記課題を解決し上記目的を達成するために、本発明の画像符号化装置は、画像内のマクロブロックを構成する矩形領域についてイントラ予測し、前記画像を符号化する装置であって、(a)イントラ予測対象の矩形領域に隣接する左側の矩形領域の、前記イントラ予測対象の矩形領域に隣接する右端の垂直方向の原画の画素データと、(b)前記イントラ予測対象の矩形領域に隣接する上側の矩形領域の、前記イントラ予測対象の矩形領域に隣接する下端の水平方向の原画の画素データとの、少なくとも一方を記憶する記憶手段と、前記記憶手段に記憶されている前記画素データを利用して、前記イントラ予測対象の矩形領域についてイントラ予測するイントラ予測手段とを備える。

#### 【0038】

前記矩形領域は4画素×4ラインのブロックであって、前記記憶手段は、前記マクロブ

10

20

30

40

50

ロックを構成する16個のイントラ予測対象のブロックそれぞれについて、前記イントラ予測対象のブロックに隣接する左側のブロックの、前記イントラ予測対象のブロックに隣接する右端の垂直方向の原画の画素データを記憶し、前記イントラ予測手段は、前記記憶手段に記憶されている前記画素データと、前記イントラ予測対象のブロックに隣接する上側のブロックの、前記イントラ予測対象のブロックに隣接する下端の水平方向の符号化処理された後の画像の画素データとを利用して、前記イントラ予測対象のブロックについてイントラ予測してもよい。

【0039】

本発明の画像符号化装置は、更に、前記イントラ予測対象のブロックに隣接する左側のブロックの原画について直交変換及び量子化することにより得られる量子化値が所定の閾値より大きいか否かを判定する量子化値判定手段と、前記量子化値判定手段によって、前記量子化値が前記閾値より大きいと判定された場合、前記左側のブロックの原画に対して解像度を低下させるフィルタ処理を行なうフィルタ処理手段とを備え、前記イントラ予測手段は、前記記憶手段に記憶されている前記画素データにより形成される画素を含む前記左側のブロックの原画に対して、前記フィルタ処理手段によってフィルタ処理された後の画像であるフィルタ処理画の右端の垂直方向の画素データと、前記イントラ予測対象のブロックに隣接する上側のブロックの、前記イントラ予測対象のブロックに隣接する下端の水平方向の符号化処理された後の画像の画素データとを利用して、前記イントラ予測対象のブロックについてイントラ予測してもよい。

【0040】

本発明の画像符号化装置は、更に、前記イントラ予測対象のブロックを含む画像がフレームであるのかフィールドであるのかを判定するフレーム判定手段を備え、前記イントラ予測手段は、(1)前記フレーム判定手段によって、前記画像がフレームであると判定された場合、前記記憶手段に記憶されている前記画素データと、前記イントラ予測対象のブロックに隣接する上側のブロックの、前記イントラ予測対象のブロックに隣接する下端の水平方向の符号化処理された後の画像の画素データとを利用して、前記イントラ予測対象のブロックについてイントラ予測し、(2)前記フレーム判定手段によって、前記画像がフィールドであると判定された場合、前記イントラ予測対象のブロックに隣接する上側のブロックの、前記イントラ予測対象のブロックに隣接する下端の水平方向の符号化処理された後の画像の画素データと、前記イントラ予測対象のブロックに隣接する左側のブロックの、前記イントラ予測対象のブロックに隣接する右端の垂直方向の符号化処理された後の画像の画素データとを利用して、前記イントラ予測対象のブロックについてイントラ予測してもよい。

【0041】

前記矩形領域は4画素×4ラインのブロックであって、前記記憶手段は、前記マクロブロックを構成する左端の垂直方向の4個のイントラ予測対象のブロックのみについて、前記イントラ予測対象のブロックに隣接する左側のブロックの、前記イントラ予測対象のブロックに隣接する右端の垂直方向の原画の画素データを記憶し、前記イントラ予測手段は、(1)前記4個のイントラ予測対象のブロックについては、前記記憶手段に記憶されている前記画素データと、前記イントラ予測対象のブロックに隣接する上側のブロックの、前記イントラ予測対象のブロックに隣接する下端の水平方向の符号化処理された後の画像の画素データとを利用して、前記イントラ予測対象のブロックについてイントラ予測し、(2)前記マクロブロックを構成する16個のブロックのうちの前記4個のイントラ予測対象のブロックを除く12個のイントラ予測対象のブロックについては、前記イントラ予測対象のブロックに隣接する上側のブロックの、前記イントラ予測対象のブロックに隣接する下端の水平方向の符号化処理された後の画像の画素データと、前記イントラ予測対象のブロックに隣接する左側のブロックの、前記イントラ予測対象のブロックに隣接する右端の垂直方向の符号化処理された後の画像の画素データとを利用して、前記イントラ予測対象のブロックについてイントラ予測してもよい。

【0042】

10

20

30

40

50

前記矩形領域は4画素×4ラインのブロックであって、前記記憶手段は、前記マクロブロックを構成する16個のイントラ予測対象のブロックそれぞれについて、前記イントラ予測対象のブロックに隣接する上側のブロックの、前記イントラ予測対象のブロックに隣接する下端の水平方向の原画の画素データを記憶し、前記イントラ予測手段は、前記記憶手段に記憶されている前記画素データと、前記イントラ予測対象のブロックに隣接する左側のブロックの、前記イントラ予測対象のブロックに隣接する右端の垂直方向の符号化処理された後の画像の画素データとを利用して、前記イントラ予測対象のブロックについてイントラ予測してもよい。

#### 【0043】

本発明の画像符号化装置は、画像内のマクロブロックについてイントラ予測し、前記画像を符号化する装置であって、前記マクロブロックについてイントラ予測するイントラ予測手段と、前記マクロブロックに対応する色差についてのサブブロックの色差についての予測モードとして、前記マクロブロックの輝度についてイントラ予測されて得られた予測モードの内容と同じ内容の予測モードを割り当てる割り当て手段とを備える。10

#### 【0044】

前記イントラ予測手段は、前記マクロブロックを構成する各サブブロックの輝度についてイントラ予測するとともに、前記マクロブロックに対応する色差についてのサブブロックの特定のブロックの色差についてイントラ予測し、前記マクロブロックにおいて、前記色差についてのサブブロックにおいて前記特定のブロックが存在する位置と相対的に同じ位置に存在する、前記マクロブロックを構成する特定のサブブロックの輝度についてイントラ予測されて得られた予測モードの内容と、前記特定のブロックの色差についてイントラ予測されて得られた予測モードの内容とが同じ場合、前記割り当て手段は、前記色差についてのサブブロックを構成する一のブロックの色差についての予測モードとして、前記マクロブロックにおける、前記色差についてのサブブロックにおいて前記一のブロックが存在する位置と相対的に同じ位置に存在する、前記マクロブロックを構成するサブブロックの輝度についてイントラ予測されて得られた予測モードの内容と同じ内容の予測モードを割り当てもよい。20

#### 【0045】

本発明の画像符号化装置は、画像内のマクロブロックについてイントラ予測し、前記画像を符号化する装置であって、前記マクロブロックについてイントラ予測するイントラ予測手段と、第1のマクロブロックを構成する第1の特定のサブブロックの輝度についての予測モードと、前記第1のマクロブロックより後にイントラ予測される、前記第1のマクロブロックに隣接する第2のマクロブロックのブロックにおいて、前記第1のマクロブロックにおいて前記第1の特定のサブブロックが存在する位置と相対的に同じ位置に存在する第2の特定のサブブロックの輝度についてイントラ予測されて得られた予測モードとが同じ場合、前記第2のマクロブロックの色差についての予測モードとして、前記第1のマクロブロックの色差についての予測モードを割り当てる割り当て手段とを備える。30

#### 【0046】

本発明は、本発明の画像符号化装置の特徴的な構成手段をステップとする方法として実現したり、それらのステップをコンピュータに実行させるプログラムとして実現したり、上記特徴的な構成手段を含む集積回路として実現することもできる。上記のプログラムは、CD-ROM等の記録媒体や通信ネットワーク等の伝送媒体を介して流通させることもできる。40

#### 【発明の効果】

#### 【0047】

本発明は、より少ないサイクル数で負荷が大きいたイントラ予測処理を行なうとともに、H.264の規格に準拠した画像復号化装置が復号化することができる符号化データを生成する画像符号化装置を提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0048】

以下に、本発明を実施するための最良の形態について、図面を参照して説明する。

【0049】

(実施の形態1)

先ず、実施の形態1の画像符号化装置を説明する。

【0050】

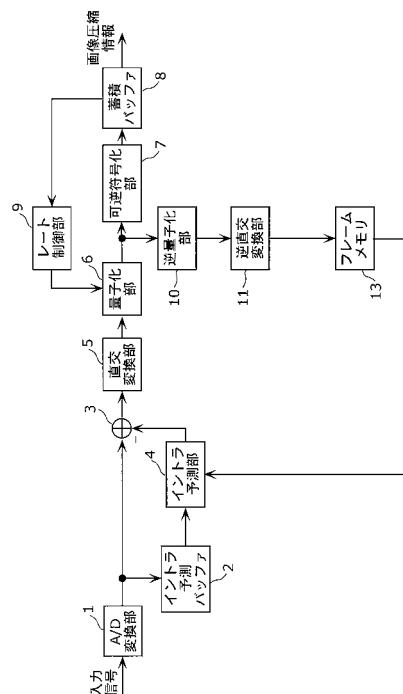

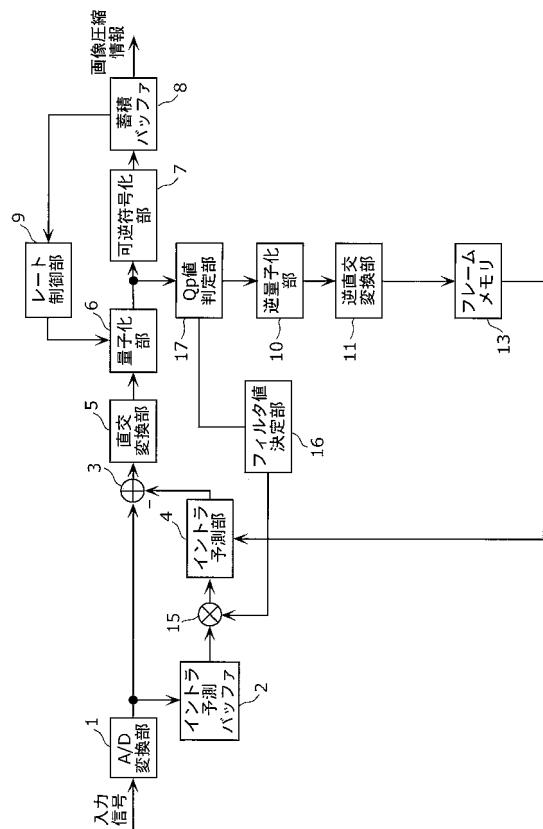

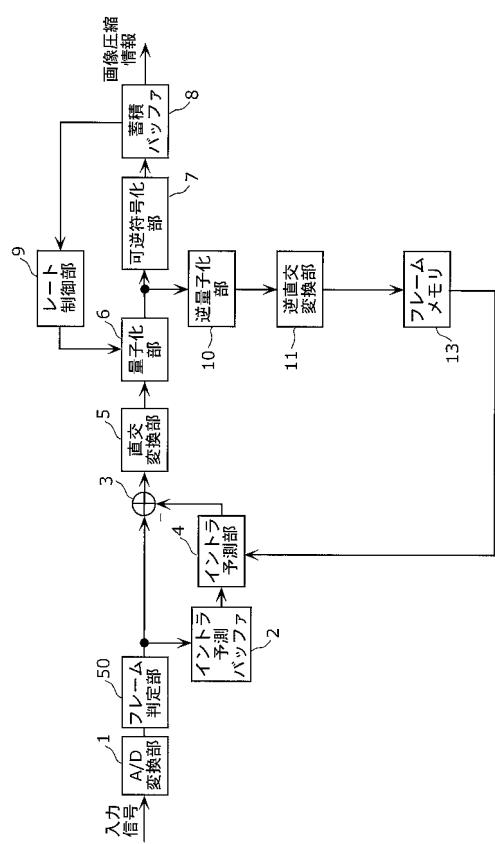

図1は、実施の形態1の画像符号化装置の構成を示すブロック図である。実施の形態1の画像符号化装置は、イントラ予測処理をより効率的にパイプライン化して実行する装置であって、A/D変換部1と、イントラ予測バッファ2と、減算部3と、イントラ予測部4と、直交変換部5と、量子化部6と、可逆符号化部7と、蓄積バッファ8と、レート制御部9と、逆量子化部10と、逆直交変換部11と、フレームメモリ13とを備える。

10

【0051】

次に、各構成部の機能を説明する。

A/D変換部1は、アナログの画像信号をデジタルの画像信号に変換する。イントラ予測バッファ2は、イントラ予測処理に必要な、予測対象ブロックの左側に隣接するラインの原画データを一時的に記憶する。減算部3は、入力されるデジタルの画像信号から、イントラ予測部4によって得られた画像信号を減算する。イントラ予測部4は、イントラ予測バッファ2から入力される、予測対象ブロックの左側に隣接するラインの原画データと、フレームメモリ13から入力される、逆直交変換(IFT)された、予測対象ブロックの上側に隣接する処理画のデータとに基づいて、4画素×4ラインのブロック又は16画素×16ラインのマクロブロックについてイントラ予測する。

20

【0052】

直交変換部5は、減算部3によって得られたデータを直交変換する。量子化部6は直交変換されたデータを量子化する。可逆符号化部7は、量子化されたデータを可逆符号化する構成部であって、情報量を保持しつつ符号量を少なくする。蓄積バッファ8は、可逆符号化された画像データを一時的にバッファリングする構成部であって、次段の処理速度と歩調を合わせるために使用される。レート制御部9は、蓄積バッファ8の空き容量等をモニタすることにより、量子化部6に対して、量子化速度や量子化精度を指示して処理レートの歩調を制御する。

【0053】

逆量子化部10は、量子化部6によって量子化されたデータを逆量子化して量子化される前のデータに戻す。逆直交変換部11は、逆量子化部10からのデータを逆直交変換して処理画を生成する。フレームメモリ13は、処理画のデータを一時的に記憶する構成部であって、そのデータを次段のイントラ予測部4に与えるためのメモリである。

30

【0054】

次に、実施の形態1の画像符号化装置の特徴的な部分の動作を説明する。

A/D変換部1は、入力されたアナログの画像信号をデジタルの画像信号に変換する。次に、イントラ予測バッファ2は、予測対象の4画素×4ラインのブロックの左側に隣接するブロックの右側1ラインの原画データを一時的に記憶する。具体的には、図2に示すように、イントラ予測バッファ2は、第0ブロックが含まれるマクロブロックの左側のマクロブロックの一部である、第0ブロックの左に隣接するブロックの一一番右端1ラインの原画データと、第0ブロックの一一番右端1ラインの原画データと、第1ブロックの一一番右端1ラインの原画データと、第4ブロックの一一番右端1ラインの原画データと、第2ブロックが含まれるマクロブロックの左側のマクロブロックの一部である、第2ブロックの左に隣接するブロックの一一番右端1ラインの原画データと、第2ブロックの一一番右端1ラインの原画データと、第3ブロックの一一番右端1ラインの原画データと、第6ブロックの一一番右端1ラインの原画データと、第8ブロックが含まれるマクロブロックの左側のマクロブロックの一部である、第8ブロックの左に隣接するブロックの一一番右端1ラインの原画データと、第8ブロックの一一番右端1ラインの原画データと、第9ブロックの一一番右端1ラインの原画データと、第12ブロックの一一番右端1ラインの原画データと、第10ブロックが含まれるマクロブロックの左側のマクロブロックの一部である、第10ブロック

40

50

の左に隣接するブロックの一番右端 1 ラインの原画データと、第 10 ブロックの一番右端 1 ラインの原画データと、第 11 ブロックの一番右端 1 ラインの原画データと、第 14 ブロックの一番右端 1 ラインの原画データとを、一時的に記憶する。

#### 【 0 0 5 5 】

イントラ予測部 4 は、各ブロックについて、イントラ予測バッファ 2 に記憶しているデータと、予測対象ブロックより前に符号化された処理画の水平方向の画素データとを利用して、イントラ予測を行なう。

#### 【 0 0 5 6 】

これにより、イントラ予測部 4 は、予測対象ブロックのイントラ予測処理 ( I P D 及び T / Q / i Q / i T ) を、予測対象ブロックの左隣のブロックの処理の終了を待つことなく、イントラ予測バッファ 2 に一時的に記憶されている、ライン方向の原画データを利用することにより開始することができる。したがって、図 3 に示すように、イントラ予測部 4 は、4 パイプラインにより、第 0 ブロック、第 1 ブロック、第 4 ブロック、及び第 5 ブロックの I P D を同時に開始することができる。

#### 【 0 0 5 7 】

イントラ予測部 4 は、第 0 ブロックのイントラ予測処理が終了した後、第 0 ブロックの処理により得られた画像のデータと、第 2 ブロックの左に隣接するマクロブロックの一番右端 1 ラインの原画データとを使用することにより、第 2 ブロックの I P D を開始することができる。

#### 【 0 0 5 8 】

同様に、イントラ予測部 4 は、第 2 ブロックのイントラ予測処理が終了した後、第 2 ブロックの処理により得られた画像のデータと、第 8 ブロックの左に隣接するマクロブロックの一番右端 1 ラインの原画データとを使用することにより、第 8 ブロックの I P D を開始することができる。第 10 ブロックについては、イントラ予測部 4 は、第 8 ブロックのイントラ予測処理が終了した後、第 8 ブロックの処理により得られた画像のデータと、第 10 ブロックの左に隣接するマクロブロックの一番右端 1 ラインの原画データとを使用することにより、第 10 ブロックの I P D を開始することができる。

#### 【 0 0 5 9 】

つまり、第 2 ブロックのイントラ予測処理は、第 0 ブロックのイントラ予測処理が終了すれば開始することができ、第 8 ブロックのイントラ予測処理は、第 2 ブロックのイントラ予測処理が終了すれば開始することができ、第 10 ブロックのイントラ予測処理は、第 8 ブロックのイントラ予測処理が終了すれば開始することができる。

#### 【 0 0 6 0 】

同様に、第 3 ブロックのイントラ予測処理は、第 1 ブロックのイントラ予測処理が終了すれば開始することができ、第 9 ブロックのイントラ予測処理は、第 3 ブロックのイントラ予測処理が終了すれば開始することができ、第 11 ブロックのイントラ予測処理は、第 9 ブロックのイントラ予測処理が終了すれば開始することができる。同様に、第 6 ブロックのイントラ予測処理は、第 4 ブロックのイントラ予測処理が終了すれば開始することができ、第 12 ブロックのイントラ予測処理は、第 6 ブロックのイントラ予測処理が終了すれば開始することができ、第 14 ブロックのイントラ予測処理は、第 12 ブロックのイントラ予測処理が終了すれば開始することができる。更に、第 7 ブロックのイントラ予測処理は、第 5 ブロックのイントラ予測処理が終了すれば開始することができ、第 13 ブロックのイントラ予測処理は、第 7 ブロックのイントラ予測処理が終了すれば開始することができ、第 15 ブロックのイントラ予測処理は、第 13 ブロックのイントラ予測処理が終了すれば開始することができる。

#### 【 0 0 6 1 】

また、上述したように、イントラ予測部 4 は、第 0 ブロック、第 1 ブロック、第 4 ブロック、及び第 5 ブロックのイントラ予測処理を同時に開始することができる。したがって、イントラ予測部 4 は、第 2 ブロック、第 3 ブロック、第 6 ブロック、及び第 7 ブロックのイントラ予測処理を、同時に開始することができる。同様に、イントラ予測部 4 は、第

10

20

30

40

50

8 ブロック、第 9 ブロック、第 12 ブロック、及び第 13 ブロックのイントラ予測処理を、同時に開始することができる。更に、イントラ予測部 4 は、第 10 ブロック、第 11 ブロック、第 14 ブロック、及び第 15 ブロックのイントラ予測処理を、同時に開始することができます。

#### 【 0 0 6 2 】

したがって、イントラ予測部 4 は、4 個のブロックのイントラ予測処理を同時に開始することができるので、図 3 に示すように、1 個のマクロブロックのイントラ予測処理 (I P D 及び T / Q / i Q / i T) を、4 パイプラインにより 4 サイクルで完了することができます。

#### 【 0 0 6 3 】

このように、実施の形態 1 の画像符号化装置は、イントラ予測処理の負荷を分散し、イントラ予測処理のパイプライン化を実現している。これにより、サイクル数を従来より減らすことができ、消費電力を低減することができる。

#### 【 0 0 6 4 】

なお、実施の形態 1 におけるブロックは、「矩形領域」の一例である。

また、実施の形態 1 では、イントラ予測バッファ 2 は、予測対象の 4 画素 × 4 ラインのブロックの左側に隣接するブロックの右側 1 ラインの原画データを一時的に記憶する。しかしながら、イントラ予測バッファ 2 は、予測対象の 4 画素 × 4 ラインのブロックの上側に隣接するブロックの下側 1 ラインの原画データを一時的に記憶してもよい。この場合、イントラ予測部 4 は、各ブロックについて、イントラ予測バッファ 2 に記憶しているデータと、予測対象ブロックより前に符号化された処理画の垂直方向の画素データとを利用して、イントラ予測を行なう。

#### 【 0 0 6 5 】

(実施の形態 2 )

次に、実施の形態 2 の画像符号化装置を説明する。

#### 【 0 0 6 6 】

実施の形態 2 の画像符号化装置の構成は、実施の形態 1 の画像符号化装置の構成と同様であるので、その説明を省略する。但し、イントラ予測バッファ 2 に一時的に記憶される原画データがイントラ予測処理対象マクロブロックの左に隣接するマクロブロックの一一番右のラインのデータのみである点が、実施の形態 1 と異なる。

#### 【 0 0 6 7 】

図 4 は、実施の形態 2 におけるブロックの処理順を示す図である。

次に、実施の形態 2 の画像符号化装置の特徴的な部分の動作を説明する。

#### 【 0 0 6 8 】

A / D 変換部 1 は、入力されたアナログの画像信号をデジタルの画像信号に変換する。次に、イントラ予測バッファ 2 は、予測対象の 4 画素 × 4 ラインのブロックの左に隣接するブロックの右端 1 ラインの原画データを一時的に記憶する。具体的には、図 4 に示すように、イントラ予測バッファ 2 は、第 0 ブロックが含まれるマクロブロックの左側のマクロブロックの一部である、第 0 ブロックの左に隣接するブロックの一一番右端 1 ラインの原画データと、第 2 ブロックが含まれるマクロブロックの左側のマクロブロックの一部である、第 2 ブロックの左に隣接するブロックの一一番右端 1 ラインの原画データと、第 8 ブロックが含まれるマクロブロックの左側のマクロブロックの一部である、第 8 ブロックの左に隣接するブロックの一一番右端 1 ラインの原画データと、第 10 ブロックが含まれるマクロブロックの左側のマクロブロックの一部である、第 10 ブロックの左に隣接するブロックの一一番右端 1 ラインの原画データとを、一時的に記憶する。

#### 【 0 0 6 9 】

イントラ予測部 4 は、各ブロックについて、イントラ予測バッファ 2 に記憶しているデータと、予測対象ブロックより前に符号化された処理画の水平方向の画素データ（原画データ）とを利用して、イントラ予測を行なう。

#### 【 0 0 7 0 】

10

20

30

40

50

これにより、イントラ予測部4は、予測対象ブロックのイントラ予測処理(IPP及びT/Q/iQ/iT)を、予測対象ブロックの左隣のブロックの処理の終了を待つことなく、イントラ予測バッファ2に一時的に記憶されている、ライン方向の原画データを利用することにより、実行することができる。

#### 【0071】

したがって、図5に示すように、イントラ予測部4は、第0ブロックのイントラ予測処理が終了した後、第0ブロックの処理により得られた画像のデータと、第2ブロックの左に隣接するマクロブロックの一番右端1ラインの原画データとを使用することにより、第2ブロックのIPPを開始することができる。同様に、イントラ予測部4は、第2ブロックのイントラ予測処理が終了した後、第2ブロックの処理により得られた画像のデータと、第8ブロックの左に隣接するマクロブロックの一番右端1ラインの原画データとを使用することにより、第8ブロックのIPPを開始することができる。更に、イントラ予測部4は、第8ブロックのイントラ予測処理が終了した後、第8ブロックの処理により得られた画像のデータと、第10ブロックの左に隣接するマクロブロックの一番右端1ラインの原画データとを使用することにより、第10ブロックのIPPを開始することができる。

#### 【0072】

第1ブロックについては、イントラ予測部4は、第1ブロックに隣接する上のブロックのイントラ予測処理が終了するとともに、第0ブロックのイントラ予測処理が終了した後、イントラ予測処理を開始することができる。第3ブロックについては、イントラ予測部4は、第1ブロック及び第0ブロックのイントラ予測処理が終了した後、イントラ予測処理を開始することができる。第9ブロックについては、イントラ予測部4は、第3ブロック及び第8ブロックのイントラ予測処理が終了した後、イントラ予測処理を開始することができる。第11ブロックについては、イントラ予測部4は、第9ブロック及び第10ブロックのイントラ予測処理が終了した後、イントラ予測処理を開始することができる。第4ブロック、第6ブロック、第12ブロック、第14ブロック、第5ブロック、第7ブロック、第13ブロック、及び第15ブロックについても同様にして、イントラ予測部4は、各ブロックの上及び左のイントラ予測処理が終了した後、イントラ予測処理を開始することができる。

#### 【0073】

したがって、イントラ予測部4は、図5に示すように、4個のブロックのイントラ予測処理(IPP及びT/Q/iQ/iT)を順次開始することが可能であり、このため、1個のマクロブロックのイントラ予測処理を、4パイプラインにより7サイクルで完了することができる。

#### 【0074】

(実施の形態3)

次に、実施の形態3の画像符号化装置を説明する。

#### 【0075】

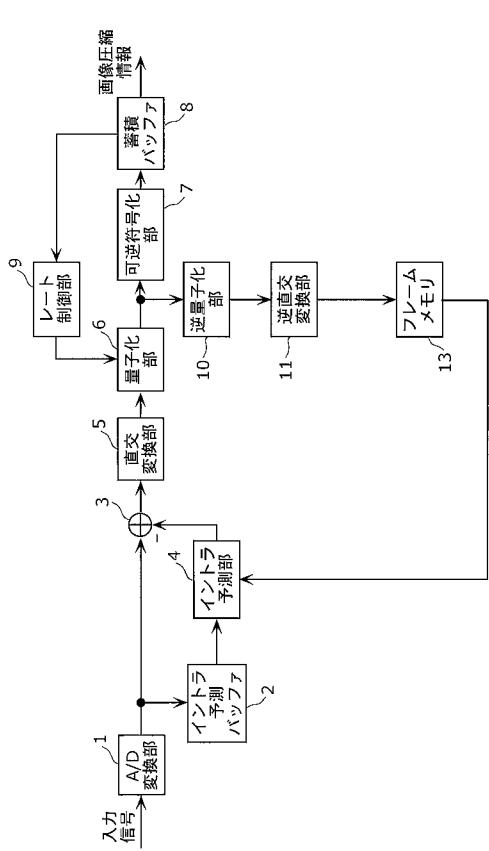

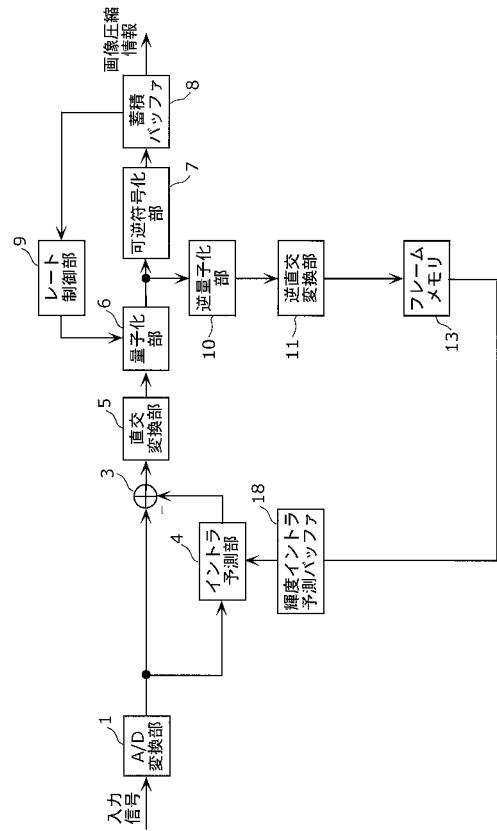

図6は、実施の形態3の画像符号化装置の構成を示すブロック図である。実施の形態3の画像符号化装置は、実施の形態1の画像符号化装置の全部の構成部に、フィルタ15、フィルタ値決定部16、及びQp値判定部17が追加された装置である。実施の形態3では、実施の形態1で説明した構成部と同じ構成部については説明を省略する。

#### 【0076】

次に、フィルタ15、フィルタ値決定部16、及びQp値判定部17の機能を説明する。

#### 【0077】

Qp値判定部17は、量子化部6により生成された量子化値Qpが閾値kより大きいか否かを判定する。フィルタ値決定部16は、Qp値判定部17によって得られた判定結果に基づいて、フィルタ乗数(補正データ)を決定する。フィルタ15は、イントラ予測バッファ2に一時的に記憶された、予測対象ブロックの左に隣接したマクロブロックの原画ラインデータに、フィルタ値決定部16によって得られたフィルタ乗数を乗算するこ

とにより、原画ラインデータをフィルタリングする。

#### 【0078】

次に、実施の形態3の画像符号化装置の特徴的な部分の動作を説明する。

実施の形態1の画像符号化装置は、予測対象ブロックの左隣のランデータとして原画データ（原画ラインデータ）を使用する。ところで、量子化部6によって得られた量子化値 $Q_p$ が閾値 $k$ を越えると、イントラ予測により得ようとする画素値が、その画素値を原画ラインデータを利用することにより予測する場合、 $T/Q/iQ/iT$ が施された処理画のデータを利用することにより予測する場合に比べて、大きく異なることがある。この場合、原画ラインデータを利用することにより行なったイントラ予測の結果を利用すると、最終的に得られる符号量が増加したり、復号画像の質が劣ることがありうる。

10

#### 【0079】

そこで、 $Q_p$ 値判定部17が、量子化値 $Q_p$ が閾値 $k$ より大きいと判定した場合、フィルタ値決定部16は、原画がローパスフィルタ処理されるように、フィルタ乗数を決定する。フィルタ15は、図7に示すように、イントラ予測バッファ2に一時的に記憶された、予測対象ブロックの左に隣接したマクロブロックの原画ラインデータに、フィルタ値決定部16によって得られたフィルタ乗数を乗算することにより、原画ラインデータをフィルタリングして原画の解像度を低下し、フィルタ処理画を生成する。これにより、最終的に得られる符号量が増加したり、復号画像の質が劣るという問題は生じない。

#### 【0080】

なお、 $Q_p$ 値判定部17が、量子化値 $Q_p$ が閾値 $k$ 以下であると判定した場合、フィルタ15から出力されるラインデータは原画ラインデータである。

20

#### 【0081】

なお、図8に示すように、実施の形態3のパイプラインの段数は実施の形態1と同じ4であり、実施の形態3のイントラ予測処理（IPD及び $T/Q/iQ/iT$ ）のサイクル数も、実施の形態1と同じ4である。

#### 【0082】

##### （実施の形態4）

次に、実施の形態4の画像符号化装置を説明する。

#### 【0083】

図9は、実施の形態4の画像符号化装置の構成を示すブロック図である。実施の形態4の画像符号化装置は、実施の形態1の画像符号化装置のイントラ予測バッファ2に替わって、輝度イントラ予測バッファ18が設けられている装置である。実施の形態4では、実施の形態1で説明した構成部と同じ機能を有する構成部については説明を省略する。

30

#### 【0084】

次に、輝度イントラ予測バッファ18及びイントラ予測部4の機能を説明する。

輝度イントラ予測バッファ18は、16画素×16ラインのマクロブロックについて輝度のイントラ予測が行なわれた結果を保持するバッファである。イントラ予測部4は、16画素×16ラインのマクロブロックについて輝度のイントラ予測を行なう機能を有する。また、イントラ予測部4は、輝度イントラ予測バッファ18から輝度のイントラ予測に関する情報を入手すると、色差のイントラ予測に関しては、輝度のイントラ予測によって決定された予測モードを用いてイントラ予測を行なう機能をも有する。

40

#### 【0085】

次に、実施の形態4の画像符号化装置の特徴的な部分の動作を説明する。

イントラ予測部4は、図10に示す輝度（Y）の16画素×16ラインのマクロブロックについて、輝度のイントラ予測を行なう。輝度イントラ予測バッファ18は、イントラ予測部4によって行なわれた、輝度についてのイントラ予測の結果（決定された予測モード）を保持する。

#### 【0086】

イントラ予測部4は、イントラ予測対象のマクロブロックの色差（Cr, Cb）についてのイントラ予測の予測モードとして、輝度イントラ予測バッファ18に保持されている

50

予測モードの内容と同じ内容の予測モード、すなわち、輝度についての予測モードの内容と同じ内容の予測モードを割り当てる。色差( $C_r, C_b$ )についてのイントラ予測が省略されるので、イントラ予測処理の高速化が実現される。

#### 【0087】

なお、イントラ予測部4は、図10に示す輝度のマクロブロックを構成する4個の8画素×8ラインのサブブロックそれぞれについて、輝度のイントラ予測を行ない、輝度イントラ予測バッファ18は、イントラ予測部4によって行なわれた、4個のサブブロックそれぞれについての予測モードを保持してもよい。その場合、イントラ予測部4は、色差についてのイントラ予測対象領域であるサブブロックを構成する4個のブロックのうちの特定のブロック(例えば、第0ブロック)について、色差のイントラ予測を行ない、予測モードを決定する。イントラ予測部4は、輝度についての特定のサブブロック(例えば、第0サブブロック)の予測モードの内容と、色差についての特定のブロック(例えば、第0ブロック)の予測モードの内容とが同じであるか否かを判定する。輝度についての特定のサブブロックの予測モードの内容と、色差についての特定のブロックの予測モードの内容とが同じである場合、イントラ予測部4は、色差についての特定のブロック以外のブロック(例えば、第1ブロック)の予測モードとして、そのブロックに対応する輝度のサブブロック(例えば、第1サブブロック)の予測モードの内容と同じ内容の予測モードを割り当てもよい。このようにして色差についてのイントラ予測の一部を省略してもよい。

#### 【0088】

輝度についての特定のサブブロックの予測モードの内容と、色差についての特定のブロックの予測モードの内容とが異なる場合、イントラ予測部4は、色差についての各ブロックについてイントラ予測する。

#### 【0089】

特定のサブブロックは、第0サブブロックに限られず、第1サブブロック、第2サブブロック、及び第3サブブロックのいずれでもよい。また、特定のブロックは、第0ブロックに限られず、第1ブロック、第2ブロック、及び第3ブロックのいずれでもよい。要するに、特定のサブブロック及び特定のブロックは、イントラ予測領域の相対的に同じ位置に存在する、サブブロック及びブロックであればよい。

#### 【0090】

また、イントラ予測部4が隣接するマクロブロックについてイントラ予測し、先に予測する方のマクロブロックについて、輝度のイントラ予測及び色差のイントラ予測が終了している場合を想定する。ここで、後に予測する方のマクロブロック内の特定のサブブロックの輝度のイントラ予測によって決定された予測モードと、先に予測する方のマクロブロック内の特定のサブブロックの輝度のイントラ予測によって決定された予測モードとが同じ場合、イントラ予測部4は、後に予測する方のサブブロックの色差のイントラ予測の予測モードとして、先に予測する方の対応するサブブロックの色差のイントラ予測の予測モードを割り当てもよい。

#### 【0091】

特定のサブブロックは、第0サブブロック、第1サブブロック、第2サブブロック、及び第3サブブロックのいずれでもよい。また、対応するサブブロックとは、イントラ予測領域の相対的に同じ位置に存在するサブブロックを意味する。例えば、先に予測する方のマクロブロックの第2サブブロックと、後に予測する方のマクロブロックの第2サブブロックとが対応する。

#### 【0092】

なお、上述した実施の形態1から3において、ブロックは、サブブロック又はマクロブロックに置き換えられて、ブロックと同様に、サブブロック又はマクロブロックに対してイントラ予測が行なわれてもよい。

#### 【0093】

また、上述した実施の形態1において各ブロックについてイントラ予測を行なう際、そのブロックが含まれる画像がフレームである場合、上述した実施の形態1において説明し

10

20

30

40

50

たようにイントラ予測を行なう。他方、イントラ予測対象のブロックが含まれる画像がフィールドである場合、上述した実施の形態1において説明したイントラ予測を行なわず、通常のイントラ予測を行なう。したがって、図12に示すように、画像符号化装置は、画像がフレームであるのかフィールドであるのかを判定するフレーム判定部50を有してもよい。

#### 【0094】

更に、実施の形態1から3では、イントラ予測時に原画を用いる場合を説明した。予測モード決定後に符号化する際、原画を用いて符号化してもよいし、符号化処理された後の画像を用いて符号化してもよい。

#### 【産業上の利用可能性】

#### 【0095】

本発明の画像符号化装置は、イントラ予測を行なって画像を符号化する装置、例えばDVD録画再生装置等として有用である。

#### 【図面の簡単な説明】

#### 【0096】

#### 【図1】実施の形態1の画像符号化装置の構成を示すブロック図

【図2】実施の形態1において、1個のマクロブロックをイントラ予測処理する際の各ブロックの処理順を示す図

#### 【図3】実施の形態1において、各ブロックの処理のタイミングを示す図

【図4】実施の形態2において、1個のマクロブロックをイントラ予測処理する際の各ブロックの処理順を示す図

#### 【図5】実施の形態2において、各ブロックの処理のタイミングを示す図

#### 【図6】実施の形態3の画像符号化装置の構成を示すブロック図

【図7】実施の形態3において、1個のマクロブロックをイントラ予測処理する際の各ブロックの処理順を示す図

#### 【図8】実施の形態3において、各ブロックの処理のタイミングを示す図

#### 【図9】実施の形態4の画像符号化装置の構成を示すブロック図

【図10】実施の形態4において、1個のマクロブロックについて、輝度のイントラ予測処理する際の各サブブロックの処理順を示す図

【図11】実施の形態4において、1個のマクロブロックについて、色差のイントラ予測処理する際の各サブブロックの処理順を示す図

【図12】処理対象の画像がフレームであるのかフィールドであるのかを判断してイントラ予測する画像符号化装置の構成を示すブロック図

【図13】H.264規格の4画素×4ラインの16個のブロックのイントラ予測を実行する際の処理順を示す図

#### 【図14】H.264規格の1個のブロックのイントラ予測を説明するための図

#### 【図15】H.264規格における、各ブロックの処理のタイミングを示す図

【図16】H.264規格における、16画素×16ラインの1個のマクロブロックの輝度についてのイントラ予測を説明するための図

【図17】H.264規格における、8画素×8ラインの1個のサブブロックの色差についてのイントラ予測を説明するための図

#### 【図18】特許文献1に記載の画像符号化装置の構成を示すブロック図

#### 【図19】特許文献1に記載の画像復号化装置の構成を示すブロック図

#### 【図20】特許文献1に記載の各ブロックの第1の処理順を示す図

#### 【図21】特許文献1に記載の各ブロックの第1の処理のタイミングを示す図

#### 【図22】特許文献1に記載の各ブロックの第2の処理順を示す図

#### 【図23】特許文献1に記載の各ブロックの第2の処理のタイミングを示す図

#### 【図24】特許文献2に記載のイントラ予測装置の構成を示す図

#### 【図25】特許文献2に記載のイントラ予測装置の動作手順を示すフローチャート

#### 【図26】特許文献2に記載の各ブロックの処理順を示す図

10

20

30

40

50

【図27】特許文献2に記載の各ブロックの処理のタイミングを示す図

## 【符号の説明】

## 【0097】

- 1 A / D 変換部

- 2 イントラ予測バッファ

- 3 減算部

- 4 イントラ予測部

- 5 直交変換部

- 6 量子化部

- 7 可逆符号化部

- 8 蓄積バッファ

- 9 レート制御部

- 10 逆量子化部

- 11 逆直交変換部

- 13 フレームメモリ

- 15 フィルタ

- 16 フィルタ値決定部

- 17 Q p 値判定部

- 18 輝度イントラ予測バッファ

- 50 フレーム判定部

10

20

【図1】

【 四 4 】

【 図 5 】

〔 図 7 〕

【 図 8 】

【 四 6 】

【 四 9 】

【 10 】

【 図 1 1 】

【 図 1 3 】

【 四 1 4 】

【 図 1 2 】

【 図 1 5 】

【図16】

【図17】

【図19】

【図18】

【図20】

【図21】

【図22】

|    |    |    |    |

|----|----|----|----|

| 0  | 1  | 3  | 5  |

| 2  | 4  | 6  | 8  |

| 7  | 9  | 11 | 13 |

| 10 | 12 | 14 | 15 |

【図24】

【図23】

| T/Q/iQ/IT | IPD 0 | 1 | 3  | 5  | 8  | 13 | 15 |

|-----------|-------|---|----|----|----|----|----|

| T/Q/iQ/IT | 0     | 1 | 3  | 5  | 8  | 13 | 15 |

| T/Q/iQ/IT | 2     | 4 | 6  | 11 | 14 |    |    |

| T/Q/iQ/IT | 7     | 9 | 12 |    |    |    |    |

| T/Q/iQ/IT | 10    |   |    |    |    |    |    |

1                    7

【図25】

【図26】

|    |    |    |    |

|----|----|----|----|

| 0  | 1  | 2b | 3b |

| 2a | 3a | 4b | 5b |

| 4a | 5a | 6b | 7b |

| 6a | 7a | 8  | 9  |

【図27】

| T/Q/iQ/IT | IPD 0 | 1  | 2a | 3a | 4a | 5a | 6a | 7a | 8 | 9 |

|-----------|-------|----|----|----|----|----|----|----|---|---|

| T/Q/iQ/IT | 0     | 1  | 2a | 3a | 4a | 5a | 6a | 7a | 8 | 9 |

| T/Q/iQ/IT | 2b    | 3b | 4b | 5b | 5b | 7b |    |    |   |   |

| T/Q/iQ/IT |       |    |    |    |    |    |    |    |   |   |

| T/Q/iQ/IT |       |    |    |    |    |    |    |    |   |   |

1                    10

---

フロントページの続き

(72)発明者 津田 賢治郎

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 重里 達郎

大阪府門真市大字門真1006番地 松下電器産業株式会社内

F ターム(参考) 5C059 KK14 KK49 MA00 MA04 MA21 MC11 MC38 ME01 PP16 TA29

TA30 TA69 TB07 TB08 TC02 TC06 TC42 UA02 UA05 UA12

5J064 AA03 BB03 BC01 BC11 BC14 BC16