(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7011149号

(P7011149)

(45)発行日 令和4年1月26日(2022.1.26)

(24)登録日 令和4年1月18日(2022.1.18)

(51)国際特許分類

|        |                 |        |       |   |

|--------|-----------------|--------|-------|---|

| H 05 B | 33/26 (2006.01) | H 05 B | 33/26 | Z |

| H 01 L | 51/50 (2006.01) | H 05 B | 33/14 | A |

| H 01 L | 27/32 (2006.01) | H 01 L | 27/32 |   |

| H 05 B | 33/12 (2006.01) | H 05 B | 33/12 | B |

| H 05 B | 33/22 (2006.01) | H 05 B | 33/22 | Z |

請求項の数 19 (全25頁) 最終頁に続く

(21)出願番号 特願2017-136830(P2017-136830)

(22)出願日 平成29年7月13日(2017.7.13)

(65)公開番号 特開2018-88391(P2018-88391A)

(43)公開日 平成30年6月7日(2018.6.7)

審査請求日 令和2年7月8日(2020.7.8)

(31)優先権主張番号 特願2016-239858(P2016-239858)

(32)優先日 平成28年11月22日(2016.11.22)

(33)優先権主張国・地域又は機関

日本国(JP)

(73)特許権者 519380923

天馬微電子有限公司

中華人民共和国広東省深セン市竜華

区民治街道北駅社区留仙大道天馬大

力

1918

(74)代理人 110001678

特許業務法人藤央特許事務所

(72)発明者 松枝 洋二郎

神奈川県川崎市幸区鹿島田一丁目1番2

号 Tianma Japan 株式会社内

高取 憲一

神奈川県川崎市幸区鹿島田一丁目1番2

号 Tianma Japan 株式会社内

高橋 純平

(72)発明者

審査官

最終頁に続く

(54)【発明の名称】 表示装置及びその製造方法

## (57)【特許請求の範囲】

## 【請求項1】

絶縁基板と、

前記絶縁基板と対向する封止構造部と、

前記絶縁基板と前記封止構造部との間に配置された、複数の下部電極と、1つの上部電極と、それぞれが前記1つの上部電極と前記複数の下部電極のそれぞれとの間に配置された複数の有機発光層と、

前記封止構造部に向かって立ち上がる複数の穿孔壁と、

前記絶縁基板と前記下部電極との間に形成され、前記下部電極それぞれに供給する電流を制御する複数の回路と、

前記絶縁基板と前記下部電極との間に形成された、タッチパネル電極とを含み、

前記複数の穿孔壁の頂面は、前記複数の有機発光層の表面よりも高い位置にあり、

前記上部電極は、前記複数の有機発光層からの光を前記封止構造部に向けて透過させる電極であって、前記複数の穿孔壁それぞれが貫通するように形成されている孔を有し、

前記複数の穿孔壁の頂面に、前記上部電極の材料が残部として付着し、

前記上部電極の孔は、前記タッチパネル電極により形成される電界が通過する、表示装置。

## 【請求項2】

請求項1に記載の表示装置であって、

前記複数の下部電極は同一面上に配置され、1つの下部電極の上に1つの有機発光層が配置されている、表示装置。

**【請求項 3】**

請求項 1 に記載の表示装置であって、

前記 1 つの上部電極と、前記複数の下部電極と、前記有機発光層により、複数の有機発光素子が形成され、

前記有機発光素子の各々は、画素定義層により分離され、

前記穿孔壁は、前記画素定義層の面上に形成されている、表示装置。

**【請求項 4】**

請求項 1 に記載の表示装置であって、

前記複数の回路は、前記下部電極の下側に配置されている、表示装置。

**【請求項 5】**

請求項 1 に記載の表示装置であって、

さらに、前記電界の変化に基づき、前記封止構造部に対する指示体の接触位置を検出する検出回路を含む、表示装置。

**【請求項 6】**

請求項 1 に記載の表示装置であって、

前記複数の穿孔壁のそれぞれは、逆テーパ形状、順テーパ形状、又は垂直形状を有する、表示装置。

**【請求項 7】**

請求項 1 に記載の表示装置であって、

前記タッチパネル電極は、M o、W、N b、M o W又はM o N bで構成されている、表示装置。

10

**【請求項 8】**

請求項 1 に記載の表示装置であって、

前記タッチパネル電極は、前記絶縁基板と前記複数の回路との間に形成されている、表示装置。

**【請求項 9】**

請求項 8 に記載の表示装置であって、

前記複数の回路におけるチャネル部と接続するソース電極及びドレイン電極と、前記タッチパネル電極と接続するタッチパネル配線とは、同一金属層を含む、表示装置。

**【請求項 10】**

請求項 1 に記載の表示装置であって、

前記複数の穿孔壁のそれぞれは、前記下部電極の間に位置する、表示装置。

30

**【請求項 11】**

請求項 1 に記載の表示装置であって、

前記複数の穿孔壁は、一つの画素に対する穿孔壁の数が一定であるように、規則的に配列されている、表示装置。

**【請求項 12】**

請求項 2 に記載の表示装置であって、

さらに、前記電界の変化に基づき、前記封止構造部に対する指示体の接触位置を検出する検出回路に接続する第 1 配線と第 2 配線とを含み、

前記タッチパネル電極は、

前記絶縁基板上に形成された第 1 絶縁膜の上に形成され、

前記第 1 配線と電気的に接続する第 1 電極と、前記第 1 電極及び前記第 1 絶縁膜の上に形成された第 2 絶縁膜の上に形成され、前記第 2 配線と電気的に接続する第 2 電極と、を含み、

前記複数の回路は、前記第 2 絶縁膜及び前記第 2 電極の上に形成された第 3 絶縁膜と前記下部電極との間に形成されている、表示装置。

**【請求項 13】**

請求項 12 に記載の表示装置であって、

前記複数の回路は、前記第 3 絶縁膜の上に形成された半導体層と、前記半導体層及び前記

40

50

第3絶縁膜を覆う第4絶縁膜と、前記半導体層の上方であって前記第4絶縁膜の上に形成されたゲート電極と、前記ゲート電極及び前記第4絶縁膜を覆う第5絶縁膜と、前記第5絶縁膜の上に形成された平坦化膜と、を含む、表示装置。

【請求項14】

請求項13に記載の表示装置であって、

前記複数の下部電極と、前記第1配線の一部と、前記第2配線の一部とは、平坦化膜の上に形成され、

前記第1配線は、積層された前記第2～第5絶縁膜及び前記平坦化膜に形成されたホールを介して前記第1電極と電気的に接続し、

前記第2配線は、積層された前記第3～第5絶縁膜及び前記平坦化膜に形成されたホールを介して前記第2電極と電気的に接続する、表示装置。 10

【請求項15】

請求項13に記載の表示装置であって、

前記複数の下部電極は、前記平坦化膜の上に形成され、

前記第1配線の一部と、前記第2配線の一部とは、前記第5絶縁膜の上に形成され、

前記第1配線は、積層された前記第2～第5絶縁膜に形成されたホールを介して前記第1電極と電気的に接続し、

前記第2配線は、積層された前記第3～第5絶縁膜に形成されたホールを介して前記第2電極と電気的に接続する、表示装置。 20

【請求項16】

表示装置の製造方法であって、

絶縁基板上にタッチパネル電極を形成し、

前記絶縁基板上に複数の回路を形成し、

前記複数の回路より上層に、前記複数の回路それぞれに接続される複数の下部電極を形成し、

前記複数の下部電極より上層に、前記絶縁基板から立ち上がり、前記絶縁基板に対向する封止構造部と前記絶縁基板と間隔を維持するスペーサとなる、複数の穿孔壁を形成し、

前記複数の穿孔壁を形成した後に、前記複数の下部電極上有機発光層を形成し、

前記有機発光層及び前記複数の穿孔壁が露出した前記絶縁基板上に透明導電材料を付着することによって、前記透明導電材料の付着と同時に前記複数の穿孔壁それぞれが貫通する複数の孔を形成し、前記複数の孔を有し前記複数の下部電極に共通の上部電極を形成する、製造方法。 30

【請求項17】

絶縁基板と、

前記絶縁基板と対向する封止構造部と、

前記絶縁基板と前記封止構造部との間に配置された、複数の下部電極と、1つの上部電極と、それぞれが前記1つの上部電極と前記複数の下部電極のそれぞれとの間に配置された複数の有機発光層と、

前記絶縁基板と前記下部電極との間に形成され、前記下部電極それぞれに供給する電流を制御する複数の回路と、 40

前記絶縁基板と前記下部電極との間に形成された、タッチパネル電極と、

前記封止構造部と前記絶縁基板との間隔を維持する複数のスペーサと、を含み、

前記複数のスペーサは、前記上部電極を貫通して複数の孔を形成し、

前記複数のスペーサの頂面に、前記上部電極の材料が残部として付着し、

前記上部電極は、前記有機発光層が出射する光を前記封止構造部に向けて透過させる電極であり、

前記タッチパネル電極により形成される電界が、前記複数の孔を通過する表示装置。

【請求項18】

請求項1に記載の表示装置であって、

3色の副画素を含む複数の第1画素と、前記3色の副画素を前記第1画素とは異なる配置

で含む複数の第2画素とが、行及び列方向に互い違いに配列された表示部を含み、前記表示部は、複数の緑色の副画素と、複数の赤色の副画素と、複数の青色の副画素と、を含み、

前記複数の第1画素の各々は、前記複数の第1画素各々の第1列に配置され、列方向に隣接する1個の緑色の副画素と1個の赤色の副画素と、前記複数の第1画素各々の前記第1列に隣接する前記複数の第1画素各々の第2列に配置された1個の青色の副画素を含み、複数の前記第2画素の各々は、前記複数の第2画素各々の前記第1列に配置され、列方向に隣接する1個の緑色の副画素と1個の赤色の副画素と、前記複数の第2画素各々の前記第1列に隣接する複数の第2画素の前記第2列に配置された1個の青色の副画素を含み、前記複数の穿孔壁は、前記複数の第1画素及び前記複数の第2画素の前記第2列に配置され、前記複数の穿孔壁は奇数列と複数列とで非対称に配置され、

前記複数の緑色の副画素のそれぞれと、前記複数の赤色の副画素のそれぞれとは、同一の形状及び同一の寸法を備え、

前記複数の青色の副画素のそれぞれは、行方向に比べて列方向に長く、かつ、行方向の長さは前記緑色の副画素及び前記赤色の副画素それぞれの行方向の長さに比べて短く、

前記複数の青色の副画素は、奇数列と偶数列とで非対称に配置されており、

前記複数の第1画素各々の青色の副画素と、前記複数の第1画素各々に列方向に隣接する前記第2画素の青色の副画素とは、近接配置されてペアを構成し、

前記ペアは千鳥状に配置されており、

前記複数の緑色の副画素の各行は、前記行方向において直線的に配置された緑色の副画素からなり、

前記複数の赤色の副画素の各行は、前記行方向において直線的に配置された赤色の副画素からなる、表示装置。

#### 【請求項19】

請求項1に記載の表示装置であって、

3色の副画素を含む複数の画素が行及び列方向に配列された表示部を含み、

前記表示部は、複数の緑色の副画素と、複数の赤色の副画素と、複数の青色の副画素と、を含み、

前記複数の画素の各々は、前記複数の画素各々の第1列で列方向に隣接する1個の緑色の副画素と1個の赤色の副画素と、前記複数の画素各々の第2列に配置された1個の青色の副画素を含み、

前記複数の穿孔壁は、前記複数の画素の前記第2列に配置され、前記複数の穿孔壁は、前記青の副画素と列方向に交互に配置されるとともに、奇数列と偶数列とで対称に配置されており、

前記複数の緑色の副画素のそれぞれと、前記複数の赤色の副画素のそれぞれとは、同一の形状及び同一の寸法を備え、

前記複数の青色の副画素のそれぞれは、行方向に比べて列方向に長く、かつ、行方向の長さは前記複数の緑色の副画素及び前記複数の赤色の副画素それぞれの行方向の長さに比べて短く、

前記複数の青色の副画素は、奇数列と偶数列とで対称に配置されており、

前記複数の緑色の副画素、前記複数の赤色の副画素、前記複数の青色の副画素及び前記穿孔壁は、行方向において、それぞれ直線的に配置されている、表示装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本開示は、表示装置及びその製造方法に関する。

##### 【背景技術】

##### 【0002】

タッチパネルを備えた液晶表示装置が提案されている（特開2014-219606号公報参照）。かかる表示装置では、例えば装置サイズを縮小するためや、部品点数を少なく

するために、構造を単純にすることが望まれる。

【0003】

また、液晶表示装置に替わり、アクティブマトリックス型のOLED (Organic Light-Emitting Diode) 表示装置が提案されている。

【先行技術文献】

【特許文献】

【0004】

【文献】特開2014-219606号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

タッチパネルを備えた、アクティブマトリックス型のOLED表示装置の構造を単純にすることが望まれる。

【課題を解決するための手段】

【0006】

本実施の形態の表示装置の一態様は、絶縁基板と、前記絶縁基板と対向する封止構造部と、前記絶縁基板と前記封止構造部との間に配置された、複数の下部電極と、1つの上部電極と、それぞれが前記1つの上部電極と前記複数の下部電極のそれぞれとの間に配置された複数の有機発光層と、前記封止構造部に向かって立ち上がる複数の穿孔壁と、前記絶縁基板と前記下部電極との間に形成され、前記下部電極それぞれに供給する電流を制御する複数の回路と、前記絶縁基板と前記下部電極との間に形成された、タッチパネル電極とを含む。そして、前記上部電極は、前記有機発光層からの光を前記封止構造部に向けて透過させる電極であって、前記複数の穿孔壁それぞれが貫通するように形成されている孔を有し、前記上部電極の孔を介して、前記タッチパネル電極により形成される電界が通過する。

【発明の効果】

【0007】

本実施の形態の一態様によれば、アクティブマトリックス型のOLED表示装置の構造を単純にすることができます。

【図面の簡単な説明】

【0008】

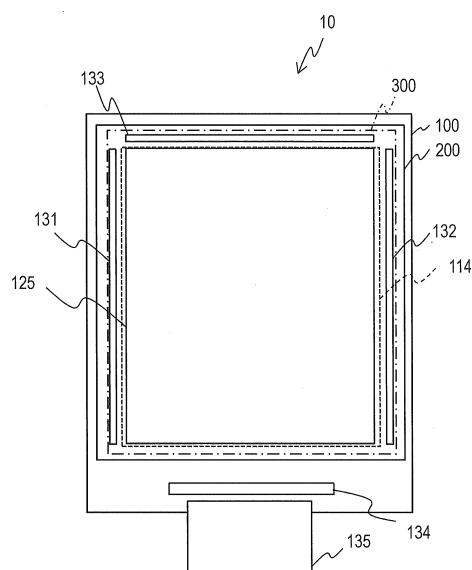

【図1】表示装置の構成例を模式的に示す。

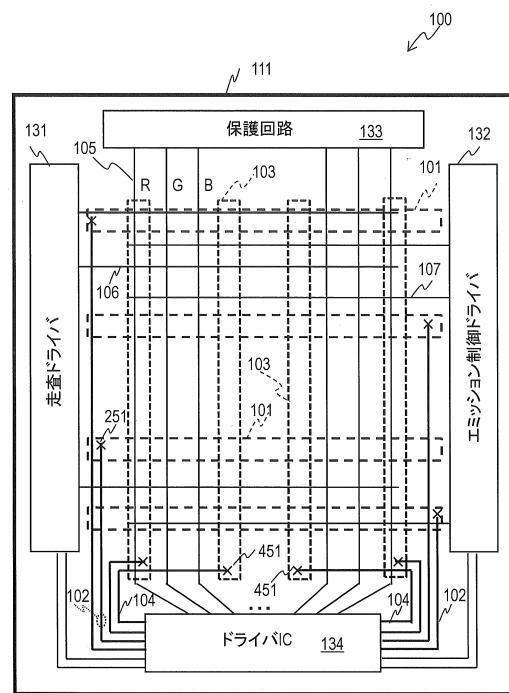

【図2】TFT基板上の回路構成を模式的に示す。

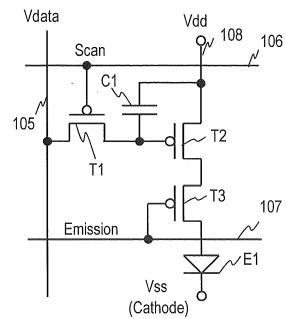

【図3A】副画素の回路(画素回路)の構成例を示す。

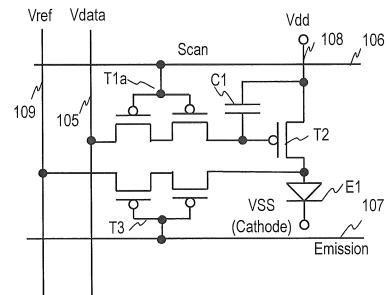

【図3B】副画素の回路(画素回路)の構成例を示す。

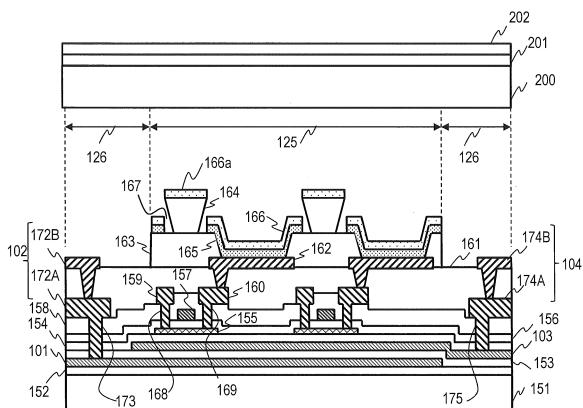

【図4】表示装置の断面構造の一部を模式的に示す。

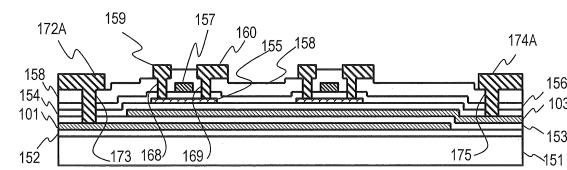

【図5A】表示装置の製造方法の一例を模式的に示す。

【図5B】表示装置の製造方法の一例を模式的に示す。

【図5C】表示装置の製造方法の一例を模式的に示す。

【図5D】表示装置の製造方法の一例を模式的に示す。

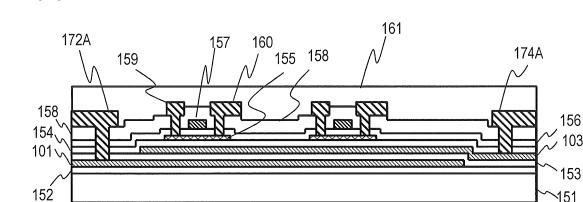

【図5E】表示装置の製造方法の一例を模式的に示す。

【図5F】表示装置の製造方法の一例を模式的に示す。

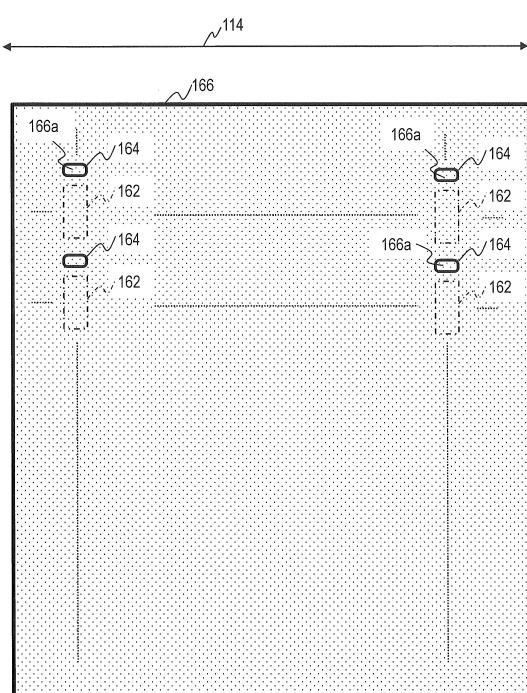

【図5G】表示装置の製造方法の一例を模式的に示す。

【図5H】表示装置の製造方法の一例を模式的に示す。

【図5I】表示装置の製造方法の一例を模式的に示す。

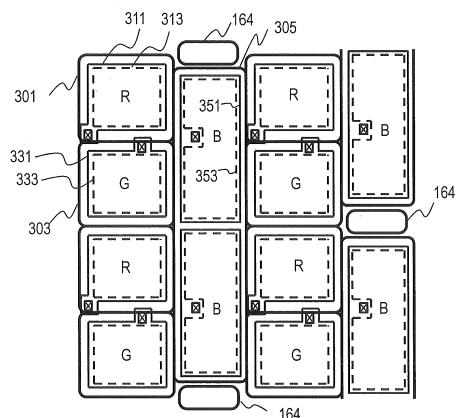

【図6】表示装置の、副画素及び穿孔壁の配列例を模式的に示す。

【図7】副画素及び穿孔壁の他の配列例を模式的に示す。

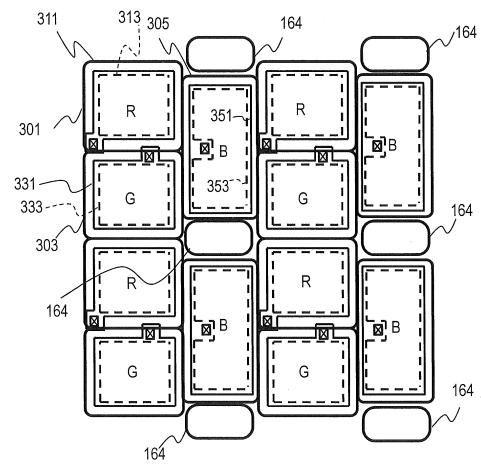

【図8】副画素及び穿孔壁の他の配列例を模式的に示す。

【図9】副画素及び穿孔壁の他の配列例を模式的に示す。

【図10】タッチパネル電極の構成例(配列例)を模式的に示す。

【図11】タッチパネル電極と画素(副画素)とのサイズ関係例を模式的に示す。

10

20

30

40

50

【発明を実施するための形態】

【0009】

以下、添付図面を参照して本発明の実施形態を説明する。本実施形態は本発明を実現するための一例に過ぎず、本発明の技術的範囲を限定するものではないことに注意すべきである。各図において共通の構成については同一の参照符号が付されている。

【0010】

以下において、タッチパネル一体型であり、アクティブマトリックス型のOLED表示装置（以下、表示装置と適宜略記する）を開示する。表示装置は、トップエミッション型の画素構造を有する。

【0011】

本実施の形態の表示装置では、構造を単純にするために、図4で説明するように、光が出射する側と反対側に配置された絶縁基板と、画素との間にタッチパネル用の電極（タッチパネル電極）が配置されている。そして、タッチパネル電極の電界を接触面（画面が表示される面）に通過させるために、画素の前面（光が出射する側）を覆う上部電極に、複数の孔を形成する。この孔は、例えば、穿孔壁により形成されている。タッチパネル電極により形成される電界は、孔から通過し、指や手などの指示体が接触する接触面に至る。すなわち、タッチパネル電極は、孔を介して、接触面に電界を形成することができる。そして、タッチパネル電極を駆動し接触位置を検出する検出回路は、指示体による電界の変化（指示体と電極と間の静電容量変化）を検出し接触位置を検出する。

10

【0012】

図1～図3を参照して、本実施形態に係る、表示装置10の全体構成を説明する。次いで、図4を参照して、前記した孔の説明など、表示装置10の詳細について説明する。なお、説明をわかりやすくするため、図示した物の寸法、形状については、誇張して記載している場合もある。

20

【0013】

【全体構成】

図1は、本実施形態に係る、表示装置10の構成例を模式的に示す。表示装置10は、発光素子が形成されるTFT（Thin Film Transistor）基板100と、発光素子を封止する封止基板200と、TFT基板100と封止基板200とを接合する接合部（ガラスフリットシール部）300を含んで構成されている。TFT基板100と封止基板200との間には、例えば、乾燥空気が封入されており、接合部300により封止されている。

30

【0014】

TFT基板100の表示領域125の外側のカソード電極形成領域114の周囲に、走査ドライバ131、エミッションドライバ132、保護回路133、ドライバIC134が配置されている。これらは、FPC（Flexible Printed Circuit）135を介して外部の機器と接続される。

【0015】

走査ドライバ131はTFT基板100の走査線を駆動する。エミッションドライバ132は、エミッション制御線を駆動して、各副画素の発光期間を制御する。ドライバIC134は、例えば、異方性導電フィルム（ACF：Anisotropic Conductive Film）を用いて実装される。FPC135は、静電気放電による破損を防ぐ。

40

【0016】

ドライバIC134は、走査ドライバ131及びエミッションドライバ132に電源及びタイミング信号（制御信号）を与え、さらに、データ線に映像データに対応するデータ電圧を与える。すなわち、ドライバIC134は、表示制御機能を有する。ドライバIC134は、表示制御機能に加え、タッチパネルの電極（タッチパネル電極と呼ぶ）を制御する機能を有する。表示画素のドライバIC134にタッチパネル制御機能を含めることで、部品点数を低減し配線構成を単純化できる。

50

## 【0017】

## [基板上の回路構成]

図2は、TFT基板100上の回路構成を模式的に示す。本実施形態の表示装置10は、いわゆるタッチパネル内蔵型であり、TFT基板100上にタッチパネル電極が配置されている。後記するように、このタッチパネル電極の配置により、表示画素のドライバIC134にタッチパネル制御機能を含めることができる。また、封止基板200にタッチパネル電極を形成する構成と比較して、製造を簡略化することができる。

## 【0018】

絶縁基板111上に表示及びタッチパネルのための回路が配置されている。絶縁基板111上の表示領域125内に、タッチパネル電極であるTx電極101及びRx電極103、データ線105、走査線106、並びにエミッション制御線107が配置されている。タッチパネル電極であるTx電極101及びRx電極103は、マトリックス状に配置されている。後述するように、Tx電極101及びRx電極103は、データ線105、走査線106、及びエミッション制御線107よりも下層に形成されている。

10

## 【0019】

図2は、Tx電極101、Rx電極103、データ線105、走査線106、及びエミッション制御線107の一部のみ図示している。データ線105と並列するように形成され、ドライバIC134に接続される電力供給線は省略されている。

## 【0020】

図2の例において、Tx電極101、走査線106及びエミッション制御線107は、左右方向に延在し、上下方向に配列されている。走査線106及びエミッション制御線107は、交互に配置されている。Rx電極103及びデータ線105は、上下方向に延在し、左右方向に配列されている。

20

## 【0021】

データ線105はドライバIC134及び保護回路133に接続されている。走査線106は走査ドライバ131に接続され、エミッション制御線107はエミッションドライバ132に接続されている。

## 【0022】

Tx電極101及びRx電極103は、ドライバIC134に接続されている。具体的には、Tx電極101は、表示領域125外において、Tx配線102の第1端にコンタクト251を介して接続されている。なお、Tx配線102は第1配線とも呼ばれる。そして、表示領域125外において、Tx配線102の第2端がドライバIC134の端子に接続されている。Rx電極103は、表示領域125外において、Rx配線104の第1端にコンタクト451を介して接続されている。なお、Rx配線104は第2配線とも呼ばれる。そして、表示領域125外において、Rx配線104の第2端がドライバIC134の端子に接続されている。

30

## 【0023】

## [画素回路]

絶縁基板111上には、複数の副画素のアノード電極にそれぞれ供給する電流を制御する複数の回路(画素回路)が形成されている。図3Aは、画素回路の構成例を示す。各副画素は、第1のトランジスタT1と、第2のトランジスタT2と、第3のトランジスタT3と、保持容量C1とを含む画素回路と、OLED素子E1とを含む。トランジスタは、TFT(Thin Film Transistor)である。以下、第1のトランジスタT1～第3のトランジスタT3をそれぞれトランジスタT1～トランジスタT3と略記する。

40

## 【0024】

トランジスタT1は副画素選択用のスイッチである。トランジスタT1はpチャネル型FET(Field Effect Transistor)であり、ゲート端子は、走査線106に接続されている。ドレイン端子は、データ線105に接続されている。ソース端子は、トランジスタT2のゲート端子に接続されている。

## 【0025】

50

トランジスタ T 2 は O L E D 素子 E 1 の駆動用のトランジスタである。トランジスタ T 2 は p チャネル型 F E T であり、そのゲート端子は T 1 のソース端子に接続されている。また、トランジスタ T 2 のソース端子は電力供給線 1 0 8 ( V d d ) に接続されている。ドレイン端子は、トランジスタ T 3 のソース端子に接続されている。トランジスタ T 2 のゲート端子とソース端子との間に保持容量 C 1 が形成されている。

#### 【 0 0 2 6 】

トランジスタ T 3 は、 O L E D 素子 E 1 への駆動電流の供給と停止を制御するスイッチである。トランジスタ T 3 は p チャネル型 F E T であり、ゲート端子はエミッション制御線 1 0 7 に接続されている。トランジスタ T 3 のソース端子はトランジスタ T 2 のドレイン端子に接続されている。ドレイン端子は、 O L E D 素子 E 1 に接続されている。

10

#### 【 0 0 2 7 】

次に、画素回路の動作を説明する。走査ドライバ 1 3 1 が走査線 1 0 6 に選択パルスを出力し、トランジスタ T 1 を開状態にする。データ線 1 0 5 を介してドライバ I C 1 3 4 から供給されたデータ電圧は、保持容量 C 1 に格納される。保持容量 C 1 は、格納された電圧を、1 フレーム期間を通じて保持する。保持電圧によって、トランジスタ T 2 のコンダクタンスがアナログ的に変化し、トランジスタ T 2 は、発光諧調に対応した順バイアス電流を O L E D 素子 E 1 に供給する。

#### 【 0 0 2 8 】

トランジスタ T 3 は、駆動電流の供給経路上に位置する。エミッションドライバ 1 3 2 は、エミッション制御線 1 0 7 に制御信号を出力して、トランジスタ T 3 開閉状態を制御する。トランジスタ T 3 が開状態のとき、駆動電流が O L E D 素子 E 1 に供給される。トランジスタ T 3 が閉状態のとき、この供給が停止される。トランジスタ T 3 の開閉を制御することにより、1 フィールド周期内の点灯期間（デューティ比）を制御することができる。

20

#### 【 0 0 2 9 】

図 3 B は、画素回路の他の構成例を示す。図 3 A の画素回路との相違は、トランジスタ T 1 a と、トランジスタ T 3 である。トランジスタ T 1 a は、図 3 A のトランジスタ T 1 の機能（副画素選択用のスイッチ）と同じ機能を有するスイッチである。なお、トランジスタ T 1 a は、オフ電流を低減させるためにデュアルゲート構造を有する。

#### 【 0 0 3 0 】

トランジスタ T 3 は、様々な目的で使用することができる。トランジスタ T 3 は、例えば、O L E D 素子 E 1 間のリーク電流によるクロストークを抑制するために、一旦、O L E D 素子 E 1 のアノード電極を黒信号レベル以下の十分低い電圧にリセットする目的で使用しても良い。なお、トランジスタ T 3 は、オフ電流を低減させるためにデュアルゲート構造を有する。

30

#### 【 0 0 3 1 】

他にも、トランジスタ T 3 は、トランジスタ T 2 の特性を測定する目的で使用してもよい。例えば、トランジスタ T 2 を飽和領域、スイッチングトランジスタ T 3 を線形領域で動作するようにバイアス条件を選んで、電力供給線 1 0 8 ( V d d ) から基準電圧供給線 1 0 9 ( V r e f ) に流れる電流を測定すれば、トランジスタ T 2 の電圧・電流変換特性を正確に測定することができる。画素毎のトランジスタ T 2 の電圧・電流変換特性の違いを補償するデータ信号を外部回路で生成すれば、均一性の高い表示画像を実現できる。

40

#### 【 0 0 3 2 】

一方、トランジスタ T 2 をオフ状態にしてトランジスタ T 3 をリニア領域で動作させ、O L E D 素子 E 1 を発光させる電圧を基準電圧供給線 1 0 9 から印加すれば、画素毎の O L E D 素子 E 1 の電圧・電流特性を正確に測定することができる。例えば、長時間の使用によって O L E D 素子 E 1 が劣化した場合にも、その劣化量を補償するデータ信号を外部回路で生成すれば、長寿命化を実現できる。

#### 【 0 0 3 3 】

##### 【 タッチパネル 】

次に、表示装置 1 0 が備えるタッチパネルについて説明する。表示装置 1 0 において、ド

50

ライバ I C 1 3 4 のタッチパネル制御機能は、ユーザがタッチした接触面（表示画面）上の座標を検出する。表示装置 1 0 には、静電容量方式のタッチパネルが組み込まれている。図 2 は、相互容量検出方式の投射型容量方式タッチパネルを例示する。

【 0 0 3 4 】

静電容量方式のタッチパネルは、電極と指示体との間の静電容量変化を検出して、指示体の接触位置を検出する。静電容量方式のタッチパネルは、投影型と表面型とに分類される。

【 0 0 3 5 】

投射型容量方式のタッチパネルは、短冊状の複数の X 電極と複数の Y 電極を有する。X 電極及び Y 電極はマトリックス状に配置され、X 電極と Y 電極とは、絶縁膜を介して形成されている。X - Y 電極に指示体が近づくと電極間の静電容量が増加し、X - Y のラインの静電容量の変化をタッチパネルコントローラが検出し、指示体の位置を検出する。

10

【 0 0 3 6 】

投射型容量方式のタッチパネルの容量検出方式として、自己容量検出方式と相互容量検出方式が存在する。自己容量検出方式は、X 電極、Y 電極を独立にスキャンし、それぞれの電極における静電容量値の変化を検出する。

【 0 0 3 7 】

相互容量方式のタッチパネルは、駆動電極としての T × 電極と検出電極としての R × 電極が絶縁体を挟んで直交するように配置され、各交点に容量（交点容量）が構成される。交点容量の近傍に指示体による容量が存在すると、この交点における相互容量は、指示体による容量によって充電される電荷が分割される分だけ、交点容量から減少する。ライバ I C 1 3 4 のタッチパネル制御機能は、この相互容量の変化がどの交点でどの程度の大きさで発生したかを検出する。

20

【 0 0 3 8 】

なお、本実施形態の T F T 基板構造は、相互容量検出方式及び自己容量検出方式等の投射型容量方式以外の任意の容量方式タッチパネルに適用することができる。

【 0 0 3 9 】

[ 表示装置の詳細構造 ]

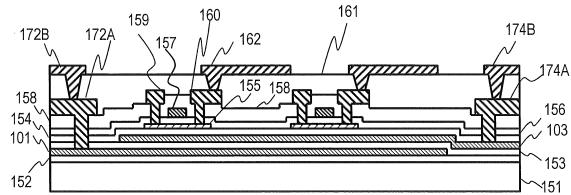

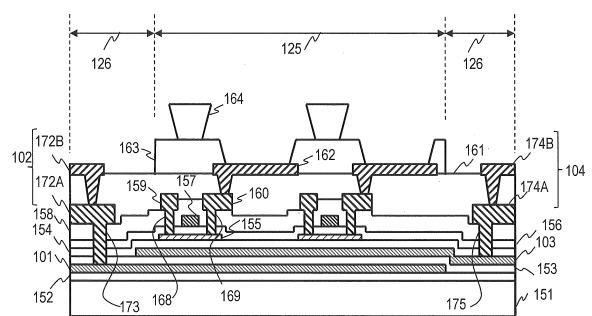

次に、表示装置 1 0 の詳細構造について、図 4 ~ 図 1 1 を参照して説明する。図 4 は、表示装置 1 0 の断面構造の一部を模式的に示す。表示装置 1 0 は、T F T 基板 1 0 0 ( 図 2 参照 ) と、T F T 基板 1 0 0 に対向する封止基板 ( 透明基板 ) 2 0 0 とを含む。図 4 は、T F T 基板 1 0 0 における一部の構成のみを模式的に示す。また、以下の説明において、上下は、図面における上下を示す。表示装置 1 0 では、構造を単純にするために、タッチパネル電極がカソード電極の下側 ( 光が射出する側と反対側 ) に配置されている。

30

【 0 0 4 0 】

図 4 に示すように、表示装置 1 0 は、絶縁基板 1 5 1 と、絶縁基板 1 5 1 と対向する封止構造部とを含む。ここで、封止構造部の一例としては、可撓性又は不撓性の封止基板 2 0 0 である。また、封止構造部は、例えば、薄膜封止 ( T F E : T h i n F i l m E n c a p s u l a t i o n ) 構造であってもよい。なお、絶縁基板 1 5 1 は、図 1 の絶縁基板 1 1 1 とみなすことができる。

40

【 0 0 4 1 】

表示装置 1 0 は、絶縁基板 1 5 1 と封止構造部との間に配置された、複数の下部電極 ( 例えば、アノード電極 1 6 2 ) と、1 つの上部電極 ( 例えば、カソード電極 1 6 6 ) と、複数の有機発光層 1 6 5 とを含む。なお、カソード電極 1 6 6 は、有機発光層 1 6 5 からの光を封止構造部に向けて透過させる透明電極である。

【 0 0 4 2 】

1 つのカソード電極 1 6 6 と1 つのアノード電極 1 6 2 との間に、1 つの有機発光層 1 6 5 ( 有機発光膜 1 6 5 とも呼ぶ ) が配置されている。より詳しく説明すると、複数のアノード電極 1 6 2 は、同一面上 ( 例えば、平坦化膜 1 6 1 の上 ) に配置され、1 つのアノード電極 1 6 2 の上に1 つの有機発光層 1 6 5 が配置されている。

【 0 0 4 3 】

50

さらに、表示装置 10 は、封止構造部に向かって立ち上がる複数の穿孔壁 164 と、複数の回路とを有する。穿孔壁は、凸状の構造体（構造部）とも呼ばれる。複数の回路の各々は、例えば図 3A、図 3B に示した画素回路である。複数の回路の各々は、絶縁基板 151 とアノード電極 162 との間に形成され、複数のアノード電極 162 の各々に供給する電流を制御する。

【0044】

さらに、表示装置 10 は、絶縁基板 151 とアノード電極 162 との間に形成された、タッチパネル電極とを含む。タッチパネル電極は、例えば、駆動電極として機能する T×電極 101、検出電極として機能する R×電極 103 である。

【0045】

図 4 に示すように、トップエミッション型の画素構造は、光が出射する側（図面上側）に、複数の画素に共通のカソード電極 166 が配置される。従来のトップエミッション型の OLED 表示装置におけるカソード電極は、表示領域 125 の全面を完全に覆う形状を有する。カソード電極が表示領域 125 の全面を完全に覆う場合、ただ単に、カソード電極の下にタッチパネル電極を配置しても、従来の金属製カソード電極がタッチパネル電極の電界を遮断する。そのため、指示体の接触位置を検知するための電界が、表示装置の表示面側に形成されない。従って、タッチパネル制御回路が指示体の接触位置を正確に検出することが困難である。

【0046】

しかし、本実施の形態におけるカソード電極 166 は、複数の孔 167 を有する。孔 167 は、穿孔壁 164 が貫通するように形成されている。孔 167 は、例えば T×電極 101 により形成される電界が通過する孔である。この電界が孔 167 から通過し、指や手などの指示体が接触する接触面に至る。この接触面は、画面が表示される面（表示装置 10 の外側の面）である。換言すれば、接触面は、例えば、封止構造部（例えば、封止基板 200）や、その上面に偏光板 202 がある場合、その偏光板 202 の面である。

【0047】

本実施の形態のカソード電極 166 の形状により、検出回路（例えば、図 2 のドライバ IC 134）は、T×電極 101 を駆動して T×電極 101 により電界を形成させ、指示体による電界の変化による静電容量の変化を R×電極 103 により検出することができる。そして、検出回路は、この変化を参照して、接触面に対する指示体の接触位置を検出することができる。

【0048】

本実施の形態の表示装置における、タッチパネル電極の配置により、装置サイズの縮小、部品数の削減、製造工程の削減を実現できる。例えば、OLED 表示装置にタッチパネルを実装する場合、タッチパネルそのものを OLED 表示装置の表示面に貼り合わせる方式（以下、第 1 方式）がある。第 1 方式では、タッチパネルは、接触面として機能する透明の第 1 基板と、表示装置の表示面に貼り合わせる透明の第 2 基板と、第 1 基板と第 2 基板との間に配置されたタッチパネル電極を含む。第 1 方式のように、タッチパネルを OLED 表示装置の表示面に貼り合わせると、表示装置全体の厚みが増し、装置サイズが大きくなる。また、部品点数も増える。

【0049】

第 1 方式に対して本実施の形態の表示装置では、タッチパネル電極を内蔵しているので、前記した第 1 基板、第 2 基板が不要になり、装置サイズを縮小できる。また、部品点数も削減できる。また、貼り合わせが不要になり、工数、コストの削減が可能である。

【0050】

また、OLED 表示装置にタッチパネルを実装する場合、タッチパネル電極を表示装置の表示面に直接配置し、その上に接触面として機能する第 1 基板を配置する方式（以下、第 2 方式）がある。第 2 方式では、第 1 方式と異なり、第 2 基板が不要になる。しかし、第 2 方式でも、タッチパネル電極の駆動回路を COF（Chip on Film）で実装し、この COF の駆動回路とタッチパネル電極とを外付けの FPC を介して電気的に接続す

10

20

30

40

50

る。この実装のため、表示制御を行うドライバICとタッチパネル電極の駆動回路とを一体化することができず、構造が複雑になる。この構造の複雑化は、第1方式でも同様である。

#### 【0051】

第1方式、第2方式に対して本実施の形態の表示装置では、Tx電極101とRx電極103と、絶縁基板151に配置されたドライバIC134とを、絶縁基板151に配置された配線(102、104)を介して電気的に接続することができる。そのため、ドライバIC134とタッチパネルの駆動回路とを一体化することができる。従って、本実施の形態の表示装置において、単純構造が実現できる。その結果、サイズ縮小が可能になる。

#### 【0052】

また、本実施の形態の表示装置では、前記したCOFの実装方式が不要であり、その結果、COFの実装方式で必要なFPCが不要になる。従って、製造工程を簡略化でき、部品点数も削減できる。

#### 【0053】

さらに、第1、第2方式では、タッチパネル電極を透明性の電極にして、表示面の上側に配置している。そのため、外部からの光(例えば、太陽光、照明光)の影響や、視点位置によって、使用者は、この透明性の電極を知覚することがある。たとえば、使用者は、タッチパネル電極により筋状の模様を知覚する。使用者は、この模様を知覚すると違和感を覚える。一方、本実施の形態の表示装置は、タッチパネル電極を画素の下側に配置しているので、タッチパネル電極を知覚することができない。そのため、使用者は、かかる違和感を知覚することができない。

#### 【0054】

以下、表示装置10についてより詳しく説明する。TFT基板100は、表示領域125内に配列されたタッチパネル電極及び副画素(画素)、並びに、表示領域125の周囲の配線領域126に形成された配線を含む。配線は、タッチパネル電極及び画素回路と、配線領域126に配置された制御回路(131、132、133、135)とを接続する。なお、本実施の形態の断面構造においては、図示を簡略化するため、表示領域125、配線領域126を狭く図示している。換言すれば、断面構造において、表示領域125、配線領域126の一部を図示している。

#### 【0055】

副画素は、赤、緑、又は青のいずれかの色を表示する。赤、緑、及び青の副画素により一つの画素(主画素)が構成される。副画素は、OLED素子及び複数のトランジスタを含む画素回路(図3参照)を、含んで構成されている。OLED素子は、下部電極であるアノード電極、有機発光層、及び上部電極であるカソード電極を含んで構成される。すなわち、複数のOLED素子は、1つのカソード電極166と、複数のアノード電極162と、複数の有機発光層165により形成されている。

#### 【0056】

図4において、副画素(OLED素子)は、トップエミッション構造を有する。絶縁基板151上に、第1絶縁膜152を介して、Tx電極101及びRx電極103が形成されている。絶縁基板151は、例えばガラス又は樹脂で形成されており、不撓性又は可撓性基板である。なお、以下の説明において、絶縁基板151に近い側を下側、遠い側を上側と呼ぶ。

#### 【0057】

Tx電極101及びRx電極103は、第2絶縁膜153によって互いに絶縁されている。Tx電極101及びRx電極103は、高融点金属材料で形成され、例えば、Mo(モリブデン)、Nb(ニオブ)、W(タンゲステン)、又は高融点金属の合金で形成されている。

#### 【0058】

図4の例において、Rx電極103は、Tx電極101より上層に形成されているが、これらの位置関係はこれに限定されず、互いに絶縁されれば、どのような層配置であつ

10

20

30

40

50

てもよい。

【0059】

T<sub>x</sub>電極101及びR<sub>x</sub>電極103の上に、第3絶縁膜154を介して、チャネル部(半導体層)155が形成されている。チャネル部155は、例えば、低温ポリシリコン(LT<sub>PS</sub>: Low-temperature poly silicon)を含む。

【0060】

チャネル部155の上に、ゲート絶縁膜156を介して、ゲート電極157が形成されている。ゲート電極157の層上に層間絶縁膜158が形成されている。表示領域125内において、層間絶縁膜158上にソース電極159及びドレイン電極160が形成されている。配線領域126に、T<sub>x</sub>配線の下層部172A、及びR<sub>x</sub>配線の下層部174Aが形成されている。ソース電極159、ドレイン電極160、T<sub>x</sub>配線の下層部172A、及びR<sub>x</sub>配線の下層部174Aは、例えば、高融点金属又はその合金で形成される。

10

【0061】

ソース電極159及びドレイン電極160は、層間絶縁膜158のコンタクトホールに形成されたコンタクト部168、169によって、チャネル部155に接続されている。T<sub>x</sub>配線の下層部172A、及びR<sub>x</sub>配線の下層部174Aは、層間絶縁膜158のコンタクトホールに形成されたコンタクト部173、175によって、それぞれ、T<sub>x</sub>電極101及びR<sub>x</sub>電極103に接続されている。

【0062】

ソース電極159、ドレイン電極160、T<sub>x</sub>配線の下層部172A、及びR<sub>x</sub>配線の下層部174Aの上に、絶縁性の平坦化膜161が形成される。そして、絶縁性の平坦化膜161の上に、アノード電極162、T<sub>x</sub>配線の一部である上層部172B、及びR<sub>x</sub>配線の一部である上層部174Bが形成されている。なお、T<sub>x</sub>配線の下層部172AとT<sub>x</sub>配線の上層部172Bとの間の平坦化膜161、及び、R<sub>x</sub>配線の下層部174AとR<sub>x</sub>配線の上層部174Bとの間の平坦化膜161は、削除されていてもよい。

20

【0063】

アノード電極162は、平坦化膜161のコンタクトホールに形成されたコンタクト部によってドレイン電極160に接続されている。T<sub>x</sub>配線の上層部172B及びR<sub>x</sub>配線の上層部174Bは、それぞれ、平坦化膜161のコンタクトホールに形成されたコンタクト部によってT<sub>x</sub>配線の下層部172A及びR<sub>x</sub>配線の下層部174Aに接続されている。画素回路(TFT)は、アノード電極162の下側に形成されている。

30

【0064】

アノード電極162の上に、OLED素子を分離する絶縁性の画素定義層(Pixel Defining Layer: PDL)163が形成されている。OLED素子は、積層された、アノード電極162、有機発光層165、及びカソード電極166(の部分)で構成される。OLED素子は、画素定義層163の開口に形成されている。図4に示すように、副画素(OLED素子)は、トップエミッション構造を有する。

【0065】

絶縁性の穿孔壁164は、2つのアノード電極162の間ににおける、画素定義層163の面上に形成されている。すなわち、穿孔壁164は、画素定義層163の非開口部に形成されている。穿孔壁164は、OLED素子の外側において、OLED素子の間に配置されている。このため、穿孔壁164がOLED素子の表示機能を阻害することはない。

40

【0066】

穿孔壁164は、画素定義層163面上で、前面の封止基板200に向かって立ち上がりしており、穿孔壁164の頂面は画素定義層163の上面よりも高い(封止基板200に近い)位置にある。穿孔壁164の頂面は、OLED素子よりも高い(封止基板200に近い)位置にあり、封止基板200が変形した場合に、封止基板200を支持して、OLED素子と封止基板200との間隔を維持するスペーサの効果をも奏する。

【0067】

図4の例において、穿孔壁164は逆テープ形状を有している。つまり、穿孔壁164の

50

絶縁基板 151 の面内方向の寸法は、上から下に向かって徐々に減少しており、穿孔壁 164 の頂面は、絶縁基板 151 に垂直な方向において見た場合、穿孔壁 164 の底面を覆つていている。なお、穿孔壁は順テープ形状を有していてもよい。つまり、順テープ状の穿孔壁の絶縁基板 151 の面内方向の寸法は、上から下に向かって徐々に増加しており、この穿孔壁の頂面は、絶縁基板 151 に垂直な方向において見た場合、この穿孔壁の底面に含まれる。また、穿孔壁は、垂直形状を有していてもよい。つまり、穿孔壁の壁面（側面）は垂直であってもよい。

#### 【 0 0 6 8 】

アノード電極 162 の上に、有機発光層 165 が形成されている。有機発光層 165 は、画素定義層 163 の開口及びその周囲において、画素定義層 163 に付着している。有機発光層 165 の上にカソード電極 166 が形成されている。カソード電極 166 は、透明電極である。カソード電極 166 は、有機発光層 165 からの可視光の全て又は一部を透過させる。

10

#### 【 0 0 6 9 】

画素定義層 163 の開口に形成された、アノード電極 162 、有機発光層 165 及びカソード電極 166 の積層膜が、OLED 素子を構成する。カソード電極 166 は、分離して形成されているアノード電極 162 及び有機発光層 165 (OLED 素子) に共通である。なお、カソード電極 166 の上には、不図示のキャップ層が形成されてもよい。

#### 【 0 0 7 0 】

図 4 に示すように、本実施形態のカソード電極 166 は孔 167 を有している。穿孔壁 164 がカソード電極 166 を貫通し、この貫通により孔 167 が形成されている。

20

#### 【 0 0 7 1 】

後述するように、穿孔壁 164 をカソード電極 166 の前に形成することで、カソード電極 166 の材料の付着時に、孔 167 を形成することができる。カソード電極 166 の層の形成時に、穿孔壁 164 によってカソード電極 166 の層が切断され、孔 167 が形成される。この形成時において、穿孔壁 164 の上にカソード電極 166 の材料が残部 166a として付着する。

#### 【 0 0 7 2 】

TFT 基板 100 と封止基板 200 とは所定の間隔で固定される。封止基板 200 は、透明な絶縁基板であって、例えばガラス基板である。封止基板 200 の光出射面（前面）に、 $\sqrt{4}$  位相差板 201 と偏光板 202 とが配置され、外部から入射した光の反射を抑制する。

30

#### 【 0 0 7 3 】

本実施形態の画素構造は、前記したように、トップエミッション型である。有機発光層 165 からの光の一部は、アノード電極 162 によって反射され、カソード電極 166 を透過して、封止基板 200 を通って表示装置 10 の表示面（接触面）に出射する。OLED 素子がキャビティ構造を有する場合、有機発光層 165 からの光は、反射アノード電極 162 と半透過カソード電極 166 との間ににおいて反射を繰り返す。この多重反射により共振波長の光が增幅される共振効果が発生する。共振効果によって副画素の色の波長成分が強調されて、光が半透過の透明カソード電極 166 から表示装置 10 の表示面に出射される。

40

#### 【 0 0 7 4 】

タッチパネルのための Tx 電極 101 及び Rx 電極 103 は、副画素の下（図面下側）に配置されている。この配置により、有機発光層及び画素回路の形成に実質的な影響を及ぼすことなくタッチパネル電極を TFT 基板 100 上に形成できる。

#### 【 0 0 7 5 】

##### 【 製造方法 】

図 5A から図 5I は、表示装置 10 の製造方法の一例を模式的に示す。以下の製造方法は一例であり、本実施形態のパネル構造が実現できれば、他の製造方法を使用することができる。以下の説明において、同一工程で（同時に）形成される要素は、同一層の要素であ

50

る。

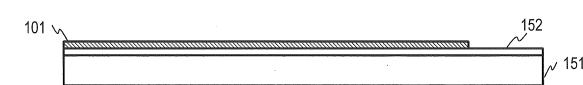

【 0 0 7 6 】

表示装置 10 の製造方法は、まず、図 5 A に示すように、ガラス等の絶縁基板 151 上に、CVD (Chemical Vapor Deposition) 等によって例えばシリコン窒化物を堆積して、第 1 絶縁膜 152 を形成する。次に、スパッタ法等により第 1 絶縁膜 152 上に高融点金属材料を堆積し、パターニングを行って、Tx 電極 101 (の層) を形成する。なお、Tx 電極は第 1 電極とも呼ばれる。

【 0 0 7 7 】

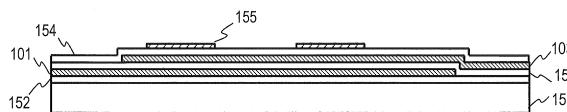

次に、図 5 B に示すように、Tx 電極 101 及び第 1 絶縁膜 152 上に、CVD 等によって例えばシリコン窒化物を堆積して、第 2 絶縁膜 153 を形成する。次に、スパッタ法等により第 2 絶縁膜 153 上に高融点金属材料を堆積して、パターニングを行って、Rx 電極 103 (の層) を形成する。なお、Rx 電極は第 2 電極とも呼ばれる。高融点金属材料は、高融点純金属又は高融点合金であり、例えば、Mo、W、Nb、MoW 又は MoNb である。以上により、タッチパネル部 (タッチパネル電極) が形成される。高融点金属材料を使用することで、後工程のタッチパネル電極への影響を回避することができる。

10

【 0 0 7 8 】

次に、第 2 絶縁膜 153 及び Rx 電極 103 の上、すなわちタッチパネル電極上に CVD 等によって例えばシリコン窒化物を堆積して、第 3 絶縁膜 154 を形成する。次に、公知の低温ポリシリコン TFT 製造技術を用いて、チャネル部 155 を含む層 (ポリシリコン層等の半導体層) を形成する。例えば、CVD 法によってアモルファスシリコンを堆積し、ELA (Excimer Laser Annealing) により結晶化してポリシリコン層を形成できる。ポリシリコン層は、表示領域 125 内において要素間の接続にも利用される。

20

【 0 0 7 9 】

次に、図 5 C に示すように、チャネル部 155 を含むポリシリコン層及び第 3 絶縁膜 154 上に、CVD 法等によって、例えばシリコン酸化膜を付着してゲート絶縁膜 156 を形成する。なお、ゲート絶縁膜は第 4 絶縁膜とも呼ばれる。更に、スパッタ法等により金属材料を堆積し、パターニングを行って、ゲート電極 157 を含む金属層を形成する。具体的には、ゲート電極 157 は、チャネル部 155 の上方であってゲート絶縁膜 156 の上に形成されている。金属材料は、例えば、Mo、Nb、W、又は Mo と Nb 若しくは W との合金である。

30

【 0 0 8 0 】

金属層は、ゲート電極 157 の他、例えば、保持容量電極、走査線 106、エミッショントリニティ線 107、電力供給線を含む。金属層として、例えば Mo、W、Nb、MoW、MoNb、Al、Nd、Ti、Cu、Cu 合金、Al 合金、Ag、Ag 合金からなる群より選択される一つの物質で単一層を形成する、又は、配線抵抗を減少させるために低抵抗物質である Mo、Cu、Al または Ag の 2 層構造またはそれ以上の多重膜構造からなる群より選択される一つの積層を形成してもよい。

30

【 0 0 8 1 】

次に、ゲート電極 157 の形成前に高濃度不純物をドーピングしておいたチャネル部 155 に、ゲート電極 157 をマスクとして追加不純物ドーピングを施して低濃度不純物層を形成することにより、TFT に LDD (Lightly Doped Drain) 構造を形成する。次に、CVD 法等によって、例えばシリコン酸化膜等を堆積して、ゲート電極 157 及びゲート絶縁膜 156 を覆う層間絶縁膜 158 を形成する。なお、層間絶縁膜は第 5 絶縁膜とも呼ばれる。

40

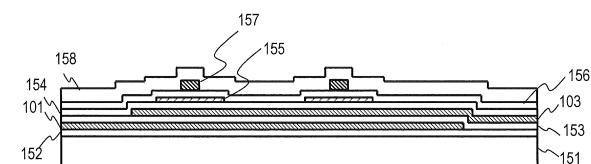

【 0 0 8 2 】

図 5 D に示すように、層間絶縁膜 158、ゲート絶縁膜 156、第 3 絶縁膜 154、及び第 2 絶縁膜 153 に異方性エッティングを行い、コンタクトホールを開口する。ソース電極 159 及びドレイン電極 160 と、チャネル部 155 と、を接続するコンタクト部 168 及び 169 のためのコンタクトホールは、層間絶縁膜 158 及びゲート絶縁膜 156 に形

50

成される。

【0083】

R<sub>x</sub>電極103とR<sub>x</sub>配線104とを接続するコンタクト部175(図2のコンタクト451参照)のためのコンタクトホールは、層間絶縁膜158、ゲート絶縁膜156及び第3絶縁膜154に開口される。

【0084】

T<sub>x</sub>電極101とT<sub>x</sub>配線102とを接続するコンタクト部173(図2のコンタクト251参照)のためのコンタクトホールは、層間絶縁膜158、ゲート絶縁膜156、第3絶縁膜154及び第2絶縁膜153に開口される。タッチパネル電極とタッチパネル配線との接続のためのコンタクトホールを、TFTのためのコンタクトホールと同時に開口し、製造工程の増加を避けることができる。10

【0085】

T<sub>x</sub>配線102、R<sub>x</sub>配線104は、図2で説明したように、表示制御機能とタッチパネル制御機能とを一体化しているドライバIC134と接続し、さらに、T<sub>x</sub>電極101、T<sub>x</sub>配線102、R<sub>x</sub>電極103、R<sub>x</sub>配線104、ドライバIC134は、同一基板上(絶縁基板151)に配置されている。そのため、タッチパネル電極とドライバICとを接続する、外付けのFPCが不要になる。その結果、構造を単純にでき、さらに、部品点数を削減できる。

【0086】

次に、スパッタ法等によって、例えば、Ti/A1/Ti等のアルミ合金を堆積し、パターニングを行って、金属層を形成する。金属層は、ソース電極159、ドレン電極160、コンタクト部168、169、T<sub>x</sub>配線下層部172A、コンタクト部173、R<sub>x</sub>配線下層部174A及びコンタクト部175を含む。この他、データ線105や電力供給線等も形成される。タッチパネル配線とTFTの電極を同時に形成し、製造工程の増加を避けることができる。20

【0087】

次に、図5Eに示すように、感光性の有機材料を堆積し、平坦化膜161を形成する。図5Fに示すように、TFTのドレン電極160に接続するためのコンタクトホール、並びに、T<sub>x</sub>配線下層部172A及びR<sub>x</sub>配線下層部174Aに接続するためのコンタクトホールを開口する。タッチパネル配線の接続のためのコンタクトホールを、TFTのためのコンタクトホールと同時に開口し、製造工程の増加を避けることができる。30

【0088】

コンタクトホールを形成した平坦化膜161上に、アノード電極162を形成する。また、T<sub>x</sub>配線上層部172B及びR<sub>x</sub>配線上層部174Bを形成する。アノード電極162は、ITO、IZO、ZnO、In<sub>2</sub>O<sub>3</sub>等の透明膜、Ag、Mg、Al、Pt、Pd、Au、Ni、Nd、Ir、Cr又はこれらの化合物金属の反射膜、前記した透明膜の3層を含む。なお、アノード電極162の3層構成は、一例であり2層でもよい。T<sub>x</sub>配線上層部172B及びR<sub>x</sub>配線上層部174Bは、例えばAg、Mg、Al、Pt、Pd、Au、Ni、Nd、Ir、Cr又はこれらの化合物金属の金属層である。このT<sub>x</sub>配線上層部172B及びR<sub>x</sub>配線上層部174Bの構成も一例である。40

【0089】

アノード電極162、T<sub>x</sub>配線上層部172B及びR<sub>x</sub>配線上層部174Bは、それぞれ、コンタクト部を介して、ドレン電極160、T<sub>x</sub>配線下層部172A及びR<sub>x</sub>配線下層部174Aと接続される。タッチパネル配線とTFTの電極を同時に形成し、製造工程の増加を避けることができる。

【0090】

次に、図5Gに示すように、スピンコート法等によって、例えば感光性の有機樹脂膜を堆積し、パターニングを行って画素定義層163を形成する。パターニングにより画素定義層163には孔が形成され、各副画素のアノード電極162が形成された孔の底で露出する。画素定義層163の孔の側面は順テープである。画素定義層163により、各副画素

10

20

30

40

50

の発光領域が分離される。

【0091】

さらに、スピンコート法等によって、例えば感光性の有機樹脂膜を堆積し、パターニングを行って、画素定義層163上に穿孔壁164を形成する。穿孔壁164は、逆テープ形状を有するようにパターニングされる。穿孔壁164の形成は、例えば、ネガ形感光性樹脂又は画像反転機能を付与したポジ型感光性樹脂を使用することができる。

【0092】

例えば、ネガ形感光性樹脂に対する露光光照射により、露光光が当たった露光領域において、ネガ形感光性樹脂は、現像液に対して不溶性となる。露光光はネガ形感光性樹脂に吸収され、ネガ形感光性樹脂の露光領域における露光強度は、画素定義層163に近づくほど低下する。

10

【0093】

露光されたネガ形感光性樹脂を現像において、露光強度が比較的小さい画素定義層163の近傍では、溶解速度がネガ形感光性樹脂の表面近傍よりも大きい。そのため、逆テープ形の断面形状を有する穿孔壁164が形成される。露光条件及びキュア温度などの条件を適切に選択し、所望の逆テープ形状を形成できる。

【0094】

穿孔壁164は、他の方法で形成されてもよい。穿孔壁164は、カソード電極166に孔を開口することができれば、どのような断面形状を有してもよい。例えば、穿孔壁164は、逆テープ形状とは異なる、オーバハンジング形状を有してもよい。オーバハンジング形状は、頂面において底面よりも大きい寸法を有し、頂面が底面を覆う形状である。本開示において、逆テープ形状はオーバハンジング形状に含まれる。オーバハンジング形状の他の例は、断面T字状のアンダーカット形状である。

20

【0095】

次に、図5Hに示すように、画素定義層163を形成した絶縁基板151に対して有機発光材料付着して有機発光層165を成膜する。RGBの色毎に、有機EL材料を成膜して、アノード電極162上に、有機発光層165を形成する。

【0096】

有機発光層165の成膜は、メタルマスク(MM)を使用する。異なる色の副画素パターンそれぞれにメタルマスクが用意される。TFT基板100の表面にメタルマスクを位置合わせて配置し、メタルマスクをTFT基板100に固定する。メタルマスクの開口を介して、TFT基板100の副画素に対応する位置に有機発光材料を蒸着させる。

30

【0097】

有機発光層165は、下層側から、例えば、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層によって構成される。有機発光層165は、電子輸送層/発光層/正孔輸送層、電子輸送層/発光層/正孔輸送層/正孔注入層、電子注入層/電子輸送層/発光層/正孔輸送層、又は発光層単独の、いずれの構造を有してもよい。電子ブロッキング層のような他の層を追加されてもよい。発光層の材料は副画素の色毎に異なり、必要に応じて正孔注入層や正孔輸送層等の膜厚も色毎に制御する。

【0098】

次に、図5Hに示すように、画素定義層163、穿孔壁164及び有機発光層165(画素定義層163の開口における)が露出した、TFT基板100に対して、カソード電極166のための金属材料を付着する。金属材料は、有機発光層165上及び穿孔壁164の頂面上に付着する。有機発光層165上に付着した金属材料は、カソード電極166である。また、穿孔壁164の頂面上に付着した金属材料は、残部166aである。図5Iは、1つのカソード電極166の平面形状を模式的に示している。複数の穿孔壁164の各々に残部166aが付着している。そして、図4、図5Hに示したように、穿孔壁164により孔167(図4、図5H参照)が形成されている。

40

【0099】

図4に示したように、穿孔壁164の頂面が有機発光層165表面より高い位置にあり、

50

穿孔壁 164 が逆テー パ形状を有している。従って、金属材料層（カソード電極 166）は、穿孔壁 164 に切断され、孔 167 が形成される。テー パ形状を有する穿孔壁 164 によって、別のパターニングを行うことなく、金属材料の付着時に、カソード電極 166（の層）に孔を穿つことができる。

【0100】

透明カソード電極 166 の層は、例えば、Li、Ca、LiF/Ca、LiF/Al、Al、Mg 又はこれらの合金を蒸着して、形成する。カソード電極 166 の膜厚は、光取り出し効率を向上させ良好な視野角依存性を確保するため最適化される。カソード電極 166 の抵抗が高く発光輝度の均一性が損なわれる場合には、さらに、ITO、IZO、ZnO または In2O3 などの透明電極形成用の材料で補助電極層を追加する。カソード電極 166 の形成後、光取り出し効率向上のため、ガラスより屈折率の高い絶縁膜を堆積させキャップ層を形成してもよい。

10

【0101】

以上により、RGB の各副画素に対応する OLED 素子が形成され、アノード電極 162 と有機発光層 165 とが接触した部分（画素定義層 163 の開口内）が各々、R 発光領域、G 発光領域、B 発光領域となる。

【0102】

次に、TFT 基板 100 の外周にガラスフリットを塗設し、その上に封止基板 200 を載置し、ガラスフリット部をレーザ光により加熱し、溶融させ TFT 基板 100 と封止基板 200 を密封する。その後、封止基板 200 の光出射側に /4 位相差板 201、偏光板 202 を形成し、表示装置 10 が完成する。

20

【0103】

本実施の形態では、有機発光層 165 を形成する前に所定位置に逆テー パの断面形状を有する穿孔壁 164 を形成することで、カソード電極 166 の材料の付着と同時に、孔 167 を形成する。また、上記製造方法により、少ないフォトマスク数で、単純構造のタッチパネル一体型の表示装置を実現できる。

【0104】

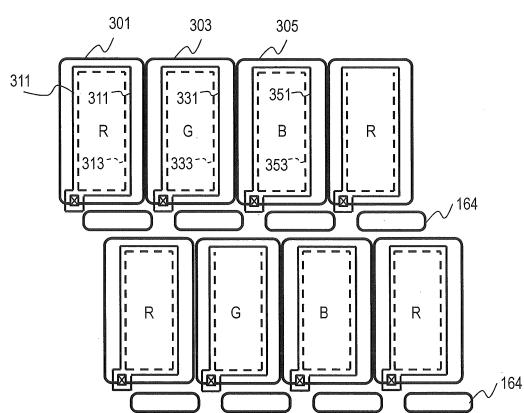

図 6 は、表示装置 10 の、副画素及び穿孔壁の配列例を模式的に示す。RGB の副画素は、発光素子として機能する発光領域（破線）313、333、353 に対応する。発光領域は、画素定義層 163 の開口部を示している。発光領域 313、333、353 を囲う矩形 311、331、351 は、アノード電極 162 に対応する。

30

【0105】

メタルマスクを用いて有機発光材料を選択的に堆積させる場合には、発光領域 313、333、353 よりやや大きめの開口部 301、303、305 を有するメタルマスクを、順次、TFT 基板 100 にアライメントしてセットし、選択的に各色の有機発光材料を堆積させる。実際に電流が流れるのは画素定義層 163 の開口部のみであるので、この部分が発光領域となる。

【0106】

なお、各画素の境界は、TFT 基板 100 の構成部材によって規定されるものではなく、副画素の組を繰り返し配置した場合における隣り合う副画素の組との関係で規定されるものであり、矩形でもよく、矩形以外の形状でもよい。

40

【0107】

図 6 の画素配列は、S ストライプ方式の基本画素配列構造を有する。S ストライプ方式の画素配列構造は、R 副画素と G 副画素とが列方向に配列され、B 副画素が R 副画素及び G 副画素に対して行方向に配置される画素配列構造である。さらに、奇数列に関しては奇数行と次の偶数行の 2 つの画素を 1 組とし、偶数列に関しては偶数行と次の奇数行の 2 つの画素を 1 組とする。各組の 2 つの画素の B 副画素の有機発光材料が連続する。

【0108】

同じ組の 2 つの B 副画素は別々に駆動されるため、アノード電極 162 は分離されている。アノード電極 162 がない部分の有機発光材料は発光に寄与しないため、画素を跨いで

50

有機発光層 165 を形成しても問題はない。B 発光領域の面積を大きくすることで、B 発光領域における電流密度が下がり青色の有機発光材料の劣化が抑制される。その結果、表示装置の長寿命化を図ることができる。

【0109】

有機発光材料の堆積領域はメタルマスクの開口部 301、303、305 によって規定され、発光領域 313、333、353 は画素定義層 163 の開口部によって規定される。アノード電極 162 とカソード電極 166 とのショート及び異なる発光色が混ざる色ずれを防止するため、製造プロセスの精度で規定されるマージンを見込んで、画素定義層 163 の開口部は、有機発光材料の堆積領域よりも内側に形成される。B の有機発光材料の堆積領域において、2 つの B 発光領域（一つの B 発光領域は二つの副画素に対応）は、製造プロセスの精度で規定されるマージンを見込んで、所定の間隔を空けて形成される。

10

【0110】

穿孔壁 164 は、表示機能を阻害しないように、OLED 素子の外側において、OLED 素子の間に配置される。図 6 の例において、穿孔壁 164 は、隣接する B 発光領域の間に配置されるように、配列されている。一例において、穿孔壁 164 は、表示領域 125 内において規則的に配列され、好適なタッチパネル機能を提供する。

【0111】

例えば、一つの画素に対する穿孔壁 164 の数（整数でなくてもよく、1 未満でもよい）が一定である。図 6 の例において、例えば、隣接する B 発光領域の各ペアに対して一つの穿孔壁 164 が配置される。また、一つの画素に対して 0.5 個の穿孔壁 164 が配置されている。

20

【0112】

図 7 は、副画素及び穿孔壁の他の配列例を模式的に示す。図 6 の配列との違いは、一つの B 発光領域（B 有機発光層 165）が二つの画素に跨っておらず、副画素毎に分離されている点である。穿孔壁 164 は、隣接する B 副画素の OLED 素子の間に配置されている。一つの画素に対して一つの穿孔壁 164 が配置されている。

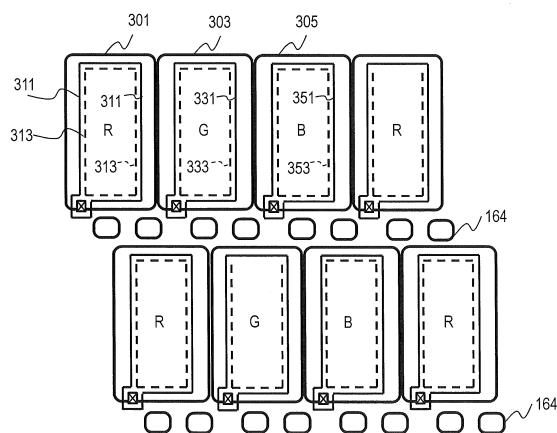

【0113】

図 8 及び図 9 は、副画素及び穿孔壁の他の配列例を模式的に示す。図 8 及び図 9 の画素配列は、デルタ配列である。行方向において、RGB の副画素が、同一順序で繰り返すように配列されている。各行の副画素の順序は同一である。副画素行は、行毎に、画素の横幅において半ピッチずれている。穿孔壁 164 は、隣接する副画素行の間に配置されている。図 8 の例において、画素当たり三つの穿孔壁 164 が配置されており、図 9 の例において、画素当たり六つの穿孔壁 164 が配置されている。穿孔壁 164 の行が、隣接する副画素行の間に配列されている。

30

【0114】

本実施形態のパネル構造を適用する画素配列は特に限定されない。例えば、ストライプ配列、モザイク配列、ペンタイル配列等から選択された任意の画素配列を、本実施形態の表示装置に使用することができる。

【0115】

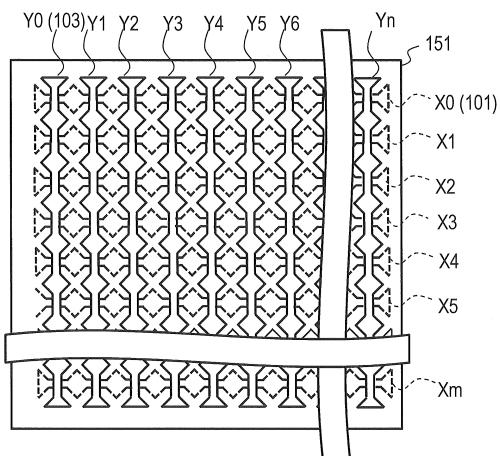

図 10 は、タッチパネル電極の構成例（配列例）を模式的に示す。X 電極（例えば T × 電極）X0 ~ Xm (m は 5 以上の整数) は、複数の菱形の電極片が接続部を介して数珠状に連結された形状を有する。即ち、一つの X 電極は、左右に隣り合う菱形の電極片を、接続部を介して電気的に接続し、左右方向に延在する。Y 電極（例えば R × 電極）Y0 ~ Yn (n は 6 以上の整数) も、同様に、複数の菱形の電極片が接続部を介して数珠状に連結された形状を有する。一つの Y 電極は、上下に隣り合う菱形の電極片を接続部を介して電気的に接続し、上下方向に延在する。

40

【0116】

X 電極 X0 ~ Xm 及び Y 電極 Y0 ~ Yn は、絶縁基板 151 に垂直に見た時に、菱形の電極片の接続部同士が絶縁膜を介して重なりあうように形成されている。X 電極 X0 ~ Xm の菱形の電極片と Y 電極 Y0 ~ Yn の菱形の電極片とは重ならないように形成されている

50

。 X 電極の菱形の電極片と Y 電極 Y 0 ~ Y n の菱形の電極片とは、同一層に形成されてもよく、異なる層に形成されてもよい。

【 0 1 1 7 】

タッチパネル電極の形状は、特に限定されない。例えば、X 電極及び Y 電極は、四角形電極片を有し、各電極片の四辺は絶縁基板 1 5 1 の四辺とそれぞれ平行であってもよい。X 電極又は Y 電極は、一方向に延在する一つの矩形電極であってもよい。

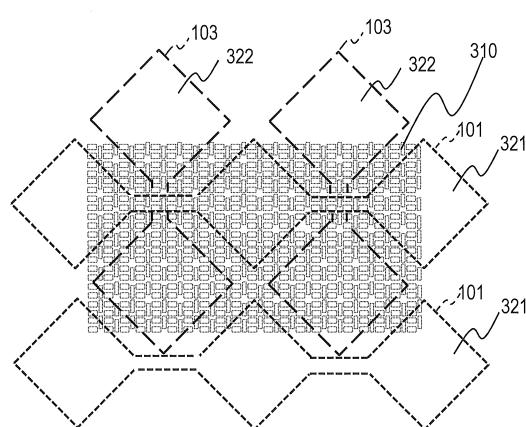

【 0 1 1 8 】

図 1 1 は、タッチパネル電極と画素（副画素）とのサイズ関係例を模式的に示す。T x 電極 1 0 1 及び R x 電極 1 0 3 は、図 1 0 に示す斜めモザイク配列構造を有する。T x 電極 1 0 1 は、複数の菱形電極片 3 2 1 を含む。R x 電極 1 0 3 は、複数の菱形電極片 3 2 2 を含む。図 1 1 に示すように、一つの菱形電極片 3 2 1 又は 3 2 2 の領域内に、複数の画素 3 1 0 が含まれ、例えば、数十から数百の画素 3 1 0 が、一つの菱形電極片 3 2 1 又は 3 2 2 と重なるように配列される。

【 0 1 1 9 】

以上、本発明の実施形態を説明したが、本発明が上記の実施形態に限定されるものではない。当業者であれば、上記の実施形態の各要素を、本発明の範囲において容易に変更、追加、変換することが可能である。ある実施形態の構成の一部を他の実施形態の構成に置き換えることが可能であり、ある実施形態の構成に他の実施形態の構成を加えることも可能である。

【 符号の説明 】

【 0 1 2 0 】

1 0 表示装置、1 0 0 TFT 基板、1 0 1 T x 電極、1 0 2 T x 配線、1 0 3 R x 電極、1 0 4 R x 配線、1 0 5 データ線、1 0 6 走査線、1 0 7 エミッショントリニティ、1 1 1 絶縁基板、1 1 4 カソード電極形成領域、1 2 5 表示領域、1 2 6 配線領域、1 3 1 走査ドライバ、1 3 2 エミッショントリニティ、1 3 3 保護回路、1 5 1 絶縁基板、1 5 2 第 1 絶縁膜、1 5 3 第 2 絶縁膜、1 5 4 第 3 絶縁膜、1 5 5 チャネル部、1 5 6 ゲート絶縁膜、1 5 7 ゲート電極、1 5 8 層間絶縁膜、1 5 9 ソース電極、1 6 0 ドレイン電極、1 6 1 平坦化膜、1 6 2 アノード電極、1 6 3 画素定義層、1 6 4 穿孔壁、1 6 5 有機発光層、1 6 6 カソード電極、1 6 7 孔、1 6 8 コンタクト部、1 7 2 A T x 配線下層部、1 7 2 B T x 配線上層部、1 7 3 コンタクト部、1 7 4 A R x 配線下層部、1 7 4 B T R 配線上層部、1 7 5 コンタクト部、2 0 0 封止基板、2 0 1 位相差板、2 0 2 偏光板、2 5 1、4 5 1 コンタクト、3 0 0 接合部、3 0 1、3 0 3、3 0 5 開口部、3 1 1、3 3 1、3 5 1 アノード電極、3 1 3、3 3 3、3 5 3 発光領域

10

20

30

40

50

## 【四面】

【 义 1 】

## 【図2】

### 【図3A】

【図3B】

【図4】

【図5A】

【 5 B 】

【 図 5 C 】

【 5 D 】

【 図 5 E 】

10

20

30

40

50

【図 5 F】

【図 5 G】

10

【図 5 H】

【図 5 I】

20

30

40

50

【図 6】

【図 7】

10

【図 8】

【図 9】

20

30

40

50

【図 1 0】

【図 1 1】

10

20

30

40

50

## フロントページの続き

## (51)国際特許分類

|         | F       | I             |

|---------|---------|---------------|

| H 0 5 B | 33/10   | (2006.01)     |

| G 0 6 F | 3/041   | (2006.01)     |

| G 0 6 F | 3/044   | (2006.01)     |

| G 0 9 F | 9/30    | (2006.01)     |

| G 0 9 F | 9/302   | (2006.01)     |

| H 0 1 L | 21/336  | (2006.01)     |

| H 0 1 L | 29/786  | (2006.01)     |

|         | H 0 5 B | 33/10         |

|         | G 0 6 F | 3/041 6 6 0   |

|         | G 0 6 F | 3/044 1 2 0   |

|         | G 0 6 F | 3/041 4 0 0   |

|         | G 0 9 F | 9/30 3 4 9 Z  |

|         | G 0 9 F | 9/30 3 6 5    |

|         | G 0 9 F | 9/30 3 3 8    |

|         | G 0 9 F | 9/302 C       |

|         | H 0 1 L | 29/78 6 1 2 Z |

## (56)参考文献

特開2016-224935 (JP, A)

特開2011-249334 (JP, A)

特開2016-130780 (JP, A)

特開2016-189190 (JP, A)

特開2008-084541 (JP, A)

国際公開第2006/084541 (WO, A1)

特開2015-229774 (JP, A)

## (58)調査した分野

(Int.Cl., DB名)

H 0 5 B 3 3 / 2 6

H 0 1 L 5 1 / 5 0

H 0 1 L 2 7 / 3 2

H 0 5 B 3 3 / 1 2

H 0 5 B 3 3 / 2 2

H 0 5 B 3 3 / 1 0

G 0 6 F 3 / 0 4 1

G 0 6 F 3 / 0 4 4

G 0 9 F 9 / 3 0

G 0 9 F 9 / 3 0 2

H 0 1 L 2 1 / 3 3 6