(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4585745号

(P4585745)

(45) 発行日 平成22年11月24日(2010.11.24)

(24) 登録日 平成22年9月10日(2010.9.10)

(51) Int.Cl.

H01L 21/027 (2006.01)

F 1

H01L 21/30 502D

請求項の数 11 (全 20 頁)

(21) 出願番号 特願2003-167445 (P2003-167445)

(22) 出願日 平成15年6月12日 (2003.6.12)

(65) 公開番号 特開2004-40092 (P2004-40092A)

(43) 公開日 平成16年2月5日 (2004.2.5)

審査請求日 平成18年3月30日 (2006.3.30)

(31) 優先権主張番号 10/184,567

(32) 優先日 平成14年6月28日 (2002.6.28)

(33) 優先権主張国 米国(US)

(73) 特許権者 503003854

ヒューレット・パッカード デベロップメント カンパニー エル.ピー.

アメリカ合衆国 テキサス州 77070

ヒューストン コンパック センタードライブ ウエスト 11445

(74) 代理人 110000246

特許業務法人才カダ・フシミ・ヒラノ

(74) 代理人 100081721

弁理士 岡田 次生

(74) 代理人 100105393

弁理士 伏見 直哉

(74) 代理人 100111969

弁理士 平野 ゆかり

最終頁に続く

(54) 【発明の名称】半導体デバイスを形成する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板を用意することと、

前記基板上に第1の材料層を堆積することと、

前記基板上に3次元(3D)レジスト構造を形成することと、を含み、前記3Dレジスト構造は、前記3Dレジスト構造において垂直方向の複数の異なる高さをもつよう構成されており、

前記基板上に交点アレイを形成することを含み、

該交点アレイを形成することは、

前記3Dレジスト構造の第1の最も薄い層を異方性エッチングして貫通することにより 10

、前記第1の材料層の第1の部分を露出させることと、

前記第1の材料層の前記露出された第1の部分をエッチングすることにより、前記第1の材料層の厚みより大きな深さをそれぞれ含む複数のポケットを前記基板内に形成することと、

前記3Dレジスト構造の2番目に最も薄い層をエッチングして貫通することにより、前記第1の材料層の第2の部分を露出することと、

前記第1の材料層の前記露出された第2の部分をエッチングすることと、

前記3Dレジスト構造の3番目に最も薄い層をエッチングして貫通することにより前記第1の材料層の第3の部分を露出することと、

前記第1の材料層の前記露出された第3の部分と、前記3Dレジスト構造の残りの部分 20

との上側に、半導体材料および導電性材料を含む第2の材料層を堆積することと、前記3Dレジスト構造の前記残りの部分を除去することと、をさらに含む、半導体デバイスを形成する方法。

【請求項2】

前記基板はフレキシブル基板材料である請求項1に記載の方法。

【請求項3】

前記レジスト層に3Dパターンを転写することは、前記レジスト層を硬化させることにより、前記3Dレジスト構造を形成することをさらに含む請求項1に記載の方法。

【請求項4】

前記半導体デバイスは、トランジスタ、抵抗器、キャパシタ、ダイオード、ヒューズの少なくとも1つである、請求項3に記載の方法。 10

【請求項5】

基板を用意することと、

前記基板上に第1の材料層を堆積することと、

前記基板上に3次元(3D)レジスト構造を形成することと、を含み、前記3Dレジスト構造は、前記3Dレジスト構造において垂直方向の複数の異なる高さをもつよう構成されており、

前記基板上に交点アレイを形成することを含み、

前記交点アレイを形成することは、

前記3Dレジスト構造の第1の最も薄い層をエッチングして貫通することにより、前記第1の材料層の第1の部分を露出させることと、 20

前記第1の材料層の前記露出された第1の部分をエッチングすることにより前記基板の一部を露出することと、

前記3Dレジスト構造の2番目に最も薄い層をエッチングして貫通することにより前記第1の材料層の第2の部分を露出することと、

前記第1の材料層の前記露出された第2の部分と、前記3Dレジスト構造の残りの部分との上側に、半導体材料および導電性材料を含む第2の材料層を堆積することと、

前記第2の材料層上に、前記3Dレジスト構造とは異なるエッチング速度の第2のレジスト層をロールコーティングすることと、

前記第2のレジスト層をエッチングすることにより、前記第2の材料層の第1の部分を露出することと、 30

前記第2の材料層の前記第1の部分をエッチングすることと、

前記3Dレジスト構造の3番目に最も薄い層をエッチングすることにより前記第1の材料層の第3の部分を露出することと、

前記第1の材料層の前記第3の部分をエッチングすることと、

前記3Dレジスト構造の残りの部分と、前記第2のレジスト層の残りの部分とを除去することと、

を含む半導体デバイスを形成する方法。

【請求項6】

前記半導体デバイスは、トランジスタ、抵抗器、キャパシタ、ダイオード、ヒューズの少なくとも1つである、請求項5に記載の方法。 40

【請求項7】

基板を用意することと、

前記基板上に第1の材料層を堆積することと、

前記基板上に3次元(3D)レジスト構造を形成することと、を含み、前記3Dレジスト構造は、前記3Dレジスト構造において垂直方向に複数の異なる高さをもつよう構成されており、

前記3Dレジスト構造は、別の溝よりも狭い溝を含み、

交点アレイを形成することを含み、該交点アレイを形成することは、

前記3Dレジスト構造の第1の最も薄い層をエッチングして貫通することにより、前記 50

第1の材料層の第1の部分を露出させることと、

前記第1の材料層の前記露出された第1の部分および前記3Dレジスト構造の残りの部分の上側に、半導体材料および導電性材料を含む第2の材料層を堆積することと、

前記狭い溝に容易に入していく第2のレジスト層を、前記第2の材料層上に堆積することと、

前記第2の材料層を異方性エッティングすることにより前記3Dレジスト構造の前記残りの部分を露出することと、

前記3Dレジスト構造の前記残りの部分および前記狭い溝に入った第2のレジスト層を除去することと、

を含む半導体デバイスを形成する方法。

10

【請求項8】

前記半導体デバイスは、トランジスタ、抵抗器、キャパシタ、ダイオード、ヒューズのうちの少なくとも1つである、請求項7に記載の方法。

【請求項9】

半導体デバイスを形成する方法であって、

フレキシブル基板材料を用意することと、

前記フレキシブル基板上に第1の材料層を堆積することと、

前記第1の材料層上にレジスト層を堆積することと、

スタンピングツールを用いることにより、前記レジスト層内に3Dパターンを形成することと、

20

前記レジスト層を硬化させることにより、前記第1の材料層上に、垂直方向に複数の異なる高さをもつ3Dレジスト構造を形成することと、

前記3Dレジスト構造を用いることにより前記フレキシブル基板上に交点アレイを形成することと、を含み、

該交点アレイを形成することは、

前記3Dレジスト構造の第1の最も薄い層をエッティングして貫通することにより、前記第1の材料層の第1の部分を露出させることと、

前記第1の材料層の前記露出された第1の部分をエッティングすることにより、前記第1の材料層の厚みより大きな深さをそれぞれ含む複数のポケットを前記基板内に形成することと、

30

前記3Dレジスト構造の2番目に最も薄い層をエッティングして貫通することにより、前記第1の材料層の第2の部分を露出することと、

前記第1の材料層の前記露出された第2の部分をエッティングすることと、

前記3Dレジスト構造の3番目に最も薄い層をエッティングして貫通することにより前記第1の材料層の第3の部分を露出することと、

前記第1の材料層の前記露出された部分と、前記3Dレジスト構造の残りの部分との上側に、半導体材料および導電性材料を含む第2の材料層を堆積することと、

前記3Dレジスト構造の前記残りの部分を除去することと、をさらに含む、半導体デバイスを形成する方法。

【請求項10】

40

半導体デバイスを形成する方法であって、

フレキシブル基板材料を用意することと、

前記フレキシブル基板上に第1の材料層を堆積することと、

前記第1の材料層上にレジスト層を堆積することと、

スタンピングツールを用いることにより、前記レジスト層内に3Dパターンを形成することと、

前記レジスト層を硬化させることにより、前記第1の材料層上に、垂直方向に複数の異なる高さをもつ3Dレジスト構造を形成することと、

前記3Dレジスト構造を用いることにより前記フレキシブル基板上に交点アレイを形成することと、を含み、

50

該交点アレイを形成することは、

前記3Dレジスト構造の第1の最も薄い層をエッティングして貫通することにより、前記第1の材料層の第1の部分を露出させることと、

前記第1の材料層の前記露出された第1の部分をエッティングすることにより前記基板の一部を露出することと、

前記3Dレジスト構造の2番目に最も薄い層をエッティングして貫通することにより前記第1の材料層の第2の部分を露出することと、

前記第1の材料層の前記露出された部分と、前記3Dレジスト構造の残りの部分との上側に、半導体材料および導電性材料を含む第2の材料層を堆積することと、

前記第2の材料層上に、前記3Dレジスト構造とは異なるエッティング速度の第2のレジスト層をロールコーティングすることと、 10

前記第2のレジスト層をエッティングすることにより、前記第2の材料層の第1の部分を露出することと、

前記第2の材料層の前記第1の部分をエッティングすることと、

前記3Dレジスト構造の前記3番目に最も薄い層をエッティングすることにより前記第1の材料層の第3の部分を露出することと、

前記第1の材料層の前記第3の部分をエッティングすることと、

前記3Dレジスト構造の残りの部分と、前記第2のレジスト層の残りの部分とを除去することとをさらに含む、半導体デバイスを形成する方法。

#### 【請求項11】

20

半導体デバイスを形成する方法であって、

フレキシブル基板材料を用意することと、

前記フレキシブル基板上に第1の材料層を堆積することと、

前記第1の材料層上にレジスト層を堆積することと、

スタンピングツールを用いることにより、前記レジスト層内に3Dパターンを形成することと、

前記レジスト層を硬化させることにより、前記第1の材料層上に、垂直方向に異なる複数の高さを有する3Dレジスト構造を形成することと、

前記3Dレジスト構造を用いることにより前記フレキシブル基板上に交点アレイを形成することと、を含み、 30

前記3Dレジスト構造は、別の溝よりも狭い溝を含み、

前記3Dレジスト構造を用いて交点アレイを形成することを含み、該交点アレイを形成することは、

前記3Dレジスト構造の第1の最も薄い層をエッティングして貫通することにより、前記第1の材料層の第1の部分を露出させることと、

前記第1の材料層の前記露出された部分と、前記3Dレジスト構造の残りの部分との上側に、半導体材料および導電性材料を含む第2の材料層を堆積することと、

前記狭い溝に容易に入っていく第2のレジスト層を前記第2の材料層の上側に堆積することと、

前記第2の材料層を異方性エッティングして貫通することにより、前記3Dレジスト構造の前記残りの部分を露出させることと、 40

前記3Dレジスト構造の露出された前記残りの部分および前記狭い溝に入った第2のレジスト層を取り除くことと、

を含む半導体デバイスを形成する方法。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は包括的に半導体デバイスの分野に関し、より詳細には半導体デバイスを形成するための方法およびシステムに関する。

##### 【0002】

50

### 【従来の技術】

現在、既存の構造を小型化するとともに、より小型の構造を製造する傾向が強くなっている。この工程は一般的に微細加工と呼ばれる。微細加工がかなりの影響力を持っている1つの分野は、マイクロエレクトロニクス分野である。詳細には、一般に超小型電子回路構造を小型化することにより、その構造のコストが下がり、性能が向上し、電力消費が減少し、さらに所与の寸法の場合に、より多くの部品を収容できるようになってきた。エレクトロニクス分野では、微細加工は多方面において盛んになっているが、バイオテクノロジー、光学、機械システム、センシング装置および原子炉のような他の応用形態にも適用されできている。

### 【0003】

微細加工工程において用いられる1つの方法は、インプリントリソグラフィである。インプリントリソグラフィは通常、基板材料上の薄膜を高分解能でパターニングするために用いられる。パターニングされる薄膜には、誘電体、半導体、金属あるいは有機材料を用いることができ、その薄膜は薄膜あるいは個々の層としてパターニングされることができる。インプリントリソグラフィは、従来のフォトリソグラフィほど平坦性を気にしないので、ロールツーロール環境において素子をパターニングするのに特に有用である。さらに、インプリントリソグラフィはより高いスループットを有し、より幅が広い基板を取り扱うことができる。

### 【0004】

通常、電子回路素子の製造はいくつかのパターニングステップを必要とし、そのパターニングステップは多くの場合に、最小機構サイズに匹敵するか、さらにはそれを上回る精度で互いに位置合わせされなければならない。従来のフォトリソグラフィでは、光学的なアライメントマークを用いて、連続するパターニングステップ間の位置合わせを保証する。ロールツーロール方式でも光学的な位置合わせを用いることはできるが、いくつかの理由により実用的ではない。まず、根底となるインプリントリソグラフィ工程が光学的ではないため、位置合わせが複雑になる。次に、ロールツーロール方式の基板が平坦でないことにより、被写界深度の制限および他の光学収差に起因して、光学的に位置合わせを行うことができる精度に問題が生じる。最後に、ロールツーロール処理において用いられるフレキシブル基板は、温度、湿度あるいは機械的応力の変動に起因して、寸法の変化が生じる懼れがある。1つのパターニングされる層が次の層に対してこのように収縮あるいは拡大することにより、大きな面積の位置合わせが不可能になる場合がある。

### 【0005】

#### 【発明が解決しようとする課題】

したがって、上記の問題を解消する、素子を製造するための方法およびシステムが必要とされる。その方法およびシステムは、簡単で、費用対効果があり、しかも既存の技術に容易に適応できなければならない。本発明の目的は、そのような方法およびシステムを提供することである。

### 【0006】

#### 【課題を解決するための手段】

本発明は半導体デバイスを形成するための方法およびシステムを含む。本発明は、スタンピングツールを用いて、3次元レジスト構造を生成することを含み、それにより薄膜パターニングステップが一度の成形ステップでレジストに転写されることができ、その後、後続の処理ステップにおいて現れるようになる。したがって、連続するパターニングステップ間の位置合わせは、製造工程において発生する可能性がある拡大あるいは収縮に関係なく、スタンピングツールが製造された精度によって決定されることができる。

### 【0007】

本発明の第1の態様は、半導体デバイスを形成するための方法を含む。その方法は、基板を用意することと、基板上に第1の材料層を堆積することと、基板上に3次元(3D)レジスト構造を形成することとを含み、その3Dレジスト構造は、その構造全体にわたって複数の垂直方向に異なる高さを含む。

10

20

30

40

50

**【 0 0 0 8 】**

本発明の第2の態様は、フレキシブル基板上に第1の材料層を堆積するための手段と、フレキシブル基板上にレジスト層を堆積するための手段と、レジスト層に3Dパターンを転写し、フレキシブル基板上に3Dレジスト層を形成するための手段と、その3Dレジスト層を用いてフレキシブル基板上に交点アレイを形成するための手段とを含む、半導体デバイスを形成するためのシステムを含む。

**【 0 0 0 9 】**

本発明の他の態様および利点は、一例によって本発明の原理を例示する、添付の図面とともに取り上げられる、以下に記載される詳細な説明から明らかになるであろう。

**【 0 0 1 0 】**

10

**【 発明の実施の形態 】**

本発明は半導体デバイスを形成するための方法およびシステムに関する。以下の説明は、当業者が本発明を実施し、利用できるようにするために提供され、特許出願およびその要件に即して与えられる。本明細書に記載される好ましい実施形態、ならびに一般的な原理および機構に対する種々の変更は、当業者には容易に明らかになるであろう。したがって、本発明は、示される実施形態に限定されることを意図するわけではなく、本明細書に記載される原理および機構に一致する最も広い範囲が認められるべきである。

**【 0 0 1 1 】**

例示のための図面に示されるように、本発明は、半導体デバイスを形成するための方法およびシステムである。本発明は、スタンピングツールを用いて、3次元レジスト構造を生成することを含み、それによって、複数のパターンが一度の成形ステップでレジストに転写され、その後、後続の処理ステップにおいて現れるようになる。

20

**【 0 0 1 2 】**

本発明は、半導体デバイスを形成するために用いられるものとして記載されているが、当業者であれば、本発明の精神および範囲内に留まりながら、本発明を用いて他のタイプの素子（たとえば、機械、光学、生物学等）を形成することができることは容易に理解されよう。

**【 0 0 1 3 】**

本発明をさらに深く理解するために、図1を参照されたい。図1は、本発明による方法の上位レベルの流れ図である。最初に、ステップ110によって、基板がおかれ。その基板は、ロールツーロール製造工程において用いるのに適したフレキシブル基板を含むことが好ましい。次に、ステップ120によって、基板上に材料層が堆積される。その材料は、有機材料あるいは無機材料を含むことが好ましい。最後に、ステップ130によって、第1の材料層上に、構造全体にわたって複数の垂直方向に異なる高さを含む3次元（3D）レジスト構造が形成される。その3Dレジスト構造は、スタンピングツールを用いることにより生成されることが好ましい。その3Dレジスト構造は構造全体にわたって複数の垂直方向に異なる高さを含むので、その構造を用いて、後続のエッチングステップに基づいて、下層にアライメントパターンを転写することができる。

30

**【 0 0 1 4 】**

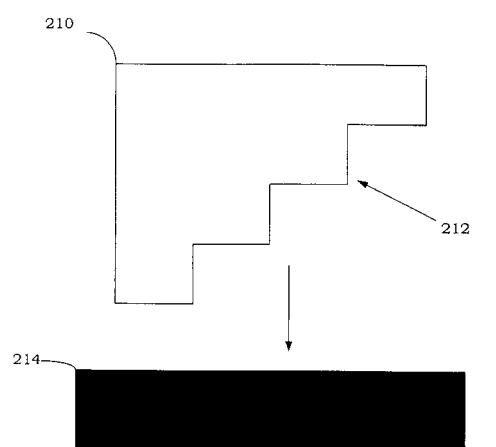

上記のように、本発明は、スタンピングツールを用いて、フレキシブル基板上の3Dレジスト構造を生成することを含む。この概念をより明瞭に理解するために、図2A～図2Cを参照されたい。図2A～図2Cは、スタンピングツールを用いて3Dレジスト構造を形成することに関する断面を示す。図2Aは、スタンピングツール210の断面と、未形成のレジスト材料層214とを示す。スタンピングツール210は、レジスト層214に転写されることになる3Dパターン212を含む。レジスト層214は、市販されている種々のポリマーのうちの任意のものを含むことができる。たとえば、ノーランド社光接着剤（NOA）ファミリーのポリマーの中のものを用いることができる。

40

**【 0 0 1 5 】**

その後、スタンピングツール210はレジスト層214に押圧され、それによりレジスト層214が変位し、スタンピングツール210の3Dパターン212が生成される。図2

50

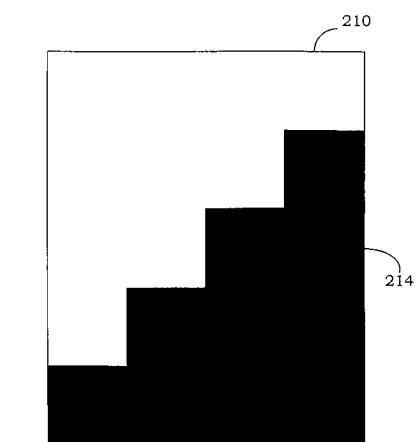

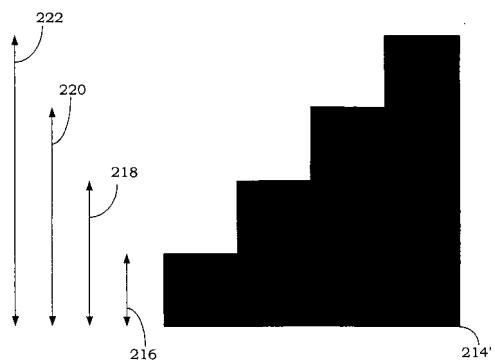

Bは、レジスト層214に押圧されているスタンピングツール210の断面を示す。その後、変位したレジスト層214は、紫外線リソグラフィあるいは他の適当な硬化手段を用いて硬化される。図2Cは形成されたレジスト層214'の断面を示す。

#### 【0016】

さらに、図2Cから明らかなように、形成されたレジスト層214'、すなわちレジスト構造は、垂直方向に異なる高さ216、218、220、222を含む。垂直方向の高さは離散して異なる、すなわち少なくとも1つの高さが別の高さとは大きく異なることが好ましい。したがって、これらの垂直方向に異なる高さによって、構造214'は、後続のエッチングステップに基づいて、下層に対してアライメントパターンを転写するために用いられるようになる。これらの構造は、交点メモリアレイを形成する際に特に有用である。

10

#### 【0017】

##### 交点アレイ

交点メモリアレイは、その間に半導体層を有し、平行に離間して配列される直交する導体の組からなる2つの層を含むことが好ましい。2組の導体は行電極と列電極とを形成し、それらの電極は、行電極がそれぞれ厳密に1つの場所で各列電極を横切るように重ね合せられる。

#### 【0018】

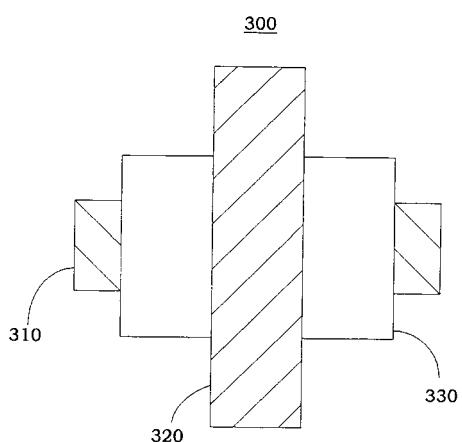

交点アレイをさらに詳しく理解するために、ここで図3を参照されたい。図3は交点アレイ構成300の図である。各交点では、半導体層330を通して行電極310と列電極320との間の接続が形成され、半導体層330は直列に接続されるダイオードおよびヒューズのように機能する。アレイ内のダイオードは全て、全ての行電極と全ての列電極との間に共通の電位がかけられる場合に、全てのダイオードに同じ方向にバイアスがかかるよう向きを定められる。ヒューズ素子は、その中に臨界電流が流れる際に開回路になる分離素子として実現される場合があるか、あるいはダイオードの機能に組み込まれる場合がある。

20

#### 【0019】

当業者であれば、上記の交点アレイが、本発明の精神および範囲内に留まりながら、限定はしないが、トランジスタ、抵抗、コンデンサ等を含む種々の半導体デバイスを形成する際に用いられ得ることは理解されよう。

30

#### 【0020】

ここで、上記の3Dレジスト構造を用いて交点アレイを形成するために、3つの異なる手法が提供されるであろう。第1の手法は、3D構造とともに「シャドーイング」効果を利用して、交点アレイを形成する。第2の手法は、相互エッチング選択性を有する2つのポリマーを用いて、交点アレイを形成する。第3の手法は、毛管力の効果を利用して、3D構造を生成し、交点アレイを形成する。3つの手法が記載されるが、その3Dレジスト構造が、本発明の精神および範囲内に留まりながら、種々の異なる手法とともに利用できることは、当業者であれば理解されよう。

#### 【0021】

##### シャドーイング効果

40

3Dレジスト構造を利用して交点アレイを形成するための第1の手法は、シャドーイング効果を考慮する。シャドーイング効果は、適当な条件下で、急勾配の側壁を有するトレーナーを含むある表面上に薄膜が堆積される際に、堆積される材料が、堆積方向に垂直な表面上に優先的に集まり、側壁を覆うことが回避される現象である。ある角度で堆積し、それにより側壁の1つを「シャドーイングする」ことにより、多くの場合に、この効果を高めることができる。

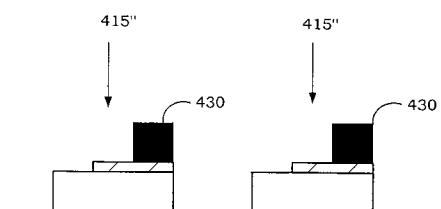

#### 【0022】

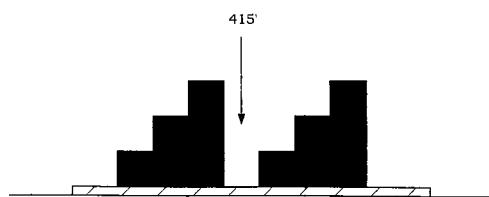

この手法においてシャドーイング効果が如何に考慮されるかをさらに深く理解するために、ここで、以下の説明とともに図4A~図4Gを参照されたい。図4A~図4Gは、シャドーイング効果を用いて交点アレイを形成する工程を示す。図4Aは、フレキシブル基板41

50

0と、第1の材料層（「第1の薄膜スタック」）415と、形成される3Dレジスト構造420とを含む構成400の側面図である。

#### 【0023】

一旦、レジスト構造が形成されると、異方性エッチング工程によってレジスト構造の最も薄い層を除去し、それにより第1の薄膜スタックの一部を露出させることによりその工程が開始される。図4Bは、第1の薄膜スタックの露出された部分415'を示す。次に、同じあるいは異なるエッチング剤を用いて、第1の薄膜スタックの露出された部分がエッチングされ、それにより構造内に複数のポケットが形成される。図4Cは、エッチングされて基板410内にポケット425が形成された後の構成を示す。この工程において、ポケットの側壁は急峻なままであり、ポケットが第1の薄膜スタックの厚みよりも非常に大きな深さを有することが重要である。理想的には、「シャドーイング」効果を高めるために、基板内のポケットが第1の薄膜スタックをわずかにアンダーカットすることが最も望ましい。

#### 【0024】

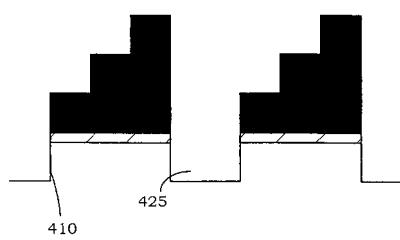

次に、レジスト構造のうちのその次に最も薄い層がエッチングされ、それにより第1の薄膜スタックの第2の部分が露出される。その後、第1の薄膜スタックの露出された第2の部分はエッチングされて貫通される。しかしながら、このステップでは、その下側にある基板から薄膜スタックが除去される際に、エッチングが停止される。図4Dは、このステップの後の露出された基板410'を示す。

#### 【0025】

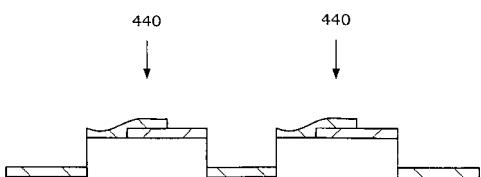

次のステップでは、レジスト構造のうちのその次に最も薄い部分がエッチングされ、それにより第1の薄膜スタックの第3の部分が露出される。しかしながら、このステップでは、第1の薄膜スタックの露出された部分はエッチングされない。このステップの終了時に、元のレジストの全ての残りの部分は一連の分離された島状部になる。図4Eは、レジストの分離された島状部430と、第1の薄膜スタックの露出された部分415'を示す。

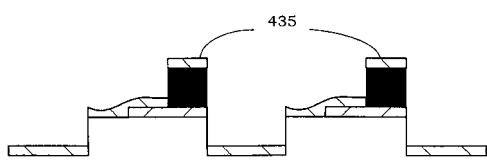

#### 【0026】

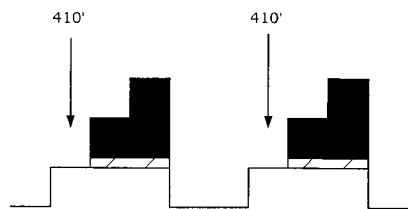

次に、その構成全体の上側に、第2の材料層（第2の薄膜スタック）が堆積される。第2の薄膜スタックは、半導体材料と導電性材料とを含むことが好ましい。これらの堆積の条件は、第1の薄膜スタックの厚みから生じる小さな段差部が、コンフォーマルに覆われるような条件になるであろう。しかしながら、ポケットの側壁に対応するより大きな段差部は覆われないのである。図4Fは堆積後の第2の薄膜スタック435を示す。

#### 【0027】

最後に、レジスト構造の残りの部分が除去され、それにより交点アレイが形成される。図4Gは交点アレイ440からなる構造を示す。このステップの終了時に、交点アレイが形成されているが、さらに別のステップとして、最終的な素子において短絡を引き起こす可能性がある、側壁上に残留する全ての薄膜を除去するための光洗浄が含まれる場合がある。

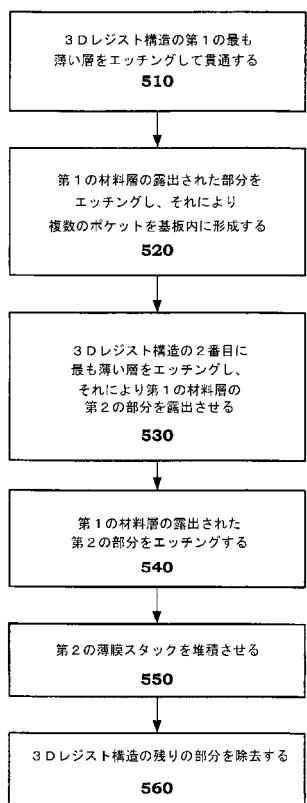

#### 【0028】

上記の手法をさらに深く理解するために、ここで図5を参照されたい。図5は、本発明による上記の方法の流れ図である。最初に、一旦、レジスト構造が形成されたなら、ステップ510によって、レジスト構造の第1の最も薄い層が異方性エッチングされ、それにより第1の薄膜スタックの第1の部分が露出される。次に、ステップ520によって、第1の薄膜スタックの露出された第1の部分がエッチングされ、基板内に複数のポケットが形成される。そのポケットは第1の薄膜スタックよりも非常に大きな深さを含み、第1の薄膜スタックをわずかにアンダーカットして、それによりシャドーイング効果を高めることが好ましい。次に、ステップ530によって、レジストの2番目に最も薄い層がエッチングされ、それにより、第1の薄膜スタックの第2の部分が露出される。

#### 【0029】

その後、ステップ540によって、第1の薄膜スタックの露出された第2の部分がエッチ

10

20

30

40

50

ングされる。その後、ステップ 550 によって、第 2 の薄膜スタックが堆積される。第 2 の薄膜スタックは、半導体材料と導電性材料とを含むことが好ましい。また、これらの堆積の条件は、第 1 の薄膜スタックの厚みから生じる小さな段差部が覆われ、ポケットの側壁に対応する、より大きな段差部が覆われないような条件である。最後に、ステップ 560 によって、レジストの残りの部分が除去される。

#### 【0030】

相互エッティング選択性を有する 2 つのマスクポリマー

3D レジスト構造を用いて交点アレイを形成するための第 2 の手法は、各化合物がある特定の条件下で他の化合物よりも非常に速くエッティングされることができ、たとえばポリマー A および B の場合に、ポリマー「A」のためのエッティングがポリマー「B」に影響を及ぼさず、ポリマー「B」のためのエッティングがポリマー「A」には影響を及ぼさないような特性を有する 2 つのポリマーを利用する。これらの条件は、異なるエッティング剤、異なる流速、異なる部分圧、異なるプラズマ電力等を含み得る。さらに、これらのエッティング方法はいずれも異方性ドライエッティングであることが好ましい。

10

#### 【0031】

上記の手法はポリマー材料とともに用いられるものとして開示されるが、当業者であれば、本発明の精神および範囲内に留まりながら、成形され、鋳造され、その後硬化できる任意の材料が、ポリマー材料の代わりにレジストとして用いることができることは容易に理解されよう。たとえば、本発明の上記の実施形態において、スピノン・オン・ガラス (SOG) を第 2 のポリマーとして用いることができる。

20

#### 【0032】

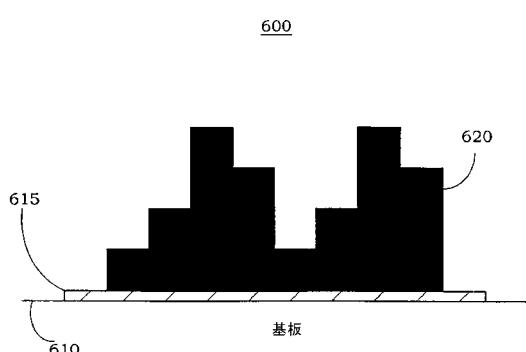

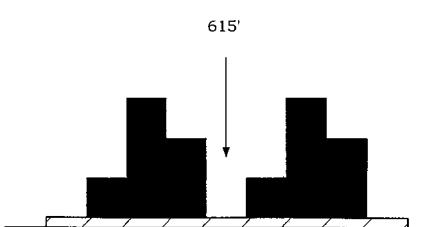

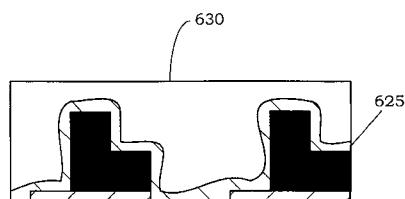

この手法についての理解をさらに深めるために、ここで、以下の説明とともに図 6A～図 6I を参照されたい。図 6A～図 6I は、2 つのポリマーを用いて交点アレイを形成する工程を示す。図 6A は、フレキシブル基板 610 と、第 1 の材料層（「第 1 の薄膜スタック」）615 と、形成された 3D レジスト構造 620 とを含む構成 600 を示しており、構造 620 全体にわたって、複数の垂直方向に異なる高さが存在する。一旦、レジスト構造が形成されたなら、レジスト構造の最も薄い層が異方性エッティング工程によって除去され、それにより第 1 の薄膜スタックの一部が露出される。図 6B は、第 1 の薄膜スタックの露出された部分 615' を示す。

30

#### 【0033】

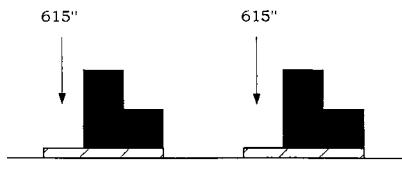

次に、同じあるいは異なるエッティング剤を用いて、第 1 の薄膜スタックの露出された部分がエッティングされる。理想的には、これらのエッティング工程は、それらの工程がレジスト構造を腐蝕する速度以上の速度で第 1 の薄膜スタックを除去することになる。次に、レジスト構造のうちの次に薄い層がエッティングされ、それにより第 1 の薄膜スタックの第 2 の部分が露出され、その場合に、第 1 の薄膜スタックの第 2 の露出された部分は以前のステップにおいてエッティングされた領域に隣接して存在する。図 6C は第 1 の薄膜スタックの第 2 の露出された部分 615'' を示す。

30

#### 【0034】

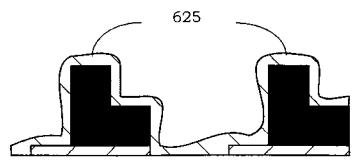

次に、第 2 の材料層（第 2 の薄膜スタック）が堆積される。第 2 の薄膜スタックは半導体材料および導電性材料を含むことが好ましい。基板、第 1 の薄膜スタックおよびレジストの全ての露出された部分がこのステップにおいてコーティングされ得る。図 6D は堆積された第 2 の薄膜スタック 625 を示す。

40

#### 【0035】

その後、第 2 のポリマーが第 2 の薄膜スタック上に被着される。このコーティングは、グラビアコーティングのようなロールコーティング工程によって被着され得るか、あるいは真空蒸着あるいは気相成長によって被着され得る。このコーティングは構造を平坦化することを意図しており、結果として、概ね平坦な表面が、先行するステップによって生成されたトポロジーの全てを覆うようになる。

図 6E は、第 2 の薄膜層 625 を覆う第 2 のポリマー層 630 を示す。

#### 【0036】

50

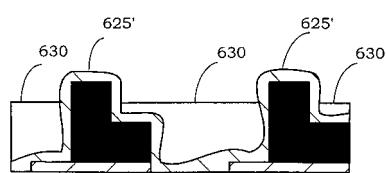

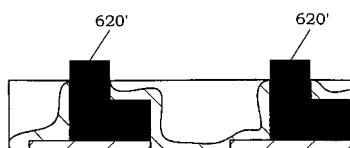

次に、最初のレジストの水平な表面上に堆積された第2の薄膜スタックの全てが現れるまで、第2のポリマー層がエッチバックされる。図6Fは、第2のポリマー層630をエッティングした後に露出された第2の薄膜スタック625'を示す。第2の薄膜スタックは除去されることになるので、この工程のためのエッティング停止層として機能する必要はないことに留意されたい。

#### 【0037】

次に、第2の薄膜スタックが、レジスト構造の上側表面からエッティングされる。ここで用いられるエッティング工程は、第2の薄膜スタックがエッティングされる速度より速く第2のポリマーを腐蝕しないことが重要である。図6Gは、第2の薄膜スタックがエッティングされた後のレジストの露出された部分620'を示す。次に、レジスト構造のうちの次に薄い部分がエッティングして除去され、それにより第1の薄膜スタックの別の部分が露出される。その後、第1の薄膜スタックのこの部分は、同じあるいは異なるエッティング剤によって除去される。レジストおよび第1の薄膜スタックを除去するために用いられる一連のエッティング工程は、第2のポリマーによって覆われる第2の薄膜スタックを除去しないことが好ましい。これは、第2のポリマー層あるいは第2の薄膜スタックの上層が第1の薄膜スタックおよびレジストを除去するエッティング工程に影響を受けないようにすることにより達成され得る。図6Hは、第2のポリマー層630の残りの部分を示す。

10

#### 【0038】

最後に、レジスト構造および第2のポリマー層の残りの部分が除去され、それにより交点アレイが形成される。再び、さらに別のステップとして、最終的な素子において短絡を引き起こす可能性がある、側壁上に残留する全ての薄膜を除去するための光洗浄が含まれる場合がある。図6Iは、交点アレイ640からなる構造を示す。

20

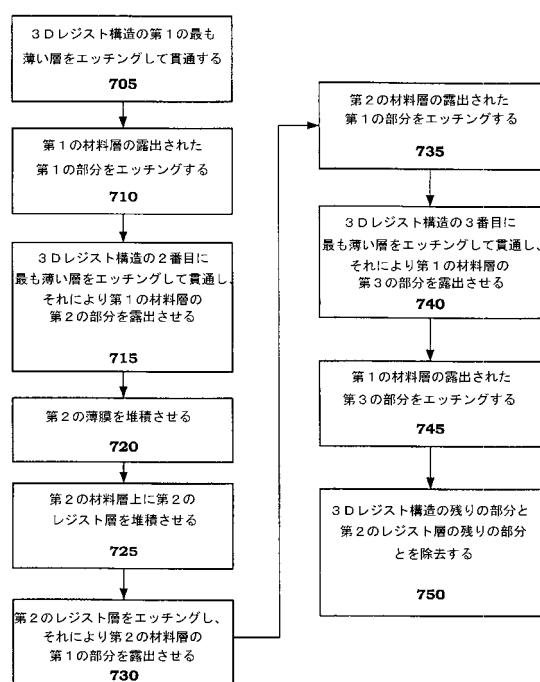

#### 【0039】

上記の手法の理解をさらに深めるために、ここで図7を参照されたい。図7は、本発明による上記の方法の流れ図である。最初に、一旦、レジスト構造が形成されたなら、ステップ705によって、そのレジスト構造の第1の最も薄い層が異方性エッティングされ、それにより第1の薄膜スタックの第1の部分が露出される。次に、ステップ710によって、第1の薄膜スタックの露出された第1の部分がエッティングされ、それにより基板の一部が露出される。その後、ステップ715によって、レジスト構造のうちの2番目に最も薄い層がエッティングされ、それにより第1の薄膜スタックの第2の部分が露出される。

30

#### 【0040】

次に、ステップ720によって、第2の薄膜スタックが堆積される。第2の薄膜スタックは半導体材料と導電性材料とを含むことが好ましい。その後、ステップ725によって、第2の薄膜スタック上に第2のレジスト層が被着される。第2のレジスト層はロールコーティング工程によって被着できることが好ましい。次に、ステップ730によって、第2のレジスト層がエッティングされ、それにより第2の薄膜スタックの第1の部分が露出される。その後、ステップ735によって、第2の薄膜層のこの部分がエッティングされる。次に、ステップ740によって、レジストの3番目に最も薄い層がエッティングされ、それにより第1の薄膜スタックの第3の部分が露出される。その後、ステップ745によって、この露出された部分がエッティングされる。最後に、ステップ750によって、レジストおよび第2のレジスト層の残りの部分が除去される。

40

#### 【0041】

##### 毛管力

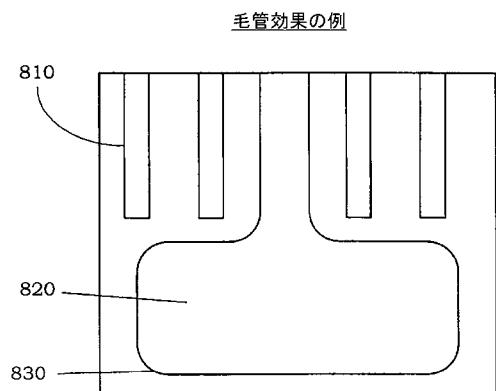

3Dレジスト構造を用いて交点アレイを形成するための第3の手法は、毛管力の現象を考慮する。毛管力は、レジスト材料が、幅が太い溝ではなく、細い溝により容易に入っていくようにする力である。この概念についての理解を深めるために、ここで図8を参照されたい。

#### 【0042】

図8は、基板がフォトポリマーの薄い層でコーティングされ、その後、P D M S (ポリジメチルシロキサン)からなる紫外線透過性の型によって成形された実験の結果を示す。こ

50

の例では、押型は、 $5 \sim 6 \mu\text{m}$ の深さを有する、細い機構( $10 \mu\text{m}$ )および太い機構( $100 \mu\text{m}$ )を含んでいた。UV硬化性ポリマーの薄い層( $0 \sim 9 \mu\text{m}$ )が基板に被着された。押型が液体ポリマーに接触するとき、毛管力がポリマーの大部分を細い溝810に引き込み、太い領域820に入っていくポリマーは少なかった。また、それよりは多くのポリマーが、太い領域820の角部830に引き込まれた。

#### 【0043】

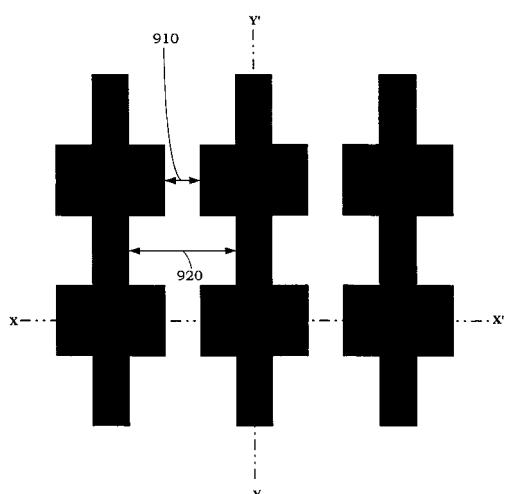

より明確に理解するために、図9を参照されたい。図9は1つのトポロジーの図であり、それによれば、第1の機構910は第2の機構920より細い。第1の機構910が第2の機構920より細いので、毛管力によって、後続の堆積されるポリマー材料は、第2の機構920よりも第1の機構910により容易に入っていくようになる。結果として、第1の機構910が、第2の機構920のポリマー材料層よりも厚いポリマー材料層を含むことになるので、下側の材料が後続の処理ステップに基づいて容易にパターニングされることができる。

#### 【0044】

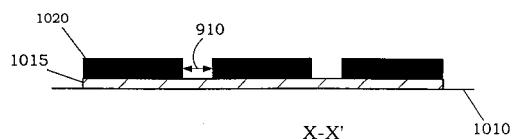

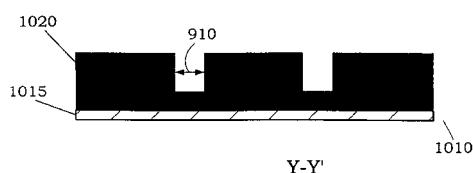

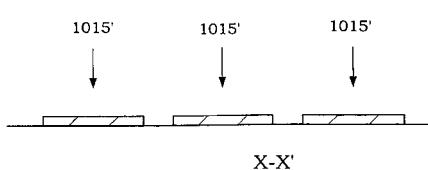

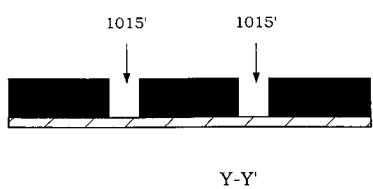

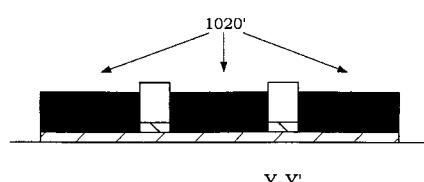

この手法をさらに深く理解するために、ここで、以下の説明とともに図10A～図10Iを参考されたい。図10A～図10Lは、毛管力を用いることにより交点アレイを形成する工程を示す。図10Aは、フレキシブル基板1010と、第1の材料層(「第1の薄膜スタック」)1015と、形成された3Dレジスト構造1020とを含む構成のX-X'(図9より)断面図を示しており、構造1020全体にわたって、複数の垂直方向に異なる高さが存在する。図10Bは、その構成のY-Y'断面図を示す。両方の図面には、図9のトポロジーの機構910に対応する機構910も示される。

#### 【0045】

一旦、レジスト構造が形成されたなら、そのレジスト構造のうちの最も薄い層が異方性エッチング工程によって除去され、それにより第1の薄膜スタックの一部が露出される。図10Cはその構成のX-X'断面図を示しており、それによれば第1の薄膜スタックの一部1015'が露出されている。図10Dは上記のエッチング工程後のその構成のY-Y'断面図を示す。

#### 【0046】

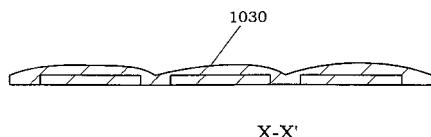

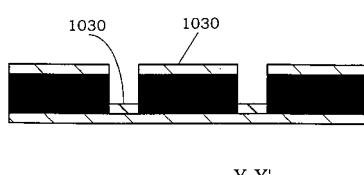

次に、第2の材料層(第2の薄膜スタック)が堆積される。第2の薄膜スタックは半導体材料と導電性材料とを含むことが好ましい。図10Eおよび図10Fはそれぞれ、第2の薄膜スタック1030を堆積した後のその構成のX-X'およびY-Y'断面図を示す。

#### 【0047】

その後、第2のポリマーがその構造全体にわたって被着される。第2のポリマーを被着する際に2つの技法が想定される。第1の技法を用いるとき、第2のポリマーは相対的に低い粘性を有し、容易にレジストを潤滑させる。被着される第2のポリマーの量は、その構造のトポロジー上に存在する空隙を完全に満たすほど十分な量ではないが、毛管力に起因して、第2のポリマーは細い通路により容易に入っていくであろう。結果として、これらの領域は、壁部間により大きな空間が存在する領域よりも深くまで満たされるであろう。

#### 【0048】

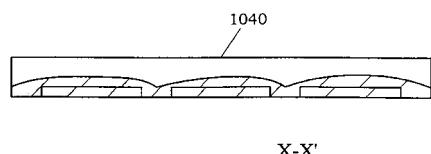

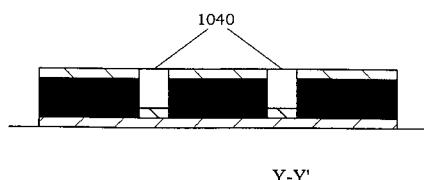

第2の想定される技法は、気相成長あるいは真空蒸着工程を用いて、その構造上に均一に第2のポリマーを被着することを含む。再び、毛管力に基づいて、太い隙間よりも速く、細い隙間が隠されるであろう。また、この工程は幾何学的な効果に依存し、エッチング選択性には依存しないため、第2のポリマーはレジスト構造と同じあるいは異なる化学的組成を有する場合がある。図10Gおよび図10Hはそれぞれ、第2のポリマー1040を堆積した後のその構成のX-X'およびY-Y'断面図を示す。

#### 【0049】

上記の手法はポリマー材料とともに利用されるものとして開示されるが、当業者であれば、本発明の精神および範囲内に留まりながら、種々のレジスト化合物のうちの任意の化合物を用いることは容易に理解されよう。

#### 【0050】

10

20

30

40

50

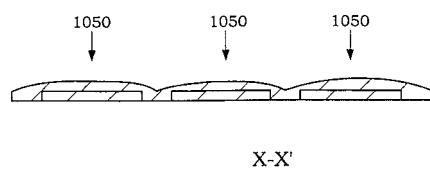

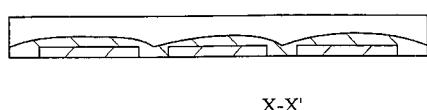

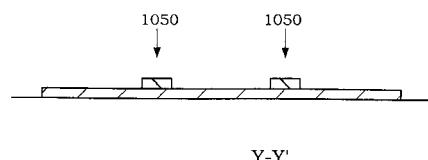

一旦、第2のポリマーが被着されたなら、異方性エッチングが実行され、それにより露出された第2の薄膜スタックが除去され、第1のレジストの一部が露出される。図10Iおよび図10Jはそれぞれ、異方性エッチングが実行された後のその構成のX-X'およびY-Y'断面図を示す。図10Jは露出されたレジスト1020'を示す。次に、レジストおよび第2のポリマーが除去される。第2の薄膜スタックが第1の薄膜スタックを覆う領域が交点アレイである。図10Kおよび図10Lはそれぞれ、形成された交点アレイ1050のX-X'およびY-Y'断面図を示す。

#### 【0051】

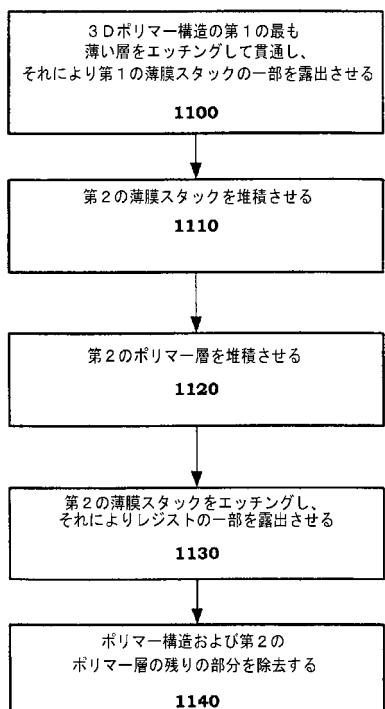

上記の手法をより深く理解するために、ここで図11を参照されたい。図11は、本発明による上記の方法の流れ図である。最初に、一旦、レジスト構造が形成されたなら、ステップ1100によって、そのレジスト構造の第1の最も薄い層が異方性エッチングされ、それにより第1の薄膜スタックの第1の部分が露出される。形成されるレジスト構造は、別の機構より幅が広い少なくとも1つの機構を含むことが好ましい。その後、ステップ1110によって、第2の薄膜スタックが堆積される。第2の薄膜スタックは半導体材料および導電性材料を含むことが好ましい。

10

#### 【0052】

次に、ステップ1120によって、第2のポリマー層が堆積される。その後、ステップ1130によって、異方性エッチングが実行され、それにより第2の薄膜スタックが除去されて、レジストの一部が露出される。最後に、ステップ1140によって、レジストおよび第2のポリマーの残りの部分が除去される。

20

#### 【0053】

半導体デバイスを形成するための方法およびシステムが開示してきた。その方法およびシステムは、スタンピングツールを用いて3Dレジスト構造を生成することを含み、それにより薄膜パターンが一度の成形ステップでレジストに転写され、その後、後続の処理ステップにおいて現れるようになる。

#### 【0054】

本発明が図示される実施形態にしたがって記載してきたが、当業者であれば、それらの実施形態に対する変形形態が実現可能であり、それらの変形形態が本発明の精神および範囲内に入ることは容易に理解されよう。したがって、併記の特許請求の範囲の精神および範囲から逸脱することなく、数多くの変更が当業者によってなされる場合がある。

30

#### 【0055】

##### 【発明の効果】

本発明によれば、半導体デバイスの製造時に、基板の拡大あるいは縮小に関係なく薄膜のパターニングステップ間の位置ずれが生じることのない、簡単で、費用対効果があり、しかも既存の技術に容易に適応する半導体微細加工方法およびシステムを提供することである。

##### 【図面の簡単な説明】

【図1】本発明による方法の上位レベルの流れ図。

【図2A】スタンピングツールを用いる3Dレジスト構造の形成を示す図。

【図2B】スタンピングツールを用いる3Dレジスト構造の形成を示す図。

40

【図2C】スタンピングツールを用いる3Dレジスト構造の形成を示す図。

【図3】交点アレイ構成の図。

【図4A】シャドーイング効果を用いて交点アレイを形成する、第1の実施形態における一段階を示す図。

【図4B】シャドーイング効果を用いて交点アレイを形成する、第1の実施形態における一段階を示す図。

【図4C】シャドーイング効果を用いて交点アレイを形成する、第1の実施形態における一段階を示す図。

【図4D】シャドーイング効果を用いて交点アレイを形成する、第1の実施形態における一段階を示す図。

50

【図4E】シャドーイング効果を用いて交点アレイを形成する、第1の実施形態における一段階を示す図。

【図4F】シャドーイング効果を用いて交点アレイを形成する、第1の実施形態における一段階を示す図。

【図4G】シャドーイング効果を用いて交点アレイを形成する、第1の実施形態における一段階を示す図。

【図5】本発明による方法の第1の実施形態の流れ図。

【図6A】2つのポリマーを用いて交点アレイを形成する、第2の実施形態における一段階を示す図。

【図6B】2つのポリマーを用いて交点アレイを形成する、第2の実施形態における一段階を示す図。 10

【図6C】2つのポリマーを用いて交点アレイを形成する、第2の実施形態における一段階を示す図。

【図6D】2つのポリマーを用いて交点アレイを形成する、第2の実施形態における一段階を示す図。

【図6E】2つのポリマーを用いて交点アレイを形成する、第2の実施形態における一段階を示す図。

【図6F】2つのポリマーを用いて交点アレイを形成する、第2の実施形態における一段階を示す図。

【図6G】2つのポリマーを用いて交点アレイを形成する、第2の実施形態における一段階を示す図。 20

【図6H】2つのポリマーを用いて交点アレイを形成する、第2の実施形態における一段階を示す図。

【図6I】2つのポリマーを用いて交点アレイを形成する、第2の実施形態における一段階を示す図。

【図7】本発明による方法の第2の実施形態の流れ図。

【図8】基板がフォトポリマーの薄い層でコーティングされ、次にP D M Sの紫外線透過性の型によって成形された実験の結果を示す図。

【図9】第1の機構が第2の機構よりも狭いトポロジーを示す図。

【図10A】毛管力を用いることにより交点アレイを形成する、第3の実施形態における一段階を示す図。 30

【図10B】毛管力を用いることにより交点アレイを形成する、第3の実施形態における一段階を示す図。

【図10C】毛管力を用いることにより交点アレイを形成する、第3の実施形態における一段階を示す図。

【図10D】毛管力を用いることにより交点アレイを形成する、第3の実施形態における一段階を示す図。

【図10E】毛管力を用いることにより交点アレイを形成する、第3の実施形態における一段階を示す図。

【図10F】毛管力を用いることにより交点アレイを形成する、第3の実施形態における一段階を示す図。 40

【図10G】毛管力を用いることにより交点アレイを形成する、第3の実施形態における一段階を示す図。

【図10H】毛管力を用いることにより交点アレイを形成する、第3の実施形態における一段階を示す図。

【図10I】毛管力を用いることにより交点アレイを形成する、第3の実施形態における一段階を示す図。

【図10J】毛管力を用いることにより交点アレイを形成する、第3の実施形態における一段階を示す図。

【図10K】毛管力を用いることにより交点アレイを形成する、第3の実施形態における 50

一段階を示す図。

【図 10 L】毛管力を用いることにより交点アレイを形成する、第 3 の実施形態における一段階を示す図。

【図 11】本発明による方法の第 3 の実施形態の流れ図。

【符号の説明】

210 スタンピングツール

212 3Dパターン

214 レジスト層

300 交点アレイ

310 行電極

320 列電極

410 フレキシブル基盤

420 3Dレジスト構造

10

【図 1】

【図 2 A】

【図 2 B】

【図 2 C】

【図 3】

【図 4 A】

【図 4 B】

【図 4 C】

【図4D】

【図4F】

【図4E】

【図4G】

【図5】

【図6A】

【図6B】

【図 6 C】

【図 6 D】

【図 6 E】

【図 6 F】

【図 6 G】

【図 6 H】

【図 6 I】

【図 7】

【図 8】

【図 9】

【図 10 A】

【図 10 B】

【図 10 C】

【図 10 D】

【図 10 E】

【図 10 F】

【図 10 G】

【図10H】

【図10K】

【図10I】

【図10J】

【図10L】

【図11】

---

フロントページの続き

(72)発明者 カール・フィリップ・タウシッグ

アメリカ合衆国94061カリフォルニア州レッドウッド・シティ、アラメダ・デ・ラス・ブルガス 2295

(72)発明者 ピン・メイ

アメリカ合衆国94306カリフォルニア州パロ・アルト、ウィルキー・ウェイ 4276、ナンバー・ディ

審査官 秋田 将行

(56)参考文献 特開平02-156624(JP,A)

特開平03-100942(JP,A)

特開平05-080530(JP,A)

特表平09-511710(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/027

G03F 7/20 -7/24