(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-141624

(P2005-141624A)

(43) 公開日 平成17年6月2日(2005.6.2)

(51) Int.C1.<sup>7</sup>

F 1

テーマコード(参考)

G06F 17/50

G06F 17/50

664A

5B042

G06F 11/28

G06F 17/50

664G

5B046

G06F 17/50

672C

G06F 11/28

340C

審査請求 未請求 請求項の数 10 O L (全 16 頁)

(21) 出願番号

特願2003-379532 (P2003-379532)

(22) 出願日

平成15年11月10日 (2003.11.10)

(71) 出願人 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100092152

弁理士 服部 毅麿

(72) 発明者 岩本 正美

神奈川県川崎市高津区坂戸3丁目2番1号

富士通エルエスアイテクノロジ株式会社

内

(72) 発明者 小澤 裕一

神奈川県川崎市高津区坂戸3丁目2番1号

富士通エルエスアイテクノロジ株式会社

内

F ターム(参考) 5B042 GA13 GC15 HH06 HH07

5B046 AA08 BA03 JA05

(54) 【発明の名称】 検証装置、検証方法およびプログラム

## (57) 【要約】

【課題】 システムLSI開発におけるハードウェアおよびソフトウェアの検証を精度良く効率的に行う。

【解決手段】 ハードウェア検証時には、HDLモデル2の論理シミュレータ11によるシミュレーション結果と、期待値算出モデル12が生成する期待値とが、等価検証部13で比較、検証される。ソフトウェア検証時には、期待値算出モデル12がインタフェース部15を介して利用され、ファームウェア3がソフトウェアデバッガ14により検証される。期待値算出モデル12は、ハードウェア検証時には期待値生成モデルとして用いられ、ソフトウェア検証時にはハードウェアのCモデルとして用いられる。このように期待値算出モデル12をハードウェア検証とソフトウェア検証の双方に用いることにより、精度良く効率的に検証が行えるようになる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

ハードウェアとハードウェアを制御するソフトウェアとをモデルを用いて検証する検証装置において、

検証時の検証レベルを示す一のタイミング情報と前記一のタイミング情報と異なる他のタイミング情報を有するモデルを、ハードウェア検証とソフトウェア検証の双方に用いることを特徴とする検証装置。

**【請求項 2】**

前記モデルは、複数の異なる検証レベルに対応する数のタイミング情報を有し、検証時の検証レベルに応じた前記タイミング情報に従って入出力データの転送方式を切り替えることを特徴とする請求項 1 記載の検証装置。 10

**【請求項 3】**

前記モデルは、検証時の入出力データを変換するデータ変換手段を有し、検証時に入力されるデータを前記データ変換手段によって変換して演算を実行し、演算後のデータを前記データ変換手段によって再変換して出力することを特徴とする請求項 1 記載の検証装置。

**【請求項 4】**

前記モデルは、検証時の検証レベルに応じたタイミング情報に従って入出力データを転送するインターフェースと、前記インターフェースから転送されるデータを用いて演算を実行するハードウェアモデルと、前記ハードウェアモデルによって演算され前記インターフェースによって出力されるデータを格納するスタックメモリと、を有することを特徴とする請求項 1 記載の検証装置。 20

**【請求項 5】**

ハードウェアとハードウェアを制御するソフトウェアとをモデルを用いて検証する検証方法において、

検証時の検証レベルを示す一のタイミング情報と前記一のタイミング情報と異なる他のタイミング情報を有するモデルを、ハードウェア検証とソフトウェア検証の双方に用いることを特徴とする検証方法。

**【請求項 6】**

前記モデルは、複数の異なる検証レベルに対応する数のタイミング情報を有し、検証時の検証レベルに応じた前記タイミング情報に従って入出力データの転送方式を切り替えることを特徴とする請求項 5 記載の検証方法。 30

**【請求項 7】**

前記モデルは、検証時に入力されるデータを変換して演算を実行し、演算後のデータを再変換して出力することを特徴とする請求項 5 記載の検証方法。

**【請求項 8】**

コンピュータを用いて、ハードウェアとハードウェアを制御するソフトウェアとをモデルを用いて検証するためのプログラムにおいて、

コンピュータに、

検証時の検証レベルを示す一のタイミング情報と前記一のタイミング情報と異なる他のタイミング情報を有するモデルを用いてハードウェア検証を行い、 40

前記モデルを用いてソフトウェア検証を行う処理を実行させることを特徴とするプログラム。

**【請求項 9】**

ハードウェア検証に使用されるモデルを、ソフトウェア検証を行えるように作成する検証装置において、

前記モデルは、前記ソフトウェア検証に使用されるタイミング情報以外のタイミング情報を有することを特徴とする検証装置。

**【請求項 10】**

ハードウェア検証に使用されるモデルを、ソフトウェア検証を行えるように作成する検 50

証装置において、

前記モデルは、前記ソフトウェア検証に使用されるタイミング情報について、複数種別のソフトウェア検証に対応する数有することを特徴とする検証装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は検証装置、検証方法およびプログラムに関し、特にシステムLSI (Large Scale Integrated Circuit) のハードウェアおよびソフトウェアの開発・検証を行うための検証装置、検証方法およびプログラムに関する。

【背景技術】

【0002】

近年のシステムLSIの開発においては、その大規模化、多機能化に伴い、開発期間の長期化やコストの増加が問題となっており、短期間で効率良く、かつ、低成本で所望の高品質システムLSIを製造することのできるハードウェアおよびソフトウェアの開発・検証環境の構築が要望されている。

【0003】

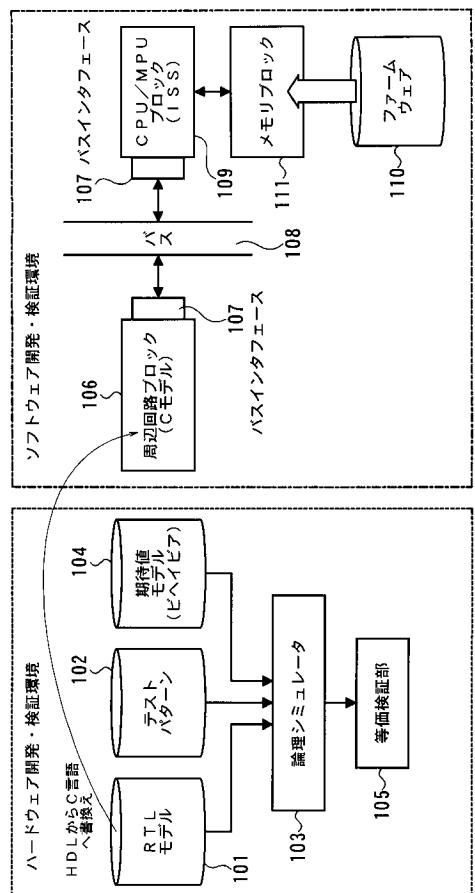

図5は従来のハードウェアおよびソフトウェアの開発・検証環境の概念図である。

システムLSI開発では、まず、LSI仕様の設計後、そのLSI仕様を基にアーキテクチャ設計を行ってシステムを機能モジュールに分割し、ハードウェアとそのハードウェアを制御するソフトウェアとの切り分けを行う。

【0004】

ハードウェアは、例えばシステムLSIに搭載されるCPU (Central Processing Unit) / MPU (Micro Processing Unit) の周辺回路であり、通常、その論理機能のビヘイビアレベルでの記述を基に、ハードウェア記述言語 (Hardware Description Language, HDL) でその動作記述が行われる。

【0005】

そして、この動作記述からハードウェアの論理機能を表現した設計データがレジスタ・トランスマスファ・レベル (Resistor Transfer Level, RTL) で記述される。ハードウェア検証では、このようにHDLを用いてRTL記述されたハードウェアモデル (RTLモデル) 101を、テストパターン102を用い、論理シミュレータ103でシミュレートする。

【0006】

さらに、ハードウェア検証では、そのシミュレーション結果と、RTLモデル101の基になったビヘイビアレベルのハードウェアモデル (期待値モデル) 104からテストパターン102を用いて得られる期待値との等価性が等価検証部105で検証される。シミュレーション結果と期待値とが等価であるか否かによって、RTLモデル101の機能の検証が行われる。

【0007】

なお、ここで用いられる期待値モデル104には、通常、ハードウェアにおける処理のタイミングといった時間的概念は考慮されない。ハードウェア検証後は、論理合成やレイアウト設計等の工程へと進む。

【0008】

一方、ソフトウェアは、通常、C / C++ 等のプログラミング言語で記述される。ソフトウェア検証では、CPU / MPUの周辺回路を動作記述した周辺回路ブロック106を、LSI仕様に合わせてC言語等で記述したバスインターフェース107およびバス108を介して、CPU / MPUを動作記述したCPU / MPUブロック109に接続し、さらに、検証すべきソフトウェア (ファームウェア) 110をメモリブロック111に格納した仮想プロトタイプが使用される。

【0009】

この仮想プロトタイプを用いたソフトウェア検証では、周辺回路ブロック106として

10

20

30

40

50

C言語で記述されたハードウェアモデルが必要になるが、通常はRTLモデル101をC言語に書き換えたプログラム(Cモデル)をソフトウェア検証用に作成し、これをソフトウェア検証時のハードウェアモデルとして使用する。このようなCモデルを用い、CPU/MPUの命令動作を実行する命令セットシミュレータ(Instruction Set Simulator, ISS)をソフトウェアデバッガとして使用し、ほぼ実回路と同じ環境でソフトウェアのデバッグを行う。

#### 【0010】

デバッグ後は、検証後のソフトウェアを、ハードウェア検証を基に形成された実回路に搭載し、システム全体の検証が行われる。

このようなシステムLSI開発においては、最近では、開発期間の短縮を目的として、ソフトウェアデバッガの動作と同期させながらRTLモデル101や期待値モデル104のシミュレーションを行って、ソフトウェアデバッガおよび論理シミュレータ103での各実行結果を比較する協調検証も行われている。

#### 【0011】

また、従来は、ハードウェア検証時のシミュレーションを高速化して開発期間を短縮する目的で、RTLモデルを用いたときのような詳細な(時刻精度が細かい)低速シミュレーションとビヘイビアレベルのモデルを用いたときのような簡略な(時刻精度が粗い)高速シミュレーションを、時刻精度と指定した切り替え時刻に基づいてモデルを切り替えて行うようにした提案もなされている(例えば特許文献1参照)。

【特許文献1】特開平10-261002号公報(段落番号[0037]～[0092])

、図1)

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0012】

しかし、従来のシステムLSI開発では、ソフトウェア検証のために、HDLで記述されたRTLモデルをC言語に書き換えたCモデルを作成する際、CモデルとRTLモデルの間の等価性に問題があった。

#### 【0013】

そのため、ソフトウェア検証を行ったときに、仕様通りの結果が得られないなど、不具合が生じた場合には、その不具合がRTLモデルに等価であるはずのCモデルに起因するものであるのか、検証しているソフトウェアに起因するものであるのか、その特定が非常に困難になる。原因特定のためには、RTLモデルやCモデルの再検証、システム全体の再検証が必要になり、CモデルとRTLモデルの等価性は、システムLSI開発期間の長期化を招く一因となっていた。

#### 【0014】

また、ソフトウェア検証に用いるCモデルは、検証精度を重視するか検証スピードを重視するかといった検証目的に応じた検証レベルごとに別々に作成していた。このようにCモデルを検証レベルごとに別々に作成すると、モデル作成やそのモデルを用いたソフトウェアデバッガに大変な労力と時間が必要になり、これによってもシステムLSI開発の効率化が損なわれていた。

#### 【0015】

本発明はこのような点に鑑みてなされたものであり、システムLSI開発におけるハードウェアおよびソフトウェアの検証を精度良く効率的に行うことのできる検証装置を提供することを目的とする。

#### 【0016】

また、本発明は、システムLSI開発におけるハードウェアおよびソフトウェアの検証を精度良く効率的に行う検証方法を提供することを目的とする。

また、本発明は、システムLSI開発におけるハードウェアおよびソフトウェアの検証を精度良く効率的に行うための処理をコンピュータに実行させるためのプログラムを提供することを目的とする。

10

20

30

40

50

**【課題を解決するための手段】****【0017】**

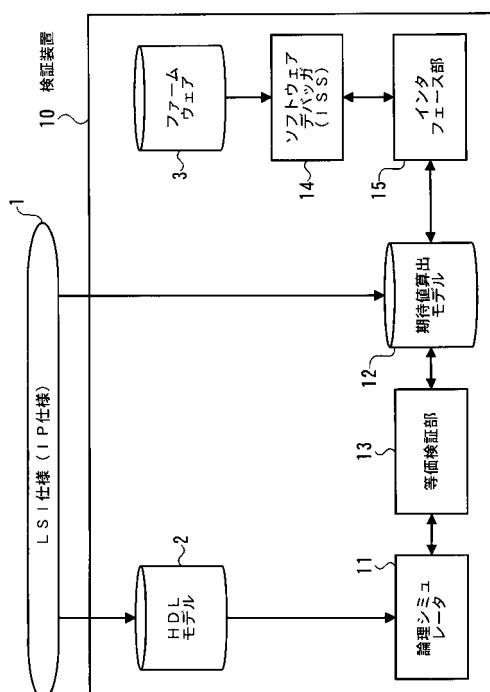

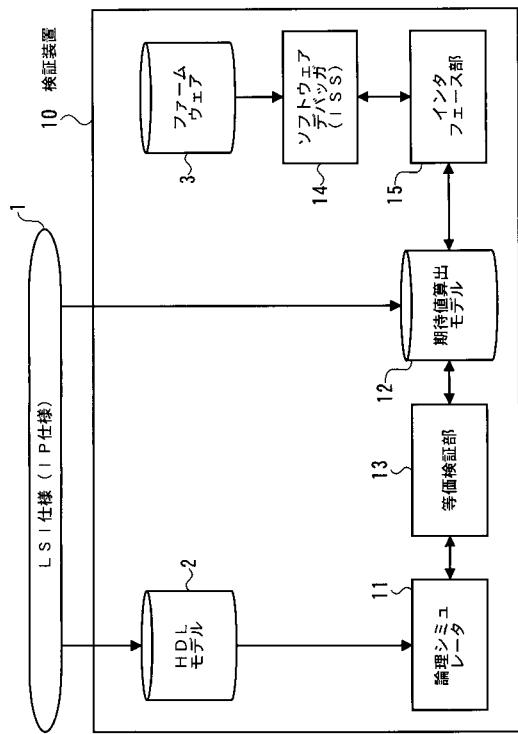

本発明では上記課題を解決するために、図1に示す構成で実現可能な検証装置が提供される。本発明の検証装置は、ハードウェアとハードウェアを制御するソフトウェアとをモデルを用いて検証する検証装置において、検証時の検証レベルを示す一のタイミング情報と前記一のタイミング情報と異なる他のタイミング情報を有するモデルを、ハードウェア検証とソフトウェア検証の双方に用いることを特徴とする。

**【0018】**

図1に示した検証装置10によれば、HDLモデル2の検証の際には、HDLモデル2の論理シミュレータ11によるシミュレーション結果と、期待値算出モデル12が生成する期待値とが、等価検証部13で比較、検証される。そして、ファームウェア3の検証の際には、このHDLモデル2の検証に用いられる期待値算出モデル12がインターフェース部15を介して利用され、ファームウェア3がソフトウェアデバッガ14により検証される。すなわち、期待値算出モデル12は、ハードウェア検証の際には期待値の生成モデルとして用いられ、ソフトウェア検証の際にはハードウェアのCモデルとして用いられる。この期待値算出モデル12は、検証時の検証レベルを示す複数のタイミング情報を有し、ハードウェアまたはソフトウェアの検証の際には、そのタイミング情報を基に、検証レベルに応じたタイミングでデータを転送する。このように期待値算出モデル12をハードウェア検証とソフトウェア検証の双方に用いることにより、精度良く効率的に検証が行えるようになる。

**【0019】**

また、本発明では、ハードウェアとハードウェアを制御するソフトウェアとをモデルを用いて検証する検証方法において、検証時の検証レベルを示す一のタイミング情報と前記一のタイミング情報と異なる他のタイミング情報を有するモデルを、ハードウェア検証とソフトウェア検証の双方に用いることを特徴とする検証方法が提供される。

**【0020】**

このような検証方法によれば、検証時の検証レベルを示す複数のタイミング情報を有するモデルが、ハードウェア検証とソフトウェア検証の双方に用いられ、精度良く効率的に検証が行えるようになる。

**【0021】**

また、本発明では、コンピュータを用いて、ハードウェアとハードウェアを制御するソフトウェアとをモデルを用いて検証するためのプログラムにおいて、コンピュータに、検証時の検証レベルを示す一のタイミング情報と前記一のタイミング情報と異なる他のタイミング情報を有するモデルを用いてハードウェア検証を行い、前記モデルを用いてソフトウェア検証を行う処理を実行させることを特徴とするプログラムが提供される。

**【0022】**

このようなプログラムによれば、検証時の検証レベルを示す複数のタイミング情報を有する期待値算出モデルがハードウェア検証に用いられ、さらにソフトウェア検証にも用いられるようになるので、精度良く効率的に検証が行えるようになる。

**【0023】**

また、本発明では、ハードウェア検証に使用されるモデルを、ソフトウェア検証を行えるように作成する検証装置において、前記モデルは、前記ソフトウェア検証に使用されるタイミング情報を有することを特徴とする検証装置が提供される。

**【0024】**

このような検証装置によれば、複数のタイミング情報を有するモデルを、ハードウェア検証とソフトウェア検証の双方に用いて、精度良く効率的に検証が行える。

また、本発明では、ハードウェア検証に使用されるモデルを、ソフトウェア検証を行えるように作成する検証装置において、前記モデルは、前記ソフトウェア検証に使用されるタイミング情報について、複数種別のソフトウェア検証に対応する数有することを特徴とする検証装置が提供される。

10

20

30

40

50

**【 0 0 2 5 】**

このような検証装置によれば、複数のタイミング情報を有するモデルを、ハードウェア検証とソフトウェア検証の双方に用いて、精度良く効率的に検証が行える。

**【 発明の効果 】****【 0 0 2 6 】**

本発明によれば、検証時の検証レベルを示す複数のタイミング情報を有するモデルを用いてハードウェア検証とソフトウェア検証が行われる。タイミング情報を基に、ひとつのモデルで異なる検証レベルの複数の検証に対応することができるので、ソフトウェア検証用にハードウェアモデル（Cモデル）を作成することが不要になり、また、不具合の原因を効率良く見つけ出すことが可能になる。これにより、システムLSIの開発効率を向上させ、高品質なシステムLSIを短期間でかつ低コストで開発・製造することが可能になる。

10

**【 発明を実施するための最良の形態 】****【 0 0 2 7 】**

以下、本発明の実施の形態を図面を参照して詳細に説明する。

図1は本発明の原理説明図である。

システムLSI開発では、まず、LSI仕様（IP（Intellectual Property）仕様）1が設計され、アーキテクチャの設計を行ってハードウェアとそのハードウェアを制御するためのソフトウェアが切り分けられ、ハードウェア、ソフトウェアそれぞれの詳細設計が行われる。

20

**【 0 0 2 8 】**

ハードウェアは、例えば、システムLSIに搭載されるCPU/MPUの周辺回路等である。ハードウェアについては、その論理機能がVHDL（Very High Speed Integrated Circuit HDL）やVerilog-HDL等のHDLを用いて記述されたハードウェアモデル（HDLモデル）2が設計される。

20

**【 0 0 2 9 】**

また、ソフトウェアは、CPU/MPUやその周辺回路等に所定の処理動作を実行させるためのプログラムからなるファームウェア3である。ソフトウェアについては、C/C++等のプログラミング言語を用いて、システムLSIに搭載されるファームウェア3が設計される。

30

**【 0 0 3 0 】**

本発明の検証装置10は、HDLモデル2およびファームウェア3を有するとともに、HDLモデル2の機能を検証するための論理シミュレータ11、および論理シミュレータ11のシミュレーション結果と期待値算出モデル12によって生成される期待値との等価性を検証する等価検証部13を有している。さらに、この検証装置10は、ファームウェア3の処理動作を検証するためのソフトウェアデバッガ14、およびこのソフトウェアデバッガ14と期待値算出モデル12とを接続するインタフェース部15を有している。

**【 0 0 3 1 】**

このような検証装置10において、論理シミュレータ11は、LSI仕様1に基づく所定のテストパターンを用いてHDLモデル2をシミュレートし、シミュレーション結果を生成する。

40

**【 0 0 3 2 】**

期待値算出モデル12は、LSI仕様1に基づくハードウェアの機能仕様に従ってC/C++等のプログラミング言語を用いて作成されたハードウェアモデルを含んでおり、このハードウェアモデルは、HDLモデル2の検証における期待値の生成モデルとして用いられる。さらに、このハードウェアモデルは、ファームウェア3の検証においては、システムLSIのハードウェアを記述したCモデルとして用いられる。

**【 0 0 3 3 】**

等価検証部13は、HDLモデル2のシミュレーション結果と、所定のテストパターンを用いて期待値算出モデル12から生成される期待値とを比較し、その等価性を検証する

50

。なお、シミュレーション結果が期待値と等価であるHDLモデル2は、ソフトウェア検証、あるいは論理合成、レイアウト設計、タイミング検証、テープアウト等の各工程で利用される。

【0034】

ソフトウェアデバッガ14は、システムLSIに搭載されるCPU/MPUの命令動作をシミュレートするISSであり、ソフトウェア検証の際には、このISSがCPU/MPUに代わってファームウェア3を実行する。

【0035】

インタフェース部15は、ソフトウェアデバッガ14とのインタフェースを有し、さらに、API(Application Program Interface)を用いた期待値算出モデル12とのインターフェースを有する。これにより、ソフトウェアデバッガ14は、このインターフェース部15を介して、ハードウェアのCモデルとして期待値算出モデル12を利用し、ファームウェア3の検証を行うことができるようになっている。

10

【0036】

このように、期待値算出モデル12は、ハードウェア検証においては、システムLSIのCPU/MPUの周辺回路等を示したHDLモデル2の期待値生成モデルとして用いられ、ソフトウェア検証においては、CPU/MPUの周辺回路等を示したCモデルとして用いられるようになっている。

20

【0037】

このようなハードウェア検証およびソフトウェア検証を行う検証装置10は、例えば、一般的なパーソナルコンピュータやワークステーションを用いて構成することができる。その場合、HDLモデル2、ファームウェア3、論理シミュレータ11、期待値算出モデル12、等価検証部13、ソフトウェアデバッガ14、インタフェース部15およびテストパターン等は、プログラムとして構成され、検証装置10が有するハードディスク等の記憶装置あるいは検証装置10内のメモリに格納される。検証装置10では、これらのプログラムが検証装置10のCPU等によって実行されることで、所定の処理機能が実現され、ハードウェア検証およびソフトウェア検証が行えるようになっている。

20

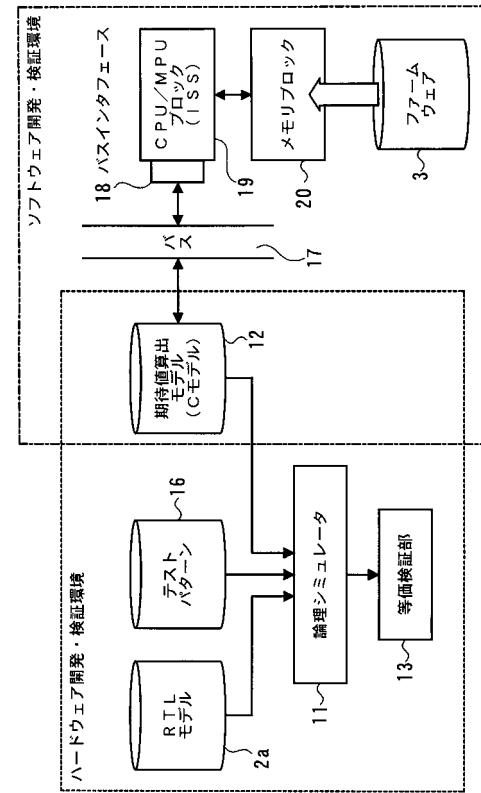

【0038】

図2はハードウェアおよびソフトウェアの開発・検証環境の概念図である。

ハードウェア開発・検証環境は、期待値算出モデル12、RTLモデル2a、テストパターン16、論理シミュレータ11、等価検証部13で構成される。

30

【0039】

ここで、RTLモデル2aは、LSI仕様(IP仕様)1に基づき、システムLSIのハードウェアの論理機能がHDLを用いてRTL記述されたハードウェアモデルである。また、テストパターン16は、このシステムLSIが使われるアプリケーションで想定される命令や命令の組み合わせを示したテストベンチである。

【0040】

ソフトウェア開発・検証環境は、図2に示すように、期待値算出モデル12のほか、期待値算出モデル12にバス17およびバスインターフェース18を介して接続されるCPU/MPUの動作を記述したCPU/MPUブロック19、およびファームウェア3が格納されるメモリブロック20を有する仮想プロトタイプとして構成することができる。

40

【0041】

ここで、バスインターフェース18は、USB(Universal Serial Bus)、PCI(Peripheral Component Interconnect)、IEEE(Institute of Electrical and Electronics Engineers)1394などの規格に従い、LSI仕様1に合わせてC言語で記述され、CPU/MPUブロック19をバス17に接続する。

【0042】

CPU/MPUブロック19としては、ソフトウェアデバッガ14であるISSが用いられる。ISSは、CPU/MPUに代わってメモリブロック20に格納されたC言語のファームウェア3を実行し、CPU/MPUの命令動作をシミュレートするようになって

50

いる。

【0043】

I S S は、ファンクション・アキュレート・レベル (Function Accurate Level) 、トランザクション・アキュレート・レベル (Transaction Accurate Level) 、サイクル・アキュレート・レベル (Cycle Accurate Level) のいずれかの検証レベルで C P U / M P U の命令動作をシミュレートする。

【0044】

ここで、ファンクション・アキュレート・レベルとは、時間概念のない、機能単位でデータを転送して高速にシミュレーションが実行される検証レベルをいう。トランザクション・アキュレート・レベルとは、バスアクセス等のイベント単位でデータを転送してシミュレーションが実行される検証レベルをいう。サイクル・アキュレート・レベルとは、クロック単位でデータを転送してシミュレーションが実行される検証レベルをいう。

【0045】

ソフトウェア検証の際には、検証精度を重視するか、検証スピードを重視するかといった検証目的に応じて、用いる I S S が選択され、選択される I S S によってソフトウェア検証の検証レベルが決まる。

【0046】

メモリブロック 20 は、システム L S I において R A M あるいは R O M として機能し、C P U / M P U やその周辺回路を動作させるファームウェア 3 が格納される。

期待値算出モデル 12 は、後述のバスインターフェースおよびバス 17 を介して、C P U / M P U ブロック 19 と接続されるようになっている。

【0047】

また、期待値算出モデル 12 は、ファンクション・アキュレート・レベル、トランザクション・アキュレート・レベル、サイクル・アキュレート・レベルをそれぞれ示すタイミング情報を有する。このタイミング情報は、期待値算出モデル 12 において、例えば I S S に応じ、ユーザが検証レベルを設定することによって決定される。期待値算出モデル 12 では、このタイミング情報によってシミュレーションの検証レベルが認識され、それによってシミュレーション時のデータ転送のタイミング（機能単位、イベント単位、クロック単位）が制御されるようになっている。

【0048】

このような構成のハードウェアおよびソフトウェアの開発・検証環境において、ハードウェア検証の際には、H D L を用いて記述された R T L モデル 2 a とテストパターン 16 を用い、論理シミュレータ 11 で R T L モデル 2 a の出力をシミュレートする。さらに、この論理シミュレータ 11 では、C 言語で記述された期待値算出モデル 12 とテストパターン 16 を用い、期待値算出モデル 12 の出力がシミュレートされ、期待値が生成される。その際、期待値は、ファンクションレベルの演算によって生成される。

【0049】

この期待値算出モデル 12 は、テストパターン 16 を用いた R T L モデル 2 a のシミュレーションにおける論理シミュレータ 11 のコントロール情報に基づいて演算を行うようになることで、R T L モデル 2 a と動作の同期が行える。このように、期待値算出モデル 12 を、R T L モデル 2 a と同期させて同じ動作をするかどうかを比較することで、ハードウェアの不具合を早い段階で見つけ出すことが可能になる。

【0050】

また、期待値算出モデル 12 は、L S I 仕様 1 に基づくハードウェアの機能仕様に従って作成されているので、R T L モデル 2 a との動作比較基準として好適である。すなわち、従来のハードウェア検証では、R T L モデル 2 a が適正に動作しているか否かの判定基準がなかったために、R T L モデル 2 a が仕様通りに動作しているか否かの見極めが難しかった。しかしながら、期待値算出モデル 12 をハードウェアの機能仕様に従って作成することにより、期待値算出モデル 12 を R T L モデル 2 a の動作が適正か否かの判断基準として利用することができる。

**【 0 0 5 1 】**

R T L モデル 2 a のシミュレーション結果と期待値算出モデル 1 2 の期待値とは、等価検証部 1 3 でその等価性が検証される。シミュレーション結果と期待値とが一致する場合には、ソフトウェア検証や、その R T L モデル 2 a を用いた論理合成等、所定の次工程に移行する。シミュレーション結果と期待値とが不一致の場合には、R T L モデル 2 a および期待値算出モデル 1 2 を再検証し、不具合の生じる原因を究明することとなる。

**【 0 0 5 2 】**

このようにして期待値算出モデル 1 2 の出力と R T L モデル 2 a の出力とが等価となっ 10 た後に、用いる I S S によって決まる検証レベルでのソフトウェア検証が行われる。ソフトウェア検証の際には、ファームウェア 3 が期待値算出モデル 1 2 のハードウェアモデル (C モデル) と共に I S S によって正しく動作するかが検証される。

**【 0 0 5 3 】**

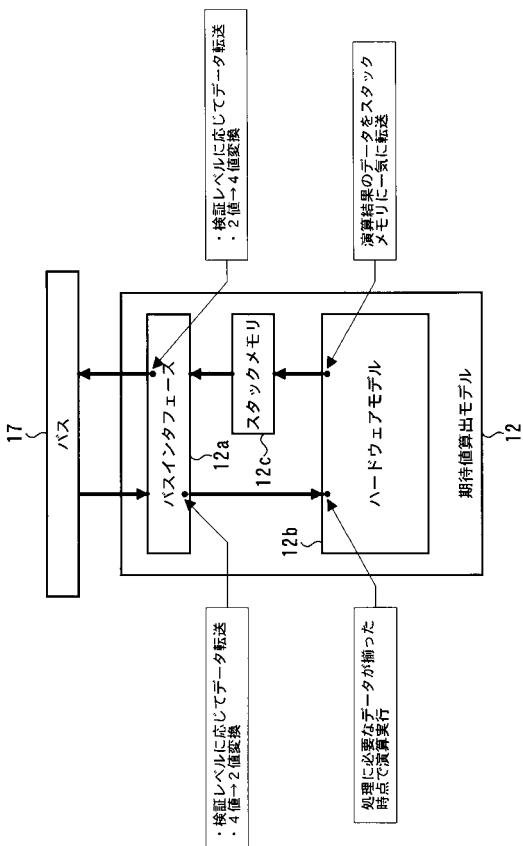

ここで、上記のようにハードウェア検証およびソフトウェア検証で用いられる期待値算出モデル 1 2 について、より詳細に説明する。

図 3 は期待値算出モデルの構成例を示す図である。

**【 0 0 5 4 】**

期待値算出モデル 1 2 は、バス 1 7 に接続される U S B 、 P C I 、 I E E E 1 3 9 4 などの規格に従ったバスインターフェース 1 2 a 、バスインターフェース 1 2 a から転送される入力データを用いて所定の演算を実行するハードウェアモデル 1 2 b 、およびハードウェアモデル 1 2 b の演算結果が格納されるスタックメモリ 1 2 c を有している。 20

**【 0 0 5 5 】**

バスインターフェース 1 2 a は、ファンクション・アキュレート・レベル、トランザクション・アキュレート・レベル、サイクル・アキュレート・レベルの各検証レベルに対応したタイミング情報に応じて、バス 1 7 から入力されてくるデータのハードウェアモデル 1 2 b への転送方式を切り替えることができるよう構成されている。

**【 0 0 5 6 】**

すなわち、バスインターフェース 1 2 a は、ファンクション・アキュレート・レベルでは、ハードウェアモデル 1 2 b が演算に必要とする入力データのすべてを転送する。トランザクション・アキュレート・レベルでは、ハードウェアモデル 1 2 b にバスアクセス等のイベントごとに入力データを転送する。サイクル・アキュレート・レベルでは、ハードウェアモデル 1 2 b に 1 クロックごとに入力データを転送する。 30

**【 0 0 5 7 】**

また、バスインターフェース 1 2 a は、タイミング情報に応じて、スタックメモリ 1 2 c からバス 1 7 への出力データの転送方式を切り替えることができるよう構成されている。

**【 0 0 5 8 】**

すなわち、バスインターフェース 1 2 a は、ファンクション・アキュレート・レベルでは、スタックメモリ 1 2 c に格納されているデータをすべてバス 1 7 に転送する。トランザクション・アキュレート・レベルでは、スタックメモリ 1 2 c に格納されているデータをイベントごとにバス 1 7 に転送する。サイクル・アキュレート・レベルでは、スタックメモリ 1 2 c に格納されているデータを 1 クロックごとにバス 1 7 に転送する。 40

**【 0 0 5 9 】**

期待値算出モデル 1 2 にこのようなタイミング情報に基づくデータ転送方式の切り替え機能を備えることにより、R T L モデル 2 a の検証のほか、I S S の種類に依らずにファームウェア 3 の検証を行うことが可能になっている。また、別のソフトウェア検証装置を用いる場合であっても、その種類に依らずにファームウェア 3 の検証が可能になる。

**【 0 0 6 0 】**

また、ハードウェアモデル 1 2 b は、先のハードウェア検証において R T L モデル 2 a と等価なファンクションレベルのモデルであり、例えば A N S I 規格の C 言語等を用いて作成される。ハードウェアモデル 1 2 b では、R T L モデル 2 a の検証あるいはファーム 50

ウェア 3 の検証の際には、バスインターフェース 12a から入力データが転送され、所定の演算処理に必要な入力データがすべて揃ったときに、その演算が実行され、演算結果のデータがスタックメモリ 12c に転送される。スタックメモリ 12c に転送される演算結果のデータが複数のデータの集合からなる場合には、そのデータの集合がスタックメモリ 12c に一気に転送される。

#### 【0061】

ここで、ハードウェアモデル 12b が ANSI 規格に従う C 言語で作成されている場合には、ハードウェア検証の際、テストパターンやシミュレーションに用いられる 4 値 (0, 1, X, Z) のうち X (不定) および Z (ハイインピーダンス) の値はそのままで演算に用いることができない。そのため、このバスインターフェース 12a は、ユーザ定義により、4 値表現の入力データを 0, 1 の 2 値表現に変換してハードウェアモデル 12b に転送するように構成されている。例えば、バスインターフェース 12a は、不定を示す X を 0 または 1 に、ハイインピーダンスを示す Z を 1 または 0 に、それぞれ変換してハードウェアモデル 12b に転送する。

#### 【0062】

ハードウェアモデル 12b では、0, 1 の 2 値で演算が実行され、その演算結果のデータがスタックメモリ 12c に転送される。

また、その場合、バスインターフェース 12a は、バス 17 に転送するデータが、入力データ転送時のデータ幅やビット幅に満たない場合には、4 値表現から 2 値表現に変換されたデータであると認識し、そのデータを、ユーザ定義により、0 または 1 を X または Z に再変換し、4 値表現でデータをバス 17 に出力する。

#### 【0063】

期待値算出モデル 12 に、このような 4 値 / 2 値変換機能を備えることで、ANSI 規格に従う C 言語で作成されハードウェアモデル 12b を、RTL モデル 2a の検証およびファームウェア 3 の検証の双方に容易に用いることが可能になる。

#### 【0064】

また、検証装置 10 は、ハードウェア検証で使用する 4 値表現のモデルを、ソフトウェア検証に使用する 2 値表現に変換する 4 値 / 2 値変換手段を有している。

なお、期待値算出モデル 12 は、その入力データに 0, 1, X, Z の 4 値以外の値 (U, W, L, H など) が含まれている場合でも、同様にして最終的に 0, 1 の 2 値に変換し、ハードウェアモデル 12b による演算を実行した後、再変換して出力するように構成することも可能である。

#### 【0065】

また、この期待値算出モデル 12 においては、演算結果のデータまたはデータの集合がスタックメモリ 12c に格納される際、その演算結果のデータまたはデータの集合にフラグが付加されるようになっている。

#### 【0066】

図 4 はスタックメモリのデータ格納例を示す図である。

期待値算出モデル 12 のスタックメモリ 12c には、ハードウェアモデル 12b による演算結果のデータが一気に転送され、各アドレスに格納される。期待値算出モデル 12 では、このように各アドレスに格納されるデータについて、検証レベルに応じて転送すべきデータ単位に、それぞれ目安となるフラグが定義されている。

#### 【0067】

図 4 に示したデータ格納例の場合、アドレス 0 × 0 ~ 0 × F までのアドレスに格納されるデータについて、検証レベルがファンクション・アキュレート・レベルのときには、アドレス 0 × 0 ~ 0 × 7, 0 × 8 ~ 0 × F のデータの集合にそれぞれ 0, 1 のフラグが付加されている。バスインターフェース 12a では、バス 17 に転送するデータ単位および転送順がこのフラグによって識別され、バス 17 へのデータ転送が制御される。

#### 【0068】

すなわち、バスインターフェース 12a は、検証レベルがファンクション・アキュレート

10

20

30

40

50

・レベルのときには、スタックメモリ 12c からのデータ転送時に、まず、0 のフラグが付加されているアドレス 0 × 0 ~ 0 × 7 のデータの集合を転送し、次いで、1 のフラグが付加されているアドレス 0 × 8 ~ 0 × F のデータの集合を転送する。

#### 【 0 0 6 9 】

また、検証レベルがトランザクション・アキュレート・レベルのときには、0 × 0 ~ 0 × 3, 0 × 4 ~ 0 × 7, 0 × 8 ~ 0 × B, 0 × C ~ 0 × F のデータの集合にそれぞれ 0 ~ 3 のフラグが付加されている。さらにまた、検証レベルがサイクル・アキュレート・レベルのときには、0 × 0 ~ 0 × F の 16 個の各データに 0 ~ 15 のフラグがそれぞれ付加されている。トランザクション・アキュレート・レベル、サイクル・アキュレート・レベルのときもファンクション・アキュレート・レベルのときと同様、バスインターフェース 12a では、バス 17 に転送するデータ単位および転送順がこのフラグによって識別され、バス 17 へのデータ転送が制御される。

#### 【 0 0 7 0 】

このように、検証レベルに応じて、転送するデータ単位にフラグを付加して格納しておくことにより、検証レベルに応じたバス 17 へのデータ転送が可能になる。したがって、この期待値算出モデル 12 では、ソフトウェア検証がファンクション・アキュレート・レベル、トランザクション・アキュレート・レベル、サイクル・アキュレート・レベルのいずれであっても、その検証レベルに応じてバス 17 にデータまたはデータの集合を転送することができる。

#### 【 0 0 7 1 】

従来はソフトウェア検証がファンクション・アキュレート・レベルかトランザクション・アキュレート・レベルかサイクル・アキュレート・レベルかに依って、すなわちソフトウェア検証に用いる ISS に依って、別々にハードウェアモデル (C モデル) を作成し、別々にシミュレーションを行う必要があった。これに対し、上記期待値算出モデル 12 によれば、ひとつのハードウェアモデル (C モデル) で複数の検証レベルあるいはソフトウェア検証装置に対応することができるので、より低コストで効率的にシミュレーションを行うことが可能になる。

#### 【 0 0 7 2 】

以上説明したように、上記検証装置 10 によれば、ハードウェア検証において作成された期待値算出モデル 12 を、ソフトウェア検証に再利用するので、従来のようにソフトウェア検証用にハードウェアモデル (C モデル) を作成することが不要になる。そのため、期待値算出モデル 12 が、RTL モデル 2a と等価である限りは、ソフトウェア検証で生じる不具合の原因はファームウェア 3 にあると考えることができ、ソフトウェア検証の際にハードウェアモデルの検証を行う必要がなくなる。これにより、システム LSI の開発効率を向上させ、高品質なシステム LSI を短期間でかつ低コストで開発・製造することが可能になる。

#### 【 0 0 7 3 】

また、期待値算出モデル 12 をソフトウェア検証に再利用するに当たり、期待値算出モデル 12 をソフトウェア検証の検証レベルに対応したタイミング情報に従ってデータの転送方式を切り替えるようにしたので、検証レベルの異なる複数種の ISS に対応することができる。すなわち、システム LSI に搭載する CPU 等が別のものに替わっても、期待値算出モデル 12 は特別な変更を加えることなく IP として以後も利用していくことができ、非常に汎用性が高い。

#### 【 0 0 7 4 】

また、期待値算出モデル 12 をハードウェア検証とソフトウェア検証の双方に利用できるようにするため、ハードウェアモデル 12b を ANSI 規格の C 言語を用いて作成し、期待値算出モデル 12 に 4 値 / 2 値変換機能を備えたことにより、期待値算出モデル 12 の汎用性がいっそう高まるとともに、ソフトウェア検証への再利用が容易に行えるようになる。

#### 【 0 0 7 5 】

10

20

30

40

50

なお、検証装置10は、ハードウェア検証の際にはタイミング情報を有していない期待値算出モデル12を用い、ソフトウェア検証の際に期待値算出モデル12に複数のタイミング情報を付加し、これを用いるようにすることができる。あるいは、あらかじめ複数のタイミング情報を有する期待値算出モデル12を、ハードウェア検証とソフトウェア検証の双方に用いるようにしてよい。

#### 【0076】

なお、上記の処理機能は、コンピュータによって実現することができる。その場合、検証装置10が有すべき機能の処理内容を記述したプログラムが提供される。そのプログラムをコンピュータで実行することにより、上記処理機能がコンピュータ上で実現される。処理内容を記述したプログラムは、コンピュータで読み取り可能な記録媒体に記録しておくことができる。コンピュータで読み取り可能な記録媒体としては、磁気記録装置、光ディスク、光磁気記録媒体、半導体メモリなどがある。磁気記録装置には、ハードディスク装置(HDD)、フレキシブルディスク(FD)、磁気テープなどがある。光ディスクには、DVD(Digital Versatile Disc)、DVD-RAM(Random Access Memory)、CD-ROM(Compact Disc Read Only Memory)、CD-R(Recordable)/RW(ReWritable)などがある。光磁気記録媒体には、MO(Magneto-Optical disk)などがある。

#### 【0077】

プログラムを流通させる場合には、例えば、そのプログラムが記録されたDVD、CD-ROMなどの可搬型記録媒体が販売される。また、プログラムをサーバコンピュータの記憶装置に格納しておき、ネットワークを介して、サーバコンピュータから他のコンピュータにそのプログラムを転送することもできる。

#### 【0078】

プログラムを実行するコンピュータは、例えば、可搬型記録媒体に記録されたプログラムもしくはサーバコンピュータから転送されたプログラムを、自己の記憶装置に格納する。そして、コンピュータは、自己の記憶装置からプログラムを読み取り、プログラムに従った処理を実行する。なお、コンピュータは、可搬型記録媒体から直接プログラムを読み取り、そのプログラムに従った処理を実行することもできる。また、コンピュータは、サーバコンピュータからプログラムが転送されるごとに、逐次、受け取ったプログラムに従った処理を実行することもできる。

#### 【0079】

(付記1) ハードウェアとハードウェアを制御するソフトウェアとをモデルを用いて検証する検証装置において、

検証時の検証レベルを示す一のタイミング情報と前記一のタイミング情報と異なる他のタイミング情報を有するモデルを、ハードウェア検証とソフトウェア検証の双方に用いることを特徴とする検証装置。

#### 【0080】

(付記2) 前記モデルは、複数の異なる検証レベルに対応する数のタイミング情報を有し、検証時の検証レベルに応じた前記タイミング情報に従って入出力データの転送方式を切り替えることを特徴とする付記1記載の検証装置。

#### 【0081】

(付記3) 前記モデルは、検証時の入出力データを変換するデータ変換手段を有し、検証時に入力されるデータを前記データ変換手段によって変換して演算を実行し、演算後のデータを前記データ変換手段によって再変換して出力することを特徴とする付記1記載の検証装置。

#### 【0082】

(付記4) 前記モデルは、検証時の検証レベルに応じたタイミング情報に従って入出力データを転送するインターフェースと、前記インターフェースから転送されるデータを用いて演算を実行するハードウェアモデルと、前記ハードウェアモデルによって演算され前記インターフェースによって出力されるデータを格納するスタックメモリと、を有することを特徴とする付記1記載の検証装置。

10

20

30

40

50

## 【0083】

(付記5) ハードウェアとハードウェアを制御するソフトウェアとをモデルを用いて検証する検証方法において、

検証時の検証レベルを示す一のタイミング情報と前記一のタイミング情報と異なる他のタイミング情報を有するモデルを、ハードウェア検証とソフトウェア検証の双方に用いることを特徴とする検証方法。

## 【0084】

(付記6) 前記モデルは、複数の異なる検証レベルに対応する数のタイミング情報を有し、検証時の検証レベルに応じた前記タイミング情報に従って入出力データの転送方式を切り替えることを特徴とする付記5記載の検証方法。

10

## 【0085】

(付記7) 前記モデルは、検証時に入力されるデータを変換して演算を実行し、演算後のデータを再変換して出力することを特徴とする付記5記載の検証方法。

(付記8) 前記モデルは、入力されるデータを検証時の検証レベルに応じたタイミング情報に従ってインターフェースによってハードウェアモデルに転送し、前記インターフェースから転送されたデータを用いてハードウェアモデルによって演算を実行し、前記ハードウェアモデルによって演算されたデータをスタックメモリに格納し、前記スタックメモリに格納されたデータを前記検証時の検証レベルに応じたタイミング情報に従って出力することを特徴とする付記5記載の検証方法。

## 【0086】

(付記9) コンピュータを用いて、ハードウェアとハードウェアを制御するソフトウェアとをモデルを用いて検証するためのプログラムにおいて、

20

コンピュータに、

検証時の検証レベルを示す一のタイミング情報と前記一のタイミング情報と異なる他のタイミング情報を有するモデルを用いてハードウェア検証を行い、

前記モデルを用いてソフトウェア検証を行う処理を実行させることを特徴とするプログラム。

## 【0087】

(付記10) 前記コンピュータに、

検証時の検証レベルに応じたタイミング情報に従って前記モデルの入出力データの転送方式を切り替える処理を実行させることを特徴とする付記9記載のプログラム。

30

## 【0088】

(付記11) 前記コンピュータに、

検証時に前記モデルに入力されるデータを変換して演算を実行し、演算後のデータを再変換して出力する処理を実行させることを特徴とする付記9記載のプログラム。

## 【0089】

(付記12) 前記コンピュータに、

前記モデルに入力されるデータを検証時の検証レベルに応じたタイミング情報に従ってインターフェースによってハードウェアモデルに転送し、前記インターフェースから転送されたデータを用いてハードウェアモデルによって演算を実行し、前記ハードウェアモデルによって演算されたデータをスタックメモリに格納し、前記スタックメモリに格納されたデータを前記検証時の検証レベルに応じたタイミング情報に従って出力する処理を実行させることを特徴とする付記9記載のプログラム。

40

## 【0090】

(付記13) ハードウェア検証に使用されるモデルを、ソフトウェア検証を行えるように作成する検証装置において、

前記モデルは、前記ソフトウェア検証に使用されるタイミング情報以外のタイミング情報を有することを特徴とする検証装置。

## 【0091】

(付記14) ハードウェア検証に使用されるモデルを、ソフトウェア検証を行えるよ

50

うに作成する検証装置において、

前記モデルは、前記ソフトウェア検証に使用されるタイミング情報について、複数種別のソフトウェア検証に対応する数有することを特徴とする検証装置。

【0092】

(付記15) ハードウェア検証に使用されるモデルを、ソフトウェア検証を行えるよう 10 うに作成する検証装置において、

前記モデルは、前記ソフトウェア検証に使用されるタイミング情報について、複数のソフトウェア検証装置に対応する数有することを特徴とする検証装置。

【0093】

(付記16) ハードウェア検証に使用されるモデルを、ソフトウェア検証を行えるよう 10 うに作成する検証装置において、

前記ハードウェア検証で使用する4値表現のモデルを、前記ソフトウェア検証に使用する2値表現に変換する4値/2値変換手段を有することを特徴とする検証装置。

【図面の簡単な説明】

【0094】

【図1】本発明の原理説明図である。

【図2】ハードウェアおよびソフトウェアの開発・検証環境の概念図である。

【図3】期待値算出モデルの構成例を示す図である。

【図4】スタックメモリのデータ格納例を示す図である。

【図5】従来のハードウェアおよびソフトウェアの開発・検証環境の概念図である。

20

【符号の説明】

【0095】

1 LSI仕様

2 HDLモデル

2a RTLモデル

3 フームウェア

10 検証装置

11 論理シミュレータ

12 期待値算出モデル

12a, 18 バスインターフェース

30

12b ハードウェアモデル

12c スタックメモリ

13 等価検証部

14 ソフトウェアデバッガ

15 インタフェース部

16 テストパターン

17 バス

19 CPU/MPUブロック

20 メモリブロック

〔 図 1 〕

【 図 2 】

【図3】

【 四 4 】

| アドレス | データ |

|------|-----|

| 0x0  | 80  |

| 0x1  | bb  |

| 0x2  | 7c  |

| 0x3  | bc  |

| 0x4  | 80  |

| 0x5  | bd  |

| 0x6  | 7c  |

| 0x7  | be  |

| 0x8  | 7f  |

| 0x9  | 29  |

| 0xA  | 83  |

| 0xB  | 28  |

| 0xC  | 7a  |

| 0xD  | 32  |

| 0xE  | 82  |

| 0xF  | 3a  |

【図5】