(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4029853号

(P4029853)

(45) 発行日 平成20年1月9日(2008.1.9)

(24) 登録日 平成19年10月26日(2007.10.26)

(51) Int.C1.

F 1

HO 2M 3/28 (2006.01)

HO 2M 3/28

H

請求項の数 2 (全 20 頁)

(21) 出願番号 特願2004-85634 (P2004-85634)

(22) 出願日 平成16年3月23日 (2004.3.23)

(65) 公開番号 特開2005-278263 (P2005-278263A)

(43) 公開日 平成17年10月6日 (2005.10.6)

審査請求日 平成17年8月29日 (2005.8.29)

(73) 特許権者 000106276

サンケン電気株式会社

埼玉県新座市北野3丁目6番3号

(74) 代理人 100082049

弁理士 清水 敬一

(72) 発明者 小池 憲吾

埼玉県新座市北野3丁目6番3号 サンケン電気株式会社内

審査官 櫻田 正紀

最終頁に続く

(54) 【発明の名称】スイッチング電源装置

## (57) 【特許請求の範囲】

## 【請求項 1】

交流電源から入力される交流電圧を直流電圧に変換する入力整流回路を含む直流電源と、1次巻線及び2次巻線並びに駆動巻線を有するトランスと、前記1次巻線を介して前記直流電源に接続されたスイッチング素子と、前記2次巻線に接続され且つ直流出力電圧を発生する整流平滑回路と、前記直流出力電圧が略一定となるように前記スイッチング素子のオン・オフ期間を制御する駆動信号を発生する制御回路とを備えたスイッチング電源装置において、

前記制御回路は、前記スイッチング素子のオン期間中に前記駆動巻線に発生する電圧を検出する入力電圧検出手段と、該入力電圧検出手段の検出電圧が基準電圧を超えたときに出力信号を発生する比較手段と、前記トランスのエネルギー放出後に前記スイッチング素子の両主端子間に印加される電圧の谷部電圧を直接又は間接的に検出する谷部電圧検出手段と、前記比較手段が前記出力信号を発生し且つ前記谷部電圧検出手段が最初の前記谷部電圧を検出したとき、前記スイッチング素子をターンオンさせ、前記比較手段が前記出力信号を発生せず且つ前記谷部電圧検出手段が複数個目の前記谷部電圧を検出したとき、前記スイッチング素子をターンオンさせる導通制御手段とを備え、

前記比較手段は、電圧の上昇に伴って前記出力信号を切り換える際の前記基準電圧と、前記電圧の低下に伴って前記出力信号を切り換える際の前記基準電圧とが互いに異なるヒステリシス特性を有することを特徴とするスイッチング電源装置。

## 【請求項 2】

前記比較手段は、前記入力電圧検出手段の複数の検出電圧と前記基準電圧とをそれぞれ比較して複数の出力信号を発生し、

前記導通制御手段は、前記比較手段から出力された前記複数の出力信号により、前記谷部電圧検出手段にて検出したそれぞれ異なる複数個目の前記谷部電圧で前記スイッチング素子をターンオンさせる請求項1に記載のスイッチング電源装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、広範囲の電源電圧に亘って変換効率の向上が可能なスイッチング電源装置に関する。 10

【背景技術】

【0002】

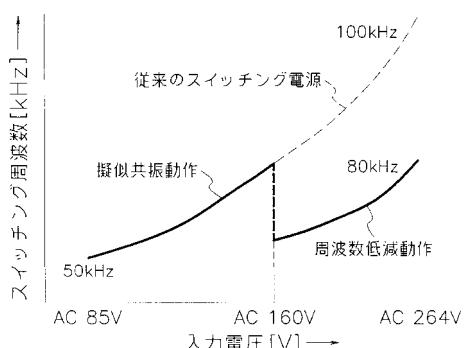

公知の技術である擬似共振（部分電圧共振）方式のフライバック型スイッチング電源装置は、簡素な回路構成で変換効率が高く且つ発生ノイズが少ない長所を有するため、従来から広く使用されている。例えば、下記の特許文献1には、上記の類の擬似共振方式スイッチング電源装置が開示されている。しかし、このスイッチング電源装置では、負荷が一定の状態で商用交流電源からの入力電圧が変動すると、スイッチング素子のスイッチング周波数が変化する問題点があった。例えば、定格出力電力が100[W]で且つ商用交流入力電圧が85～264[V]の全世界の電源電圧に対応可能な上記のスイッチング電源装置を考えた場合、商用交流入力電圧が85[V]のときのスイッチング素子のスイッチング周波数を50[kHz]とすると、商用交流入力電圧が264[V]のときのスイッチング素子のスイッチング周波数は100[kHz]まで増加する。 20

【0003】

【特許文献1】特開2003-61345号公報（第7頁、図2）

【発明の開示】

【発明が解決しようとする課題】

【0004】

ところで、上記のスイッチング電源装置では、トランスの1次巻線に印加される電源電圧の上昇に伴ってスイッチング素子のオン期間が短くなるため、高いレンジ（185～264[V]）の電源電圧が入力された場合、スイッチング素子のスイッチング周波数が増加し、これに伴ってスイッチング回数も増加する。したがって、高いレンジの電源電圧入力において、スイッチング損失が増加し、変換効率が低下する問題点があった。 30

【0005】

一方、下記の特許文献2では、2次側の負荷状態を判定して最小オフ期間を切り換えることにより擬似共振動作と周波数低減動作とを切り換えるDC-DCコンバータが開示されている。このDC-DCコンバータでは、重負荷時に擬似共振動作、軽負荷時に周波数低減動作に切り換えることにより、軽負荷時でのスイッチング素子の単位時間当たりのスイッチング回数の増加を抑え、軽負荷時におけるスイッチング損失の低減を図っている。しかし、高いレンジの電源電圧が入力された場合は、前記と同様の理由によりスイッチング素子のスイッチング周波数が増加するため、スイッチング素子の単位時間当たりのスイッチング回数が増加する。したがって、上記のDC-DCコンバータにおいても、高いレンジの電源電圧入力時にスイッチング損失が増加し、変換効率が低下する問題点があった。また、擬似共振動作から周波数低減動作への移行時又は前記とは逆の移行時にトランスの発振周波数が不連続的に変化するため、トランスに流れる電流のピーク値もトランスの発振周波数にしたがって大きく変化する。そのため、負荷の条件によってはトランスの振動が可聴音となり、トランスから騒音が発生する問題点があった。 40

【0006】

【特許文献2】特開2001-231257号公報（第25頁、図1）

【0007】

そこで、本発明は、広範囲の電源電圧に亘って変換効率を向上すると共に、トランス等 50

からの騒音を抑制できるスイッチング電源装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明によるスイッチング電源装置は、交流電源(1a)から入力される交流電圧を直流電圧に変換する入力整流回路(1c)を含む直流電源(1)と、1次巻線(2a)及び2次巻線(2b)並びに駆動巻線(2c)を有するトランス(2)と、1次巻線(2a)を介して直流電源(1)に接続されたスイッチング素子(3)と、2次巻線(2b)に接続され且つ直流出力電圧( $V_{OUT}$ )を発生する整流平滑回路(6)と、直流出力電圧( $V_{OUT}$ )が略一定となるようにスイッチング素子(3)のオン・オフ期間を制御する駆動信号を発生する制御回路(8)とを備える。制御回路(8)は、スイッチング素子(3)のオン期間中に駆動巻線(2c)に発生する電圧を検出する入力電圧検出手段(31)と、入力電圧検出手段(31)の検出電圧が基準電圧( $V_{RH}$ )を超えたときに出力信号( $V_{CP}$ )を発生する比較手段(41)と、トランス(2)のエネルギー放出後にスイッチング素子(3)の両主端子間に印加される電圧の谷部電圧を直接又は間接的に検出する谷部電圧検出手段(51)と、比較手段(41)が出力信号( $V_{CP}$ )を発生し且つ谷部電圧検出手段(51)が最初の谷部電圧を検出したとき、スイッチング素子(3)をターンオンさせ、前記比較手段(41)が前記出力信号( $V_{CP}$ )を発生せず且つ谷部電圧検出手段(51)が複数個目の谷部電圧を検出したとき、スイッチング素子(3)をターンオンさせる導通制御手段(61)とを備える。比較手段(41)は、電圧の上昇に伴って出力信号を切り換える際の基準電圧( $V_{RL}$ )と、電圧の低下に伴って出力信号を切り換える際の基準電圧( $V_{RL}$ )とが互いに異なるヒステリシス特性を有する。

10

20

【0009】

駆動巻線(2c)に発生する電圧が低いときは、スイッチング素子(3)の両主端子間電圧( $V_{DS}$ )の最初の谷部電圧でスイッチング素子(3)がターンオンするため、トランス(2)のエネルギー放出後にスイッチング素子(3)の両主端子間に印加される電圧( $V_{DS}$ )が谷部電圧となつたときにスイッチング素子(3)をオフ状態からオン状態に切り換える擬似共振動作が行われる。また、駆動巻線(2c)の電圧が高くなり、入力電圧検出手段(31)の検出電圧( $V_{DT}$ )が基準電圧( $V_{R2}$ )を超えると、スイッチング素子(3)の両主端子間電圧( $V_{DS}$ )の複数個目の谷部電圧を谷部電圧検出手段(51)が検出したとき、導通制御手段(61)はスイッチング素子(3)を遅れてターンオンさせるため、スイッチング素子(3)のオフ期間が延長され、スイッチング素子(3)のスイッチング周波数が低下する。したがって、スイッチング素子(3)のスイッチング回数を減少させてスイッチング損失を低減でき、広範囲の電圧に亘ってスイッチング電源装置の変換効率を向上することが可能となる。また、比較手段(41)のヒステリシス動作により、電圧の変動に対してMOS-FET(3)のスイッチング周波数が円滑に制御されるため、広範囲の電圧に亘りスイッチング電源装置を安定に動作させることができる。

30

【発明の効果】

【0010】

本発明によれば、駆動巻線の電圧が高い場合においてスイッチング素子でのスイッチング損失を低減できるので、広範囲の電圧に亘ってスイッチング電源装置の変換効率を向上することが可能となる。したがって、全世界の電源電圧に対応可能で且つ低損失のスイッチング電源装置を容易に得ることができる。また、電圧に依存して擬似共振動作とスイッチング周波数を低下させる動作とに切り換えられるので、実際に使用する場合にはそれらの動作は何れか一方に固定される。このため、擬似共振動作とスイッチング周波数を低下させる動作との切換時にトランス等から発生する騒音を抑制することができる。また、ヒステリシス動作により、広範囲の電圧に亘りスイッチング電源装置を安定に動作させることができる。

40

【発明を実施するための最良の形態】

【0011】

以下、本発明によるスイッチング電源装置の5つの実施形態を図1～図20に基づいて説明する。

50

## 【実施例 1】

## 【0012】

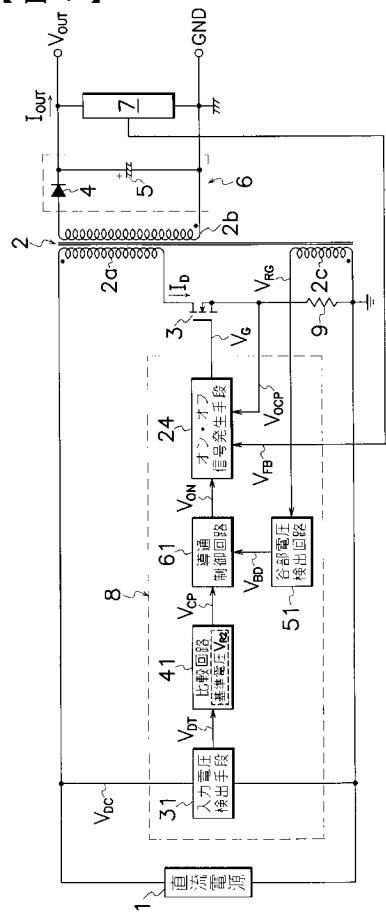

本発明の第1の実施形態を示す実施例1のスイッチング電源装置は、図1に示すように、直流電源(1)と、直流電源(1)に対して直列に接続されたトランス(2)の1次巻線(2a)及びスイッチング素子としてのMOS-FET(MOS型電界効果トランジスタ)(3)と、トランス(2)の2次巻線(2b)に接続された出力整流ダイオード(4)及び出力平滑コンデンサ(5)から成り且つ直流出力電圧 $V_{OUT}$ を発生する出力整流平滑回路(6)と、直流出力電圧 $V_{OUT}$ を検出する出力電圧検出回路(7)と、出力電圧検出回路(7)からの検出信号 $V_{FB}$ に基づいて直流出力電圧 $V_{OUT}$ のレベルが略一定となるようにMOS-FET(3)のオン・オフ期間を制御する駆動信号 $V_G$ を発生するオン・オフ信号発生手段(24)を有する制御回路(8)と、トランス(2)の1次巻線(2a)又はMOS-FET(3)に流れる電流 $I_D$ を電圧として検出し且つその検出信号 $V_{OCP}$ を制御回路(8)に出力する電流検出用抵抗(9)とを備えている。更に、制御回路(8)は、直流電源(1)からの直流入力電圧 $V_{DC}$ を検出する入力電圧検出手段(31)と、入力電圧検出手段(31)の検出電圧 $V_{DT}$ と基準電圧 $V_{R2}$ とを比較して高い電圧(H)レベル又は低い電圧(L)レベルの出力信号 $V_{CP}$ を発生する比較手段としての比較回路(41)と、トランス(2)のエネルギー放出後にMOS-FET(3)のドレイン・ソース端子間に印加されるドレイン・ソース間電圧 $V_{DS}$ と相似なトランス(2)の駆動巻線(2c)に発生するリング電圧 $V_{RG}$ の谷部電圧を検出する谷部電圧検出手段としての谷部電圧検出回路(51)と、比較回路(41)の出力信号 $V_{CP}$ が高い電圧(H)レベルのときは谷部電圧検出回路(51)が最初の谷部電圧を検出したときにMOS-FET(3)をターンオンさせ、比較回路(41)の出力信号 $V_{CP}$ が低い電圧(L)レベルのときは谷部電圧検出回路(51)が2個目の谷部電圧を検出したときにMOS-FET(3)をターンオンさせる出力信号 $V_{ON}$ を発生する導通制御手段としての導通制御回路(61)とを備えている。10 20

## 【0013】

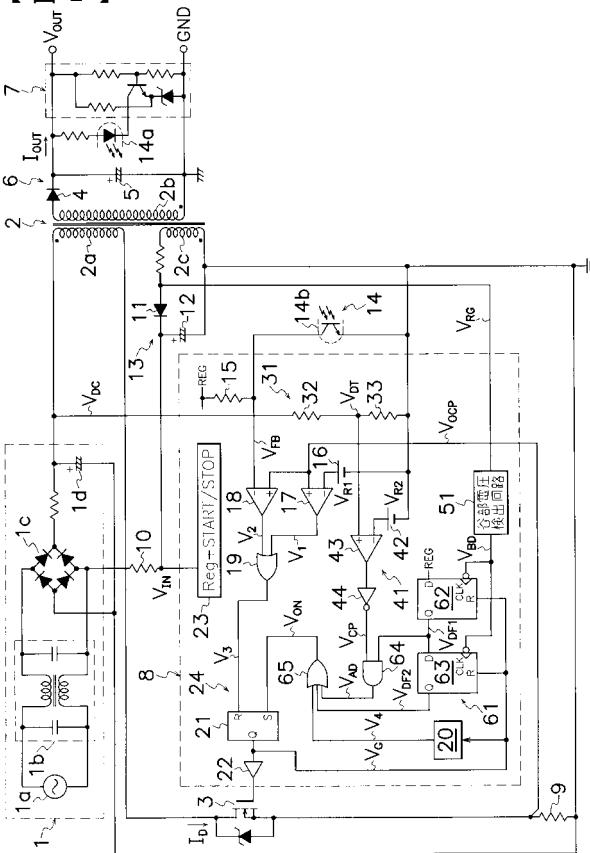

図1のスイッチング電源装置の各回路の詳細を図2に示す。図2に示すように、直流電源(1)は、交流電源(1a)に入力フィルタ回路(1b)を介して接続された整流ブリッジ回路(1c)と、整流ブリッジ回路(1c)の整流出力端子に接続された入力平滑コンデンサ(1d)とで構成される。直流電源(1)を構成する整流ブリッジ回路(1c)には、起動時に制御回路(8)へ駆動用電力を供給する起動抵抗(10)が接続されている。駆動巻線(2c)は、1次巻線(2a)及び2次巻線(2b)と電磁的に結合してトランス(2)を構成する。トランス(2)を構成する駆動巻線(2c)には、整流ダイオード(11)及び駆動用平滑コンデンサ(12)から成り且つ制御回路(8)を駆動する直流電圧 $V_{IN}$ を出力する補助整流平滑回路(13)が接続されている。また、出力電圧検出回路(7)の検出出力は、フォトカプラ(14)を構成する発光素子(14a)及び受光素子(14b)を介してトランス(2)の1次側に伝達され、受光素子(14b)及びブルアップ抵抗(15)の接続点に発生する電圧 $V_{FB}$ が出力電圧検出回路(7)からの検出信号として制御回路(8)を構成するオン・オフ信号発生手段(24)に入力される。30

## 【0014】

オン・オフ信号発生手段(24)は、トランス(2)の1次巻線(2a)又はMOS-FET(3)に流れる最大電流値を規定する基準電圧 $V_{R1}$ を発生する基準電源(16)と、電流検出用抵抗(9)の検出信号 $V_{OCP}$ の電圧レベルが基準電源(16)の基準電圧 $V_{R1}$ のレベルに達したときにMOS-FET(3)をオフ状態にする高い電圧(H)レベルの信号 $V_1$ を出力する過電流制限用コンパレータ(17)と、電流検出用抵抗(9)の検出信号 $V_{OCP}$ の電圧レベルが出力電圧検出回路(7)からの検出信号 $V_{FB}$ の電圧レベルに達したときに高い電圧(H)レベルの信号 $V_2$ を出力する電流モード制御用コンパレータ(18)と、過電流制限用コンパレータ(17)の出力信号 $V_1$ と電流モード制御用コンパレータ(18)の出力信号 $V_2$ との論理和信号 $V_3$ を出力するORゲート(19)と、MOS-FET(3)がオフしてから一定の時間が経過する毎にパルス信号 $V_4$ を出力するパルス発生器(20)と、導通制御回路(61)の出力信号 $V_{ON}$ によりセット状態となり緩衝增幅器(22)を介してMOS-FET(3)のゲート端子に高い電圧(H)レベルの駆動信号 $V_G$ を出力し、ORゲート(19)の論理和信号 $V_3$ によりリセット状態となり緩衝增幅器(22)を介してMOS-FET(3)のゲート端子に低い電圧(L)レベルの駆動信号 $V_G$ を出40 50

力する R-S フリップフロップ(21)と、起動抵抗(10)又は補助整流平滑回路(13)からの直流電圧  $V_{IN}$  が駆動電圧に達したときに制御回路(8)を構成する各素子に駆動用直流電力を供給し且つ直流電圧  $V_{IN}$  が停止電圧まで低下したときに前記の各素子への駆動用直流電力の供給を停止する制御電源回路(23)とから構成される。

【0015】

入力電圧検出手段(31)は、直流電源(1)を構成する出力平滑コンデンサ(1d)と並列に接続された 2 つの分圧抵抗(32,33)から成り、直流電源(1)からの直流入力電圧  $V_{DC}$  を分圧してそれらの分圧点から検出電圧  $V_{DT}$  を出力する。比較回路(41)は、直流入力電圧  $V_{DC}$  に応じてスイッチング制御形態を切り換えるための電圧レベルを規定する基準電圧  $V_{R2}$  を発生する基準電源(42)と、入力電圧検出手段(31)の検出電圧  $V_{DT}$  が基準電源(42)の基準電圧  $V_{R2}$  に達しないときに低い電圧(L)レベルの出力信号を発生し、入力電圧検出手段(31)の検出電圧  $V_{DT}$  が基準電源(42)の基準電圧  $V_{R2}$  を超えたときに高い電圧(H)レベルの出力信号を発生する入力電圧比較用コンパレータ(43)と、入力電圧比較用コンパレータ(43)の出力信号の反転信号を比較信号  $V_{CP}$  として出力する反転器(44)とから構成される。図 2 に示す比較回路(41)は、交流電源(1a)から低いレンジ(85 ~ 135 [V])の交流電圧が入力されたときは、入力電圧検出手段(31)の検出電圧  $V_{DT}$  が基準電源(42)の基準電圧  $V_{R2}$  に達しないため、入力電圧比較用コンパレータ(43)から低い電圧(L)レベルの信号が出力され、反転器(44)から高い電圧(H)レベルの比較信号  $V_{CP}$  (図 7 (D)に図示)として出力される。また、交流電源(1a)から高いレンジ(185 ~ 264 [V])の交流電圧が入力されたときは、入力電圧検出手段(31)の検出電圧  $V_{DT}$  が基準電源(42)の基準電圧  $V_{R2}$  を超えるため、入力電圧比較用コンパレータ(43)から高い電圧(H)レベルの信号が出力され、反転器(44)から低い電圧(L)レベルの比較信号  $V_{CP}$  (図 8 (D)に図示)として出力される。

10 20 20

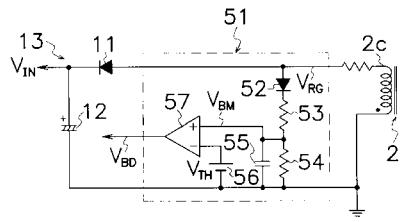

【0016】

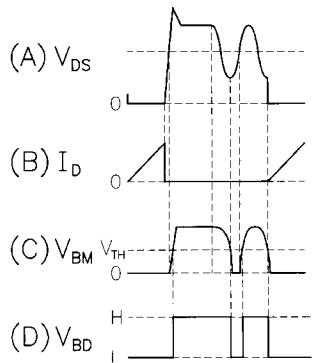

谷部電圧検出回路(51)は、図 3 に示すように、トランス(2)の駆動巻線(2c)の両端に直列に接続されたクリッピングダイオード(52)及び分圧抵抗(53,54)と、一方の分圧抵抗(54)と並列に接続されたコンデンサ(55)と、閾値電圧  $V_{TH}$  を発生する基準電源(56)と、コンデンサ(55)の充電電圧  $V_{BM}$  が基準電源(56)の閾値電圧  $V_{TH}$  より低いときに低い(L)レベルの出力電圧  $V_{BD}$  を発生し、コンデンサ(55)の充電電圧  $V_{BM}$  が基準電源(56)の閾値電圧  $V_{TH}$  のレベルより高いときに高い(H)レベルの出力電圧  $V_{BD}$  を発生するコンパレータ(57)とから構成される。即ち、図 3 に示す谷部電圧検出回路(51)は、MOS-FET(3)のオフ期間中にトランス(2)の駆動巻線(2c)に発生するMOS-FET(3)のドレイン・ソース間電圧  $V_{DS}$  (図 4 (A)に図示)と相似なリング電圧  $V_{RG}$  をクリッピングダイオード(52)、分圧抵抗(53,54)及びコンデンサ(55)により図 4 (C)に示すように波形整形し、図 4 (C)に示すコンデンサ(55)の充電電圧  $V_{BM}$  と基準電源(56)の閾値電圧  $V_{TH}$  をコンパレータ(57)で比較することにより図 4 (D)に示すパルス列電圧  $V_{BD}$  に変換し出力する。このため、図 4 (A) ~ (D)に示すように、コンパレータ(57)から出力されるパルス列電圧  $V_{BD}$  の立ち下がりエッジをMOS-FET(3)のドレイン・ソース間電圧  $V_{DS}$  の谷部電圧として検出することができる。

30

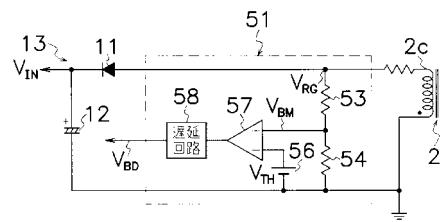

【0017】

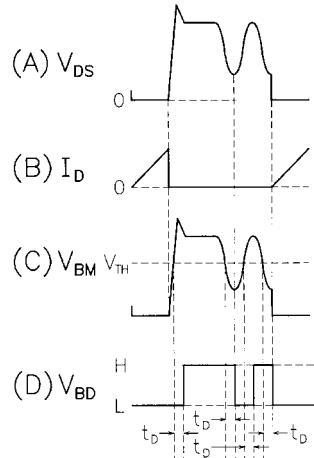

また、谷部電圧検出回路(51)は図 5 に示すように構成することもできる。図 5 に示す谷部電圧検出回路(51)は、トランス(2)の駆動巻線(2c)の両端に接続された分圧抵抗(53,54)と、閾値電圧  $V_{TH}$  を発生する基準電源(56)と、分圧抵抗(53,54)の分圧点の電圧  $V_{BM}$  が基準電源(56)の閾値電圧  $V_{TH}$  のレベルより低いときに低い(L)レベルの出力電圧  $V_{BD}$  を発生し、分圧抵抗(53,54)の分圧点の電圧  $V_{BM}$  が基準電源(56)の閾値電圧  $V_{TH}$  のレベルより高いときに高い(H)レベルの出力電圧  $V_{BD}$  を発生するコンパレータ(57)と、コンパレータ(57)の出力から形成されるパルス列電圧  $V_{BD}$  を一定時間  $t_D$  だけ遅延させる遅延回路(58)とから構成される。即ち、図 5 に示す谷部電圧検出回路(51)は、MOS-FET(3)のオフ期間中にトランス(2)の駆動巻線(2c)に発生するMOS-FET(3)のドレイン・ソース間電圧  $V_{DS}$  (図 6 (A)に図示)と相似なリング電圧  $V_{RG}$  を分圧抵抗(53,54)により分圧し、図 6 (C)に示す分圧抵抗(53,54)の分圧点の電圧  $V_{BM}$  と基準電源(56)の閾値電圧  $V_{TH}$  と

40 50

をコンパレータ(57)で比較することにより図6(D)に示すパルス列電圧 $V_{BD}$ に変換し、コンパレータ(57)からのパルス列電圧 $V_{BD}$ を遅延回路(58)にて一定時間 $t_D$ だけ遅延させることにより、図6(A)～(D)に示すようにコンパレータ(57)から出力されるパルス列電圧 $V_{BD}$ の立ち下がりエッジをMOS-FET(3)のドレイン・ソース間電圧 $V_{DS}$ の谷部電圧に一致させる。これにより、図5に示す谷部電圧検出回路(51)でもコンパレータ(57)から出力されるパルス列電圧 $V_{BD}$ の立ち下がりエッジをMOS-FET(3)のドレイン・ソース間電圧 $V_{DS}$ の谷部電圧として検出することができる。

### 【0018】

導通制御回路(61)は、図2に示すように、R-Sフリップフロップ(21)の出力信号 $V_g$ の立ち上がりによってリセットされるリセット端子(R)を有する第1及び第2のDフリップフロップ(62,63)を有する。谷部電圧検出回路(51)の出力信号 $V_{BD}$ は第1及び第2のDフリップフロップ(62,63)のクロック入力端子(CLK)に入力され、第1のDフリップフロップ(62)の信号入力端子(D)は高い電圧(H)レベル(REG)に保持され、第2のDフリップフロップ(63)の信号入力端子(D)は第1のDフリップフロップ(62)の信号出力端子(Q)に接続され、ORゲート(65)の各入力端子は第2のDフリップフロップ(63)の信号出力端子(Q)とパルス発生器(20)及びANDゲート(64)の各出力端子に接続されている。ANDゲート(64)の一方の入力端子は第1のDフリップフロップ(62)の信号出力端子(Q)に接続され、他方の入力端子は比較回路(41)の反転器(44)に接続されている。ORゲート(65)の出力端子はR-Sフリップフロップ(21)のセット端子(S)に接続されている。クロック入力端子(CLK)に入力される谷部電圧検出回路(51)の出力信号 $V_{BD}$ の最初の立ち下がりエッジに同期して第1のDフリップフロップ(62)の出力信号 $V_{DF1}$ の出力レベルが高い電圧(H)レベルとなる。クロック入力端子(CLK)に入力される谷部電圧検出回路(51)の出力信号 $V_{BD}$ の2個目の立ち下がりエッジに同期して第2のDフリップフロップ(63)の出力信号 $V_{DF2}$ の出力レベルが高い電圧(H)レベルとなる。図2に示す導通制御回路(61)は、交流電源(1a)から低いレンジ(85～135[V])の交流電圧が入力されたときは、比較回路(41)の出力信号 $V_{CP}$ が高い電圧(H)レベルであり、クロック入力端子(CLK)に入力される谷部電圧検出回路(51)の出力信号 $V_{BD}$ の最初の立ち下がりエッジに同期して出力される第1のDフリップフロップ(62)の出力信号 $V_{DF1}$ が高い電圧(H)レベルであるから、ANDゲート(64)の出力信号 $V_{AD}$ は高い電圧(H)レベルとなる。ANDゲート(64)の出力信号 $V_{AD}$ はORゲート(65)を介してR-Sフリップフロップ(21)のセット端子(S)に入力され、緩衝増幅器(22)を介してMOS-FET(3)のゲート端子に付与される駆動信号 $V_g$ が高い電圧(H)レベルとなる。これにより、低いレンジの電源電圧入力時は谷部電圧検出回路(51)が最初の谷部電圧を検出したときにMOS-FET(3)をターンオンさせることができる。また、交流電源(1a)から高いレンジ(185～264[V])の交流電圧が入力されたときは、比較回路(41)の出力信号 $V_{CP}$ が低い電圧(L)レベルであるから、ANDゲート(64)の出力信号 $V_{AD}$ は低い電圧(L)レベルとなり、R-Sフリップフロップ(21)をセット状態にすることはできない。一方、クロック入力端子(CLK)に入力される谷部電圧検出回路(51)の出力信号 $V_{BD}$ の2個目の立ち下がりエッジに同期して第2のDフリップフロップ(63)の出力信号 $V_{DF2}$ の出力レベルが高い電圧(H)レベルとなるため、第2のDフリップフロップ(63)の出力信号 $V_{DF2}$ がORゲート(65)を介してR-Sフリップフロップ(21)のセット端子(S)に入力され、MOS-FET(3)のゲート端子に付与される駆動信号 $V_g$ が高い電圧(H)レベルとなる。これにより、高いレンジの電源電圧入力時は谷部電圧検出回路(51)が2個目の谷部電圧を検出したときにMOS-FET(3)をターンオンさせることができる。

### 【0019】

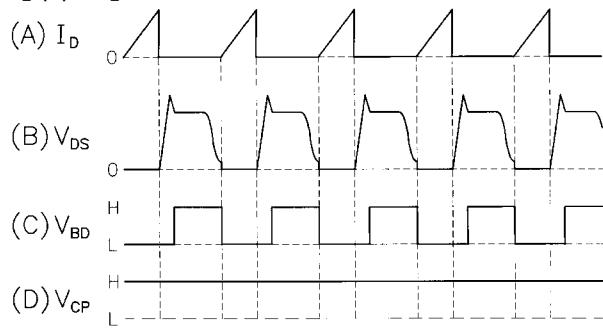

次に、図2に示す実施例1のスイッチング電源の動作について説明する。交流電源(1a)から低いレンジ(85～135[V])の交流電圧が入力されたときは、図7(D)に示すように比較回路(41)の反転器(44)から出力される比較信号 $V_{CP}$ が高い電圧(H)レベルとなる。また、MOS-FET(3)のオフ期間中にドレイン・ソース端子間に印加されていたドレイン・ソース間電圧 $V_{DS}$ が図7(B)に示すようにトランス(2)のフライバックエネルギーの放出完了と同時に降下し始め、ドレイン・ソース間電圧 $V_{DS}$ の谷部電圧近辺で谷部電圧検

10

20

30

40

50

出回路(51)の出力信号  $V_{BD}$  が図 7 (C) に示すように高い電圧 (H) レベルから低い電圧 (L) レベルとなる。これにより、図 7 (C) に示す谷部電圧検出回路(51)の出力信号  $V_{BD}$  の最初の立ち下がりエッジに同期して導通制御回路(61)の第 1 の D フリップフロップ(62)の信号出力端子 (Q) から高い電圧 (H) レベルまで上昇する信号  $V_{DF1}$  が出力される。このため、谷部電圧検出回路(51)の出力信号  $V_{BD}$  の最初の立ち下がりエッジに同期して高い電圧 (H) レベルまで上昇する論理積信号  $V_{AD}$  が AND ゲート (64) から出力される。また、導通制御回路(61)の第 2 の D フリップフロップ(63)の信号出力端子 (Q) からは低い電圧 (L) レベルの信号  $V_{DF2}$  が出力されるため、OR ゲート (65) からは谷部電圧検出回路(51)の出力信号  $V_B$  の最初の立ち下がりエッジに同期して高い電圧 (H) レベルまで上昇する論理和信号  $V_{ON}$  が出力され、R-S フリップフロップ(21)がセット状態となる。これにより、図 7 (C) に示す谷部電圧検出回路(51)の出力信号  $V_{BD}$  の最初の立ち下がりエッジに同期して R-S フリップフロップ(21)から緩衝増幅器(22)を介して MOS-FET (3) のゲート端子に付与される駆動信号  $V_G$  が低い電圧 (L) レベルから高い電圧 (H) レベルに切り換えられ、MOS-FET (3) がターンオンする。これにより、MOS-FET (3) に流れるドレイン電流  $I_D$  が図 7 (A) に示すように直線的に増加する。電流検出用抵抗(9)の検出電圧  $V_{OCP}$  が出力電圧検出回路(7)からの検出信号  $V_{FB}$  の電圧レベルに達すると、電流モード制御用コンパレータ(18)から高い電圧 (H) レベルの信号  $V_2$  が出力され、R-S フリップフロップ(21)がリセット状態となる。これにより、R-S フリップフロップ(21)から緩衝増幅器(22)を介して MOS-FET (3) のゲート端子に付与される駆動信号  $V_G$  が高い電圧 (H) レベルから低い電圧 (L) レベルとなり、MOS-FET (3) がオン状態からオフ状態となる。以上の過程の繰り返しによって、低いレンジの電源電圧入力時は、トランス(2)のフライバックエネルギーの放出が終了して MOS-FET (3) のドレイン・ソース間電圧  $V_{DS}$  が谷部電圧に達すると同時に MOS-FET (3) がターンオンする擬似共振動作が行われる。

#### 【0020】

また、交流電源(1a)から高いレンジ (185 ~ 264 [V]) の交流電圧が入力されたときは、MOS-FET (3) のオフ期間中にドレイン・ソース端子間に印加されていたドレイン・ソース間電圧  $V_{DS}$  が図 8 (B) に示すようにトランス(2)のフライバックエネルギーの放出完了と同時に降下し始め、ドレイン・ソース間電圧  $V_{DS}$  の谷部電圧近辺で谷部電圧検出回路(51)の出力信号  $V_{BD}$  が図 8 (C) に示すように高い電圧 (H) レベルから低い電圧 (L) レベルとなる。また、比較回路(41)の反転器(44)から出力される比較信号  $V_{CP}$  は図 8 (D) に示すように低い電圧 (L) レベルとなるため、谷部電圧検出回路(51)の出力信号  $V_{BD}$  の最初の立ち下がりエッジに同期して導通制御回路(61)の第 1 の D フリップフロップ(62)の信号出力端子 (Q) から出力される高い電圧 (H) レベルまで上昇する信号  $V_{DF1}$  は AND ゲート (64) により阻止される。このため、AND ゲート (64) からは低い電圧 (L) レベルの論理積信号  $V_{AD}$  が出力され、OR ゲート (65) に入力される。一方、導通制御回路(61)の第 2 の D フリップフロップ(63)の信号出力端子 (Q) からは、図 8 (C) に示す谷部電圧検出回路(51)の出力信号  $V_{BD}$  の 2 個目の立ち下がりエッジに同期して高い電圧 (H) レベルまで上昇する信号  $V_{DF2}$  が出力され、OR ゲート (65) に入力される。このため、OR ゲート (65) からは谷部電圧検出回路(51)の出力信号  $V_{BD}$  の 2 個目の立ち下がりエッジに同期して高い電圧 (H) レベルまで上昇する論理和信号  $V_{ON}$  が出力され、R-S フリップフロップ(21)がセット状態となる。これにより、図 8 (C) に示す谷部電圧検出回路(51)の出力信号  $V_{BD}$  の 2 個目の立ち下がりエッジに同期して R-S フリップフロップ(21)から緩衝増幅器(22)を介して MOS-FET (3) のゲート端子に付与される駆動信号  $V_G$  が低い電圧 (L) レベルから高い電圧 (H) レベルに切り換えられ、MOS-FET (3) がターンオンする。これにより、MOS-FET (3) に流れるドレイン電流  $I_D$  が図 8 (A) に示すように直線的に増加する。電流検出用抵抗(9)の検出電圧  $V_{OCP}$  が出力電圧検出回路(7)からの検出信号  $V_{FB}$  の電圧レベルに達すると、電流モード制御用コンパレータ(18)から高い電圧 (H) レベルの信号  $V_2$  が出力され、R-S フリップフロップ(23)がリセット状態となる。これにより、R-S フリップフロップ(23)から緩衝増幅器(22)を介して MOS-FET (3) のゲート端子に付与される駆動信号  $V_G$  が高い電圧 (H) レベルから低い電圧 (L) レベルに切り換えられ、MOS-FET (3)

)がオン状態からオフ状態となる。したがって、高いレンジの電源電圧入力時は、MOS-FET(3)のオフ期間中に発生するドレイン・ソース間電圧 $V_{DS}$ の2個目の谷部電圧でMOS-FET(3)がターンオンするため、MOS-FET(3)のオフ期間が延長され、MOS-FET(3)のスイッチング周波数が低下する周波数低減動作となる。

#### 【0021】

図2に示すスイッチング電源装置の交流電源(1a)の交流入力電圧に対するMOS-FET(3)のスイッチング周波数特性を図9に示す。交流電源(1a)の交流入力電圧が85Vから例えれば160Vまでの低いレンジの領域では擬似共振動作が行われ、交流入力電圧の上昇に伴ってMOS-FET(3)のスイッチング周波数が50kHzから指數関数的に増加する。交流電源(1a)の交流入力電圧が160Vに達すると、擬似共振動作から周波数低減動作に移行し、MOS-FET(3)のスイッチング周波数が急激に減少する。交流電源(1a)の交流入力電圧が160Vから264Vまでの高いレンジの領域に達すると、周波数低減動作により交流入力電圧の上昇に伴ってMOS-FET(3)のスイッチング周波数が80kHz程度まで指數関数的に増加する。したがって、交流電源(1a)の交流入力電圧が85Vから264Vまでの範囲において、従来のスイッチング電源装置のスイッチング周波数が破線部に示すように50kHzから100kHzまで指數関数的に上昇するのに対し、図2に示す実施例1のスイッチング電源装置では、交流電源(1a)の交流入力電圧が例えば160Vに達した時点で擬似共振動作から周波数低減動作に移行することにより、スイッチング電源装置のスイッチング周波数の上昇幅を50kHzから80kHzまでの範囲に抑えることができる。

#### 【0022】

実施例1では、交流電源(1a)から低いレンジ(85~135[V])の交流電圧が入力されたとき、MOS-FET(3)のドレイン・ソース間電圧 $V_{DS}$ の最初の谷部電圧でMOS-FET(3)がターンオンするため、トランス(2)のエネルギー放出後にMOS-FET(3)のドレイン・ソース端子間に印加される電圧 $V_{DS}$ が谷部電圧になると同時にMOS-FET(3)をオフ状態からオン状態に切り換える擬似共振動作が行われる。また、交流電源(1a)から高いレンジ(185~264[V])の交流電圧が入力されたときは、入力電圧検出手段(31)の検出電圧 $V_{DT}$ が基準電圧 $V_{R2}$ を超え、且つMOS-FET(3)のドレイン・ソース間電圧 $V_{DS}$ の2個目の谷部電圧を谷部電圧検出回路(51)にて検出したときに、導通制御回路(61)によりMOS-FET(3)が遅れてターンオンするので、MOS-FET(3)のオフ期間が延長され、MOS-FET(3)のスイッチング周波数が低下する。したがって、MOS-FET(3)のスイッチング回数を減少させてスイッチング損失を低減できるので、広範囲の電源電圧に亘ってスイッチング電源装置の変換効率を向上することが可能となる。また、直流電源(1)からの直流入力電圧 $V_{DC}$ に依存して擬似共振動作とMOS-FET(3)のスイッチング周波数を低下させる動作とに切り換えられるので、実際に使用する場合にはそれらの動作は何れか一方に固定される。このため、MOS-FET(3)のスイッチング制御形態を切り換える際にトランス(2)等から発生する騒音を抑制することができる。

#### 【実施例2】

#### 【0023】

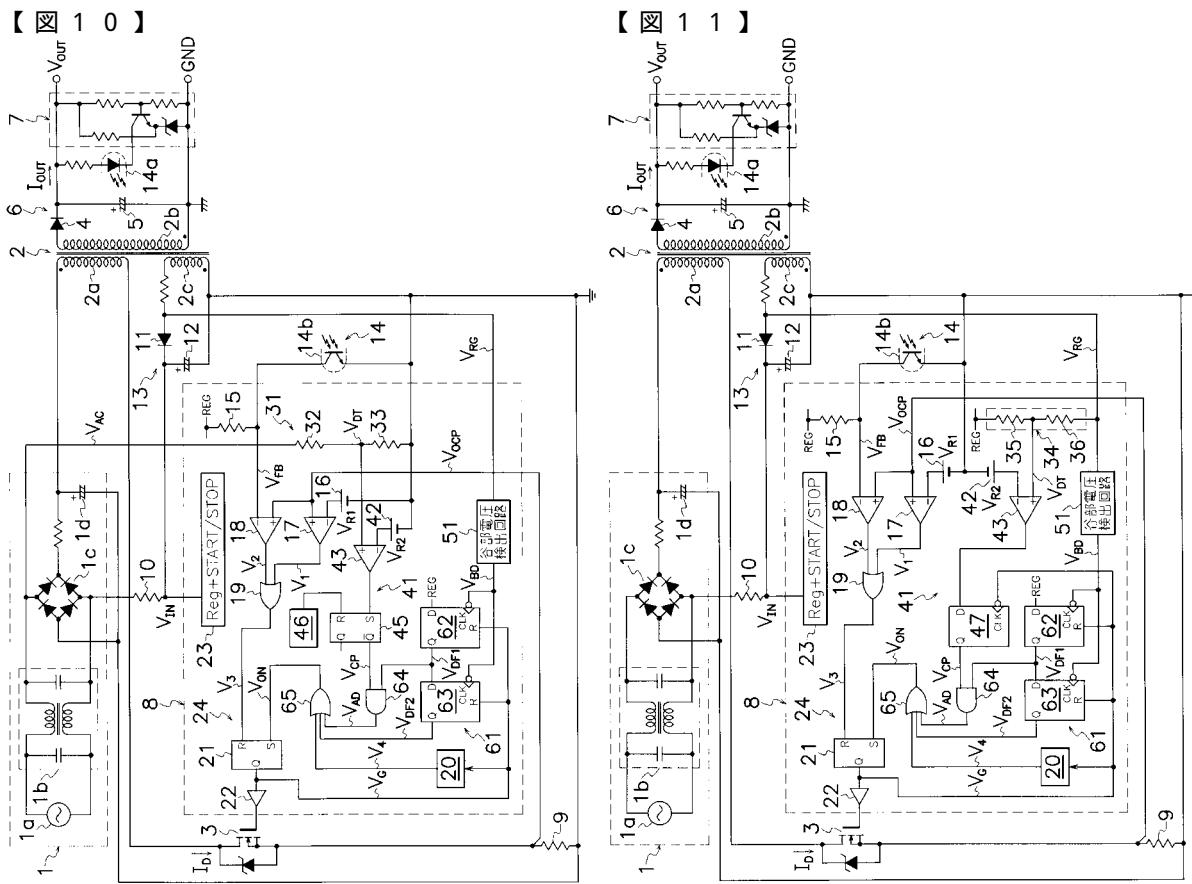

図2に示す実施例1は変更が可能である。例えば、本発明の第2の実施形態を示す実施例2のスイッチング電源装置は、図10に示すように、図2に示す入力電圧検出手段(31)を構成する2つの分圧抵抗(32,33)を入力フィルタ回路(1b)の出力端子と1次側接地端子との間に接続し、図2に示す比較回路(41)を構成する反転器(44)をR-Sフリップフロップ(45)及びワンショットパルス発生器(46)に変更したものである。図10に示す入力電圧検出手段(31)は、交流電源(1a)から入力フィルタ回路(1b)を介して出力される交流入力電圧 $V_{AC}$ を2つの分圧抵抗(32,33)により分圧してそれらの分圧点から検出電圧 $V_{DT}$ を出力する。R-Sフリップフロップ(45)は、比較回路(41)を構成する入力電圧比較用コンパレータ(43)から出力される高い電圧(H)レベルの出力信号によりセット状態となり、スイッチング電源装置の起動時にワンショットパルス発生器(46)から出力される単発のパルス信号によりリセット状態となる。その他の構成は、図2に示す実施例1のスイッチング電源装置と略同様である。

10

20

30

40

50

## 【0024】

図10に示す実施例2のスイッチング電源装置では、交流電源(1a)から低いレンジ(85~135[V])の交流電圧が入力されたときは、入力電圧検出手段(31)を構成する分圧抵抗(32,33)の分圧点に発生する検出電圧 $V_{DT}$ のピーク値が比較回路(41)を構成する基準電源(42)の基準電圧 $V_{R2}$ を超えないため、入力電圧比較用コンパレータ(43)から低い電圧(L)レベルの出力信号が発生し、R-Sフリップフロップ(45)のセット端子(S)に付与される。一方、R-Sフリップフロップ(45)のリセット端子(R)には、装置起動時にワンショットパルス発生器(46)から単発のパルス信号が既に付与されているため、R-Sフリップフロップ(45)はリセット状態を保持し、反転出力端子から高い電圧(H)レベルの比較信号 $V_{CP}$ が出力される。これ以降は、図2に示す実施例1の回路と略同様の動作が行われ、トランジス(2)のライバックエネルギーの放出が終了してMOS-FET(3)のドレイン・ソース間電圧 $V_{DS}$ が谷部電圧に達すると同時にMOS-FET(3)がターンオンする擬似共振動作が行われる。10

## 【0025】

また、交流電源(1a)から高いレンジ(185~264[V])の交流電圧が入力されたときは、入力電圧検出手段(31)を構成する分圧抵抗(32,33)の分圧点に発生する検出電圧 $V_{DT}$ のピーク値が比較回路(41)を構成する基準電源(42)の基準電圧 $V_{R2}$ を超えるため、入力電圧比較用コンパレータ(43)から高い電圧(H)レベルの出力信号が発生し、R-Sフリップフロップ(45)のセット端子(S)に付与される。これにより、R-Sフリップフロップ(45)がセット状態となり、反転出力端子から低い電圧(L)レベルの比較信号 $V_{CP}$ が出力される。R-Sフリップフロップ(45)は、ワンショットパルス発生器(46)からリセット端子(R)に単発のパルス信号が再度入力されるまでセット状態を保持する。これ以降は、図2に示す実施例1の回路と略同様の動作が行われ、MOS-FET(3)のオフ期間中に発生するドレイン・ソース間電圧 $V_{DS}$ の2個目の谷部電圧でMOS-FET(3)がターンオンするため、MOS-FET(3)のオフ期間が延長され、MOS-FET(3)のスイッチング周波数が低下する周波数低減動作となる。20

## 【0026】

実施例2では、交流電源(1a)から入力フィルタ回路(1b)を介して出力される交流入力電圧 $V_{AC}$ を入力電圧検出手段(31)にて検出し、その検出電圧 $V_{DT}$ のピーク値を比較回路(41)にて基準電圧 $V_{R2}$ と比較し、その比較出力信号の電圧レベルをR-Sフリップフロップ(45)にて保持するため、入力電圧検出手段(31)での電力損失を最小限に抑えることができる。したがって、広範囲の電源電圧に亘ってスイッチング電源装置の変換効率を更に向上することが可能となる。なお、交流入力電圧 $V_{AC}$ の検出電圧 $V_{DT}$ のピーク値を比較回路(41)にて比較する代わりに、交流入力電圧 $V_{AC}$ の検出電圧 $V_{DT}$ の平均値又は実効値を比較回路(41)にて比較しても同様の作用効果が得られる。30

## 【実施例3】

## 【0027】

本発明の第3の実施形態を示す実施例3のスイッチング電源装置は、図11に示すように、MOS-FET(3)のオン期間中にトランス(2)の駆動巻線(2c)に発生する電圧 $V_{RG}$ を検出する入力電圧検出手段としてのレベルシフト回路(34)を設け、図2に示す比較回路(41)を構成する反転器(44)をDフリップフロップ(47)に変更したものである。レベルシフト回路(34)は、制御電源回路(23)の出力端子とトランス(2)の駆動巻線(2c)に接続された補助整流平滑回路(13)を構成する整流ダイオード(11)のアノード端子との間に接続された2つのレベルシフト用抵抗(35,36)から成り、MOS-FET(3)のオン期間中にトランス(2)の駆動巻線(2c)に発生する負極性の電圧 $V_{RG}$ を正方向にレベルシフトしたトランス(2)の駆動巻線(2c)の検出電圧 $V_{DT}$ を2つのレベルシフト用抵抗(35,36)の接続点から出力する。Dフリップフロップ(47)は、信号入力端子(D)に入力される入力電圧比較用コンパレータ(43)の出力信号をクロック入力端子(CLK)に入力されるR-Sフリップフロップ(21)の出力信号 $V_G$ の立ち下がりエッジに同期する比較信号 $V_{CP}$ として信号出力端子(Q)から出力する。その他の構成は、図2に示す実施例1のスイッチング電源装置と略同様である。40

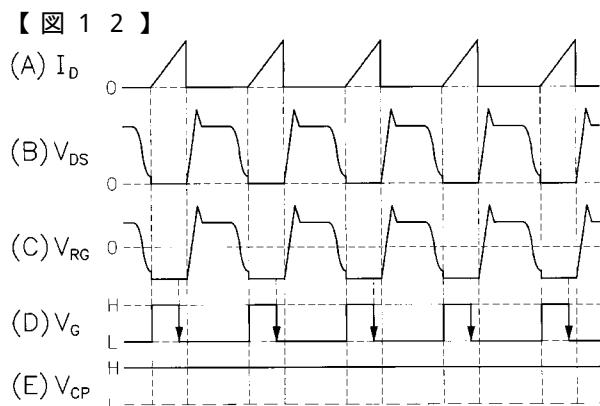

## 【0028】

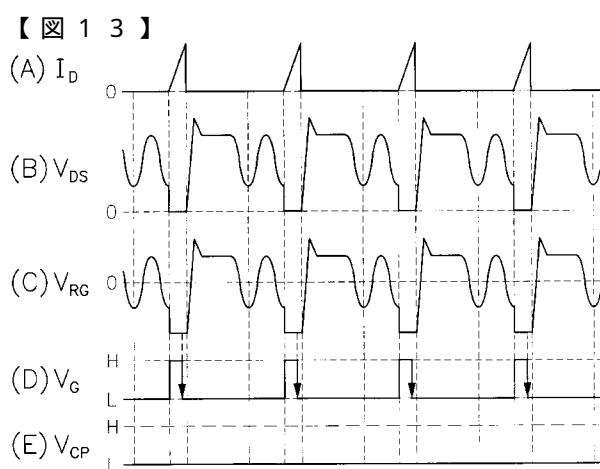

図11に示す実施例3のスイッチング電源装置では、MOS-FET(3)のオン期間中は、MOS-FET(3)に流れるドレイン電流 $I_D$ が図12(A)に示すように直線的に増加すると共に、MOS-FET(3)のドレイン・ソース端子間に印加されるドレイン・ソース間電圧 $V_{DS}$ が図12(B)に示すように略0Vとなる。このとき、図12(C)に示すように、図12(B)に示すMOS-FET(3)のドレイン・ソース間電圧 $V_{DS}$ と略相似な負極性の電圧 $V_{RG}$ がトランス(2)の駆動巻線(2c)に発生する。ここで、交流電源(1a)から低いレンジ(85~135[V])の交流電圧が入力されたときは、MOS-FET(3)のオン期間中にトランス(2)の駆動巻線(2c)に発生する負極性の電圧 $V_{RG}$ が図12(C)に示すように高くなる。このため、レベルシフト回路(34)を構成する2つのレベルシフト用抵抗(35,36)の接続点から出力されるトランス(2)の駆動巻線(2c)の検出電圧 $V_{DT}$ が比較回路(41)内の基準電源(42)の基準電圧 $V_{R2}$ を超え、比較回路(41)内の入力電圧比較用コンパレータ(43)から高い電圧(H)レベルの出力信号が発生する。これにより、図12(D)に示すR-Sフリップフロップ(21)の出力信号 $V_G$ の立ち下がりエッジに同期してDフリップフロップ(47)の信号出力端子(Q)から図12(E)に示すように高い電圧(H)レベルの比較信号 $V_{CP}$ が出力される。これ以降は、図2に示す実施例1の回路と略同様の動作が行われる。したがって、低いレンジの電源電圧入力時は、トランス(2)のライバックエネルギーの放出が終了して図12(B)に示すようにMOS-FET(3)のドレイン・ソース間電圧 $V_{DS}$ が谷部電圧に達すると同時にMOS-FET(3)がターンオンする擬似共振動作が行われる。

## 【0029】

また、交流電源(1a)から高いレンジ(185~264[V])の交流電圧が入力されたときは、MOS-FET(3)のオン期間中にトランス(2)の駆動巻線(2c)に発生する負極性の電圧 $V_{RG}$ が図13(C)に示すように低くなる。このため、レベルシフト回路(34)を構成する2つのレベルシフト用抵抗(35,36)の接続点から出力されるトランス(2)の駆動巻線(2c)の検出電圧 $V_{DT}$ が比較回路(41)内の基準電源(42)の基準電圧 $V_{R2}$ 以下となり、比較回路(41)内の入力電圧比較用コンパレータ(43)から低い電圧(L)レベルの出力信号が発生する。これにより、図13(D)に示すR-Sフリップフロップ(21)の出力信号 $V_G$ の立ち下がりエッジに同期してDフリップフロップ(47)の信号出力端子(Q)から図13(E)に示すように低い電圧(L)レベルの比較信号 $V_{CP}$ が出力される。これ以降は、図2に示す実施例1の回路と略同様の動作が行われる。したがって、高いレンジの電源電圧入力時は、図13(B)に示すようにMOS-FET(3)のオフ期間中に発生するドレイン・ソース間電圧 $V_{DS}$ の2個目の谷部電圧でMOS-FET(3)がターンオンするため、MOS-FET(3)のオフ期間が延長され、MOS-FET(3)のスイッチング周波数が低下する周波数低減動作となる。

## 【0030】

実施例3では、MOS-FET(3)のオン期間中にトランス(2)の駆動巻線(2c)に発生する電圧 $V_{RG}$ が交流電源(1a)から入力される交流電圧に比例するため、レベルシフト回路(34)にてトランス(2)の駆動巻線(2c)の電圧 $V_{RG}$ を検出することにより、交流電源(1a)から入力される交流電圧に応じてMOS-FET(3)のスイッチング周波数を最適な周波数に制御することができる。また、R-Sフリップフロップ(21)の出力信号 $V_G$ の立ち下がりエッジは、MOS-FET(3)のオン・オフ動作の遅れにより、MOS-FET(3)のターンオフより50~500[ns]程度早くなるので、R-Sフリップフロップ(21)の出力信号 $V_G$ の立ち下がりエッジに同期してトランス(2)の駆動巻線(2c)の電圧 $V_{RG}$ を検出することにより、MOS-FET(3)のターンオンやターンオフ時に発生するスイッチングノイズによる比較回路(41)の誤動作を回避することができる。

## 【実施例4】

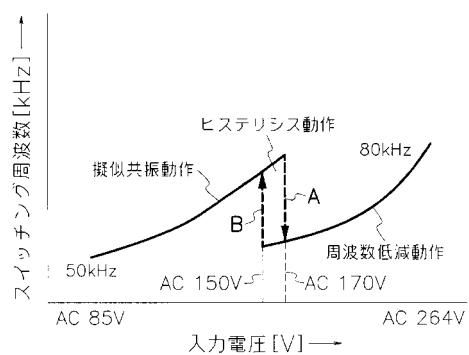

## 【0031】

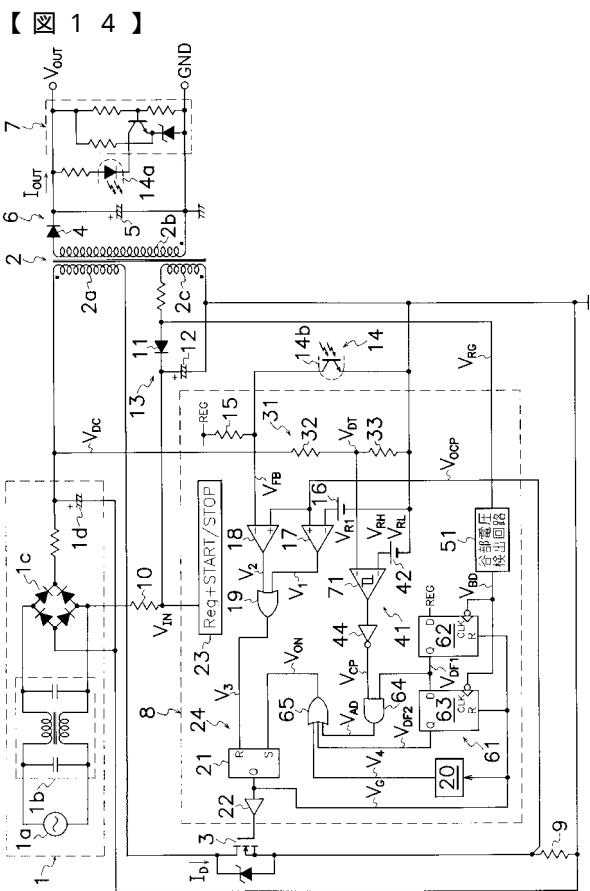

本発明の第4の実施形態を示す実施例4のスイッチング電源装置は、図14に示すように、図2に示す入力電圧比較用コンパレータ(43)をヒステリシスコンパレータ(71)に変更したものである。ヒステリシスコンパレータ(71)は、出力する信号の電圧レベルを低い電圧(L)レベルから高い電圧(H)レベルに切り換える際の基準電圧と、出力する信号の電圧

10

20

30

40

50

レベルを高い電圧(H)レベルから低い電圧(L)レベルに切り換える際の基準電圧とが互いに異なるヒステリシス特性を有する。即ち、ヒステリシスコンパレータ(71)の出力信号が低い電圧(L)レベルから高い電圧(H)レベルに切り換わるときの基準電源(42)の基準電圧を例えば $V_{RH}$ とすると、ヒステリシスコンパレータ(71)の出力信号が高い電圧(H)レベルから低い電圧(L)レベルに切り換わるときの基準電源(42)の基準電圧は $V_{RH}$ よりも低い $V_{RL}$ となる。図14に示す回路では、 $V_{RH}$ は入力電圧検出手段(31)が交流電源(1a)からの170Vの交流電圧を検出したときの検出電圧 $V_{DT}$ に略等しく、 $V_{RL}$ は入力電圧検出手段(31)が交流電源(1a)からの150Vの交流電圧を検出したときの検出電圧 $V_{DT}$ に略等しい。その他の構成は、図2に示す実施例1のスイッチング電源装置と略同様である。

## 【0032】

10

図14に示す実施例4のスイッチング電源装置は、交流電源(1a)の交流入力電圧が85Vから170Vまで上昇する場合、ヒステリシスコンパレータ(71)の出力信号が低い電圧(L)レベルとなり、比較回路(41)の出力信号 $V_{CP}$ が高い電圧(H)レベルとなるため、擬似共振動作が行われ、図15に示すように交流入力電圧の上昇に伴ってMOS-FET(3)のスイッチング周波数が50kHzから指数関数的に増加する。交流電源(1a)の交流入力電圧が170Vに達すると、ヒステリシスコンパレータ(71)の出力信号が低い電圧(L)レベルから高い電圧(H)レベルとなるため、擬似共振動作から周波数低減動作に移行し、図15の破線部Aに示すようにMOS-FET(3)のスイッチング周波数が急激に減少する。更に、交流電源(1a)の交流入力電圧が170Vから264Vまで上昇すると、図15に示すように周波数低減動作により交流入力電圧の上昇に伴ってMOS-FET(3)のスイッチング周波数が80kHz程度まで指数関数的に増加する。また、交流電源(1a)の交流入力電圧が264Vから低下して150Vに達すると、ヒステリシスコンパレータ(71)の出力信号が高い電圧(H)レベルから低い電圧(L)レベルとなり、周波数低減動作から擬似共振動作に移行するため、図15の破線部Bに示すようにMOS-FET(3)のスイッチング周波数が急激に増加する。交流電源(1a)の交流入力電圧が150Vから更に低下すると、擬似共振動作により交流入力電圧の低下に伴ってMOS-FET(3)のスイッチング周波数が指数関数的に減少して行く。

20

## 【0033】

実施例4では、交流電源(1a)の交流入力電圧が150Vと170Vとの間におけるヒステリシス動作により、電源電圧の変動に対してMOS-FET(3)のスイッチング周波数が円滑に制御されるため、広範囲の電源電圧に亘りスイッチング電源装置を安定に動作させることができる。

30

## 【実施例5】

## 【0034】

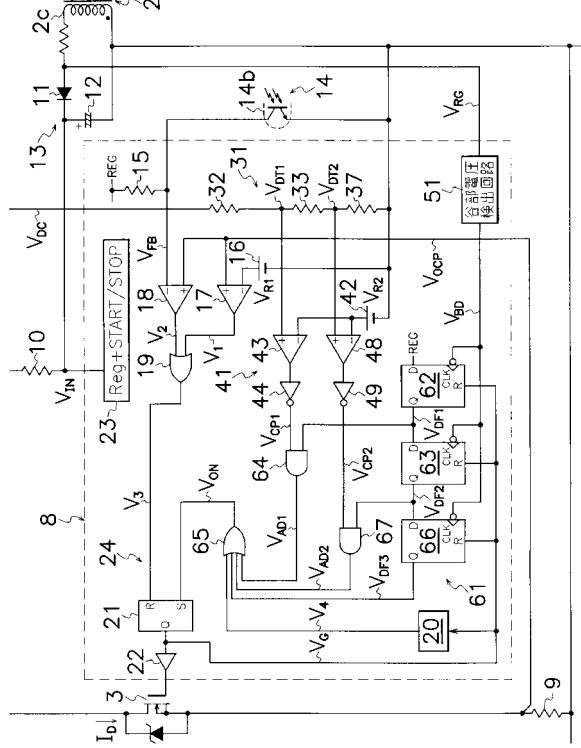

本発明の第5の実施形態を示す実施例5のスイッチング電源装置の制御回路(8)は、図16に示すように、図2に示す分圧抵抗(33)と1次側接地端子との間に別の分圧抵抗(37)を接続し、分圧抵抗(32,33)間の第1の分圧点及び分圧抵抗(33,37)間の第2の分圧点からそれぞれ第1及び第2の検出電圧 $V_{DT1}$ ,  $V_{DT2}$ を発生する入力電圧検出手段(31)を構成し、図2に示す第1の入力電圧比較用コンパレータ(43)及び第1の反転器(44)と並行して第2の入力電圧比較用コンパレータ(48)及び第2の反転器(49)とを設けて第1及び第2の比較信号 $V_{CP1}$ ,  $V_{CP2}$ を出力する比較回路(41)を構成し、図2に示す第1及び第2のDフリップフロップ(62,63)と直列に第3のDフリップフロップ(66)を接続すると共に第2のDフリップフロップ(63)の出力信号 $V_{DF2}$ と第2の反転器(49)の出力信号 $V_{CP2}$ との論理積信号 $V_{AD2}$ を出力する第2のANDゲート(67)を追加して導通制御回路(61)を構成したものである。その他の構成は、図2に示す実施例1のスイッチング電源装置と略同様である。

40

## 【0035】

図16に示す制御回路(8)を有する実施例5のスイッチング電源装置の動作は以下の通りである。交流電源(1a)から低いレンジ(85~135[V])の交流電圧が入力されたときは、入力電圧検出手段(31)を構成する分圧抵抗(32,33)間の第1の分圧点に発生する第1の検出電圧 $V_{DT1}$ と、分圧抵抗(33,37)間の第2の分圧点に発生する第2の検出電圧 $V_{DT2}$

50

<sub>2</sub>が共に基準電源(42)の基準電圧 $V_{R2}$ を超えないため、比較回路(41)を構成する第1及び第2の入力電圧比較用コンパレータ(43,48)からそれぞれ第1及び第2の反転器(44,49)を介して出力される第1及び第2の比較信号 $V_{CP1}, V_{CP2}$ が図17(D)及び(E)に示すように共に高い電圧(H)レベルとなる。また、MOS-FET(3)のオフ期間中にドレイン・ソース端子間に印加されていたドレイン・ソース間電圧 $V_{DS}$ が図17(B)に示すようにトランス(2)のフライバックエネルギーの放出完了と同時に降下し始め、ドレイン・ソース間電圧 $V_{DS}$ の谷部電圧近辺で谷部電圧検出回路(51)の出力信号 $V_{BD}$ が図17(C)に示すように高い電圧(H)レベルから低い電圧(L)レベルとなる。これにより、図17(C)に示す谷部電圧検出回路(51)の出力信号 $V_{BD}$ の最初の立ち下がりエッジに同期して導通制御回路(61)の第1のDフリップフロップ(62)の信号出力端子(Q)から高い電圧(H)レベルまで上昇する信号 $V_{DF1}$ が出力される。このため、谷部電圧検出回路(51)の出力信号 $V_{BD}$ の最初の立ち下がりエッジに同期して高い電圧(H)レベルまで上昇する第1の論理積信号 $V_{AD1}$ が第1のANDゲート(64)から出力される。また、導通制御回路(61)の第2及び第3のDフリップフロップ(63,66)の各信号出力端子(Q)からは低い電圧(L)レベルの信号 $V_{DF2}, V_{DF3}$ が出力され、第2のANDゲート(67)から出力される第2の論理積信号 $V_{AD2}$ が低い電圧(L)レベルとなるため、ORゲート(65)からは谷部電圧検出回路(51)の出力信号 $V_{BD}$ の最初の立ち下がりエッジに同期して高い電圧(H)レベルまで上昇する論理和信号 $V_{ON}$ が出力され、R-Sフリップフロップ(21)がセット状態となる。これにより、図17(C)に示す谷部電圧検出回路(51)の出力信号 $V_{BD}$ の最初の立ち下がりエッジに同期してR-Sフリップフロップ(21)から緩衝増幅器(22)を介してMOS-FET(3)のゲート端子に付与される駆動信号 $V_G$ が低い電圧(L)レベルから高い電圧(H)レベルに切り換えられ、MOS-FET(3)がターンオンする。これにより、MOS-FET(3)に流れるドレイン電流 $I_D$ が図17(A)に示すように直線的に増加する。電流検出用抵抗(9)の検出電圧 $V_{OCP}$ が出力電圧検出回路(7)からの検出信号 $V_{FB}$ の電圧レベルに達すると、電流モード制御用コンパレータ(18)から高い電圧(H)レベルの信号 $V_2$ が出力され、R-Sフリップフロップ(21)がリセット状態となる。これにより、R-Sフリップフロップ(21)から緩衝増幅器(22)を介してMOS-FET(3)のゲート端子に付与される駆動信号 $V_G$ が高い電圧(H)レベルから低い電圧(L)レベルとなり、MOS-FET(3)がオン状態からオフ状態となる。以上の過程の繰り返しによって、低いレンジの電源電圧入力時は、トランス(2)のフライバックエネルギーの放出が終了してMOS-FET(3)のドレイン・ソース間電圧 $V_{DS}$ が谷部電圧に達すると同時にMOS-FET(3)がターンオンする擬似共振動作が行われる。

### 【0036】

また、交流電源(1a)から中間レンジ(165~200[V])の交流電圧が入力されたときは、入力電圧検出手段(31)を構成する分圧抵抗(32,33)間の第1の分圧点に発生する第1の検出電圧 $V_{DT1}$ が基準電源(42)の基準電圧 $V_{R2}$ を超えるため、比較回路(41)を構成する第1の入力電圧比較用コンパレータ(43)から第1の反転器(44)を介して出力される第1の比較信号 $V_{CP1}$ が図18(D)に示すように低い電圧(L)レベルとなる。一方、入力電圧検出手段(31)を構成する分圧抵抗(33,37)間の第2の分圧点に発生する第2の検出電圧 $V_{DT2}$ は基準電源(42)の基準電圧 $V_{R2}$ を超えないため、第2の入力電圧比較用コンパレータ(48)から第2の反転器(49)を介して出力される第2の比較信号 $V_{CP2}$ は図18(E)に示すように高い電圧(H)レベルとなる。また、MOS-FET(3)のオフ期間中にドレイン・ソース端子間に印加されていたドレイン・ソース間電圧 $V_{DS}$ は図18(B)に示すようにトランス(2)のフライバックエネルギーの放出完了と同時に降下し始め、ドレイン・ソース間電圧 $V_{DS}$ の谷部電圧近辺で谷部電圧検出回路(51)の出力信号 $V_{BD}$ が図18(C)に示すように高い電圧(H)レベルから低い電圧(L)レベルとなる。よって、第1の入力電圧比較用コンパレータ(43)から第1の反転器(44)を介して出力される第1の比較信号 $V_{CP1}$ が低い電圧(L)レベルであるため、谷部電圧検出回路(51)の出力信号 $V_{BD}$ の最初の立ち下がりエッジに同期して導通制御回路(61)の第1のDフリップフロップ(62)の信号出力端子(Q)から出力される高い電圧(H)レベルまで上昇する信号 $V_{DF1}$ は第1のANDゲート(64)により阻止される。このため、第1のANDゲート(64)からは低い電圧(L)レベルの第1の論理積信

10

20

30

40

50

号  $V_{AD1}$  が出力され、OR ゲート (65) に入力される。また、導通制御回路 (61) の第 2 の D フリップフロップ (63) の信号出力端子 (Q) からは、図 18 (C) に示す谷部電圧検出回路 (51) の出力信号  $V_{BD}$  の 2 個目の立ち下がりエッジに同期して高い電圧 (H) レベルまで上昇する信号  $V_{DF2}$  が出力される。一方、第 2 の入力電圧比較用コンパレータ (48) から第 2 の反転器 (49) を介して出力される第 2 の比較信号  $V_{CP2}$  は高い電圧 (H) レベルであるため、谷部電圧検出回路 (51) の出力信号  $V_{BD}$  の 2 個目の立ち下がりエッジに同期して高い電圧 (H) レベルまで上昇する第 2 の論理積信号  $V_{AD2}$  が第 2 の AND ゲート (67) から出力され、OR ゲート (65) に入力される。更に、導通制御回路 (61) の第 3 の D フリップフロップ (66) の信号出力端子 (Q) から低い電圧 (L) レベルの信号  $V_{DF3}$  が出力され、OR ゲート (65) に入力されるため、OR ゲート (65) からは谷部電圧検出回路 (51) の出力信号  $V_{BD}$  の 2 個目の立ち下がりエッジに同期して高い電圧 (H) レベルまで上昇する論理和信号  $V_{ON}$  が出力され、R-S フリップフロップ (21) がセット状態となる。これにより、図 18 (C) に示す谷部電圧検出回路 (51) の出力信号  $V_{BD}$  の 2 個目の立ち下がりエッジに同期して R-S フリップフロップ (21) から緩衝増幅器 (22) を介して MOS-FET (3) のゲート端子に付与される駆動信号  $V_g$  が低い電圧 (L) レベルから高い電圧 (H) レベルとなり、MOS-FET (3) がターンオンする。これにより、MOS-FET (3) に流れるドレイン電流  $I_D$  が図 18 (A) に示すように直線的に増加する。電流検出用抵抗 (9) の検出電圧  $V_{OCP}$  が出力電圧検出回路 (7) からの検出信号  $V_{FB}$  の電圧レベルに達すると、電流モード制御用コンパレータ (18) から高い電圧 (H) レベルの信号  $V_2$  が出力され、R-S フリップフロップ (23) がリセット状態となる。これにより、R-S フリップフロップ (23) から緩衝増幅器 (22) を介して MOS-FET (3) のゲート端子に付与される駆動信号  $V_g$  が高い電圧 (H) レベルから低い電圧 (L) レベルとなり、MOS-FET (3) がオン状態からオフ状態となる。したがって、中間レンジの電源電圧入力時は、MOS-FET (3) のオフ期間中に発生するドレイン・ソース間電圧  $V_{DS}$  の 2 個目の谷部電圧で MOS-FET (3) がターンオンする周波数低減 (短) 動作となる。

### 【 0 0 3 7 】

更に、交流電源 (1a) から高いレンジ (220 ~ 264 [V]) の交流電圧が入力されたときは、入力電圧検出手段 (31) を構成する分圧抵抗 (32, 33) 間の第 1 の分圧点に発生する第 1 の検出電圧  $V_{DT1}$  と、分圧抵抗 (33, 37) 間の第 2 の分圧点に発生する第 2 の検出電圧  $V_{DT2}$  が共に基準電源 (42) の基準電圧  $V_{R2}$  を超えるため、比較回路 (41) を構成する第 1 及び第 2 の入力電圧比較用コンパレータ (43, 48) からそれぞれ第 1 及び第 2 の反転器 (44, 49) を介して出力される第 1 及び第 2 の比較信号  $V_{CP1}$ ,  $V_{CP2}$  が図 19 (D) 及び (E) に示すように共に低い電圧 (L) レベルとなる。また、MOS-FET (3) のオフ期間中にドレイン・ソース端子間に印加されていたドレイン・ソース間電圧  $V_{DS}$  が図 19 (B) に示すようにトランジス (2) のライバックエネルギーの放出完了と同時に降下し始め、ドレイン・ソース間電圧  $V_{DS}$  の谷部電圧近辺で谷部電圧検出回路 (51) の出力信号  $V_{BD}$  が図 19 (C) に示すように高い電圧 (H) レベルから低い電圧 (L) レベルとなる。よって、第 1 及び第 2 の入力電圧比較用コンパレータ (43, 48) からそれぞれ第 1 及び第 2 の反転器 (44, 49) を介して出力される第 1 及び第 2 の比較信号  $V_{CP1}$ ,  $V_{CP2}$  が共に低い電圧 (L) レベルであるため、谷部電圧検出回路 (51) の出力信号  $V_{BD}$  の最初及び 2 個目の立ち下がりエッジに同期してそれぞれ導通制御回路 (61) の第 1 及び第 2 の D フリップフロップ (62, 63) の信号出力端子 (Q) から出力される高い電圧 (H) レベルまで上昇する信号  $V_{DF1}$ ,  $V_{DF2}$  は、第 1 及び第 2 の AND ゲート (64, 67) により阻止される。このため、第 1 及び第 2 の AND ゲート (64, 67) からは、共に低い電圧 (L) レベルの第 1 及び第 2 の論理積信号  $V_{AD1}$ ,  $V_{AD2}$  が出力され、OR ゲート (65) に入力される。また、導通制御回路 (61) の第 3 の D フリップフロップ (66) の信号出力端子 (Q) からは、図 19 (C) に示す谷部電圧検出回路 (51) の出力信号  $V_{BD}$  の 3 個目の立ち下がりエッジに同期して高い電圧 (H) レベルまで上昇する信号  $V_{DF3}$  が出力され、OR ゲート (65) に入力される。このため、OR ゲート (65) からは谷部電圧検出回路 (51) の出力信号  $V_{BD}$  の 3 個目の立ち下がりエッジに同期して高い電圧 (H) レベルまで上昇する論理和信号  $V_{ON}$  が出力され、R-S フリップフロップ (21) がセット状態となる。これにより、図 19 (C) に示す谷部電圧検出回路 (51) の出力信号  $V_{BD}$  の 3 個目の立ち下がりエッジに同期して R-

10

20

30

40

50

S フリップフロップ(21)から緩衝増幅器(22)を介してMOSFET(3)のゲート端子に付与される駆動信号 $V_G$ が低い電圧(L)レベルから高い電圧(H)レベルとなり、MOSFET(3)がターンオンする。これにより、MOSFET(3)に流れるドレイン電流 $I_D$ が図19(A)に示すように直線的に増加する。電流検出用抵抗(9)の検出電圧 $V_{OCP}$ が出力電圧検出回路(7)からの検出信号 $V_{FB}$ の電圧レベルに達すると、電流モード制御用コンパレータ(18)から高い電圧(H)レベルの信号 $V_2$ が出力され、R-Sフリップフロップ(23)がリセット状態となる。これにより、R-Sフリップフロップ(23)から緩衝増幅器(22)を介してMOSFET(3)のゲート端子に付与される駆動信号 $V_G$ が高い電圧(H)レベルから低い電圧(L)レベルとなり、MOSFET(3)がオン状態からオフ状態となる。したがって、高いレンジの電源電圧入力時は、MOSFET(3)のオフ期間中に発生するドレイン・ソース間電圧 $V_{DS}$ の3個目の谷部電圧でMOSFET(3)がターンオンする周波数低減(長)動作となる。

#### 【0038】

図16に示す制御回路(8)を有する実施例5のスイッチング電源装置の交流電源(1a)の交流入力電圧に対するMOSFET(3)のスイッチング周波数特性を図20に示す。交流電源(1a)の交流入力電圧が85Vから135Vまでの低いレンジの領域では、擬似共振動作が行われ、交流入力電圧の上昇に伴ってMOSFET(3)のスイッチング周波数が50kHzから指數関数的に増加する。交流電源(1a)の交流入力電圧が150Vに達すると、擬似共振動作からMOSFET(3)のオフ期間の比較的短い周波数低減(短)動作に移行し、MOSFET(3)のスイッチング周波数が急激に減少する。また、交流電源(1a)の交流入力電圧が165Vから200Vまでの中間レンジの領域ではMOSFET(3)のオフ期間の比較的短い周波数低減(短)動作が行われ、交流入力電圧の上昇に伴ってMOSFET(3)のスイッチング周波数が指數関数的に増加する。交流電源(1a)の交流入力電圧が210Vに達すると、MOSFET(3)のオフ期間の比較的短い周波数低減(短)動作からMOSFET(3)のオフ期間の比較的長い周波数低減(長)動作に移行し、MOSFET(3)のスイッチング周波数が急激に減少する。更に、交流電源(1a)の交流入力電圧が220Vから264Vまでの高いレンジの領域では、交流入力電圧の上昇に伴ってMOSFET(3)のオフ期間の比較的長い周波数低減(長)動作によりMOSFET(3)のスイッチング周波数が70kHz程度まで指數関数的に増加する。

#### 【0039】

実施例5では、比較的高いレンジ(165~264[V])の交流電源(1a)の交流電圧が入力されたとき、MOSFET(3)のスイッチング周波数が交流電源(1a)の電圧に応じて2段階で低下するため、実施例1に比較してMOSFET(3)のスイッチング制御形態を切り換える際のスイッチング周波数の変化幅を狭くすることができる。したがって、実施例1に比較してMOSFET(3)のスイッチング周波数をより細密に制御できる。

#### 【0040】

本発明の実施態様は前記の5つの実施例1~5に限定されず、更に種々の変更が可能である。例えば、実施例4及び5では実施例1の回路に適用した例を示したが、実施例2又は3の回路にも適用することが可能である。また、上記の各実施例1~5のMOSFET(3)のスイッチング制御形態を切り換える際の交流電源(1a)の交流電圧は、上記の数値に限定されることはなく、85Vから264Vの範囲内の任意の値を使用することができる。また、実施例5に示すDフリップフロップの段数を4段以上にすることも可能である。この場合は、MOSFET(3)のスイッチング制御形態を切り換える際のスイッチング周波数の変化幅がDフリップフロップの段数が増える毎に狭くなるので、Dフリップフロップの段数が多い程、スイッチング周波数をより細密に制御できる。また、上記の各実施例1~5の谷部電圧検出回路(51)では、MOSFET(3)のオフ期間中にトランス(2)の駆動巻線(2c)に発生するリング電圧 $V_{RG}$ の谷部電圧を検出することにより、MOSFET(3)のドレイン・ソース間電圧 $V_{DS}$ の谷部電圧を間接的に検出したが、MOSFET(3)のオフ期間中にドレイン・ソース端子間に発生する電圧 $V_{DS}$ の谷部電圧を直接検出してもよい。更に、上記の各実施例1~5ではスイッチング素子としてMOSFET

10

20

30

40

50

T (MOS型電界効果トランジスタ)を使用したが、IGBT (絶縁ゲート型トランジスタ)、J-FET (接合型電界効果トランジスタ)、SiT (静電誘導型トランジスタ)又はPNP、NPN型等のバイポーラトランジスタも使用可能である。

【産業上の利用可能性】

【0041】

本発明は、広範囲の電源電圧に対応可能なスイッチング電源装置に効果が顕著である。

【図面の簡単な説明】

【0042】

【図1】本発明によるスイッチング電源装置の第1の実施形態を示すブロック回路図 (実施例1) 10

【図2】図1の詳細を示す電気回路図

【図3】図2の谷部電圧検出回路の内部構成を示す電気回路図

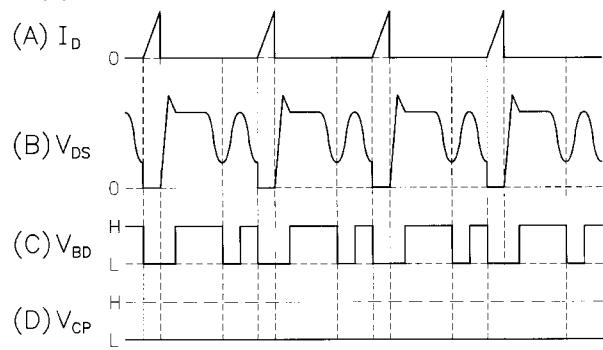

【図4】高いレンジの電源電圧入力時のMOS-FETのドレイン・ソース間電圧に対する図3の谷部電圧検出回路の各部信号の波形図

【図5】図2の谷部電圧検出回路の他の実施形態を示す電気回路図

【図6】高いレンジの電源電圧入力時のMOS-FETのドレイン・ソース間電圧に対する図5の谷部電圧検出回路の各部信号の波形図

【図7】低いレンジの電源電圧入力時における図2の回路の各部の電流及び電圧を示すタイミングチャート

【図8】高いレンジの電源電圧入力時における図2の回路の各部の電流及び電圧を示すタイミングチャート 20

【図9】図2の回路の入力電圧に対するスイッチング周波数特性を示すグラフ

【図10】本発明の第2の実施形態を示す電気回路図 (実施例2)

【図11】本発明の第3の実施形態を示す電気回路図 (実施例3)

【図12】低いレンジの電源電圧入力時における図11の回路の各部の電流及び電圧を示すタイミングチャート

【図13】高いレンジの電源電圧入力時における図11の回路の各部の電流及び電圧を示すタイミングチャート

【図14】本発明の第4の実施形態を示す電気回路図 (実施例4)

【図15】図14の回路の入力電圧に対するスイッチング周波数特性を示すグラフ 30

【図16】本発明の第5の実施形態の制御回路を示す電気回路図 (実施例5)

【図17】低いレンジの電源電圧入力時における図16の回路の各部の電流及び電圧を示すタイミングチャート

【図18】中間レンジの電源電圧入力時における図16の回路の各部の電流及び電圧を示すタイミングチャート

【図19】高いレンジの電源電圧入力時における図16の回路の各部の電流及び電圧を示すタイミングチャート

【図20】図16の回路の入力電圧に対するスイッチング周波数特性を示すグラフ

【符号の説明】

【0043】

(1)・・直流電源、(1a)・・交流電源、(1b)・・入力フィルタ回路、(1c)・・整流ブリッジ回路 (入力整流回路)、(1d)・・入力平滑コンデンサ、(2)・・トランジスタ、(2a)・・1次巻線、(2b)・・2次巻線、(2c)・・駆動巻線、(3)・・MOS-FET (スイッチング素子)、(4)・・出力整流ダイオード、(5)・・出力平滑コンデンサ、(6)・・出力整流平滑回路、(7)・・出力電圧検出回路、(8)・・制御回路、(9)・・電流検出用抵抗、(10)・・起動抵抗、(11)・・整流ダイオード、(12)・・駆動用平滑コンデンサ、(13)・・補助整流平滑回路、(14)・・フォトカプラ、(14a)・・発光素子、(14b)・・受光素子、(15)・・プルアップ抵抗、(16)・・基準電源、(17)・・過電流制限用コンパレータ、(18)・・電流モード制御用コンパレータ、(19)・・ORゲート、(20)・・パルス発生器、(21)・・R-Sフリップフロップ、(50)

22) .. 緩衝増幅器、 (23) .. 制御電源回路、 (24) .. オン・オフ信号発生手段、 (31) .. 入力電圧検出手段、 (32, 33) .. 分圧抵抗、 (34) .. レベルシフト回路 (入力電圧検出手段) (35, 36) .. レベルシフト用抵抗、 (37) .. 分圧抵抗、 (41) .. 比較回路 (比較手段)、 (42) .. 基準電源、 (43) .. (第1の) 入力電圧比較用コンパレータ、 (44) .. (第1の) 反転器、 (45) .. Dフリップフロップ、 (46) .. ワンショットパルス発生器、 (47) .. Dフリップフロップ、 (48) .. 第2の入力電圧比較用コンパレータ、 (49) .. 第2の反転器、 (51) .. 谷部電圧検出手路 (谷部電圧検出手段)、 (52) .. クリッピングダイオード、 (53, 54) .. 分圧抵抗、 (55) .. コンデンサ、 (56) .. 基準電源、 (57) .. コンパレータ、 (58) .. 遅延回路、 (61) .. 導通制御回路 (導通制御手段)、 (62) .. 第1のDフリップフロップ、 (63) .. 第2のDフリップフロップ、 (64) .. (第1の) ANDゲート、 (65) .. ORゲート、 (66) .. 第3のDフリップフロップ、 (67) .. 第2のANDゲート、 (71) .. ヒステリシスコンパレータ

10

【 四 1 】

【 义 2 】

【図3】

【図5】

【図4】

【図6】

【図7】

【図9】

【図8】

【図15】

【図16】

---

フロントページの続き

(56)参考文献 特開2003-061345(JP, A)

特開2003-125582(JP, A)

特開2003-125585(JP, A)

国際公開第2004/023634(WO, A1)

特開2001-231257(JP, A)

特開2002-345242(JP, A)

特開2002-374672(JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/00 - 3/44