(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

|             |                   |             |                 |

|-------------|-------------------|-------------|-----------------|

| (21) 출원번호   | 10-2004-7002073   | (65) 공개번호   | 10-2004-0051584 |

| (22) 출원일자   | 2004년02월10일       | (43) 공개일자   | 2004년06월18일     |

| 번역문 제출일자    | 2004년02월10일       |             |                 |

| (86) 국제출원번호 | PCT/US2002/022937 | (87) 국제공개번호 | WO 2003/015179  |

| 국제출원일자      | 2002년07월19일       | 국제공개일자      | 2003년02월20일     |

(30) 우선권주장 09/927,320 2001년08월10일 미국(US)

(73) 특히권자 실리코닉스 인코퍼레이티드

미국 캘리포니아주(우편번호95054) 산타클라라 라우렐우드 2201

(72) 발명자 다른위쉬,모하메드,엔.

미합중국캘로피니아95008.캄프밸.레자스트라이브675

질레스,프레데릭크,피.

미합중국캘리포니아95118.산조세.프린세톤드라이브1561

루이, 캄홍

미합중국캘리포니아, 95051 산타클라라, 제네바드라이브 3433

천, 쿠오-인

미합중국캘리포니아94024.로스에인에스.뉴캐슬틀드라이브1673

테리르키레

미합중국캘리포니아95050 삼타클라라밸리 테리드라이브 3385

(74) 대리인 서봉석

윤복규

### 심사관 : 김주식

#### (54) 트렌치 게이트 전극을 포함하는 금속-절연체-반도체 장치 및 이의 제조 방법

요약

트렌치의 바닥에 두꺼운 절연층을 포함하는 트렌치 MIS 장치가 그 제조 방법과 함께 개시된다. 일 실시예에 따른 트렌치 MOSFET은 트렌치 바닥에 따라 기질에서 스트레스의 변화가 거의 없는 두꺼운 산화물 층을 포함한다. 두꺼운 절연층은 트렌치 바닥에서 드레인 영역으로부터 트렌치 게이트를 분리하여 감소된 게이트와 드레인 사이의 캐패시턴스를 제공하고

이러한 MOSFET을 고주파 적용을 위해 적당하게 한다. 제작 과정 실시예에서, 두꺼운 절연층은 트렌치의 바닥에 증착된다. 박막 절연성 게이트 유전체는 노출된 측벽에 형성되고 두꺼운 절연층에 결합된다. 게이트는 잔여 트렌치 부분에 형성된다. 과정은 바디와 소스의 임플란트, 패시베이션 및 금속화에 의해 완료된다.

## 대표도

도 3

## 명세서

### 기술분야

본 발명은 트렌치 금속-절연체-반도체(MIS) 장치에 관한 것으로서, 특히 고주파 가동을 위해 적당한 트렌치 MOSFET에 관한 것이다.

### 배경기술

몇몇 금속 절연체 반도체(MIS) 장치는 반도체 기질(예를 들면, 실리콘)의 표면에서 아래쪽으로 연장되는 트렌치 내에 위치하는 게이트를 포함한다. 그런 장치 안에 전류는 1차적으로 수직이고, 그 결과 셀은 더 조밀하게 패킹된다. 동등한 것 모두는 캐패시턴스를 가지는 전류를 증가시키고 장치의 온-저항을 감소시킨다. MIS 장치의 일반적인 카테고리에 포함되는 장치는 금속 산화막 반도체 전계 효과 트랜지스터(Mosfet), 절연된 게이트 양극 트랜지스터(IGBTs), 및 MOS-게이트 사이리스터를 포함한다.

트렌치 Mosfet은, 예를 들면 최적 선형 신호 증폭 및 스위칭을 위하여 중요한 높은 상호 전도력성( $gm$ , 최대)과 낮은 특정 온저항( $R_{on}$ )으로 제조될 수 있다. 고주파 가동을 위해 가장 중요한 것의 하나는, MOSFET 내부 캐패시턴스의 감소이다. 내부 캐패시턴스는 피드백 캐패시턴스( $C_{rss}$ ), 입력 캐패시턴스( $C_{iss}$ ), 및 산출 캐패시턴스( $C_{oss}$ )라고도 불리는, 게이트와 드레인 사이의 캐패시턴스( $C_{gd}$ )가 포함한다.

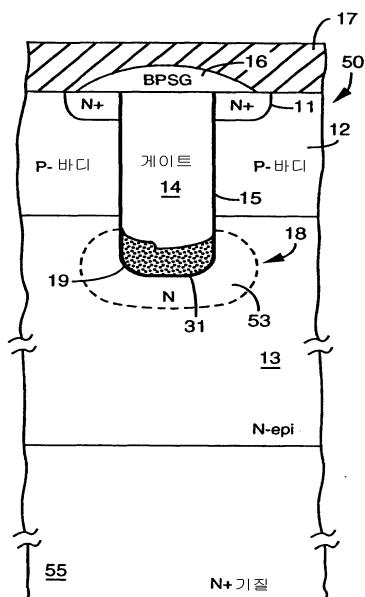

도1은 종래의 n형 트렌치 MOSFET10의 단면도이다. MOSFET10 내에, 보통  $N^+$  기질(미도시) 상에서 성장하는, n형 에피택셜("N-epi")층13은 드레인이다. N-epi층13은 약하게 도핑된 층, 즉  $N^-$ 층이다. p형 바디 영역12는  $N^+$  소스 영역11로부터 N-epi층13을 분리한다. 전류는 트렌치19의 측벽을 따라서 채널(점선으로 표시)을 통해서 수직으로 흐른다. 트렌치19의 측벽 및 바닥은 박막 게이트 절연체15(예를 들면, 이산화 실리콘)와 일렬이다. 트렌치19는 게이트14를 형성하는 도핑된 폴리실리콘과 같은 전도성 물질로 채워진다. 내부의 게이트14를 포함하여 트렌치19는, BPSG(borophosphosilicate glass)와 같은 절연층16으로 덮인다. 소스 영역11과 바디 영역12는 금속 또는 금속 합금인 컨덕터17을 사용한다. 게이트14는 도1의 평면 외부의 3차원 안에 접촉된다.

MOSFET10의 중요한 단점은 드레인이 운영하는 전압에 박막 게이트 절연체15의 부분을 복종시키는, 게이트14와 N-epi 층13 사이에 형성되는 큰 오버랩 영역18이다. 큰 오버랩은 MOSFET10의 드레인 전압 정격을 제한하고, 박막 게이트 절연체15를 위한 장기 신뢰도 문제점을 제공하고, 게이트와 드레인 사이의 캐패시턴스, MOSFET10의  $C_{gd}$ 을 매우 증가시킨다. 트렌치 구조에서,  $C_{gd}$ 은 MOSFET10의 종래의 측면 장치보다 커서, 스위칭 속도 및 고주파 적용에서의 이용을 제한한다.

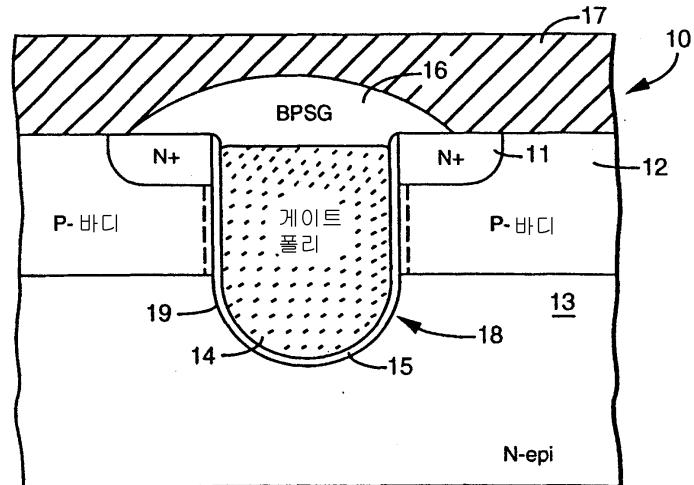

이 단점을 해결하는 가능한 방법은 참고 출원 번호 09/591,179에 기재되어 있으며 도2에 도시되어 있다. 도2는 트렌치19의 바닥의 가까이 도핑되지 않은 폴리실리콘 플러그22를 가지는 트렌치 MOSFET20의 단면도이다. MOSFET20은 산화물 층21에 의해 트렌치19의 바닥 및 산화물 층23에 의해 게이트14에서 고립시키는 폴리실리콘 플러그22를 제외하면 도1의 MOSFET10에 유사하다. 산화물 층21, 폴리실리콘 플러그22, 및 산화물 층23의 샌드위치는 게이트14와 N-epi층13 사이 거리를 증가시켜  $C_{gd}$ 을 감소시킨다.

그러나, 일정 경우에, 고주파 적용을 위해  $C_{gd}$ 을 최소화하는 트렌치19의 바닥에 도핑되지 않은 폴리실리콘보다는 절연성 물질이 바람직할 수 있다. 그러므로, 감소된 게이트와 드레인 사이의 캐패시턴스,  $C_{gd}$ 이 감소된 트렌치 MOSFET으로 더 나은 고주파 수행이 바람직하다.

### 발명의 상세한 설명

본 발명에 따라, 금속 절연체 반도체 (MIS) 장치는 기질의 표면에서 기질 내부로 연장되는 트렌치를 가지는 반도체 기질을 포함한다. 제1 전도도 타입의 소스 영역은 트렌치의 측벽 및 기질의 표면에 인접한다. 제1 전도도 타입의 반대편의 전도도 타입의 바디 영역은 소스 영역 및 측벽에 인접한다. 제1 전도도 타입의 드레인 영역은 바디 영역 및 측벽에 인접한다. 트렌치는 바디 영역에 인접하는 측벽의 부분을 따라 제1 절연층과 일렬이다. 또한 트렌치는 트렌치의 바닥 부분에 따라 제2 절연층과 일렬이다. 제2 절연층은 제1 절연층에 결합되고, 제2 절연층은 제1 절연층보다는 두껍다. 트렌치의 바닥 부분에 따라 기질 내의 스트레스는 뚜렷이 변화하지 않는다.

이러한 MIS 장치를 위한 제작 과정의 실시예에서, 측벽 및 바닥을 포함하는 트렌치가 기질 안에 형성된다. 두꺼운 절연층은 트렌치의 바닥에 증착된다. 박막 절연층은 측벽에 형성되고, 두꺼운 절연층에 결합된다. 게이트는 두꺼운 절연층의 위 부분에 형성되고 트렌치 안에서 박막 절연층과 인접한다.

두꺼운 절연층은 감소된 게이트와 드레인 사이의 캐패시턴스를 유도하는 트렌치의 바닥에서 드레인 전도성 영역으로부터 트렌치 게이트를 분리한다. 이것은 본 발명에 따른 MIS 장치, 예를 들면 트렌치 MOSFET을 고주파 적용에 적당하도록 한다.

### 도면의 간단한 설명

본 발명은 다음의 실시예 및 도면에 의해 더 잘 이해될 것이다. 도면에서, 동일 또는 유사한 부재는 동일한 참조 번호를 붙인다.

도1은 종래의 트렌치 MOSFET의 단면도이다.

도2는 트렌치의 바닥에 폴리실리콘 플러그를 가지는 트렌치 MOSFET의 단면도이다.

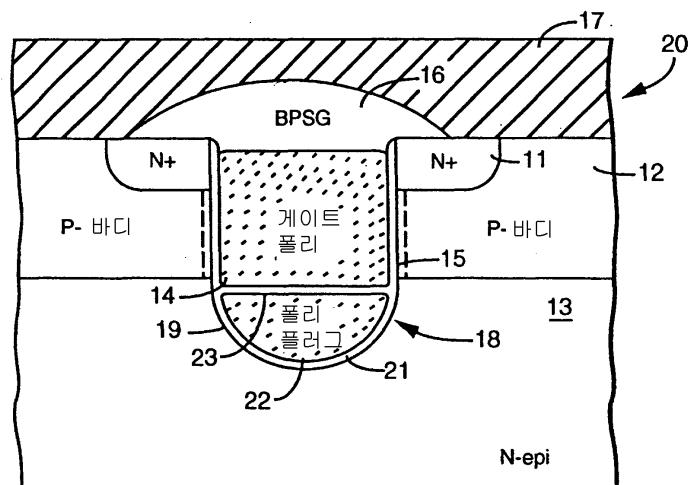

도3은 본 발명의 일 실시예에 따른 트렌치 MOSFET의 단면도이다.

도4A-4K는 본 발명에 따른 일 실시예에 따른 트렌치 MOSFET을 제작하기 위한 과정을 나타내는 단면도이다.

도5는 본 발명의 다른 실시예에 따른 트렌치 MOSFET의 단면도이다.

### 실시예

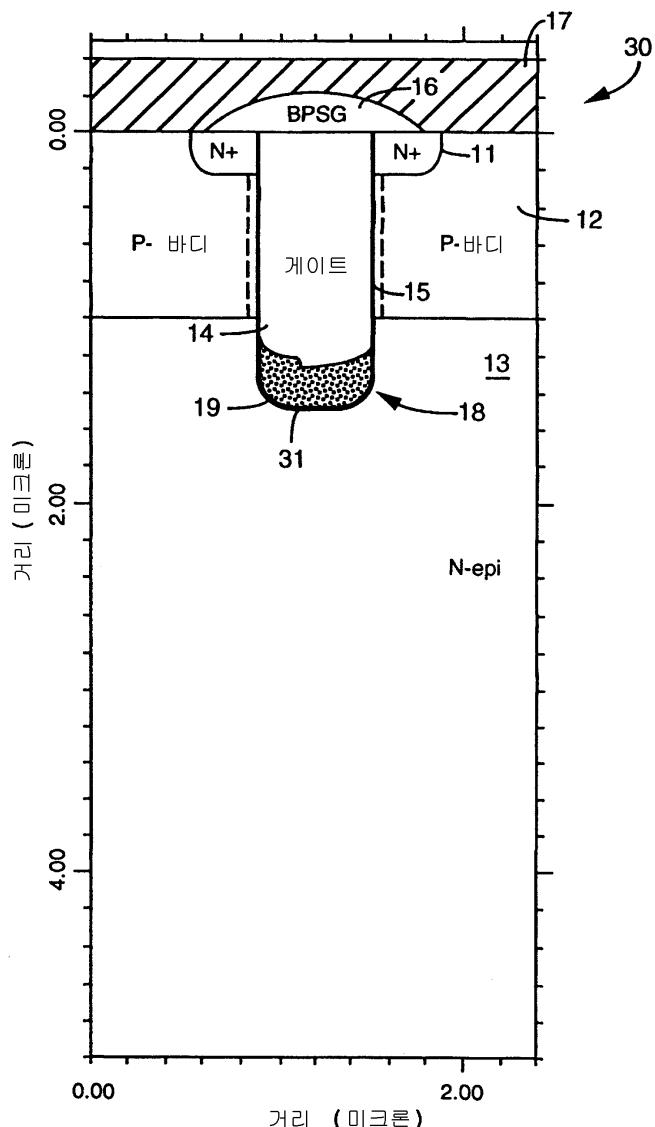

도3은 본 발명의 일 실시예에 따른 트렌치 MOSFET30의 단면도이다. MOSFET30은 도1의 MOSFET10과 일부 유사하다. 트렌치19의 외부의 MOSFET30 구성 요소는 도1의 MOSFET10과 동일할 수 있다. 그러나, MOSFET30에서, 트렌치19의 측벽만 박막 게이트 절연체15(예를 들면, 이산화 실리콘)과 일렬한다. 도1의 MOSFET과 다르게, 두꺼운 절연층31(예를 들면, 이산화 실리콘)은 도3의 MOSFET30의 트렌치19의 바닥과 일렬이다. 두꺼운 절연층31은 N-epi층13(N<sup>-</sup>층일 수 있다)으로부터 게이트14를 분리한다. 이것은 도1과 같이 오로지 얇은 절연층15가 N-epi층13(드레인)에서 게이트14를 분리할 때 생기는 문제를 해결한다. 두꺼운 절연층31은 도2에 도시한 바와 같은 폴리실리콘 플러그22를 가질 때 얻을 수 있는 것 보다 더욱 효과적인 절연체를 제공한다. 따라서, 두꺼운 절연층31은 게이트와 드레인 사이의 캐패시턴스,  $C_{gd}$ 를 최소화하고 고주파 적용을 위해 유용한 트렌치 MOSFET30을 제공한다.

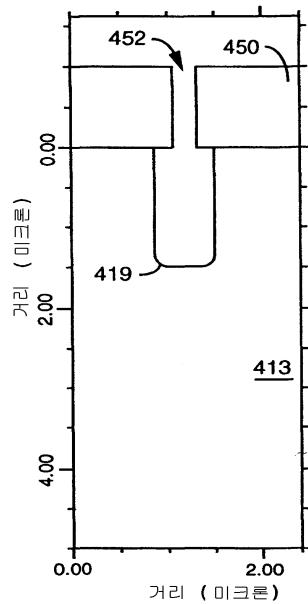

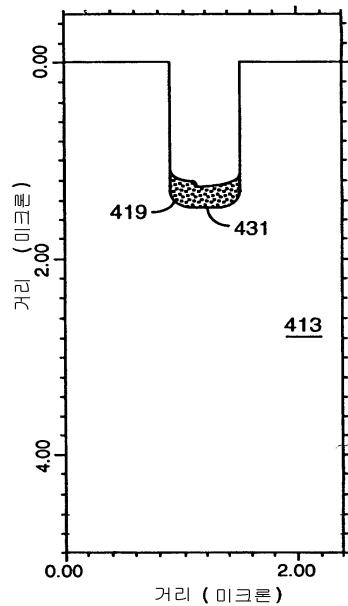

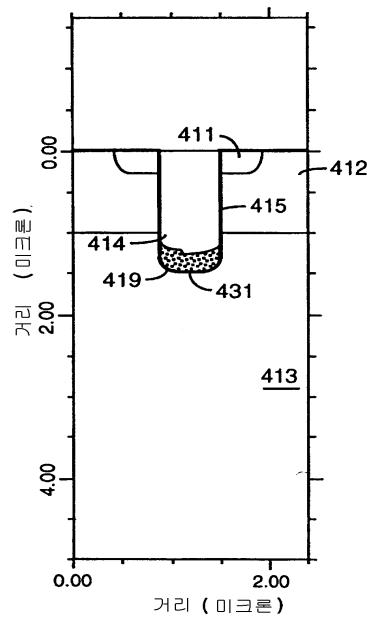

도4A-4K는 본 발명에 따른 일 실시예에 따른 도3의 MOSFET30과 같은 트렌치 MOSFET30을 제작하기 위한 과정을 나타내는 단면도이다. 도4A에 도시된 바와 같이, 과정은 많이 도핑된 N<sup>+</sup> 기질(미도시)에서 성장한 약간 도핑된 N-epi층413(전형적으로 대략 8μm 두께)으로 시작된다. 감광저항 또는 산화물인 트렌치 마스크450은 N-epi층413 위에 증착되고 트렌

치419가 위치하는 개방452를 형성하기 위하여 패턴된다. 트렌치419는 전형적인 건조 플라스마 식각, 예를 들면 반응성 이온 식각(RIE:reactive ion etch)을 이용하여 개방452를 통하여 식각된다. 트렌치419는 대략  $0.5\text{--}1.2\mu\text{m}$ 의 넓이와 대략  $1\text{--}2\mu\text{m}$ 의 깊이를 가진다.

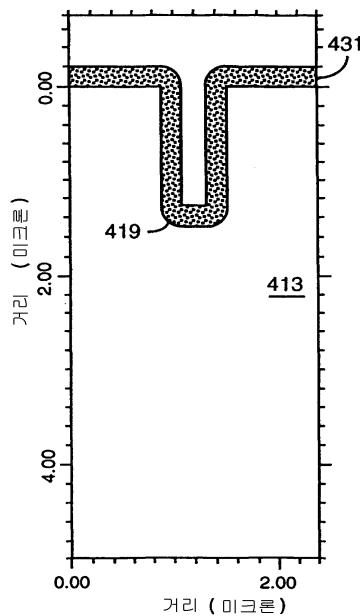

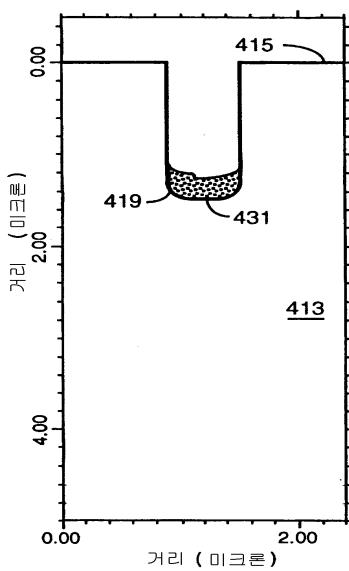

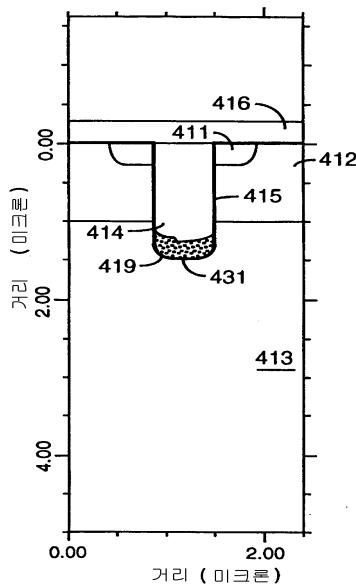

마스크450은 제거되고, 두꺼운 절연층431(예를 들면, 대략  $0.1\text{--}0.3\mu\text{m}$  두께)은 도4B에 도시된 바와 같이 N-epi층413 위에 증착된다. N-epi층413의 윗 표면뿐 아니라 트렌치419의 측벽 및 바닥에서 절연층431의 등각 증착을 제공하기 위하여 화학 증착법(CVD)과 같은 종래의 증착 기술에 따라, 증착 과정이 선택된다. 두꺼운 절연층431은, 예를 들면, 저온 산화물(LTO), PSG(phosphosilicate glass), BPSG, 또는 다른 절연성 물질일 수 있다. 일부 실시예에서, 얇은 절연층(예를 들면,  $100\text{--}200\text{\AA}$ 의 이산화 실리콘)은 예를 들면, 두꺼운 절연층431의 증착 전에 10분 동안  $950^\circ\text{C}$ 에서 잘 알려진 건조 산화 과정을 이용하여 열로 성장될 수 있다.

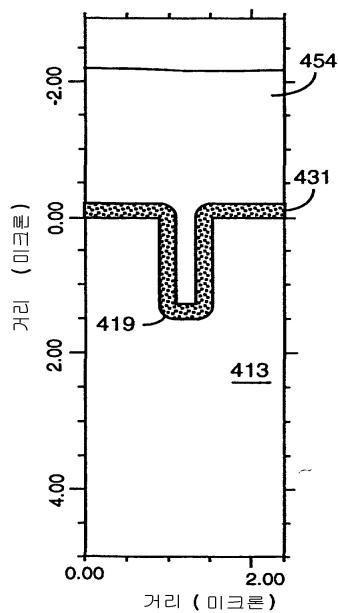

다음, 도4C에 도시된 바와 같이 배리어 층454는 CVD에 의해 증착된다. 이 증착은 비등각이며, 트렌치419를 채우고, 두꺼운 절연층431의 최상 표면을 지나서 범람될 수 있다. 배리어 층454는, 예를 들면, 실리콘 질화물( $\text{Si}_3\text{N}_4$ )일 수 있고,  $2\text{--}4\mu\text{m}$ 의 두께일 있다. 배리어 층454는 다시 식각되고, 두꺼운 절연층431에는 없고 배리어 층454에 대해 높은 선택성이 있는 식각 재료를 사용하여 습식 식각 후, 건조 식각을 실행하는 것에 의해 전형적으로 식각된다. 도4D에 도시된 바와 같이 배리어 층454는 단지 대략  $0.1\text{--}0.2\mu\text{m}$ 가 트렌치419에 남을 때까지 트렌치419로 식각된다.

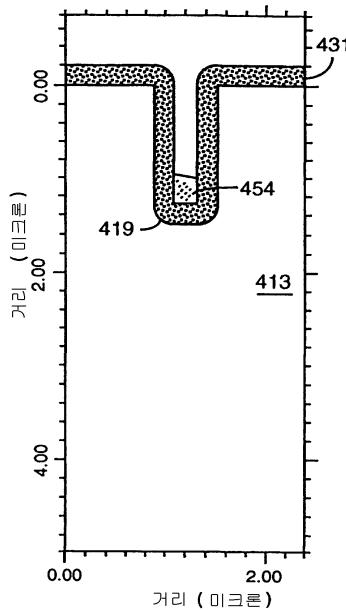

두꺼운 절연층431은 배리어 층454 및 N-epi층413에는 없고 절연층431에 높은 선택성이 있는 식각 재료를 사용하여 습식 식각 기술에 의해 전형적으로 식각된다. 절연층431은 N-epi층413의 정상과 트렌치419의 측벽으로부터 절연층431이 트렌치419의 바닥에 이를 때까지 식각된다. 배리어 층454의 나머지는 제거되어, 도4E에 도시된 구조가 된다.

도4F에 도시된 바와 같이, 박막 게이트 절연체415(예를 들면, 대략  $100\text{--}1000\text{\AA}$  두께)는 N-epi 층413의 윗 표면과 트렌치419의 측벽에 형성된다. 박막 게이트 절연체415는, 예를 들면, 20분 동안  $1050^\circ\text{C}$ 에서 건조 산화 기술을 사용하여 열로 성장하는, 이산화 실리콘 층일 수 있다. 일부 실시예에서, 희생 게이트 산화물(미도시)은 박막 게이트 절연체415를 성장시키기 전에 트렌치419의 측벽을 청소하기 위하여 열로 성장하고 습식 식각에 의해 제거될 수 있다. 두꺼운 절연층431의 식각을 극소화하기 위하여 이러한 희생 게이트 산화물의 습식 식각은 얕게 한다.

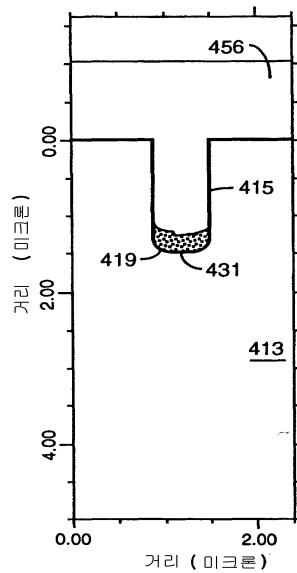

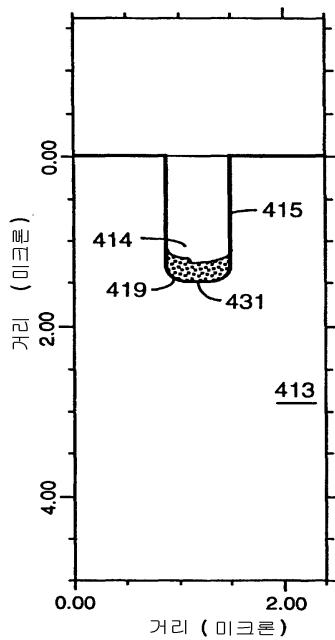

도4G에 도시된 바와 같이, 트렌치419를 채우고 박막 게이트 절연체415의 최상 표면을 지나서 범람하기 위하여 전도성 물질456은 CVD에 의해, 가능하다면 저압 CVD(LPCVD)에 의하여 증착된다. 전도성 물질456은, 예를 들면, 그 위치에 도핑된 폴리실리콘, 또는 연속적으로 이식되고 단련되는 도핑되지 않은 폴리실리콘층, 또는 대체 전도성 물질일 수 있다. 전도성 물질456은 전도성 물질456의 윗 표면이 N-epi층413의 정상과 대략 수평이 될 때까지 전형적인 반응성 이온 식각을 사용하여 식각되며, 따라서 도4H에 도시된 바와 같이 게이트414를 형성한다. n형 MOSFET에서, 게이트414는, 예를 들면  $10^{20}\text{cm}^{-3}$ 의 농도로 도핑된 폴리실리콘층일 수 있다. 실시예에서, 트렌치419의 정상을 지나서 전도성 물질456은 식각될 수 있고, 이에 따라 게이트와 드레인 사이의 캐패시턴스를 극소화하기 위하여 게이트414를 우뚝하게 한다.

공지의 주입과 확산 과정을 사용하여, p형 바디 영역412와  $\text{N}^+$  소스 영역411은 도4I에 도시된 바와 같이 N-epi층413 안에 형성된다. p형 바디 영역412와 N-epi층413의 나머지 사이의 PN 접속점은 두꺼운 절연층431과 박막 게이트 절연체415 사이 공용영역 위의 높이에 위치한다.

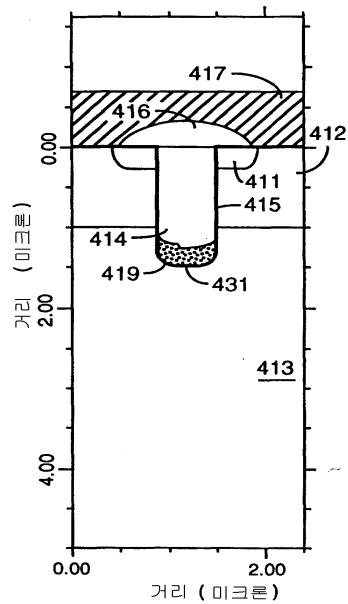

도4J에 도시된 바와 같이, BPSG(borophosphosilicate glass)일 수 있는 절연층416은 N-epi층413과 게이트414의 표면에 CVD에 의해 증착된다. 도4K에 도시된 바와 같이 p형 바디 영역412와  $\text{N}^+$  소스 영역411의 부분을 노출하기 위하여 절연층416은 건조 식각을 사용하여 전형적으로 식각된다. 바디 영역412와 소스 영역411에 대한 전기 접촉은 전형적으로 금속 또는 금속 합금으로 증착(예를 들면, 물리적 수증기 증착, 도금, 스퍼터링, 또는 증발)되는 컨덕터417에 의한다. 게이트414에 대한 전기 접촉은 도4K의 평면 밖의 3차원에서 이루어진다. 드레인(미도시)에 대한 전기적 접촉은 N-epi층413이 성장하는  $\text{N}^+$  기질(미도시)의 반대 표면에서 이루어진다.

이 방법은 열로 성장하는 두꺼운 절연층431에 의해 발생할 수 있는 바람직하지 않은 효과 또는 제조 염려의 최소화와  $\text{C}_{\text{gd}}$ 을 극소화하기 위하여 트렌치419의 바닥에서 두꺼운 절연층431의 결합을 허용한다. 예를 들면, 트렌치419의 오목한 바닥에서 두꺼운 산화물을 성장하는 것으로부터의 스트레스 효과는 산화물을 열로 성장하는 것보다 증착함으로써 피할 수 있다. 두꺼운 절연층431의 열 성장 동안 "새의 부리(bird's beak)"의 형성에 의해 일어날 수 있는 두꺼운 절연층431 및 박막 게이트 절연체415의 접합에서 절연층의 얇아짐은, 두꺼운 절연층431을 증착함으로써 피할 수 있다. 한편, 트렌치419의

식각된 측벽 프로필의 시프트도 두꺼운 절연층431의 증착에 의해 피할 수 있다. 두꺼운 절연층431의 성장은 "밸브(bulb)" 효과를 유발하는 트렌치419의 측벽에 박막 게이트 절연체415의 연속적인 성장에 의해 보상되지 않는 트렌치419의 바닥에서 시프트를 발생시킬 수 있다.

도5는 본 발명의 다른 실시예에 따른 트렌치 MOSFET50의 단면도이다. MOSFET50은 도3의 MOSFET30과 많이 유사하다. 특히, 두꺼운 절연층31은 트렌치19의 바닥과 일렬인 반면, 트렌치19의 측벽만은 박막 게이트 절연체15와 일렬이다. 도3의 MOSFET30에서, 두꺼운 절연층31은 트렌치19의 바닥에 축적 층안에 펴지는 저항 증가에 기인하는 MOSFET30의 온-저항( $R_{on}$ )을 증가시킬 수 있다. 그러나, 도5의 MOSFET50은 전류가 효과적으로 펴지는 것을 돋도록 트렌치19의 바닥에 많이 도핑된 영역53을 포함한다. 많이 도핑된 영역53은  $N^+$  기질55 위에 있는 N-epi층13에서 형성한다. 많이 도핑된 영역53은 도4A에 도시된 바와 같이 트렌치 식각 후 마스크450이 제거되기 전에 비소 또는 인과 같은 n형 도편트를 이식해서 형성할 수 있다. 따라서, 두꺼운 절연층31은 게이트와 드레인 사이의 캐패시턴스,  $C_{gd}$ 를 극소화하고, 많이 도핑된 영역53은 온-저항,  $R_{on}$ 을 극소화시켜 고주파 적용을 위해 적절한 트렌치 MOSFET50을 제공한다.

상기 도 3 내지 5에서, 트렌치의 직경에 대한 관계가 규정된다. 도 3 내지 5에 의하면, 상기 제2 절연층의 수직 중점에서의 상기 트렌치의 제1 직경은 상기 바디 영역에 인접하는 상기 트렌치의 직경과 동일한 것으로 도시되어 있다. 따라서, 제2 절연층의 수직 중점에서의 상기 트렌치의 제1 직경은 바디 영역에 인접하는 상기 트렌치의 직경보다 명백하게 크지 않다.

이상과 같이, 본 발명은 비록 한정된 실시예와 도면에 의해 설명되었으나, 본 발명은 이것에 의해 한정되지 않으며 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에 의해 본 발명의 기술 사상과 아래에 기재될 특허 청구범위의 균등 범위 내에서 다양한 수정 및 변형이 가능함은 물론이다. 예를 들면, 트렌치 외부 영역 및 트렌치 게이트 사이의 절연층을 형성하는데 바람직한 금속 절연체 반도체(MIS) 장치의 어떤 타입도 본 발명의 구조와 방법에서 이용될 수 있다. 또한 다양한 절연성 또는 전도성 물질도 이용될 수 있으며, 본 발명은 p형 MOSFET에도 적용 가능하다. 본 발명은 다음 청구범위에 의하 여만 제한된다.

### (57) 청구의 범위

#### 청구항 1.

기질의 표면에서 기질 내부로 연장되는 트렌치를 가지는 반도체 기질;

상기 트렌치의 측벽 및 표면에 인접하는 제1 전도도 타입의 소스 영역;

상기 소스 영역 및 상기 측벽에 인접하는 상기 제1 전도도 타입의 반대편의 제2 전도도 타입의 바디 영역; 및

상기 바디 영역 및 상기 측벽에 인접하는 상기 제1 전도도 타입의 드레인 영역; 을 포함하는 금속-절연체-반도체(MIS) 장치로서,

상기 트렌치의 바닥 부분을 따라 상기 기질에서의 스트레스는 뚜렷하게 변화하지 않고,

상기 트렌치는 바디 영역에 인접하는 상기 측벽의 부분을 따라 제1 절연층과 일렬이며,

상기 트렌치는 상기 트렌치의 상기 바닥 부분을 따라 제2 절연층과 일렬이고, 상기 제2 절연층은 제1 절연층과 연결되며, 상기 제2 절연층은 상기 제1 절연층보다 두꺼운 MIS 장치.

#### 청구항 2.

제 1 항에 있어서,

상기 트렌치에서 상기 제1 절연층 및 상기 제2 절연층에 연결되는 게이트 영역을 더 포함하는 MIS 장치.

### 청구항 3.

제 2 항에 있어서,

상기 게이트 영역은 폴리실리콘을 포함하는 MIS 장치.

### 청구항 4.

제 1 항에 있어서,

상기 트렌치의 적어도 상기 바닥 부분에 인접하는 상기 드레인 영역에서 형성되는 상기 제1 전도도 타입의 높은 전도도 영역을 더 포함하는 MIS 장치.

### 청구항 5.

제 1 항에 있어서,

상기 제1 절연층은 산화물을 포함하는 MIS 장치.

### 청구항 6.

제 1 항에 있어서,

상기 제2 절연층은 산화물을 포함하는 MIS 장치.

### 청구항 7.

삭제

### 청구항 8.

제 1 항에 있어서,

상기 MIS 장치는 MOSFET을 포함하는 MIS 장치.

### 청구항 9.

기질의 표면에서 기질 내부로 연장되는 트렌치를 가지는 반도체 기질;

상기 트렌치의 측벽 및 상기 표면에 인접하는 제1 전도도 타입의 소스 영역; 상기 소스 영역 및 상기 측벽에 인접하는 상기 제1 전도도 타입의 반대편의 제2 전도도 타입의 바디 영역;

상기 바디 영역 및 상기 측벽에 인접하는 상기 제1 전도도 타입의 드레인 영역(상기 트렌치의 바닥 부분을 따라 상기 기질에서의 스트레스는 뚜렷하게 변화하지 않고, 상기 트렌치는 상기 바디 영역에 인접하는 상기 측벽의 부분을 따라 제1 절연층과 일렬이며, 상기 트렌치는 상기 트렌치의 바닥 부분을 따라 제2 절연층과 일렬이고, 상기 제2 절연층은 상기 제1 절연층과 연결되며 제1 절연층보다 더 두껍다); 및

상기 트렌치에서 상기 제1 절연층 및 상기 제2 절연층에 결합하는 게이트 영역; 을 포함하는 트렌치 게이트 MOSFET.

### 청구항 10.

제 9 항에 있어서,

상기 게이트 영역은 폴리실리콘을 포함하는 트렌치 게이트 MOSFET.

### 청구항 11.

제 9 항에 있어서,

상기 트렌치의 적어도 상기 바닥 부분에 인접하는, 상기 드레인 영역에서 형성되는 상기 제1 전도도 타입의 높은 전도도 영역을 더 포함하는 트렌치 게이트 MOSFET.

### 청구항 12.

제 9 항에 있어서,

상기 제1 절연층은 산화물을 포함하는 트렌치 게이트 MOSFET.

### 청구항 13.

제 9 항에 있어서,

상기 제2 절연층은 산화물을 포함하는 트렌치 게이트 MOSFET.

### 청구항 14.

식 제

### 청구항 15.

기질의 표면에서 기질 내부로 연장되는 트렌치를 가지는 반도체 기질;

상기 트렌치의 측벽 및 상기 표면에 인접하는 제1 전도도 타입의 소스 영역; 상기 소스 영역 및 상기 측벽에 인접하는 상기 제1 전도도 타입의 반대편의 제2 전도도 타입의 바디 영역;

상기 바디 영역 및 상기 측벽에 인접하는 제1 전도도 타입의 드레인 영역;

상기 바디 영역에 인접하는 상기 측벽의 부분을 따라 상기 트렌치와 일렬인 제1 절연층;

상기 트렌치의 바닥 부분을 따라 상기 트렌치와 일렬이고, 제1 전도층 보다 두꺼우며, 제1 절연층과 결합되는 제2 절연층; 및

상기 트렌치에서 상기 제1 절연층 및 제2 절연층에 결합하는 게이트 영역; 을 포함하는 트렌치 게이트 MOSFET.

### 청구항 16.

제 15 항에 있어서,

상기 트렌치의 적어도 상기 바닥 부분에 인접하는, 상기 드레인 영역에서 형성되는 상기 제1 전도도 타입의 높은 전도도 영역을 더 포함하는 트렌치 게이트 MOSFET.

### 청구항 17.

기질의 표면에서 기질 내부로 연장되는 트렌치를 가지는 반도체 기질;

상기 트렌치의 측벽 및 상기 표면에 인접하는 제1 전도도 타입의 소스 영역; 상기 소스 영역 및 상기 측벽에 인접하는 상기 제1 전도도 타입의 반대편의 제2 전도도 타입의 바디 영역;

상기 바디 영역 및 상기 측벽에 인접하는 제1 전도도 타입의 드레인 영역;

상기 바디 영역에 인접하는 상기 측벽의 부분을 따라 상기 트렌치와 일렬인 제1 절연층;

상기 트렌치의 바닥 부분을 따라 상기 트렌치와 일렬이고, 제1 절연층보다 두꺼우며, 제1 절연층과 결합되는 제2 절연층 (상기 제2 절연층의 수직 중점에서 얻은 상기 트렌치의 제1 직경은 상기 바디 영역에 인접하여 얻어진 상기 트렌치의 제2 직경보다 크지 않다); 및

상기 트렌치에서 상기 제1 절연층 및 제2 절연층에 결합되는 게이트 영역; 을 포함하는 트렌치 게이트 MOSFET.

### 청구항 18.

제 17 항에 있어서,

상기 트렌치의 적어도 상기 바닥 부분에 인접하는, 상기 드레인 영역에서 형성되는 상기 제1 전도도 타입의 높은 전도도 영역을 더 포함하는 트렌치 게이트 MOSFET.

### 청구항 19.

반도체 기질을 제공하는 단계;

상기 기질 내에 트렌치를 형성하는 단계(상기 트렌치는 측벽 및 바닥을 가진다);

상기 측벽 및 바닥에 두꺼운 절연층을 증착하는 단계;

상기 트렌치에 마스크 층을 증착하는 단계;

상기 트렌치의 상기 바닥 부분에서 상기 마스크 층의 부분을 놔두는 반면 상기 측벽 상의 상기 두꺼운 절연층의 부분을 노출시키기 위하여 마스크 층을 식각하는 단계;

상기 트렌치의 상기 바닥 부분에서 상기 두꺼운 절연층의 부분을 놔두는 반면 상기 측벽의 노출된 부분을 형성하기 위하여 상기 두꺼운 절연층을 식각하는 단계;

상기 측벽의 상기 노출된 부분 상에 박막 절연층을 형성하는 단계; 및

상기 트렌치에 상기 두꺼운 절연층 위 및 상기 박막 절연층과 인접한 부분에 게이트를 형성하는 단계;를 포함하는 MIS 장치를 제작하는 방법.

## 청구항 20.

제 19 항에 있어서,

상기 박막 절연층을 형성하는 단계는 상기 측벽을 열로 산화하는 것을 포함하는 MIS 장치를 제작하는 방법.

## 청구항 21.

제 20 항에 있어서,

상기 박막 절연층을 형성하는 단계 이전에 상기 측벽에 박막 희생 산화물 층을 성장시키는 단계를 더 포함하는 MIS 장치를 제작하는 방법.

## 청구항 22.

제 19 항에 있어서,

상기 게이트를 형성하는 단계는,

상기 트렌치에 도핑된 폴리실리콘을 증착하는 단계; 및

상기 도핑된 폴리실리콘을 상기 기질의 상기 표면과 같은 높이로 식각하는 단계를 포함하는 MIS 장치를 제작하는 방법.

## 청구항 23.

제 19 항에 있어서,

상기 두꺼운 절연층을 증착하는 단계 이전에 상기 측벽 및 상기 바닥 위에 박막 절연층을 형성시키는 단계를 더 포함하는 MIS 장치를 제작하는 방법.

## 청구항 24.

제 19 항에 있어서,

상기 측벽에 인접하는 상기 기질에 바디 영역을 형성하는 단계; 및

상기 바디 영역에 소스 영역을 형성하는 단계(상기 소스 영역은 상기 측벽 및 상기 기질의 윗 표면과 인접한다);를 더 포함하는 MIS 장치를 제작하는 방법.

## 청구항 25.

제 19 항에 있어서,

상기 트렌치의 적어도 상기 바닥 부분에 인접하는 상기 기질에 높은 전도도 영역을 형성하는 단계를 더 포함하는 MIS 장치를 제작하는 방법.

### 청구항 26.

반도체 기질을 제공하는 단계;

상기 기질 내에 트렌치를 형성하는 단계(상기 트렌치는 측벽 및 바닥을 가진다);

상기 바닥에 두꺼운 절연층을 증착하는 단계;

상기 측벽에 박막 절연층을 형성하는 단계(상기 박막 절연층은 상기 두꺼운 절연층과 연결된다); 및

상기 트렌치에 상기 두꺼운 절연층 위 및 상기 박막 절연층에 인접한 게이트를 형성하는 단계;를 포함하는 MIS 장치를 제작하는 방법.

### 청구항 27.

제 26 항에 있어서,

상기 두꺼운 절연층을 증착하는 단계는,

상기 측벽 및 상기 바닥에 상기 두꺼운 절연층을 증착하는 단계;

상기 트렌치에 마스크 층을 증착하는 단계;

상기 트렌치의 상기 바닥 부분에서 상기 마스크 층의 부분을 놔두는 반면 상기 측벽 상의 상기 두꺼운 절연층의 부분을 노출시키기 위하여 상기 마스크 층을 식각하는 단계; 및

상기 트렌치의 상기 바닥 부분에서 상기 두꺼운 절연층의 부분을 놔두는 반면 상기 측벽 상의 노출된 부분을 형성하기 위하여 상기 두꺼운 절연층을 식각하는 단계;를 포함하는 MIS 장치를 제작하는 방법.

### 청구항 28.

제 26 항에 있어서,

상기 측벽에 인접하는 상기 기질에 바디 영역을 형성하는 단계; 및

상기 바디 영역에 소스 영역을 형성하는 단계(상기 소스 영역은 상기 측벽 및 상기 기질의 윗 표면과 인접한다);를 포함하는 MIS 장치를 제작하는 방법.

### 청구항 29.

제 26 항에 있어서,

상기 트렌치의 적어도 상기 바닥 부분에 인접하는 상기 기질에 높은 전도도 영역을 형성하는 단계를 더 포함하는 MIS 장치를 제작하는 방법.

### 청구항 30.

기질의 표면에서 기질 내부로 연장되는 트렌치를 가지는 반도체 기질;

상기 트렌치의 측벽 및 표면에 인접하는 제1 전도도 타입의 소스 영역;

상기 소스 영역 및 상기 측벽에 인접하는 상기 제1 전도도 타입의 반대편의 제2 전도도 타입의 바디 영역;

상기 바디 영역 및 상기 측벽에 인접하는 상기 제1 전도도 타입의 드레인 영역(상기 트렌치는 바디 영역에 인접하는 상기 측벽의 부분을 따라 제1 절연층과 일렬이며, 상기 트렌치는 상기 트렌치의 바닥 부분을 따라 제2 절연층과 일렬이고, 상기 제2 절연층은 제1 절연층과 접촉되며, 이에 의해 상기 제 2 절연층의 형성이 상기 기질내에서 실질적인 스트레스를 형성하지 않는다); 및 상기 트렌치의 상기 바닥 부분과 접촉하는 상기 드레인 영역에 상기 제 1 전도도 타입의 높은 도핑 영역;을 포함하는 MIS 장치.

### 청구항 31.

제 30 항에 있어서,

상기 트렌치에서 상기 제1 절연층 및 상기 제2 절연층에 인접하는 게이트 영역을 더 포함하는 MIS 장치.

### 청구항 32.

제 30 항에 있어서,

상기 MIS 장치는 MOSFET인 MIS 장치.

### 청구항 33.

기질의 표면에서 기질 내부로 연장되는 트렌치를 가지는 반도체 기질;

상기 트렌치의 측벽 및 상기 표면에 인접하는 제1 전도도 타입의 소스 영역; 상기 소스 영역 및 상기 측벽에 인접하는 상기 제1 전도도 타입의 반대편의 제2 전도도 타입의 바디 영역;

상기 바디 영역 및 상기 측벽에 인접하는 상기 제1 전도도 타입의 드레인 영역(상기 트렌치는 상기 바디 영역에 인접하는 상기 측벽의 부분을 따라 제 1 절연층과 일렬이며, 상기 트렌치의 바닥 부분을 따라 제 2 절연층과 일렬이고, 상기 제 2 절연층은 상기 제 1 절연층과 접촉하며 상기 제 1 절연층보다 더 두껍고, 이에 의해 상기 제 2 절연층의 형성이 상기 기질내에 실질적인 스트레스를 형성하지 않는다);

상기 트렌치에서 상기 제 1 절연층 및 상기 제 2 절연층에 인접하는 게이트; 및

상기 트렌치의 상기 바닥 부분과 접촉하는 상기 드레인 영역에 상기 제 1 전도도 타입의 도핑 영역;을 포함하는 트렌치 게이트 장치.

### 청구항 34.

제 31 항 또는 제 33 항에 있어서,

상기 게이트는 폴리실리콘을 포함하는 MIS 장치 또는 트렌치 게이트 장치.

### 청구항 35.

제 31 항 또는 제 33 항에 있어서,

상기 제 1 절연층은 산화물을 포함하는 MIS 장치 또는 트렌치 게이트 장치.

### 청구항 36.

제 31 항 또는 제 33 항에 있어서,

상기 제 2 절연층은 산화물을 포함하는 MIS 장치 또는 트렌치 게이트 장치.

### 청구항 37.

삭제

### 청구항 38.

제 31 항 또는 제 33 항에 있어서,

상기 제 1 절연층은 열로 성장하는 MIS 장치 또는 트렌치 게이트 장치.

### 청구항 39.

기질의 표면에서 기질 내부로 연장되는 트렌치를 가지는 반도체 기질;

상기 트렌치의 측벽 및 상기 표면에 인접하는 제1 전도도 타입의 소스 영역; 상기 소스 영역 및 상기 측벽에 인접하는 상기 제1 전도도 타입의 반대편의 제2 전도도 타입의 바디 영역;

상기 바디 영역 및 상기 측벽에 인접하는 제1 전도도 타입의 드레인 영역;

상기 바디 영역에 인접하는 상기 측벽의 부분을 따라 상기 트렌치와 일렬인 제1 절연층;

상기 트렌치의 바닥 부분을 따라 상기 트렌치와 일렬이고, 상기 제1 전도층 보다 두꺼우며, 제1 절연층과 접촉하는 제2 절연층(상기 제1 절연층 및 제2 절연층의 접속부에서의 과도 절연층의 두께는 적어도 상기 제1 절연층의 두께 이상이다);

상기 트렌치에서 상기 제1 절연층 및 제2 절연층에 인접하는 게이트; 및

상기 트렌치의 상기 바닥 부분과 접촉하는 상기 드레인 영역에 상기 제 1 전도도 타입의 높은 도핑 영역; 을 포함하는 트렌치 게이트 장치.

### 청구항 40.

기질의 표면에서 기질 내부로 연장되는 트렌치를 가지는 반도체 기질;

상기 트렌치의 측벽 및 상기 표면에 인접하는 제1 전도도 타입의 소스 영역; 상기 소스 영역 및 상기 측벽에 인접하는 상기 제1 전도도 타입의 반대편의 제2 전도도 타입의 바디 영역;

상기 바디 영역 및 상기 측벽에 인접하는 제1 전도도 타입의 드레인 영역;

상기 바디 영역에 인접하는 상기 측벽의 부분을 따라 상기 트렌치와 일렬인 제1 절연층;

상기 트렌치의 바닥 부분을 따라 상기 트렌치와 일렬이고, 상기 제1 절연층보다 두꺼우며, 제1 절연층과 접촉하고, 이에 의해 그 형성이 상기 기질 내에 실질적인 스트레스를 형성하지 않는 제2 절연층(상기 제2 절연층의 수직 중점에서의 상기 트렌치의 폭은 상기 바디 영역에 인접하는 상기 트렌치의 폭보다 크지 않다); 상기 트렌치에서 상기 제1 절연층 및 제2 절연층에 인접하는 게이트; 및

상기 트렌치의 상기 바닥 부분과 접촉하는 상기 드레인 영역에 상기 제 1 전도도 타입의 높은 도핑 영역;을 포함하는 트렌치 게이트 장치.

#### 청구항 41.

제 1 드레인 영역;

상기 제 1 드레인 영역의 제 1 표면에 위치한 바디 영역;

상기 바디 영역을 통해, 부분적으로는 상기 제 1 드레인 영역 내부로 연장된 게이트 영역;

상기 바디 영역의 제 1 부분과 상기 게이트 영역의 제 1 부분 사이에 위치한 소스 영역;

상기 소스 영역과 상기 게이트 영역의 상기 제 1 부분 사이 및 상기 바디 영역과 상기 게이트 영역의 제 2 부분 사이에 위치한 제 1 절연층(상기 제 1 절연층은 제 1 두께를 가진다); 및

상기 제 1 드레인 영역의 제 1 부분과 상기 게이트 영역의 제 3 부분 사이에 적어도 일부가 위치하고, 상기 제 1 절연층과 인접하는 제 2 절연층(상기 제 2 절연층은 상기 제 1 두께보다 큰 제 2 두께를 가지며, 상기 제 1 드레인 영역을 산화시키므로써 형성되지 않는다);을 포함하는 MIS 장치.

#### 청구항 42.

제 41 항에 있어서, 상기 게이트 영역은 폴리실리콘을 포함하는 MIS 장치.

#### 청구항 43.

제 41 항에 있어서, 상기 게이트 영역의 상기 제 3 부분에 인접하는 상기 제 1 드레인 영역에 형성된 높은 전도도 영역을 더 포함하는 MIS 장치.

#### 청구항 44.

제 41 항에 있어서, 상기 제 1 절연층은 산화물을 포함하는 MIS 장치.

#### 청구항 45.

제 41 항에 있어서, 상기 제 2 절연층은 PSG(phosphosilicate glass) 및 BPSG(borophosphosilicate glass)를 구성하는 그룹에서 선택되는 MIS 장치.

#### 청구항 46.

제 1 드레인 영역;

상기 제 1 드레인 영역의 제 1 표면에 위치한 바디 영역;

상기 바디 영역을 통해, 부분적으로는 상기 제 1 드레인 영역 내부로 연장된 게이트 영역;

상기 바디 영역의 제 1 부분과 상기 게이트 영역의 제 1 부분 사이에 위치한 소스 영역;

상기 소스 영역과 상기 게이트 영역의 상기 제 1 부분 사이, 상기 바디 영역의 제 2 부분과 상기 게이트 영역의 제 2 부분 사이 및 상기 제 1 드레인 영역의 제 1 부분과 상기 게이트 영역의 제 3 부분 사이에 위치하는 산화물층(상기 산화물층은 제 1 두께를 가진다); 및

PSG 및 BPSG를 구성하는 물질의 그룹에서 선택되며, 상기 제 1 드레인 영역의 제 2 부분과 상기 게이트 영역의 제 4 부분 사이에 위치하고, 상기 산화물층과 연결되는 절연층(상기 절연층은 상기 제 1 두께보다 큰 제 2 두께를 가진다);을 포함하는 MIS 장치.

#### 청구항 47.

제 46 항에 있어서,

상기 제 1 드레인 영역은 제 1 전도도 타입의 반도체를 포함하는 MIS 장치.

#### 청구항 48.

제 46 항에 있어서,

상기 바디 영역은 제 2 전도도 타입의 반도체를 포함하는 MIS 장치.

#### 청구항 49.

제 46 항에 있어서,

상기 소스 영역은 제 1 전도도 타입의 반도체를 포함하는 MIS 장치.

#### 청구항 50.

제 46 항에 있어서,

상기 제 1 드레인 영역의 제 2 표면에 위치하는 제 2 드레인 영역(상기 제 2 표면은 상기 제 1 표면과 반대편이다)을 더 포함하는 MIS 장치.

#### 청구항 51.

제 46 항에 있어서,

상기 제 2 드레인 영역은 제 1 전도도 타입의 반도체를 포함하는 MIS 장치.

## 청구항 52.

제 1 드레인 영역;

상기 제 1 드레인 영역 위에 위치한 바디 영역;

상기 바디 영역을 통해, 부분적으로는 상기 제 1 드레인 영역 내부로 연장된 게이트 영역;

상기 바디 영역의 제 1 부분과 상기 게이트 영역의 제 1 부분 사이에 위치한 소스 영역;

상기 소스 영역과 상기 게이트 영역의 상기 제 1 부분 사이, 상기 바디 영역의 제 2 부분과 상기 게이트 영역의 제 2 부분 사이 및 상기 제 1 드레인 영역의 제 1 부분과 상기 게이트 영역의 제 3 부분 사이에 위치하는 이산화 실리콘층(상기 이산화 실리콘층은 제 1 두께를 가진다); 및

PSG 및 BPSG를 구성하는 물질의 그룹에서 선택되며, 상기 제 1 드레인 영역의 제 2 부분과 상기 게이트 영역의 제 4 부분 사이에 위치하고, 상기 이산화 실리콘층과 연결되는 절연층(상기 절연층은 상기 제 1 두께보다 큰 제 2 두께를 가진다); 을 포함하는 MIS 장치.

## 청구항 53.

제 52 항에 있어서,

상기 제 1 드레인 영역은 낮게 n-도핑된 반도체를 포함하는 MIS 장치.

## 청구항 54.

제 53 항에 있어서,

상기 바디 영역은 p-도핑된 반도체를 포함하는 MIS 장치.

## 청구항 55.

제 54 항에 있어서,

상기 소스 영역은 높게 n-도핑된 반도체를 포함하는 MIS 장치.

## 청구항 56.

제 55 항에 있어서,

상기 제 1 드레인 영역 하에 위치한 제 2 드레인 영역을 더 포함하는 MIS 장치.

## 청구항 57.

제 56 항에 있어서,

상기 제 2 드레인 영역은 높게 n-도핑된 반도체를 포함하는 MIS 장치.

### 청구항 58.

제 57 항에 있어서,

상기 게이트 영역은 폴리실리콘을 포함하는 MIS 장치.

### 청구항 59.

제 58 항에 있어서,

상기 게이트 영역의 제 4 부분과 인접하는 상기 제 1 드레인 영역에 위치한 n-도핑된 반도체 영역을 더 포함하는 MIS 장치.

### 청구항 60.

제 41 항 또는 제 52 항에 있어서,

상기 절연층의 두께는 약  $0.1 - 0.3\mu\text{m}$  범위인 MIS 장치.

### 청구항 61.

제 41 항 또는 제 52 항에 있어서,

상기 절연 영역은 상기 드레인 영역에 실질적인 스트레스를 형성하지 않는 MIS 장치.

### 청구항 62.

제 41 항 또는 제 52 항에 있어서,

상기 이산화 실리콘층의 두께는  $100 - 1000\text{\AA}$  범위인 MIS 장치.

도면

## 도면1

## 도면2

도면3

도면4A

도면4B

도면4C

도면4D

도면4E

도면4F

도면4G

도면4H

도면4I

도면4J

도면4K

도면5