(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-246116

(P2010-246116A)

(43) 公開日 平成22年10月28日(2010.10.28)

(51) Int.Cl.

H03L 7/093 (2006.01)

H03K 17/06 (2006.01)

F 1

H03L 7/08

H03K 17/06

テーマコード(参考)

E 5J055

A 5J106

審査請求 未請求 請求項の数 3 O L 外国語出願 (全 12 頁)

(21) 出願番号 特願2010-81117(P2010-81117)

(22) 出願日 平成22年3月31日(2010.3.31)

(31) 優先権主張番号 12/416,679

(32) 優先日 平成21年4月1日(2009.4.1)

(33) 優先権主張国 米国(US)

(71) 出願人 500575824

ハネウェル・インターナショナル・インコ

ーポレーテッド

アメリカ合衆国ニュージャージー州O79

62-2245, モーリスタウン, コロン

ピア・ロード 101, ピー・オー・ボッ

クス 2245

(74) 代理人 100140109

弁理士 小野 新次郎

(74) 代理人 100089705

弁理士 社本 一夫

(74) 代理人 100075270

弁理士 小林 泰

(74) 代理人 100080137

弁理士 千葉 昭男

最終頁に続く

(54) 【発明の名称】放射線硬化チャージポンプ・トポロジ

(57) 【要約】 (修正有)

【課題】シングル・イベント・アップセット(SEUs)により影響されにくいチャージポンプ回路を提供する。

【解決手段】第1のチャージポンプ出力を備えた第1のチャージポンプ30と、第2のチャージポンプ出力を備えた第2のチャージポンプ32と、前記第1のチャージポンプ出力及び前記第2のチャージポンプ出力を入力するよう受け取り、第1の一致信号を出力するように生成する第1の一致検出器34と、第1の一致信号に基づいて、前記第1のチャージポンプ出力、または、前記第2のチャージポンプ出力のいずれかを選択するためのアナログ2:1マルチブレクサ36とを有する。

【選択図】図2

## 【特許請求の範囲】

## 【請求項 1】

第1のチャージポンプ出力を備えた第1のチャージポンプと、

第2のチャージポンプ出力を備えた第2のチャージポンプと、

前記第1のチャージポンプ出力及び前記第2のチャージポンプ出力を入力するように受け取り、第1の一一致信号を出力するように生成する第1の一一致検出器と、

第1の一一致信号に基づいて、前記第1のチャージポンプ出力、または、前記第2のチャージポンプ出力のいずれかを選択するためのアナログ2：1マルチプレクサと、

を有することを特徴とする放射線硬化チャージポンプ回路。

## 【請求項 2】

第3のチャージポンプ出力を備える第3のチャージポンプと、

前記第2のチャージポンプ出力及び前記第3のチャージポンプ出力を入力するように受け取り、第2の一一致信号を出力するように生成する第2の一一致検出器と、

前記第1の一一致信号と前記第2の一一致信号とを入力として受け取り、前記第1の一一致信号および前記第2の一一致信号に基づいて選択信号を出力するように生成する決定ロジックと、

を更に有し、

前記アナログ2：1マルチプレクサが、前記第1の一一致信号ではなく前記選択信号に基づいて、前記第1のチャージポンプ出力か前記第2のチャージポンプ出力のいずれかを選択することを特徴とする、請求項1に記載の回路。

## 【請求項 3】

第1のフィードバック・クロック信号を生成する第1の電圧制御発振器と、

第2のフィードバック・クロック信号を生成する第2の電圧制御発振器と、

基準クロック信号および前記第1のフィードバック・クロック信号を入力するように受信し、前記第1のチャージポンプに出力するように生成する第1の位相周波数ディテクタと、

前記基準クロック信号及び第2のフィードバック・クロック信号を入力するように受信し、前記第2のチャージポンプに出力するように生成する第2の位相周波数ディテクタと、

前記第1のチャージポンプ出力をフィルタリングするための第1のループ・フィルタと、

前記第2のチャージポンプ出力をフィルタリングし、それにより、放射線硬化位相ロック・ループを生じさせる第2のループ・フィルタと、

を更に有することを特徴とする請求項1に記載の回路。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、放射線硬化に関し、より詳しくは、放射線硬化チャージポンプ・トポロジに関する。

## 【背景技術】

## 【0002】

チャージポンプは、ソース電圧より高いか又は低い電圧レベルを提供するために、位相ロック・ループ(PLL)、遅延ロック・ループ(DLL)、電圧調整器および他の用途に用いられる。これを行うため、チャージポンプは典型的には、交流電源と組み合わせた一つ以上のコンデンサと、一つ以上コンデンサにストアした電荷を加算(又は減算)するためのスイッチング機構とを組み込み、かくして、結果として容量および格納された電荷の量に関連したカスタマイズされた出力電圧となる。

## 【0003】

しかし、チャージポンプはシングル・イベント・アップセット(SEUs)のような放射線イベントに影響されやすい。これらのイベントは、チャージポンプ出力を大きく崩壊させ

10

20

30

40

50

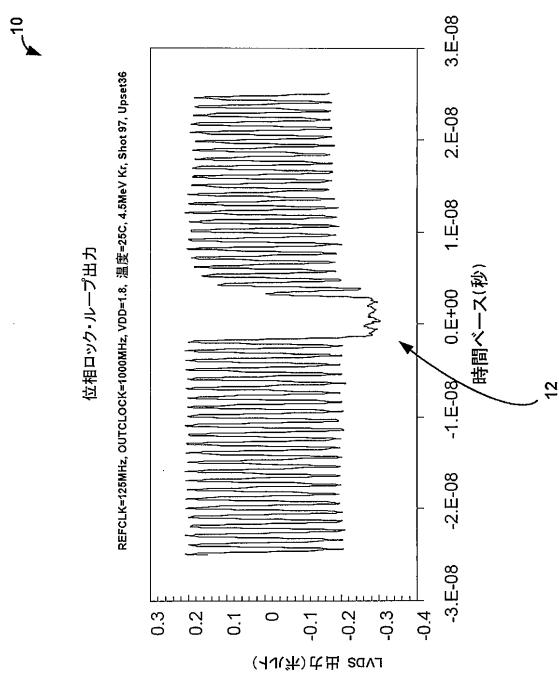

ることができ、順番にチャージポンプが存在するシステムを崩壊させることができる。例えば、図1は、チャージポンプが放射線イベントを経験するときに、位相ロック・ループにおいて、観察されるかもしれない一種の妨害12を例示している差動出力電圧グラフ10である。間隔を隔てたベースの電子機器のようなアプリケーションおよびその他の高い信頼性を必要としているものに関して、SEUsにより影響されやすくないチャージポンプ・トポロジが望ましい。

【発明の概要】

【課題を解決するための手段】

【0004】

放射線硬化チャージポンプ回路を提供する。該回路は、第1のチャージポンプ出力を備えた第1のチャージポンプと、第2のチャージポンプ出力を備えた第2のチャージポンプと、前記第1のチャージポンプ出力及び前記第2のチャージポンプ出力を入力するよう受け取り、第1の一一致信号を出力するように生成する第1の一一致検出器と、第1の一一致信号に基づいて、前記第1のチャージポンプ出力、または、前記第2のチャージポンプ出力のいずれかを選択するためのアナログ2：1マルチブレクサと、を有することを特徴とする。別の実施形態では、回路は、少なくとも3つのチャージポンプと、少なくとも2つの一致検出器と、決定ロジックと、対応する大きさのアナログ・マルチブレクサとを含む。

【0005】

このチャージポンプ・トポロジは、SEUsに対してより影響されにくく、また、回路の活動寿命中または最初のいずれかで、(後述するように)位相周波数ディテクタ/チャージポンプ回路の失敗を比較するのに用いられ得る。

【図面の簡単な説明】

【0006】

【図1】図1は、位相ロック・ループにおいて、観察されうる一種の妨害を例示するグラフである。

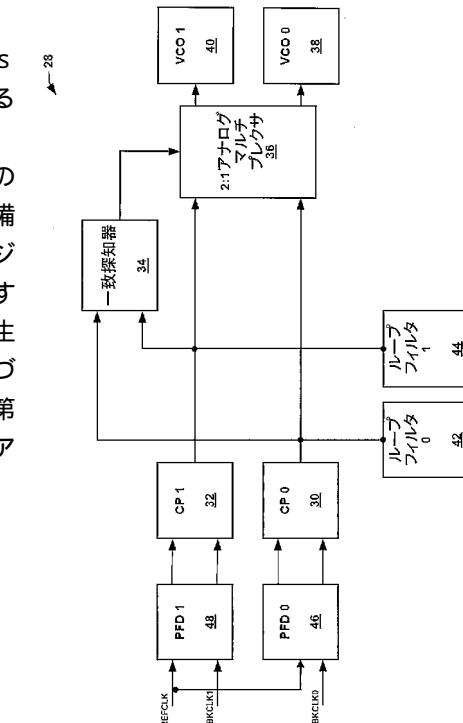

【図2】図2は、本発明の第1実施形態による、位相ロック・ループ回路において実装されるような、例示の放射線硬化チャージポンプ・トポロジを図示する簡略ブロック図である。

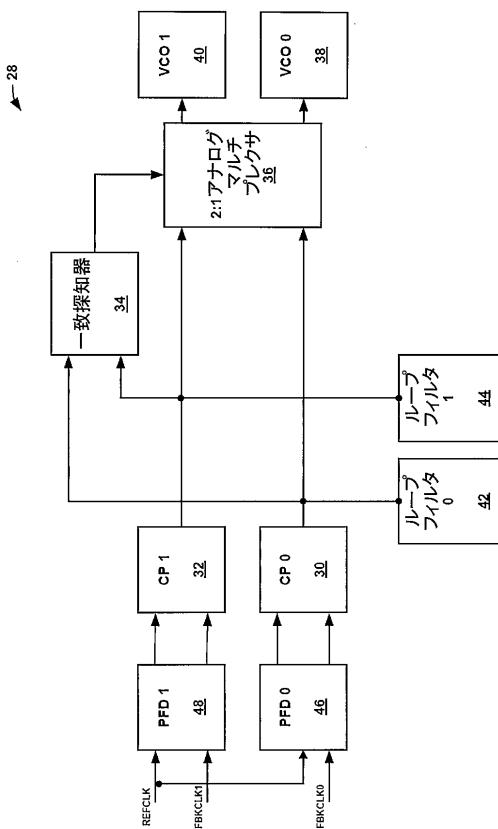

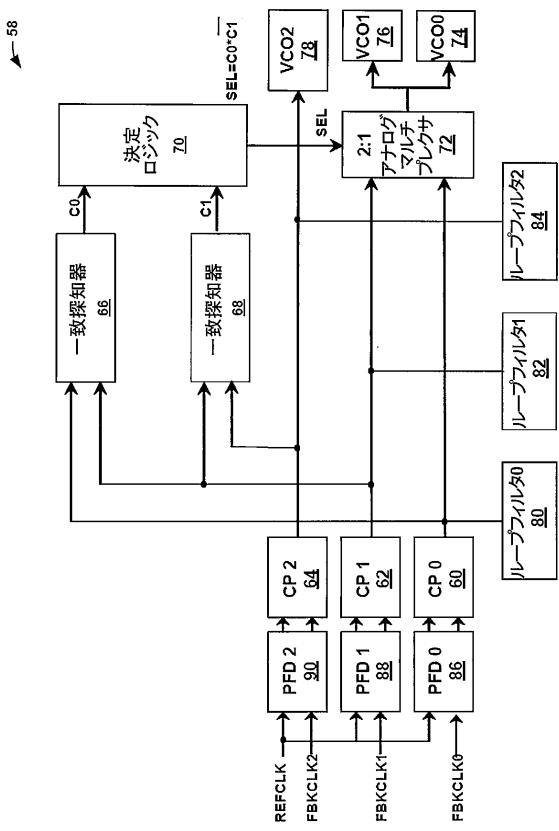

【図3】図3は、本発明の第2の実施形態による、別の位相ロック・ループ回路において、実装されるような、例示の放射線硬化チャージポンプ・トポロジを図示する簡略ブロック図である。

【図4】図4は、可調閾値を有する信号一致検出回路の簡略ブロック図である。

【図5】図5は、可調閾値を有する信号一致検出回路の更に詳細に、簡略化したスキーム/ブロック線図である。

【発明を実施するための形態】

【0007】

図2は、本発明の第1実施形態による、位相ロック・ループ(PLL)回路において、実装されるような、放射線硬化チャージポンプ・トポロジ28を例示する簡略ブロック図である。トポロジ28は、一致探知器34およびアナログ2：1マルチブレクサ36への出力を各々提供している第1および第2のチャージポンプ30および32を含む。一致探知器34は、チャージポンプ30および32の出力が一致するか(すなわち、互いの規定済みの許容範囲内か)どうか、対応するアナログ・マルチブレクサ36への出力を提供するアナログ・コンパレータである。一致探知器34から出るこの出力に基づいて、アナログ・マルチブレクサ36は、の出力一つは、電圧制御発振器(VCO)38および40に2の信号のうちの1つを出力する。これらのVCO 38および40は、出力(例えば、OUTCLK0およびOUTCLK1)として役立ち、更に、位相周波数ディテクタ(PFD)46および48にフィードバック・クロック信号(FBKCLK0およびFBKCLK1)を提供し、基準クロック信号REFCLKと一緒に、クロック信号が同調しているかどうか判断するためにPFD 46および48によって用いられる。ノイズを取り除くためのループ・フィルタ42および44は、第1および第2のチャージポンプ30および32の出力にそれぞれ接続している。

10

20

30

40

50

## 【0008】

チャージポンプ・トポロジ28は、放射線イベントにより影響されやすくないように設計されている。例えば、SEUストライキがチャージポンプ30または32の一つで起こる場合、イベントの効果が減弱するまで、チャージポンプ・トポロジ28は、そのSEUストライキを検出して、チャージポンプ30および32とループ・フィルタ42および44との間の結合を不能にすることが可能である。一致探知器34は、SEUストライキが、お互いの規定済みの許容（一致バンド）にあるかどうか判断するために、チャージポンプ30および32の出力を比較することによって、チャージポンプ30および32の一つで起こりやすいかどうか判断する。チャージポンプ30および32の出力が一致バンドの範囲内でない場合、一致探知器はその出来事にフラグを立てる。対応するループ・フィルタに送られたチャージは、シャント・オフされる。SEUイベントが消える（1ナノ秒未満のオーダー）まで、ループ・フィルタ42および44の各々は、少なくともその電圧を維持でき、チャージポンプ30および32の出力は、再び一致バンドの範囲内にある。したがって、ループは解錠されないかまたは中断せず、あたかも何も起こらないかのように、システムは作動し続ける。別の実施形態では、SEUストライキが静まるまで、ループ・フィルタの電圧は、変化せずにチャージポンプにインテリジェンスに続いたようにループ・フィルタ電圧を利用することができる。10

## 【0009】

PLLアプリケーションに関する好ましい実施形態では、各々のチャージポンプ30および32は、約3uAのスイッチ交流源として実装され、コンデンサは、コンデンサ（例えば、0.5pF）と並列の組合せで、レジスタ（例えば、150pFコンデンサおよび20kΩレジスタ）と直列である。20

## 別の位相ロック・ループ回路の実施

本発明の第2の実施形態によれば、図3は、別の位相ロック・ループ回路において実装されるような、放射線硬化チャージポンプ・トポロジを例示するブロック図である。

## 【0010】

この別の実施形態における放射線硬化チャージポンプ・トポロジ58では、回路デザインは、第1のチャージポンプ60、第2のチャージポンプ62および第3チャージポンプ64を含む。チャージポンプ60、62、64の出力は、ノイズ信号干渉を減らすのに役立つ第1のループ・フィルタ80、第2のループ・フィルタ82および第3のループ・フィルタ84にそれぞれ接続している。この第2の実施形態は、チャージポンプ60、62、64から出力を受け取るための第2の一致探知器68と同様に、第1の一致探知器66を含む。第1の一致探知器66は、第1のチャージポンプ60からの信号が、第2のチャージポンプ62から信号と一致するとき、高い信号を出力するアナログ・コンパレータである。第2の一致探知器68は、第2のチャージポンプ62からの信号が、第3のチャージポンプ64からの信号と一致するとき、高い信号を出力するアナログ・コンパレータである。第1および第2の一致探知器66および68からの出力信号C0およびC1は、決定ロジック70へ送られ、該決定ロジック70は、ハードウェア、ソフトウェア、または、ハードウェアとソフトウェアとの組合せとして実行される。決定ロジック70から、出力信号SELは、アナログ2:1マルチプレクサ72に送信される。SELに関する信号の値を判断するロジックテーブルが表1に見うけられる。30

## 【0011】

【表1】

表 1.  $SEL = C0 * \overline{C1}$

| C0 | C1 | SEL |

|----|----|-----|

| 0  | 0  | 0   |

| 0  | 1  | 0   |

| 1  | 0  | 1   |

| 1  | 1  | 0   |

10

【0012】

アナログ2:1マルチプレクサ72は、第1のチャージポンプ60および第2のチャージポンプ62の出力信号からその2つの入力信号を受信する。アナログの2:1マルチプレクサ72は、2つのチャージポンプ60、62からの信号がその出力であるように選択するのにSEL信号を使用する。アナログ2:1マルチプレクサ72からの出力が、信号値がVCO 74および76に送られたと決定する。第1および第2のVCO 74、76と異なって、第3のVCO 78は、第3のチャージポンプ64の出力から、常にその信号を受信する。VCO 74、76、78の各々は、対応する第1のPFD86、第2のPFD 88および第3のPFD 90に戻るようなループであるそれぞれのフィードバック・クロック信号FBKCLK0、FBKCLK1、FBKCLK2を提供する。各々のフィードバック・クロック信号FBKCLK0、FBKCLK1、FBKCLK2は、2つのクロック信号が同調しているかどうかを判断するように、PFD 86、88、90で、基準クロックREFCLKと比較される。

20

【0013】

第2のチャージポンプ62および第3のチャージポンプ64からの出力は、目的を投票するように用いられるように設計されている。上の表1に示すように、SEL信号は、大部分の状況における、アナログ2:1マルチプレクサの出力として第1のチャージポンプ60信号を選択する。SEL信号が、アナログ2:1マルチプレクサ72に関する異なる出力を選択する唯一の時は、SEUストライキが第3のチャージポンプ64で起こる時である。このシナリオでは、SEUストライキによって、第3のチャージポンプ64で電圧妨害が生じ、第1の一致探知器66は電圧妨害を感知せず、第2の一一致探知器68も同様である。このシナリオだけで、決定ロジック70は、SEL信号高さをセットし、アナログ2:1マルチプレクサ72によって、その出力として第2のチャージポンプ62信号を選択させる。

30

【0014】

チャージポンプ・トポロジ58は、ループ回路に干渉することから電圧妨害が生じることがありえる放射線イベントに、より影響されやすくないように設計されている。チャージポンプからの入力が一致のままの限り、一致探知器66および68から出る出力は高いままである。しかし、SEUストライキのような放射線イベントが、チャージポンプ60、62、64のうちの1つに起こるときに、電圧障害はそのチャージポンプで引き起こされる。対応する一致探知器66、68は、互いに一致しないチャージポンプ入力を検出することによって、SEUストライキの発生のフラグを立てる。チャージポンプ・トポロジ58が、SEUストライキを検出するとき、それはチャージポンプ60、62、64およびその対応するループ・フィルタ80、82、84との間の結合を不能にする。少なくともSEUイベントが消える(1ナノ秒未満のオーダー)まで、各々のループ・フィルタ80、82、84は、その電圧を維持でき、チャージポンプ60、62、64の出力はもう一度一致バンドの範囲内にある。この方法では、ループが解錠されないか、または、回路周辺の電圧妨害によって中断せず、あたかも何も起こらないかのように、システムは作動し続ける。別の実施形態では、SEUストライキが静まるまで

40

50

、ループ・フィルタの電圧は、ごく自然なチャージポンプ信号にインテリジェンスに続くようにループ・フィルタ電圧を利用することができます。

#### 【0015】

PLLアプリケーションに関する好ましい実施形態では、各々のチャージポンプ30および32は、約3uAのスイッチ交流源として実装され、コンデンサ（例えば、0.5pF）と並列に組合せ、レジスタ（例えば、150pFコンデンサおよび20kレジスタ）と直列のコンデンサである。

#### 【0016】

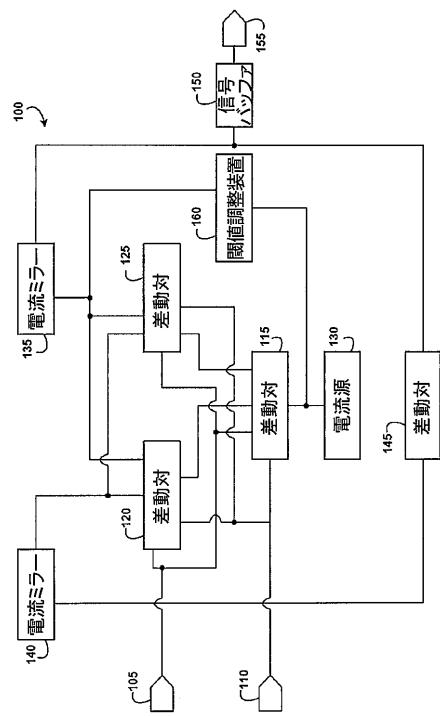

### 可調閾値を有する信号一回路

図4を参照すると、例示の信号一致検出回路100を図示するブロック図が示されている。この回路は、ハネウェル・インターナショナル社に譲受されている米国特許第7,279,909号の更なる詳細に記載されている。回路100は、第1の入力信号端子105および第2の入力信号端子110を含む。入力信号端子105,110は、第1の差動のトランジスタ対115、第2の差動のトランジスタ対120および第3の差動のトランジスタ対125に連結する。作動中、第1の入力信号端末105は第1の入力信号を受信する。そして、第2の入力信号端末110は第2の入力信号を受信する。信号一致検出回路100は、第1および第2の入力信号が一致するか否かを判断する。

#### 【0017】

第1および第2の入力信号が一致するかどうか判断するために、第1および第2の入力信号は、入力信号端子105,110から第1、第2、第3の差動対115,120,125に伝達される。一致に関して第1および第2の入力信号を比較する際に、第1のテール電流は、電流源130によって、第1の差動対115に提供される。次に、第1の差動対115は、第3の差動のトランジスタ対125（例えば、第二トランジスタを介して）に、第2の差動のトランジスタ対120（例えば、第1のトランジスタを介して）および第3のテール電流に第2のテール電流を提供する。第2および第3のテール電流は、第1および第2の入力信号に基づく。

#### 【0018】

第2および第3の差動対120,125は、第1および第2の入力信号に基づく複数の電流を（第2および第3のテール電流から）生成する。回路100に関して、第2および第3の差動のトランジスタ対120,125によって、生成された電流は、2つの結合された電流を生成するように結合される。結合された電流を生成させるために、第2および第3の差動のトランジスタ対120,125のトランジスタのそれぞれのドレイン端子は、お互いに連結する。

#### 【0019】

第1の結合された電流は、電流ミラー135に伝えられる。電流ミラー135は、回路100のプルアップ装置として作動する。第2の結合された電流は、電流ミラー140に伝えられる。電流ミラー140は、第2の結合された電流を反映させ、他の電流ミラー145にその反映する電流を伝える。電流ミラー145は、回路100のプルダウン装置として作動する。第1および第2の結合された電流は、次いで、信号バッファ150に（電流ミラー135,140,145を介して）連通される。

#### 【0020】

信号バッファ150は、第1および第2の結合された電流に基づいてデジタル信号を生成し、信号バッファ150によって生成されたデジタル信号は、第1および第2の入力信号が一致するか（例えば、一致のバンドの範囲内で）否かを示す。たとえば、信号バッファ150は、第1および第2の入力信号が一致することを示すロジック「1」信号を生成することができ、第1および第2の入力信号が一致しないことを示すためにロジック「0」信号を生成できる。もちろん、反対の場合もあってよく、ロジック「0」は入力信号が一致することを示し、ロジック「1」は入力信号が一致しないことを示してもよい。いうまでもなく、信号バッファ150は、いかなる数の形式になることもできる。例えば、信号バッファ150は、インバータとして、あるいは、16進法バッファとして実装されることができる。信号バッファ150によって生成されたデジタル信号は、次いで、出力信号端子155を介して

通信された他の回路であってもよい。

【0021】

信号一致検出回路100は、更に、閾値調整装置160含む。閾値調整装置160は、第2および第3の差動対および電流ミラー135に連結する。回路100において、閾値調整装置160は、電流「ステアリング(steering)」装置として作用する。電流は、閾値電圧を閾値調整装置160に印加することによって、(差動のトランジスタ対115,120,125を介して)電流源115から「進められる」。

【0022】

この種のアプローチにおいて、閾値調整装置160は、差動のトランジスタ対115,120,125と並列に連結されるn型電界効果トランジスタ(FET)という形態をとることができ、FETのソース端子は電流源に連結し、FETのドレイン端子は第2および第3の差動対および電流ミラー135に連結する。更に、閾値電圧は、FETのゲート端子に印加される。

10

【0023】

この種の回路において、第1および第2の入力信号が閾値調整装置160に印加される閾値電圧で、または、下にある電圧振幅を有するときに、(そして、差動のトランジスタ対115,120,125で通信した)電流源130によって、生成された電流は(そして、電流ミラー135から間隔をあいて配置される)閾値調整装置160を介して「進められる」。しかし、印加閾値電圧より大きい電圧振幅を有する入力信号に関して、電流の比較的少ない分だけは、閾値調整装置160を介して「進められる」。閾値調整装置160を介して「進められ」ない電流の一部は、電流ミラー135に、そして、次に、信号バッファ150に伝えられる。それらの入力信号の電圧振幅が、閾値電圧を上回る第1および第2の入力信号の一致を示しているだけの回路100のこの電流「進行(steering)」結果は、閾値調整装置160(例えば閾値調整手段160を実装するために用いるn型FETの入口に印加される電圧)にあてはまる。

20

【0024】

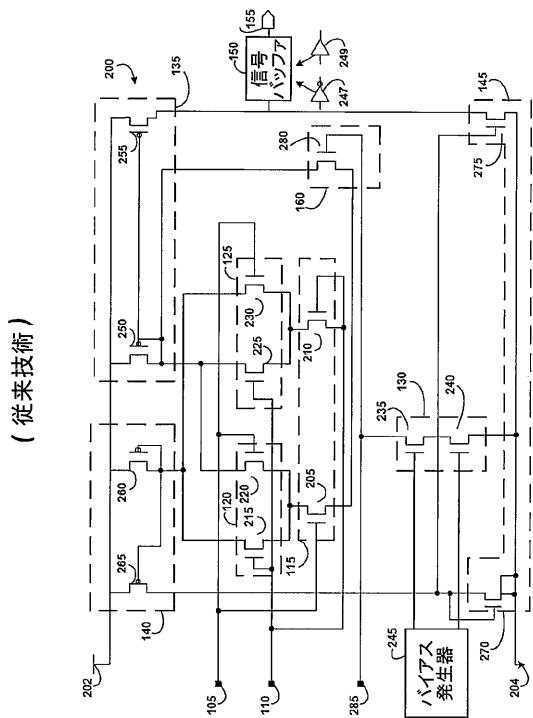

図5を参照すると、更に詳細に、信号一致検出回路200を例示しているブロック線図が示される。回路200は、回路200の構成要素に、適当な電力供給電圧を通信するのに使われる電力供給端末202を含む。同様に、回路200も回路200の構成要素の地上参照を提供する電気アース端子204を含む。回路200において、第1の差動トランジスタ対115は、第1のn型FET 205および第2のn型FET 210を含む。FET 205,210のソース端子は、互いに連結する。第2の差動対120は、第1のn型FET 215および第2のn型FET 220を含み、FET 215,220のソース端子は、互いに連結する。同様に、第3の差動トランジスタ対125は、第1のn型FET 225および第2のn型FET 230を含み、FET 225,230のソース端子は、互いに連結する。

30

【0025】

第1の差動対115のFET 205のドレイン端子は、第2の差動対120のFET 215,220のソース端子に連結して、上述したように、第2の差動対120に、テール電流を印加する。同様に、第1の差動対115のFET 210のドレイン端子は、第3の差動対125のFET 225,230のソース端子に連結して、第3の差動対125に、テール電流を印加する。

【0026】

図5に示すように、差動対115,120,125のそれぞれのFETのソース端子は、直接互いに連結する。かかる実施形態では、(上述したような)回路200に関する一致のバンドは、差動対115,120,125のFETのサイズを調整することによって決められる。他の実施形態では、一致バンドは、また、抵抗減衰(resistive degeneration)と呼ばれる技術を使用して決められることが可能である。かかるアプローチでは、各々に直接各々の差動対115,120,125のそれぞれのFETのソース端子を連結するよりはむしろ、レジスタはソース端子の間に挿入される。かかるアプローチは、一致バンドの「チューニング」を許容し、更に信号一致検出回路の線形を増大させる。しかしながら、抵抗減衰は、かかる信号一致検出回路のゲインの減少となる。したがって、一致バンドを確立するために使用される特定の方法は、特定の信号一致検出回路の意図された使用に依存する。

40

【0027】

回路200の電流源130は、第1のn型FET 235および第2のn型FET 240を含む。FET 235,2

50

40が、差動対115のFET 205および210のソース端子に連結しているFET 235のドレインとスタックされた配置に連結される。FET 235のソース端子は、FET 240のドレイン端子に連結し、FET 240のソース端子はグランドリファレンス端末204に連結する。電流源130のFET 235,240のゲート端子は、バイアス発生器245に連結し、それは電流源130に2本の直流電圧バイアスを提供する。電流源130は、バイアス発生器245に提供される「ミラー」電流リファレンスに、これらの電圧バイアスを使用する。バイアス発生器245は、いかなる数の形式をとることができうる。たとえば、バイアス発生装置は、カスコードされたバイアス発生器として実装されることができる。

#### 【0028】

図5に示されるように、そして、上述したように、信号バッファ150はインバータ247として実装されることができる。別の実施形態では、信号バッファ150は、16進法バッファ249として実装され得る。他の可能性も、存在する。たとえば、信号バッファ150は、一連のインバータまたは16進法バッファとして実装されることができる。かかるアプローチが、単一のインバータまたは16進法バッファの使用と比較して、更なるノイズ免除を提供できることはいうまでもない。

10

#### 【0029】

回路200において、第2の差動対120の第2のFET 220および第3の差動対の第1のFET 225のドレイン端子は、互いに連結する。FET 220,225のドレイン端子は更に、電流ミラー135に連結し、それは回路200のプルアップ装置として作用する。FET 220,225のドレイン端子が互いに連結するので、FET 220,225によって生成された電流は結合され、電流ミラー135へ通信される（閾値可調装置160がオフである仮定する）。

20

#### 【0030】

電流ミラー135は、第1のp型FET 250および第2のp型FET 255を含む。FET 220,225からの結合された電流は、FET 250に伝えられる。結合された電流は、次いで、FET 255によってミラーリングされ、ミラーリングされた電流は信号バッファ150に通信される。

#### 【0031】

また、回路200で、第2の差動対120の第1のFET 215、および、第3の差動対125の第2のFET 230のドレイン端子は、FET 215,230が第2の結合された電流を生成するように互いに連結する。第2の結合された電流は、電流ミラー140に伝えられる。電流ミラー140は、第1のp型FET 260および第2のp型FET 265を含む。第2の結合された電流は、FET 260に伝えられる。第2の結合された電流は次いで、FET 265によって、ミラーリングされ、電流ミラー145へ通信し、それは回路200のプルダウン装置として作用する。

30

#### 【0032】

電流ミラー145は、第1のn型FET 270および第2のn型FET 275を含む。電流ミラー140からミラーリングされた電流は、回路200のダイオードとして作動するトランジスタ270に連通される。次いで、電流は、FET 275によってミラーリングされ、信号バッファ150へ通信される。信号バッファ150は、FET 255,275によって、それに伝えられる電流に基づいて、デジタル信号を生成する。このデジタル信号は、回路200の入力信号端子105,110に適用される第1および第2の入力信号が一致するか否か、指示示す。回路200の信号バッファ150がインバータとして実装される場合、第1および第2の入力信号が一致するときに、回路200によって、生成されたデジタル信号はロジック「1」であり、入力信号が一致しないとき、デジタル信号はロジック「0」である。

40

#### 【0033】

図5に示すように、回路200に関する閾値電圧を確立するとき、閾値調整手段160は、n型FET 280として実装され、それは、電流ステアリング装置として作用する。閾値電圧は、閾値電圧入力ターミナル285介してFET 280のゲート端子に印加される。0V以外の閾値電圧が、閾値電圧入力ターミナル285に印加されるとき、入力信号端子105,110に適用される入力信号の振幅が閾値電圧以下であるとき、FET 235,240によって生成された結合された電流は、上述したようにFET 280で「進められる（ステアリングされる）」。上述したように、入力信号の振幅が閾値電圧よりも大きいとき、FET 235,240の結合された電流の比

50

較的小さい部分だけが、FET 280を介して「進められる（ステアリングされる）」。残りの部分は、電流ミラー135を介して信号バッファ150に伝えられ、第1および第2の入力信号の一一致を示すためにデジタル信号を生成するのに用いられる。

## 【0034】

## まとめ

上記したチャージポンプ・トポロジは、例えば位相ロック・ループのコンテキストにあり、トポロジはまた、SEUsに影響されやすいアプリケーションのためのチャージポンプを使用する他の回路において利用され得る。例えば、チャージポンプ・トポロジはまた、遅延ロック・ループ（DLL）、電圧調整器、および、さもなければSEUsによって崩壊するかもしれない他のアプリケーションにおいて用いられる。

10

【図1】

【図2】

【図3】

【 四 4 】

【図5】

---

フロントページの続き

(74)代理人 100096013

弁理士 富田 博行

(74)代理人 100147681

弁理士 夫馬 直樹

(72)発明者 ブラッドリー・エイ・カンター

アメリカ合衆国ミネソタ州 55442, プリマス, フォーティエイス・プレイス・ノース 116

25

(72)発明者 ジェームズ・ディー・シーフェルト

アメリカ合衆国ニュージャージー州 07962-2245, モーリスタウン, コロンビア・ロード

101, ピー・オー・ボックス 2245, ハネウェル・インターナショナル・インコーポレー

テッド, パテント・サーヴィシーズ エム/エス エイビー/2ビー

F ターム(参考) 5J055 AX23 BX16 EZ08 EZ13 EZ55 FX05 GX02

5J106 AA04 CC02 CC30 CC41 DD06 DD09 DD46 EE07 FF09 GG15

HH10 JJ08 KK12

【外國語明細書】

2010246116000001.pdf