(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4438067号

(P4438067)

(45) 発行日 平成22年3月24日(2010.3.24)

(24) 登録日 平成22年1月15日(2010.1.15)

(51) Int.Cl.

F 1

|             |              |                  |      |      |         |

|-------------|--------------|------------------|------|------|---------|

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | G09G | 3/30 | J       |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/30 | K       |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 1 2 E |

|             |              |                  | G09G | 3/20 | 6 2 3 B |

|             |              |                  | G09G | 3/20 | 6 2 4 B |

請求項の数 4 (全 8 頁) 最終頁に続く

(21) 出願番号

特願2004-342129 (P2004-342129)

(22) 出願日

平成16年11月26日(2004.11.26)

(65) 公開番号

特開2006-154067 (P2006-154067A)

(43) 公開日

平成18年6月15日(2006.6.15)

審査請求日

平成19年11月26日(2007.11.26)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090538

弁理士 西山 恵三

(74) 代理人 100096965

弁理士 内尾 裕一

(72) 発明者 山下 孝教

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

(72) 発明者 井関 正己

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

最終頁に続く

(54) 【発明の名称】アクティブマトリクス型表示装置およびその電流プログラミング方法

## (57) 【特許請求の範囲】

## 【請求項 1】

電流駆動型表示素子を含む複数の画素回路がマトリクス状に配列された画素回路部と、前記複数の画素回路の列ごとに設けられ、データ電流が供給される複数のデータ線と、前記データ電流が供給される前記画素回路を行ごとに選択する信号が供給される複数の走査線と、

表示に係わらない基準電流によって、記憶電流駆動型表示素子が黒表示するときに前記データ線に供給される電流を減らす所定電流を供給可能な状態に設定され、前記データ線に供給する、前記データ線ごとに設けられた複数の電流設定回路と、

前記画素回路部と前記複数の電流設定回路との間に、前記データ線ごとに設けられた複数のスイッチと、

を備えるアクティブマトリクス型表示装置であって、

前記スイッチにより前記画素回路部を切り離して前記電流設定回路に前記所定電流を設定し、その後、前記スイッチにより前記画素回路部と前記電流設定回路とを接続して前記データ電流と前記所定電流とを前記データ線に供給するアクティブマトリクス型表示装置。

## 【請求項 2】

請求項1に記載のアクティブマトリクス型表示装置において、前記基準電流は、前記画素回路を用いて前記電流駆動型表示素子が黒表示に設定されるときに前記データ線に流れれる電流と同じ値の電流であるアクティブマトリクス型表示装置。

**【請求項 3】**

請求項 2 に記載のアクティブマトリクス型表示装置において、前記電流駆動型表示素子はエレクトロルミネッセンス素子であることを特徴とするアクティブマトリクス型表示装置。

**【請求項 4】**

電流駆動型表示素子を含む複数の画素回路がマトリクス状に配列された画素回路部と、前記複数の画素回路の列ごとに設けられ、データ電流が供給される複数のデータ線と、前記データ電流が供給される前記画素回路を行ごとに選択する信号が供給される複数の走査線と、

表示に係わらない基準電流によって、記電流駆動型表示素子が黒表示するときに前記データ線に供給される電流を減らす所定電流を供給可能な状態に設定され、前記データ線に供給する、前記データ線ごとに設けられた複数の電流設定回路と、

前記画素回路部と前記複数の電流設定回路との間に、前記データ線ごとに設けられた複数のスイッチと、

を備えるアクティブマトリクス型表示装置の電流プログラミング方法であって、

前記スイッチにより前記画素回路部を切り離して前記電流設定回路に前記所定電流を設定し、その後、前記スイッチにより前記画素回路部と前記電流設定回路とを接続して前記データ電流と前記所定電流とを前記データ線に供給する電流プログラミング方法。

**【発明の詳細な説明】****【技術分野】**

20

**【0001】**

本発明はアクティブマトリクス型表示装置およびその電流プログラミング方法に係わり、特に電流駆動型表示素子に用いたアクティブマトリクス型表示装置に好適に用いられるものである。

**【背景技術】****【0002】**

データ線に流す電流を、トランジスタのゲート - ソース電圧として保持する電流プログラミング回路は、特許文献 1 の図 18 に示すように、電界発光素子を用いたアクティブマトリクス型表示装置の、電界発光素子駆動電流を書き込むための電流書き込み型画素回路に用いられている。また、特許文献 1 では高品位な黒および低輝度階調表示を可能するために、電流プログラミング回路を電流を書き込む電流駆動回路として設け、データ書き込みの際に書き込み電流を打ち消す方向に当該電流を流すことが記載されている。

**【特許文献 1】特開 2002-351400 号公報****【発明の開示】****【発明が解決しようとする課題】****【0003】**

本発明者は上記電流駆動回路を用いたときに、電流の書き込み動作を安定に行うことことができない場合があることを見出した。

**【0004】**

本発明は上記電流の書き込み動作を安定して行うことができるアクティブマトリクス型表示装置およびその電流プログラミング方法を提供することを目的とする。

**【課題を解決するための手段】****【0006】**

本発明のアクティブマトリクス型表示装置は、電流駆動型表示素子と、データ線に流される表示に係わる映像データ電流に基づく、該電流駆動型表示素子の駆動電流が書き込まれる駆動電流設定回路とをそれぞれ備えた、マトリクス状に配されてなる複数の画素回路と、

一方向に配列された複数の前記駆動電流設定回路がそれぞれ接続された複数の前記データ線と、

各データ線に少なくとも一つ接続され、前記データ線に流される表示に係わらない基準

30

40

50

電流に基づく電流が書き込まれる電流設定回路と、

前記電流設定回路と前記電流設定回路に隣接する前記駆動電流設定回路との間に配置され、その間で前記データ線の切り離し、接続を制御するスイッチと、

を備え、

前記スイッチは、前記基準電流に基づく電流を前記電流設定回路に書き込む際には前記データ線を切り離し、前記映像データ電流に基づき前記駆動電流を前記駆動電流設定回路に書き込む際には前記データ線の接続を行い、

前記スイッチにより前記データ線の接続を行うときに、前記電流設定回路は前記基準電流に基づく電流を前記データ線に流してなるアクティブマトリクス型表示装置である。

#### 【0008】

また本発明の電流プログラミング方法は、電流駆動型表示素子と、データ線に流される表示に係わる映像データ電流に基づく、該電流駆動型表示素子の駆動電流が書き込まれる駆動電流設定回路とをそれぞれ備えた、マトリクス状に配されてなる複数の画素回路と、

一方向に配列された複数の前記駆動電流設定回路がそれぞれ接続された複数の前記データ線と、

各データ線に少なくとも一つ接続され、前記データ線に流される表示に係わらない基準電流に基づく電流が書き込まれる電流設定回路と、

前記電流設定回路と前記電流設定回路に隣接する前記駆動電流設定回路との間に配置され、その間で前記データ線の切り離し、接続を制御するスイッチと、

を備えたアクティブマトリクス型表示装置の電流プログラミング方法であって、

前記スイッチにより前記データ線を切り離して、前記基準電流に基づく電流を前記電流設定回路に書き込み、

その後、前記スイッチにより前記データ線を接続し、前記電流設定回路により前記基準電流に基づく電流を前記データ線に流しつつ、前記映像データ電流に基づき前記駆動電流を前記駆動電流設定回路に書き込む電流プログラミング方法である。

#### 【発明の効果】

#### 【0009】

本発明によれば、データ線の寄生容量の影響を抑え、電流の書き込み動作を安定化させることができる。

#### 【発明を実施するための最良の形態】

#### 【0010】

以下、本発明の実施の形態について図面を用いて詳細に説明する。

#### 【0011】

(第1の実施形態)

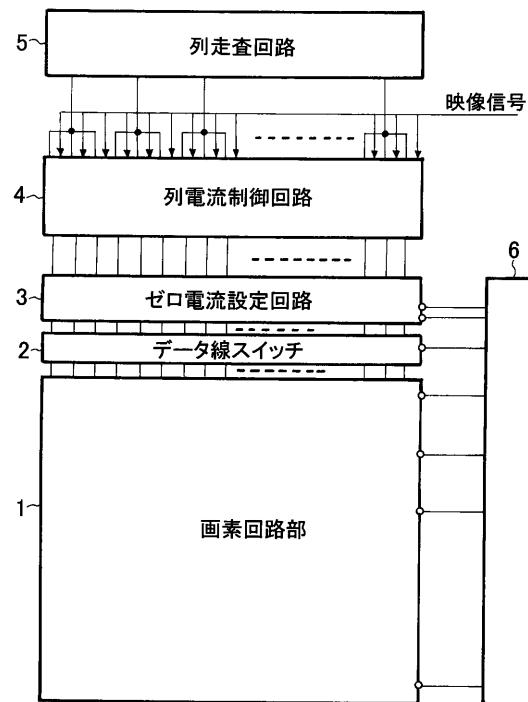

図3は本発明に係わるアクティブマトリクス電界発光表示装置の構成を示す構成図である。

#### 【0012】

図3において、1はマトリクス状に配された画素回路からなる画素回路部、2はデータ線の切り離し、接続を行うデータ線スイッチ、3はゼロ設定電流(基準電流)に基づく電流が書き込まれる画素回路列ごとに設けられたゼロ電流設定回路、4は列方向に配された画素回路群と接続されるデータ線に線順次データ線電流信号I<sub>data</sub>とゼロ設定電流を供給する列電流制御回路、5は列電流制御回路4に接続され、データ線に線順次データ線電流信号I<sub>data</sub>を与えるための列走査回路、6は行方向に配された画素回路に接続され、画素回路に行ごとに順次行走査信号P<sub>1m</sub>、行走査信号P<sub>2m</sub>を出力する行走査回路である(mは1以上の正の自然数)。

#### 【0013】

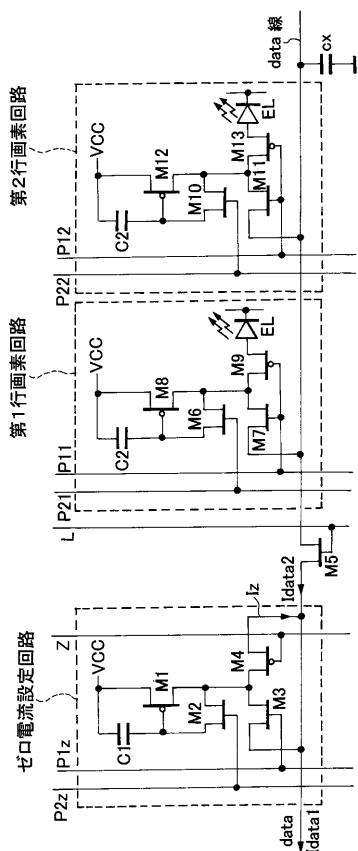

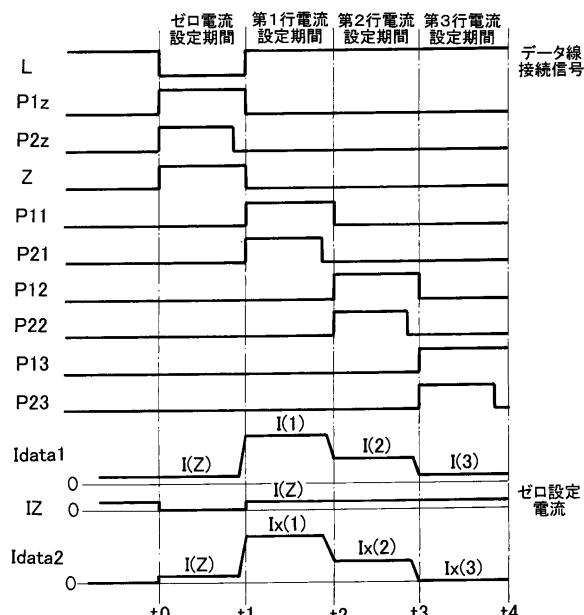

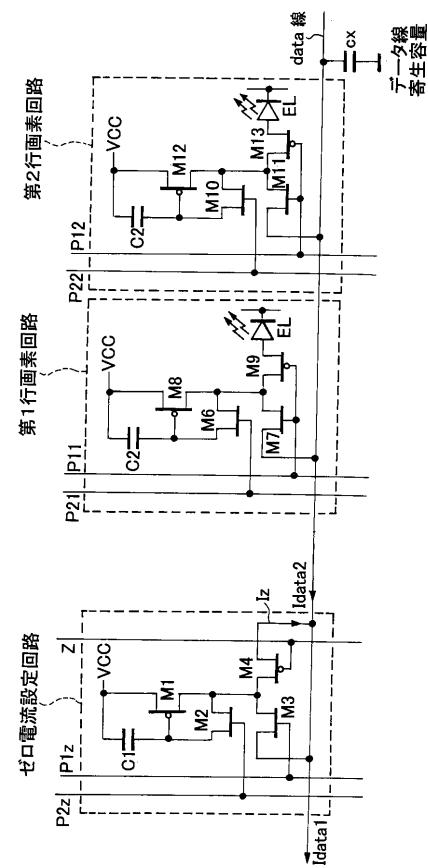

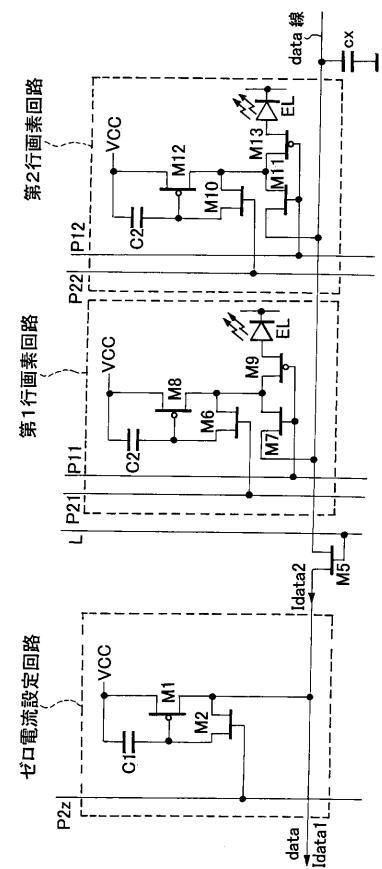

図1は本発明の第1の実施形態に係わる画素回路及びゼロ電流設定回路の一構成例を示す図である。図2は図1の画素回路及びゼロ電流設定回路の動作を説明するためのタイミングチャートである。図4は比較例の画素回路及びゼロ電流設定回路の構成を示す図である。

10

20

30

40

50

**【 0 0 1 4 】**

図 4 の比較例は図 1 に示した画素回路及びゼロ電流設定回路と基本構成は同じであり、本実施形態は図 4 の比較例に比べて、ゼロ電流設定回路と第 1 行画素回路との間にデータ線スイッチ M 5 を設けて、各画素回路が接続されるデータ線部分をゼロ電流設定回路と切り離し可能としている点が異なる。

**【 0 0 1 5 】**

まず、理解の容易化のためにデータ線スイッチを設けない比較例の構成と動作について図 2 及び図 3 を用いて説明する。

**【 0 0 1 6 】**

今、あるデータ線に接続される、第 1 行画素回路の動作を考えると、図 2 において、行走査信号 P 1 1 がハイレベルとなると、第 1 のプログラム（行選択）用スイッチとなる n MOS トランジスタ M 7 がオン、発光選択用スイッチとなる p MOS トランジスタ M 9 がオフする。また行走査信号 P 2 1 がハイレベルになると、第 2 のプログラム用スイッチとなる n MOS トランジスタ M 6 がオンする。そして、駆動用スイッチとなる p MOS トランジスタ M 8 のゲートに接続されている容量 C 2 の電圧は、データ線に流れる映像データ電流に基づき電界発光素子（エレクトロルミネッセンス素子）E L を駆動する電流が p MOS トランジスタ M 8 を介して流れるに十分なゲート - ソース電圧に設定される。次に、行走査信号 P 2 1 がロウレベルになると、第 2 のプログラム用スイッチとなる n MOS トランジスタ M 6 がオフし、容量 C 2 の電圧が保持される。これまでの期間が第 1 行電流設定期間（駆動電流プログラミング期間）である。

10

20

**【 0 0 1 7 】**

その後、行走査信号 P 1 1 がロウレベルになると、第 1 のプログラム（行選択）用スイッチとなる n MOS トランジスタ M 7 がオフ、発光選択用スイッチとなる p MOS トランジスタ M 9 がオンする。駆動用トランジスタ M 8 のゲート電位により電界発光素子 E L への駆動電流の供給が制御され、電界発光素子 E L に流れる電流が制御される。電界発光素子 E L が発光（黒表示の場合は非発光）している期間が発光期間である。また第 1 行電流設定期間が終わると第 2 行電流設定期間が開始し、順次各行の電流設定期間に映像データ信号に基づき駆動電流が書き込まれていく。

**【 0 0 1 8 】**

ところで、黒表示において、線順次データ線電流信号は電流ゼロが好ましいが実際には回路構成上電流ゼロにすることは困難である。線順次データ線電流信号の電流がゼロにならないと、電界発光素子 E L の駆動電流をゼロにすることはできずそのため黒表示の設定を十分にすることができない。黒表示の設定を十分に行うためにゼロ電流設定回路を設けている。

30

**【 0 0 1 9 】**

垂直プランキング期間に図 3 の列電流制御回路 4 に入力される映像信号電圧をゼロ電流設定電圧（黒表示電圧レベル）として、列電流制御回路 4 に接続されるデータ線にゼロ設定電流（基準電流）を流す。この期間をゼロ電流設定期間（ゼロ電流プログラミング期間）という。ゼロ電流設定期間に制御信号 P 1 z , P 2 z をそれぞれハイレベルとして、n MOS トランジスタ M 3 , M 2 をそれぞれオンすると、p MOS トランジスタ M 1 のゲートに接続されている容量 C 1 の電圧は、ゼロ設定電流に相関のあるゼロ電流設定レベルに設定され、各画素回路の電流設定時にゼロ設定電流に基づく設定電流 I z が p MOS トランジスタ M 1 , M 4 を介してデータ線に流れるに十分なゲート - ソース電圧に設定される。次に、制御信号 P 1 z , P 2 z がロウレベルになると、容量 C 1 の電圧が保持される。

40

**【 0 0 2 0 】**

次に第 1 行画素回路を映像表示（例えば黒表示）に設定するためにデータ電流 I data1 がデータ線に流れたとすると、上記ゼロ電流設定回路から設定電流 I z が p MOS トランジスタ M 1 , M 4 を介してデータ線に流れ、第 1 行画素回路の書き込み設定電流 I data2 は  $I_{data2} = I_{data1} - I_z$  となる。このようにゼロ電流設定回路を設けることにより画素回路間の黒表示の設定が可能となる。

50

## 【0021】

しかしながら、本発明者は、ゼロ電流設定回路で電流の設定をしようとしても、ゼロ電流設定時のゼロプログラミングがデータ線の寄生容量  $C_x$  の影響で安定に行うことが困難であることを見いだした。ここで、データ線の寄生容量は配線容量、データ線に接続される画素回路のトランジスタのゲート - ソース間容量等である。ゼロ設定電流は微少電流であるため、データ線の寄生容量の影響があるとゼロ電流設定回路で電流の設定をしようとしても、限られた垂直プランキング期間にゼロ設定電流も基づく電流を書き込むことは必ずしも容易ではない。また、例えはあるフレームで、あるデータ線に 1 行 ~ n 行の画素回路が接続され、n 行番目の画素回路を高輝度に設定するために、容量  $C_1$  の電圧が低く設定され、データ線寄生容量  $C_x$  の電位も低く設定されていたとする。すると、次のフレームでのゼロ電流設定期間では、ゼロ電流書き込み動作が微少電流書き込みであるために、限られたゼロ電流設定期間にデータ線寄生容量  $C_x$  の影響によりゼロ電流設定回路の容量  $C_1$  の電位は十分に上げることは困難になる。さらに、n 行番目の画素回路を黒表示に設定するために容量  $C_1$  の電圧が高く設定され、データ線寄生容量  $C_x$  の電位も高く設定されていたとすると、n 行番目の画素回路を高輝度に設定した場合とデータ線寄生容量  $C_x$  の電位に差が生じることになり、ゼロ電流設定時のゼロプログラミングがデータ線の寄生容量の影響で安定に行うことが困難となる。

10

## 【0022】

本発明者は図 2 に示すように、ゼロ電流設定期間に、制御信号 L をロウレベルとし、データ線スイッチ ( $n$  MOS トランジスタ) M 5 をオフにしてデータ線を切り離し、各画素回路が接続されるデータ線部分をゼロ電流設定回路と切り離した。こうすることで、ゼロ電流設定期間でのゼロ設定電流がデータ線の寄生容量と切り離されてゼロ電流設定回路に書き込むことができる。そして、寄生容量の影響を受けないので、より速くゼロ設定電流の書き込みを行うことができる。

20

## 【0023】

容量  $C_1$  は個別に容量素子として形成してもよいが、素子として形成しなくとも、ゲート - ソース間に形成される寄生容量（ゲート電極とソース領域との重なり容量等）を用いてよい。

## 【0024】

## (第 2 の実施形態)

30

図 5 は本発明の第 2 の実施形態に係わる画素回路及びゼロ電流設定回路の一構成例を示す図である。本実施形態ではゼロ電流設定回路の構成をより簡略化したものであり、 $n$  MOS トランジスタ M 3 と  $p$  MOS トランジスタ M 4 を削除し、 $p$  MOS トランジスタ M 1 を直接データ線に接続したものである。このような構成でも第 1 の実施形態と同様な効果を得ることができる。

## 【0025】

以上本発明に係わる電流プログラミング装置を用いた例として、電流駆動表示素子を用いたアクティブマトリクス型の表示装置を取り上げて説明したが、本発明に係わる電流プログラミング装置はデータ線に流す電流を、トランジスタのゲート - ソース電圧として保持する電流設定回路を用いる用途であれば適用することができ、その用途は電界発光素子、電子放出素子等の電流駆動表示素子を用いたアクティブマトリクス型の表示装置に限られず、アナログメモリ等の電流プログラミングのための回路として用いられる。アナログメモリとして用いる場合には各画素回路から電界発光素子 E\_L が除かれた構成の回路構成をとり、アナログ値を回路から電流値として取り出す。また本発明はマトリクス状の表示装置に限られずライン状の表示装置にも適用可能である。

40

## 【産業上の利用可能性】

## 【0026】

本発明は電界発光素子 (E\_L 素子) 等の電流駆動型発光素子のアクティブマトリクス型表示装置やアナログメモリに用いられるものである。

## 【図面の簡単な説明】

50

## 【0027】

【図1】本発明の第1の実施形態に係わる画素回路及びゼロ電流設定回路の一構成例を示す図である。

【図2】本発明の第1の実施形態に係わる画素回路及びゼロ電流設定回路の動作を説明するためのタイミングチャートである。

【図3】本発明に係わるアクティブマトリクス電界発光表示装置の構成を示す構成図である。

【図4】比較例の画素回路及びゼロ電流設定回路の構成を示す図である。

【図5】本発明の第2の実施形態に係わる画素回路及びゼロ電流設定回路の一構成例を示す図である。

10

## 【符号の説明】

## 【0028】

1 画素回路部

2 データ線スイッチ

3 ゼロ電流設定回路

4 列電流制御回路

5 列走査回路

6 行走査回路

M1, M4, M8, M9, M12, M13 pMOSトランジスタ

M2, M3, M6, M7, M10, M11 nMOSトランジスタ

20

M5 データ線スイッチ (nMOSトランジスタ) C1 容量

EL 電界発光素子

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 624 E

G 09 G 3/20 641 D

H 05 B 33/14 A

(72)発明者 川野 藤雄

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 中村 直行

(56)参考文献 特開2003-050564 (JP, A)

特開2003-076327 (JP, A)

特開2004-004789 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3 / 00 - 3 / 38

H 01 L 51 / 50