(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-123721

(P2007-123721A)

(43) 公開日 平成19年5月17日(2007.5.17)

(51) Int.CI.

H01L 31/04

(2006.01)

F 1

H01L 31/04

テーマコード(参考)

E

5 F O 5 1

審査請求 未請求 請求項の数 8 O L (全 15 頁)

(21) 出願番号

特願2005-316789 (P2005-316789)

(22) 出願日

平成17年10月31日 (2005.10.31)

(71) 出願人 000116024

ローム株式会社

京都府京都市右京区西院溝崎町21番地

(71) 出願人 301021533

独立行政法人産業技術総合研究所

東京都千代田区霞が関1-3-1

(74) 代理人 100105647

弁理士 小栗 昌平

(74) 代理人 100105474

弁理士 本多 弘徳

(74) 代理人 100108589

弁理士 市川 利光

(72) 発明者 松島 理

京都市右京区西院溝崎町21番地 ローム

株式会社内

最終頁に続く

(54) 【発明の名称】光電変換装置の製造方法および光電変換装置

## (57) 【要約】

【課題】化合物半導体薄膜(CIGS薄膜)を用いた光電変換素子(フォトセンサや太陽電池)の暗電流を劇的に低減し得る、新規な製造プロセス技術を提供する。

【解決手段】フォトリソグラフィによるエッチングによって、下部電極層(Mo)10、光吸收層として機能するカルコパイライト構造のp型の化合物半導体薄膜(CIGS薄膜)30、n型の透光性電極層(ZnO)60の各々をパターニングする手法を採用し、かつ、CIGS薄膜30については、ドライエッチングとウエットエッチングを組み合わせた2段エッチングを行うことによって、化合物半導体の結晶にダメージや欠陥を生じさせることなく、また、残渣を残すことなく、高精度のパターニングを実現する。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

基板上に下部電極層、光吸収層として機能するカルコパライライト構造の化合物半導体薄膜、透光性電極層が積層されて構成される光電変換装置の製造方法であって、

前記カルコパライライト構造の化合物半導体薄膜をフォトリソグラフィによってパターニングする工程を含む光電変換装置の製造方法。

**【請求項 2】**

請求項 1 記載の光電変換装置の製造方法であって、

前記カルコパライライト構造の化合物半導体薄膜をパターニングする工程は、

ドライエッチングによりパターニングする第 1 の工程と、

この第 1 の工程で生じるエッチング残渣を、ウェットエッチングより除去する第 2 の工程と、

を含むことを特徴とする、光電変換装置の製造方法。

10

**【請求項 3】**

請求項 2 記載の光電変換装置の製造方法であって、

前記第 1 の工程では、塩素系ガスおよび臭素系ガスをエッチャントとしてドライエッチングを行い、また、前記第 2 の工程では、前記カルコパライライト構造の化合物半導体薄膜を、臭素とメタノールの混合液、または、水とアンモニアの混合液で処理した後、塩酸と硝酸の混合液で処理することを特徴とする光電変換装置の製造方法。

20

**【請求項 4】**

請求項 1 乃至 3 のいずれかに記載の光電変換装置の製造方法であって、

前記カルコパライライト構造の化合物半導体薄膜は、 $Cu(1-x, Ga_{(1-x)})Se_2 (0 < x < 1)$  であることを特徴とする光電変換装置の製造方法。

30

**【請求項 5】**

請求項 4 記載の光電変換装置の製造方法であって、

前記カルコパライライト構造の化合物半導体薄膜を形成する工程は、CVD 法により、 $Cu(1-x, Ga_{(1-x)})Se_2 (0 < x < 1)$  薄膜を成膜する工程を含み、

前記透光性電極層を形成する工程は、前記化合物半導体薄膜上にノンドープの ZnO 膜を形成する工程と、前記ノンドープの ZnO 膜上に  $n^+$  型の ZnO 膜、ITO 膜などの透明電極膜とを形成する工程を含む光電変換装置の製造方法。

30

**【請求項 6】**

請求項 1 乃至 5 のいずれかに記載の光電変換装置の製造方法によって製造された光電変換装置。

**【請求項 7】**

請求項 6 記載の光電変換装置であって、

前記光電変換装置は、近赤外光領域にも感度をもつフォトセンサであることを特徴とする光電変換装置。

40

**【請求項 8】**

請求項 6 記載の光電変換装置であって、

前記光電変換装置は、太陽電池であることを特徴とする光電変換装置。

40

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、光電変換装置の製造方法および光電変換装置に係り、特にカルコパライライト構造の化合物半導体薄膜を用いたフォトセンサや太陽電池等の光電変換装置に関する。

**【背景技術】****【0002】**

Ib 族元素と IIIB 族元素と VIB 族元素とからなる、カルコパライライト構造の半導体薄膜である  $CuInSe_2$  (CIS 系薄膜)、あるいは、これに Ga を固溶した  $Cu(1-x, Ga_x)Se_2$  (CIGS 系薄膜) を光吸収層に用いた薄膜太陽電池は、高いエネル

50

ギー変換効率を示し、光照射等による効率の劣化が少ないという利点を有している。

【0003】

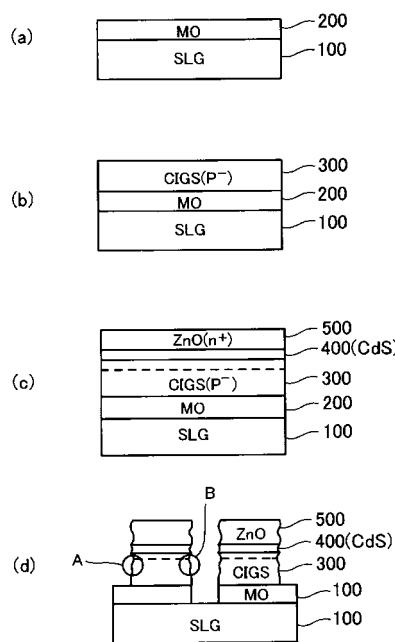

図8(a)乃至(d)は、従来の、CIGS系薄膜太陽電池のセルの製造方法を説明するためのデバイスの断面図である。

【0004】

図8(a)に示すように、まず、SLG(ソーダライムガラス)基板100上にプラス側の下部電極となるMo(モリブデン)電極層200が形成される。

【0005】

次に、図8(b)に示すように、Mo電極層200上に、組成制御により、p<sup>-</sup>型を示す、CIGS系薄膜からなる光吸收層3が形成される。10

【0006】

次に、図8(c)に示すように、その光吸收層3上に、CdSなどのバッファ層400を形成し、そのバッファ層400上に、不純物がドーピングされてn<sup>+</sup>型を示す、マイナス側の上部電極となるZnO(酸化亜鉛)からなる透光性電極層500を形成する。

【0007】

次に、図8(d)に示すように、メカニカルスクライブ装置によって、ZnOからなる透光性電極層500からMo電極層200までを、一括してスクライブ加工する。これによって、薄膜太陽電池の各セルが電気的に分離(すなわち、各セルが個別化)される。

【0008】

このスクライビング工程は、レーザスクライビング(レーザ光を照射することによって薄膜を部分的に除去するスクライブ技術)を利用することもできる。20

【0009】

しかし、この場合には、レーザ光を集中的に照射するために、局部的に高熱が発生し、これによってセルの特性が劣化するという不都合が生じる。

【0010】

したがって、太陽電池のセルは、一般に、メカニカルスクライビング装置によって電気的に分離される。

【0011】

特許文献1に記載のメカニカルスクライブ装置では、所定のテーパー角度をもって先細りになり、かつ先端が平坦な刃を、所定の圧力をもって被加工面のスクライブ箇所に垂直に押し付け、その刃を被加工面に沿って移動させることによってスクライブ加工を行っている。30

【特許文献1】特開2004-115356号公報

【発明の開示】

【発明が解決しようとする課題】

【0012】

CIS系薄膜、CIGS系薄膜は、太陽電池としての利用が主流である。

【0013】

一方、本発明者らは、この化合物半導体薄膜材料の高い光吸収係数と、可視光から近赤外光までの広い波長域に渡って高い感度をもつ特性に着目し、この化合物半導体薄膜材料を、セキュリティカメラ(昼間は可視光をセンシングし、夜間は近赤外光をセンシングするカメラ)や、個人認証カメラ(外光の影響を受けない近赤外光で個人認証するためのカメラ)、あるいは、車載カメラ(夜間の視覚補助や遠方の視野確保等のために車に搭載されるカメラ)用のイメージセンサとして利用することについて検討した。40

【0014】

この結果として、CIS系薄膜(CuInSe<sub>2</sub>)を例にとると、暗電流(逆バイアス時にPN接合に流れる電流)が予想外に大きいことがわかった。

【0015】

すなわち、例えば、-0.8Vの逆バイアス時に、 $1 \times 10^{-3}$  A/cm<sup>2</sup>程度の暗電流が流れ、この値は、シリコン系材料よりも6桁大きい。このままで、1000Lux50

(ルクス)以下の弱い光は、雑音に埋もれてしまい、検出できることになる。

【0016】

そこで、暗電流を大幅に低減する必要が生じた。本発明の発明者は、化合物半導体薄膜において暗電流が増大する要因を詳細に調べたが、その結果、メカニカルスクライビング時に化合物半導体材料の結晶にダメージや欠陥が生じ、これにより、PN接合の界面に複数のエネルギー準位が発生し、これが大きな暗電流の要因となることがわかった。

【0017】

すなわち、図8(d)において、PN接合の界面(空乏層の境界:点線で示す)の端部(図中、丸で囲んで示すA,B部分)は、メカニカルスクライビングされて露出するCIGS薄膜300の側壁に到達している。メカニカルスクライビング面は、結晶のダメージが大きく、不要な界面順位が存在する。したがって、この部分で、PN接合のリーク電流が増大してしまう。

【0018】

本発明は、このような考察に基づいてなされたものであり、化合物半導体薄膜を用いた光電変換素子の暗電流を大幅に低減することを目的とする。

【課題を解決するための手段】

【0019】

本発明の光電変換装置の製造方法は、基板上に下部電極層、光吸収層として機能するカルコパイライト構造の化合物半導体薄膜、透光性電極層が積層されて構成される光電変換装置の製造方法であって、前記カルコパイライト構造の化合物半導体薄膜をフォトリソグラフィによってパターニングする工程を含む。

【0020】

この構成によれば、メカニカルスクライビングの代わりに、フォトリソグラフィによるエッチングによって、カルコパイライト構造の化合物半導体薄膜をパターニングするものである。これに伴い、下部電極層、透光性電極層の各々もフォトリソグラフィを用いたエッチングによってパターニングされることになる。これによって、メカニカルスクライビングを行ったときのような、ダメージや欠陥が化合物半導体薄膜に生じず、暗電流の大幅な低減が可能となる。

【0021】

また、本発明の光電変換装置の製造方法は、前記カルコパイライト構造の化合物半導体薄膜をパターニングする工程は、ドライエッチングによりパターニングする第1の工程と、この第1の工程で生じるエッチング残渣を、ウェットエッチングより除去する第2の工程と、を含む。

【0022】

光吸収層として機能するカルコパイライト構造の化合物半導体薄膜のパターニングに際し、ドライエッチングとウェットエッチングを組み合わせた2段エッチングを行い、これによって、残渣がなく、精度の高いパターン形成を実現するものである。光吸収層として機能するカルコパイライト構造のp型の化合物半導体薄膜は、ドライエッチングを用いてエッチング可能であるが、この場合は完全なエッチングができず、多数の柱状の残渣が残る。また、ウェットエッチングでは、サイドエッチング(レジストパターンの直下の部分について横方向のエッチングが進む現象)によってアンダーカットが生じ、精度よくパターンを形成することができない。そこで、ドライエッチングによって、サイドエッチングなく化合物半導体薄膜をパターニングし、その後の短時間のウェットエッチング処理によって、ドライエッチングの残渣のみを除去するようにし、これによって、残渣を生じさせることなく、高精度のパターンを形成することが可能となる。これによって、メカニカルエッチングを採用したときのような、ダメージや欠陥が化合物半導体の結晶に生じず、暗電流の大幅な低減が可能となる。

【0023】

また、本発明の光電変換装置の製造方法は、前記第1の工程では、塩素系ガスをエッチャントとしてドライエッチングを行い、また、前記第2の工程では、前記カルコパイラ

10

20

30

40

50

ト構造の化合物半導体薄膜を、臭素とメタノールの混合液、または、水とアンモニアの混合液で処理した後、塩酸と硝酸の混合液で処理するようにしたものを含む。

【0024】

ドライエッチングのエッチャントとして塩素系ガスを用いることによって、光吸収層を構成する化合物半導体薄膜を高レートでエッチングできる。また、ウェットエッチングについても、効率的かつ完全に残渣を除去することができる。

【0025】

また、本発明の光電変換装置の製造方法は、前記カルコパイライト構造の化合物半導体薄膜は、 $Cu(In_x, Ga_{(1-x)})Se_2$  ( $0 < x < 1$ ) であるものを含む。

【0026】

暗電流の低減には、CIS系薄膜 ( $CuInSe_2$ ) のバンドギャップの広幅化が有効であり、そこで、In (インジウム) の一部をガリウムに置換したCIGS系薄膜を使用するものである。バンド幅を広げることによって、キャリアの再結合過程を減らすことができ、暗電流を低減することができる。

なおカルコパイライト構造の化合物半導体薄膜としては、このほか  $CuAlS_2$ ,  $CuAlSe_2$ ,  $CuAlTe_2$ ,  $CuGaS_2$ ,  $CuGaSe_2$ ,  $CuGaTe_2$ ,  $CuInS_2$ ,  $CuInSe_2$ ,  $CuInTe_2$ ,  $AgAlS_2$ ,  $AgAlSe_2$ ,  $AgAlTe_2$ ,  $AgGaS_2$ ,  $AgGaSe_2$ ,  $AgGaTe_2$ ,  $AgInS_2$ ,  $AgInSe_2$ ,  $AgInTe_2$  など、他の化合物半導体薄膜も適用可能である。

【0027】

また、本発明の光電変換装置の製造方法前記カルコパイライト構造の化合物半導体薄膜を形成する工程は、PVD法により、 $Cu(In_x, Ga_{(1-x)})Se_2$  ( $0 < x < 1$ ) 薄膜を成膜する工程を含み、前記透光性電極層を形成する工程は、前記化合物半導体薄膜上にノンドープのZnO膜を形成する工程と、前記ノンドープのZnO膜上に $n^+$ 型のZnO膜とを形成する工程を含むものを含む。

【0028】

この構成によれば、透光性電極層としてノンドープのZnO膜 ( $i - ZnO$ ) を設けることにより、下地のCIGS薄膜に生じるボイドやピンホールを半絶縁層で埋め込むと共に、CIGS薄膜とi-p接合を形成し、導電性のZnO膜 ( $n^+$ ) をCIGS薄膜と直接に接触させた場合に起こるトンネル電流によるリークを防ぐことができる。したがって、ノンドープのZnO膜 ( $i - ZnO$ ) を厚膜化することによって、PN接合界面の暗電流を低減することができる。ここでPVD法とは、真空中で蒸発させた原材料を堆積させて成膜する方法をいうものとする。

【0029】

また、本発明の光電変換装置は、本発明の光電変換装置の製造方法によって製造された光電変換装置である。

【0030】

本発明の光電変換装置は、フォトリソグラフィを用いて、残渣を残さずに精度良くパターニングされており、メカニカルスクライビングを採用したときのような、ダメージや欠陥が化合物半導体の結晶に生じず、したがって、PN接合の界面に無用なエネルギー準位が生じず、暗電流の劇的な低減が可能である。すなわち、製造プロセスを変更し、光吸収層や透光性電極層のデバイス構造を最適化することによって、暗電流を103のオーダーで、改善することができる。また、 $Cu(In_x, Ga_{(1-x)})Se_2$ でのバンドギャップコントロールによって、暗電流を102のオーダーで、低減することができる。

【0031】

また、本発明の光電変換装置の一態様では、近赤外光領域にも感度をもつフォトセンサである。

【0032】

暗電流が大幅に低減された、化合物半導体薄膜を使用してフォトセンサ (イメージセンサ) を形成することによって得られた、本発明のセンサは、近赤外光にも高い感度を有するため、セキュリティカメラ (昼間は可視光をセンシングし、夜間は近赤外光をセンシ

10

20

30

40

50

グするカメラ)や、個人認証カメラ(外光の影響を受けない近赤外光で個人認証するためのカメラ)、あるいは、車載カメラ(夜間の視覚補助や遠方の視野確保等にために車に搭載されるカメラ)として、十分に利用可能である。

#### 【0033】

また、本発明の光電変換装置は、太陽電池である。

#### 【0034】

本発明の光電変換は、PN接合の界面における光電変換口スが、従来に比べて、十分に低減されているため、光により発生した電荷の収集効率が高く、光電変換効率が高い太陽電池を実現することができる。

#### 【発明の効果】

#### 【0035】

本発明によれば、フォトリソグラフィによるエッチングによって、下部電極層、光吸収層として機能するカルコパイライト構造の化合物半導体薄膜をパターニングする手法を採用することによって、メカニカルスクライビングを行ったときのような、ダメージや欠陥が化合物半導体薄膜に生じず、暗電流の大幅な低減が可能となる。

#### 【0036】

また、光吸収層については、ドライエッチングとウエットエッチングを組み合わせた2段エッチングを行うことによって、化合物半導体薄膜の結晶にダメージや欠陥を生じさせることなく、また、残渣を残さずに、高精度なパターニングを実現することができる。

#### 【0037】

また、ドライエッチングのエッチャントとして塩素系ガスを用いることによって、光吸収層を構成する化合物半導体薄膜を高レートで精度よくエッチングできる。また、ウエットエッチングについても、効率的かつ完全に残渣を除去することができる。

#### 【0038】

また、光吸収層となる化合物半導体薄膜として、In(インジウム)の一部をガリウムに置換したCIGS系薄膜を使用し、バンド幅を広げることによって、キャリアの再結合過程を減らすことができ、暗電流を低減することができる(1/5に低減)。

#### 【0039】

また、本発明の光電変換装置は、フォトリソグラフィを用いて、残渣を残さずに精度良くスクライビングされており、メカニカルスクライビングを採用したときのような、ダメージや欠陥が化合物半導体の結晶に生じず、したがって、PN接合の界面に無用なエネルギー準位が生じず、暗電流の大幅な低減が可能である。すなわち、製造プロセスを変更して、光吸収層ならびに透光性電極層のデバイス構造を最適化することによって、暗電流を103のオーダで、改善することができる。また、Cu(In<sub>x</sub>, Ga<sub>(1-x)</sub>)Se<sub>2</sub>でのバンドギャップコントロールによって、暗電流を102のオーダで、低減することができる。

#### 【0040】

本発明のセンサは、近赤外光にも高い感度を有するため、セキュリティカメラ(昼間は可視光をセンシングし、夜間は近赤外光をセンシングするカメラ)や、個人認証カメラ(外光の影響を受けない近赤外光で個人認証するためのカメラ)、あるいは、車載カメラ(夜間の視覚補助や遠方の視野確保等にために車に搭載されるカメラ)として、十分に利用可能である。

#### 【0041】

また、本発明の光電変換は、PN接合の界面における光電変換口スが、従来に比べて、十分に低減されているため、光により発生した電荷の収集効率が高く、光電変換効率が高い太陽電池を実現することができる。

#### 【発明を実施するための最良の形態】

#### 【0042】

次に、本発明の実施の形態について、図面を参照して説明する。

(実施の形態1)

10

20

30

40

50

## 【0043】

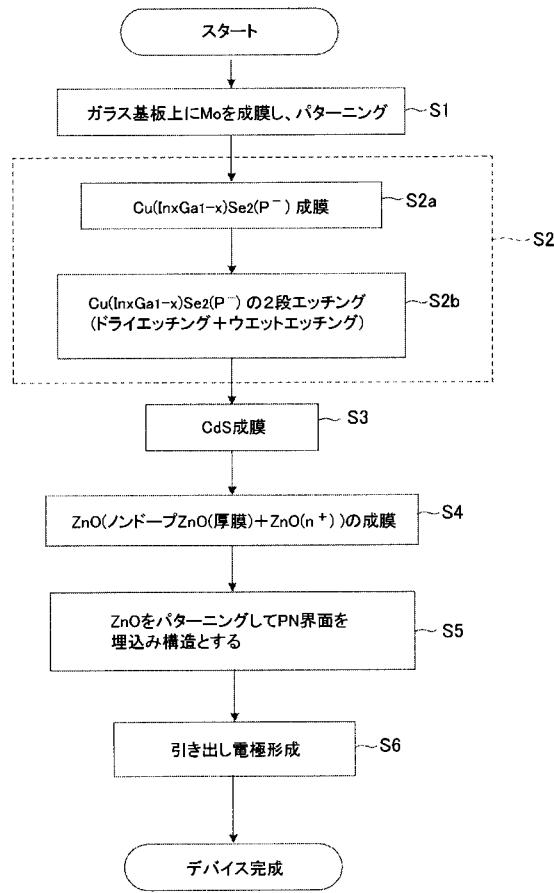

図1は、本発明にかかる光電変換装置の製造方法の概要を示すフロー図である。

## 【0044】

本製造プロセスでは、積層形成される下部電極層、光吸収層として機能するカルコパイライト構造のp型の化合物半導体薄膜（以下、CIGS薄膜という）、透光性電極層（ノンドープの部分と、不純物がドープされてn<sup>+</sup>型を示す部分の双方を含んでいる）の各々を、フォトリソグラフィ技術を用いてパターニングし、CIGS薄膜の結晶に与えるダメージを最小限に抑えるようにしたことを特徴とする。

## 【0045】

すなわち、本発明の光電変換装置の製造方法は、ガラス基板上に下部電極となるMo（モリブデン）層をスパッタ法により成膜し（0.6μm程度）、その後、フォトリソグラフィを用いてパターニングする（工程S1）。これによって、電気的に分離されたMoのアイランド領域が形成される。10

## 【0046】

次に、CIGS薄膜の成膜と、フォトリソグラフィを用いたパターニングを行う（工程S2）。この工程S2が、本発明の製造方法の最も重要な特徴点となる。

## 【0047】

すなわち、組成制御されたp<sup>-</sup>型のCIGS薄膜（Cu（In<sub>x</sub>, Ga<sub>(1-x)</sub>）Se<sub>2</sub>（0<x<1））を、例えれば、イオンビームスパッタ法によって成膜する（工程S2a）。その厚みは、1.7μm程度である。20

## 【0048】

次に、そのCIGS薄膜（p<sup>-</sup>）を、ドライエッチングとウエットエッチングを併用した2段エッチングによってパターニングする（工程S2b）。これにより、電気的に分離されたCIGS薄膜（p<sup>-</sup>）が得られる。

## 【0049】

次に、バッファ層（窓層）としての、薄いCdS膜（50nm程度）を溶液成長法により成膜する（工程S3）。

## 【0050】

次に、スパッタ法により、ノンドープのZnO膜（i-ZnO）と、不純物がドープされた低抵抗のZnO（n<sup>+</sup>）膜を連続的に成膜する（工程S4）。ここで、i-ZnOは60nm程度と薄く、一方、低抵抗化のZnO（n<sup>+</sup>）は、1μm程度と十分な厚みがある。30

## 【0051】

ノンドープのZnO膜（i-ZnO）は、下地のCIGS薄膜に生じるボイドやピンホールを半絶縁層で埋め込むと共に、CIGS薄膜とi-p接合を形成し、低抵抗のZnO膜（n<sup>+</sup>）をCIGS薄膜と直接に接触させた場合に起こるトンネル電流によるリークを防ぐ役割を果たす。

## 【0052】

したがって、ノンドープのZnO膜（i-ZnO）を厚膜化することによって、PN接合界面の暗電流を低減することができる（約1/5とする効果が確認された）。但し、厚膜化するといつても、その厚みは十分に薄いため（例えれば、60nm）、透光性電極層として機能する低抵抗のZnO（n<sup>+</sup>）膜とCIGS薄膜（p<sup>-</sup>）との間で実質的なpn接合が形成されると考えられる。40

## 【0053】

次に、ZnO膜（i-ZnOとZnO（n<sup>+</sup>））をパターニングする（工程S5）。この工程S5では、ZnO膜の端部の位置が、パターニングされたCIGS薄膜（p<sup>-</sup>）の側面よりも内側になるようにパターニングする（すなわち、CIGS薄膜（p<sup>-</sup>）の上に、このCIGS薄膜（p<sup>-</sup>）よりも横幅が狭いZnO膜が形成されて、親亀子亀構造が形成されることになる）。

## 【0054】

10

20

30

40

50

これにより、ZnO ( $n^+$ ) と CIS 薄膜 ( $p^-$ ) によって形成される PN 接合の界面（空乏層の境界）の端部が、パターニングされた CIS 薄膜 ( $p^-$ ) の側壁（エッティングにより露出している面）に達する事なく、これによって、PN 接合界面の埋込み構造が実現される。

#### 【0055】

フォトリソグラフィによりパターニングされた CIS 薄膜 ( $p^-$ ) の側面は、メカニカルスクライビングの場合に比べ、結晶欠陥やダメージは十分に少ないが、それでも、ダングリングボンド（結合手）等が存在して不要なエネルギー準位が形成されることはいえない。したがって、PN 接合界面の端部が、このパターニングされた CIS 薄膜 ( $p^-$ ) の側面（エッティングにより露出している面）に達しないようにすることによって、PN 接合の界面の端部からのリーク電流を、さらに低減できる。10

#### 【0056】

最後に、引き出し電極を形成する（工程 S6）。これによって光電変換デバイスが完成する。

#### 【0057】

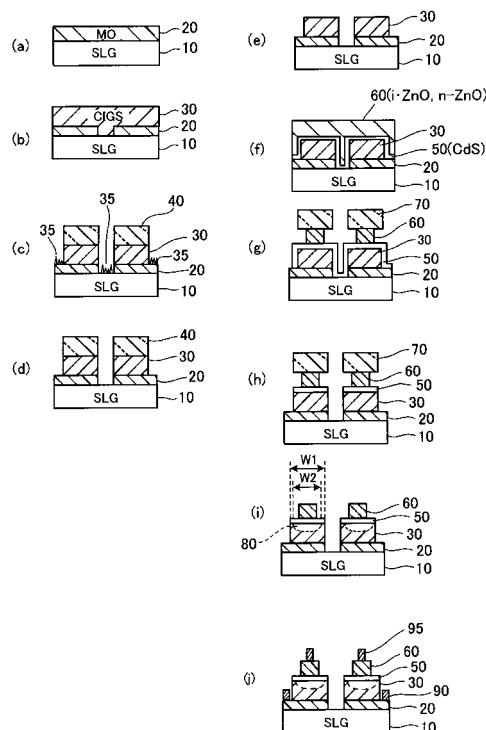

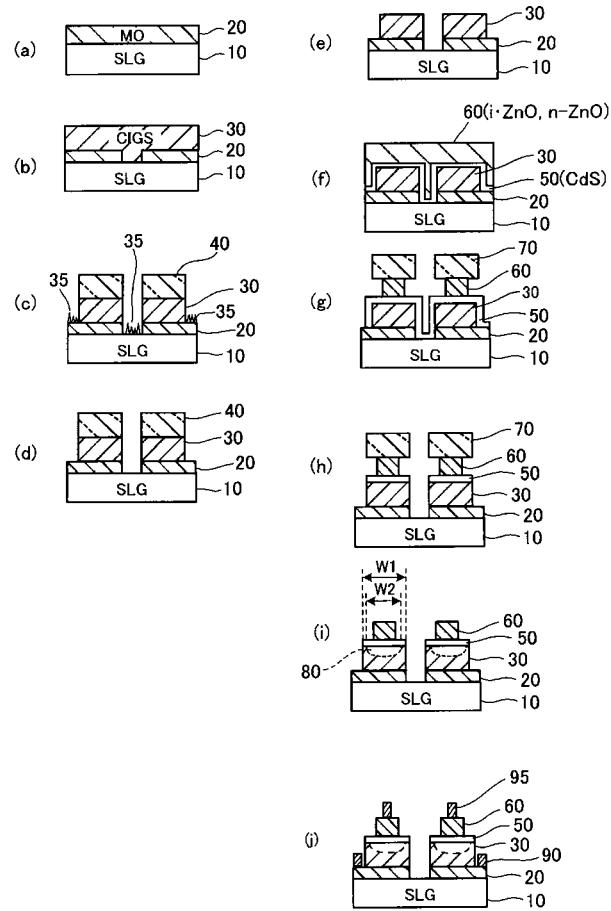

次に、図2を参照して、本発明の光電変換装置の製造方法を具体的に説明する。

#### 【0058】

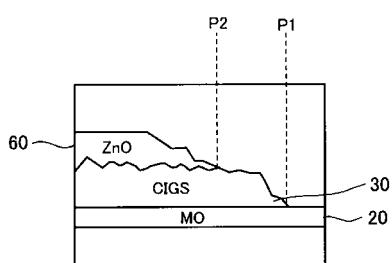

図2(a)乃至(j)は、本発明の光電変換装置の製造方法を具体的に説明するための、主要な工程毎のデバイスの断面図である。

#### 【0059】

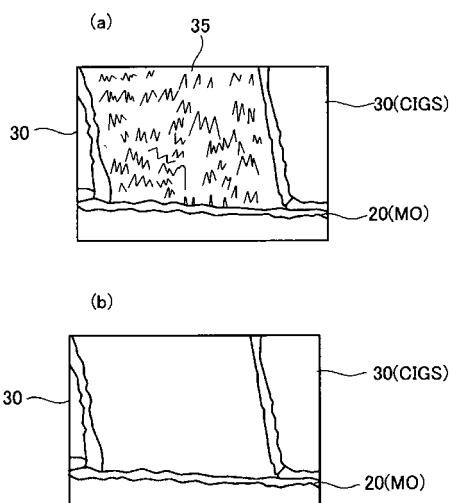

なお、以下の説明では、図3(a)、(b)ならびに図4を、適宜、参照する。ここで、図3は、CIS 薄膜のパターニング方法を説明するためのデバイスのSEM（走査顕微鏡）による1万倍の拡大写真を模式化して示す図であり、(a)は、CIS 薄膜のドライエッティング直後の状態を示す図であり、(b)は、さらにウェットエッティングを行った後の状態を示す図である。20

#### 【0060】

また、図4は、透光性電極層（ZnO膜）のパターニング後のデバイスのSEM（走査顕微鏡）の断面写真（2万倍の拡大写真）を模式化して示す図である。

#### 【0061】

まず、図2(a)に示すように、ソーダライムガラス基板(SLG)10上に、スパッタ法によりMo（モリブデン）膜を0.6 μmの厚さで形成する。30

#### 【0062】

図2(b)に示すように、例えば、Cu : In : Ga : Se = 1 : 0.5 : 0.5 : 2 の組成のスパッタターゲットを使用してイオンビームスパッタ法によって CIS 薄膜 30 を 1.7 μm の厚さで形成する。

#### 【0063】

図2(c)に示すように、レジストパターン40を用いて、CIS 薄膜 30 を、ドライエッティングする。すなわち、塩素系ガスをエッチャントとして用いて、CIS 薄膜 30 を垂直にエッティングしてパターニングを行う。この場合、高いレートで、サイドエッチがほとんどないエッティングが可能であるが、多数の残渣 35 が残る（図3(a)からわかるように、多数のMo膜上に多数の柱状の残渣が残存している）。40

#### 【0064】

そこで、図2(d)に示すように、臭素とメタノールの混合液、または、水とアンモニアの混合液で処理した後、塩酸と硝酸の混合液で処理して、残渣 35 を完全に除去する。図3(b)に示すように、残渣 35 は完全に除去される。

#### 【0065】

このように、ドライエッティングのエッチャントとして塩素系ガスを用いることによって、光吸収層を構成する CIS 薄膜 30 を高レートで、アンダーカットを生じさせることなく高精度にエッティングできる。その後、短時間のウェットエッティングを実施して、柱状の残渣 35 を完全に除去する。これによって、残渣を生じさせることなく、高精度の CI

10

20

30

40

50

G S 薄膜のパターンニングが可能となる。この場合、メカニカルエッティングを採用したときのような、ダメージや欠陥が C I G S 薄膜 3 0 の結晶に生じず、暗電流の大幅な低減が可能となる。

#### 【 0 0 6 6 】

次に、レジストパターン 4 0 を除去する。この状態のデバイス断面を図 2 ( e ) に示す。

#### 【 0 0 6 7 】

図 2 ( f ) に示すように、バッファ層（窓層）としての、薄い C d S 膜 5 0 ( 5 0 nm 程度) をスパッタ法により成膜し、続いて、スパッタ法により、 Z n O 膜 6 0 を成膜する。

10

#### 【 0 0 6 8 】

Z n O 膜 6 0 は、ノンドープの Z n O 膜 ( i - Z n O ) と、 n 型不純物がドープされた、低抵抗の Z n O ( n<sup>+</sup> ) 膜 ( 図中、 n - Z n O と表記されている ) を、連続的に成膜することによって形成される。ここで、 i - Z n O の厚みは 6 0 nm 程度であり、一方、低抵抗化の Z n O ( n<sup>+</sup> ) の厚みは、 1 μ m 程度である。

#### 【 0 0 6 9 】

ノンドープの Z n O 膜 ( i - Z n O ) は、下地の C I G S 薄膜に生じるボイドやピンホールを半絶縁層で埋め込むと共に、 C I G S 薄膜 3 0 と i - p 接合を形成し、トンネル電流によるリークを防ぐ役割を果たす。

20

#### 【 0 0 7 0 】

したがって、ノンドープの Z n O 膜 ( i - Z n O ) を厚膜化することによって、 P N 接合界面の暗電流を低減することができる。但し、厚膜化するとはいえ、その厚みは十分に薄いため ( 例えば、 6 0 nm ) 、透光性電極層として機能する低抵抗の Z n O ( n<sup>+</sup> ) 膜と C I G S 薄膜 ( p<sup>-</sup> ) との間で実質的な p n 接合が形成されると考えられる。

#### 【 0 0 7 1 】

次に、図 2 ( g ) に示すように、エッティングマスクとしてレジストパターン 7 0 を形成した後、 Z n O 膜 ( i - Z n O と Z n O ( n<sup>+</sup> ) ) 3 0 をウエットエッティングする。

#### 【 0 0 7 2 】

すなわち、例えば、塩酸 : 水 = 1 : 1 0 の希酸を用いて、ウエットエッティングを行う。このとき、エッティング時間を調整し、意図的に、サイドエッチを生じさせ、レジストパターン 7 0 の下にアンダーカットを生じさせる。これは、パターンングされた Z n O 膜 6 0 の端部の位置が、パターンングされた C I G S ( p<sup>-</sup> ) 薄膜 6 0 の側面よりも内側になるようにするためである。

30

#### 【 0 0 7 3 】

次に、レジストパターン 7 0 を用いてドライエッティングを行い、 C I G S 薄膜 3 0 の側壁上の C d S 膜 5 0 を除去する。この状態のデバイスの断面構造が図 2 ( h ) に示されている。

#### 【 0 0 7 4 】

次に、図 2 ( i ) に示すよう、レジストパターン 7 0 を除去する。図示すように、 Z n O 膜 6 0 の横幅 W 2 は、 C I G S ( p<sup>-</sup> ) 薄膜 3 0 の横幅 W 1 よりも狭く、これによって、親亀子亀構造が形成されている。図 4 から明らかなように、 Z n O 膜 6 0 の端部の位置 P 2 は、 C I G S 薄膜 3 0 の側壁の位置 P 1 よりも内側に位置している。

40

#### 【 0 0 7 5 】

この結果、図 2 ( i ) に示すように、 Z n O ( n<sup>+</sup> ) 膜 6 0 と C I G S ( p<sup>-</sup> ) 薄膜 3 0 によって形成される P N 接合の界面 8 0 ( 空乏層の境界 : 図中、点線で示されている ) の端部が、パターンングされた C I G S ( p<sup>-</sup> ) 薄膜 3 0 の側壁 ( エッティングにより露出した面 ) に達することなく、これによって、 P N 接合界面の埋込み構造が実現される。

#### 【 0 0 7 6 】

フォトリソグラフィによりパターンングされた C I G S ( p<sup>-</sup> ) 薄膜の側壁 ( エッティングにより露出した面 ) は、メカニカルスクライビングの場合に比べ、結晶欠陥やダメージ

50

は十分に少ないが、それでも、ダングリングボンド（結合手）等が存在して不要なエネルギー準位が形成されることはないとはいえない。

【0077】

したがって、P N接合界面80の端部が、このパターニングされたC I G S ( p<sup>-</sup>)薄膜30の側壁に達しないようにすることによって、P N接合の界面の端部からのリーク電流を、さらに低減できる。

【0078】

最後に、図2(j)に示すように、アルミニウム等からなる引き出し電極90, 95を形成する。これによって光電変換装置が完成する。

【0079】

この光電変換装置は、高効率の太陽電池としても適用可能である。

(実施の形態2)

【0080】

本実施の形態では、本発明の光電変換装置を、近赤外光領域にも高い感度をもつフォトセンサとして使用する例について説明する。

【0081】

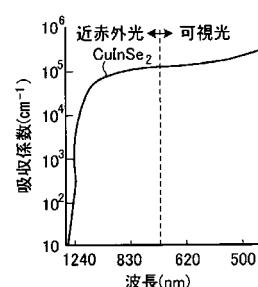

図5は、C I S薄膜(C I G S薄膜も同様である)の、光の波長に対する吸収係数を示す図である。図示するように、C I S膜(C I G S薄膜)は、可視光から近赤外光までの広範囲に渡り、高い感度をもつことがわかる。

【0082】

この点に着目し、本実施の形態では、本発明の化合物半導体薄膜からなる光電変換装置を、M O Sトランジスタなどの形成されたシリコン基板上に積層して、複合イメージセンサを形成する。

【0083】

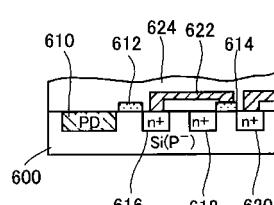

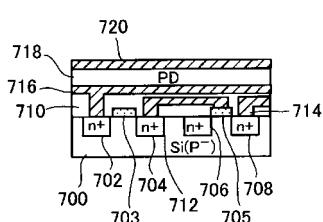

図6は、通常の、シリコン基板に形成されるC M O Sイメージセンサの概略断面図である。また、図7は、シリコン系のC M O S回路上に化合物半導体薄膜からなる光電変換装置(フォトセンサ)を積層してなる、本発明の複合イメージセンサの概略断面図である。

【0084】

図6に示すように通常のC M O Sイメージセンサは、P<sup>-</sup>型シリコン基板600内に、フォトダイオード610(例えば、p i n構造をもつ)と、M O Sトランジスタを構成するn<sup>+</sup>拡散層616, 618, 620が形成され、また、P<sup>-</sup>型シリコン基板600上に、M O Sトランジスタのゲート層612, 614と、配線層622と、保護膜(層間絶縁膜を含む)624が形成されている。

【0085】

これに対し、本発明の複合イメージセンサは、P<sup>-</sup>型シリコン基板700内に、M O Sトランジスタを構成するn<sup>+</sup>拡散層702, 704, 706, 708が形成され、また、P<sup>-</sup>型シリコン基板700上に、M O Sトランジスタのゲート層703, 705と、配線層712, 714と、層間絶縁膜710が形成されている。

【0086】

そして、この層間絶縁膜710上に、化合物半導体薄膜からなる光電変換装置(フォトセンサ)が積層形成されている。

【0087】

この光電変換装置(フォトセンサ)は、下部配線層716と、光吸収層として機能するC I G S薄膜(P D)718(図中、電極層は省略している)と、上部配線層720と、によって構成されている。

【0088】

前記実施の形態で説明したように、本発明のC I G S薄膜は、フォトリソグラフィを用いた、ドライとウェットの2段エッチングによって残渣なく、高精度にパターニングされ、結晶へのダメージ、結晶欠陥が低減され、また、Z n O膜のパターニングによって、P N接合界面の端部がC I G S薄膜のエッチングされた側壁に達しないように埋め込まれて

10

20

30

40

50

おり、暗電流が、従来デバイスに比べ、5桁程度、劇的に低減されている。

【0089】

本発明のセンサは、近赤外光にも高い感度を有するため、セキュリティカメラ（昼間は可視光をセンシングし、夜間は近赤外光をセンシングするカメラ）や、個人認証カメラ（外光の影響を受けない近赤外光で個人認証するためのカメラ）、あるいは、車載カメラ（夜間の視覚補助や遠方の視野確保等にために車に搭載されるカメラ）として、十分に利用可能である。

【0090】

なお、上記の実施の形態では、カルコパライライト構造をもつ化合物半導体薄膜（CIGS薄膜）としては、 $Cu(Ind_x, Ga_{(1-x)})Se_2$  を用いているが、これに限定されるものではない。 10

【0091】

CIGS薄膜としては、 $Cu(Ind_x, Ga_{(1-x)})(Se_y, S_{(1-y)})_2$   $x = 0 \sim 1$ ,  $y = 0 \sim 1$  という組成のものも知られており、このような組成をもつCIGS薄膜も利用可能である。 20

【0092】

このCIGS薄膜は、真空蒸着法やスパッタ法により基板上に形成可能である。真空蒸着法を用いる場合、化合物の各成分（Cu, In, Ga, Se, S）を蒸発源として基板上に別々に蒸着させる。スパッタ法では、カルコパライライト化合物をターゲットとして用いるか、あるいは、その各成分を別々にターゲットとして用いる。なお、カルコパライライト化合物半導体薄膜を金属基板又はガラス基板の上に形成する場合、基板を高温に加熱するため、カルコゲナイト元素（Se, S）の加熱による再蒸発が起こる。このため、カルコゲナイト元素の離脱による組成ずれが起こる場合がある。この場合は、成膜後にSe又はSの蒸気雰囲気中で400～600 の温度で1～数時間程度の熱処理を行うようこことにより、Se又はSを補充するのが望ましい（セレン化処理又は硫化処理）。 20

【0093】

以上説明したように、本発明によれば、フォトリソグラフィによるエッチングによって、下部電極層、光吸収層として機能するカルコパライライト構造の化合物半導体薄膜、透光性電極層の各々をパターニングする手法を採用することによって、メカニカルスクライビングを行ったときのような、ダメージや欠陥が化合物半導体薄膜に生じず、暗電流の大幅な低減が可能となる。 30

【0094】

また、光吸収層については、ドライエッチングとウェットエッチングを組み合わせた2段エッチングを行うことによって、化合物半導体の結晶にダメージや欠陥を生じさせることなく、また、残渣を残さずに、高精度なパターニングを実現することができる。

【0095】

また、ドライエッチングのエッチャントとして塩素系ガスを用いることによって、光吸収層を構成する化合物半導体薄膜を高レートでエッチングできる。また、ウェットエッチングについても、効率的かつ完全に残渣を除去することができる。

【0096】

また、光吸収層となる化合物半導体薄膜として、In（インジウム）の一部をガリウムに置換したCIGS系の化合物半導体薄膜を使用し、バンド幅を広げることによって、キャリアの再結合過程を減らすことができ、暗電流を低減することができる。 40

【0097】

また、本発明の光電変換装置は、フォトリソグラフィを用いて、残渣を残さずに精度良くスクライビングされており、メカニカルエッチングを採用したときのような、ダメージや欠陥が化合物半導体の結晶に生じず、したがって、PN接合の界面に無用なエネルギー準位が生じず、暗電流の大幅な低減が可能である。

【0098】

すなわち、製造プロセスを変更し、デバイス構造を最適化することによって、暗電流を 50

103のオーダで、改善することができる。また、 $Cu(In_xGa_{(1-x)})_2Se_2$ でのバンドギャップコントロールによって、暗電流を102のオーダで、低減することができる。

### 【0099】

本発明のセンサは、近赤外光にも高い感度を有するため、セキュリティカメラ（昼間は可視光をセンシングし、夜間は近赤外光をセンシングするカメラ）や、個人認証カメラ（外光の影響を受けない近赤外光で個人認証するためのカメラ）、あるいは、車載カメラ（夜間の視覚補助や遠方の視野確保等にために車に搭載されるカメラ）として、十分に利用可能である。

### 【0100】

また、本発明の光電変換は、PN接合の界面における光電変換ロスが、従来に比べて、十分に低減されているため、光により発生した電荷の収集効率が高く、光電変換効率が高い太陽電池を実現することができる。

### 【産業上の利用可能性】

### 【0101】

本発明は、化合物半導体薄膜を用いた光電変換素子の暗電流を大幅に低減できることから、セキュリティカメラや個人認証カメラ等に好適なフォトセンサ、固体撮像素子ならびに太陽電池、これらの光電変換素子の製造方法として有効である。

### 【図面の簡単な説明】

### 【0102】

【図1】本発明にかかる光電変換装置の製造方法の主要な工程の概要を示すフロー図

【図2】(a)乃至(j)は、本発明の光電変換装置の製造方法を具体的に説明するための、主要な工程毎のデバイスの断面図

【図3】CIGS薄膜のパターニング方法を説明するためのデバイスのSEM(走査顕微鏡)写真を模式化して示す図であり、(a)は、CIGS薄膜のドライエッチング直後の状態を示す図、(b)は、さらにウェットエッチングを行った後の状態を示す図

【図4】透光性電極層(ZnO膜)のパターニング後のデバイスのSEM(走査顕微鏡)の断面写真を模式化して示す図

【図5】CIS薄膜(CIGS薄膜)の、光の波長に対する吸収係数を示す図

【図6】シリコン基板に形成されるCMOSイメージセンサの概略断面図

30

【図7】化合物半導体薄膜からなる光電変換装置(フォトセンサ)の概略断面図

【図8】(a)乃至(d)は、従来の、CIGS系薄膜太陽電池のセルの製造方法を説明するためのデバイスの断面図

### 【符号の説明】

### 【0103】

10 ソーダライムガラス(SLG)

20 Mo(モリブデン)膜

30 光吸収層としてのCIGS薄膜

35 ドライエッチング後の残渣

40

40 CIGS薄膜エッチング用のレジストパターン

50 バッファ層としてのCdS膜

60 ZnO膜(i-ZnO, n-ZnO)

70 ZnO膜のエッチング用マスク(レジストパターン)

80 PN接合界面(空乏層の境界)

85, 90 光電変換装置の引き出し電極

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 高岡 将樹

京都市右京区西院溝崎町21番地 ローム株式会社内

(72)発明者 仁木 栄

茨城県つくば市東1-1-1 独立行政法人産業技術総合研究所つくばセンター内

(72)発明者 櫻井 啓一郎

茨城県つくば市東1-1-1 独立行政法人産業技術総合研究所つくばセンター内

(72)発明者 石塚 尚吾

茨城県つくば市東1-1-1 独立行政法人産業技術総合研究所つくばセンター内

F ターム(参考) 5F051 AA02 AA10 CB15 CB21 CB22 DA03 DA04 FA02 FA04 FA06

GA03 GA04