(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2014년10월27일

(11) 등록번호 10-1454301

(24) 등록일자 2014년10월17일

(51) 국제특허분류(Int. Cl.)

H03M 13/00 (2006.01) H03M 13/27 (2006.01)

H04L 1/00 (2006.01)

(21) 출원번호 10-2012-7013946

(22) 출원일자(국제) 2010년10월29일

심사청구일자 2012년05월29일

(85) 번역문제출일자 2012년05월29일

(65) 공개번호 10-2012-0088781

(43) 공개일자 2012년08월08일

(86) 국제출원번호 PCT/US2010/054703

(87) 국제공개번호 WO 2011/059813

국제공개일자 2011년05월19일

(30) 우선권주장

12/608,919 2009년10월29일 미국(US)

(56) 선행기술조사문현

KR1020080067987 A\*

JP2009095008 A

\*는 심사관에 의하여 인용된 문현

(73) 특허권자

웰컴 인코포레이티드

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

(72) 발명자

웬, 한평

미국 92121 캘리포니아 샌디에고 모어하우스 드라이브 5775

웨이, 용빈

미국 92121 캘리포니아 샌디에고 모어하우스 드라이브 5775

(74) 대리인

특허법인 남앤드남

전체 청구항 수 : 총 55 항

심사관 : 성경아

(54) 발명의 명칭 2차 순열 다항식 인터리버를 갖는 LTE 터보 디코더에 대한 비경쟁 저장소 설계

**(57) 요 약**

터보 디코더 내에서의 경쟁 및/또는 충돌없는 메모리의 보장을 용이하게 하는 시스템들 및 방법들이 설명된다. 사후 확률(APP) 랜덤 액세스 메모리(RAM)는 각각의 파일 내에 인터리빙 하위 그룹을 갖는 2개 또는 그보다 많은 파일들로 세그먼트화 또는 분할될 수 있다. 이는 터보 디코더에서의 병렬 동작을 가능하게 하며 터보 디코더가 메모리 액세스 경쟁 없이 다수의 파일들에 동시에 액세스하게 한다.

대 표 도 - 도3

## 특허청구의 범위

### 청구항 1

비경쟁(contention free) 메모리 액세스를 제공하는 터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법으로서,

사후 확률(APP: A Posteriori Probability) 랜덤 액세스 메모리(RAM: Random Access Memory)를 식별하는 단계; 상기 APP RAM을  $k$  개의 파일들로 편성하는(organizing) 단계;

2차 순열 다항식(QPP: Quadratic Permutation Polynomial) 터보 인터리버를 기반으로 모든 APP 값들을 적어도 2개의 인터리빙 하위 그룹들로 분할하는 단계 – 상기 분할은,  $n=1\dots k$ 인  $n$  번째 인터리빙 하위 그룹을  $k$  개의 파일들 중  $n$  번째 파일에 대해  $kit+n-1$  형식(format)으로 구성(formatting)하는 것을 포함하고, 여기서  $i$ 는  $k$  개의 인터리빙 하위 그룹들 중의 각각의 인터리빙 하위 그룹 내의 인덱스임 – ;

개별 인터리빙 하위 그룹들을 개별 APP RAM 파일들에 맵핑하는 단계; 및

하위 그룹 내의 제 1 APP 값 및 다른 하위 그룹 내의 제 2 APP 값에 액세스하는 단계를 포함하는,

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

### 청구항 2

제 1 항에 있어서,

상기 터보 디코더는 최대 사후(MAP: Maximum A Posteriori) 병렬 디코더를 포함하고, 상기 MAP 병렬 디코더는 상기 인터리빙 하위 그룹들 중 적어도 하나의 인터리빙 하위 그룹에 대한 판독 액세스(access) 또는 기록 액세스 중 적어도 하나를 이용하는,

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

### 청구항 3

제 1 항에 있어서,

상기 터보 디코더는 최대 사후(MAP) 병렬 디코더를 포함하고, 상기 MAP 병렬 디코더는 상기 인터리빙 하위 그룹들 중 적어도 하나의 인터리빙 하위 그룹에 대한 판독 액세스 또는 기록 액세스 중 적어도 하나를 이용하도록 다른 MAP 병렬 디코더로부터 분리되는,

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

### 청구항 4

제 1 항에 있어서,

$k=2$ 인,

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

### 청구항 5

제 4 항에 있어서,

상기 2 개의 RAM 파일들 각각에 대한 상기 하위 그룹에 대한 기록 액세스와 판독 액세스 사이에 클록 사이클 오프셋을 적용하는 단계를 더 포함하는,

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

### 청구항 6

제 1 항에 있어서,

$k=4$ 인],

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

#### 청구항 7

제 6 항에 있어서,

동시 판독 및 기록을 제공하기 위해 이중 포트 RAM 설계를 이용하는 단계를 더 포함하는,

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

#### 청구항 8

제 6 항에 있어서,

상기 4 개의 RAM 파일들 각각에 대한 상기 하위 그룹에 대한 기록 액세스와 판독 액세스 사이에 클록 사이클 오프셋을 적용하는 단계를 더 포함하는,

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

#### 청구항 9

삭제

#### 청구항 10

제 1 항에 있어서,

$k=8$ 인],

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

#### 청구항 11

제 10 항에 있어서,

동시 판독 및 기록을 제공하기 위해 이중 포트 RAM 설계를 이용하는 단계를 더 포함하는,

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

#### 청구항 12

제 10 항에 있어서,

상기 8 개의 RAM 파일들 각각에 대한 상기 하위 그룹에 대한 기록 액세스와 판독 액세스 사이에 클록 사이클 오프셋을 적용하는 단계를 더 포함하는,

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

#### 청구항 13

제 1 항에 있어서,

$k=16$ 인],

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

#### 청구항 14

제 13 항에 있어서,

동시 판독 및 기록을 제공하기 위해 이중 포트 RAM 설계를 이용하는 단계를 더 포함하는,

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

### 청구항 15

제 13 항에 있어서,

상기 16 개의 RAM 파일들 각각에 대한 상기 하위 그룹에 대한 기록 액세스와 판독 액세스 사이에 클록 사이클 오프셋을 적용하는 단계를 더 포함하는,

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

### 청구항 16

제 1 항에 있어서,

$k=32$ 인,

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

### 청구항 17

제 16 항에 있어서,

동시 판독 및 기록을 제공하기 위해 이중 포트 RAM 설계를 이용하는 단계를 더 포함하는,

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

### 청구항 18

제 16 항에 있어서,

상기 32 개의 RAM 파일들 각각에 대한 상기 하위 그룹에 대한 기록 액세스와 판독 액세스 사이에 클록 사이클 오프셋을 적용하는 단계를 더 포함하는,

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

### 청구항 19

제 1 항에 있어서,

상기 QPP 터보 인터리버에 관련된 하위 그룹에 멤버십을 유지하는 단계를 더 포함하며,

상기 QPP 터보 인터리버의 하위 그룹에 대한 멤버십은 APP RAM 내의 상기 하위 그룹의 멤버십으로 변환되는,

터보 디코더의 이용을 용이하게 하는 무선 통신 시스템에서 사용되는 방법.

### 청구항 20

무선 통신 장치로서,

프로세서 – 상기 프로세서는,

사후 확률(APP) 랜덤 액세스 메모리(RAM)를 식별하도록;

상기 APP RAM을  $k$  개의 파일들로 편성하도록;

2차 순열 다항식(QPP) 터보 인터리버를 기반으로 모든 APP 값들을 적어도 2개의 인터리빙 하위 그룹들로 분할하도록 – 상기 분할은,  $n=1\dots k$ 인  $n$  번째 인터리빙 하위 그룹을  $k$  개의 파일들 중  $n$  번째 파일에 대해  $ki+r-1$  형식(format)으로 구성(formatting)하는 것을 포함하고, 여기서  $i$ 는  $k$  개의 인터리빙 하위 그룹들 중의 각각의 인터리빙 하위 그룹 내의 인덱스임 – ;

개별 인터리빙 하위 그룹들을 개별 APP RAM 파일들에 맵핑하도록; 그리고

하위 그룹 내의 제 1 APP 값 및 다른 하위 그룹 내의 제 2 APP 값에 액세스하도록 구성됨 –; 및

상기 프로세서에 연결된 메모리를 포함하는,

무선 통신 장치.

### 청구항 21

제 20 항에 있어서,

상기 프로세서는 최대 사후(MAP) 병렬 디코더를 구현하도록 구성되고, 상기 MAP 병렬 디코더는 상기 인터리빙 하위 그룹들 중 적어도 하나의 인터리빙 하위 그룹에 대한 판독 액세스 또는 기록 액세스 중 적어도 하나를 이용하는,

무선 통신 장치.

### 청구항 22

제 20 항에 있어서,

상기 프로세서는 최대 사후(MAP) 병렬 디코더를 구현하도록 구성되고, 상기 MAP 병렬 디코더는 상기 인터리빙 하위 그룹들 중 적어도 하나의 인터리빙 하위 그룹에 대한 판독 액세스 또는 기록 액세스 중 적어도 하나를 이용하도록 다른 MAP 병렬 디코더로부터 분리되는,

무선 통신 장치.

### 청구항 23

제 20 항에 있어서,

$k=2$ 인,

무선 통신 장치.

### 청구항 24

제 23 항에 있어서,

상기 프로세서는 추가적으로, 상기 2 개의 RAM 파일들 각각에 대한 상기 하위 그룹에 대한 기록 액세스와 판독 액세스 사이에 클록 사이클 오프셋을 적용하도록 구성되는,

무선 통신 장치.

### 청구항 25

제 20 항에 있어서,

$k=4$ 인,

무선 통신 장치.

### 청구항 26

제 25 항에 있어서,

상기 프로세서는 추가적으로, 동시 판독 및 기록을 제공하기 위해 이중 포트 RAM 설계를 이용하도록 구성되는,

무선 통신 장치.

### 청구항 27

제 25 항에 있어서,

상기 4 개의 RAM 파일들 각각에 대한 상기 하위 그룹에 대한 기록 액세스와 판독 액세스 사이에 클록 사이클 오프셋을 적용하기 위한 프로세서를 더 포함하는,

무선 통신 장치.

### 청구항 28

삭제

### 청구항 29

제 20 항에 있어서,

$k=8$ 인,

무선 통신 장치.

### 청구항 30

제 29 항에 있어서,

동시 판독 및 기록을 제공하기 위해 이중 포트 RAM 설계를 이용하도록 구성된 프로세서를 더 포함하는,

무선 통신 장치.

### 청구항 31

제 29 항에 있어서,

상기 8 개의 RAM 파일들 각각에 대한 상기 하위 그룹에 대한 기록 액세스와 판독 액세스 사이에 클록 사이클 오프셋을 적용하도록 구성된 프로세서를 더 포함하는,

무선 통신 장치.

### 청구항 32

제 20 항에 있어서,

$k=16$ 인,

무선 통신 장치.

### 청구항 33

제 32 항에 있어서,

동시 판독 및 기록을 제공하기 위해 이중 포트 RAM 설계를 이용하도록 구성된 프로세서를 더 포함하는,

무선 통신 장치.

### 청구항 34

제 32 항에 있어서,

상기 16 개의 RAM 파일들 각각에 대한 상기 하위 그룹에 대한 기록 액세스와 판독 액세스 사이에 클록 사이클 오프셋을 적용하도록 구성된 프로세서를 더 포함하는,

무선 통신 장치.

### 청구항 35

제 20 항에 있어서,

$k=32$ 인,

무선 통신 장치.

### 청구항 36

제 35 항에 있어서,

동시 판독 및 기록을 제공하기 위해 이중 포트 RAM 설계를 이용하도록 구성된 프로세서를 더 포함하는,

무선 통신 장치.

**청구항 37**

제 35 항에 있어서,

상기 32 개의 RAM 파일들 각각에 대한 상기 하위 그룹에 대한 기록 액세스와 판독 액세스 사이에 클록 사이클 오프셋을 적용하도록 구성된 프로세서를 더 포함하는,

무선 통신 장치.

**청구항 38**

제 20 항에 있어서,

상기 프로세서는 추가적으로, 상기 QPP 터보 인터리버에 관련된 하위 그룹에 멤버십을 유지하도록 구성되어,

상기 QPP 터보 인터리버의 하위 그룹에 대한 멤버십은 APP RAM 내의 상기 하위 그룹의 멤버십으로 변환되는,

무선 통신 장치.

**청구항 39**

비경쟁 메모리 액세스를 제공하는 터보 디코더를 이용하는 무선 통신 장치로서,

사후 확률(APP) 랜덤 액세스 메모리(RAM)를 식별하기 위한 수단;

상기 APP RAM을  $k$  개의 파일들로 편성하기 위한 수단;

2차 순열 다항식(QPP) 터보 인터리버를 기반으로 모든 APP 값들을 적어도 2개의 인터리빙 하위 그룹들로 분할하기 위한 수단— 상기 분할은,  $n=1\dots k$ 인  $n$  번째 인터리빙 하위 그룹을  $k$  개의 파일들 중  $n$  번째 파일에 대해  $ki+n-1$  형식(format)으로 구성(formatting)하는 것을 포함하고, 여기서  $i$ 는  $k$  개의 인터리빙 하위 그룹들 중의 각각의 인터리빙 하위 그룹 내의 인덱스임 — ;

개별 인터리빙 하위 그룹들을 개별 APP RAM 파일들에 맵핑하기 위한 수단; 및

하위 그룹 내의 제 1 APP 값 및 다른 하위 그룹 내의 제 2 APP 값에 액세스하기 위한 수단을 포함하는,

무선 통신 장치.

**청구항 40**

제 39 항에 있어서,

상기 터보 디코더는 최대 사후(MAP) 병렬 디코더를 포함하고, 상기 MAP 병렬 디코더는 상기 인터리빙 하위 그룹들 중 적어도 하나의 인터리빙 하위 그룹에 대한 판독 액세스 또는 기록 액세스 중 적어도 하나를 이용하도록,

무선 통신 장치.

**청구항 41**

제 39 항에 있어서,

상기 터보 디코더는 최대 사후(MAP) 병렬 디코더를 포함하고, 상기 MAP 병렬 디코더는 상기 인터리빙 하위 그룹들 중 적어도 하나의 인터리빙 하위 그룹에 대한 판독 액세스 또는 기록 액세스 중 적어도 하나를 이용하도록 다른 MAP 병렬 디코더로부터 분리되는,

무선 통신 장치.

**청구항 42**

제 39 항에 있어서,

$k=2^m$ ,

무선 통신 장치.

### 청구항 43

제 42 항에 있어서,

상기 2 개의 RAM 파일들 각각에 대한 상기 하위 그룹에 대한 기록 액세스와 판독 액세스 사이에 클록 사이클 오프셋을 적용하기 위한 수단을 더 포함하는,

무선 통신 장치.

### 청구항 44

제 39 항에 있어서,

$k=4$ 인,

무선 통신 장치.

### 청구항 45

제 44 항에 있어서,

동시 판독 및 기록을 제공하기 위해 이중 포트 RAM 설계를 이용하기 위한 수단을 더 포함하는,

무선 통신 장치.

### 청구항 46

제 44 항에 있어서,

상기 4 개의 RAM 파일들 각각에 대한 상기 하위 그룹에 대한 기록 액세스와 판독 액세스 사이에 클록 사이클 오프셋을 적용하기 위한 수단을 더 포함하는,

무선 통신 장치.

### 청구항 47

삭제

### 청구항 48

제 39 항에 있어서,

$k=8$ 인,

무선 통신 장치.

### 청구항 49

제 48 항에 있어서,

동시 판독 및 기록을 제공하기 위해 이중 포트 RAM 설계를 이용하기 위한 수단을 더 포함하는,

무선 통신 장치.

### 청구항 50

제 48 항에 있어서,

상기 8 개의 RAM 파일들 각각에 대한 상기 하위 그룹에 대한 기록 액세스와 판독 액세스 사이에 클록 사이클 오프셋을 적용하기 위한 수단을 더 포함하는,

무선 통신 장치.

### 청구항 51

제 48 항에 있어서,

$k=16$ 인,

무선 통신 장치.

### 청구항 52

제 51 항에 있어서,

동시 판독 및 기록을 제공하기 위해 이중 포트 RAM 설계를 이용하기 위한 수단을 더 포함하는,

무선 통신 장치.

### 청구항 53

제 51 항에 있어서,

상기 16 개의 RAM 파일들 각각에 대한 상기 하위 그룹에 대한 기록 액세스와 판독 액세스 사이에 클록 사이클 오프셋을 적용하기 위한 수단을 더 포함하는,

무선 통신 장치.

### 청구항 54

제 48 항에 있어서,

$k=32$ 인,

무선 통신 장치.

### 청구항 55

제 54 항에 있어서,

동시 판독 및 기록을 제공하기 위해 이중 포트 RAM 설계를 이용하기 위한 수단을 더 포함하는,

무선 통신 장치.

### 청구항 56

제 54 항에 있어서,

상기 32 개의 RAM 파일들 각각에 대한 상기 하위 그룹에 대한 기록 액세스와 판독 액세스 사이에 클록 사이클 오프셋을 적용하기 위한 수단을 더 포함하는,

무선 통신 장치.

### 청구항 57

제 39 항에 있어서,

상기 QPP 터보 인터리버에 관련된 하위 그룹에 멤버십을 유지하기 위한 수단을 더 포함하며,

상기 QPP 터보 인터리버의 하위 그룹에 대한 멤버십은 APP RAM 내의 상기 하위 그룹의 멤버십으로 변환되는,

무선 통신 장치.

### 청구항 58

컴퓨터 판독 가능 매체로서,

적어도 하나의 컴퓨터로 하여금 사후 확률(APP) 랜덤 액세스 메모리(RAM)를 식별하게 하기 위한 코드;

적어도 하나의 컴퓨터로 하여금 상기 APP RAM을  $k$  개의 파일들로 편성하게 하기 위한 코드;

적어도 하나의 컴퓨터로 하여금 2차 순열 다항식(QPP) 터보 인터리버를 기반으로 모든 APP 값들을 적어도 2개의 인터리빙 하위 그룹들로 분할하게 하기 위한 코드— 상기 분할은,  $n=1\dots k$ 인  $n$  번째 인터리빙 하위 그룹을  $k$  개의 파일들 중  $n$  번째 파일에 대해  $ki+n-1$  형식(format)으로 구성(formatting)하는 것을 포함하고, 여기서  $i$ 는  $k$

개의 인터리빙 하위 그룹들 중의 각각의 인터리빙 하위 그룹 내의 인덱스임 – ;

적어도 하나의 컴퓨터로 하여금 개별 인터리빙 하위 그룹들을 개별 APP RAM 파일들에 맵핑하게 하기 위한 코드; 및

적어도 하나의 컴퓨터로 하여금 하위 그룹 내의 제 1 APP 값 및 다른 하위 그룹 내의 제 2 APP 값에 액세스하게 하기 위한 코드를 포함하는,

컴퓨터 판독 가능 매체.

## 명세서

### 기술분야

[0001]

다음 설명은 일반적으로 무선 통신들에 관한 것으로, 더 구체적으로는 메모리 저장소의 일부분 내에서의 메모리 충돌들을 줄이기 위한 저장소 설계에 관한 것이다.

### 배경기술

[0002]

무선 통신 시스템들은 다양한 타입들의 통신을 제공하도록 널리 사용되는데, 예컨대 이러한 무선 통신 시스템들을 통해 음성 및/또는 데이터가 제공될 수 있다. 통상의 무선 통신 시스템 또는 네트워크는 하나 또는 그보다 많은 공유 자원들(예를 들어, 대역폭, 송신 전력, ...)에 대한 다수의 사용자들의 액세스를 제공할 수 있다. 예컨대, 시스템은 주파수 분할 다중화(FDM: Frequency Division Multiplexing), 시분할 다중화(TDM: Time Division Multiplexing), 코드 분할 다중화(CDM: Code Division Multiplexing), 직교 주파수 분할 다중화(OFDM: Orthogonal Frequency Division Multiplexing)와 같은 다양한 다중 액세스 기술들을 사용할 수 있다.

[0003]

일반적으로, 무선 다중 액세스 통신 시스템들은 다수의 모바일 디바이스들에 대한 통신을 동시에 지원할 수 있다. 각각의 모바일 디바이스는 순방향 및 역방향 링크들 상의 송신들을 통해 하나 또는 그보다 많은 기지국들과 통신할 수 있다. 순방향 링크(또는 다운링크)는 기지국들로부터 모바일 디바이스들로의 통신 링크를 지칭하고, 역방향 링크(또는 업링크)는 모바일 디바이스들로부터 기지국들로의 통신 링크를 지칭한다.

[0004]

무선 통신 시스템들은 흔히 커버리지 영역을 제공하는 하나 또는 그보다 많은 기지국들을 이용한다. 일반적인 기지국은 브로드캐스트, 멀티캐스트 및/또는 유니캐스트 서비스들을 위해 다수의 데이터 스트림들을 전송할 수 있는데, 여기서 데이터 스트림은 모바일 디바이스에게 독립적인 수신 대상일 수 있는 데이터의 스트림일 수 있다. 이러한 기지국의 커버리지 영역 내의 모바일 디바이스는 합성 스트림에 의해 운반되는 하나, 하나보다 많은 또는 모든 데이터 스트림들을 수신하는데 이용될 수 있다. 마찬가지로, 모바일 디바이스는 기지국 또는 다른 모바일 디바이스로 데이터를 전송할 수 있다.

[0005]

무선 통신 시스템 내에서 추적 영역(tracking area)은 사용자 장비(예를 들어, 모바일 디바이스, 모바일 통신 장치, 셀룰러 디바이스, 스마트폰 등)에 대한 추적 영역 위치가 정의될 수 있게 한다. 일반적으로, 네트워크가 사용자 장비(UE: user equipment)를 요청 또는 페이징할 수 있는데, 이러한 네트워크에서 UE는 이러한 추적 영역 위치로 응답할 수 있다. 이는 UE의 추적 영역 위치가 네트워크에 전달되어 업데이트될 수 있게 한다.

[0006]

무선 통신 시스템에서의 신뢰성 있는 통신을 위해 흔히 터보 코드가 사용되는데, 여기서 송신기는 터보 인코더를 사용하여 정보 비트들을 인코딩하는 한편, 수신기는 전송된 비트들을 터보 디코더(TDEC: turbo decoder)를 사용하여 디코딩한다. 터보 디코더는 메모리, 일반적으로 사후 확률(APP: A Posteriori Probability) 랜덤 액세스 메모리(RAM: Random Access Memory)의 일부를 포함하여, 터보 디코더의 서로 다른 부분들 사이에서 정보를 교환할 수 있다. 예를 들어, 터보 디코더는 APP RAM을 공유할 수 있는 2개의 최대 사후(MAP: Maximum A Posteriori) 디코더들을 포함할 수 있다. 넓은 대역폭과 다중 입력 다중 출력(MIMO: multiple-in-multiple-out)을 지원하기 위한 터보 디코더의 높은 스루풋 요구로 인해, 메모리 충돌 및/또는 경쟁이 일어날 수 있다. 예를 들어, MAP 디코더들 사이에서 APP RAM의 공유는 APP RAM으로/으로부터 값들의 로딩 또는 언로딩을 기초로 메모리 경쟁 및/또는 충돌을 일으킬 수 있으며, 이는 터보 디코더의 처리 스루풋을 바람직하지 않게 감소시킨다. 따라서 다수의 MAP 디코더들이 메모리 액세스 경쟁을 일으키지 않고 APP RAM을 공유할 수 있도록 APP RAM을 설계할 필요가 있다.

### 발명의 내용

- [0007] 다음은 하나 또는 그보다 많은 실시예들의 기본적인 이해를 제공하기 위해 이러한 실시예들의 간단한 요약을 제시한다. 이 요약은 예측되는 모든 실시예들의 광범위한 개요가 아니며, 모든 실시예들의 주요 또는 핵심 엘리먼트들을 식별하거나 임의의 또는 모든 실시예들의 범위를 기술하지는 않는 것으로 의도된다. 그 유일한 목적은 하나 또는 그보다 많은 실시예들의 일부 개념들을 뒤에 제시되는 보다 상세한 설명에 대한 서론으로서 간단한 형태로 제시하는 것이다.

- [0008] 관련된 양상들에 따르면, 비경쟁(contention free) 메모리 액세스를 제공하는 터보 디코더의 이용을 용이하게 하는 방법이 제공된다. 이 방법은 사후 확률(APP) 랜덤 액세스 메모리(RAM)를 식별하는 단계를 포함할 수 있다. 또한, 상기 방법은 상기 APP RAM을 적어도 2개의 파일들로 편성(organize)하는 단계를 포함할 수 있다. 더욱이, 상기 방법은 2차 순열 다항식(QPP: Quadratic Permutation Polynomial) 터보 인터리버를 기반으로 모든 APP 값들을 적어도 2개의 인터리빙 하위 그룹들로 분할하는 단계를 포함할 수 있다. 상기 방법은 추가로, 개별 인터리빙 하위 그룹들을 개별 RAM 파일들에 맵핑하는 단계를 포함할 수 있다.

- [0009] 다른 양상은 무선 통신 장치에 관한 것이다. 이 무선 통신 장치는 사후 확률(APP) 랜덤 액세스 메모리(RAM)를 식별하고, 상기 APP RAM을 적어도 2개의 파일들로 편성하고, 2차 순열 다항식(QPP) 터보 인터리버를 기반으로 모든 APP 값들을 적어도 2개의 인터리빙 하위 그룹들로 분할하고, 그리고 개별 인터리빙 하위 그룹들을 개별 RAM 파일들에 맵핑하도록 구성된 적어도 하나의 프로세서를 포함할 수 있다. 또한, 상기 무선 통신 장치는 적어도 하나의 프로세서에 연결된 메모리를 포함할 수 있다.

- [0010] 또 다른 양상은 비경쟁 메모리 액세스를 제공하는 터보 디코더를 이용하는 무선 통신 장치에 관한 것이다. 이 무선 통신 장치는 사후 확률(APP) 랜덤 액세스 메모리(RAM)를 식별하기 위한 수단을 포함할 수 있다. 추가로, 상기 무선 통신 장치는 상기 APP RAM을 적어도 2개의 파일들로 편성하기 위한 수단을 포함할 수 있다. 또한, 상기 무선 통신 장치는 2차 순열 다항식(QPP) 터보 인터리버를 기반으로 모든 APP 값들을 적어도 2개의 인터리빙 하위 그룹들로 분할하기 위한 수단을 포함할 수 있다. 더욱이, 상기 무선 통신 장치는 개별 인터리빙 하위 그룹들을 개별 RAM 파일들에 맵핑하기 위한 수단을 포함할 수 있다.

- [0011] 또 다른 양상은 적어도 하나의 컴퓨터로 하여금 사후 확률(APP) 랜덤 액세스 메모리(RAM)를 식별하게 하고, 상기 APP RAM을 적어도 2개의 파일들로 편성하게 하고, 2차 순열 다항식(QPP) 터보 인터리버를 기반으로 모든 APP 값들을 적어도 2개의 인터리빙 하위 그룹들로 분할하게 하고, 그리고 개별 인터리빙 하위 그룹들을 개별 RAM 파일들에 맵핑하게 하기 위한 코드를 저장한 컴퓨터 판독 가능 매체를 포함하는 컴퓨터 프로그램 물건에 관한 것이다.

- [0012] 앞서 언급된 것 그리고 관련된 목적들의 이행을 위해, 하나 또는 그보다 많은 실시예들은 이후에 충분히 설명되며 청구항들에서 특별히 지적되는 특징들을 포함한다. 다음 설명 및 첨부 도면들은 여기서 하나 또는 그보다 많은 실시예들의 특정 예시적인 양상들을 상세히 설명한다. 그러나 이러한 양상들은 다양한 실시예들의 원리들이 이용될 수 있는 다양한 방식들 중 몇몇을 나타낼 뿐이며, 설명되는 실시예들은 이러한 모든 양상들 및 그 등가물들을 포함하는 것으로 의도된다.

- ### 도면의 간단한 설명

- [0013] 도 1은 본원에 제시되는 다양한 양상들에 따른 무선 통신 시스템의 실례이다.

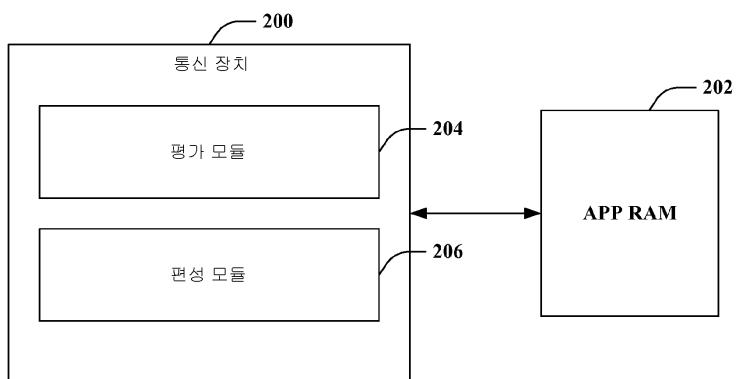

- 도 2는 무선 통신 환경 내에서 사용하기 위한 예시적인 통신 장치의 실례이다.

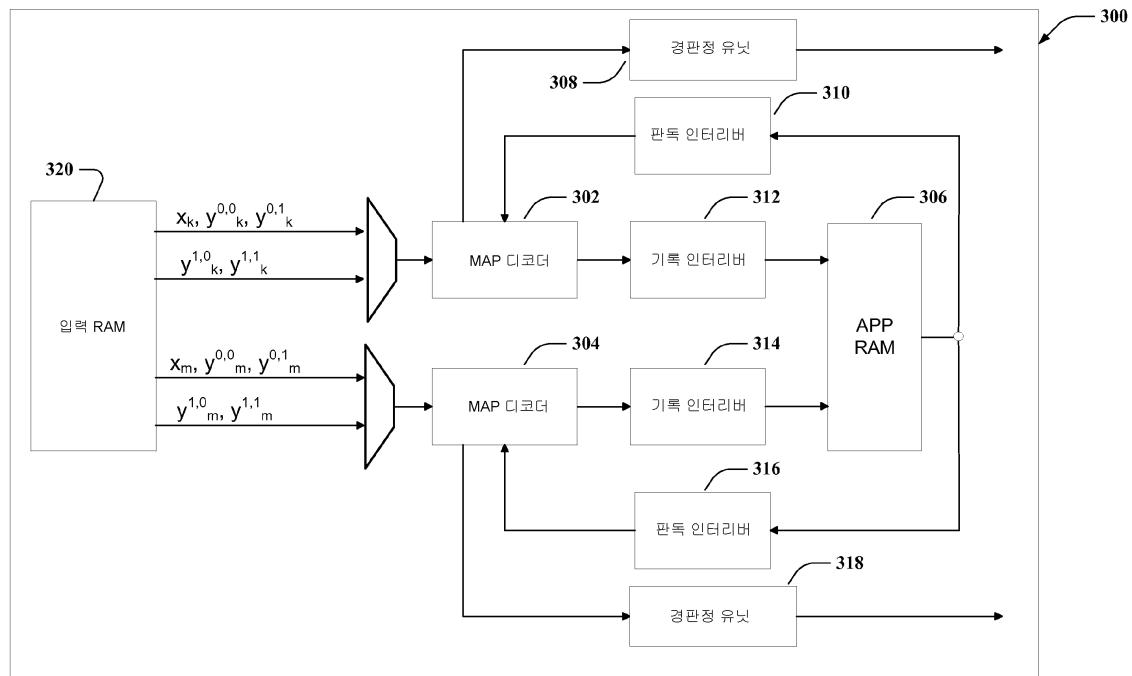

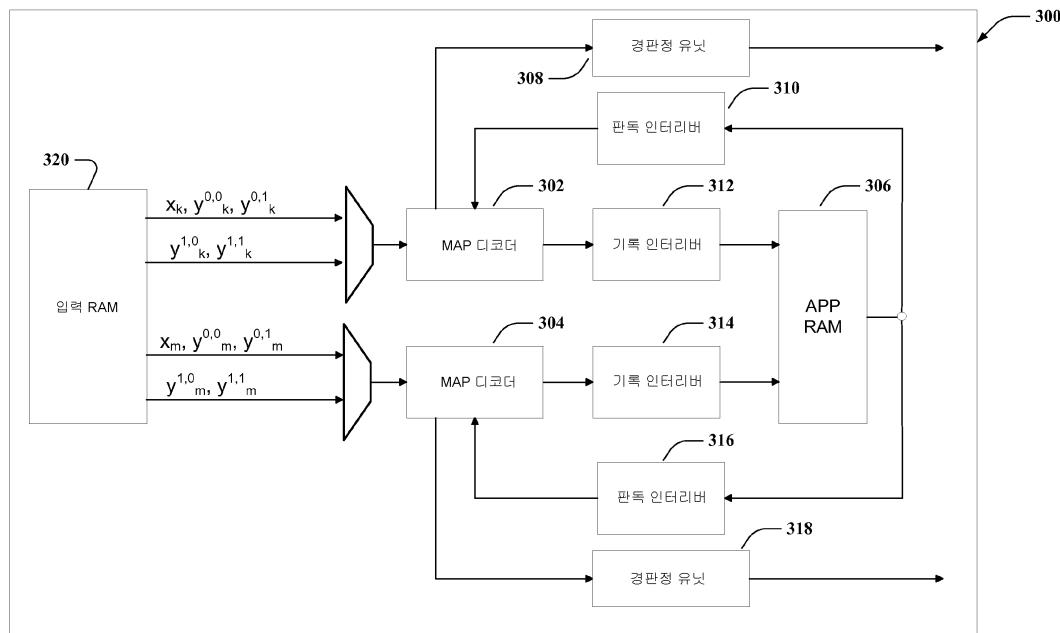

- 도 3은 대상의 혁신에 따른 예시적인 터보 디코더의 실례이다.

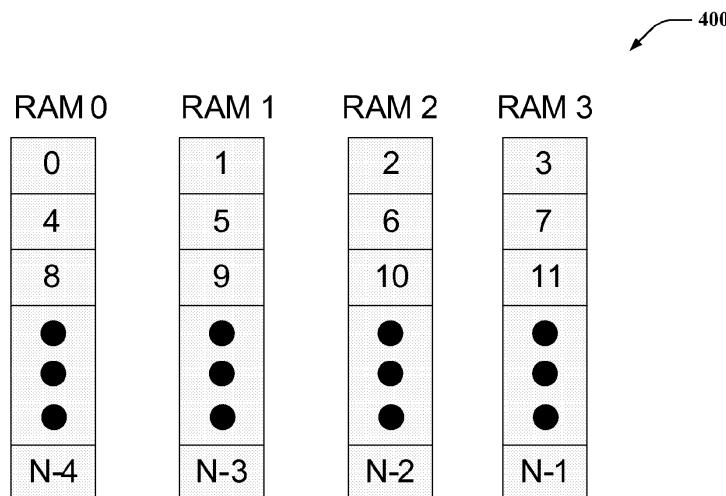

- 도 4는 대상의 혁신에 따른 4개의 하위 그룹들을 포함하는 예시적인 사후 확률(APP) 랜덤 액세스 메모리(RAM) 설계의 실례이다.

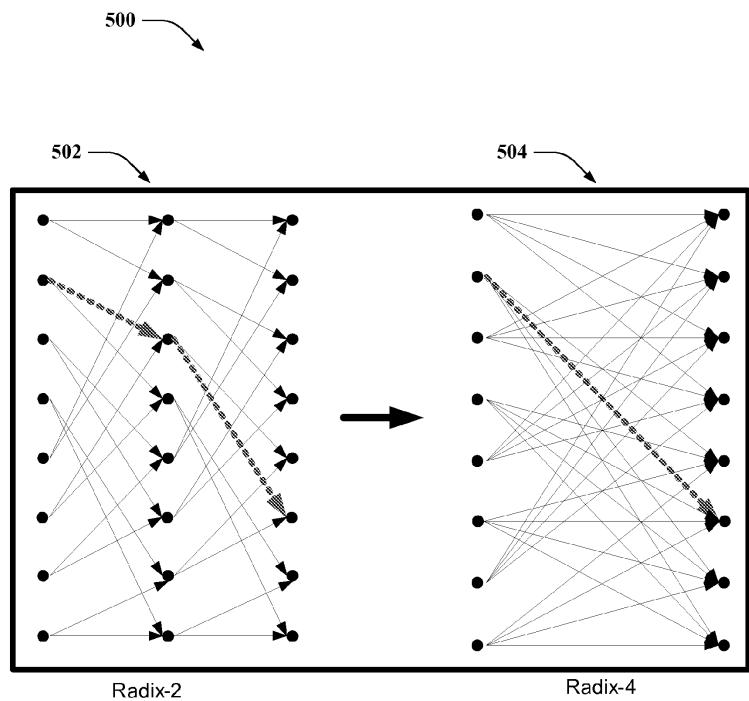

- 도 5는 radix-2 구성 및 radix-4 구성의 실례이다.

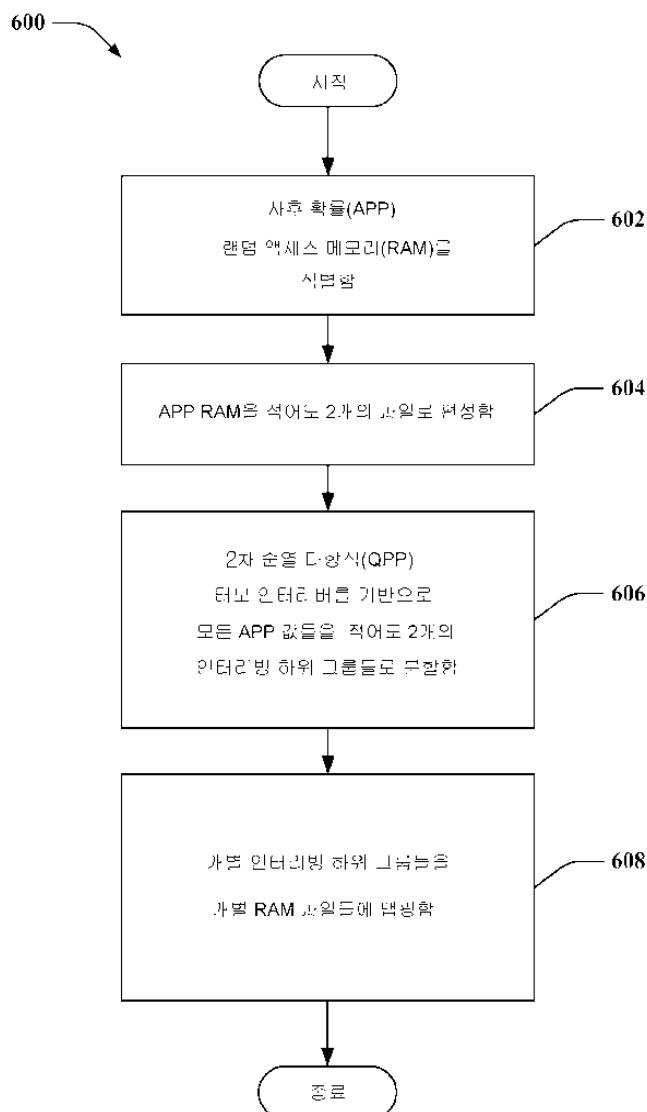

- 도 6은 비경쟁 메모리 액세스를 제공하는 터보 디코더의 이용을 용이하게 하는 예시적인 방법의 실례이다.

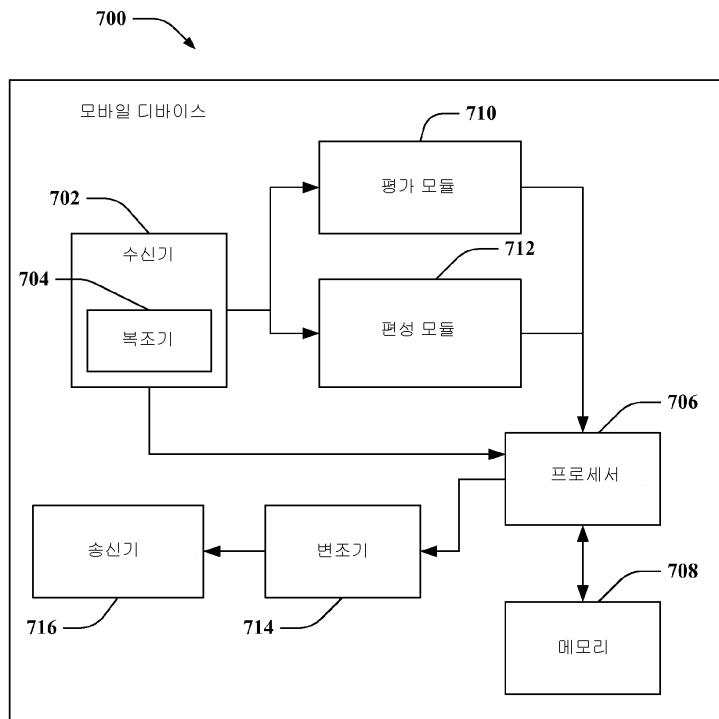

- 도 7은 무선 통신 시스템에서 메모리 충돌들을 피하도록 터보 디코더에 대한 메모리 일부의 편성을 용이하게 하는 예시적인 모바일 디바이스의 실례이다.

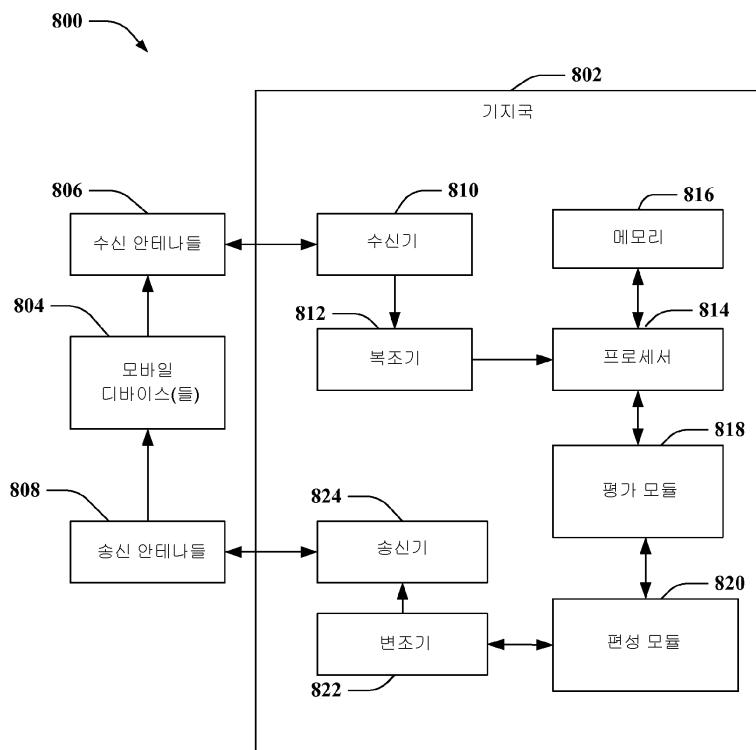

- 도 8은 무선 통신 환경에서 메모리 충돌들을 피하도록 사후 확률(APP) 랜덤 액세스 메모리(RAM)의 분할을 용이하게 하는 예시적인 시스템의 실례이다.

도 9는 여기서 설명되는 다양한 시스템들 및 방법들과 관련하여 사용될 수 있는 예시적인 무선 네트워크 환경의 실례이다.

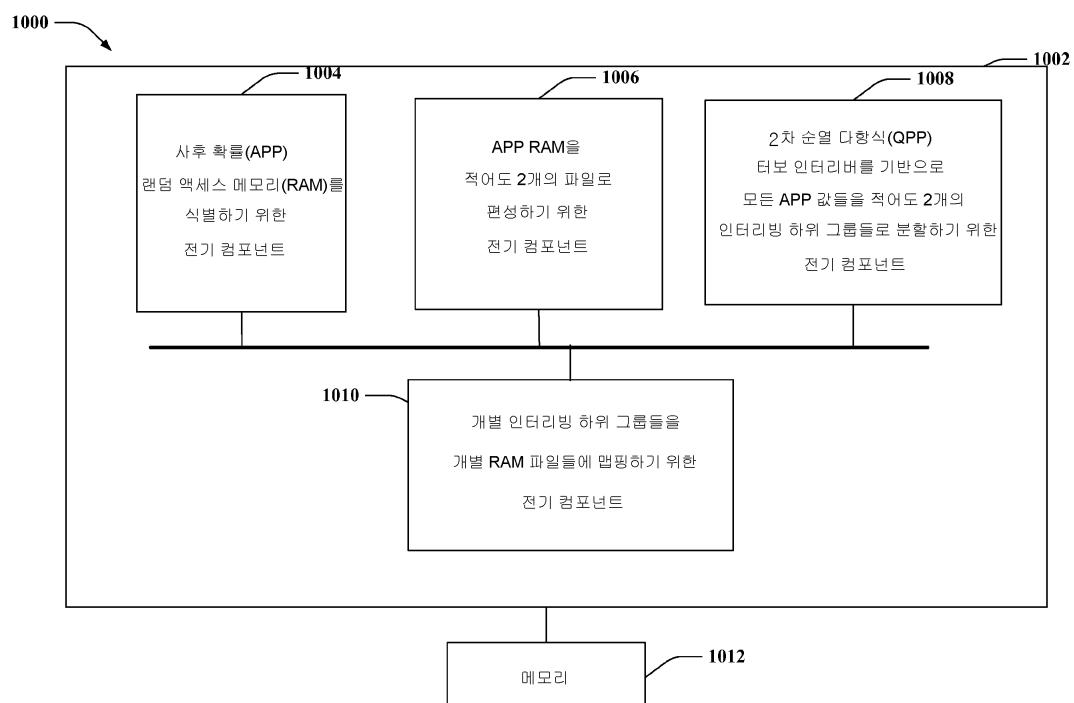

도 10은 비경쟁 메모리 액세스를 제공하는 터보 디코더의 이용을 용이하게 하는 예시적인 시스템의 실례이다.

### 발명을 실시하기 위한 구체적인 내용

[0014]

이제, 도면들을 참조하여 다양한 실시예들이 설명되는데, 여기서는 전체에 걸쳐 동일 엘리먼트들을 지칭하기 위해 동일 참조 부호들이 사용된다. 다음 설명에서는, 하나 또는 그보다 많은 엘리먼트들의 전반적인 이해를 제공하기 위해, 설명을 목적으로 다수의 특정 세부항목들이 제시된다. 그러나 이러한 실시예(들)는 이들 특정 세부항목들 없이 실시될 수도 있음이 명백할 수 있다. 다른 경우들에, 하나 또는 그보다 많은 실시예들의 설명을 용이하게 하기 위해 잘 알려진 구조들 및 디바이스들이 블록도 형태로 도시된다.

[0015]

본 출원에서 사용되는 바와 같이, "모듈", "반송파", "시스템", "인터리버", "유닛", "디코더" 등의 용어들은 컴퓨터 관련 엔티티, 하드웨어나 펌웨어, 하드웨어와 소프트웨어의 결합, 소프트웨어, 또는 실행중인 소프트웨어를 언급하는 것으로 의도된다. 예를 들어, 이에 한정되는 것은 아니지만, 컴퓨터는 프로세서상에서 실행하는 프로세스, 프로세서, 객체, 실행 파일(executable), 실행 스레드, 프로그램 및/또는 컴퓨터일 수도 있다. 예시로, 컴퓨팅 디바이스 상에서 구동하는 애플리케이션과 컴퓨팅 디바이스 모두 컴퓨터일 수 있다. 하나 또는 그보다 많은 컴퓨터들이 프로세스 및/또는 실행 스레드 내에 상주할 수 있으며, 컴퓨터가 하나의 컴퓨터에 집중될 수도 있고 그리고/또는 2개 또는 그보다 많은 컴퓨터들 사이에 분산될 수도 있다. 또한, 이러한 컴퓨터들은 각종 데이터 구조들을 저장한 각종 컴퓨터 판독 가능 매체들로부터 실행될 수 있다. 컴퓨터들은, 예컨대 하나 또는 그보다 많은 데이터 패킷들(예를 들어, 로컬 시스템, 분산 시스템에서 다른 컴퓨터와, 그리고/또는 신호에 의해 다른 시스템들과 인터넷과 같은 네트워크를 거쳐 상호 작용하는 하나의 컴퓨터로부터의 데이터)을 갖는 신호에 따라, 로컬 및/또는 원격 프로세스들에 의해 통신할 수 있다.

[0016]

여기서 설명되는 기술들은 코드 분할 다중 액세스(CDMA: code division multiple access), 시분할 다중 액세스(TDMA: time division multiple access), 주파수 분할 다중 액세스(FDMA: frequency division multiple access), 직교 주파수 분할 다중 액세스(OFDMA: orthogonal frequency division multiple access), 단일 반송파-주파수 분할 다중 액세스(SC-FDMA: single carrier-frequency division multiple access) 및 다른 시스템들과 같은 다양한 무선 통신 시스템들에 사용될 수 있다. "시스템들"과 "네트워크들"이라는 용어들은 종종 상호 교환 가능하게 사용된다. CDMA 시스템은 범용 지상 무선 액세스(UTRA: Universal Terrestrial Radio Access), CDMA2000 등과 같은 무선 기술을 구현할 수 있다. UTRA는 광대역-CDMA(W-CDMA) 및 CDMA의 다른 변형들을 포함한다. CDMA2000은 IS-2000, IS-95 및 IS-856 표준들을 커버한다. TDMA 시스템은 글로벌 모바일 통신 시스템(GSM: Global System for Mobile Communications)과 같은 무선 기술을 구현할 수 있다. OFDMA 시스템은 진화형(Evolved) UTRA(E-UTRA), 울트라 모바일 브로드밴드(UMB: Ultra Mobile Broadband), IEEE 802.11(Wi-Fi), IEEE 802.16(WiMAX), IEEE 802.20, 플래시-OFDM 등과 같은 무선 기술을 구현할 수 있다. UTRA 및 E-UTRA는 범용 모바일 통신 시스템(UMTS: Universal Mobile Telecommunication System)의 일부이다. 3GPP 롱 텀 에볼루션(LTE: Long Term Evolution)은 다운링크에 대해서는 OFDMA를 그리고 업링크에 대해서는 SC-FDMA를 이용하는 E-UTRA를 사용하는 UMTS의 향후 릴리스(upcoming release)이다.

[0017]

단일 반송파 주파수 분할 다중 액세스(SC-FDMA)는 단일 반송파 변조 및 주파수 도메인 등화를 이용한다. SC-FDMA는 OFDMA 시스템과 비슷한 성능 및 본질적으로 동일한 전체 복잡도를 갖는다. SC-FDMA는 그 고유의 단일 반송파 구조 때문에 더 낮은 피크대 평균 전력비(PAPR: peak-to-average power ratio)를 갖는다. SC-FDMA는 이를 테면, 송신 전력 효율 면에서 더 낮은 PAPR의 액세스 단말들에 크게 이익이 될 수 있는 업링크 통신들에 이용될 수 있다. 이에 따라, SC-FDMA가 3GPP 롱 텀 에볼루션(LTE) 또는 진화형 UTRA에서 업링크 다중 액세스 방식으로서 구현될 수 있다.

[0018]

더욱이, 여기서 다양한 실시예들은 모바일 디바이스와 관련하여 설명된다. 모바일 디바이스는 또한 시스템, 가입자 유닛, 가입자국, 이동국, 모바일, 원격국, 원격 단말, 액세스 단말, 사용자 단말, 단말, 무선 통신 디바이스, 사용자 에이전트, 사용자 디바이스 또는 사용자 장비(UE)로 지칭될 수도 있다. 모바일 디바이스는 셀룰러 전화, 코드리스(cordless) 전화, 세션 시작 프로토콜(SIP: Session Initiation Protocol) 전화, 무선 로컬 루프(WLL: wireless local loop) 스테이션, 개인 디지털 보조 기기(PDA: personal digital assistant), 무선 접속 능력을 가진 핸드헬드 디바이스, 컴퓨팅 디바이스, 또는 무선 모뎀에 접속된 다른 처리 디바이스일 수 있다. 더욱이, 여기서는 기지국과 관련하여 다양한 실시예들이 설명된다. 기지국은 모바일 디바이스(들)와의 통신에

이용될 수 있으며, 또한 액세스 포인트, 노드 B 또는 다른 어떤 전문용어로 지칭될 수도 있다.

[0019] 더욱이, 여기서 설명되는 다양한 양상들 또는 특징들은 표준 프로그래밍 및/또는 엔지니어링 기술들을 이용하는 방법, 장치 또는 제품으로서 구현될 수 있다. 여기서 사용된 것과 같은 "제품"이라는 용어는 임의의 컴퓨터 판독 가능 디바이스, 캐리어 또는 매체로부터 액세스 가능한 컴퓨터 프로그램을 포괄하는 것으로 의도된다. 예를 들어, 컴퓨터 판독 가능 매체는 이에 한정된 것은 아니지만, 자기 저장 디바이스들(예를 들어, 하드디스크, 플로피디스크, 자기 스트립들 등), 광 디스크들(예를 들어, 콤팩트 디스크(CD: compact disk), 디지털 다기능 디스크(DVD: digital versatile disk) 등), 스마트 카드들 및 플래시 메모리 디바이스들(예를 들어, EPROM, 카드, 스택, 키 드라이브 등)을 포함할 수 있다. 추가로, 여기서 설명된 다양한 저장 매체들은 정보를 저장하기 위한 하나 또는 그보다 많은 디바이스들 및/또는 다른 기계 판독 가능 매체들을 나타낼 수 있다. "머신 판독 가능 매체"라는 용어는 이에 한정되지 않으면서, 명령(들) 및/또는 데이터를 저장, 포함 및/또는 전달할 수 있는 무선 채널들 및 다양한 다른 매체들을 포함할 수 있다.

[0020] 이제 도 1을 참조하면, 본원에 제시된 다양한 실시예들에 따른 무선 통신 시스템(100)이 설명된다. 시스템(100)은 다수의 안테나 그룹들을 포함할 수 있는 기지국(102)을 포함한다. 예를 들어, 하나의 안테나 그룹은 안테나들(104, 106)을 포함할 수 있고, 다른 그룹은 안테나들(108, 110)을 포함할 수 있으며, 추가 그룹은 안테나들(112, 114)을 포함할 수 있다. 각각의 안테나 그룹에 대해 2개의 안테나들이 도시되지만, 각각의 그룹에 대해 더 많은 또는 더 적은 안테나들이 이용될 수 있다. 기지국(102)은 추가로 송신기 체인과 수신기 체인을 포함할 수 있는데, 기술분야에서 통상의 지식을 가진 자에 의해 인식되는 바와 같이, 이들 각각은 차례로 신호 송신 및 수신과 연관된 다수의 컴포넌트(예를 들어, 프로세서들, 변조기들, 멀티플렉서들, 복조기들, 디멀티플렉서들, 안테나들 등)를 포함할 수 있다.

[0021] 기지국(102)은 모바일 디바이스(116) 및 모바일 디바이스(122)와 같은 하나 또는 그보다 많은 모바일 디바이스들과 통신할 수 있지만, 기지국(102)은 모바일 디바이스들(116, 122)과 비슷한, 실질적으로 임의의 수의 모바일 디바이스들과 통신할 수 있는 것으로 인식되어야 한다. 모바일 디바이스들(116, 122)은 예를 들어 셀룰러폰들, 스마트폰들, 램프들, 핸드헬드 통신 디바이스들, 핸드헬드 컴퓨팅 디바이스들, 위성 라디오들, 글로벌 위치 결정 시스템들, PDA들, 및/또는 무선 통신 시스템(100)을 통해 통신하기 위한 임의의 다른 적당한 디바이스일 수 있다. 도시된 바와 같이, 모바일 디바이스(116)는 안테나들(112, 114)과 통신하는데, 여기서 안테나들(112, 114)은 순방향 링크(118)를 통해 모바일 디바이스(116)에 정보를 전송하고 역방향 링크(120)를 통해 모바일 디바이스(116)로부터 정보를 수신한다. 더욱이, 모바일 디바이스(122)는 안테나들(104, 106)과 통신하는데, 여기서 안테나들(104, 106)은 순방향 링크(124)를 통해 모바일 디바이스(122)에 정보를 전송하고 역방향 링크(126)를 통해 모바일 디바이스(122)로부터 정보를 수신한다. 주파수 분할 듀플렉스(FDD: frequency division duplex) 시스템에서, 예를 들어, 순방향 링크(118)는 역방향 링크(120)에 의해 사용되는 것과는 다른 주파수 대역을 이용할 수 있고, 순방향 링크(124)는 역방향 링크(126)에 의해 이용되는 것과는 다른 주파수 대역을 이용할 수 있다. 또한, 시분할 듀플렉스(TDD: time division duplex) 시스템에서, 순방향 링크(118) 및 역방향 링크(120)가 공통 주파수 대역을 이용할 수 있고, 순방향 링크(124) 및 역방향 링크(126)가 공통 주파수 대역을 이용할 수 있다.

[0022] 안테나들의 각각의 그룹 및/또는 이들이 통신하도록 지정된 영역은 기지국(102)의 섹터로 지칭될 수 있다. 예를 들어, 안테나 그룹들은 기지국(102)에 의해 커버되는 영역들의 섹터에 있는 모바일 디바이스들과 통신하도록 설계될 수 있다. 순방향 링크들(118, 124)을 통한 통신에서, 기지국(102)의 송신 안테나들은 모바일 디바이스들(116, 122)에 대한 순방향 링크들(118, 124)의 신호대 잡음비를 개선하기 위해 빔 형성을 이용할 수 있다. 또한, 기지국(102)이 연관된 커버리지 도처에 랜덤하게 흩어져 있는 모바일 디바이스들(116, 122)에 전송하기 위해 빔 형성을 이용하는 동안, 이웃하는 셀들의 모바일 디바이스들에는 단일 안테나를 통해 자신의 모든 모바일 디바이스들에 전송하는 기지국에 비해 더 적은 간섭이 가해질 수 있다.

[0023] 기지국(102)(및/또는 기지국(102)의 각각의 섹터)은 하나 또는 그보다 많은 다중 액세스 기술들(예를 들어, CDMA, TDMA, FDMA, OFDMA, ...)을 이용할 수 있다. 예컨대, 기지국(102)은 대응하는 대역폭 상에서 모바일 디바이스들(예를 들어, 모바일 디바이스들(116, 122))과 통신하기 위해 특정 기술을 이용할 수 있다. 더욱이, 기지국(102)에 의해 1개보다 많은 수의 기술이 이용된다면, 각각의 기술은 개개의 대역폭에 연관될 수 있다. 여기서 설명되는 기술들은 글로벌 모바일 통신 시스템(GSM), 일반 패킷 무선 서비스(GPRS: General Packet Radio Service), EDGE(Enhanced Data Rates for GSM Evolution), 범용 모바일 통신 시스템(UMTS), 광대역 코드 분할 다중 액세스(W-CDMA), cdmaOne(IS-95), CDMA2000, EV-DO(Evolution-Data Optimized), 울트라 모바일 브로드밴드(UMB), WiMAX(Worldwide Interoperability for Microwave Access), MediaFLO, 디지털 멀티미디어 브로드캐스

팅(DMB: Digital Multimedia Broadcasting), 디지털 비디오 브로드캐스팅-핸드헬드(DVB-H: Digital Video Broadcasting – Handheld) 등을 포함할 수 있다. 위에서 언급된 기술들의 리스트는 일례로 제공되며 청구 대상은 이에 한정되는 것은 아니고, 오히려 실질적으로 임의의 무선 통신 기술이 본원에 첨부된 청구항들의 범위 내에 포함되는 것으로 의도된다는 점이 인식되어야 한다.

[0024] 기지국(102)은 제 1 기술에 제 1 대역폭을 이용할 수 있다. 더욱이, 기지국(102)은 제 2 대역폭 상에서 제 1 기술에 대응하는 파일럿을 전송할 수 있다. 예시에 따르면, 제 2 대역폭은 임의의 제 2 기술을 이용하는 통신을 위해 기지국(102) 및/또는 (도시되지 않은) 임의의 다른 기지국에 의해 레버리징(leveraging)될 수 있다. 더욱이, 파일럿은 제 1 기술의 존재를 (예를 들어, 제 2 기술을 통해 통신하는 모바일 디바이스에) 표시할 수 있다. 예를 들어, 파일럿은 제 1 기술의 존재에 관한 정보를 운반하기 위한 비트(들)를 사용할 수 있다. 또한, 제 1 기술을 이용하는 섹터의 Sector ID, 제 1 주파수 대역폭을 표시하는 Carrier Index 등과 같은 정보가 파일럿에 포함될 수 있다.

[0025] 다른 예에 따르면, 파일럿은 비컨(및/또는 비컨들의 시퀀스)일 수 있다. 비컨은 전력의 상당 부분이 하나의 부반송파 또는 적은 부반송파들(예를 들어, 소수의 부반송파들) 상에서 전송되는 OFDM 심벌일 수 있다. 따라서 비컨은 모바일 디바이스들에 의해 관찰될 수 있는 강한 피크를 제공하는 동시에, 대역폭의 좁은 부분 상에서 데이터와 간섭한다(예를 들어, 나머지 대역폭은 비컨에 의해 영향받지 않을 수 있다). 이러한 예에 따라, 제 1 섹터는 제 1 대역폭 상에서 CDMA를 통해 통신할 수 있고 제 2 섹터는 제 2 대역폭 상에서 OFDM을 통해 통신할 수 있다. 이에 따라, 제 1 섹터는 제 2 대역폭 상에서 OFDM 비컨(또는 OFDM 비컨들의 시퀀스)을 전송함으로써 제 1 대역폭 상에서 CDMA의 유효성(availability)을 (예를 들어, 제 2 대역폭 상에서 OFDM을 이용하여 동작하는 모바일 디바이스(들)에) 나타낼 수 있다.

[0026] 대상의 혁신은 클록 사이클 내에서 판독 및/또는 기록 동작들 동안 메모리 충돌들을 감소 및/또는 제거하기 위해 터보 디코더 내에서 이용되는 메모리 부분에 대한 분할 기술들을 이용할 수 있다. 사후 확률(APP) 랜덤 액세스 메모리(RAM)를 파일들로 분할 및/또는 편성하는 것을 식별하기 위해 APP RAM이 평가될 수 있다. 분할 및/또는 편성의 목적은 터보 디코더가 임의의 클록 사이클 내에서 파일들 중 임의의 파일의 1개보다 많은 수의 어드레스에 결코 액세스(판독 또는 기록)하지 않도록 하는 것이다. 터보 디코더가 파일들 중 임의의 파일의 1개보다 많은 수의 어드레스에 액세스할 필요가 있다면, 메모리 액세스 경쟁이 일어난다. 이러한 경쟁은 경쟁이 해결되고 있는 동안 터보 디코더가 정지하여 대기하게 할 것이다. 이는 불가피하게 터보 디코더의 처리 스루풋을 감소시킬 것이다.

[0027] 도 2를 참조하면, 무선 통신 환경 내에서 사용하기 위한 통신 장치(200)가 예시된다. 통신 장치(200)는 기지국 또는 그 일부, 모바일 디바이스 또는 그 일부, 또는 무선 통신 환경에서 전송된 데이터를 수신하는 실질적으로 임의의 통신 장치일 수 있다. 통신 장치(200)는 기지국(예를 들어, 액세스 포인트, 노드 B, eNode B 등) 및/또는 사용자 장비(예를 들어, 이동국, 모바일 디바이스, 및/또는 (도시되지 않은) 임의의 수의 개별 디바이스들) 일 수 있는 것으로 인식되어야 한다. 통신 장치(200)는 순방향 링크 채널 또는 다운링크 채널을 통해 정보를 전송할 수 있고; 또 통신 장치(200)는 역방향 링크 채널 또는 업링크 채널을 통해 정보를 수신할 수 있으며; 또 통신 장치(200)는 역방향 링크 채널 또는 업링크 채널을 통해 정보를 전송할 수 있고; 또 통신 장치(200)는 순방향 링크 채널 또는 다운링크 채널을 통해 정보를 수신할 수 있다. 더욱이, 통신 장치(200)는 MIMO 시스템에서 이용될 수 있다. 추가로, 통신 장치(200)는 (예를 들어, 3GPP, 3GPP2, 3GPP LTE 등과 같은) OFDMA 무선 네트워크에서 작동할 수 있다. 통신 시스템들에서, 통신 장치(200)는 메모리 충돌들을 감소시키기 위해 아래에 설명되는 컴포넌트들을 이용하여 사후 확률(APP) 랜덤 액세스 메모리(RAM)를 평가하고 평가를 기초로 메모리의 분할을 생성한다.

[0028] 통신 장치(200)는 APP RAM(202)을 식별하고 검사할 수 있는 평가 모듈(204)을 포함할 수 있다. APP RAM(202)은 통신 장치(200)와는 별개로 도시되지만, APP RAM(202)은 통신 장치(200), 독립형 RAM, 또는 이들의 임의의 적당한 결합으로 통합될 수 있는 것으로 인식되어야 한다. 평가 모듈(204)은 이에 한정된 것은 아니지만, APP RAM(202)을 공유하는 MAP 디코더들의 크기, 개수 등과 같은 정보를 수집하기 위해 APP RAM(202)을 평가할 수 있다. 통신 장치(200)는 APP RAM(202)을 분할 및/또는 세그먼트화할 수 있는 편성 모듈(206)을 더 포함할 수 있다. 예를 들어, 편성 모듈(206)은 APP RAM(202)의 평가를 기초로 APP RAM(202)을 세그먼트화 및/또는 분할할 수 있다. 편성 모듈(206)은 APP RAM(202)의 크기 및/또는 MAP 디코더들의 개수와 구현을 기초로 2개 또는 그보다 많은 파일들을 생성할 수 있다. 편성 모듈(206)은 2차 순열 다항식(QPP) 터보 인터리버를 기반으로 모든 APP 값들을 적어도 2개의 인터리빙 하위 그룹들로 나눌 수 있다. 편성 모듈(206)은 개별 인터리빙 하위 그룹들

을 개별 RAM 파일들에 맵핑할 수 있다. APP RAM 분할 및 APP RAM 편성의 평가는 또한 일정할 수 있다.

[0029] 예를 들어, 편성 모듈(206)은 APP RAM(202)을 4개의 RAM 파일들로 편성할 수 있다.  $P[0], P[1], \dots, P[4L-1]$ 로 표기되는 총 4L개의 APP 값들이 있다고 가정한다. 이 예에서, 제 1 파일은  $P[4i]$ 의 APP 값들을 포함할 수 있고, 제 2 파일은  $P[4i+1]$ 에 대한 APP 값들을 포함할 수 있고, 제 3 파일은  $P[4i+2]$ 에 대한 APP 값들을 포함할 수 있고, 마지막 파일은  $P[4i+3]$ 에 대한 APP 값들을 포함할 수 있으며, 여기서  $i$ 는 각각의 파일 내의 엔트리들의 인덱스이다. 인덱스  $i$ 는 0 내지  $L-1$ 의 범위이며, 여기서  $L$ 은 4개의 파일들 각각의 크기이다. 다른 예에서, 편성 모듈(206)은 APP RAM(202)을 8개의 RAM 파일들로 편성할 수 있다.  $P[0], P[1], \dots, P[8L-1]$ 로 표기되는 총 8L개의 APP 값들이 있다고 가정한다. 이 예에서, 제 1 파일은  $P[8i]$ 의 APP 값들을 포함할 수 있고, 제 2 파일은  $P[8i+1]$ 에 대한 APP 값들을 포함할 수 있고, 제 3 파일은  $P[8i+2]$ 에 대한 APP 값들을 포함할 수 있고, …, 마지막 파일은  $P[8i+7]$ 에 대한 APP 값들을 포함할 수 있으며, 여기서  $i$ 는 각각의 파일 내의 엔트리들의 인덱스이다. 인덱스  $i$ 는 0 내지  $L-1$ 의 범위이며, 여기서  $L$ 은 8개의 파일들 각각의 크기이다. 더욱이, 도시되진 않았지만, 통신 장치(200)는 사후 확률(APP) 랜덤 액세스 메모리(RAM)의 식별, 적어도 2개의 파일들로 APP RAM의 편성 등에 관한 명령들을 보유하는 메모리를 포함할 수 있는 것으로 인식되어야 한다. 또한, 통신 장치(200)는 명령들(예를 들어, 메모리 내에 보유된 명령들, 다른 소스로부터 획득된 명령들, …)의 실행과 관련하여 이용될 수 있는 프로세서를 포함할 수 있다.

[0030] 이제 도 3을 참조하면, 대상의 혁신에 따른 2개의 MAP 디코더들을 갖는 예시적인 터보 디코더(300)가 예시된다. 터보 디코더(300)는 MAP 디코더(302), MAP 디코더(304), APP RAM(306), 경판정(hard decision) 유닛(308), 판독 인터리버(310), 기록 인터리버(312), 기록 인터리버(314), 판독 인터리버(316) 및 경판정 유닛(318)을 포함할 수 있다. MAP 디코더(302)와 MAP 디코더(304) 모두는 APP 값들에 대한 판독 및 기록을 위해 APP RAM(306)에 액세스하는 것으로 인식되어야 한다. 대상의 혁신은 메모리 충돌들 및/또는 메모리 경쟁을 막기 위해 APP RAM(306)을 파일들로 세그먼트화 또는 분할하는 것을 제공할 수 있다.

[0031] 내부 TDEC 구현들은 다양한 특징들을 가질 수 있다. 2개의 MAP 디코더들을 갖는 예시적인 터보 디코더(300)에서, 하나의 MAP 디코더는 격자(trellis)들의 처음 절반(0에서부터  $N/2-1$ 까지)을 커버하고, 다른 MAP 디코더는 두 번째 절반의 격자들( $N/2$ 에서부터  $N-1$ 까지)을 커버하며, 여기서  $N$ 은 (터보) 코드 블록의 길이이다. 이는 2의 차수의 유사성(parallelism)을 제공한다. 2개의 MAP 디코더들은 이들의 격자 방향들을 정반대 방향들로 정의한다. 제 1 MAP 디코더에 대한 순방향 격자는 0에서부터  $N/2-1$ 까지이고, 역방향 격자는  $N/2-1$ 에서부터  $N$ 까지이다. 이는 0에서의 초기 상태가 알려져 있기 때문에(모두 0인 상태) 그러하다. 제 2 MAP 디코더의 경우, 격자 방향들은 반대이다. 제 2 MAP 디코더에 대한 순방향 격자는  $N-1$ 에서부터  $N/2$ 까지이고, 역방향 격자는  $N/2$ 에서부터  $N-1$ 까지이다. 이는  $N$ 에서의 마지막 상태가 역시 알려져 있기 때문에(모두 0인 상태) 그러하다.

[0032] 모든 상태 메트릭들을 저장하기 위해 엄청난 양의 메모리를 필요로 하는 전체  $N/2$  격자의 순방향 및 역방향 상태 메트릭들을 계산하기보다는, 각각의 MAP 디코더에 대한  $N/2$  길이의 격자들이 길이가 각각  $L$ 인  $M$ 개의 비-중첩 윈도우들로 더 분할될 수 있으며, 순방향 및 역방향 상태 메트릭 계산들이 제 1 윈도우에 대해 먼저, 그 다음에 제 2 윈도우에 대해 실행되고, 기타 등등이 이루어진다. 더욱이, MAP 디코더들(302, 304)은 radix-4 격자를 사용하여 구현될 수 있다. 즉, 2개의 연속한 radix-2 격자들이 하나의 단일 radix-4 격자로서 어그리게이트(aggregate)된다(도 5 참고).

[0033] 일부 오버헤드를 무시하면, 상기의 예시적인 구현은 제 1 Radix-4 MAP 디코더에서 이루어지는 2회의 전이들 및 다른 MAP 디코더에서의 2회의 전이들에 의해 클록 사이클마다 4회의 코드 격자 전이들을 처리한다. 이러한 처리 용량을 충분히 활용하기 위해, 다음 2개의 기준들이 충족될 필요가 있다.

[0034] 기준 1: 메모리 액세스 경쟁 없이 각각의 클록 사이클에서 4세트들의 입력 샘플들이 판독될 수 있는데, 여기서 입력 샘플들의 각각의 세트는 1 또는 0의 체계적(systematic) 비트(제 1 구성 코드(CC: constituent code)에 대해서는 1 그리고 제 2 CC에 대해서는 0)에 대한 샘플, (1/3 CC 코드 레이트로 인한) 패리티 비트들에 대한 2개의 샘플들, 및 하나의 APP 값들을 포함한다. MAP 디코딩이 제 1 구성 코드에 대응하는지 아니면 제 2 구성 코드에 대응하는지에 따라, 이러한 4세트들의 어드레스들은  $m \cdot L + 2k$ ,  $m \cdot L + 2k + 1$ ,  $n \cdot L + L - 1 - 2k$ , 및  $n \cdot L + L - 2 - 2k$  또는  $\pi(m \cdot L + 2k)$ ,  $\pi(m \cdot L + 2k + 1)$ ,  $\pi(n \cdot L + L - 1 - 2k)$ , 및  $\pi(n \cdot L + L - 2 - 2k)$

$$k \in \left\{0, 1, \dots, \frac{L}{2} - 1\right\}$$

$k$ )이며, 여기서  $m$ ,  $n$ 은 일부 슬라이딩 윈도우 인덱스들이고,  $\pi$ 는 슬라이딩 윈도우 내의 클록 사이클에 관련된다. 처음 2개의 어드레스들은 Radix-4 구현으로 인해 (터보 인터리버 없이 또는 터보 인터리버에 의해) 서로 나란히 붙어 있다. 마찬가지로, 마지막 2개의 어드레스들 또한 서로 나란히 붙어 있다. 처

음 2개의 어드레스들은 제 1 MAP 디코더에 대응하는데, 여기서는 입력 샘플 로딩이 윈도우의 시작에서부터 윈도우의 끝까지 이루어진다. 마지막 2개의 어드레스들은 제 2 MAP 디코더에 대응하는데, 여기서는 입력 샘플 로딩이 반대 방향, 예를 들어 윈도우의 끝에서부터 윈도우의 시작까지 이루어진다.

[0035] 기준 2: 메모리 액세스 경쟁 없이 각각의 클록 사이클에서 4개의 APP 값들이 기록될 수 있다. 이러한 APP 값들의 어드레스들은 MAP 디코딩이 제 1 구성 코드에 대응하는지 아니면 제 2 구성 코드에 대응하는지에 따라,  $m \cdot L + 2k$ ,  $m \cdot L + 2k + 1$ ,  $n \cdot L + L - 1 - 2k$ , 및  $n \cdot L + L - 2 - 2k$  또는  $\pi(m \cdot L + 2k)$ ,  $\pi(m \cdot L + 2k + 1)$ ,  $\pi(n \cdot L + L - 1 - 2k)$ , 및  $\pi(n \cdot L + L - 2 - 2k)$ 의 포맷이다.  $m$ ,  $n$ 과  $k$ 는 이전과 같이 정의된다.

[0036] 상기의 기준을 충족하도록 APP 레이아웃을 설계하는 방법은 터보 인터리버 구조와 관련된다. 일례로, LTE에 대한 터보 인터리버는 2차 순열 다항식(QPP)을 이용하여 정의된다.

[0037] QPP 인터리버는 다음과 같이 정의된다:

$$\pi(i) = f_1 \cdot i + f_2 \cdot i^2 \pmod{N}$$

[0038] 여기서  $f_1$ 과  $f_2$ 는 2차 다항식에 정의된 계수들이며,  $N$ 은 인터리버의 길이이다. 다항식이  $\{0, 1, \dots, N-1\} \rightarrow \{0, 1, \dots, N-1\}$ 의 일대일 맵핑을 정의한다면, 다항식은 순열 다항식이라 한다.

[0039] LTE에 대해 정의된 QPP 인터리버들의 파라미터들은 다양한 코드 블록 크기들에 대해 식별될 수 있다. LTE에 대해 정의된 총 188개의 인터리버 크기들이 존재할 수 있다. 모든 인터리버 크기들은 적어도 바이트 정렬될 수 있다.  $40 \leq N \leq 512$ 일 경우, 인터리버 크기들은 모두 8의 배수들이다.  $512 \leq N \leq 1024$ 일 경우, 인터리버 크기들은 모두 16의 배수들이다.  $1024 \leq K \leq 2048$ 일 경우, 인터리버 크기들은 모두 32의 배수들이다.  $2048 \leq K \leq 6144$ 일 경우, 인터리버 크기들은 모두 64의 배수들이다.

[0040]  $N = \prod_{i=1}^m p_i^{n_i}$ 로서 인수분해될 수 있다고 가정하며, 여기서  $p_i$ '들은 개개의 소수들이고,  $n_i$ '들은 대응하는 거듭제곱 지수(power exponential)들이다.  $\pi(X)$ 가 모듈로(modulo)  $N$ 을 갖는 QPP라면,  $\pi(X)$  또한 모듈로  $p_i^{n_i}$ 를 갖는 순열 다항식이라는 점이 증명될 수 있다.

[0041] 또한,  $\pi(X)$  또한 임의의  $0 < m < n_i$ 에 대한 순열 다항식 모듈로  $p_i^m$ 이라는 점 또한 증명될 수 있다. 상기 2개의 팩터들을 결합하면, QPP 인터리버는  $N$ 을 나누는 임의의  $M$ 에 대해 다음의 하위 그룹 인터리빙 특성을 갖는 것으로 밝혀질 수 있다.

[0042] 임의의  $0 \leq m, n < N/M$  그리고  $0 \leq k, l \leq M-1$ 에 대해

$$\begin{aligned} \pi(m \cdot M + k) \pmod{M} &= \pi(n \cdot M + k) \pmod{M} \\ \pi(m \cdot M + k) \pmod{M} &\neq \pi(n \cdot M + l) \pmod{M} \quad k \neq l \text{일 경우} \end{aligned}$$

[0043] 상기로부터, 0부터  $N-1$ 까지  $N$ 개의 어드레스들은  $M$ 개의 하위 그룹들로 분할될 수 있으며, 여기서  $k$ 번째 하위 그룹은  $\{m \cdot M + k : 0 \leq m \leq N/M - 1\}$ 의 어드레스들을 포함한다. 그 다음, 하위 그룹의 모든 어드레스들은 인터리빙 후에도 여전히 하나의 하위 그룹으로 남아 있다. 더욱이, 서로 다른 하위 그룹들의 어드레스들은 인터리빙 후 서로 다른 하위 그룹에 속한다. 즉, 각각의 하위 그룹 내에서 터보 인터리빙이 유효하다.

[0044] 인터리빙에 의해 하위 그룹의 무결성이 유지된다 하더라도, 하위 그룹 내에서의 실제 인터리빙 동작은 원래의 QPP 식을 이용하여 계산될 필요가 있으며, 이는 각각의 하위 그룹에 대해 수행될 필요가 있다.

[0045] 상기의 예시적인 구현에서, TDEC는 클록 사이클당 4회의 판독들 및 4회의 기록들을 포함하는,  $m \cdot L + 2k$ ,  $m \cdot L + 2k + 1$ ,  $n \cdot L + L - 1 - 2k$ , 및  $n \cdot L + L - 2 - 2k$  또는  $\pi(m \cdot L + 2k)$ ,  $\pi(m \cdot L + 2k + 1)$ ,  $\pi(n \cdot L + L - 1 - 2k)$ , 및  $\pi(n \cdot L + L - 2 - 2k)$ 의 인덱스들을 갖는 APP 값들에 액세스할 필요가 있다. 이중 포트 RAM 설계를 통해 동시 판독 및 기록이 해결된다. 4회의 판독들 또는 기록들 사이의 비경쟁을 보장하기 위해, 일례로 전체  $N$ 개의 APP 값들은  $M=4$ 개의 하위 그룹들로 분할된다. 대응하게, 4개의 RAM 뱅크들이 사용되는데, 여기서 제 1 RAM 뱅크는  $P[4i]$ 의 APP 값들을 포함할 수 있고, 제 2 RAM 뱅크는  $P[4i+1]$ 에 대한 APP 값들을 포함할 수

있고, 제 3 RAM 뱅크는  $P[4i+2]$ 에 대한 APP 값들을 포함할 수 있고, 마지막 RAM 뱅크는  $P[4i+3]$ 에 대한 APP 값들을 포함할 수 있다.  $L$ 에 대한 일반적인 값은  $32/64/128$ 이다.  $L$ 에 대한 이러한 값들로  $m \cdot L + 2k$ ,  $m \cdot L + 2k + 1$ ,  $n \cdot L + L - 1 - 2k$ , 및  $n \cdot L + L - 2 - 2k$  또는  $\pi(m \cdot L + 2k)$ ,  $\pi(m \cdot L + 2k + 1)$ ,  $\pi(n \cdot L + L - 1 - 2k)$ , 및  $\pi(n \cdot L + L - 2 - 2k)$ 인 4개의 어드레스들은 QPP의 하위 그룹 인터리빙 특성 덕분에 항상 서로 다른 하위 그룹들에 속하고, 그러므로 서로 다른 RAM 뱅크들에 저장된다는 점을 확인하는 것은 쉽다. 그 결과, 위에서 언급된 APP 값들은 어떠한 경쟁이나 충돌도 없이 항상 동시에 액세스 가능하다.

[0048] 일례로, APP 값들을 8개의 인터리빙 하위 그룹들로 분할함으로써 상기 예의 이중 포트 RAM이 방지될 수 있는데, 각각의 하위 그룹은 개개의 단일 포트 RAM 파일에 저장된다. 단일 포트 RAM은 언제든 판독 또는 기록될 수 있다. 하나의 클록 사이클에서 각각의 RAM 파일로부터 하나씩 8개의 값들을 판독하고 다음 클록 사이클에서 각각의 RAM 파일에 대해 하나씩 8개의 값들을 기록하는 등에 의해 여전히 클록 사이클당 4회의 판독들 및 4회의 기록들이 달성될 수 있다.

[0049] 모든 코드 블록 크기들이 8의 배수들이라는 사실이 주어지면, 8개의 RAM 뱅크들 내의 APP 값들을 하나의 RAM 뱅크의 각각의 인터리빙 하위 그룹에 분배함으로써 8회까지의 동시에 APP 액세스들이 실행 가능하다. 16, 32 또는 64의 배수들인 큰 코드 블록 크기의 경우, 16, 32 또는 64개의 RAM 뱅크들 각각의 APP 값들을 하나의 RAM 뱅크에 저장된 각각의 인터리빙 하위 그룹에 분배함으로써 16, 32 또는 64회의 동시에 APP 액세스들이 이루어질 수 있다.

[0050] 이제 도 4를 참조하면, 대상의 혁신에 따른 4개의 하위 그룹들을 포함하는 예시적인 사후 확률(APP) 랜덤 액세스 메모리(RAM) 설계(400)가 예시된다. APP RAM 설계(400)는 (예를 들어, RAM0, RAM1, RAM2 및 RAM3으로 표시된) 4개의 파일들을 포함할 수 있다. APP 값들은 하나의 RAM 파일에 각각 저장되는 4개의 인터리빙 하위 그룹으로 분할된다.

[0051] TDEC는 터보 반복들 동안 인터리버 또는 디인터리버 어드레스들을 계산할 필요가 있다. 계산은 바로 QPP를 기반으로 한다. 각각의 클록 사이클 내에서 각각의 하위 그룹에 대한 하나의 인터리버 어드레스를 계산하기 위해, QPP 계산 로직은 각각의 하위 그룹에 대해 한 번씩 여러 번 예시될 필요가 있다.

[0052] 빠르게 도 5를 참조하면, radix-2 구성 및 radix-4 구성의 설계(500)가 도시된다. radix-2(502)뿐만 아니라 radix-4(504) 또한 예시될 수 있다. 터보 디코더 내의 MAP 디코더들은 radix-4 구성으로서 구현될 수 있는 것으로 인식되어야 한다. radix-4(504) 내에서, 하나의 클록 사이클에서 2개의 격자 전이들이 이동할 수 있다. 더욱이, radix-4(504) 내에는 더욱 복잡한 상태 메트릭 계산들이 존재한다. 따라서 radix-4(504)에서는, 각각의 클록 사이클 내에서 APP RAM으로부터의 2개의 값들이 액세스된다.

[0053] 도 6을 참조하면, 판독 또는 기록 동작들 동안 에러들을 감소시키기 위한 RAM의 세그먼트화에 관한 방법이 예시된다. 설명의 단순화를 위해, 방법들은 일련의 동작들로 도시되어 설명되지만, 하나 또는 그보다 많은 실시예들에 따라 일부 동작들은 여기서 도시 및 설명되는 것과 다른 순서들로 그리고/또는 다른 동작들과 동시에 일어날 수 있으므로 방법들은 이러한 동작들의 순서로 한정되지는 않는 것으로 이해 및 인식되어야 한다. 예를 들어, 기술분야에 통상의 지식을 가진 자들은 방법이 대안으로 상태도에서와 같이 일련의 상호 관련 상태들이나 이벤트들로서 표현될 수 있음을 이해 및 인식할 것이다. 더욱이, 하나 또는 그보다 많은 실시예들에 따른 방법을 구현하기 위해 설명되는 모든 동작들이 필요한 것은 아닐 수도 있다.

[0054] 이제 도 6을 참조하면, 비경쟁 메모리 액세스를 제공하는 터보 디코더의 이용을 용이하게 하는 방법(600)이 제공된다. 참조번호(602)에서, 사후 확률(APP) 랜덤 액세스 메모리(RAM)가 식별될 수 있다. 참조번호(604)에서, APP RAM이 적어도 2개의 파일들로 편성될 수 있다. 참조번호(606)에서, 2차 순열 디항식(QPP) 터보 인터리버를 기반으로 모든 APP 값들이 적어도 2개의 인터리빙 하위 그룹들로 분할될 수 있다. 참조번호(608)에서, 개별 인터리빙 하위 그룹들이 개별 RAM 파일들에 맵핑될 수 있다.

[0055] 도 7은 무선 통신 시스템에서 메모리 충돌들을 피하도록 터보 디코더에 대한 메모리의 일부의 편성을 용이하게 하는 모바일 디바이스(700)의 실례이다. 모바일 디바이스(700)는 예컨대, (도시되지 않은) 수신 안테나로부터 신호를 수신하고, 수신된 신호에 대해 일반적인 동작들을 수행(예를 들어, 필터링, 증폭, 하향 변환 등)하고, 조정된 신호를 디지털화하여 샘플들을 얻는 수신기(702)를 포함한다. 수신기(702)는 수신된 신호들을 복조하여 이를 채널 추정을 위해 프로세서(706)에 제공할 수 있는 복조기(704)를 포함할 수 있다. 프로세서(706)는 수신기(702)에 의해 수신되는 정보의 분석 및/또는 송신기(716)에 의한 송신을 위한 정보의 생성에 전용되는 프로세서, 모바일 디바이스(700)의 하나 또는 그보다 많은 컴포넌트들을 제어하는 프로세서, 및/또는 수신기(702)에

의해 수신되는 정보를 분석하기도 하고, 송신기(716)에 의한 송신을 위한 정보를 생성하기도 하고, 모바일 디바이스(700)의 하나 또는 그보다 많은 컴포넌트들을 제어하기도 하는 프로세서일 수 있다.

[0056] 모바일 디바이스(700)는 추가로, 프로세서(706)에 동작 가능하게 연결되며 전송될 데이터, 수신된 데이터, 이용 가능한 채널들에 관련된 정보, 간접 세기 및/또는 분석된 신호와 연관된 데이터, 할당된 채널, 전력, 레이트 등에 관련된 정보, 그리고 채널을 추정하고 채널을 통해 통신하기 위한 임의의 다른 적당한 정보를 저장할 수 있는 메모리(708)를 포함할 수 있다. 메모리(708)는 채널의 추정 및/또는 이용과 연관된 프로토콜들 및/또는 알고리즘들(예를 들어, 성능 기반, 용량 기반 등)을 추가로 저장할 수 있다.

[0057] 여기서 설명된 데이터 저장소(예를 들어, 메모리(708))는 휘발성 메모리 또는 비휘발성 메모리일 수 있고, 또는 휘발성 및 비휘발성 메모리를 모두 포함할 수 있는 것으로 인식될 것이다. 한정이 아닌 예시로, 비휘발성 메모리는 판독 전용 메모리(ROM: read only memory), 프로그램 가능 ROM(PROM: programmable ROM), 전기적으로 프로그램 가능한 ROM(EPROM: electrically programmable ROM), 전기적으로 소거 가능한 PROM(EEPROM: electrically erasable ROM) 또는 플래시 메모리를 포함할 수 있다. 휘발성 메모리는 외부 캐시 메모리 역할을 하는 랜덤 액세스 메모리(RAM)를 포함할 수 있다. 한정이 아닌 예시로, RAM은 동기식 RAM(SRAM: synchronous RAM), 동적 RAM(DRAM: dynamic RAM), 동기식 DRAM(SDRAM: synchronous DRAM), 2배속 SDRAM(DDR SDRAM: double data rate SDRAM), 확장 SDRAM(ESDRAM: enhanced SDRAM), 싱크링크 DRAM(SLRAM: Synclink DRAM) 및 다이렉트 램버스 RAM(DRRAM: direct Rambus RAM)과 같은 많은 형태들로 이용 가능하다. 해당 시스템들 및 방법들의 메모리(708)는 이에 한정되지 않으면서 이러한 그리고 임의의 다른 적당한 타입들의 메모리를 포함하는 것으로 의도된다.

[0058] 프로세서(706)는 평가 모듈(710) 및/또는 편성 모듈(712)에 동작 가능하게 추가로 연결될 수 있다. 평가 모듈(710)은 APP RAM의 일부를 식별하여 검사할 수 있다. 더욱이, 편성 모듈(712)은 메모리 경쟁 및/또는 메모리 충돌을 방지하기 위해 세그먼트가 터보 디코더 내의 MAP 디코더에 대응할 수 있도록 APP RAM을 세그먼트화 또는 분할할 수 있다. 편성 모듈(712)은 2차 순열 다항식(QPP) 터보 인터리버를 기반으로 모든 APP 값들을 적어도 2개의 인터리빙 하위 그룹들로 나눌 수 있다. 편성 모듈(712)은 개별 인터리빙 하위 그룹들을 개별 RAM 파일들에 맵핑할 수 있다.

[0059] 모바일 디바이스(700)는 각각 신호들을 변조하여, 예컨대 기지국, 다른 모바일 디바이스 등으로 전송하는 변조기(714) 및 송신기(716)를 더 추가로 포함한다. 프로세서(706)와 별개인 것으로 도시되어 있지만, 평가 모듈(710), 편성 모듈(712), 복조기(704) 및/또는 변조기(714)는 프로세서(706) 또는 (도시되지 않은) 다수의 프로세서들의 일부일 수 있는 것으로 인식되어야 한다.

[0060] 도 8은 위에서 설명된 바와 같은 무선 통신 환경에서 메모리 충돌들을 피하도록 사후 확률(APP) 랜덤 액세스 메모리(RAM)의 분할을 용이하게 하는 시스템(800)의 실례이다. 시스템(800)은 다수의 수신 안테나들(806)을 통해 하나 또는 그보다 많은 모바일 디바이스들(804)로부터 신호(들)를 수신하는 수신기(810), 및 송신 안테나(808)를 통해 하나 또는 그보다 많은 모바일 디바이스들(804)로 전송하는 송신기(824)를 구비한 기지국(802)(예를 들어, 액세스 포인트, ...)을 포함한다. 수신기(810)는 수신 안테나들(806)로부터 정보를 수신할 수 있으며, 수신된 정보를 복조하는 복조기(812)와 동작 가능하게 연관된다. 복조된 신호들은 도 7과 관련하여 위에서 설명된 프로세서와 유사할 수 있으며, 신호(예를 들어, 파일럿) 세기 및/또는 간접 세기의 추정과 관련된 정보, 모바일 디바이스(들)(804)로 전송될 또는 모바일 디바이스(들)(804)(또는 (도시되지 않은) 다른 기지국)로부터 수신되는 데이터, 및/또는 본원에 제시된 다양한 동작들 및 기능들의 수행과 관련된 임의의 다른 적당한 정보를 저장하는 메모리(816)에 연결되는 프로세서(814)에 의해 분석된다.

[0061] 프로세서(814)는 또한 평가 모듈(818) 및/또는 편성 모듈(820)에 연결된다. 평가 모듈(818)은 APP RAM을 그리고 그와 연관된 크기로서 식별할 수 있다. 편성 모듈(820)은 각각의 파일 및/또는 하위 그룹 간의 분리(isolation)를 보장하기 위해 APP RAM 내에 적어도 2개의 파일들 및 각각의 파일 내의 하위 그룹들을 생성할 수 있다. 편성 모듈(820)은 2차 순열 다항식(QPP) 터보 인터리버를 기반으로 모든 APP 값들을 적어도 2개의 인터리빙 하위 그룹들로 나눌 수 있다. 편성 모듈(820)은 개별 인터리빙 하위 그룹들을 개별 RAM 파일들에 맵핑할 수 있다. 더욱이, 프로세서(814)와 별개인 것으로 도시되어 있지만, 평가 모듈(818), 편성 모듈(820), 복조기(812) 및/또는 변조기(822)는 프로세서(814) 또는 (도시되지 않은) 다수의 프로세서들의 일부일 수 있는 것으로 인식되어야 한다.

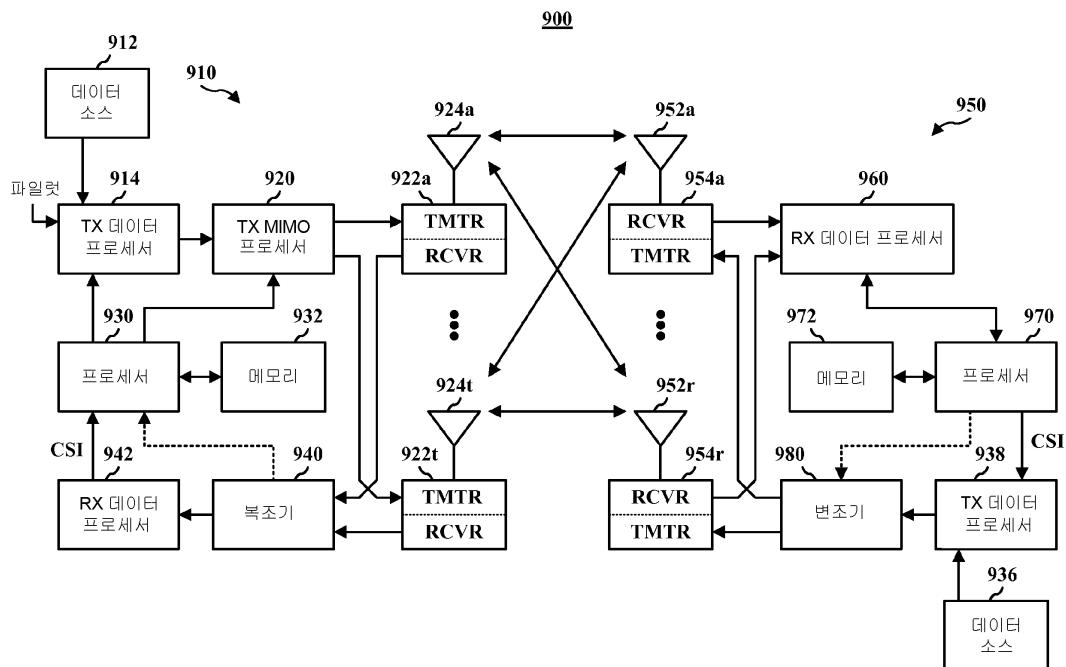

[0062] 도 9는 예시적인 무선 통신 시스템(900)을 나타낸다. 무선 통신 시스템(900)은 간결성을 위해 하나의 기지국(910) 및 하나의 모바일 디바이스(950)를 나타낸다. 그러나 시스템(900)은 하나보다 많은 수의 기지국 및/또는

하나보다 많은 수의 모바일 디바이스를 포함할 수 있으며, 추가 기지국들 및/또는 모바일 디바이스들은 아래에 설명되는 예시적인 기지국(910) 및 모바일 디바이스(950)와 실질적으로 유사할 수 있거나 상이할 수 있는 것으로 인식되어야 한다. 또한, 기지국(910) 및/또는 모바일 디바이스(950)는 여기서 설명된 시스템들(도 1 - 도 3 및 도 7 - 도 8), 기술들/구성들(도 4 - 도 5) 및/또는 방법들(도 6)을 이용하여 그 사이의 무선 통신을 용이하게 할 수 있는 것으로 인식되어야 한다.

[0063] 기지국(910)에서는, 다수의 데이터 스트림들에 대한 트래픽 데이터가 데이터 소스(912)로부터 송신(TX) 데이터 프로세서(914)로 제공된다. 일례에 따르면, 각각의 데이터 스트림은 각각의 안테나를 통해 전송될 수 있다. TX 데이터 프로세서(914)는 해당 데이터 스트림에 대해 선택된 특정 코딩 방식을 기초로 트래픽 데이터 스트림을 포맷화, 코딩 및 인터리빙하여 코딩된 데이터를 제공한다.

[0064] 각각의 데이터 스트림에 대한 코딩된 데이터는 직교 주파수 분할 다중화(OFDM) 기술들을 이용하여 파일럿 데이터와 다중화될 수 있다. 추가로 또는 대안으로, 파일럿 심벌들은 주파수 분할 다중화(FDM), 시분할 다중화(TDM) 또는 코드 분할 다중화(CDM)될 수 있다. 파일럿 데이터는 일반적으로, 공지된 방식으로 처리되는 공지된 데이터 패턴이며 채널 응답을 추정하기 위해 모바일 디바이스(950)에서 사용될 수 있다. 각각의 데이터 스트림에 대한 다중화된 파일럿 및 코딩된 데이터는 해당 데이터 스트림에 대해 선택된 특정 변조 방식(예를 들어, 이진 위상 시프트 키잉(BPSK: binary phase-shift keying), 직각 위상 시프트 키잉(QPSK: quadrature phase-shift keying), M-위상 시프트 키잉(M-PSK: M-phase-shift keying), M-직각 진폭 변조(M-QAM: M-quadrature amplitude modulation) 등)을 기초로 변조(예를 들어, 심벌 맵핑)되어 변조 심벌들을 제공할 수 있다. 각각의 데이터 스트림에 대한 데이터 레이트, 코딩 및 변조는 프로세서(930)에 의해 수행 또는 제공되는 명령들에 의해 결정될 수 있다.

[0065] 데이터 스트림들에 대한 변조 심벌들은 TX MIMO 프로세서(920)에 제공될 수 있고, TX MIMO 프로세서(920)는 (예를 들어, OFDM을 위해) 변조 심벌들을 추가 처리할 수 있다. 그 다음, TX MIMO 프로세서(920)는  $N_t$ 개의 변조 심벌 스트림들을  $N_t$ 개의 송신기들(TMTR; 922a-922t)에 제공한다. 다양한 실시예들에서, TX MIMO 프로세서(920)는 데이터 스트림들의 심벌들 및 안테나에 빔 형성 가중치들을 적용하는데, 상기 안테나로부터 심벌이 전송되고 있다.

[0066] 각각의 송신기(922)는 각각의 심벌 스트림을 수신 및 처리하여 하나 또는 그보다 많은 아날로그 신호들을 제공하며, 아날로그 신호들을 추가 조정(예를 들어, 증폭, 필터링 및 상향 변환)하여 MIMO 채널을 통한 송신에 적합한 변조된 신호를 제공한다. 또한, 송신기들(922a-922t)로부터의  $N_t$ 개의 변조된 신호들은  $N_t$ 개의 안테나들(924a-924t)로부터 각각 전송된다.

[0067] 모바일 디바이스(950)에서, 전송된 변조 신호들은  $N_r$ 개의 안테나들(952a-952r)에 의해 수신되고, 각각의 안테나(952)로부터의 수신 신호는 각각의 수신기(RCVR; 954a-954r)에 제공된다. 각각의 수신기(954)는 각각의 신호를 조정(예를 들어, 필터링, 증폭 및 하향 변환)하고, 조정된 신호를 디지털화하여 샘플들을 제공하며, 샘플들을 추가 처리하여 대응하는 "수신" 심벌 스트림을 제공한다.

[0068] RX 데이터 프로세서(960)는 특정 수신기 처리 기술을 기반으로  $N_r$ 개의 수신기들(954)로부터  $N_r$ 개의 수신 심벌 스트림들을 수신하고 처리하여  $N_r$ 개의 "검출된" 심벌 스트림들을 제공할 수 있다. RX 데이터 프로세서(960)는 각각의 검출된 심벌 스트림을 복조, 디인터리빙 및 디코딩하여 데이터 스트림에 대한 트래픽 데이터를 복원할 수 있다. RX 데이터 프로세서(960)에 의한 처리는 기지국(910)에서의 TX MIMO 프로세서(920) 및 TX 데이터 프로세서(914)에 의해 수행되는 처리와 상보적이다.

[0069] 프로세서(970)는 위에서 논의된 바와 같이 어떤 프리코딩 행렬을 이용할지를 주기적으로 결정할 수 있다. 또한, 프로세서(970)는 행렬 인덱스 부분 및 랭크값 부분을 포함하는 역방향 링크 메시지를 형식화(formulate)할 수 있다.

[0070] 역방향 링크 메시지는 통신 링크 및/또는 수신된 데이터 스트림에 관한 다양한 타입들의 정보를 포함할 수 있다. 역방향 링크 메시지는 데이터 소스(936)로부터 다수의 데이터 스트림들에 대한 트래픽 데이터를 또한 수신하는 TX 데이터 프로세서(938)에 의해 처리되고, 변조기(980)에 의해 변조되고, 송신기들(954a-954r)에 의해 조정되어, 다시 기지국(910)으로 전송될 수 있다.

[0071] 기지국(910)에서, 모바일 디바이스(950)에 의해 전송된 역방향 링크 메시지를 추출하기 위해, 모바일 디바이스

(950)로부터의 변조된 신호들이 안테나들(924)에 의해 수신되고, 수신기들(922)에 의해 조정되며, 복조기(940)에 의해 복조되고, RX 데이터 프로세서(942)에 의해 처리된다. 또한, 프로세서(930)는 추출된 메시지를 처리하여, 범 형성 가중치들을 결정하기 위해 어떤 프리코딩 행렬을 사용할지를 결정할 수 있다.

[0072] 프로세서들(930, 970)은 각각 기지국(910) 및 모바일 디바이스(950)에서의 동작을 지시(direct)(예를 들어, 제어, 조정, 관리 등)할 수 있다. 각각의 프로세서들(930, 970)은 프로그램 코드들 및 데이터를 저장하는 메모리(932, 972)와 연관될 수 있다. 프로세서들(930, 970)은 또한 각각 업링크 및 다운링크에 대한 주파수 및 임펄스 응답 추정치들을 도출하기 위한 계산들을 수행할 수 있다.

[0073] 여기서 설명된 실시예들은 하드웨어, 소프트웨어, 펌웨어, 미들웨어, 마이크로코드 또는 이들의 임의의 결합으로 구현될 수 있는 것으로 이해되어야 한다. 하드웨어 구현의 경우, 처리 유닛들이 하나 또는 그보다 많은 주문형 집적 회로(ASIC: application specific integrated circuit)들, 디지털 신호 프로세서(DSP: digital signal processor)들, 디지털 신호 처리 디바이스(DSPD; digital signal processing device)들, 프로그래밍 가능 로직 디바이스(PLD: programmable logic device)들, 필드 프로그래밍 가능 게이트 어레이(FPGA: field programmable gate array)들, 프로세서들, 제어기들, 마이크로컨트롤러들, 마이크로프로세서들, 여기서 설명된 기능들을 수행하도록 설계된 다른 전자 유닛들, 또는 이들의 결합 내에 구현될 수 있다.

[0074] 실시예들이 소프트웨어, 펌웨어, 미들웨어 또는 마이크로코드, 프로그램 코드 또는 코드 세그먼트들로 구현될 때, 이들은 저장 컴포넌트와 같은 기계 판독 가능 매체에 저장될 수 있다. 코드 세그먼트는 프로시저, 함수, 하위 프로그램, 프로그램, 루틴, 하위 루틴, 모듈, 소프트웨어 패키지, 클래스, 또는 명령들, 데이터 구조들 또는 프로그램 명령문들의 임의의 결합을 나타낼 수 있다. 코드 세그먼트는 정보, 데이터, 인수(argument)들, 파라미터들 또는 메모리 컨텐츠를 전달 및/또는 수신함으로써 다른 코드 세그먼트 또는 하드웨어 회로에 연결될 수 있다. 정보, 인수들, 파라미터들, 데이터 등은 메모리 공유, 메시지 전달, 토큰 전달, 네트워크 송신 등을 포함하는 임의의 적절한 수단을 이용하여 전달되거나, 포워딩되거나 또는 전송될 수 있다.

[0075] 소프트웨어 구현의 경우, 여기에서 설명된 기술들은 여기에서 설명된 기능들을 수행하는 모듈들(예를 들어, 프로시저들, 기능들 등)로 구현될 수 있다. 소프트웨어 코드들은 메모리 유닛들에 저장되어 프로세서들에 의해 실행될 수 있다. 메모리 유닛은 프로세서 내에 또는 프로세서 외부에 구현될 수 있으며, 이 경우 메모리 유닛은 기술분야에 공지된 바와 같이 다양한 수단을 통해 프로세서에 통신하도록 연결될 수 있다.

[0076] 도 10을 참조하면, 비경쟁 메모리 액세스를 제공하는 터보 디코더를 이용하는 시스템(1000)이 설명된다. 예를 들어, 시스템(1000)은 기지국, 모바일 디바이스 등의 내부에 적어도 부분적으로 상주할 수 있다. 시스템(1000)은 프로세서, 소프트웨어, 또는 이들의 결합(예를 들어, 펌웨어)에 의해 구현되는 기능들을 나타내는 기능 블록들일 수 있는 기능 블록들을 포함하는 것으로 표현되는 것으로 인식되어야 한다. 시스템(1000)은 결합하여 작동할 수 있는 전기 컴포넌트들의 논리 그룹(1002)을 포함한다. 예컨대, 논리 그룹(1002)은 사후 확률(APP) 랜덤 액세스 메모리(RAM)를 식별하기 위한 전기 컴포넌트(1004)를 포함할 수 있다. 또한, 논리 그룹(1002)은 APP RAM을 적어도 2개의 파일들로 편성하기 위한 전기 컴포넌트(1006)를 포함할 수 있다. 더욱이, 논리 그룹(1002)은 2차 순열 다향식(QPP) 터보 인터리버를 기반으로 모든 APP 값들을 적어도 2개의 인터리빙 하위 그룹들로 분할하기 위한 전기 컴포넌트(1008)를 포함할 수 있다. 또한, 논리 그룹(1002)은 개별 인터리빙 하위 그룹들을 개별 RAM 파일들에 맵핑하기 위한 전기 컴포넌트(1010)를 포함할 수 있다. 추가로, 시스템(1000)은 전기 컴포넌트들(1004, 1006, 1008, 1010)과 연관된 기능들을 실행하기 위한 명령들을 보유하는 메모리(1012)를 포함할 수 있다. 메모리(1012) 외부에 있는 것으로 도시되었지만, 전기 컴포넌트들(1004, 1006, 1008, 1010) 중 하나 또는 그보다 많은 전기 컴포넌트는 메모리(1012) 내부에 존재할 수 있는 것으로 이해되어야 한다.

[0077] 위에서 설명된 것은 하나 또는 그보다 많은 실시예들의 예들을 포함한다. 물론, 위에서 언급된 실시예들을 설명할 목적으로 컴포넌트들 또는 방법들의 착안 가능한 모든 조합을 설명하는 것은 가능하지 않지만, 기술분야에서 통상의 지식을 가진 자는 다양한 실시예들의 많은 추가적인 조합들 및 치환들이 가능하다는 점을 인지할 수 있다. 그에 따라, 설명된 실시예들은 첨부된 청구항들의 사상 및 범위 내에 있는 이러한 모든 변경들, 수정들 및 변형들을 포함하는 것으로 의도된다. 더욱이, "포함한다(include)"라는 용어가 상세한 설명 또는 청구항들에 사용되는 경우에, 이러한 용어는 "포함하는(comprising)"이라는 용어가 청구항에서 전이어(transitional word)로서 사용될 때 해석되는 것과 같이, "포함하는(comprising)"과 비슷한 식으로 포함하는 것으로 의도된다.

도면

도면1

도면2

## 도면3

## 도면4

## 도면5

## 도면6

## 도면7

## 도면8

## 도면9

## 도면10